Page 1

S-14801XZ-C1

Apr. 2011

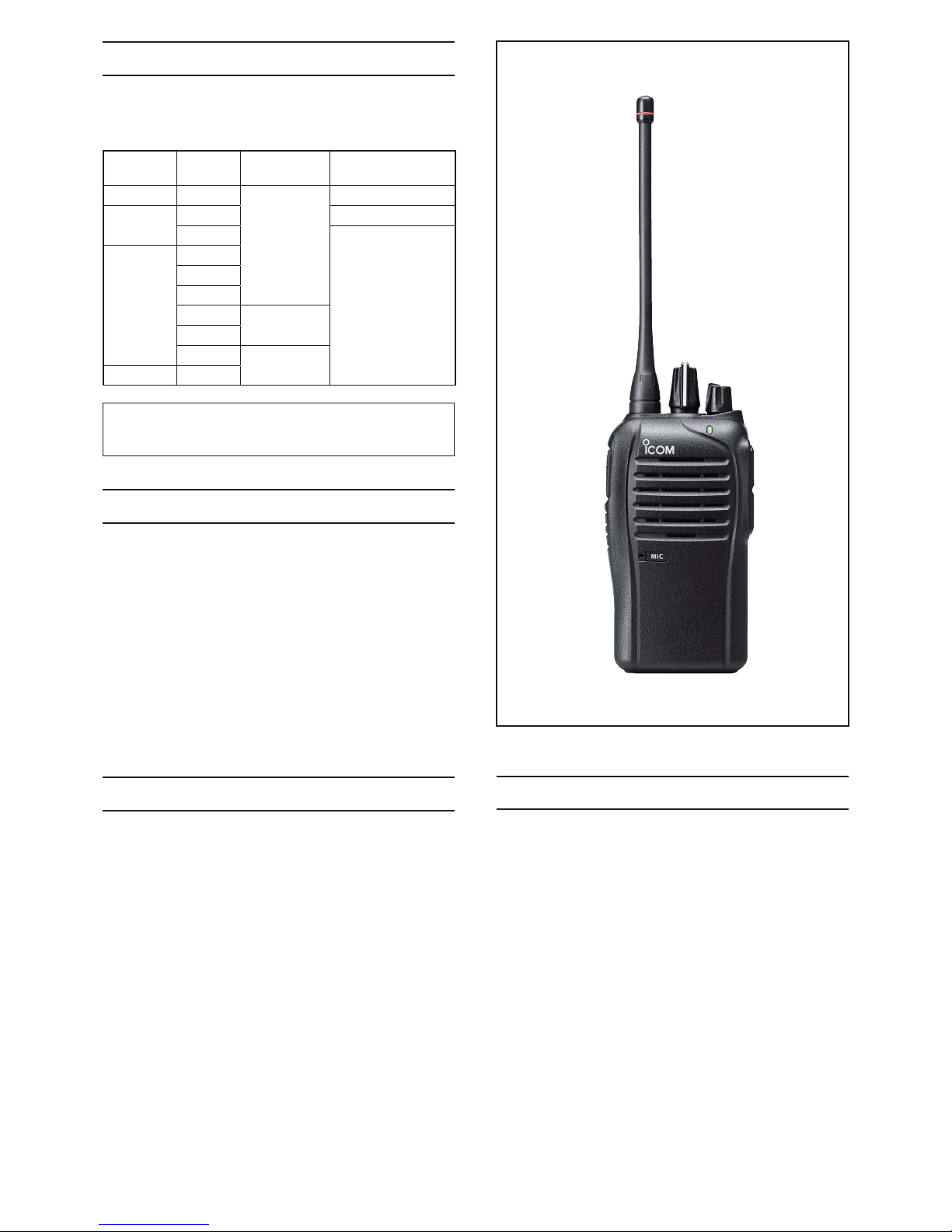

UHF TRANSCEIVERS

Page 2

This service manual describes the latest technical

information for the IC-F4101D, IC-F4102D, IC-F4103D and

IC-F4106D

UHF TRANSCEIVERS, at the time of publication.

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than the specified voltage.

This will ruin the transceiver.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when

connecting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW) to

the antenna connector. This could damage the transceiver’s

front-end.

To upgrade quality, any electrical or mechanical parts

and internal circuits are subject to change without notice

or obligation.

MODEL VERSION

FREQUENCY

RANGE (MHz)

CHANNEL

SPACING (kHz)

IC-F4101D USA-01

400–470

6.25/12.5

IC-F4102D

EUR-01 6.25/12.5/20.0/25.0

UK-01

6.25/12.5/25.0IC-F4103D

EXP-01

EXP-02

EXP-03

EXP-07

350–400

EXP-08

AUS-01

400–470

IC-F4106D RUS-01

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit Icom part number

2. Component name

3. Equipment model name and unit name

4. Quantity required

<ORDER EXAMPLE>

1110003491 S.IC TA31136FNG IC-F4101D MAIN UNIT 5 pieces

8820001210 Screw 2438 screw IC-F4101D Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

ORDERING PARTS

1. Make sure that the problem is internal before disassembling the transceiver.

2. DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn them

slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An

insulated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the

transceiver is defective.

6. DO NOT transmit power into a Standard Signal Generator

or a Sweep Generator.

7. ALWAYS connect a 30 dB to 40 dB attenuator between

the transceiver and a Deviation Meter or Spectrum

Analyzer, when using such test equipment.

8. READ the instructions of the test equipment throughly

before connecting it to the transceiver.

REPAIR NOTES

INTRODUCTION

CAUTION

Icom, Icom Inc. and the Icom logo are registered trademarks of Icom Incorporated (Japan) in Japan, the United States, the

United Kingdom, Germany, France, Spain, Russia and/or other countries.

Page 3

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASSEMBLY INSTRUCTION

SECTION 4 CIRCUIT DESCRIPITON

4-1 RECEIVER CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4-2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4-3 FREQUENCY SYNTHESIZER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4-4 VOLTAGE DIAGRAMS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4-5 PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5-2 FREQUENCY ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5-3 TRANSMIT ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5-4 RECEIVE ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

SECTION 6 PARTS LIST

SECTION 7 MECHANICAL PARTS

SECTION 8 BOARD LAYOUTS

SECTION 9 BLOCK DIAGRAM

SECTION 10 VOLTAGE DIAGRAM

Page 4

1 - 1

SECTION 1. SPECIFICATIONS

M GENERAL

• Frequency range : 400–470 MHz [USA-01], [EUR-01], [UK-01], [EXP-01], [EXP-02], [EXP-03],

[AUS-01], [RUS-01]

350–400 MHz [EXP-07], [EXP-08]

• Number of conventional channels : 16

• Type of emission : Wide 16K0F3E (30.0 kHz) Except [USA], [EUR], [UK]

16K0F3E (25.0 KHz) Except [USA]

Middle 14K0F3E (20.0 kHz) [EUR], [UK] only

Narrow 11K0F3E (15.0 kHz) Except [EUR], [UK]

8K50F3E (12.5 kHz)

Digital 4K00F1E, D (6.25 kHz)

• Antenna impedance : 50 Ω (nominal)

• Operating temperature range : –30˚C to +60˚C; –22˚F to +140˚F Except [EUR], [UK]

–25˚C to +55˚C [EUR], [UK]

• Power supply voltage : Specifi ed Icom's battery packs only (7.5 V DC; negative ground)

• Current drain (approximately) : Receiving 100 mA (in digital mode, stand-by)

400 mA (max. audio, with the internal speaker)

Transmitting 1.3 A (4 W)

• Dimensions

(projections not included)

: 58.0 (W)×111.0 (H)×36.5 (D) mm; 2.3 (W)×4.4 (H)×1.4 (D) in. (with BP-265)

• Weight (approximately) : 150 g; 5.3 oz.

310 g; 10.9 oz. (including MB-124, BP-265, FA-SC57U)

M TRANSMITTER

• Output power : 4 W

• Modulation : Variable reactance frequency modulation

• Maximum frequency deviation : Narrow ±2.5 kHz

Middle ±4.0 kHz [EUR], [UK] only

Wide ±5.0 kHz Except [USA]

• Frequency stability : ±1.0 ppm

• Spurious emissions : 70 dB min. Except [EUR], [UK]

0.25 µW (

≤

1 GHz)

[EUR], [UK]

1.00 µW (

>

1 GHz)

[EUR], [UK]

• Adjacent channel power : Narrow 60 dB min., 70 dB typ.

Middle 70 dB min., [EUR], [UK] only

Wide 70 dB min., 74 dB typ. Except [USA]

Digital 60 dB min., 66 dB typ.

• Audio harmonic distortion : 1.0% typ. (at AF 1 kHz, 40% deviation)

• FSK error : 5% max.

• FM hum and Noise (Except [EUR], [UK])

(without CCITT Filter)

: Narrow 34 dB min., 44 dB typ.

Wide 40 dB min., 50 dB typ. Except [USA]

• Rasidual modulation ([EUR], [UK] only)

(with CCITT Filter)

: Narrow 40 dB min.

Middle 43 dB min.

Wide 45 dB min.

• Limitting charact of modulator : 60–100% of max. deviation

• Input impedance (MIC) : 2.2 k

Ω

Page 5

1 - 2

M RECEIVER

• Sensitivity : 0.24 µV typ. at 12 dB SINAD Except [EUR], [UK]

–4 dBµV (EMF) typ. at 20 dB SINAD [EUR], [UK]

–8 dBµV (EMF) typ. at 5% BER [Digital mode]

• Squelch sensitivity (at threshold) : 0.20 µV typ. Except [EUR], [UK]

–8 dBµV (EMF) typ. [EUR], [UK]

• Intermediate frequency : 1st IF; 46.35 MHz, 2nd IF; 450 kHz

• Adjacent channel selectivity : Narrow 60 dB min., 67 dB typ.

Middle 70 dB min. [EUR], [UK] only

Wide 70 dB min., 74 dB typ. Except [USA]

Digital 50 dB min., 58 dB typ.

• Spurious response : 70 dB min., 80 dB typ.

• Intermodulation : Narrow 70 dB min., 75 dB typ. Except [EUR], [UK]

Wide 70 dB min., 75 dB typ. Except [EUR], [UK], [USA]

Digital 65 dB min., 70 dB typ. Except [EUR], [UK]

65 dB min. [EUR], [UK]

• FM hum and Noise (Except [EUR], [UK])

(without CCITT Filter)

: Narrow 34 dB min., 42 dB typ.

Wide 40 dB min., 47 dB typ. Except [USA]

• FM hum and Noise ([EUR], [UK])

(with CCITT Filter)

: Narrow 40 dB min.

Middle 43 dB min.

Wide 45 dB min.

• Audio output power : 0.8 W typ. at 5% distorsion with a12 Ω load (internal speaker)

0.4 W typ. at 5% distorsion With an 8 Ω (external speaker)

• Audio output impedance : 8

Ω

Measurements made in accordance with TIA-603, EN 300 086 or EN 301 166.

All stated specifi cations are subject to change without notice or obligation.

Page 6

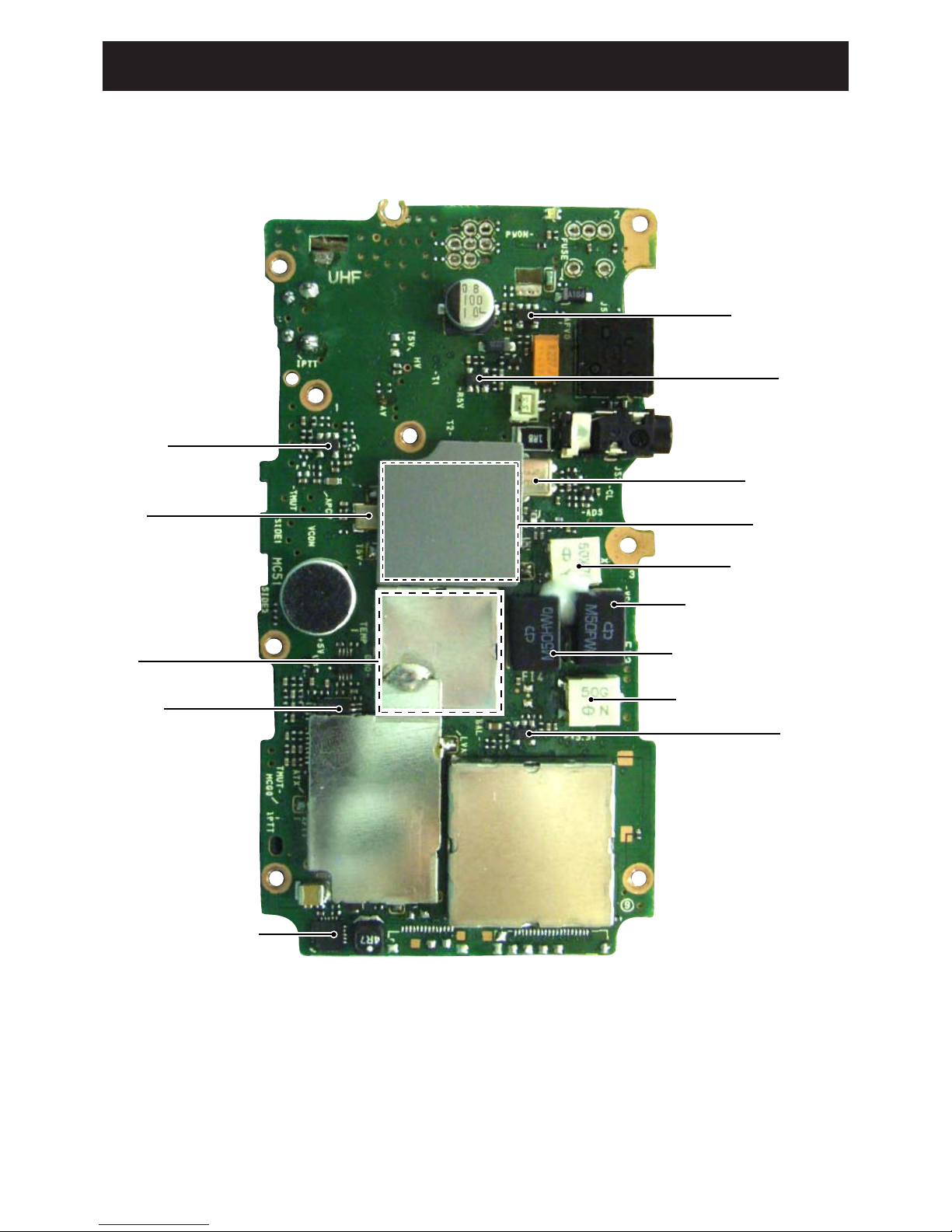

2 - 1

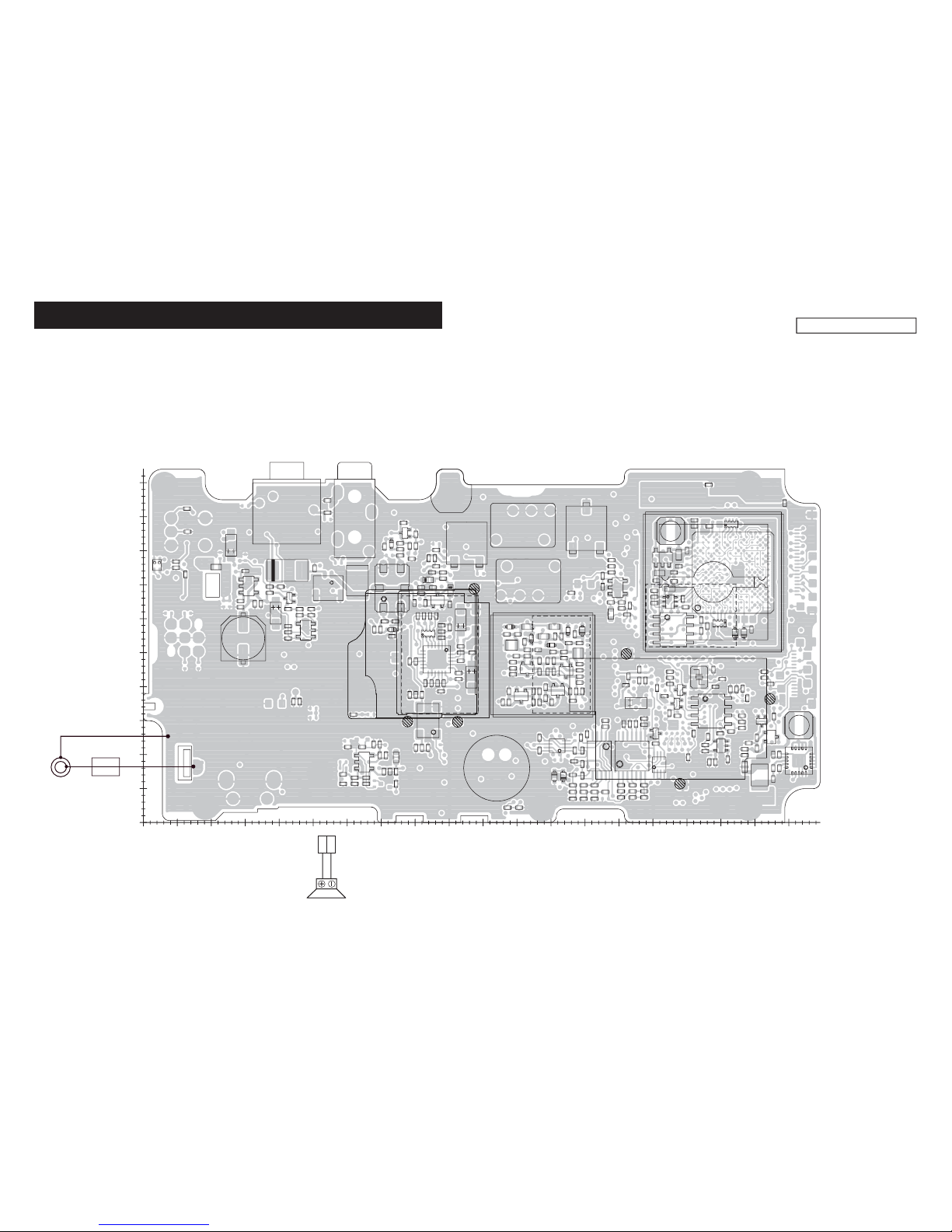

SECTION 2. INSIDE VIEWS

• MAIN-A/MAIN-C UNIT

(TOP VIEW)

VCO

5 V REGULATOR

(IC54)

PLL CIRCUIT

APC AMP

(IC1)

TCXO

(X2)

3.3 V DC-DC CONVERTER

(IC65)

MIC AMP

(IC64)

2ND IF FILTER (For wide)

(FI3)

1ST IF FILTER

(FI2)

DISCRIMINATOR

(X1)

2ND IF FILTER (For narrow)

(FI4)

2ND IF FILTER (For digital)

(FI5)

AF AMP

(IC21)

AF AMP

(IC58)

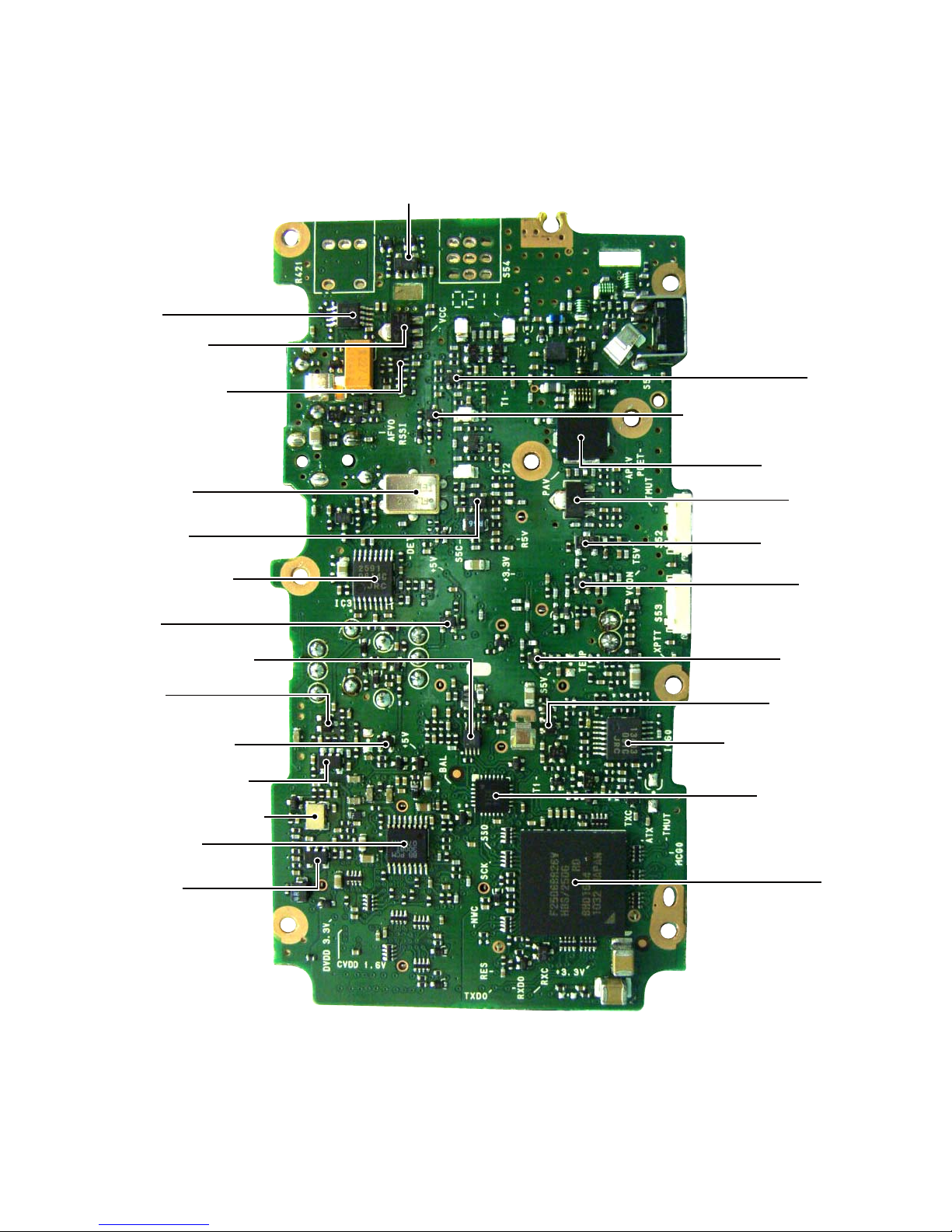

Page 7

2 - 2

• MAIN-A/MAIN-C UNIT

(BOTTOM VIEW)

TX POWER AMP

(Q1)

BUFFER

(Q28)

PLL LOCK VOLTAGE SW

(IC6)

CLOCK AMP

(IC905)

2ND IF AMP (For digital)

(IC5)

AF POWER AMP SW

(Q64)

DRIVE AMP

(Q2)

PRE-DRIVE AMP

(Q3)

PRE AMP

(Q4)

RF AMP

(Q22)

RF AMP GATE BIAS CONTROL

(Q21)

AF AMP

(IC55)

IF DEMODULATOR IC

(IC3)

BUFFER

(Q17)

1ST IF FILTER

(FI1)

R5 LINE REGULATOR

(Q72)

RIPPLE FILTER

(Q15)

1ST IF MIXER

(Q23)

AF POWER AMP

CONTROLLER

(Q63)

LINEAR CODEC

(IC902)

LINEAR CODEC/DSP CLOCK

(X900)

D/A CONVERTER

(IC57)

LPF/BUFFER/VOX AMP

(IC60)

CPU

(IC51)

PLL BUFFER

(Q9)

VCC LINE SW

(Q92)

Page 8

3 - 1

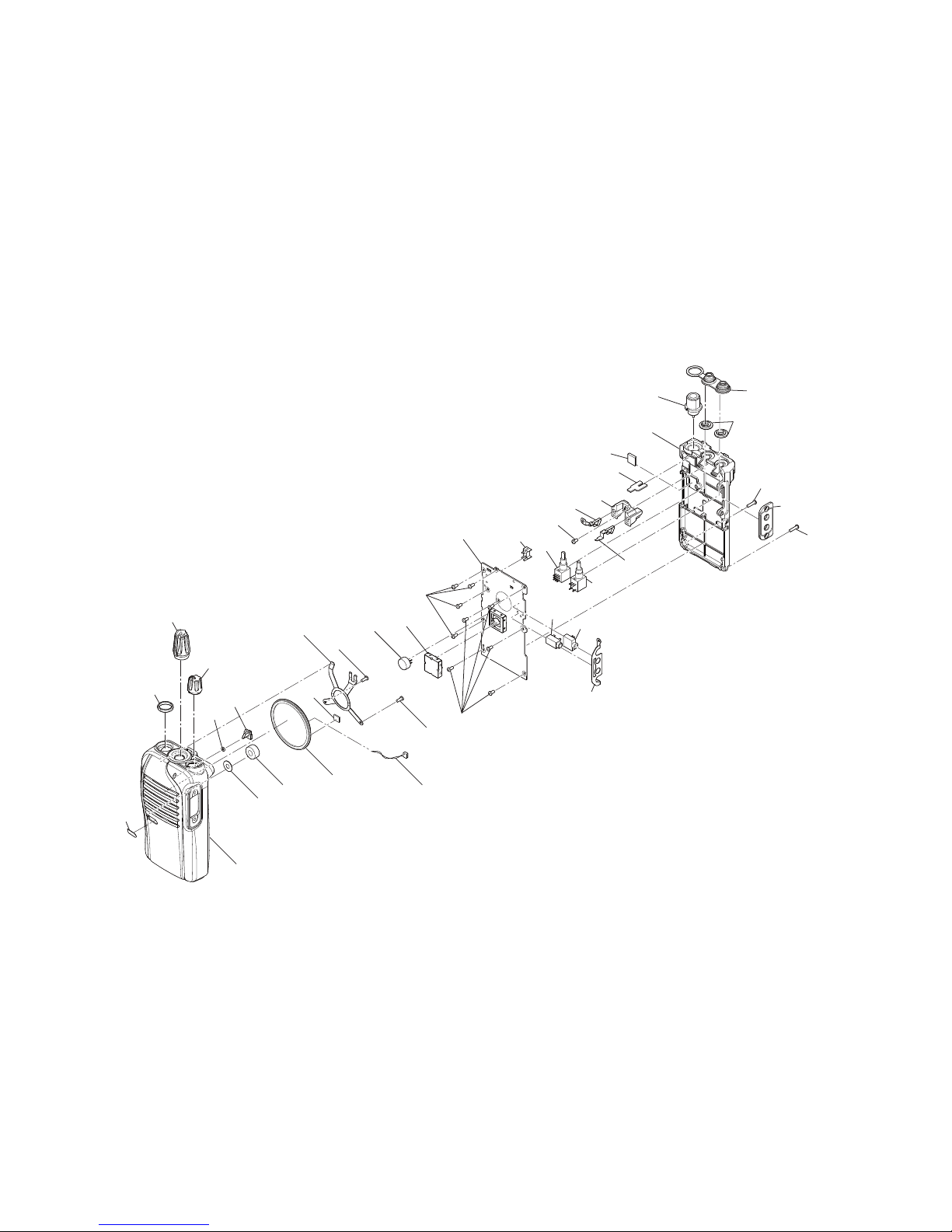

SECTION 3. DISASSEMBLY INSTRUCTION

3 - 1

BE CAREFUL to not pull out the speaker wire when

separating the CHASSIS and the FRONT PANEL.

For easy separation of the CHASSIS

Use a suction lifter to lift the bottom of the CHASSIS up.

1. REMOVING THE CHASSIS

1) Remove the ANT connector nut and 2 knobs.

2. REMOVING THE MAIN UNIT

1) Remove the 9 screws and the side plate from the

MAIN UNIT.

2) Unsolder the 2 points shown, and then remove the

MAIN UNIT.

2) Remove 2 screws from the bottom of the CHASSIS.

3) Lift the bottom of the CHASSIS up in the direction

of the arrow.

4)

CAREFULLY lift the chassis out of the FRONT PANEL

and turn it over in order to unplug the speaker wire.

(Continued on the right above)

5) Remove the seals and nuts from the CHASSIS.

ANT CONNECTOR NUT

KNOB

FRONT PANEL

Remove with;

“ICOM Driver (K)”

(8960000110)

FRONT PANEL

CHASSIS

SCREW×2

SPEAKER

WIRE

CHASSIS

FRONT PANEL

TOP SEAL

NUT×2

SIDE SEAL

CHASSIS

Remove with;

“ICOM Driver (AG)”

(8960000560)

UNSOLDER

Solder

remover

CHASSIS

SCREW×9

PCB

MAIN UNIT

SIDE PLATE

Suction lifter

Suction lifter

• Part name : EA950R-2

• Manufacture : ESCO CO.LTD

Page 9

4 - 1

SECTION 4. CIRCUIT DESCRIPTION

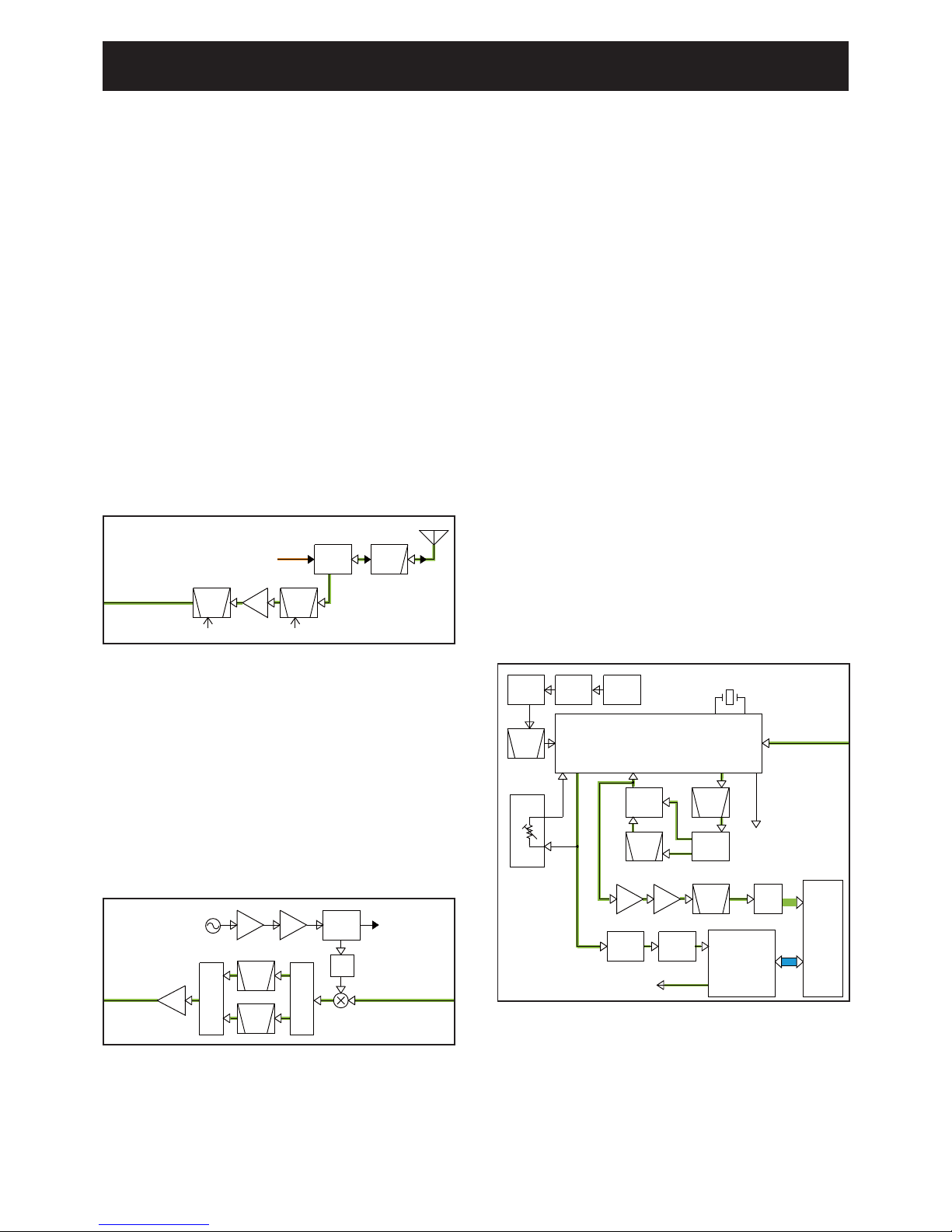

4-1 RECEIVER CIRCUITS

RF CIRCUITS

The RX signal from the antenna is passed through the LPF

and antenna SW (D3, D22), then filtered by the 2-staged

tuned BPF (D24 and D26) to eliminate unwanted out-ofband signals. The filtered RX signal is amplified by the RF

AMP (Q22), and filtered by another 2-staged tuned BPF

(D28) to obtain a good image response, then applied to the

1st IF circuits.

The BPFs are tuned to the RX frequency by applying adequate tuning voltages: “T1” and “T2” to the variable capacitors.

1ST IF CIRCUITS

The RX signal from the RF circuits is applied to the 1st IF

mixer (Q23) and mixed with the 1st LO signal from the RX

VCO, resulting in the 46.35 MHz 1st IF signal. The 1st IF signal is passed through the IF SWs (D31–D34) and the crystal

fi lter (FI1: analog mode, FI2: digital mode) to be fi ltered, amplified by the 1st IF AMP (Q24), then applied to the 2nd IF

circuits.

2ND IF AND DEMODULATOR CIRCUITS

The signal from the 1st IF circuits is applied to the IF demodulator IC (IC3) which contains the 2nd IF mixer, 2nd IF AMP,

FM detector, squelch circuit and AF AMP in its package.

The 1st IF signal is applied to the 2nd IF mixer and mixed

with the 2nd LO signal resulting in the 450 kHz 2nd IF signal.

The 2nd LO signal is generated by tripling the 15.3 MHz

reference frequency signal generated by the reference frequency oscillator (TCXO; X2).

• WHILE OPERATING IN THE ANALOG MODE

The 2nd IF signal is filtered by the 2nd IF filter (FI3: wide/

middle mode) or fi lters (FI3 and FI4: narrow) to eliminate unwanted signals. It is amplifi ed by the 2nd IF AMP, and then

demodulated by the detector circuit, which employs the discriminator (X1) as the phase shifter.

The demodulated AF signal is amplified by the AF AMP

(IC21), and then applied to the linear codec (IC902) through

the fi lter SW (Q901). The fi lter SW toggles the frequency response of the AF fi lter (R904, R908, C924), according to the

type of reception; Wide, Mid or Narrow.

The AF signal is converted into a digital audio signal by the

linear codec (IC902), processed by the DSP (IC903), and

then decoded into an analog audio signal.

• WHILE OPERATING IN THE DIGITAL MODE

The 2nd IF signal is fi ltered by the 2nd IF fi lters (FI3 and FI4)

to eliminate unwanted signals and applied to the IF AMP

(IC5) through the buffer (Q28). The amplifi ed 2nd IF signal is

passed through the ceramic fi lter (FI5), and then directly applied to the DSP (IC903).

The 2nd IF signal is demodulated by the DSP (IC903), and

then applied to the linear codec (IC902) to be decoded into

an analog audio signal.

The AF signal is applied to the RX AF circuits.

LPF

ANT

SW

D1,D22

RF

AMP

Q22

BPF

D28 D24,D26

BPF

T2

T1

From the TX circuits

To the 1st IF circuits

ANT

LO

SW

D5,D6

D31,D32D33,D34

Q23

BPF

XTAL

FI1

IF

AMP

Q24

BUFF

Q8

BUFF

Q10

ATT

IF SW

IF SW

RX VCO

To the TX circuits

From the RF circuits

2nd IF circuits

46.35MHz

BPF

XTAL

FI2

46.35MHz

1st IF mixer

PLL

IC

IC2

X3

Q26

BPF

X2

TCXO

W/N

SW

D38,D39

X1

Discriminator

BPF

CERAMIC

FI3

BPF

CERAMIC

FI4

W/N

SW

D36,D37

D/A

converter

IF IC

From the 1st IF

circuits

(Analog path)

To the RX AF circuit

(Digitalpath)

IC3

15.3MHz

45.9MHz

DISC

SQIN

IC57

450kHz

450kHz

NOIS

CERAMIC

BPF

FI5

DIF

BUFF

IC5

BUFF

Q28

A/D

IC901

FILTER

SW

Q901

DSP

LINEAR

DISC

CODEC

IC902

IC903

DAFO

AF

FILTER

R904,R908,C924

• 1ST IF CIRCUITS

• 2ND IF AND DEMODULATOR CIRCUITS

• RF CIRCUITS

Page 10

4 - 2

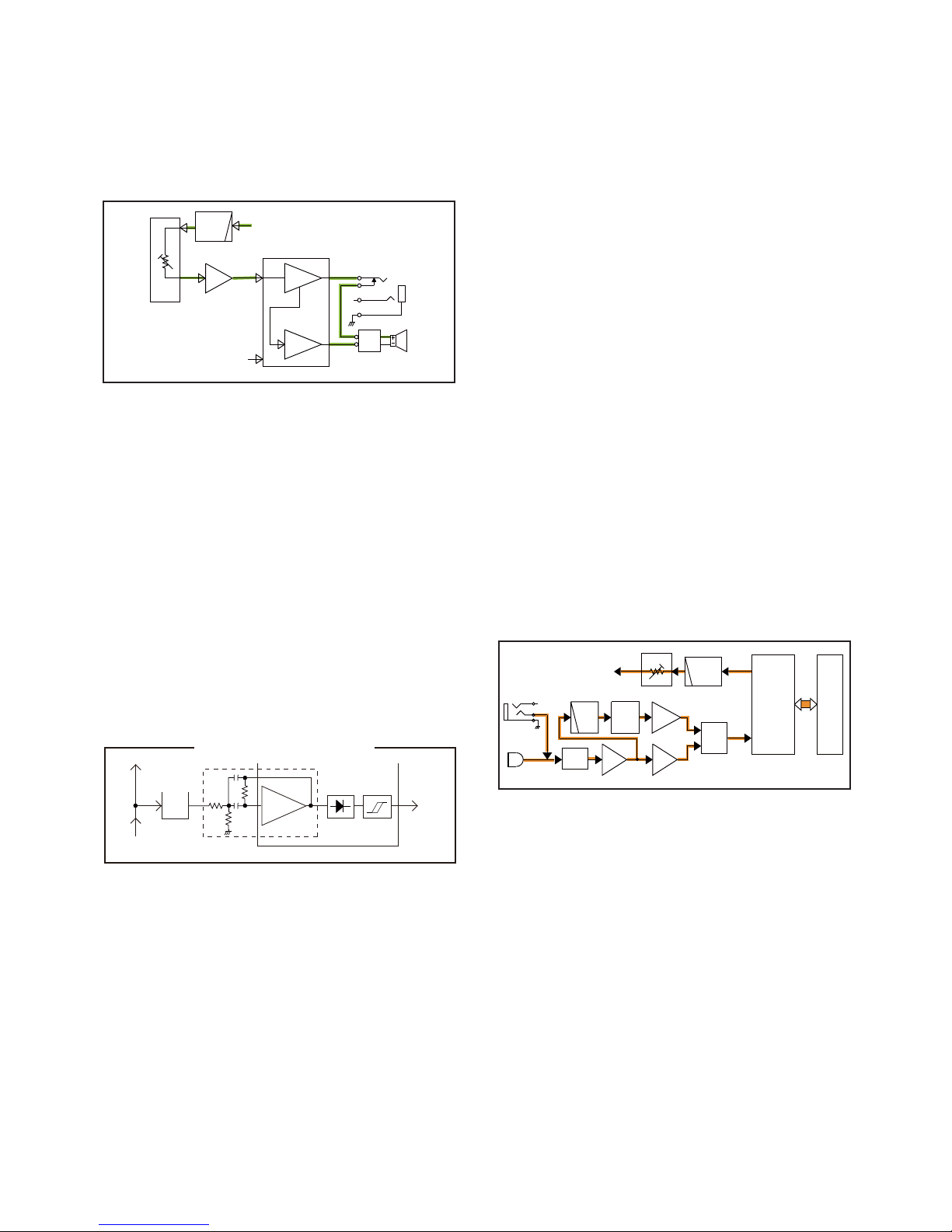

RX AF CIRCUITS

The demodulated AF signal from the linear codec (IC902) is

passed through the LPF (IC60C), and then adjusted in level

by the D/A converter (IC57). The level-adjusted AF signal is

then amplifi ed by AF AMPs (IC58 and IC55).

The amplifi ed AF signal is applied to the internal or external

speaker.

SQUELCH CIRCUITS (Analog mode only)

The squelch circuit cuts off the AF output signals when no

RF signals are received. Detecting noise components in the

demodulated AF signals, the squelch circuit stops audio signals being emitted.

A portion of demodulated AF signal from the IF IC (IC3) is

passed through the D/A converter (IC57) for level (=threshold) adjustment. The level-adjusted AF signals are passed

through the noise filter (IC3, pins 7, 8 and R139–R142,

C241–C243) to fi lter the noise components (approx. 30 kHz

signals) only. The noise components are rectified, resulting

in DC voltage corresponding to the noise level.

If the noise level is higher than the preset one, the internal

comparator set the “NOISE” signal to the CPU to “High”,

then the CPU turns the “AFON” signal which controlls the AF

power AMP (IC55) to “Low,” to inactivate it.

• RX AF CIRCUITS

• SQUELCH CIRCUITS

AF

AM P

AF

AMP

IC55 TPA0211DGN

J52

SP1

AF

AM P

J53

Int.speaker

Ext.speaker

1

2

LPF

IC60C

From the linear codec

IC58

AFON

AFO

DAFO

D/A

converter

IC57

DAC

Noise

AMP

Noise filter

From IF IC

(IC3, Pin16)

To RX AF circuits

Noise

detector

Com-

parator

NOISE SQUELCH DIAGRAM

“NOIS”

IC57

IC3

14

8

7

13

15

4-2 TRANSMITTER CIRCUITS

TX AF CIRCUITS

The audio signal from the internal or external microphone

(MIC signal) is passed through the MIC gain SW (IC62), and

then applied to the MIC AMP (IC64).

• WHILE OPERATING IN THE ANALOG MODE

The amplifi ed MIC signal is passed through the HPF (IC63A),

which attenuates frequencies 300 Hz and below, and then

applied to the limiter AMP (IC60A), through the mute SW

(Q66).

The amplitude-limited MIC signal is applied to the lin-

ear codec (IC902), through the MIC line SW (IC66).

The MIC signal is converted into a digital audio signal by the

linear codec (IC902), processed by the DSP (IC903), and

then converted into an analog baseband signal (modulation

signal).

• WHILE OPERATING IN THE DIGITAL MODE

The amplifi ed MIC signal is applied to the ALC (IC63B) which

keeps the signal level fi xed.

The level-adjusted MIC signal is

applied to the linear codec

(IC902) through the MIC line SW (IC66).

The MIC signal is converted into a digital audio signal by the

linear codec (IC902), processed by the DSP (IC903), and

then converted into the digital baseband signal (modulation

signal).

The signal from the linear codec (IC902) is passed through

the LPF (IC60B), and then applied to the D/A converter

(IC57)

which adjusts its level (=deviation)

. The level-adjusted

modulation signal is applied to the modulation circuit.

• TX AF CIRCUITS

MC51

[Ext. MIC]

[Int. MIC]

J51

MIC

GAIN

SW

IC62

AMP

IC64

ALC

AMP

IC63B

HPF

IC63A

LIMIT

AMP

IC60A

MIC

LINE

IC66

SW

MUTE

SW

Q66

DMI

To the modulation circuit

DSP

LINEAR

CODEC

IC902

IC903

LPF

IC60B

MOD DMO

D/A

IC57

Page 11

4 - 3

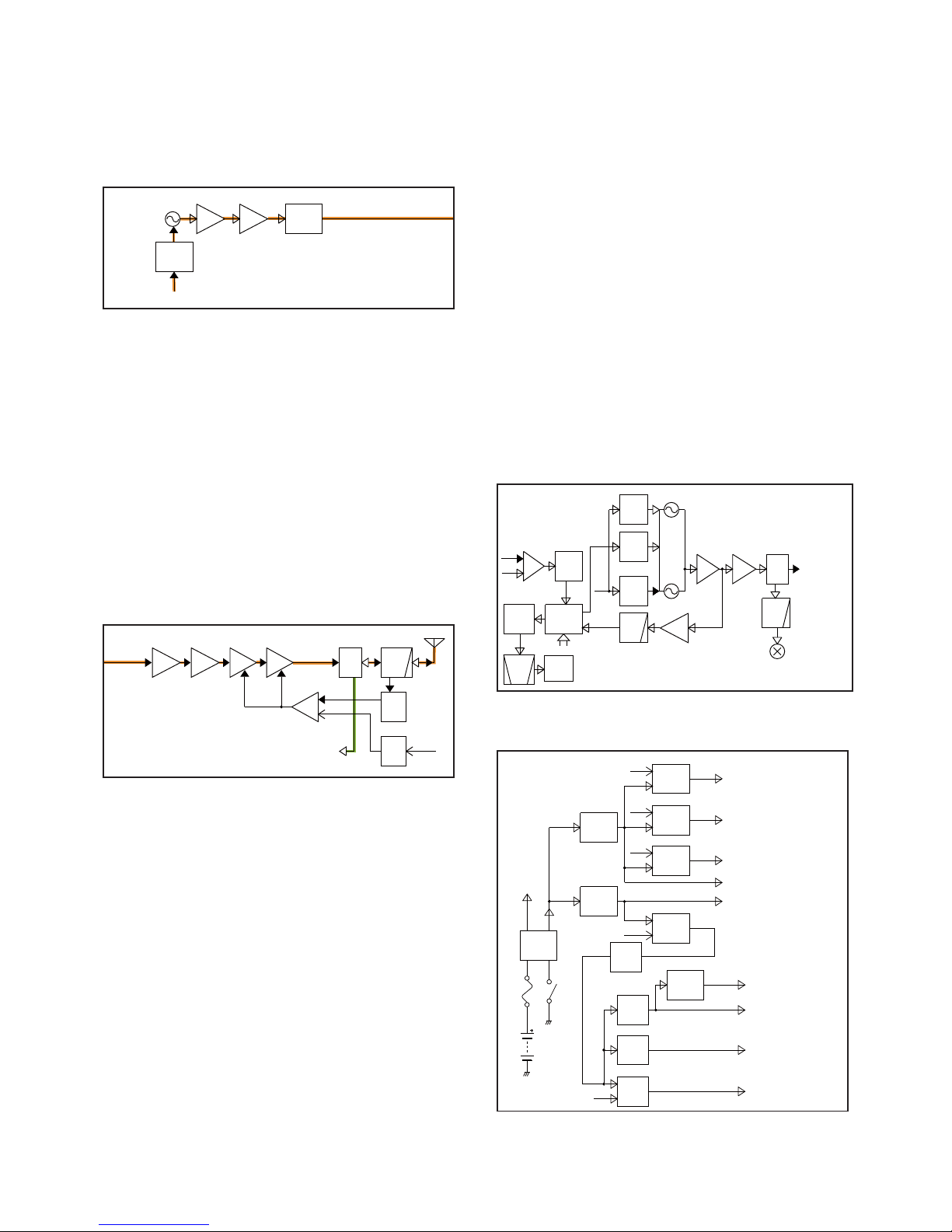

MODULATION CIRCUIT

The modulation signal from the TX AF circuits is applied to

D15 of the TX VCO (Q14, D14–D16) to modulate it (FM for

the analog mode, 4FSK for the digital mode). The modulated

signal from the TX VCO is buffer-amplified by two buffers

(Q8, Q10), and applied to the TX AMP circuits through the

LO SW (D5).

TX AMPLIFIERS

The buffer amplifi ed signal from the LO SW (D5) is sequentially amplified by the pre-AMP (Q4), pre-drive AMP (Q3),

drive AMP (Q2), and power AMP (Q1), to obtain TX power.

The amplifi ed TX signal is passed through the antenna SW

(D3, D22) and the LPF, which eliminates harmonics, and

then fed to the antenna.

APC CIRCUITS

D1 and D2 rectify a portion of the TX signal to direct voltage,

and the APC AMP (IC1) compares the voltage and the TX

power control reference voltage, “T1.” The resulting voltage

controls the gain of the power and drive AMPs to keep the

TX power constant.

• FREQUENCY SYNTHESIZER CIRCUITS

• TX AMPLIFIERS AND APC CIRCUITS

5-4 VOLTAGE DIAGRAMS

LO

SW

D5

Q14,

D14,D16,D17

MODULATION

FM:Analog

4-FSK: Digital

D15

BUFF

Q8

BUFF

Q10

TX VCO

From the TX AF circuits

To the TX AMP circuits

MOD

LPF

PWR

DET

D1,D2

MUTE

SW

Q6

ANT

SW

D1,D22

PWR

AMP

Q1

APC

AMP

IC1

DRIVE

AMP

Q2

AMP

PRE

Q4

DRIVE

PRE

Q3

T1

TMUT

ANT

From the

TX VCO

To the RX circuits

• MODULATION CIRCUIT

LPF

LPF

LO

SW

D5,D6

Q13,D12

Q14,D16

FILTER

LOOP

PLL

IC

SO,SCL,PLST

IC4

X3

Q26

Q23

To the TX AMPs

BPF

BUFF

Q8

BUFF

Q10

BUFF

Q9

X2

TCXO

LV

ADJ

D14

LV

ADJ

D11

BUFF

IC60

IF IC

RX VCO

TX VCO

IC3

REF

BAL

15.3MHz

45.9MHz

1st IF mixer

LV

LVA

S5

REG

Q71

,Q86

REG

R5

Q72

,Q87

REG

T5

Q73

,Q88

F51

R1(CHASSIS)

12

BT1

REG

+5V

IC54

DC-DC

1.6V

IC900

DC-DC

3.3V

IC65

REG

+3.3V

Q90

,Q91

Q92,

Q93,

D59

POWER

SW

LINE

FILTER

LINE

FILTER

LINE

FILTER

LINE

FILTER

VCC

+5V

T5V

Transmit circuits

Receive circuits

TX/RX common circuits

TX/RX common circuits

Logic circuits

R5V

S5V

TXC

RXC

S5C

VCC CPUV

CVDD_1.6 V

3.3V_VD D

+3.3V

+3.3V_A

+3.3V

PWON

POSWH

DVDD_3.3V

DSP

DSP flash

Liner codec

DSP reference voltage

CPUV

4-3

FREQUENCY SYNTHESIZER CIRCUITS

The RX VCO is composed of Q13, and D11, D12. The VCO

output signal is buffer-amplifi ed by two buffers (Q8 and Q10)

and applied to the 1st IF mixer, through the LO SW (D6) and

the LPF (L18, C208, C209).

The TX VCO is composed of Q14 and D14–D17. The VCO

output signal is buffer-amplifi ed by two buffers (Q8 and Q10)

and applied to the pre-AMP (Q4), through the LO SW (D5)

and the LPF.

A portion of signal generated by each VCO is fed back to

the PLL IC (IC4, pin 17) through the buffer (Q9) and the LPF

(L46, C167, C168).

The applied VCO output signal is divided and phase-compared with a 15.3 MHz reference frequency signal from the

TCXO (X2), which is also divided. The resulting signal is

output from the PLL IC (IC4), and DC-converted by the loop

fi lter, and then applied to the VCO as the lock voltage.

When the oscillation frequency drifts, its phase changes

from that of the reference frequency, causing a lock voltage

change to compensate for the drift in the VCO oscillating frequency.

Page 12

4 - 4

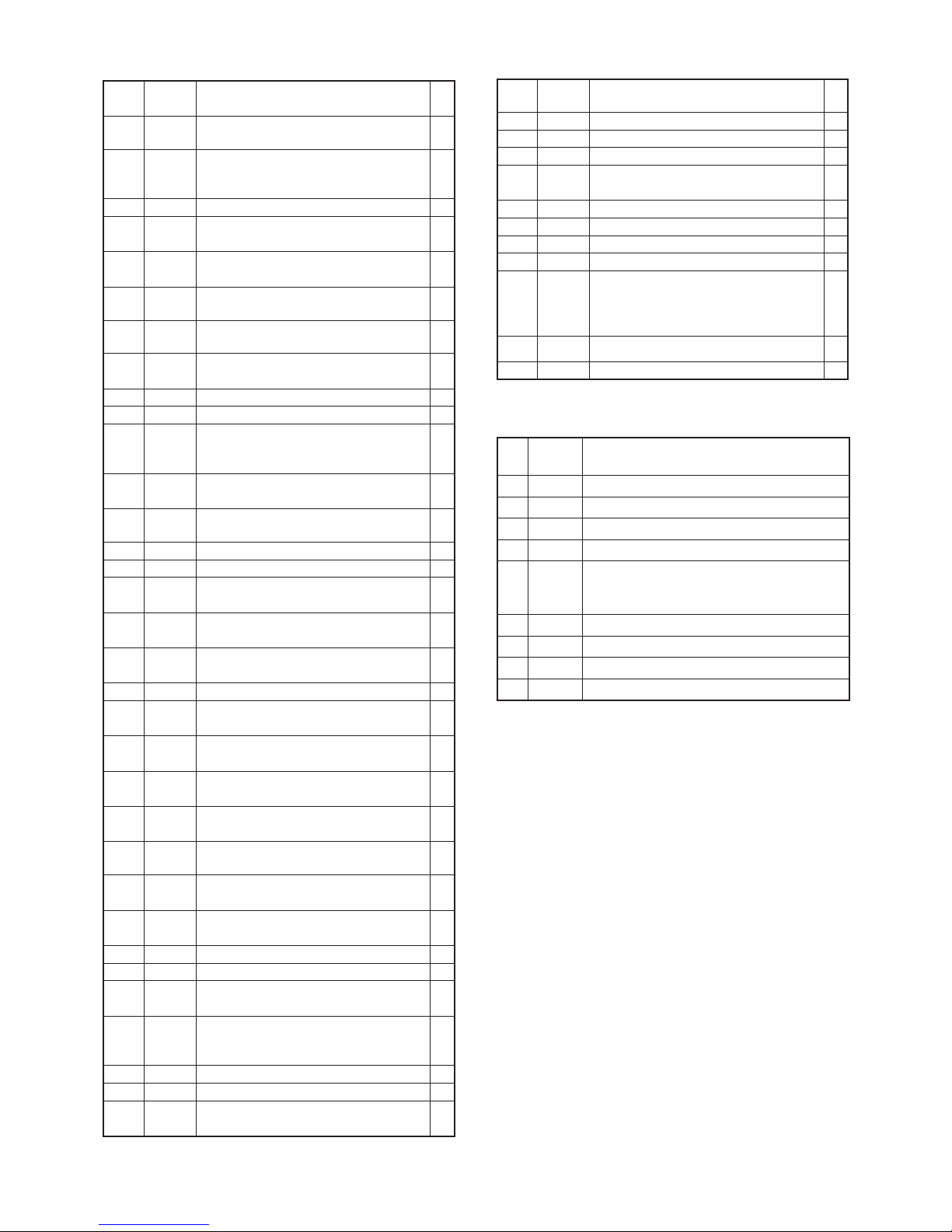

4-5 PORT ALLOCATIONS

• CPU (IC51)

• D/A CONVERTER (IC57)

PIN

No.

LINE

NAME

DESCRIPTION

3 BAL DTCS balance adjustment.

4 AFVO AF volume adjustment.

12 TENC Outputs CTCSS deviation adjustment.

15 SQLC Squelch threshold setting.

16 T1

During RX: Outputs BPF tuning voltage.

During TX: Outputs TX power reference

voltage.

19 T2 Outputs BPF tuning voltage.

20 REF Outputs reference frequency adjust voltage.

23 LVA Outputs additional lock voltage adjustment.

24 MOD Max. deviation/AF volume adjustment.

BALL

No.

LINE

NAME

DESCRIPTION

I/O

A5 RXC

Power supply switching control.

H= During receive or stand-by.

O

A6 RMUTE

RX AF mute switch control.

L= During the squelch circuit is

activated.

O

A7 DMOSI Serial data to the DSP (IC903). O

A15 PWON

Power supply switching control.

H= The transceiver's power is ON.

O

B12 NOIS

Noise level detect.

H= Squelch close.

I

B15 AFON

AF power AMP control.

H= AF power AMP (IC55) is activated.

O

C1, C2CBI2,

CBI0

[ROTARY SELECTOR] input. I

C5 TXC

Power supply switching control.

H= While transmitting.

O

C8 ESDA EEPROM (IC52) serial data. I/O

C13 POSW [POWER] input. I

C14 ADS

1st IF filters (FI1 and FI2) switching

control.

L= During digital mode.

O

C15 NWC

Receive bandwidth switching.

L= During narrow mode.

O

D2, D3CBI3,

CBI1

[ROTARY SELECTOR] input. I

D6 DSCK DSP (IC903) clock. O

D8 ESCL EEPROM (IC52) clock. O

D13 DPDN

DSP (IC903) power control.

H= DSP is inactivated.

O

D14 DRES

DSP (IC903) reset.

L= Reset.

O

D15 CSFT

Clock frequency shift.

H= Clock frequency is shifted.

O

E13 RES CPU reset. I

H1 SIDE1

[UPPER] key input.

L= Pushed.

I

H2 SIDE2

[LOWER] key input.

L= Pushed.

I

J1 IPTT

Internal [PTT] input.

L= Pushed.

I

J2 XPTT

External PTT input.

H= An external PTT is pushed.

I

L1, L2

MCG0,

MCG1

MIC gain control. O

L12 TLED

Busy LED (Red) control.

L= LED lights

. (While transmitting)

O

L13 RLED

Busy LED (Green) control.

L= LED lights. (While receiving a signal)

O

L14 SSO Common serial data. O

L15 SCK Common clock. O

M1 TMUT

Transmission mute.

L= TX inhibit.

O

M2 ATX

Automatic TX control for VOX mode.

H= While MIC audio from the

connected headset is detected.

O

M8 BEEP Beep audio. (Square waves) O

M11 MDET External connection detect. I

M14 DAST

D/A converter (IC57) strobe.

H= Load enable.

O

BALL

No.

LINE

NAME

DESCRIPTION

I/O

N11 VOXV Microphone input sensing voltage. I

N12 BATV Battery voltage sensing. I

N14 DMISO DSP (IC903) serial data. O

P4 PLSW

PLL lock up time control.

L= Fast lock up.

O

P10 TEMP Temperature sensing voltage. I

P11 RSSI RSSI sensing voltage. I

P12 AFVI [VOLUME CONTROL] input. I

P15 DSS DSP (IC903) chip select. O

R3 S5C

Power supply line "S5C" switching

control.

H= Supplying current to the TX/RX

common circuits.

O

R4 PLST PLL strobe. O

R10 LVIN Lock voltage input. I

Page 13

5 - 1

SECTION 5. ADJUSTMENT PROCEDURE

¤ JIG CABLE

EQUIPMENT GRADE AND RANGE EQUIPMENT GRADE AND RANGE

Cloning software CS-F3100D/F5120D

(Revision 1.0 or later)

JIG cable

Modifi ed OPC-478UC (See the illust below)

RF power meter

(50 Ω terminated)

Measuring range : 0.1–10 W

Frequency range : 100–600 MHz

SWR : Less than 1.2 : 1

Frequency counter

Frequency range : 0.1–600 MHz

Frequency accuracy : ±1 ppm or better

Input level : Less than 1 mW

Modulation

Analyzer

Frequency range : 30–600 MHz

Measuring range : 0 to ±10 kHz

Standard signal

generator (SSG)

Frequency range : 0.1–600 MHz

Output level : –20 dBµ to 90 dBµ

(–127 to –17 dBm)

AC millivoltmeter Measuring range : 10 mV to 10 V

Oscilloscope

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Attenuator

Power attenuation : 30 dB

Capacity : More than 10 W

Audio generator

(AG)

Frequency range : 300–3000 Hz

Output level : 1–500 mV

External speaker

Input impedance : 8

Ω

Capacity : More than 1 W

¤ REQUIRED EQUIPMENTS

5-1 PREPARATION

3-conductor 2.5 (d) mm plug

(MIC)

(GND

)

33 k

3-conductor 3.5(d) mm plug

(CLONE)

OPC-478UC

(GND)

(SP)

[JIG cable1]

[JIG cable2]

+−

AC

MILLIVOLTMETER

(10 mV to 10 V)

AUDIO GENERATOR

(300–3000 Hz/1–500 mV)

+−

PTT

+

4.7 µF

EXT. SPEAKER

(1 W/8 Ω)

+

−

SETTING;

Frequency : 1 kHz

Level : 150 mV

Waveform : Sine wave

¤ CONNECTION

Modulation

analyzer

Speaker (8 Ω)

to the antenna connector

Attenuator

30 dB

RF power meter

0.1– 10 W/50 Ω

Frequency

counter

Standard signal generator

–20 to 90 dBµ

(–127 to –17 dBm)

CAUTION!

NEVER transmit while

an SSG is connected to

the antenna connector.

To [SP]

To [MIC]

(JIG cable 1)

(JIG cable 2)

To [SP] connector

PC

to USB port

OPC-478UC

(USB type)

Page 14

5 - 2

CONVENIENT: The cloning data fi le for the adjustment, as described in this service manual, is attached.

Right click the clip icon, and select "Save Embeded File to Disk."

• For 400 MHz band versions: • For 350 MHz band versions:

¤ ADJUSTMENT CHANNELS

• For 350 MHz band versions

• For 400 MHz band versions

Before starting the adjustments, use the cloning software to create the same cloning file as shown below, then

upload it into the transceiver.

Page 15

S-METER

DIGITAL DEVIATION

2/5 TONE DEVIATION

5 - 3

¤ ADJUSTMENT UTILITY

ADJUSTMENT CONDITION

REFERENCE FREQUENCY

TX OUTPUT POWER

FM DEVIATION

SQUELCH

SENSITIVITY

PLL LOCK VOLTAGE

CTCSS DEVIATION

DTCS DEVIATION

MODULATION BALANCE

For [EUR] versions:

When adjusting “Deviation” in the middle band, change the bandwidth

to “Middle” as shown.

Select “Middle”

Page 16

5 - 4

ADJUSTMENT

TRANSCEIVER’S

CONDITION

OPERATION

ADJUSTMENT

ITEM

VALUE

PLL LOCK VOLTAGE

-RX(Band low)

1 • Channel : 1-1

• Receiving

1) Connect an RF power meter to the

antenna connector.

2) Set the preset adjustment value on

the adjustment utility window.

[RX LVA(Adjust)]

1.00 V

(Band high) 2 • Channel : 1-2

• Receiving

[RX LVA(Check)] 3.70 V

-TX(Band low)

3 • Channel : 1-1

• Transmitting

[TX LVA(Adjust)]

1.00 V

(Band high)* 4 • Channel : 1-2

• Transmitting

[TX LVA(Check)]

3.20 V

-VERIFY-** 5 • Channel : 1-2

• Transmitting

• Click the [Update (F5)] button to check

on the "I/O Check window" as below.

[LVIN]

(On the "I/O

Check window")

2.00–4.00 V

(Verify)

REFERENCE

FREQUENCY

1 • Channel : 1-3

• Transmitting

• Loosely couple a frequency counter to

the antenna connector.

[REF]

470.000000 MHz

[400 MHz band]

400.000000 MHz

[350 MHz band]

(±50 Hz)

*: For only [350 MHz band]. **: For only [400 MHz band].

5-2 FREQUENCY ADJUSTMENTS

1) Select an adjustment item using [↑]/[↓] on the PC's keyboard.

2) Set or modify the adjustment value as specifi ed using [←]/[→] on the PC's keyboard, then push [ENTER].

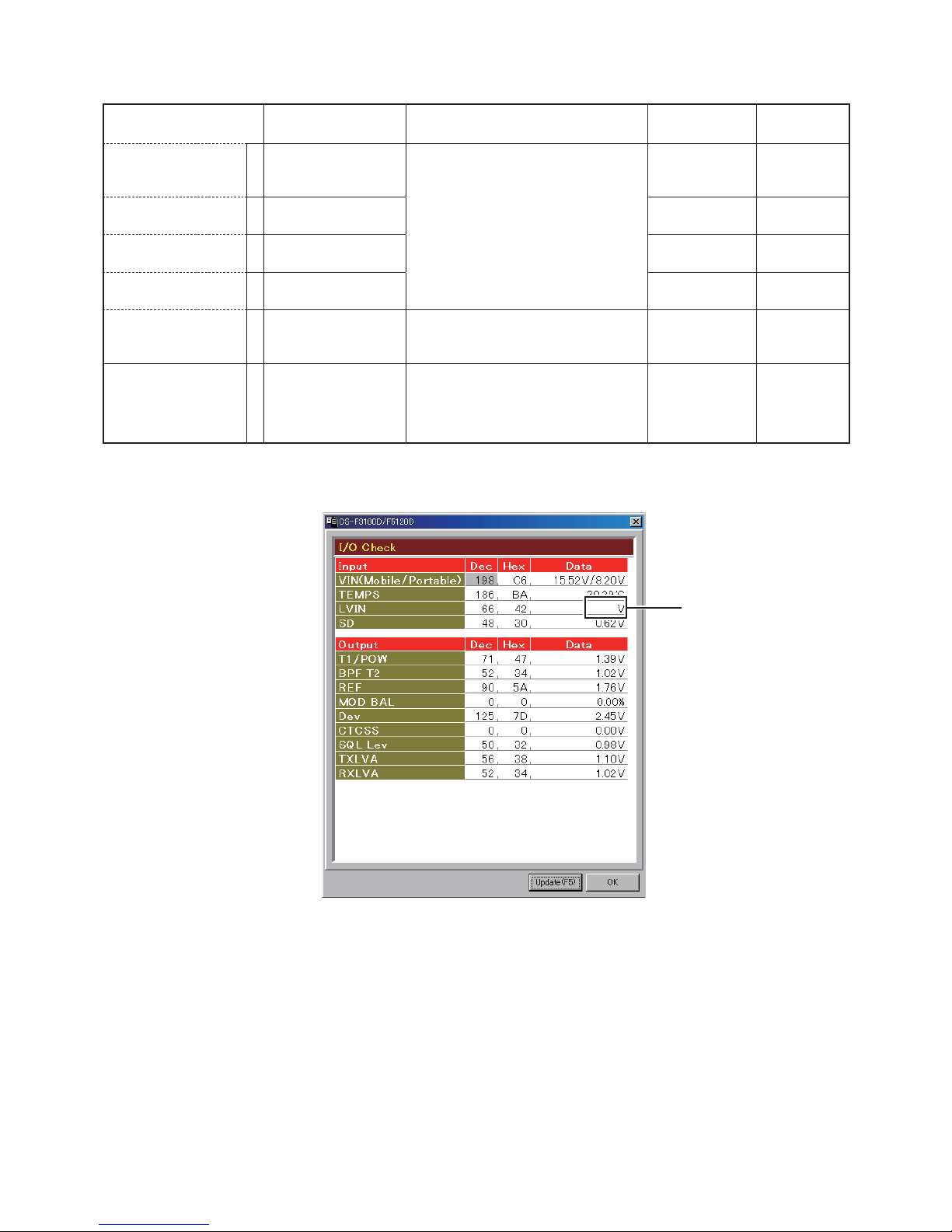

• I/O Check window

(The values shown above are an example only. Each transceiver has own values.)

Lock voltage

appears here

* * *

Page 17

5 - 5

ADJUSTMENT

TRANSCEIVER’S

CONDITION

OPERATION

ADJUSTMENT

ITEM

VALUE

TX OUTPUT

POWER

(Hi power)

1 • Channel : 1-4

• Transmitting

• Connect an RF power meter to the antenna connector. [Power (Hi)]

4.0 W

(L2 power) 2 • Channel : 1-5

• Transmitting

[Power (L2)] 2.0 W

(L1 power) 3 • Channel : 1-6

• Transmitting

[Power (L1)]

1.0 W

MODULATION

BALANCE

1

–

• Set “MOD -Narrow-” to “90,” and set the

TX mode to “2” on the “ADJUSTMENT

UTILITY” screen.

[MOD -Narrow-] 90

[TX mode] 2

2• Set the coursor on [BAL Start] to enter the “MODULATION BAL-

ANCE” adjustment mode.

[BAL Start] –

(Band low) 3 • Channel : 1-7

• Transmitting

• Connect a modulation analyzer with an

oscilloscope to the antenna connector

through an attenuator, and set it as;

HPF : OFF

LPF : 15 kHz

De-emphasis : OFF

Detector : (P–P)/2

[BAL 1]

(Band center) 4 • Channel : 1-8

• Transmitting [BAL 2]

(Band high) 5 • Channel : 1-9

• Transmitting [BAL 3]

6• Set the coursor on [BAL Start] to quit the “MODULATION BAL-

ANCE” adjustment mode.

[BAL Start] –

FM DEVIATION

-Narrow(Band low)

1• Set the coursor on [MOD N Start] to enter the “FM DEVIATION

-Narrow-” adjustment mode.

[MOD N Start]

–

2 • Channel : 1-10

• Transmitting

• Connect a modulation analyzer to

the antenna connector through an

attenuator, and set it as “MODULATION

BALANCE.”

• Connect an audio generator to the [MIC]

jack through the JIG cable, and set it as;

Frequency : 1 kHz

Waveform : Sinewave

Level : 150 mVrms

[MOD N L]

±2.05 to ±2.15

kHz

(Band center) 3 • Channel : 1-11

• Transmitting

[MOD N C]

(Band high) 4 • Channel : 1-12

• Transmitting

[MOD N H]

5• Set the coursor on [MOD N Start] to quit the “FM DEVIATION

-Narrow-” adjustment mode.

[MOD N Start]

–

FM DEVIATION

-Wide-*

(Band low)

1• Set the coursor on [MOD W Start] to enter the “FM DEVIATION

-Wide-” adjustment mode.

[MOD W Start]

–

2 • Channel : 1-13

• Transmitting

• Connect a modulation analyzer to

the antenna connector through an

attenuator, and set it as “MODULATION

BALANCE.”

• Connect an audio generator to the [MIC]

jack through the JIG cable, and set it as

“FM DEVIATION -Wide-.”

[MOD W L]

±4.05 to ±4.15

kHz±

(Band center) 3

• Channel : 1-14

• Transmitting

[MOD W C]

(Band high) 4 • Channel : 1-15

• Transmitting

[MOD W H]

5• Set the coursor on [MOD W Start] to quit the “FM DEVIATION

-Wide-” adjustment mode.

[MOD W Start]

–

*: For all models except [USA].

5-3 TRANSMIT ADJUSTMENTS

1) Select an adjustment item using [↑]/[↓] on the PC's keyboard.

2) Set or modify the adjustment value as specifi ed using [←]/[→] on the PC's keyboard, then push [ENTER].

No over or under shoot.

As flat as possible.

Page 18

5 - 6

5-3 TRANSMIT ADJUSTMENTS (Continued)

1) Select an adjustment item using [↑]/[↓] on the PC's keyboard.

2) Set or modify the adjustment value as specifi ed using [←]/[→] on the PC's keyboard, then push [ENTER].

ADJUSTMENT

TRANSCEIVER’S

CONDITION

OPERATION

ADJUSTMENT

ITEM

VALUE

FM DEVIATION

-Middle-***

(Band low)

1• Set the coursor on [MOD W Start] to enter the “FM DEVIATION

-Middle-” adjustment mode.

[MOD M Start]

–

2 • Channel : 1-16

• Transmitting

• Connect a modulation analyzer with an

oscilloscope to the antenna connector

through an attenuator, and set it as;

HPF : OFF

LPF : 15 kHz

De-emphasis : OFF

Detector : (P–P)/2

• Connect an audio generator to the [MIC]

jack through the JIG cable, and set it as;

Frequency : 1 kHz

Waveform : Sine wave

Level : 150 mVrms

[MOD M L]

±3.25 to ±3.35

kHz±

(Band center) 3 • Channel : 1-17

• Transmitting

[MOD M C]

(Band high) 4 • Channel : 1-18

• Transmitting

[MOD M H]

5• Set the coursor on [MOD W Start] to quit the “FM DEVIATION

-Middle-” adjustment mode.

[MOD M Start]

–

DIGITAL

DEVIATION

(Band low)

1• Set the coursor on [MOD D Start] to enter the “DIGITAL DEVIA-

TION” adjustment mode.

[MOD N Start]

–

2 • Channel : 1-19

• Transmitting

• Connect a modulation analyzer to

the antenna connector through an

attenuator, and set it as “FM DEVIATION -Middle-.”

• Connect an audio generator to the [MIC]

jack through the JIG cable, and set it as

“FM DEVIATION -Middle-.”

[MOD D L]

±1.36 to ±1.40

kHz

(Band center) 3 • Channel : 1-20

• Transmitting

[MOD D C]

(Band high) 4 • Channel : 1-21

• Transmitting

[MOD D H]

5• Set the coursor on [MOD D Start] to quit the “DIGITAL DEVIA-

TION” adjustment mode.

[MOD N Start]

–

CTCSS

DEVIATION

1 • Channel : 1-22*

1-23**

• No AF input from

the MIC.

• Transmitting

• Connect a modulation analyzer with an

oscilloscope to the antenna connector

through an attenuator, and set it as;

HPF : OFF

LPF : 15 kHz

De-emphasis : OFF

Detector : (P–P)/2

[CTCSS]

±0.65 to ±0.75 kHz*

±0.30 to ±0.40 kHz**

DTCS DEVIATION 1 • Channel : 1-24*

1-25**

• No AF input from

the MIC.

• Transmitting

• Connect a modulation analyzer to

the antenna connector through an

attenuator, and set it as “CTCSS DEVIATION.”

[DTCS]

±0.65 to ±0.75 kHz*

±0.30 to ±0.40 kHz**

2/5 TONE, DTMF

DEVIATION

1 • Channel : 1-26

• Transmitting

• Set the TX mode to “5” on the “ADJUSTMENT UTILITY” screen.

[TX Mode]

5

2• Connect a modulation analyzer to

the antenna connector through an

attenuator, and set it as "MODULATION

BALANCE."

[S.Tone]

±1.45 to ±1.55

kHz

*: For all models except [USA]. **: For [USA] ***: For only [EUR].

Page 19

5 - 7

ADJUSTMENT

TRANSCEIVER’S

CONDITION

OPERATION

ADJUSTMENT

ITEM

VALUE

RECEIVE

SENSITIVITY

NOTE:

“RECEIVE SENSITIVITY” must be adjusted before “S-METER.” Otherwise, “S-METER” will not beadjusted

properly. When “RECEIVE SENSITIVITY” is re-adjusted, “S-METER” must be also re-adjusted.

1 • Channel : 1-27*

1-28**

• Receiving

• Connect an SSG to the antenna connector and set it as;

Frequency : 400 MHz [400 MHz band]

350 MHz [350 MHz band]

Level

†

: +20 dBµ (–87 dBm)

Modulation : 1 kHz

Deviation : ±3.0 kHz*

±1.5 kHz**

[BPF C ALL]

Push [ENTER]

(Automatic

adjustment)

S-METER NOTE: When “RECEIVE SENSITIVITY” is re-adjusted, “S-METER” must be also re-adjusted.

1 • Channel : 1-29*

1-30**

• Receiving

• Connect an SSG to the antenna connec-

tor and set it as;

Frequency : 400 MHz [400 MHz band]

350 MHz [350 MHz band]

Level

†

: +23 dBµ (–84 dBm)

Modulation : 1 kHz

Deviation : ±3.0 kHz*

±1.5 kHz**

[RSSI S3 Level]

Push [ENTER]

(Automatic

adjustment)

2• Set the SSG as;

Level

†

: –7 dBµ (–114 dBm)

[RSSI S1 Level]

SQUELCH NOTE: When “RECEIVE SENSITIVITY” is re-adjusted, “SQUELCH” must be also re-adjusted.

1 • Channel : 1-31*

1-32**

• Receiving

1) Connect an SSG to the antenna con-

nector and set it as;

Frequency : 400 MHz [400 MHz band]

350 MHz [350 MHz band]

Level

†

: –14 dBµ (–121 dBm)

Modulation : 1 kHz

Deviation : ±3.0 kHz*

±1.5 kHz**

2) Once close the squelch by increasing the

[SQL] value, and then decrease the value

to open the squelch.

[SQL]

Squelch opens

(Push [ENTER]

to store the

value

)

†

; The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

*: For all models except [USA]. **: For [USA]

5-4 RECEIVE ADJUSTMENTS

1) Select an adjustment item using [↑]/[↓] on the PC's keyboard.

2) Set or modify the adjustment value as specifi ed using [←]/[→] on the PC's keyboard, then push [ENTER].

Page 20

6 - 1

SECTION 6. PARTS LIST

IC1 1110002751 S.IC TA75S01F(TE85RF) T 32.5/8.9

IC3 1110007320 S.IC NJM2591V-TE1-#ZZZB B 45.8/38.9

IC4 1130015270 S.IC AK1541P-L T 43.2/24.0

IC5 1110006230 S.IC NJM2711F-TE1-#ZZZB B 68.3/44.2

IC6 1130011741 S.IC TC7W66FK(TE85LF) B 65.3/26.7

IC21 1110002751 S.IC TA75S01F(TE85RF) T 69.8/34.6

IC51 1140015010 S.IC HD64F2506RBR26DV(EMPTY) B 83.0/14.3

IC52 1130015080 S.IC R1EX24512ASAS0A T 83.6/16.4

IC53 1110007780 S.IC NJU7704F3-28A-TE1-#ZZZH T 85.0/11.3

IC54 1180003600 S.REG NJM2871BF05-TE1-#ZZZB T 15.5/34.8

IC55 1110007610 S.IC TPA0211DGNR B 13.3/42.1

IC57 1110007290 S.IC AK2330P-L B 72.3/24.3

IC58 1110002751 S.IC TA75S01F(TE85RF) T 23.9/28.3

IC60 1110005320 S.IC NJM13403V-TE1-#ZZZB B 65.1/8.3

IC62 1130011741 S.IC TC7W66FK(TE85LF) T 60.9/11.3

IC63 1110007630 S.IC NJM2783V-TE1-#ZZZH T 71.9/9.8

IC64 1110005330 S.IC NJM12904V-TE1-#ZZZB T 67.1/9.8

IC65 1180003670 S.REG BD9141MUV-E2 T 96.5/9.1

IC66 1130009981 S.IC TC7W53FK(TE85LF) T 75.9/8.5

IC900 1180003680 S.REG TPS62204DBVR T 76.4/39.0

IC901 1190002900 S.IC ADS7886SDCKR T 77.5/32.5

IC902 1110007770 S.IC PCM3008T/2K B 78.6/34.7

IC903 1140013290 S.IC TMS320VC5509AZHH T 86.8/36.8

IC904 1130015620 S.IC EN25Q40-100GIP <MSK> T 78.0/28.4

IC905 1110006230 S.IC NJM2711F-TE1-#ZZZB B 80.2/46.0

Q1 1560001700 S.FET RD07MUS2B-T112 B 28.6/13.5

Q2 1560001241 S.FET RD01MUS1-T113 B 36.1/14.4

Q3 1530004180 S.TRA 2SC3356-T1B YS (R25) B 41.3/12.9

Q4 1530003311 S.TRA 2SC5107-O(TE85RF) B 46.2/13.4

Q8 1530003311 S.TRA 2SC5107-O(TE85RF) T 55.6/18.6

Q9 1530003311 S.TRA 2SC5107-O(TE85RF) B 55.4/18.9

Q10 1530003311 S.TRA 2SC5107-O(TE85RF) T 61.0/19.4

Q11 1590004070 S.TRA LDTC144EET1G <SLVJ> B 53.4/23.2

Q12 1590004070 S.TRA LDTC144EET1G <SLVJ> B 62.7/23.3

Q13 1530002921 S.TRA 2SC4226-T1 Y25 (R25) T 56.5/22.6

Q14 1530002921 S.TRA 2SC4226-T1 Y25 (R25) T 62.2/22.3

Q15 1530002851 S.TRA 2SC4116-BL(TE85RF) B 63.6/17.2

Q16 1590004090 S.TRA LDTC114YET1G <SLVJ> B 68.5/21.3

Q17 1560000541 S.FET 2SK880-Y(T5RICOMF) B 50.9/29.7

Q21 1560000841 S.FET 2SK1829(TE85RF) B 25.7/31.5

Q22 1580000731 S.FET 3SK293(TE85LF) B 21.2/29.0

Q23 1580000731 S.FET 3SK293(TE85LF) B 36.4/26.1

Q24 1530003311 S.TRA 2SC5107-O(TE85RF) B 38.3/42.6

Q26 1530002851 S.TRA 2SC4116-BL(TE85RF) T 43.3/32.7

Q27 1590004090 S.TRA LDTC114YET1G <SLVJ> B 56.3/35.9

Q28 1530002851 S.TRA 2SC4116-BL(TE85RF) B 63.6/44.7

Q29 1590004090 S.TRA LDTC114YET1G <SLVJ> T 38.5/42.6

Q51 1510001090 S.TRA KTA2015Y-RTK/P B 25.7/43.5

Q52 1590004090 S.TRA LDTC114YET1G <SLVJ> B 24.6/39.8

Q58 1590004220 S.TRA DRA9123Y0L B 54.9/7.1

Q59 1590004090 S.TRA LDTC114YET1G <SLVJ> B 49.1/7.3

Q63 1520000460 S.TRA 2SB1132 T100 R B 15.3/35.5

Q64 1590004590 S.TRA DMC506010R B 19.3/36.0

Q66 1560001360 S.FET 2SK3019 TL B 72.7/7.0

Q67 1590004090 S.TRA LDTC114YET1G <SLVJ> T 75.4/13.1

Q71 1510001090 S.TRA KTA2015Y-RTK/P B 66.9/16.3

Q72 1510000771 S.TRA 2SA1586-GR(TE85LF) B 65.8/37.4

Q73 1510001090 S.TRA KTA2015Y-RTK/P B 70.2/12.5

Q81 1590004100 S.TRA LDTC144TET1G <SLVJ> B 93.4/20.2

Q82 1590004050 S.TRA LDTA144EET1G <SLVJ> T 79.0/19.5

Q83 1590004050 S.TRA LDTA144EET1G <SLVJ> T 78.5/17.5

Q84 1590004070 S.TRA LDTC144EET1G <SLVJ> B 19.2/43.8

Q85 1590004090 S.TRA LDTC114YET1G <SLVJ> T 21.5/33.0

Q86 1590004090 S.TRA LDTC114YET1G <SLVJ> B 70.6/16.3

Q87 1590004090 S.TRA LDTC114YET1G <SLVJ> B 68.5/35.7

Q88 1590004090 S.TRA LDTC114YET1G <SLVJ> B 72.5/12.4

Q90 1510000920 S.TRA 2SA1577 T106 Q T 92.4/12.6

Q91 1590004090 S.TRA LDTC114YET1G <SLVJ> T 91.0/14.9

Q92 1590003321 S.FET TPC6103(TE85LF) B 6.9/35.0

Q93 1590004090 S.TRA LDTC114YET1G <SLVJ> B 4.0/34.6

Q95 1590004050 S.TRA LDTA144EET1G <SLVJ> B 68.5/33.2

Q900 1590004050 S.TRA LDTA144EET1G <SLVJ> B 73.5/48.8

Q901 1590004090 S.TRA LDTC114YET1G <SLVJ> B 75.1/27.8

D1 1750002230 S.DIO LRB751S-40T1G <SLVJ> B 13.8/6.3

D2 1750002230 S.DIO LRB751S-40T1G <SLVJ> B 15.2/10.6

D3 1750001890 S.DIO HVD142AKRF-E B 15.7/14.8

D5 1750001890 S.DIO HVD142AKRF-E B 49.6/15.2

D6 1750001890 S.DIO HVD142AKRF-E B 49.6/16.6

D10 1790001241 S.DIO MA2S7280GL B 61.6/17.5

D11 1750001840 S.VAR HVD350BKRF-E T 57.1/27.1

D12 1750001840 S.VAR HVD350BKRF-E T 54.0/28.8

D14 1750002270 S.VAR HVD396CKRF-E T 60.0/26.1

D15 1750001650 S.VAR 1SV309(TPH3F) T 64.6/28.2

D16 1750001840 S.VAR HVD350BKRF-E T 62.5/28.2

D21 1750001810 S.DIO L1SS400T1G <SLVJ> B 28.0/33.3

D22 1750001890 S.DIO HVD142AKRF-E B 15.7/18.3

D24 1750001780 S.VAR HVB350BYPTL-E B 18.1/23.8

D26 1750001780 S.VAR HVB350BYPTL-E B 18.1/26.7

D28 1750001780 S.VAR HVB350BYPTL-E B 29.2/26.7

D31 1750001910 S.DIO HVD144AKRF-E B 40.3/30.1

D32 1750001910 S.DIO HVD144AKRF-E T 36.6/28.4

D33 1750001910 S.DIO HVD144AKRF-E B 36.7/39.8

D34 1750001910 S.DIO HVD144AKRF-E T 36.5/41.0

D36 1750001790 S.DIO 1SS390 TE61 B 54.1/40.0

REF PARTS

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

[MAIN-A UNIT] (For [400 MHz band] versions)

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

S.=Surface mount

REF PARTS

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

[MAIN-A UNIT] (For [400 MHz band] versions)

D37 1750001790 S.DIO 1SS390 TE61 B 51.7/36.8

D38 1750001790 S.DIO 1SS390 TE61 B 56.6/40.0

D39 1750001790 S.DIO 1SS390 TE61 B 58.1/38.6

D51 1750001820 S.DIO LRB706F-40T1G <SLVJ> B 91.9/17.8

D52 1790001241 S.DIO MA2S7280GL B 26.2/41.0

D53 1750001810 S.DIO L1SS400T1G <SLVJ> T 61.8/6.8

D54 1750001810 S.DIO L1SS400T1G <SLVJ> T 60.5/6.8

D55 1750001810 S.DIO L1SS400T1G <SLVJ> B 22.8/34.9

D59 1750001850 S.DIO LDAN222T1G <SLVJ> B 4.2/37.5

D60 1750001790 S.DIO 1SS390 TE61 B 85.0/23.6

D901 1790001241 S.DIO MA2S7280GL T 87.1/27.9

D902 1790001241 S.DIO MA2S7280GL B 86.2/44.9

D903 1790001241 S.DIO MA2S7280GL B 92.1/30.8

D904 1790001241 S.DIO MA2S7280GL T 88.4/27.9

D905 1790001241 S.DIO MA2S7280GL B 96.3/30.8

FI1 2030000870 S.MON MFT46.3P3 46.350 MHz (FL-442) B 35.4/34.1

FI2 2010002760 S.XTA MFT46.3J 46.350 MHz (FL-448) T 36.6/34.5

FI3 2020002410 CER LTM450FW <JJE>

FI4 2020002570 CER LTM450HW <JJE>

FI5 2020002610 S.CER LTUCG450G <JJE> T 65.2/43.3

X1 6070000310 S.DIS JTBM450CX70 <JJE> T 47.6/40.9

X2 6050013000 S.XTA CR-892 TTS14VSB-A8 15.3 MHz T 41.9/15.0

X51 6050013160 S.XTA CR-912 TSS3225A 19.6608 MHz T 81.8/21.4

X900 6050013170 S.XTA CR-914 TTS18VSE-A11

12.288 MHz B 75.1/46.0

L1 6200012490 S.COI 0.30-0.9-6TR 13.6N <COMO> B 9.5/7.5

L2 6200012490 S.COI 0.30-0.9-6TR 13.6N <COMO> B 10.4/10.5

L3 6200013010 S.COI 0.30-0.9-5TL 10.3N <COMO> B 12.7/13.4

L4 6200002851 S.COI NLV25T-R82J B 18.2/16.6

L5 6200012610 S.COI 0.40-0.9-2TL 2.8N <COMO> B 18.2/13.4

L6 6200012610 S.COI 0.40-0.9-2TL 2.8N <COMO> B 20.7/13.4

L7 6200012980 S.COI 0.40-1.4-5TR 18.3N <COMO> B 23.6/13.4

L8 6200013860 S.COI MLK1005S12NJT B 41.0/10.7

L9 6200013840 S.COI MLK1005S18NJT B 45.5/10.7

L11 6200010850 S.COI LQW18AN22NG00D

(LQW1608A22NG00) B 13.9/16.6

L13 6200007700 S.COI LQW2BHN22NJ03L B 15.1/22.4

L14 6200007700 S.COI LQW2BHN22NJ03L B 15.1/28.1

L15 6200007680 S.COI LQW2BHN12NJ03L B 25.8/27.6

L16 6200007680 S.COI LQW2BHN12NJ03L B 32.7/27.6

L18 6200013800 S.COI MLK1005S39NJT B 36.4/22.3

L19 6200013780 S.COI MLK1005S56NJT B 34.4/23.9

L20 6200004770 S.COI ELJNC R56J-F B 39.1/26.4

L23 6200012170 S.COI MLG1608S R18J-T T 41.9/35.7

L24 6200012170 S.COI MLG1608S R18J-T T 45.2/34.2

L31 6200013810 S.COI MLK1005S33NJT T 53.8/17.7

L32 6200013810 S.COI MLK1005S33NJT B 53.4/19.3

L33 6200013830 S.COI MLK1005S22NJT T 59.2/18.3

L35 6190002030 S.COI MLG1608S 1R0J-T B 59.8/25.7

L36 6200013581 S.COI 0.30-0.9-4TR 8.6J <COMO> T 54.2/26.1

L37 6200011860 S.COI LQW18ANR47G00D T 56.5/28.8

L40 6200014240 S.COI 0.30-0.9-3TR 5.8J <COMO> T 64.0/24.9

L41 6200011860 S.COI LQW18ANR47G00D T 58.9/27.4

L42 6200011860 S.COI LQW18ANR47G00D T 60.5/28.8

L46 6200013840 S.COI MLK1005S18NJT B 48.9/20.0

L48 6200013990 S.COI MLK1005S1N0ST B 32.7/13.1

L51 6200014170 S.COI VLCF4028T-4R7N1R5-2 T 96.5/14.3

L900 6200014160 S.COI VLCF4028T-100M1R0-2 T 77.6/42.9

L901 6200007830 S.COI ELJFC 4R7K-F B 84.5/48.0

R1 7030005070 S.RES ERJ2GEJ 683 X (68K) B 7.2/5.5

R2 7030009140 S.RES ERJ2GEJ 272 X (2.7K) B 12.2/8.9

R3 7030005120 S.RES ERJ2GEJ 102 X (1K) B 13.5/8.4

R4 7030005120 S.RES ERJ2GEJ 102 X (1K) B 13.5/10.0

R5 7030009140 S.RES ERJ2GEJ 272 X (2.7K) B 12.2/10.9

R6 7030004990 S.RES ERJ2GEJ 221 X (220) B 20.3/17.9

R8 7030005220 S.RES ERJ2GEJ 223 X (22K) T 31.1/5.7

R9 7030005050 S.RES ERJ2GEJ 103 X (10K) T 31.1/6.6

R10 7030005090 S.RES ERJ2GEJ 104 X (100K) T 32.2/11.1

R11 7030005080 S.RES ERJ2GEJ 823 X (82K) T 30.1/11.1

R12 7030005170 S.RES ERJ2GEJ 474 X (470K) T 32.8/5.7

R13 7030005530 S.RES ERJ2GEJ 100 X (10) T 34.8/9.9

R14 7030008280 S.RES ERJ2GEJ 271 X (270) T 35.4/7.5

R15 7030005120 S.RES ERJ2GEJ 102 X (1K) T 36.3/7.5

R16 7030005050 S.RES ERJ2GEJ 103 X (10K) T 29.4/7.1

R21 7030005530 S.RES ERJ2GEJ 100 X (10) B 33.2/10.8

R22 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 34.1/9.2

R23 7030005060 S.RES ERJ2GEJ 333 X (33K) B 35.0/9.2

R24 7030004970 S.RES ERJ2GEJ 470 X (47) B 38.2/10.8

R27 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 38.2/9.2

R29 7030004970 S.RES ERJ2GEJ 470 X (47) B 41.0/9.8

R30 7030005220 S.RES ERJ2GEJ 223 X (22K) B 41.8/15.1

R31 7030004980 S.RES ERJ2GEJ 101 X (100) B 45.5/9.8

R32 7030005220 S.RES ERJ2GEJ 223 X (22K) B 45.8/15.2

R33 7030005050 S.RES ERJ2GEJ 103 X (10K) B 49.6/13.1

R34 7030004980 S.RES ERJ2GEJ 101 X (100) B 49.6/14.0

R35 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 51.7/16.6

R41 7030005530 S.RES ERJ2GEJ 100 X (10) T 57.4/17.7

R42 7030005070 S.RES ERJ2GEJ 683 X (68K) T 57.4/19.3

R43 7030004980 S.RES ERJ2GEJ 101 X (100) B 55.4/16.2

R44 7030005090 S.RES ERJ2GEJ 104 X (100K) B 55.4/20.7

Page 21

6 - 2

REF PARTS

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

[MAIN-A UNIT] (For [400 MHz band] versions)

R45 7030004980 S.RES ERJ2GEJ 101 X (100) T 63.2/17.9

R46 7030005090 S.RES ERJ2GEJ 104 X (100K) T 62.8/19.3

R51 7030005000 S.RES ERJ2GEJ 471 X (470) B 54.5/24.5

R52 7030005000 S.RES ERJ2GEJ 471 X (470) B 61.1/22.8

R53 7030006020 S.RES RR0510P-682-D (6.8K) T 58.3/23.8

R54 7030006020 S.RES RR0510P-682-D (6.8K) T 58.1/25.4

R55 7030006020 S.RES RR0510P-682-D (6.8K) T 59.5/23.8

R56 7030006020 S.RES RR0510P-682-D (6.8K) T 60.3/25.1

R57 7030010040 S.RES ERJ2GEJ-JPW T 61.9/24.2

R58 7030005090 S.RES ERJ2GEJ 104 X (100K) B 62.4/28.0

R59 7030005700 S.RES ERJ2GEJ 274 X (270K) B 62.4/26.4

R62 7030005310 S.RES ERJ2GEJ 124 X (120K) B 68.0/27.2

R64 7030005530 S.RES ERJ2GEJ 100 X (10) T 64.2/26.4

R65 7030005600 S.RES ERJ2GEJ 273 X (27K) B 65.3/29.6

R66 7030005100 S.RES ERJ2GEJ 154 X (150K) B 65.3/28.7

R67 7030007290 S.RES ERJ2GEJ 222 X (2.2K) B 60.5/18.0

R68 7030005170 S.RES ERJ2GEJ 474 X (470K) B 63.7/30.5

R69 7030005100 S.RES ERJ2GEJ 154 X (150K) B 65.3/30.5

R70 7030005110 S.RES ERJ2GEJ 224 X (220K) B 63.7/31.4

R71 7030005050 S.RES ERJ2GEJ 103 X (10K) B 49.1/28.7

R72 7030004980 S.RES ERJ2GEJ 101 X (100) B 51.1/27.9

R73 7030005050 S.RES ERJ2GEJ 103 X (10K) B 65.3/32.3

R74 7030005290 S.RES ERJ2GEJ 682 X (6.8K) B 63.7/32.3

R76 7030005710 S.RES ERJ2GEJ 121 X (120) T 48.4/25.0

R77 7030007290 S.RES ERJ2GEJ 222 X (2.2K) T 46.7/25.9

R78 7030010040 S.RES ERJ2GEJ-JPW T 46.7/23.8

R79 7030007570 S.RES ERJ2GEJ 122 X (1.2K) T 46.7/25.0

R80 7410001130 S.ARR EXB28V102JX T 41.9/27.8

R81 7030005600 S.RES ERJ2GEJ 273 X (27K) T 46.4/22.0

R82 7030005050 S.RES ERJ2GEJ 103 X (10K) T 40.1/18.8

R83 7030005580 S.RES ERJ2GEJ 560 X (56) T 43.8/19.3

R84 7030005090 S.RES ERJ2GEJ 104 X (100K) T 40.1/23.7

R87 7030005090 S.RES ERJ2GEJ 104 X (100K) T 63.5/27.7

R88 7510001730 S.THE ERTJOEP 473J T 58.3/10.6

R89 7030010080 S.RES ERJ2RHD 1003X (100K) B 55.4/12.4

R101 7030005110 S.RES ERJ2GEJ 224 X (220K) B 28.0/32.1

R102 7030005170 S.RES ERJ2GEJ 474 X (470K) B 25.7/33.3

R103 7030008400 S.RES ERJ2GEJ 182 X (1.8K) B 28.0/30.9

R104 7030005050 S.RES ERJ2GEJ 103 X (10K) B 20.1/22.9

R105 7030005050 S.RES ERJ2GEJ 103 X (10K) B 20.1/27.2

R106 7030005240 S.RES ERJ2GEJ 473 X (47K) B 18.3/29.0

R107 7030005600 S.RES ERJ2GEJ 273 X (27K) B 20.2/31.0

R108 7030005080 S.RES ERJ2GEJ 823 X (82K) B 19.2/29.0

R109 7030005530 S.RES ERJ2GEJ 100 X (10) B 21.2/31.0

R110 7030004980 S.RES ERJ2GEJ 101 X (100) B 22.1/25.4

R112 7030004970 S.RES ERJ2GEJ 470 X (47) B 25.8/25.4

R113 7030007300 S.RES ERJ2GEJ 332 X (3.3K) B 24.2/28.5

R114 7030005090 S.RES ERJ2GEJ 104 X (100K) B 27.4/26.8

R115 7030005090 S.RES ERJ2GEJ 104 X (100K) B 31.0/26.8

R116 7030005310 S.RES ERJ2GEJ 124 X (120K) B 34.5/28.8

R117 7030005090 S.RES ERJ2GEJ 104 X (100K) B 33.4/23.9

R118 7030005310 S.RES ERJ2GEJ 124 X (120K) B 36.4/23.9

R119 7030005100 S.RES ERJ2GEJ 154 X (150K) B 36.1/27.9

R120 7030005710 S.RES ERJ2GEJ 121 X (120) B 39.1/23.9

R121 7030007300 S.RES ERJ2GEJ 332 X (3.3K) B 41.0/26.3

R122 7030004970 S.RES ERJ2GEJ 470 X (47) B 41.9/23.9

R123 7030010040 S.RES ERJ2GEJ-JPW T 71.2/30.6

R126 7030004980 S.RES ERJ2GEJ 101 X (100) B 39.5/40.8

R127 7030005310 S.RES ERJ2GEJ 124 X (120K) B 37.9/40.8

R128 7030005010 S.RES ERJ2GEJ 681 X (680) B 39.1/44.4

R132 7030005050 S.RES ERJ2GEJ 103 X (10K) B 47.4/17.6

R134 7030005090 S.RES ERJ2GEJ 104 X (100K) T 92.8/15.6

R135 7030005030 S.RES ERJ2GEJ 152 X (1.5K) T 43.1/37.7

R136 7030005030 S.RES ERJ2GEJ 152 X (1.5K) T 42.9/38.9

R138 7030005000 S.RES ERJ2GEJ 471 X (470) B 43.0/35.5

R139 7030005090 S.RES ERJ2GEJ 104 X (100K) B 48.3/35.5

R140 7030008410 S.RES ERJ2GEJ 392 X (3.9K) B 46.5/34.6

R141 7030005070 S.RES ERJ2GEJ 683 X (68K) B 46.5/33.7

R142 7030005310 S.RES ERJ2GEJ 124 X (120K) B 46.5/31.9

R146 7030004970 S.RES ERJ2GEJ 470 X (47) B 45.6/44.0

R147 7030005030 S.RES ERJ2GEJ 152 X (1.5K) B 47.1/42.2

R148 7030005120 S.RES ERJ2GEJ 102 X (1K) T 40.9/33.7

R149 7030007060 S.RES ERJ2GEJ 684X (680K) T 41.5/32.3

R151 7030005600 S.RES ERJ2GEJ 273 X (27K) B 51.7/39.0

R152 7030005210 S.RES ERJ2GEJ 822 X (8.2K) B 53.9/35.1

R153 7030007300 S.RES ERJ2GEJ 332 X (3.3K) B 55.5/38.7

R154 7030005210 S.RES ERJ2GEJ 822 X (8.2K) B 57.8/36.9

R155 7030005600 S.RES ERJ2GEJ 273 X (27K) B 58.8/39.8

R156 7030005120 S.RES ERJ2GEJ 102 X (1K) B 20.1/21.9

R157 7030005120 S.RES ERJ2GEJ 102 X (1K) B 31.0/25.1

R158 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 59.7/35.7

R159 7030008010 S.RES ERJ2GEJ 123 X (12K) B 29.7/23.8

R161 7030008300 S.RES ERJ2GEJ 184 X (180K) B 62.4/42.8

R162 7030004980 S.RES ERJ2GEJ 101 X (100) B 64.0/42.8

R163 7030004980 S.RES ERJ2GEJ 101 X (100) B 69.7/46.4

R164 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 67.3/41.0

R165 7030005030 S.RES ERJ2GEJ 152 X (1.5K) B 65.7/44.6

R166 7030009290 S.RES ERJ2GEJ 562 X (5.6K) B 65.7/43.7

R167 7030005290 S.RES ERJ2GEJ 682 X (6.8K) B 65.7/42.8

R169 7030005030 S.RES ERJ2GEJ 152 X (1.5K) B 64.0/41.0

R171 7030005220 S.RES ERJ2GEJ 223 X (22K) T 36.6/27.4

R172 7030005530 S.RES ERJ2GEJ 100 X (10) B 39.2/31.1

R173 7030007300 S.RES ERJ2GEJ 332 X (3.3K) B 41.5/32.3

R174 7030007300 S.RES ERJ2GEJ 332 X (3.3K) B 38.3/38.8

R175 7030008370 S.RES ERJ2GEJ 561 X (560) B 35.1/38.8

R176 7030005220 S.RES ERJ2GEJ 223 X (22K) T 35.5/40.6

R177 7030005120 S.RES ERJ2GEJ 102 X (1K) T 40.1/40.7

R178 7030009290 S.RES ERJ2GEJ 562 X (5.6K) T 39.2/40.7

R181 7030007270 S.RES ERJ2GEJ 151 X (150) T 35.5/29.6

R182 7030007290 S.RES ERJ2GEJ 222 X (2.2K) T 34.0/28.4

R183 7030007290 S.RES ERJ2GEJ 222 X (2.2K) T 37.8/41.1

R184 7030005530 S.RES ERJ2GEJ 100 X (10) T 37.8/39.3

R185 7030005090 S.RES ERJ2GEJ 104 X (100K) T 68.8/32.4

R186 7030005700 S.RES ERJ2GEJ 274 X (270K) T 70.4/31.5

R187 7030005090 S.RES ERJ2GEJ 104 X (100K) T 67.6/36.3

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

S.=Surface mount

REF PARTS

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

[MAIN-A UNIT] (For [400 MHz band] versions)

R188 7030005090 S.RES ERJ2GEJ 104 X (100K) T 67.6/34.7

R189 7030004980 S.RES ERJ2GEJ 101 X (100) T 68.9/36.8

R190 7030005120 S.RES ERJ2GEJ 102 X (1K) B 65.7/46.4

R243 7030005530 S.RES ERJ2GEJ 100 X (10) B 82.1/21.9

R244 7030005160 S.RES ERJ2GEJ 105 X (1M) B 83.0/21.9

R357 7030005220 S.RES ERJ2GEJ 223 X (22K) B 58.7/9.8

R358 7030009280 S.RES ERJ2GEJ 391 X B 56.0/8.7

R359 7030005210 S.RES ERJ2GEJ 822 X (8.2K) B 56.0/10.5

R360 7030007290 S.RES ERJ2GEJ 222 X (2.2K) B 56.0/9.6

R361 7030009290 S.RES ERJ2GEJ 562 X (5.6K) B 24.8/41.7

R362 7030005060 S.RES ERJ2GEJ 333 X (33K) B 51.6/7.5

R363 7030005000 S.RES ERJ2GEJ 471 X (470) B 58.3/8.6

R364 7030005240 S.RES ERJ2GEJ 473 X (47K) T 55.3/2.2

R365 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 26.2/38.9

R366 7030005100 S.RES ERJ2GEJ 154 X (150K) B 57.8/12.4

R367 7030005600 S.RES ERJ2GEJ 273 X (27K) T 53.6/2.2

R368 7030005700 S.RES ERJ2GEJ 274 X (270K) T 58.3/12.5

R369 7030005100 S.RES ERJ2GEJ 154 X (150K) T 63.5/10.6

R370 7030005170 S.RES ERJ2GEJ 474 X (470K) T 68.0/14.1

R371 7030005090 S.RES ERJ2GEJ 104 X (100K) B 60.3/11.6

R372 7030005090 S.RES ERJ2GEJ 104 X (100K) B 60.3/10.7

R373 7030005090 S.RES ERJ2GEJ 104 X (100K) T 75.4/11.6

R388 7030011120 S.RES ERJ2RHD 2702X (27.0K) T 73.9/20.9

R389 7030012510 S.RES ERJ2RHD 3901X (3.90K) T 71.0/20.2

R390 7030012520 S.RES ERJ2RHD 8201X (8.20K) T 71.4/21.5

R393 7030005170 S.RES ERJ2GEJ 474 X (470K) B 61.7/8.9

R394 7030005080 S.RES ERJ2GEJ 823 X (82K) B 59.9/7.3

R395 7030005600 S.RES ERJ2GEJ 273 X (27K) B 60.8/8.9

R396 7030008300 S.RES ERJ2GEJ 184 X (180K) B 60.8/7.3

R397 7030005100 S.RES ERJ2GEJ 154 X (150K) B 60.6/5.7

R398 7030005100 S.RES ERJ2GEJ 154 X (150K) B 61.7/7.3

R405 7030011290 S.RES ERJ12YJ1R8U (1.8) T 31.5/35.6

R406 7030005090 S.RES ERJ2GEJ 104 X (100K) B 12.6/45.7

R408 7030004980 S.RES ERJ2GEJ 101 X (100) B 35.6/46.3

R412 7030005050 S.RES ERJ2GEJ 103 X (10K) B 15.9/39.5

R413 7030005090 S.RES ERJ2GEJ 104 X (100K) T 18.6/34.7

R414 7030005230 S.RES ERJ2GEJ 334 X (330K) B 20.6/34.1

R416 7030005120 S.RES ERJ2GEJ 102 X (1K) B 21.5/36.0

R417 7030007570 S.RES ERJ2GEJ 122 X (1.2K) B 21.3/37.3

R418 7030009280 S.RES ERJ2GEJ 391 X B 19.8/37.9

R420 7030005090 S.RES ERJ2GEJ 104 X (100K) B 89.8/25.2

R421 7210003390 VAR F081165S-5 A10K L15FCX7

<SLVJ>

R422 7030005090 S.RES ERJ2GEJ 104 X (100K) T 64.6/6.9

R423 7030012530 S.RES ERJ2RHD 3302X (33.0K) T 6.2/36.5

R424 7030012540 S.RES ERJ2RHD 1502X (15.0K) T 4.8/38.4

R426 7030009140 S.RES ERJ2GEJ 272 X (2.7K) T 66.4/3.5

R427 7030007340 S.RES ERJ2GEJ 153 X (15K) T 64.8/3.5

R428 7030005120 S.RES ERJ2GEJ 102 X (1K) T 64.8/5.5

R429 7030008310 S.RES ERJ2GEJ 564 X (560K) T 66.4/5.5

R430 7030005160 S.RES ERJ2GEJ 105 X (1M) T 63.2/4.5

R431 7030005050 S.RES ERJ2GEJ 103 X (10K) B 68.9/15.7

R432 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 68.9/17.3

R433 7030005050 S.RES ERJ2GEJ 103 X (10K) B 67.8/37.8

R434 7030005050 S.RES ERJ2GEJ 103 X (10K) B 68.7/37.8

R435 7030005050 S.RES ERJ2GEJ 103 X (10K) B 70.6/14.4

R436 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 72.2/14.0

R437 7030005090 S.RES ERJ2GEJ 104 X (100K) T 15.0/37.0

R439 7030005100 S.RES ERJ2GEJ 154 X (150K) T 63.2/5.5

R440 7030009280 S.RES ERJ2GEJ 391 X B 17.4/43.5

R441 7030005050 S.RES ERJ2GEJ 103 X (10K) T 18.6/33.8

R442 7030007280 S.RES ERJ2GEJ 331 X (330) B 21.5/35.1

R444 7030005120 S.RES ERJ2GEJ 102 X (1K) T 90.3/12.5

R451 7030005060 S.RES ERJ2GEJ 333 X (33K) T 24.7/30.5

R452 7030005240 S.RES ERJ2GEJ 473 X (47K) T 21.3/28.9

R453 7030005240 S.RES ERJ2GEJ 473 X (47K) T 21.3/28.0

R454 7030005310 S.RES ERJ2GEJ 124 X (120K) T 23.0/30.5

R455 7030010040 S.RES ERJ2GEJ-JPW T 21.3/31.4

R468 7030005010 S.RES ERJ2GEJ 681 X (680) T 75.6/19.8

R469 7030008280 S.RES ERJ2GEJ 271 X (270) T 77.5/20.4

R491 7030005220 S.RES ERJ2GEJ 223 X (22K) B 71.1/8.3

R492 7030009290 S.RES ERJ2GEJ 562 X (5.6K) T 72.0/3.7

R493 7030005050 S.RES ERJ2GEJ 103 X (10K) T 70.3/4.6

R494 7030005240 S.RES ERJ2GEJ 473 X (47K) T 70.3/5.5

R495 7030005240 S.RES ERJ2GEJ 473 X (47K) B 70.7/7.1

R496 7030005080 S.RES ERJ2GEJ 823 X (82K) T 73.7/5.5

R497 7030005220 S.RES ERJ2GEJ 223 X (22K) B 66.4/13.0

R498 7030008290 S.RES ERJ2GEJ 183 X (18K) T 71.6/14.5

R499 7030005290 S.RES ERJ2GEJ 682 X (6.8K) B 72.3/8.9

R500 7030007350 S.RES ERJ2GEJ 393 X (39K) B 70.2/9.9

R502 7030005170 S.RES ERJ2GEJ 474 X (470K) B 69.3/9.9

R503 7030004980 S.RES ERJ2GEJ 101 X (100) B 61.9/11.6

R504 7030005090 S.RES ERJ2GEJ 104 X (100K) B 67.3/13.0

R517 7030008400 S.RES ERJ2GEJ 182 X (1.8K) B 63.3/13.5

R518 7030005090 S.RES ERJ2GEJ 104 X (100K) B 62.1/14.8

R527 7030005090 S.RES ERJ2GEJ 104 X (100K) B 64.6/13.0

R610 7030005080 S.RES ERJ2GEJ 823 X (82K) T 65.3/13.0

R611 7030010040 S.RES ERJ2GEJ-JPW T 64.6/10.6

R612 7030005090 S.RES ERJ2GEJ 104 X (100K) T 64.6/8.6

R614 7030005310 S.RES ERJ2GEJ 124 X (120K) B 62.1/13.1

R615 7030005220 S.RES ERJ2GEJ 223 X (22K) B 69.6/6.2

R616 7030005100 S.RES ERJ2GEJ 154 X (150K) B 68.4/8.3

R618 7030005050 S.RES ERJ2GEJ 103 X (10K) B 67.4/3.9

R619 7030005600 S.RES ERJ2GEJ 273 X (27K) B 68.4/5.1

R620 7030005240 S.RES ERJ2GEJ 473 X (47K) T 92.7/10.0

R621 7030007340 S.RES ERJ2GEJ 153 X (15K) T 93.6/10.0

R622 7030008290 S.RES ERJ2GEJ 183 X (18K) T 92.7/8.0

R623 7030009290 S.RES ERJ2GEJ 562 X (5.6K) T 6.4/46.2

R624 7030005050 S.RES ERJ2GEJ 103 X (10K) T 90.3/10.9

R625 7030005700 S.RES ERJ2GEJ 274 X (270K) B 7.8/37.2

R626 7030005090 S.RES ERJ2GEJ 104 X (100K) B 6.2/37.2

R627 7030005090 S.RES ERJ2GEJ 104 X (100K) T 77.5/21.3

R628 7030005090 S.RES ERJ2GEJ 104 X (100K) T 88.1/15.7

R630 7030010040 S.RES ERJ2GEJ-JPW B 63.3/15.2

R631 7030005050 S.RES ERJ2GEJ 103 X (10K) B 85.3/25.0

Page 22

6 - 3

REF PARTS

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

[MAIN-A UNIT] (For [400 MHz band] versions)

R632 7030005050 S.RES ERJ2GEJ 103 X (10K) B 82.9/23.1

R633 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 85.7/21.9

R634 7030005050 S.RES ERJ2GEJ 103 X (10K) T 82.7/11.4

R635 7030005050 S.RES ERJ2GEJ 103 X (10K) T 88.1/14.8

R636 7030005050 S.RES ERJ2GEJ 103 X (10K) T 88.1/13.9

R637 7030005050 S.RES ERJ2GEJ 103 X (10K) T 91.4/21.3

R638 7030005090 S.RES ERJ2GEJ 104 X (100K) T 77.4/16.1

R639 7030005090 S.RES ERJ2GEJ 104 X (100K) T 78.6/15.7

R640 7030005090 S.RES ERJ2GEJ 104 X (100K) B 74.8/13.1

R641 7030005090 S.RES ERJ2GEJ 104 X (100K) T 77.5/22.2

R646 7030005090 S.RES ERJ2GEJ 104 X (100K) B 93.0/22.8

R647 7030005120 S.RES ERJ2GEJ 102 X (1K) B 90.3/20.9

R651 7030005120 S.RES ERJ2GEJ 102 X (1K) T 86.5/13.4

R652 7030005120 S.RES ERJ2GEJ 102 X (1K) B 90.5/22.1

R653 7030005120 S.RES ERJ2GEJ 102 X (1K) B 84.8/21.9

R657 7030005120 S.RES ERJ2GEJ 102 X (1K) T 84.9/13.1

R661 7410001130 S.ARR EXB28V102JX B 90.9/12.3

R662 7410001130 S.ARR EXB28V102JX B 90.9/14.8

R663 7410001130 S.ARR EXB28V102JX B 88.4/22.3

R664 7410001150 S.ARR EXB28V471JX B 80.2/22.3

R665 7410001130 S.ARR EXB28V102JX B 77.2/22.3

R666 7410001130 S.ARR EXB28V102JX B 75.3/11.1

R667 7410001130 S.ARR EXB28V102JX B 79.4/6.4

R668 7410001130 S.ARR EXB28V102JX B 82.4/6.4

R669 7410001130 S.ARR EXB28V102JX B 85.2/6.4

R683 7030005120 S.RES ERJ2GEJ 102 X (1K) B 90.7/19.7

R688 7030007290 S.RES ERJ2GEJ 222 X (2.2K) T 81.0/13.1

R691 7030005090 S.RES ERJ2GEJ 104 X (100K) T 83.1/12.6

R692 7030005120 S.RES ERJ2GEJ 102 X (1K) T 92.3/20.4

R693 7030007340 S.RES ERJ2GEJ 153 X (15K) B 93.6/21.9

R694 7030012540 S.RES ERJ2RHD 1502X (15.0K) B 91.9/20.8

R904 7030007300 S.RES ERJ2GEJ 332 X (3.3K) B 73.6/30.0

R905 7030007250 S.RES ERJ2GEJ 220 X (22) T 75.2/33.2

R906 7030005210 S.RES ERJ2GEJ 822 X (8.2K) T 75.2/34.1

R907 7030005210 S.RES ERJ2GEJ 822 X (8.2K) B 76.1/30.2

R908 7030007300 S.RES ERJ2GEJ 332 X (3.3K) T 71.6/31.9

R909 7030004980 S.RES ERJ2GEJ 101 X (100) B 76.1/29.3

R910 7030005240 S.RES ERJ2GEJ 473 X (47K) T 79.4/32.9

R911 7030010040 S.RES ERJ2GEJ-JPW B 83.3/33.6

R912 7030004980 S.RES ERJ2GEJ 101 X (100) B 85.2/29.5

R913 7030004980 S.RES ERJ2GEJ 101 X (100) B 85.2/30.4

R914 7030010040 S.RES ERJ2GEJ-JPW B 75.9/42.5

R915 7030005090 S.RES ERJ2GEJ 104 X (100K) B 84.8/34.2

R916 7030005240 S.RES ERJ2GEJ 473 X (47K) B 79.0/38.0

R917 7030005090 S.RES ERJ2GEJ 104 X (100K) B 85.6/32.1

R918 7030005240 S.RES ERJ2GEJ 473 X (47K) B 81.5/28.6

R919 7030005240 S.RES ERJ2GEJ 473 X (47K) B 80.0/29.8

R920 7030010040 S.RES ERJ2GEJ-JPW B 82.4/28.6

R921 7030010040 S.RES ERJ2GEJ-JPW T 79.8/31.7

R922 7030004980 S.RES ERJ2GEJ 101 X (100) B 85.5/35.2

R923 7030005120 S.RES ERJ2GEJ 102 X (1K) B 72.3/46.3

R925 7030005240 S.RES ERJ2GEJ 473 X (47K) B 75.5/49.3

R930 7030005240 S.RES ERJ2GEJ 473 X (47K) T 83.0/28.9

R931 7030005240 S.RES ERJ2GEJ 473 X (47K) T 82.1/28.2

R932 7030005240 S.RES ERJ2GEJ 473 X (47K) T 82.1/29.8

R933 7030004970 S.RES ERJ2GEJ 470 X (47) B 72.3/45.4

R934 7030005240 S.RES ERJ2GEJ 473 X (47K) B 76.9/48.6

R935 7030004970 S.RES ERJ2GEJ 470 X (47) B 81.4/48.6

R936 7030005240 S.RES ERJ2GEJ 473 X (47K) B 79.6/48.6

R937 7030005240 S.RES ERJ2GEJ 473 X (47K) B 78.7/48.6

R938 7030004980 S.RES ERJ2GEJ 101 X (100) B 79.9/43.8

R939 7030007290 S.RES ERJ2GEJ 222 X (2.2K) B 79.9/42.0

R940 7030005240 S.RES ERJ2GEJ 473 X (47K) B 76.8/41.8

R941 7030005240 S.RES ERJ2GEJ 473 X (47K) B 77.7/42.5

R945 7410001140 S.ARR EXB28V104JX T 86.5/43.9

R946 7410001140 S.ARR EXB28V104JX B 82.9/41.4

R947 7410001140 S.ARR EXB28V104JX B 92.3/37.0

R948 7410001140 S.ARR EXB28V104JX B 87.8/35.8

R949 7410001140 S.ARR EXB28V104JX B 93.9/33.0

R950 7410001140 S.ARR EXB28V104JX B 88.4/33.0

R951 7410001140 S.ARR EXB28V104JX T 84.8/29.3

R952 7030005090 S.RES ERJ2GEJ 104 X (100K) T 78.1/36.8

R953 7030005090 S.RES ERJ2GEJ 104 X (100K) T 78.8/37.7

R956 7030010040 S.RES ERJ2GEJ-JPW B 96.3/32.9

R957 7030005090 S.RES ERJ2GEJ 104 X (100K) B 94.7/30.9

R958 7030005090 S.RES ERJ2GEJ 104 X (100K) B 85.7/42.4

R961 7030005090 S.RES ERJ2GEJ 104 X (100K) B 90.9/30.9

R962 7030005090 S.RES ERJ2GEJ 104 X (100K) T 89.5/28.4

R963 7030005090 S.RES ERJ2GEJ 104 X (100K) B 95.4/32.9

R964 7410001140 S.ARR EXB28V104JX B 85.9/39.4

R965 7030005090 S.RES ERJ2GEJ 104 X (100K) B 78.8/29.8

R966 7030005090 S.RES ERJ2GEJ 104 X (100K) B 77.9/29.8

R968 7030005090 S.RES ERJ2GEJ 104 X (100K) T 88.9/18.3

R969 7030005160 S.RES ERJ2GEJ 105 X (1M) T 88.2/19.7

R970 7030010040 S.RES ERJ2GEJ-JPW B 71.4/38.1

R971 7030010040 S.RES ERJ2GEJ-JPW B 75.3/38.0

R972 7030010040 S.RES ERJ2GEJ-JPW B 74.0/38.6

R973 7030004970 S.RES ERJ2GEJ 470 X (47) B 84.7/36.7

R974 7030004970 S.RES ERJ2GEJ 470 X (47) B 82.5/37.7

C1 4030017550 S.CER C1005 CH 1H 1R5B-T B 8.5/5.7

C2 4030017600 S.CER C1005 CH 1H 080C-T B 10.6/5.7

C3 4030017340 S.CER C1005 CH 1H 010B-T B 12.2/8.0

C4 4030017550 S.CER C1005 CH 1H 1R5B-T B 8.9/10.5

C5 4030017590 S.CER C1005 CH 1H 070C-T B 10.7/14.9

C6 4030017340 S.CER C1005 CH 1H 010B-T B 12.2/10.0

C7 4030017460 S.CER C1005 JB 1H 102K-T B 14.7/9.5

C8 4030017560 S.CER C1005 CH 1H 2R5B-T B 12.4/14.9

C9 4030017360 S.CER C1005 CH 1H 030B-T B 12.4/15.8

C10 4030017460 S.CER C1005 JB 1H 102K-T B 14.8/13.5

C11 4030017460 S.CER C1005 JB 1H 102K-T B 16.4/13.5

C12 4030017610 S.CER C1005 CH 1H 090C-T B 17.2/12.0

C13 4030017640 S.CER C1005 CH 1H 150J-T B 19.7/11.8

C14 4030007060 S.CER C1608 CH 1H 270J-T B 21.4/10.3

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

S.=Surface mount

REF PARTS

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

[MAIN-A UNIT] (For [400 MHz band] versions)

C18 4030017460 S.CER C1005 JB 1H 102K-T B 19.8/19.2

C19 4030017460 S.CER C1005 JB 1H 102K-T B 18.2/19.2

C26 4030017460 S.CER C1005 JB 1H 102K-T T 29.4/5.7

C27 4030017460 S.CER C1005 JB 1H 102K-T T 37.2/5.7

C28 4030017460 S.CER C1005 JB 1H 102K-T T 33.9/11.5

C30 4030018890 S.CER C1005 JB 0J 224K-T T 32.8/6.6

C31 4030016930 S.CER C1005 JB 1A 104K-T T 34.8/11.5

C32 4030017460 S.CER C1005 JB 1H 102K-T T 35.7/9.9

C33 4030017460 S.CER C1005 JB 1H 102K-T T 37.2/7.5

C34 4030018910 S.CER C1608 JB 0J 475K-T T 37.2/9.6

C35 4030017460 S.CER C1005 JB 1H 102K-T B 37.3/9.2

C36 4030017420 S.CER C1005 CH 1H 470J-T B 23.8/16.1

C37 4030017720 S.CER C1005 JB 1H 331K-T B 24.7/16.1

C38 4030017460 S.CER C1005 JB 1H 102K-T B 32.7/15.1

C39 4030017420 S.CER C1005 CH 1H 470J-T B 32.7/14.1

C45 4030017420 S.CER C1005 CH 1H 470J-T B 32.7/12.1

C47 4030017720 S.CER C1005 JB 1H 331K-T B 32.3/9.2

C48 4030017420 S.CER C1005 CH 1H 470J-T B 23.6/19.7

C49 4030017460 S.CER C1005 JB 1H 102K-T B 21.2/19.7

C50 4030017420 S.CER C1005 CH 1H 470J-T T 22.1/17.8

C51 4030017570 S.CER C1005 CH 1H 040B-T B 39.1/14.2

C52 4030017460 S.CER C1005 JB 1H 102K-T B 41.0/8.9

C53 4030017720 S.CER C1005 JB 1H 331K-T B 42.6/10.7

C54 4030017460 S.CER C1005 JB 1H 102K-T B 42.6/8.9

C55 4030017620 S.CER C1005 CH 1H 100C-T B 39.1/12.5

C57 4030017720 S.CER C1005 JB 1H 331K-T B 37.3/10.8

C59 4030017380 S.CER C1005 CH 1H 050B-T B 43.7/14.0

C60 4030017420 S.CER C1005 CH 1H 470J-T B 45.5/8.9

C61 4030017460 S.CER C1005 JB 1H 102K-T B 47.1/11.6

C62 4030017600 S.CER C1005 CH 1H 080C-T B 45.5/11.6

C63 4030017380 S.CER C1005 CH 1H 050B-T B 47.4/15.2

C64 4030017460 S.CER C1005 JB 1H 102K-T B 49.6/12.1

C65 4030017460 S.CER C1005 JB 1H 102K-T B 51.2/14.0

C66 4030017350 S.CER C1005 CH 1H 020B-T T 60.1/17.7

C67 4030017350 S.CER C1005 CH 1H 020B-T B 51.7/15.7

C68 4030017460 S.CER C1005 JB 1H 102K-T T 23.0/17.8

C71 4030017620 S.CER C1005 CH 1H 100C-T T 52.9/17.7

C72 4030017460 S.CER C1005 JB 1H 102K-T B 57.1/16.2

C73 4030017460 S.CER C1005 JB 1H 102K-T T 53.8/19.3

C74 4030017380 S.CER C1005 CH 1H 050B-T T 58.3/19.3

C75 4030017420 S.CER C1005 CH 1H 470J-T B 47.1/10.7

C76 4030017460 S.CER C1005 JB 1H 102K-T B 55.4/17.1

C77 4030017460 S.CER C1005 JB 1H 102K-T T 64.6/19.3

C78 4030017460 S.CER C1005 JB 1H 102K-T T 59.2/19.9

C79 4030016930 S.CER C1005 JB 1A 104K-T B 66.1/18.1

C80 4030017720 S.CER C1005 JB 1H 331K-T B 64.4/23.2

C81 4030017360 S.CER C1005 CH 1H 030B-T T 58.3/17.7

C82 4030017420 S.CER C1005 CH 1H 470J-T B 53.6/20.7

C83 4030017540 S.CER C1005 CH 1H R75B-T T 58.3/22.2

C84 4030017720 S.CER C1005 JB 1H 331K-T T 54.4/22.7

C85 4030017460 S.CER C1005 JB 1H 102K-T T 54.4/21.8

C86 4030017380 S.CER C1005 CH 1H 050B-T T 56.5/24.5

C87 4030017390 S.CER C1005 CH 1H 180J-T T 54.4/23.6

C88 4030017620 S.CER C1005 CH 1H 100C-T T 56.5/25.4

C89 4030017630 S.CER C1005 CH 1H 120J-T T 56.1/26.6

C90 4030017530 S.CER C1005 CH 1H 0R5B-T T 53.5/27.7

C91 4030018860 S.CER C1005 JB 0J 105K-T B 60.1/29.6

C92 4030017640 S.CER C1005 CH 1H 150J-T T 55.1/27.7

C93 4030017720 S.CER C1005 JB 1H 331K-T B 56.5/30.6

C94 4030017420 S.CER C1005 CH 1H 470J-T B 50.1/25.7

C95 4030017420 S.CER C1005 CH 1H 470J-T B 42.6/8.0

C101 4030017530 S.CER C1005 CH 1H 0R5B-T T 59.5/22.2

C102 4030017460 S.CER C1005 JB 1H 102K-T T 64.2/20.6

C103 4030017420 S.CER C1005 CH 1H 470J-T T 64.2/21.5

C104 4030017380 S.CER C1005 CH 1H 050B-T T 60.4/23.8

C105 4030017620 S.CER C1005 CH 1H 100C-T T 64.2/22.4

C106 4030017630 S.CER C1005 CH 1H 120J-T T 61.9/25.1

C107 4030017630 S.CER C1005 CH 1H 120J-T T 60.6/27.4

C108 4030017360 S.CER C1005 CH 1H 030B-T T 64.2/23.3

C109 4030017460 S.CER C1005 JB 1H 102K-T B 61.5/24.9

C110 4030017530 S.CER C1005 CH 1H 0R5B-T T 62.6/26.4

C111 4030017600 S.CER C1005 CH 1H 080C-T T 61.5/27.4

C112 4030017460 S.CER C1005 JB 1H 102K-T B 58.5/29.0

C116 4030018860 S.CER C1005 JB 0J 105K-T B 63.7/29.6

C117 4030017910 S.CER C1005 JB 1H 152K-T B 62.1/29.6

C118 4030017420 S.CER C1005 CH 1H 470J-T B 66.5/29.1

C119 4550006270 S.TAN TEESVP 1A 105M8R B 60.3/27.3

C120 4030017460 S.CER C1005 JB 1H 102K-T B 62.1/31.4

C121 4030019560 S.CER GRM21BB31C106KE15L B 59.9/19.7

C122 4030016790 S.CER C1005 JB 1E 103K-T B 65.0/15.5

C123 4030017460 S.CER C1005 JB 1H 102K-T B 47.0/29.0

C124 4030017460 S.CER C1005 JB 1H 102K-T B 65.3/31.4

C127 4030017460 S.CER C1005 JB 1H 102K-T T 63.0/33.8

C132 4550000560 S.TAN TEESVA 1V 334M8R T 48.3/21.4

C134 4550003250 S.TAN TEESVA 1V 474M8R T 46.7/29.8

C141 4030017580 S.CER C1005 CH 1H 060C-T B 51.5/20.0

C144 4030017430 S.CER C1005 CH 1H 101J-T T 43.3/20.5

C145 4030018890 S.CER C1005 JB 0J 224K-T T 42.4/20.5

C146 4030018890 S.CER C1005 JB 0J 224K-T T 41.5/20.5

C147 4030017460 S.CER C1005 JB 1H 102K-T T 46.4/21.1

C148 4030019560 S.CER GRM21BB31C106KE15L B 44.0/26.2

C149 4030017430 S.CER C1005 CH 1H 101J-T T 44.2/20.5

C150 4030016790 S.CER C1005 JB 1E 103K-T T 43.9/28.1

C151 4030017430 S.CER C1005 CH 1H 101J-T T 43.9/27.2

C152 4030017460 S.CER C1005 JB 1H 102K-T T 43.9/29.0

C153 4030017420 S.CER C1005 CH 1H 470J-T T 43.1/30.4

C154 4030017420 S.CER C1005 CH 1H 470J-T T 42.2/30.4

C155 4030017420 S.CER C1005 CH 1H 470J-T T 41.3/30.4

C156 4030016930 S.CER C1005 JB 1A 104K-T T 40.4/30.4

C157 4030017460 S.CER C1005 JB 1H 102K-T T 41.0/18.8

C158 4030017620 S.CER C1005 CH 1H 100C-T T 39.2/18.8

C159 4030016930 S.CER C1005 JB 1A 104K-T T 40.1/11.0

C160 4030017460 S.CER C1005 JB 1H 102K-T T 41.9/11.0

C167 4030017590 S.CER C1005 CH 1H 070C-T B 49.3/21.3

C168 4030017590 S.CER C1005 CH 1H 070C-T B 48.4/21.3

Page 23

6 - 4

REF PARTS

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

[MAIN-A UNIT] (For [400 MHz band] versions)

C171 4030017570 S.CER C1005 CH 1H 040B-T B 15.3/16.0

C172 4030017350 S.CER C1005 CH 1H 020B-T B 15.3/17.2

C173 4030017460 S.CER C1005 JB 1H 102K-T B 13.9/18.8

C175 4030017420 S.CER C1005 CH 1H 470J-T B 13.9/20.5

C176 4030017650 S.CER C1005 CH 1H 270J-T B 15.8/23.9

C177 4030017600 S.CER C1005 CH 1H 080C-T B 15.8/24.8

C178 4030017350 S.CER C1005 CH 1H 020B-T B 14.5/25.2

C179 4030017580 S.CER C1005 CH 1H 060C-T B 15.8/25.7

C180 4030017660 S.CER C1005 CH 1H 330J-T B 15.8/26.6

C181 4030017590 S.CER C1005 CH 1H 070C-T B 17.4/29.0

C182 4030017460 S.CER C1005 JB 1H 102K-T B 21.7/21.9

C183 4030017460 S.CER C1005 JB 1H 102K-T B 20.1/25.4

C184 4030016930 S.CER C1005 JB 1A 104K-T B 20.1/26.3

C186 4030016930 S.CER C1005 JB 1A 104K-T B 19.2/31.0

C188 4030017460 S.CER C1005 JB 1H 102K-T B 23.2/31.0

C189 4030017460 S.CER C1005 JB 1H 102K-T B 23.9/25.4

C192 4030017460 S.CER C1005 JB 1H 102K-T B 23.9/27.2

C194 4030017460 S.CER C1005 JB 1H 102K-T B 22.1/27.2

C195 4030017350 S.CER C1005 CH 1H 020B-T B 23.2/28.5

C196 4030017630 S.CER C1005 CH 1H 120J-T B 27.4/28.5

C197 4030017530 S.CER C1005 CH 1H 0R5B-T B 29.2/28.9

C198 4030017630 S.CER C1005 CH 1H 120J-T B 31.0/28.5

C199 4030017350 S.CER C1005 CH 1H 020B-T B 34.4/26.4