Page 1

GUIDE FOR CD

1) COMPOSITION

IC_756PRO3

A3format.pdf

756PRO3.pdf

FYC

A4format.pdf

Instruction.pdf

Unitparts.pdf

ar505eng.exe

Installer

W_README.txt

2) DESCRIPTION

756PRO3.pdf

756PRO3.pdf is a service manual for IC-756PROIII and including all service information in this CD. This file is

mainly used for viewing on the computer display and checking page order to make printed service manual. Or

when you want to find a component, you can find very fast using “FIND” function (except Board layout).

A3format.pdf

A3format.pdf consists of A3 format pages (Board layout, Mechanical parts and disassembly, and etc.) in

756PRO3.pdf. This file is used for printing out A3 format pages.

A4format.pdf

A4format.pdf consists of A4 format pages (Circuit description, Adjustment procedures, Parts list, and etc.) in

756PRO3.pdf. This file is used for printing out A4 format pages.

Instruction.pdf

Instruction.pdf is a instruction manual for IC-756PROIII. This file is exactly same as supplying instruction

manual withproduct and consists of all A4 format pages. If you have A4 format printer, you can print out and

make brand new instruction manual any time you want. Also this fi le is very helpful when you want to change

or set product conditionfor adjustment or else.

Unitparts.pdf

Unitparts.pdf is assemble unit information for IC-756PROIII. This information for authorized dis-tributor/dealer

only. Because we (ICOM INC.) don’t sell assemble unit to general.

ar505eng.exe

ar505eng.exe is an installation program of Adobe Acrobat® Reader 5.0 (English version) for Microsoft®

Windows® 95/98/Me/NT/2000/XP users.

1

Page 2

W_README.txt

W_README.txt is a readme text about this service manual for Windows® user that not installed Acrobat®

Reader yet.

=========================================================================================

Icom, Icom Inc. and Icom logo are registered trademarks of Icom Incorporated (Japan) in the United states, the

United Kingdom, Germany, France, Spain, Russia and/or other countries.

Acrobat Reader Copyright © 1987-2002 Adobe Systems Incorporated. All rights reserved.

Adobe, the Adobe logo, Acrobat, and the Acrobat logo are trademarks of Adobe Systems Incorporated.

Microsoft and Windows are registered trademarks of Microsoft Corporation in the U.S.A. and other countries.

Copyright 2004 Icom Inc.

=========================================================================================

2

Page 3

HF/50MHz ALL MODE TRANSCEIVER

SERVICE

MANUAL

Page 4

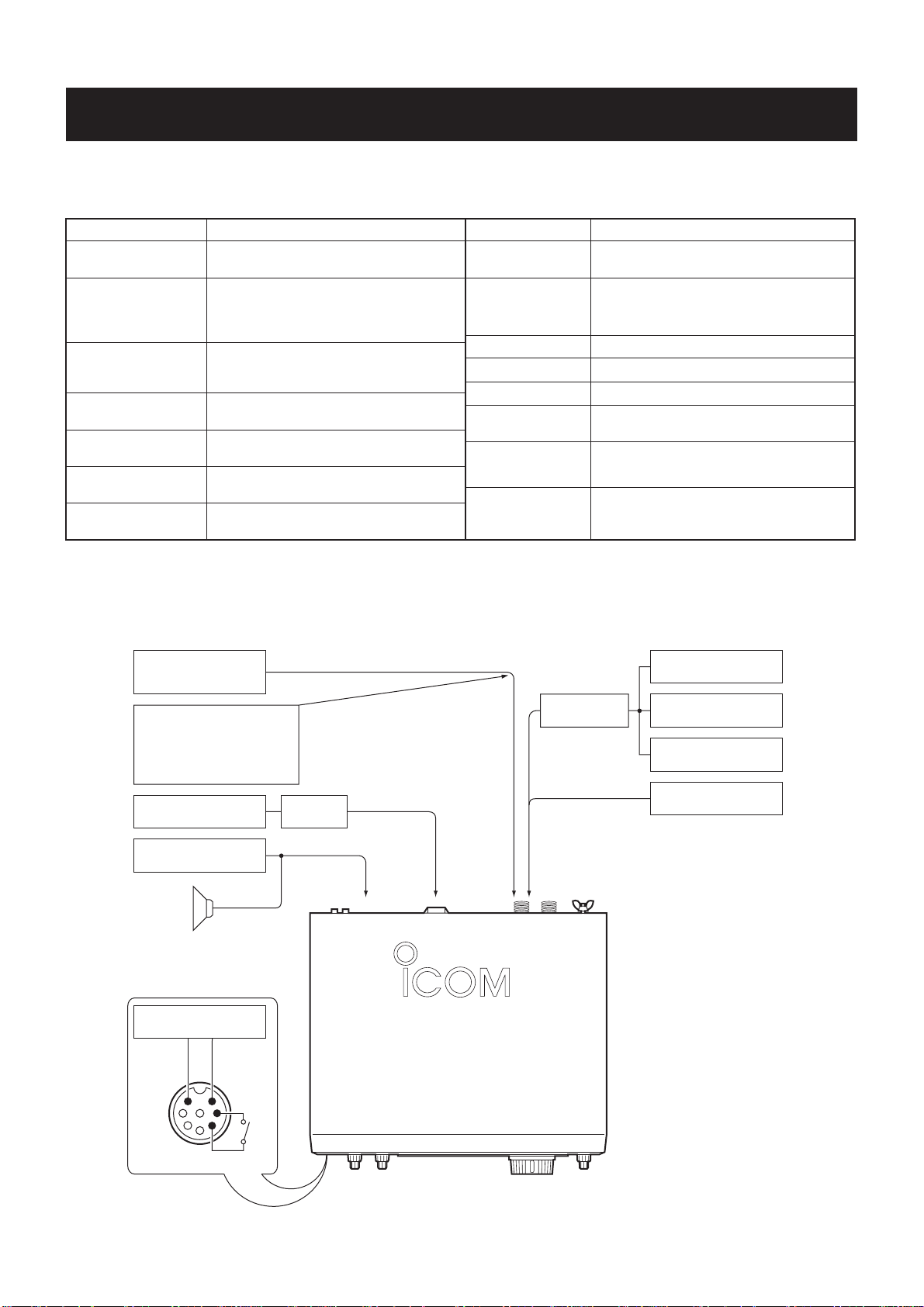

U.S.A.

Europe

France

United Kingdom

Italy

Korea

Spain

#32

#33

#34

#35

#38

#39

#40

USA

EUR

FRA

UK

ITA

KOR

ESP

INTRODUCTION

This service manual describes the latest service information

for the IC-756PROIII HF/50MHz ALL MODE TRANSCEIVER.

DANGER

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 16 V. This will ruin the

transceiver.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOTre v erse the polarities of the power supply when con-

necting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW)

to the antenna connector. This could damage the transceiver’s front end.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1110000960 S.IC NJM4558M IC-756PROIII MAIN-A UNIT 5 pieces

8810005770 Screw BiH M3

×8 ZK IC-756PROIII Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

REPAIR NOTES

1. Make sure a problem is internal before disassembling the

transceiver.

2.

DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3.

DO NOT force any of the variable components. Turn

them slowly and smoothly.

4.

DO NOT shor t any circuits or electronic parts. An insulated tuning tool

MUST be used for all adjustments.

5.

DO NOT keep power ON for a long time when the transceiver is defective.

6.

DO NOT transmit power into a signal generator or a

sweep generator.

7.

ALWAYS connect a 50 dB to 60 dB attenuator between

the transceiver and a deviation meter or spectrum analyzer when using such test equipment.

8.

READ the instructions of test equipment thoroughly

before connecting equipment to the transceiver.

To upgrade quality, any electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

Icom, Icom Inc. and are registered trademarks of Icom Incor porated (Japan) in the United States, the United Kingdom,

Germany, France, Spain, Russia and/or other countries.

VER.NO. SYMBOL VERSION

Page 5

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 CIRCUIT DESCRIPTION

SECTION 4 ADJUSTMENT PROCEDURES

SECTION 5 PARTS LIST

SECTION 6 MECHANICAL PARTS AND DISASSEMBLY

SECTION 7 SEMI-CONDUCTOR INFORMATION

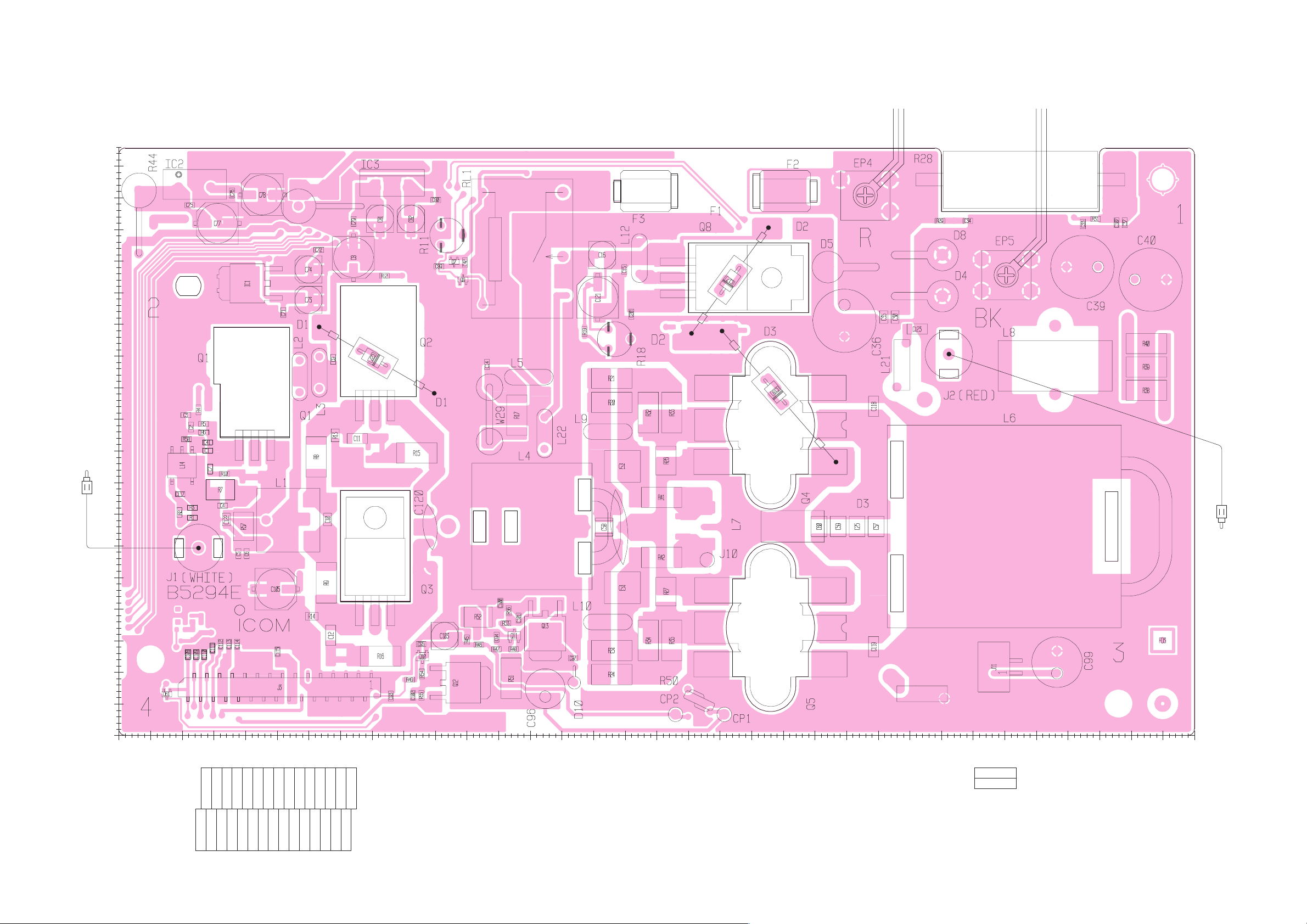

SECTION 8 BOARD LAYOUTS

8 - 1 DISPLAY BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 1

8 - 2 MODE BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 3

8 - 3 PHONE BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 3

8 - 4 KEY BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 3

8 - 5 TEN-KEY BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 3

8 - 6 PBT BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 5

8 - 7 RIT BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 5

8 - 8 MIC BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 5

8 - 9 MEMORY BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 5

8 - 10 MAIN-A UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 7

8 - 11 DSP-A BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 9

8 - 12 RF-B UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 11

8 - 13 BPF-A BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 13

8 - 14 PREAMP BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 13

8 - 15 PLL UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 15

8 - 16 PA UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 17

8 - 17 FILTER-A UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 19

8 - 18 CTRL-A UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 - 21

8 - 19 TUNER-A BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8- 23

SECTION 9 BLOCK DIAGRAM

SECTION 10 VOLTAGE DIAGRAMS

10 - 1 FRONT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 1

10 - 2 DSP-A BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 3

10 - 3 TUNER-A, MEMORY BOARDS AND CTRL-A UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 5

10 - 4 MAIN-A UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 7

10 - 5 PLL UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 12

10 - 6 PA AND FILTER-A UNITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 15

10 - 7 BPF-A, PREAMP BOARDS AND RF-B UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 17

Page 6

SECTION 1 SPECIFICATIONS

■ GENERAL

• Frequency coverage:

Receive 0.030–60.000 MHz*

Transmit 1.800–1.999 MHz*2 3.500–3.999 MHz*

5.3305, 5.3465, 5.3665, 5.3715, 5.4035 MHz*

7.000–7.300 MHz*2 10.100–10.150 MHz*

14.000–14.350 MHz*2 18.068–18.168 MHz*

21.000–21.450 MHz*2 24.890–24.990 MHz*

28.000–29.700 MHz*2 50.000–54.000 MHz*

*1 Some frequency bands are not guaranteed.

2

Depending on version.

*

3

*

[USA] only.

• Mode : USB, LSB, CW, RTTY, AM, FM

• Number of memory channels :

101 (99 regular, 2 scan edges)

• Antenna connector : SO-239

phono jack (RCA; 50 Ω)

• Usable temp. range : –10˚C to +50˚C (14˚F to 122˚F)

• Frequency stability : Less than ±0.5 ppm from 1 min. after

power ON.

• Freq. resolution : 1 Hz

• Power supply

requirement:

13.8 V DC ±15%

• Current drain :

Transmit max. power 23 A

Receive stand-by 3.0 A (typical)

max. audio 3.3 A (typical)

• Dimensions : 340(W)×111(H)×285(D) mm

3

(proj. not included) ; 3

⁄8(W)×43⁄8(H)×117⁄32(D) in

• Weight (approx.) : 9.6 kg (21 lb 3 oz)

• ACC 1 connector : 8-pin DIN connector

• ACC 2 connector : 7-pin DIN connector

• CI-V connector : 2-conductor 3.5(d) mm (

• Display : 5-inch (diagonal) TFT color LCD

,

1

2

*

× 2 (50 Ω)

(–10˚C to +50˚C; 14˚F to 122˚F)

(negative ground)

1

⁄8")

2

3

2

2

2

2

■ TRANSMITTER

• Output power :

SSB/CW/RTTY/FM 5–100 W

AM 5–40 W

• Modulation system :

SSB PSN modulation

AM Low power modulation

FM Phase modulation

• Spurious emission : Less than –50 dB (HF bands)

Less than –60 dB (50 MHz band)

• Carrier suppression : More than 40 dB

• Unwanted sideband suppression:

More than 55 dB

• TX variable range : ±9.999 kHz

• Mic. connector : 8-pin connector (600 Ω)

1

• ELE-KEY connector: 3-conductor 6.35(d) mm (

• KEY connector : 3-conductor 6.35(d) mm (

• SEND connector : Phono jack (RCA)

• ALC connector : Phono jack (RCA)

⁄4")

1

⁄4")

■ RECEIVER

• Receive system : Triple-conversion

superheterodyne system

• Intermediate frequencies:

1st IF 64.455 MHz

2nd IF 455 kHz

3rd IF 36 kHz

• Sensitivity :

SSB, CW, RTTY (at 2.4 kHz bandwidth)

1

1.8–29.99 MHz*

50.0–54.0 MHz*

0.16 µV (10 dB S/N)

2

0.13 µV (10 dB S/N)

AM (at 6.0 kHz bandwidth)

0.5–1.799 MHz 13 µV (10 dB S/N)

1

1.8–29.99 MHz*

50.0–54.0 MHz*

FM (at 15 kHz bandwidth)

28.0–29.99 MHz*

50.0–54.0 MHz*

*1 Pre-amp 1 ON *2 Pre-amp 2 ON

2.0 µV (10 dB S/N)

2

1.0 µV (10 dB S/N)

1

0.5 µV (12 dB SINAD)

2

0.32 µV (12 dB SINAD)

• Squelch sensitivity : (Pre-amp OFF)

SSB/CW/RTTY Less than 5.6 µV

FM Less than 1.0 µV

• Selectivity :

SSB/RTTY (at 2.4 kHz bandwidth)

More than 2.4 kHz/–6 dB

Less than 3.6 kHz/–60 dB

CW (at 500 Hz bandwidth)

More than 500 Hz/–6 dB

Less than 700 Hz/–60 dB

AM (at 6 kHz bandwidth)

More than 6.0 kHz/–6 dB

Less than 15.0 kHz/–60 dB

FM (at 15 kHz bandwidth)

More than 12 kHz/–6 dB

Less than 20 kHz/–60 dB

• Spurious and image rejection ratio:

More than 70 dB

(except IF through in 50 MHz band)

• RIT variable range : ±9.999 kHz

• Audio output power : More than 2.0 W at 10% distortion

(at 13.8 V DC) with an 8 Ω load

• PHONES connector: 3-conductor 6.35(d) mm (

• EXT SP connector : 2-conductor 3.5(d) mm (

1

1

⁄8") 8

⁄4")

Ω

■ ANTENNA TUNER

• Matching impedance range:

HF bands 16.7 to 150 Ω unbalanced*

50 MHz band 20 to 125 Ω unbalanced*

*1 Less than VSWR 3:1 *2 Less than VSWR 2.5:1

• Minimum operating input power:

8 W

• Tuning accuracy : VSWR 1.5:1 or less

• Insertion loss : Less than 1.0 dB

(after tuning)

1

2

All stated specifications are subject to change without notice or obligation.

1 - 1

Page 7

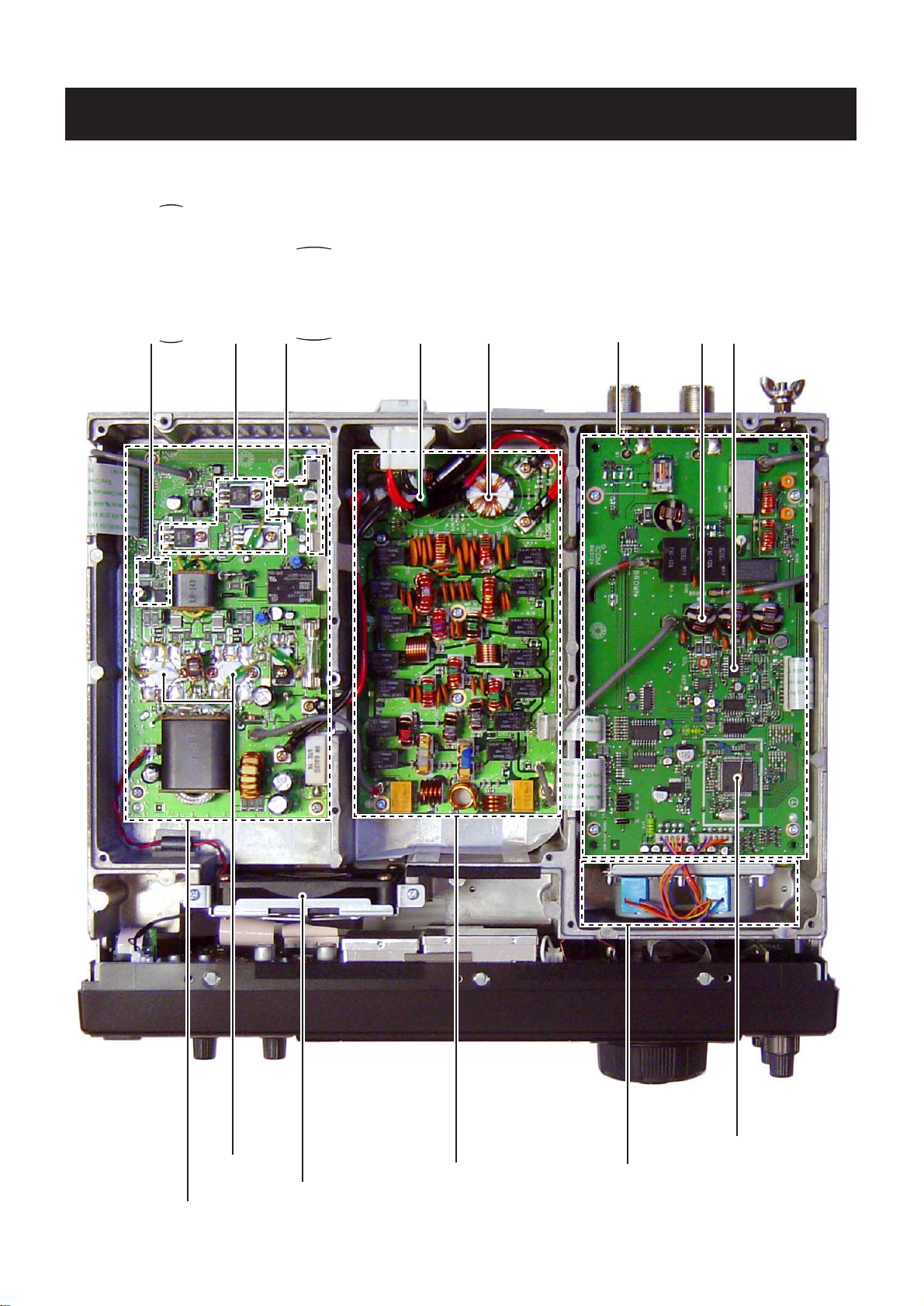

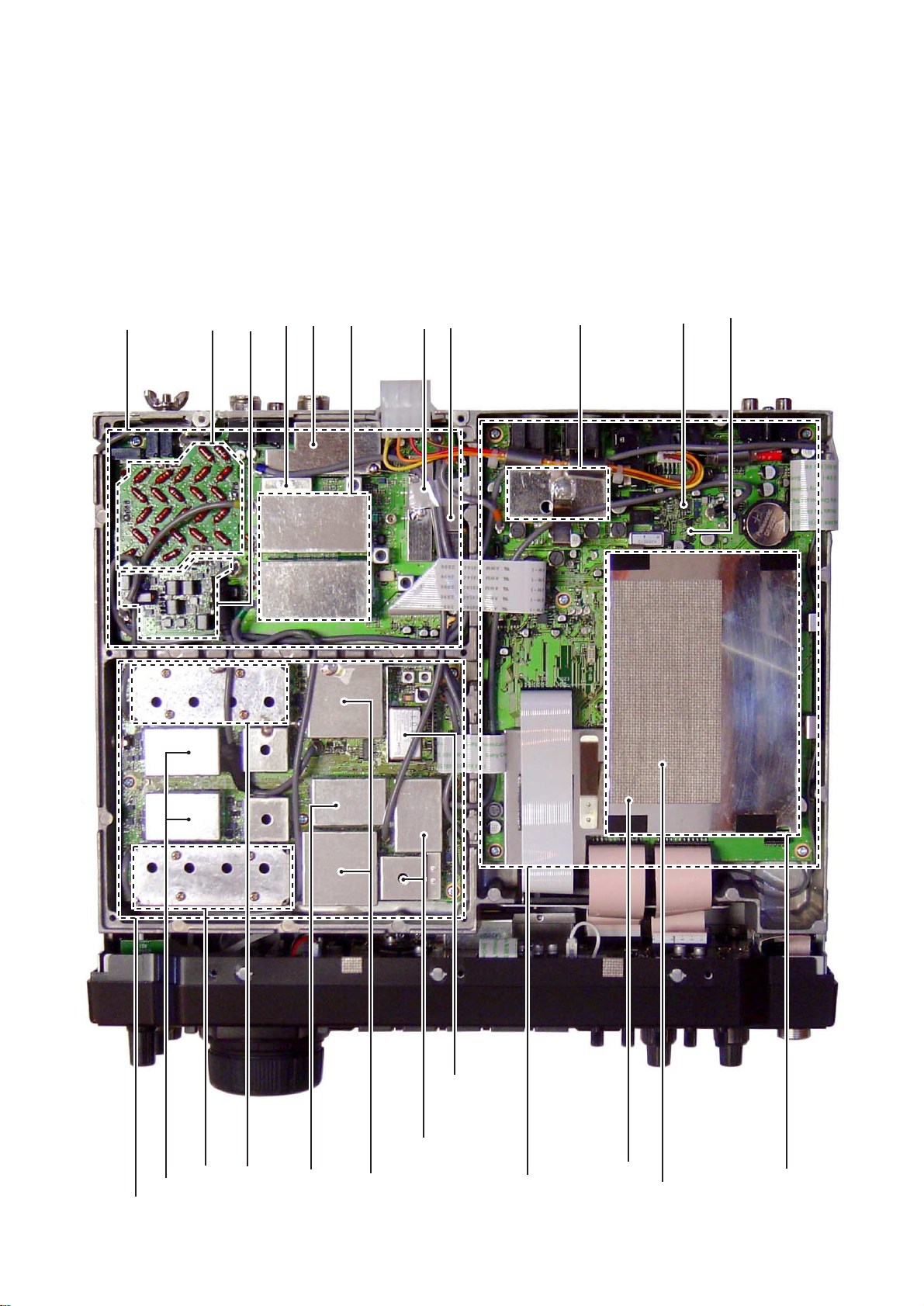

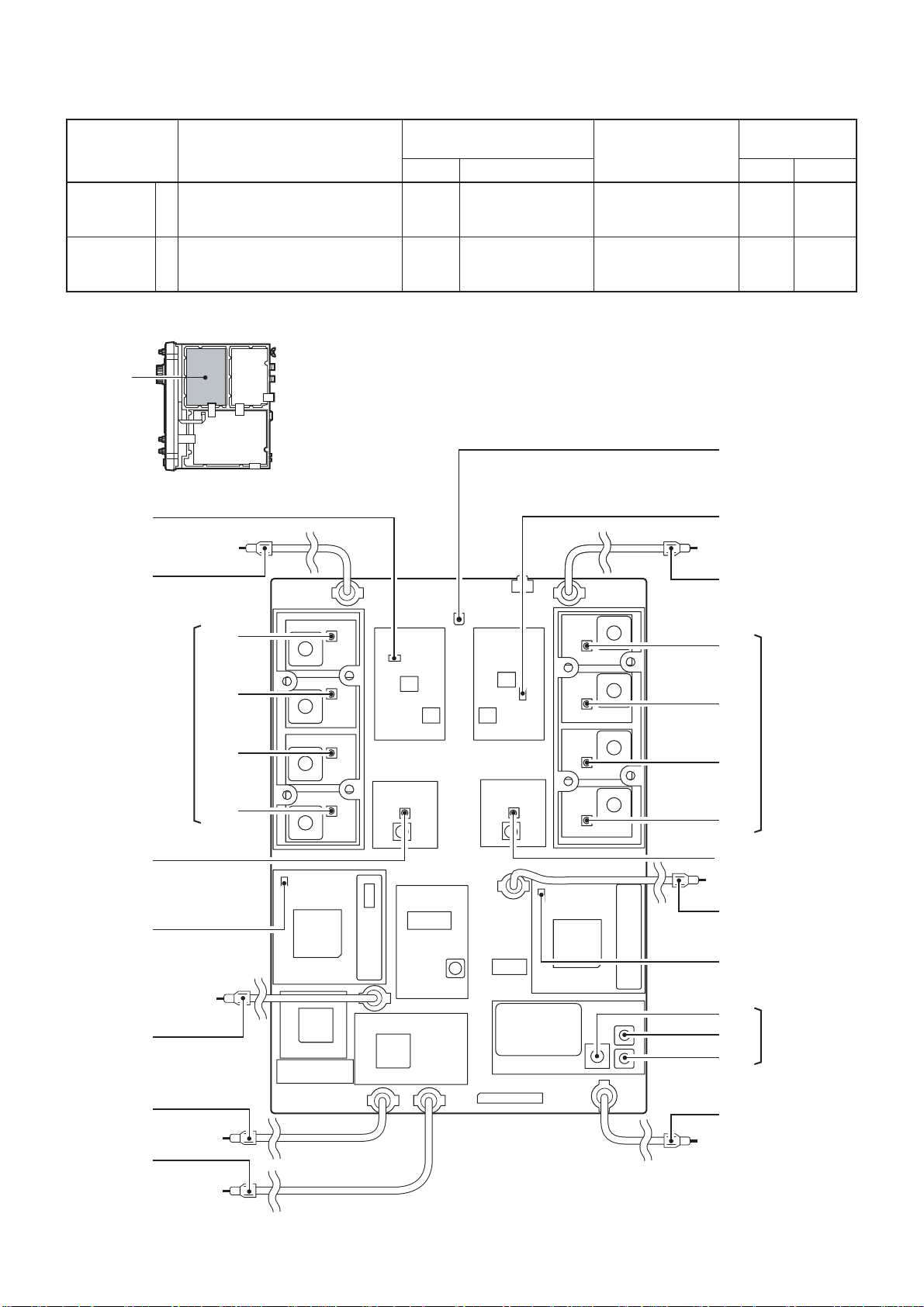

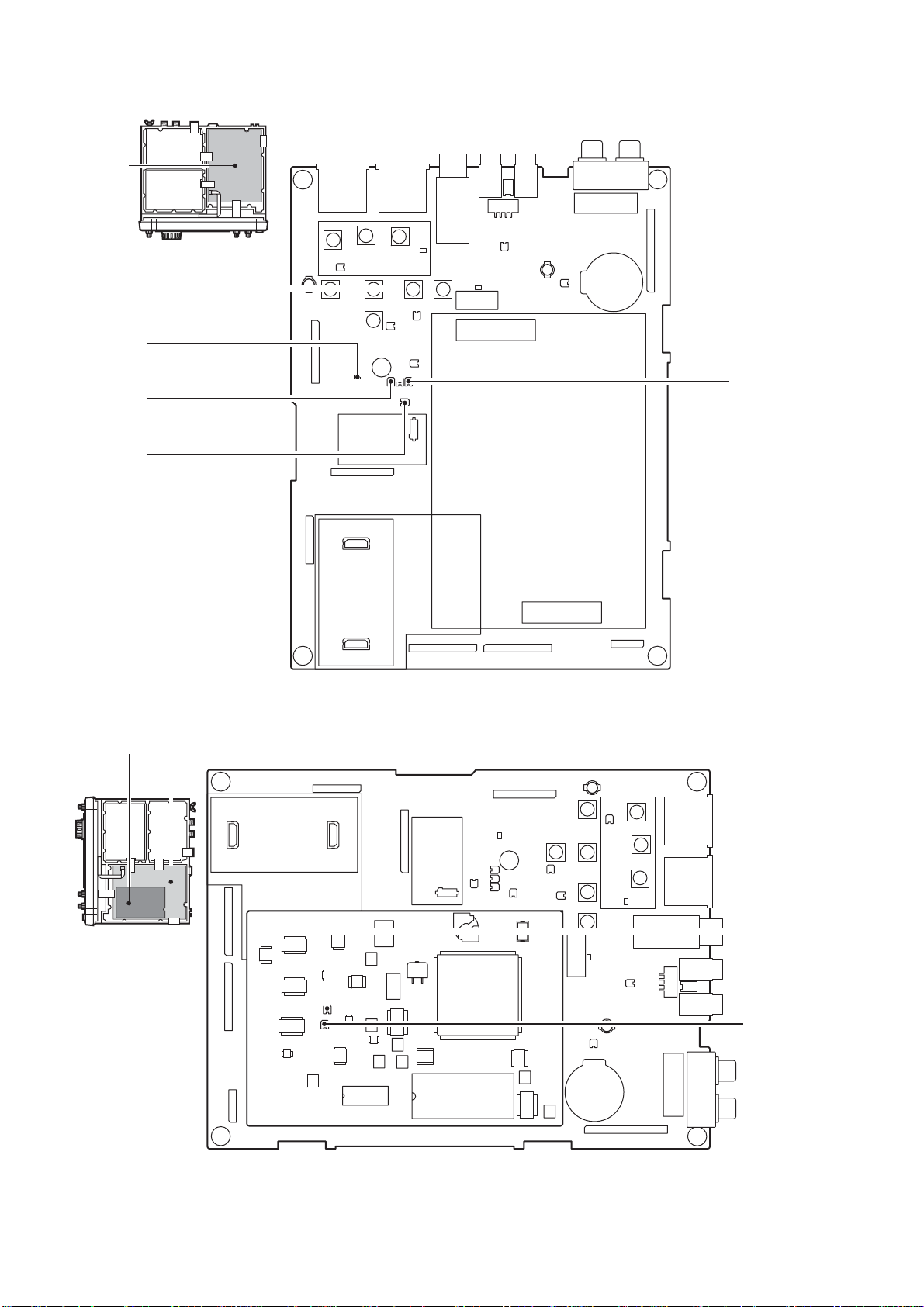

SECTION 2 INSIDE VIEWS

2 - 1

• TOP VIEW

Fan control circuit

PA unit

Fan

FILTER-A unit

TUNER-A unit

Antenna tuner CPU

(IC5: M38022M2-138FP)

Drive amplifier

Voltage regulator

Common filter

(L501: LR-386)

Common filter

(L502: LR-386)

CTRL-A unit

Current transformer

(L1: LR-364)

C-MOS IC

(IC14: TC74AC04F)

Fan control circuit

Q10, Q11: 2SC4081×2

Q12, Q13: 2SB1201×2

PA unit

Cooling fan

FILTER-A unit

TUNER-A unit

Antenna tuner CPU

(IC5: M38022M2-138FP)

Drive amplifier circuit

(Q2, Q3: 2SC1972×2)

Voltage regulator

IC1: TA7805F

IC2: TA7805S

IC3: TA78T08C

Common filter

(L501: LR-386)

Common filter

(L502: LR-386)

CTRL-A unit

Current transformer

(L1: LR-364)

C-MOS IC

(IC14: TC74AC04F)

Power amplifier

(Q4, Q5: 2SC5125×2)

Power amplifiers

(Q4, Q5: 2SC5125×2)

Page 8

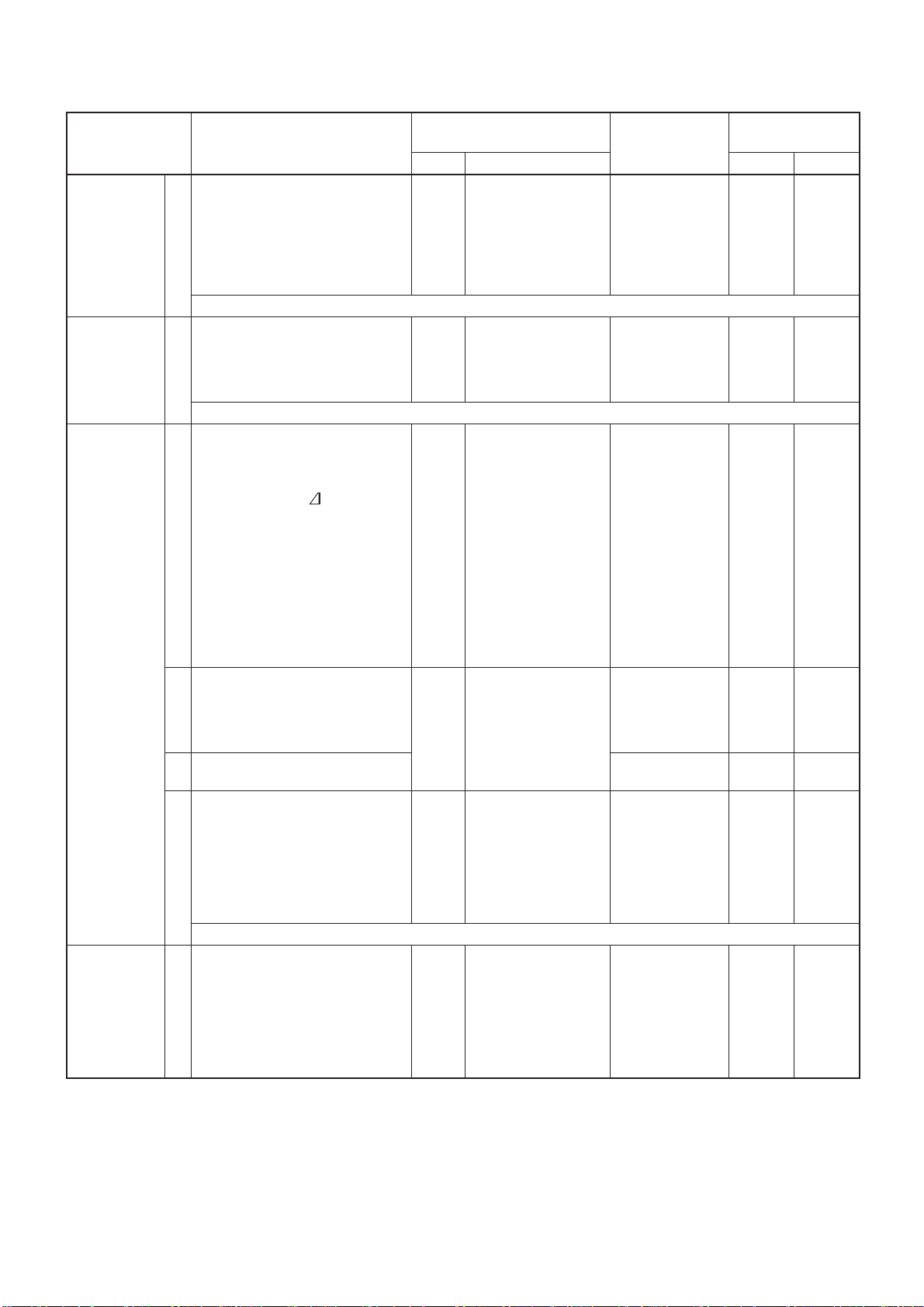

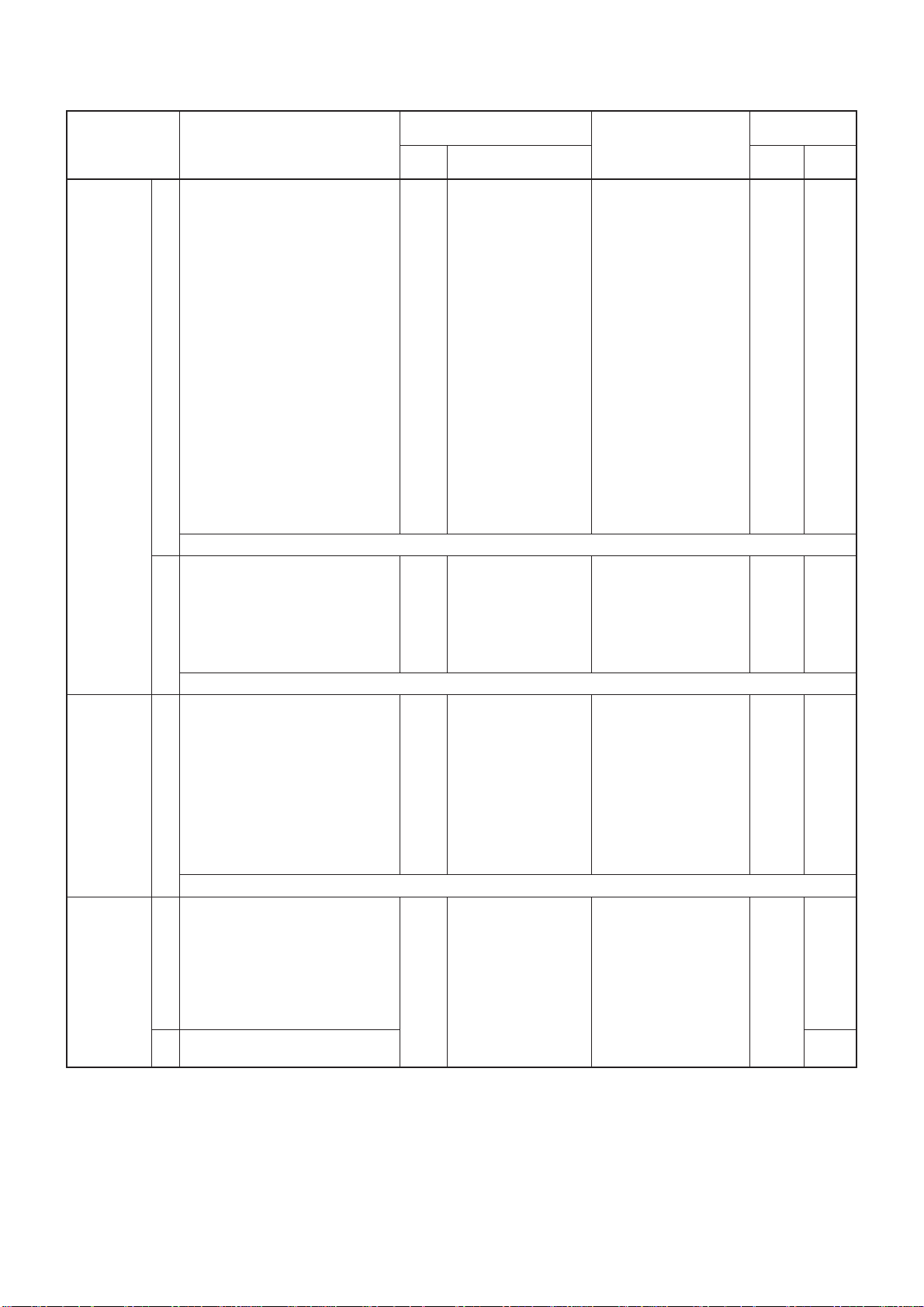

2 - 2

• BOTT OM VIEW

Reference frequency oscillator

(X52: CR-338 32.00056MHz)

RF-B unit

BPF-A board

PLL unit

1LO PLL IC

(IC381, IC681: LMX2306TM)

VCO-B circuit

VCO-A circuit

S2LO PLL IC

(IC901: LC7153M)

1LO DDS IC

(IC101, IC401: SC-1246A)

3LO/S3LO DDS IC

(IC701, IC801: SC-1287)

MAIN-A unit

Noise blanker circuit

LCD contorller

(IC3551: S1D13504F00A000)

MAIN CPU

(IC3501: HD64F2375F20)

TX 3rd mixer

(IC221: NJM1496V)

RX 3rd mixer

(IC151: TC4W53FU)

DSP-A board

PREAMP board

TX 1st mixer

(D1451: HSB88WS)

FM IF IC

(IC2001: TA3116FN)

RX 1st mixer circuit

RX 2nd mixer

(D1752: HSB88WS)

TX 2nd mixer

(D1852: HSB88WS)

Reference frequency oscillator

(X52: CR-338. 32.00056MHz)

RF-B unit

BPF-A board

PLL unit

1LO PLL IC

(IC381, IC681: LMX2306TM)

VCO-B circuit

VCO-A circuit

S2LO PLL IC

(IC901: LC7153M)

1LO DDS IC

(IC101, IC401: SC-1246A)

3LO/S3LO DDS IC

(IC701, IC801: SC-1287)

MAIN-A unit

Noise blanker circuit

LCD contorller

(IC3551: S1D13504F00A000)

MAIN CPU

(IC3501: HD64F2375F20)

TX 3rd mixer

(IC221: NJM1496V)

RX 3rd mixer

(IC151: TC4W53FU)

DSP-A board

PREAMP board

TX 1st mixer

(D1451: HSB88WS)

FM IF IC

(IC2001: TA3116FN)

RX 1st mixer circuit

RX 2nd mixer

(D1752: HSB88WS)

TX 2nd mixer

(D1852: HSB88WS)

Page 9

SECTION 3 CIRCUIT DESCRIPTION

•

3-1 RECEIVER CIRCUIT

3-1-1 RF SWITCHING CIRCUIT

(CTRL-A AND RF-B UNITS)

The RF switching circuit leads receive signals to bandpass

fi lters from an antenna connector while receiving. However,

the circuit leads the signal from the RF power amplifier to

the antenna connector while transmitting.

RF signals from [ANT 1] or [ANT 2] pass through the antenna selector (RL3), transmit/receive switching relays (RL1,

RL2, RL4), and low-pass fi lter (L27, L28, C63–C66, C105),

and are then applied to the RF-B unit via J101 (RF-B unit).

The signals from the CTRL-A unit either bypass or pass

through the 6 dB (RF-B unit, R102, R106, R111, RL102)

and/or 12 dB (RF-B unit, R112, R113, R114, RL103)

attenuators via the antenna selector (RL101). By selecting

the attenuators, 0 (bypass), 6, 12 and 18 dB attenuations

are obtained. The signals are then applied to the RF fi lters.

When the [RX ANT] is selected, the RF signals are passed

through the low-pass filter (RF-B unit, L101, L102, C101

–C105), then applied to the antenna selector (RF-B unit,

RL101).

3-1-2 RF BANDPASS FILTER CIRCUIT

(RF-B UNIT AND BPF-A BOARD)

RF bandpass fi lters pass only the desired band signals and

suppress any undesired band signals. The RF circuit has 11

bandpass fi lters and 1 low-pass fi lter.

• Used RF fi lter

Band

0.03–1.6 MHz B0 D801 11–15 MHz B7 D551

1.6–2 MHz B1 *D3201 15–22 MHz B8 D602

2–3 MHz B2 *D3301 22–30 MHz B9 D651

3–4 MHz B3 *D3401 30–50 MHz B10W D701

4–6 MHz B4 *D3501 50–54 MHz B10 D751

6–8 MHz B5 *D3601 54–60 MHz B10W D701

8–11 MHz B6 D501

*: On the BPF-A board

Control

signal

Input

diode

Band

Control

signal

Input

diode

3-1-3 PRE-AMPLIFIER CIRCUITS (PRIAMP BOARD)

The IC-756PROIII has 2 gain levels of pre-amplifi er circuits.

One has 10 dB gain for the 1.8–21 MHz bands and the other

one has 16 dB gain for the upper 24 MHz bands.

When the [P.AMP] switch is set to [P.AMP 1] or [P.AMP

2], the signals are applied to the pre-amplifier 1 (Q4201,

Q4202) or pre-amplifi er 2 (Q4302) circuit, respectively. Preamplifi ed or bypassed signals are applied to the RF amplifi er

circuits (RF-B unit; Q1001, Q1002 or Q1201, Q1202).

3-1-4 RF AMPLIFIER AND 1ST MIXER CIRCUITS

(RF-B UNIT)

The 1st mixer circuit mixes the receive signals with the 1st

LO signal to convert the receive signal frequencies into a

64.455 MHz 1st IF signal. The IC-756PROIII has two 1st

mixer circuits for the dualwatch function.

(1) 0.03–1.6 MHz (RF-B UNIT)

The signals pass through the low-pass filter (L801–L802,

C802, C805–C807), attenuator (R801–R803), and are then

applied to the RF amplifi ers (Q1001, Q1002).

The signals from the pre-amplifier circuit, or signals which

bypass the pre-amplifi ers, are divided at L902, L903. Each

signal is applied to a 60 MHz cut-off low-pass fi lter, RF amplifi er (Q1001, Q1002 for sub readout or Q1201, Q1202 for

main readout) and then to a 1st mixer (Q1003–Q1006 sub

(2) 1.6–60 MHz (RF-B UNIT AND BPF-A BOARD)

The signals pass through the band switch (D104) and high-

readout or Q1203–Q1206 for main readout) to convert the

frequency into the 64.455 MHz 1st IF signal.

pass filter (L251–L253, C251, C252, C271–C274) to suppress excessively strong signals below 1.6 MHz. The fi ltered

signals are applied to one of 11 bandpass fi lters on the table

at right above, and then applied to or bypassed the preamplifi er circuit.

Each 1st LO signal (64.4850–124.4550 MHz) from the PLL

unit via J1101 or J1301. The LO signals are amplifi ed at the

LO amplifi er (Q1101; sub or Q1301; main), fi ltered by a lowpass fi lter, and then applied to each 1st mixer.

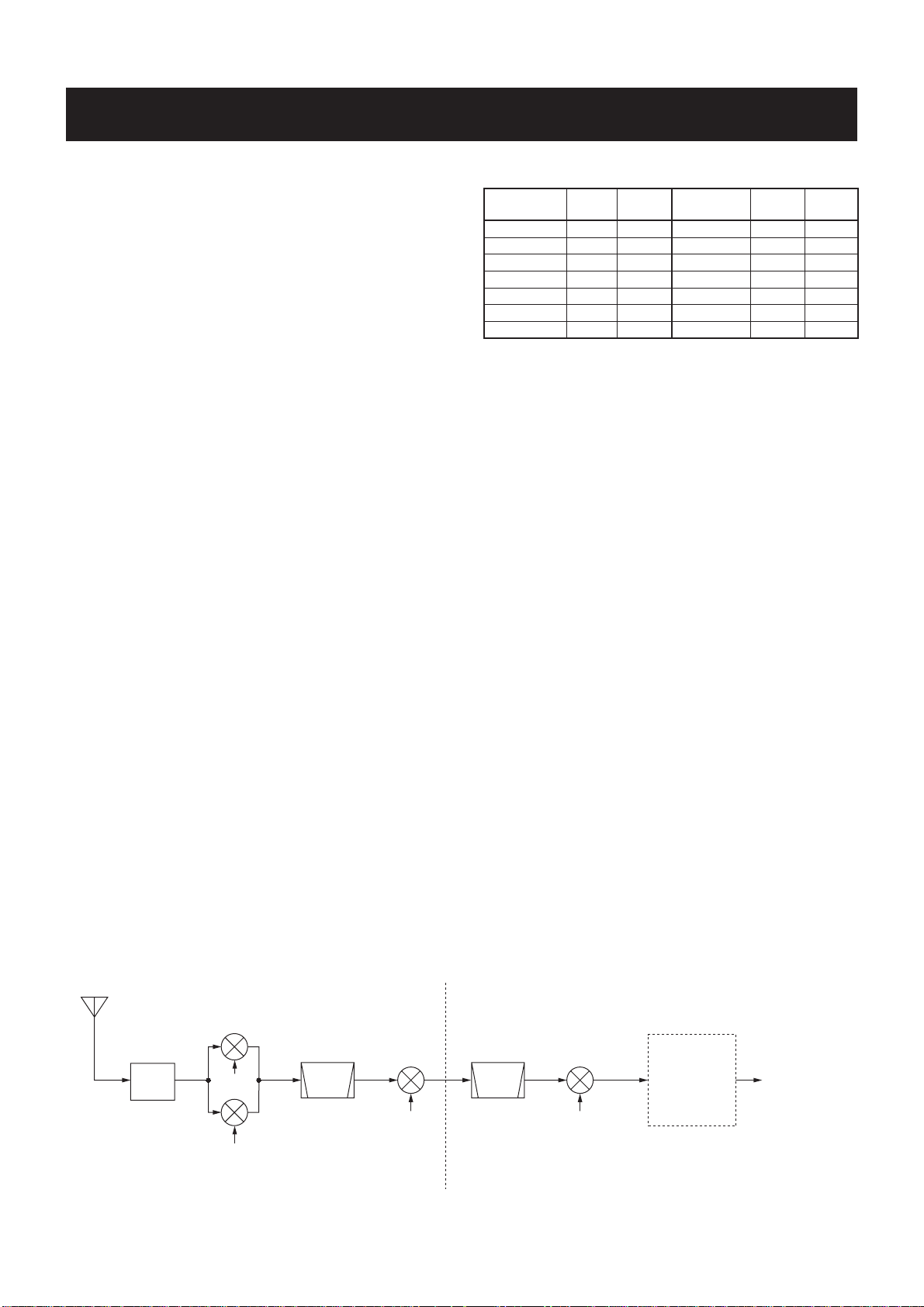

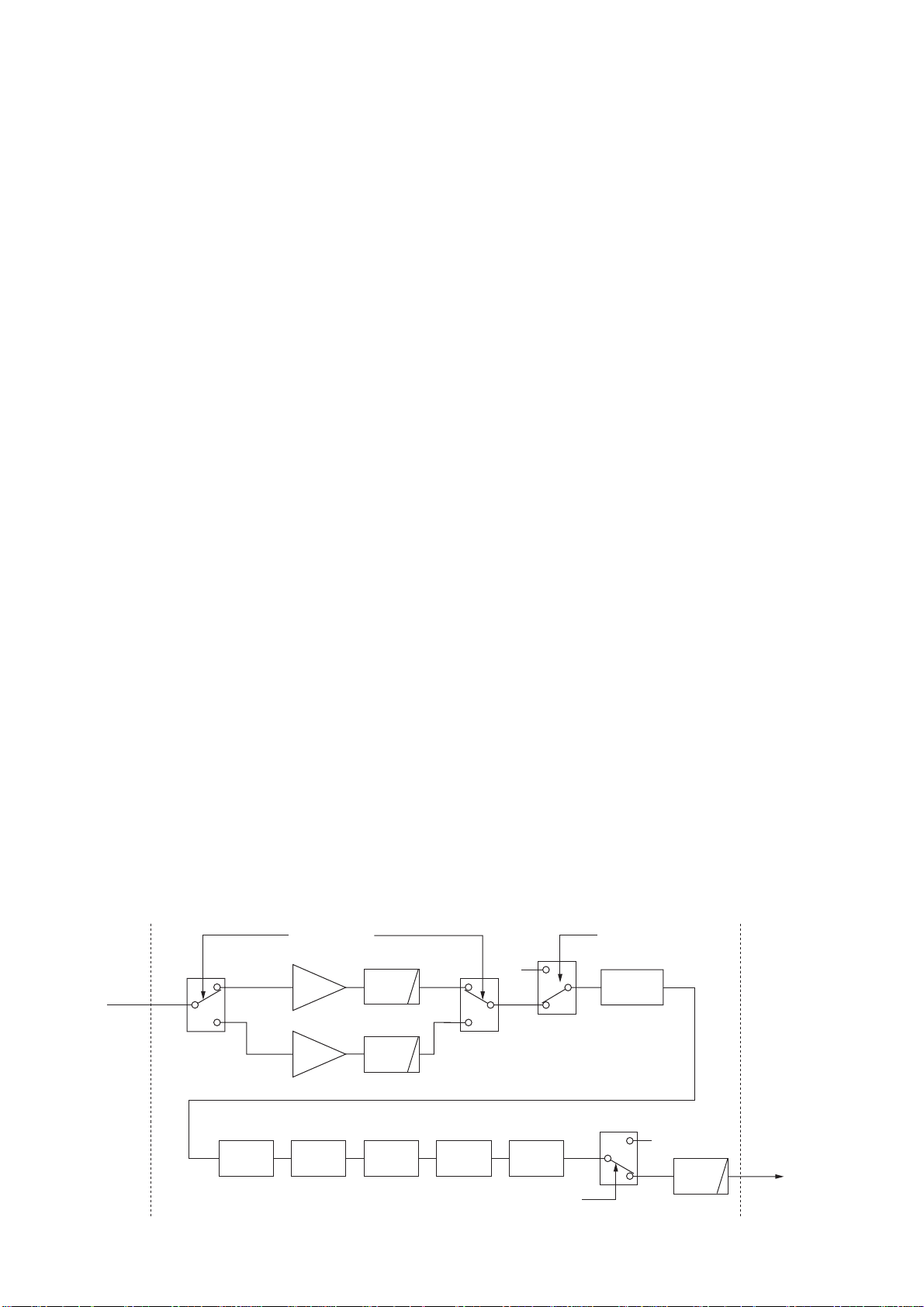

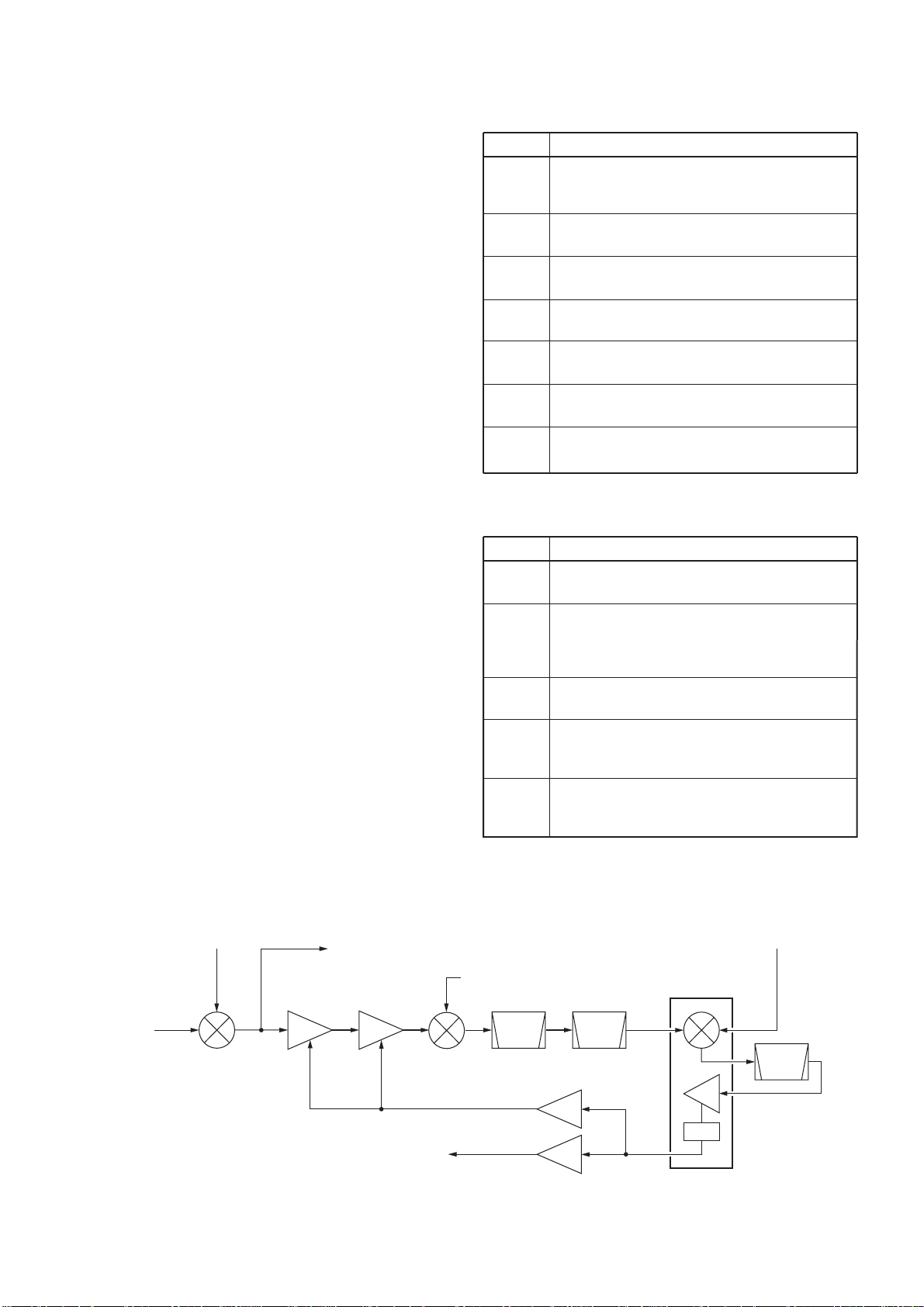

Receiver construction

1st mixer B

Q1003–Q1006

FI1701

LPF or

BPF

0.03–60.0 MHz

1st LO B

1st mixer A

Q1203–Q1206

1st LO A

Crystal

filter

64.455 MHz

2nd mixer

D1752

2nd LO

64.0 MHz

RF-B UNIT MAIN-A UNIT

FI111

Ceramic

filter

455 kHz

3rd mixer

IC151

3rd LO

491 kHz

36 kHz

DSP-A

board

to squelch gate

(IC301)

3 - 1

Page 10

3-1-5 1ST IF CIRCUIT (RF-B UNIT)

The 1st IF circuit filters and amplifies the 1st IF signal. The

1st IF signal combined at L1018 and is then applied to a

MCF (Monolithic Crystal Filter; FI1701) to suppress out-ofband signals.

The 1st IF signal level is adjusted at the PIN attenuators

(D1001, D1003, D1004; sub or D1201, D1203, D1204 for

main) controlled by the [BAL] controller for the dualwatch

function. The signal is applied to the 1st IF amplifier (Q1008;

sub or Q1208; main) and then combined at L1018.

The combined signal is pass through the MCFs (FI1701)

and is then applied to the 1st IF amplifier (Q1751). The

amplified signal is then applied to the 2nd mixer circuit.

Some DC voltage from the noise detector circuit is fed back

to the noise amplifiers (Q271, Q272) via the DC amplifiers

(Q274, Q275). The DC amplifiers function as an AGC circuit to reduce average noise. Therefore, the noise blanker

function shuts off pulse-type noise only.

3-1-8 2ND IF CIRCUIT (MAIN-A UNIT)

The 2nd IF circuit amplifies and filters the 2nd IF signal,

and applies the 2nd IF signal to the 3rd mixer circuit.

The 2nd IF signal from the noise blanker gate (D113,

D114) is amplified at the 2nd IF amplifier (Q141) and

passed through the ceramic filter (FI111). The filtered signal is applied to the 3rd mixer circuit.

3-1-6 2ND MIXER CIRCUIT (RF-B UNIT)

The 2nd mixer circuit mixes the 1st IF signal and 2nd LO

signal (64.00 MHz) for conversion into the 2nd IF signal.

The 1st IF signal from the 1st IF amplifier (Q1751) is converted into a 455 kHz 2nd IF signal at the 2nd mixer circuit

(D1752).

The 2nd IF signal is applied to the noise blanker gate

(MAIN-A unit) via the J1851.

3-1-7 NOISE BLANKER CIRCUIT (MAIN-A UNIT)

The noise blanker circuit detects pulse-type noise, and

turns OFF the signal line when the noise appears.

The 2nd IF signal from the RF-B unit is applied to the noise

blanker gate (D113, D114).

A portion of the 2nd IF signal is amplified at the noise

amplifiers (Q271–Q273, Q279), and is then detected at the

noise detector (D271) to convert the noise components to

DC voltages.

The signal is then applied to the noise blanker switch (Q276,

Q278). At the moment the detected voltage exceeds Q276’

s threshold level, Q278 outputs a blanking signal to close

the noise blanker gate (D113, D114). The PLL unlock signal are also applied to Q278, to control the noise blanker

gate.

3-1-9 3RD MIXER AND 3RD IF CIRCUITS

(MAIN-A UNIT)

The 3rd mixer circuit mixes the 2nd IF signal and the 3rd

LO signal to obtain the 3rd IF (36 kHz) signal.

The 2nd IF signal from the ceramic filter (FI111) is applied

to the 3rd mixer circuit (IC151, pin 1). The 3rd LO signal

from the PLL unit is applied to the 3rd mixer (IC151, pin 5).

The 3rd IF signal is output from pin 6.

The 3rd IF signal is passed through the low-pass filter

(IC201a) and amplified at the 3rd IF amplifier (IC201b). The

amplified signal is then applied to the DSP-A board via

J201 (pin 27) as DRIF signal.

3-1-10 DSP RECEIVER CIRCUIT (DSP-A BOARD)

The DSP (Digital Signal Processor) circuit enables digital

IF filter, digital noise reduction, digital PSN (Phase Shift

Network)/Low Power/Phase demodulation, digital automatic

notch, and etc.

The 36 kHz 3rd IF signal from the 3rd IF amplifier (MAIN-A

unit, IC201b) is amplified at the differential amplifiers

(IC2301a/b) after being passed through the T/R switch

(IC2291), and is then applied to the A/D converter (IC2321).

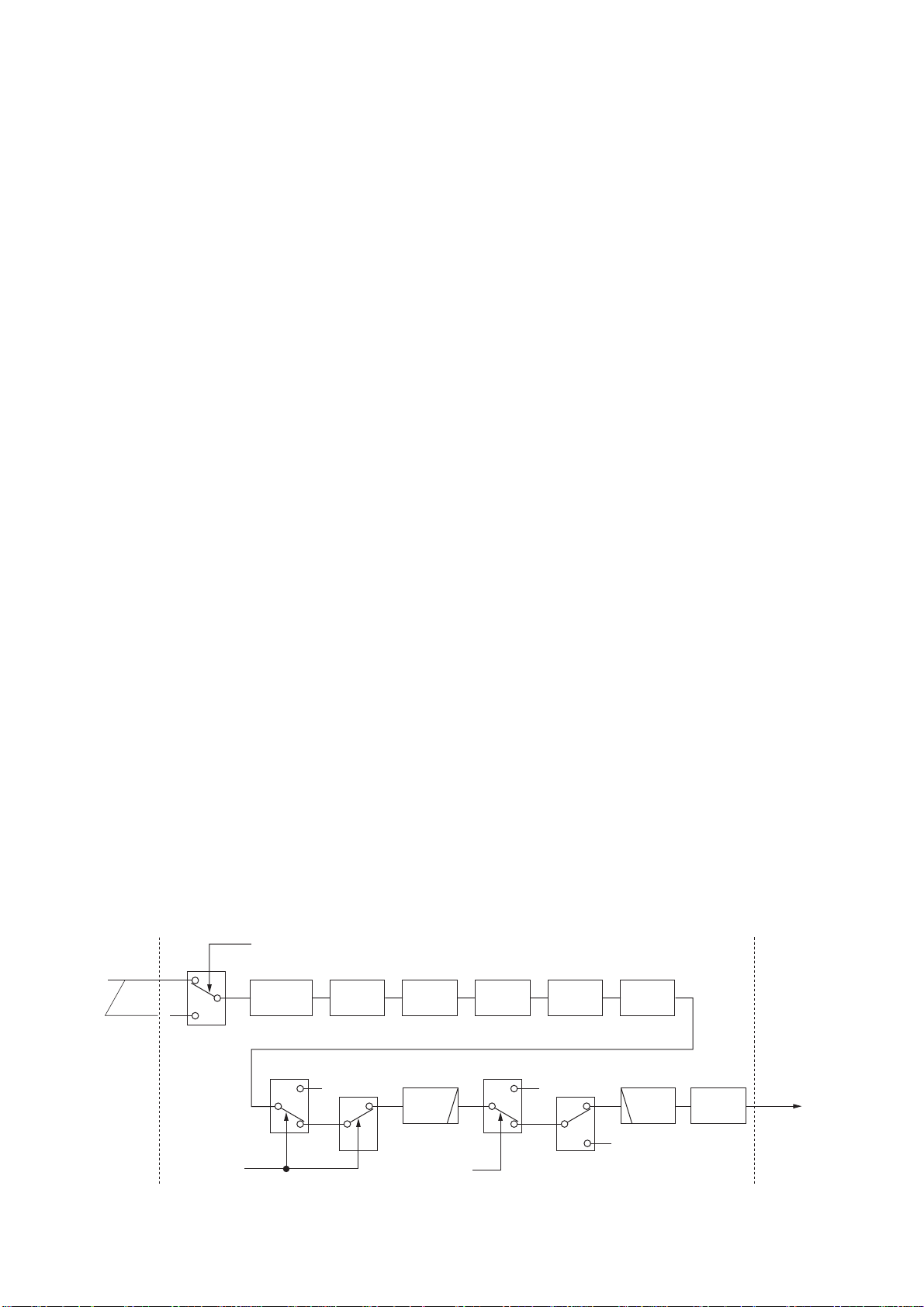

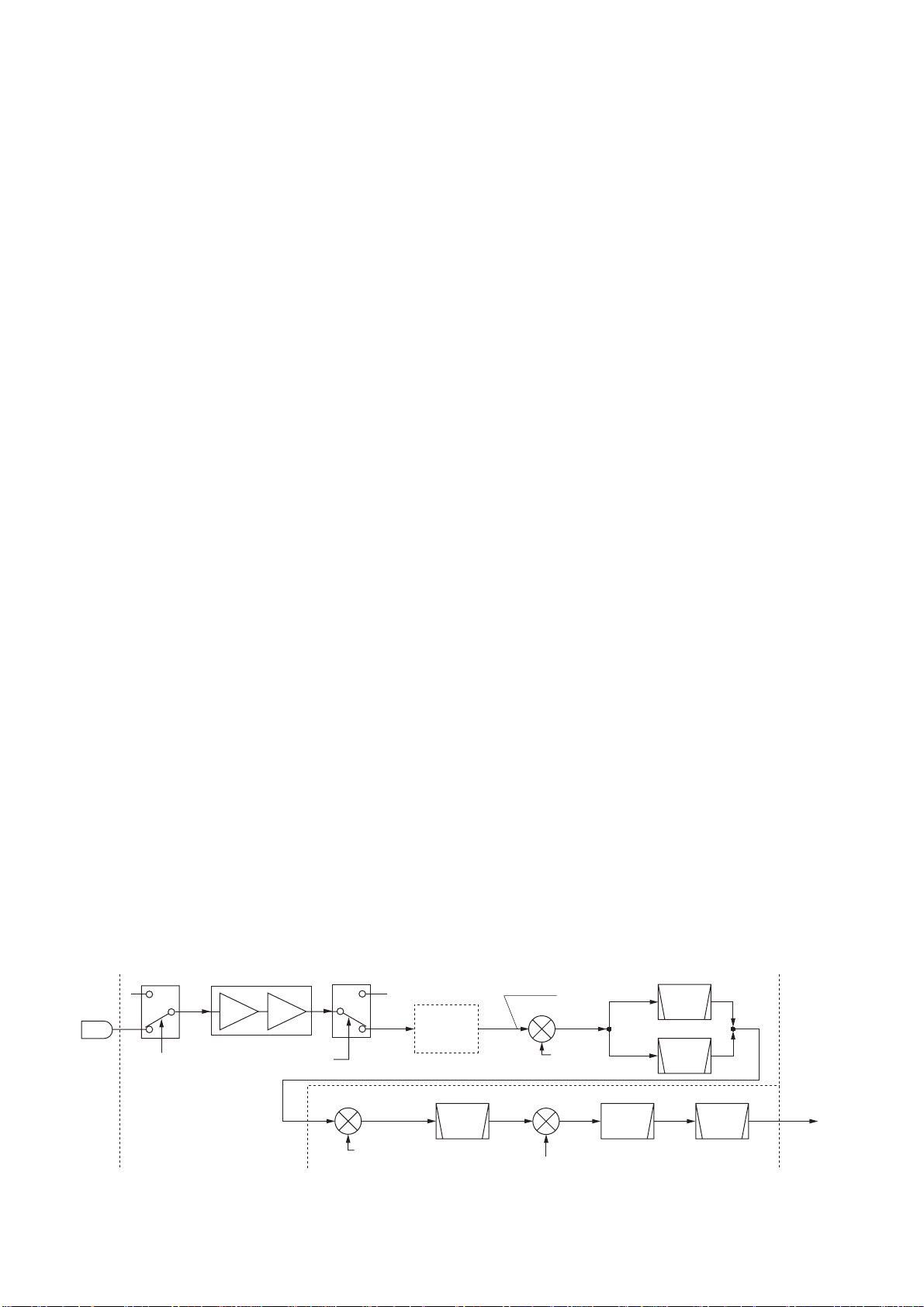

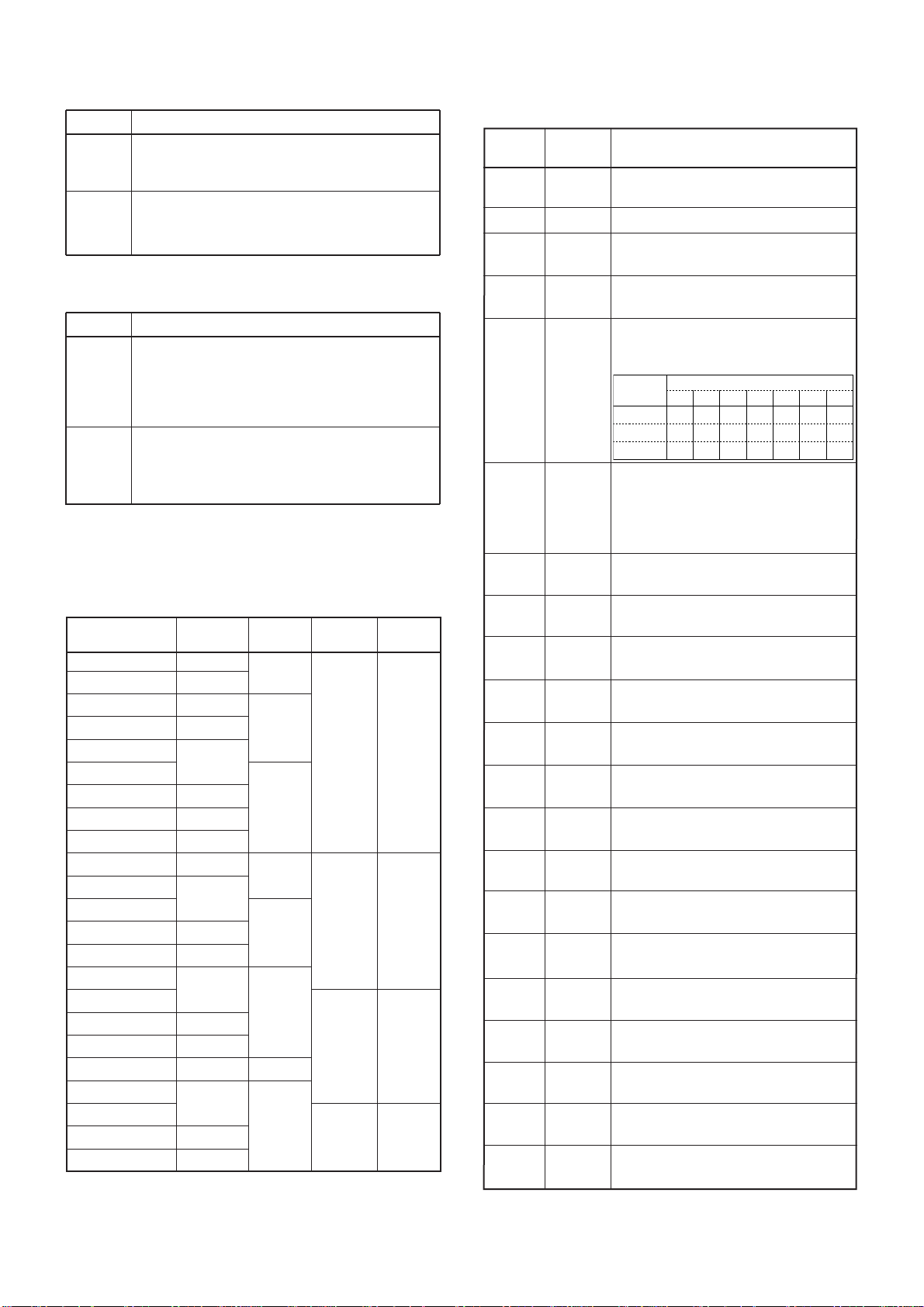

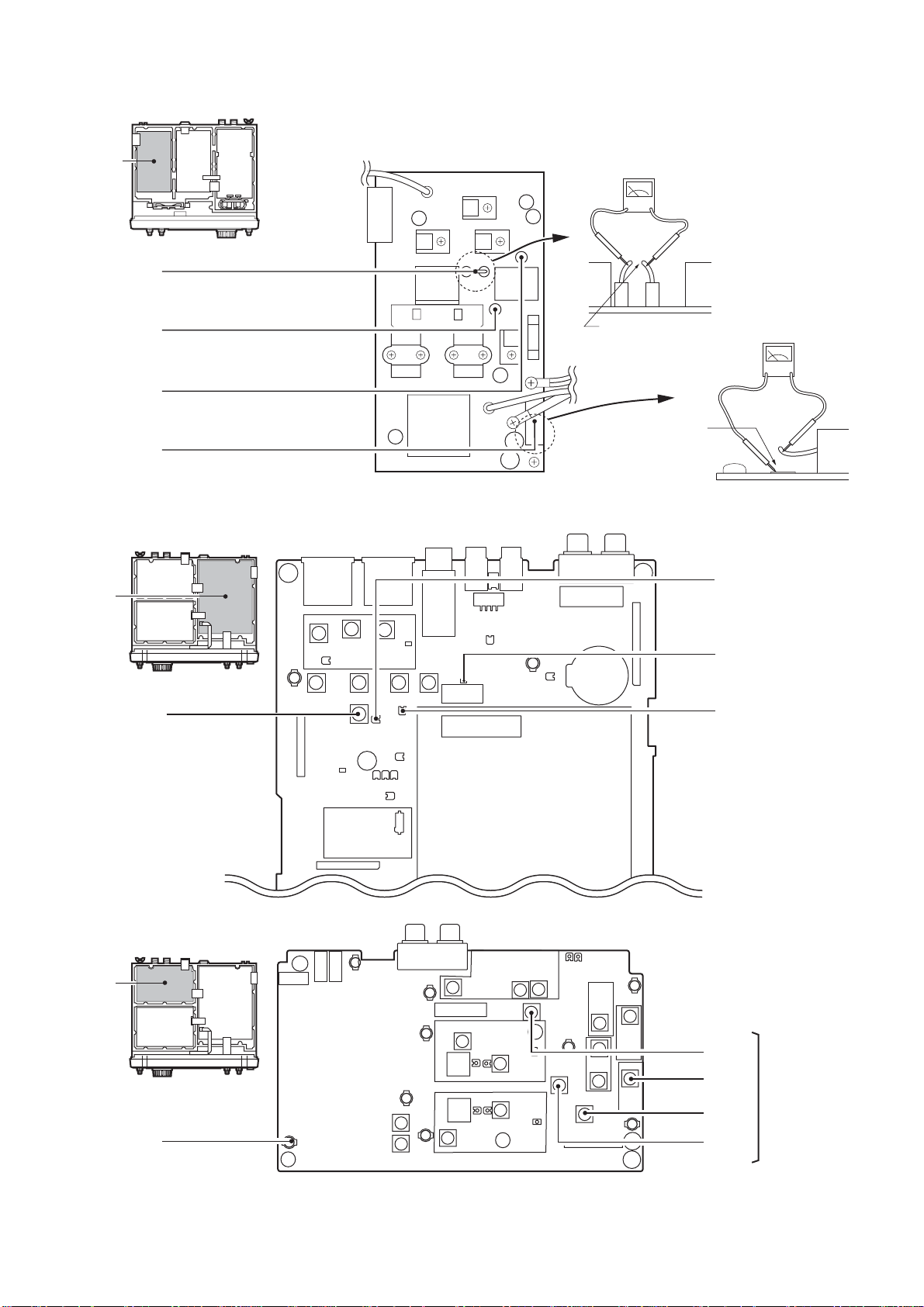

• DSP receiver circuit

“TXS” signal

3rd IF

signal

36 kHz

MAIN-A unit DSP-A board MAIN-A unit

DRIF

IC2291

5

6

7

T/R switch

“TXS” signal

IC2301b/a IC2321

Differential

1

converter

IC2372x

13

14

12

11

A/D

converter

IC2372y

1

10

IC2051

converter

IC2401

15

“TXS” signal

Level

LPF

IC2001

DSP IC

IC2372z

4

9

5

3

IC2052

Level

converter

IC2473

1

7

4

IC2351

D/A

converter

IC2441a

HPF

IC2471a

Mixer

amplifier

DRAF

3 - 2

AF

signals

Page 11

The converted signal is changed from a 5 V level signal to

a 3.3 V signal in the level converter (IC2051), and is then

applied to the DSP IC (IC2001) for 36 kHz digital IF filter,

demodulation, automatic notch and noise reduction, etc.

The output signal from the DSP IC (IC2001) is changed

from a 3.3 V level signal to a 5 V level signal in the level

converter (IC2502), and is applied to the D/A converter

(IC2351) to convert into the analog audio signals.

The converted audio signals are passed through the active

filter (IC2371a), AF amplifier (IC2371b), analog switches

(IC2372, pins 13, 14 and pins 1, 15) then applied to the

low-pass filter (IC2401, pins 5, 11). The filtered signals are

passed through the analog switches (IC2372, pins 3, 4 and

IC2473, pins 1, 7), high-pass filter (IC2441A) and mixer

amplifier (IC2471A), and then applied to the MAIN-A unit

via J2001 (pin 13) as the DRAF signal.

3-1-11 TWIN PBT CIRCUIT (DSP-A BOARD)

General PBT (Passband Tuning) circuit shifts the center frequency of IF signal to electronically narrow the passband

width. The IC-756PROIII uses the DSP circuit for the digital

PBT function and actually shifts the both lower and higher

passbands of 3rd IF filter within ±1.8 kHz.

The twin PBT circuit in DSP IC (IC2001) controlled by the

[TWIN PBT] controller adjusts the 3rd IF passband width

and rejects interference.

3-1-13 S-METER CIRCUIT (MAIN-A UNIT)

The S-meter circuit indicates the relative received signal

strength while receiving by utilizing the AGC voltage which

changes depending on the received signal strength.

A portion of the AGC bias voltage from the DSP-A board

is applied to the differential amplifier (IC101a, pin 2) where

the difference between the AGC and reference voltage is

detected.

The detected voltage is passed through the analog switch

(IC3631, pins 12, 14) as the SML signal and applied to the

main CPU (IC3501, pin 108) to activate the S/RF meter via

the sub CPU (DISPLAY board, IC401).

3-1-14 SQUELCH CIRCUIT (MAIN-A UNIT)

The squelch circuit mutes audio output when the S-meter

signal is lower than the [RF/SQL] setting level.

The S-meter signal is applied to the main CPU (IC3501, pin

108) and is compared with the threshold level set by the

[RF/SQL] control. The [RF/SQL] setting signal is applied to

the main CPU via the sub CPU (DISPLAY board; IC401,

pin 91). The main CPU analyzes the compared signal and

outputs control signal to the squelch gate (IC301, pin 5)

via the interface IC (IC3653, pin 19) to open or close the

squelch as the SQLS signal.

3-1-12 AGC CIRCUIT (DSP-A BOARD)

The AGC (Automatic Gain Control) circuit reduces IF amplifier gain and attenuates IF signal to keep the audio output

at a constant level.

The receiver gain is determined by the voltage on the

AGC line (IC2461, pin 4). The D/A converter (IC2461) for

AGC supplies control voltage to the AGC line and sets the

receiver gain with the [RF/SQL] control.

The 3rd IF signal from the level converter (IC2051) is

detected at the AGC detector section in DSP IC (IC2001),

and is applied to the D/A converter for AGC via the level

converter (IC2052). The AGC voltage is amplified at the

buffer amplifier (IC2471b), and is then applied to the

MAIN-A unit via J2001 (pin 16) to control the AGC line.

When receiving strong signals, the AGC voltage decreases

via the buffer amplifier (IC2471b). As the AGC voltage is

used for the bias voltage of the IF amplifier (RF-B unit;

Q1751), and IF amplifier gain is decreased.

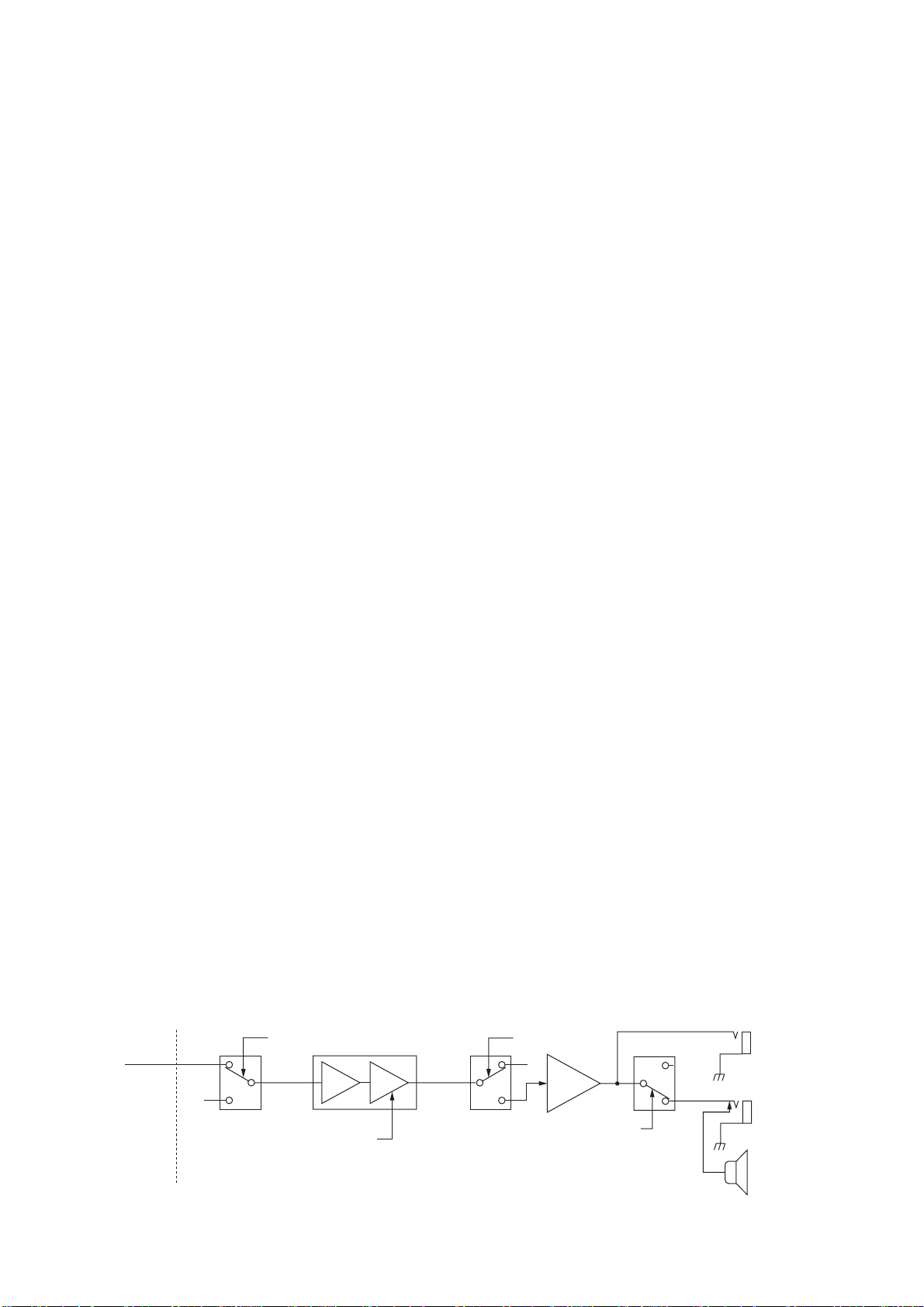

• AF amplifier circuit

DRAF

IC301 IC311

7

6

5

MAIN-A unitDSP-A board

“SQLS” signal

2

1

AMP VCA

“AFGV” signal

9

3-1-15 AF AMPLIFIER CIRCUIT (MAIN-A UNIT)

The AF amplifier amplifies the audio signals to a suitable

driving level for the speaker.

The AF signals (DRAF) from the DSP-A board are passed

through the squelch gate (IC301, pins 1, 7) and amplified

at the AF amplifier section of IC311 (pins 2, 4), and volume

is controlled by the AFGV signal at the VCA section (pins 7

–9). The volume controlled AF signals are passed through

the AF mute gate (IC331, pins 1, 7), then applied to the AF

power amplifier (IC332, pins 1, 4).

The amplified audio signals are passed through the SP

mute switch (RL351) and [EXT SP] jack then applied to the

internal speaker when no plug is connected to the jack.

The AF mute gate is controlled by the [AF] control via the

sub and main CPUs.

When headphones are connected, the SP mute signal from

the main CPU (IC3501, pin 56) is applied to the SP mute

switch (RL351) via the BUS driver (IC3654, pins 8, 13) as

the SPS signal.

IC331

1

Mute switchSquelch gate

“AFMS” signal

2

6

7

IC332

AF

power

amp.

“SPS” signal

RL351

[PHONES]

[EXT SP]

Int. speaker

3 - 3

Page 12

3-2 TRANSMITTER CIRCUITS

3-2-1 MICROPHONE AMPLIFIER CIRCUIT

(MAIN-A UNIT)

The microphone amplifier circuit amplifies microphone

audio signals to a level needed for the DSP circuit.

Audio signals from the [MIC] connector (MIC board; J1,

pin 1) are amplified at the audio amplifier section in IC451

(pins 21, 22) via the analog switch (IC3002, pins 12, 14),

then applied to the buffer amplifier section (IC451, pin 5)

and VCA section. The gain controlled signals are output

from (IC451, pin 9) and passed through the analog switch

(IC3005, pins 12, 14) and then applied to the DSP circuit

via J201 (pin 15) as the DTAF signal.

The VCA section in IC451 (pin 9) controls microphone

input gain according to the [MIC GAIN] control level using

the MIGV signal coming from the main CPU via the I/O

expander (IC3751, pin 4).

(1) When SSB mode

The audio signals from the analog switch (IC2201, pin 5)

are amplified at the limiter amplifier (IC2281b) and applied

to the low-pass filter (IC2281c/d) to limit the transmit

passband width.

The filtered signals are then applied to the differential

amplifiers (IC2301a/b) via the analog switch (IC2201, pins

12, 14) and T/R switch (IC2291, pins 1, 7).

(2) When FM/AM modes

The audio signals from the analog switch (IC2201, pin 3)

are applied to the modulation adjustment pots (R2227:

FM mode, R2229: AM mode) via the limiter amplifier, preemphasis circuit (only FM mode) and splatter filter consist

of IC2211. The level adjusted signals are applied to the differential amplifiers (IC2301a/b) after being passed through

the analog switch (IC2201, pins 1, 2, 13–15) and T/R

switch (IC2291 pins 1, 7). The pre-emphasis circuit is cancelled by Q2201, Q2202, Q2211 on AM mode.

3-2-2 VOX CIRCUIT (MAIN-A UNIT)

The VOX (Voice-Operated Transmission) circuit sets transmitting conditions according to voice input.

A portion of the audio signals from the VCA section (IC451,

pin 9) is applied to the AF amplifier (IC3004b, pins 6, 7),

and then applied to the main CPU (IC3501, pin 106) after

passing through the analog switch (IC362, pins 1, 6) as the

VOXL signal.

The VOGV signal is applied to the VCA section in IC3003

(pin 8) from the main CPU via the I/O expander (IC3751,

pin 9) to adjust VOX actionable sensitivity. This is controlled

by the VOX gain set in the VOX SET mode.

3-2-3 DSP TRANSMITTER CIRCUIT

(DSP-A BOARD)

The microphone audio signals from the MAIN-A unit via the

DTAF line are applied to the analog switch (IC2201, pin 4)

and output from pin 3 or 5 to the each modulation circuits.

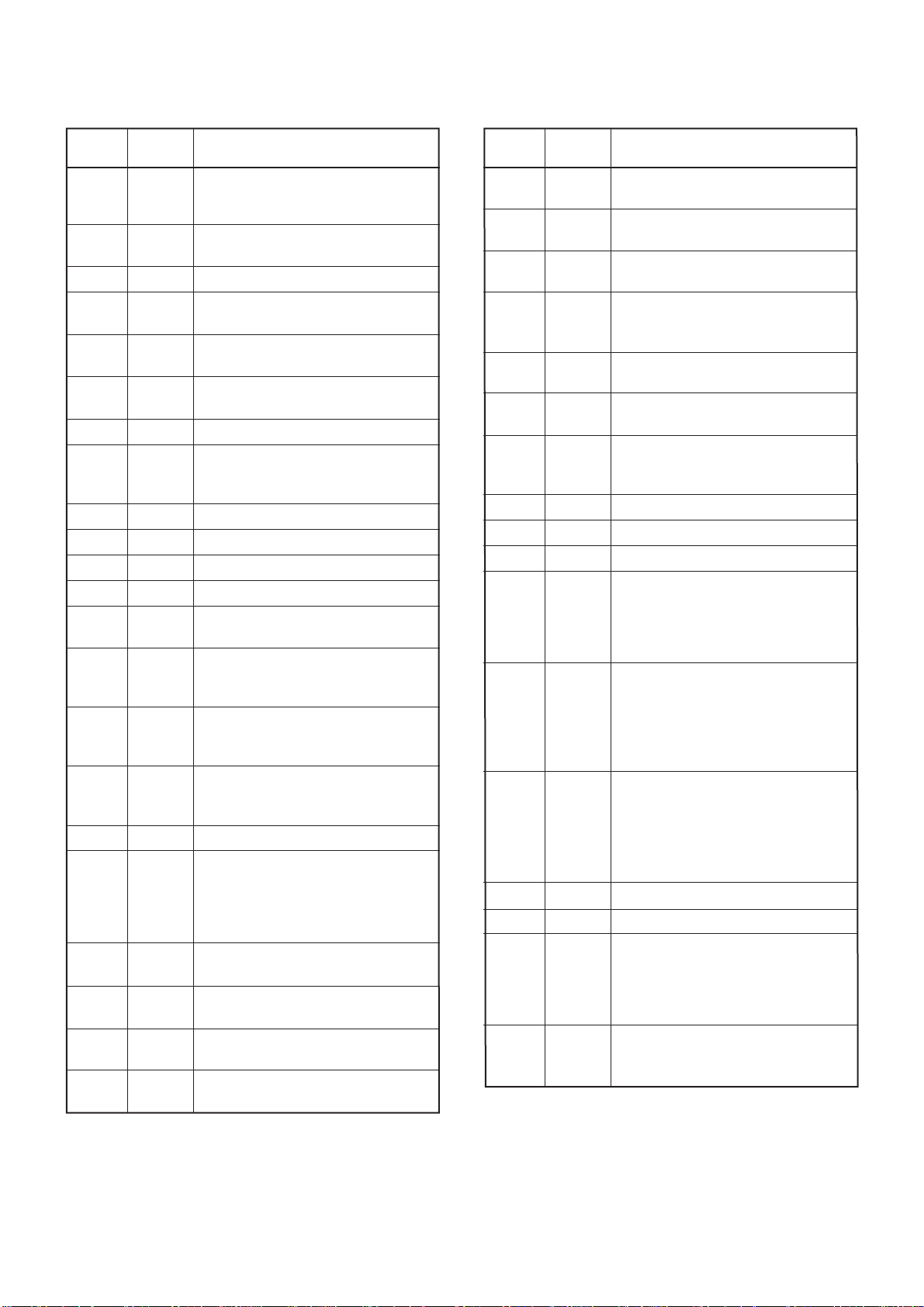

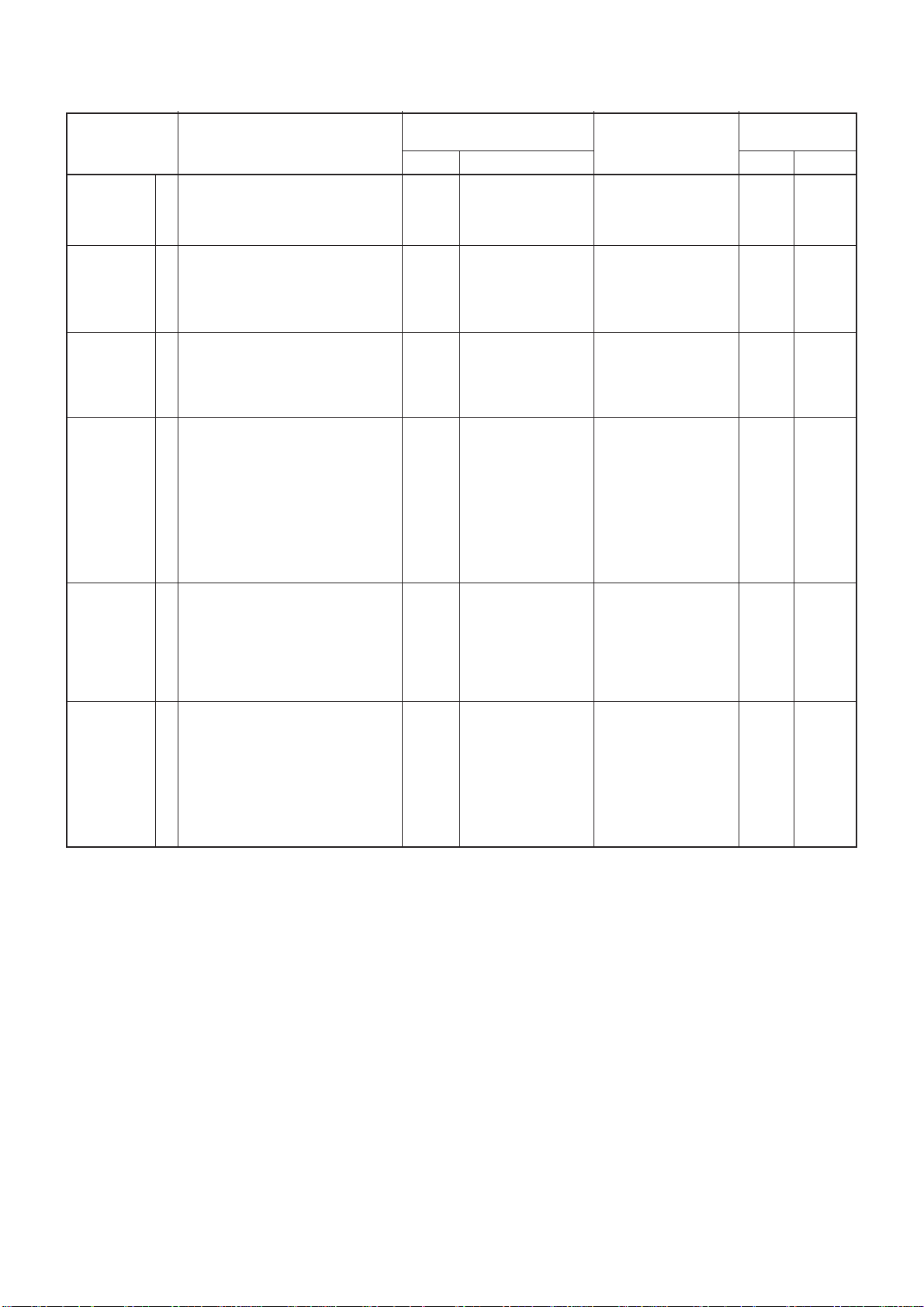

• DSP Transmitter circuit

The amplified signals at the differential amplifiers (IC2301a/

b) are applied to the A/D converter (IC2321 pins 4, 5). The

converted signals are changed from 5 V level signals to 3.3

V level signals in the level converter (IC2051).

The converted signals are applied to the DSP IC (IC2001)

and modulated at the DSP IC to produce the 36 kHz transmitter IF signal. The modulated IF signal from the DSP IC

is changed from a 3.3 V signal to a 5 V signal in the level

converter (IC2052), and is applied to the D/A converter

(IC2351) to convert into the analog IF signal.

The converted IF signal is passed through the active filter (IC2371a), buffer amplifier (IC2371b), analog switch

(IC2372, pins 12, 14) then applied to the low-pass filter

(IC2381c/d). The filtered signal is applied to the MAIN-A

unit via J2001 (pin 29) as the DTIF signal.

When SSB or RTTY mode, a portion of the filtered signal

from the low-pass filter (IC2381c/d) is amplified at the IF

and buffer amplifiers (IC2381a/b) and is applied to the

transmit monitor circuit for the monitor function.

IC2201z

AF

DTAF

signal

MAIN-A unit DSP-A board

9

4

Mode switch

SSB

5

mode

3

FM/AM

mode

IC2321

A/D

converter

“MODS” signal

Limitter

IC2211a

Limitter

IC2051

Level

converter

IC2281c/dIC2281b

LPF

IC2211b

LPF

IC2001

DSP IC

IC2201x

12

13

Mode switch

IC2052

Level

converter

3 - 4

11

14

converter

IC2291

5

6

7

T/R switch

IC2351

D/A

“TXS” signal

“TXS” signal

IC2301a/b

Differential

1

converter

IC2372x

14

11

13

12

IC2381d/c

LPF

DTIF

MAIN-A unit

36 kHz IF

Page 13

3-2-4 SPEECH COMPRESSOR CIRCUIT

(DSP-A BOARD)

The speech compressor compresses the transmitter audio

input signals to increase the average output level (average

talk power).

When the speech compressor function is ON, the level

shifted signal from the level converter (IC2051) is applied

to the DSP IC (IC2001) and compressed at the DSP IC to

obtain an average audio level.

At the same time, the compressed signals are modulated

at the DSP IC and applied to the level converter (IC2052).

3-2-5 IF AMPLIFIER AND MIXER CIRCUITS

(MAIN-A AND RF-B UNITS)

The modulated 3rd IF signal from the DSP-A board (DTIF:

36 kHz) is applied to the 3rd mixer circuit (MAIN-A unit;

IC221, pin 1). The applied 3rd IF signal is mixed with the

3rd LO signal from the DDS circuit (PLL unit; IC701) to produce a 455 kHz 2nd IF signal.

The 2nd IF signal is output from (MAIN-A; IC221, pin 6)

and amplified at the IF amplifier (MAIN-A unit; Q241). The

amplified signal is passed through the ceramic bandpass

filter (MAIN-A unit; FI131: FM/AM modes, FI133: other

modes) for unwanted signals are suppressed. The filtered

2nd IF signal is amplified at IF amplifier (MAIN-A unit;

Q261) and applied to the 2nd mixer circuit on the RF-B unit

via J101 (MAIN-A unit).

3-2-6 RF CIRCUIT (RF-B AND PA UNITS)

The RF circuit amplifies operating (transmitting) frequency

to obtain 100 W of RF output.

The signal from the 1st IF mixer (RF-B unit; D451) is

passed through the low-pass filter (RF-B unit; L1402,

L1403, C1405–C1409) and amplified at the RF amplifier

(RF-B unit; IC1401). The amplified signal is amplified again

at the wide-band YGR amplifier (RF-B unit, IC201) after

passing through one of 10 bandpass (Refer to page 3-1

for bandpass filters used) and high-pass filters, and is then

applied to the PA unit via J201 (RF-B unit).

The signal applied from the RF-B unit is amplified at the

pre-drive (Q1), drive (Q2, Q3) and power amplifiers (Q4,

Q5) in sequence to obtain a stable 100 W of RF output

power. The amplified signal is applied to one of 8 low-pass

filters in the FILTER-A unit.

3-2-7 LOW-PASS FILTER CIRCUIT (FILTER-A UNIT)

The low-pass filter circuit contains 8 Chebyschev low-pass

filters to suppress the higher harmonic components.

The amplified signal from the PA unit is applied to one of

8 low-pass filters, which is selected by the I/O expander

(CTRL-A unit, IC11) via the buffer amplifier (CTRL-A unit;

IC12).

The filtered signal is then applied to one of 2 antenna connectors via the CTRL-A unit.

The 2nd IF signal is mixed with the 64 MHz 2nd LO signal,

coming from the PLL unit, at the 2nd mixer circuit (RF-B

unit; D1852) to obtain a 64.455 MHz 1st IF signal. The 1st

IF signal is passed through a MCFs (RF-B unit; FI1701)

to cut-off the undesired signals then amplified at the IF

amplifier (RF-B unit; Q1551) via the T/R switch (RF-B unit;

D1551). The amplified 1st IF signal is applied to the 1st IF

mixer circuit (RF-B unit; D1451).

The operating (transmitting) frequency is produced at the

1st IF mixer circuit (RF-B unit; D1451) by mixing the 1st IF

and 1st LO signals. The mixed signal is then applied to the

RF circuit.

• Transmitter construction

IC3005x

14

11

12

DTAF

13

MIC

IC3002

13

12

“MISL” signal

14

11

AMP VCA

IC451

“MOSL” signal

DSP-A

board

3-2-8 ALC CIRCUIT (MAIN-A UNIT)

The ALC (Automatic Level Control) circuit controls the gain

of IF amplifiers in order for the transceiver to output a constant RF power set by the [RF POWER] control even when

the supplied voltage shifts, and etc.

The RF power level is detected at one of the APC detector

circuits (CTRL-A unit; D2) to be converted into DC voltage

and applied to the MAIN-A unit as the FORV signal.

The FORV signal from the CTRL-A unit is applied to the

comparator (IC551b, pins 6, 7). The POCV signal, controlled by the [RF POWER] control via the I/O expander

(IC3751, pin 5), is also applied to the other input (IC551b,

pin 5) for reference. The compared signal is output from

pin 7 and applied to the IF amplifiers in the MAIN-A (Q261)

and RF-B (Q1551) units to control amplifying gain.

FI131

Ceramic

filter

FI133

Ceramic

filter

DTIF

36 kHz IF

IC221

455 kHz

3rd LO

(491 kHz)

FM/AM

modes

other

modes

MAIN-A UNIT

D1852

64.455 kHz

2nd LO

(64.00 MHz)

FI1701

Crystal

filter

3 - 5

D1451

1st LO

(64.485–

124.455 MHz)

LPF

RF-B UNIT

BPFs

PAIN

PA UNIT

Page 14

When the FORV signal exceeds the POCV voltage, ALC

bias voltage from the comparator (IC551b) controls the IF

amplifiers (Q261). This adjusts the output power to a specified level from the [RF POWER] control until the FORV and

POCV voltages are equalized.

The thermistor (R50) detects the temperature of the final

amplifier (Q5), and activates Q11 and Q13 to accelerate

the cooling fan when the detected temperature exceeds

70˚C (158˚F). The cooling fan rotates at high speed at 80˚C

(176˚F) or more.

In AM mode, the comparator operates as an averaging ALC

amplifier. Q502 turns ON and the POCV voltage is shifted

for 40 W AM output power (maximum) through R510.

The ALC bias voltage is also applied to the ALC meter

amplifier (IC551a, pins 1, 2) to obtain an ALC meter signal

(ALCL). The amplified signal is passed through the analog

switch (IC 3631, pins 13, 14) and applied to the main CPU

(IC3501, pin 108) to drive the S/RF meter via the sub CPU

(IC401) on the DISPLAY board.

An external ALC input from the [ALC] jack or [ACC] sockets is applied to the buffer amplifier (Q521). External ALC

operation is identical to that of the internal ALC.

The FORV signal is also applied to the power meter amplifier (IC571a, pins 1, 3). The amplified signal is passed

through the analog switch (IC3631, pins 1, 15) as an FORL

signal and applied to the main CPU (IC3501, pin 109) to

drive the S/RF meter when the power meter is selected.

3-2-9 APC CIRCUIT (MAIN-A UNIT)

The APC (Automatic Power Control) circuit protects the

power amplifiers on the PA unit from high SWR and excessive current.

The reflected wave signal appears and increases when the

connected antenna is mismatched to 50 Ω. The APC detector circuit (CTRL-A unit; D1 and L1) detects the reflected

signal, and applies it to the APC circuit (IC551c, pins 9, 8)

as REFV signal.

When the REFV signal level increases, the APC circuit

decreases the ALC voltage to activate the APC.

The thermistor keeps the cooling fan rotating even while

receiving until the Q5 temperature drops to 60˚C (140˚F) or

below.

3-2-11 MONITOR CIRCUIT

(DSP-A BOARD AND MAIN-A UNIT)

The microphone audio signals can be monitored to check

voice characteristics.

(1) When FM/AM modes (MAIN-A UNIT)

A portion of the microphone audio signals from the VCA

section (IC451; pins 9, 22) are applied to the analog switch

(IC361; pins 1, 7). The selected audio signals are applied to

IC371 (pin 2), and the output signals from pin 9 are applied

to the AF amplifier circuit (IC311, pin 2, 9).

(2) When SSB/RTTY modes

A portion of the transmit IF signal from the low-pass filter

(IC2381c/d) is amplified at the IF (IC2381b) and buffer

(IC2381a) amplifiers, and applied to the digital mixer circuit

(IC2302). The applied signal is mixed with a 36 kHz LO signal from the D/A converter (IC2342) to demodulate into the

AF signals. The demodulated signals are passed through

the buffer amplifier (IC2381a), low-pass filter (IC2441b/

c) and AF amplifier (IC2441d), and then applied to the

MAIN-A unit via J2001 (pin 19) as the DMAF signal.

The DMAF signal from the DSP-A board is amplified at the

ALC amplifier (MAIN-A unit; IC372, pins 1, 13) and applied

to the VCA section of IC371 (MAIN-A unit; pins 7, 9). The

volume controlled AF signals is applied to the AF amplifier

circuit (MAIN-A unit; IC311, pins 2, 9).

(DSP-A BOARD)

For the current APC, the power transistor current is

obtained by detecting the voltages (ICH and ICL) which

appear at both terminals of the current detector (PA unit;

R28). The detected voltages are applied to the differential

amplifier (IC551d, pins 12–14). When the current of transistors is increased, the amplifier controls the ALC line to prevent excessive current flow.

A portion of the REFV signal is applied to the SWR meter

amplifier (IC571b, pins 5, 7). The amplified signal is passed

through the analog switch (IC3631, pins 3, 4) as an REFL

signal and applied to the main CPU (IC3501, pin 110) to

drive the S/RF meter when the SWR meter is selected.

3-2-10 TEMPERATURE PROTECTION CIRCUIT

(PA UNIT)

The cooling fan (CHASSIS; MF1) is activated while transmitting or when the temperature of the power amplifier

exceeds the preset value. The temperature protection circuit consists of Q10–Q13 and R50.

While transmitting, Q10 and Q12 are turned ON, and provide a voltage to the cooling fan to rotate at medium speed.

3-3 PLL CIRCUITS

3-3-1 GENERAL

The PLL unit generates a pair of 1st LO frequencies (64.485

–124.455 MHz) for dualwatch and spectrum scope functions; a 2nd LO frequency (64 MHz), 3rd LO frequency

(491 kHz) and sweep LO frequency for the spectrum scope

function.

The 1st LO PLLs adopt a mixer-less dual loop PLL system and has 4 VCO circuits. The LOs, except the 2nd, use

DDSs while the 2nd LO uses the fixed frequency of the

crystal oscillator.

3-3-2 1ST LO PLL CIRCUIT

The 1st LO PLLs contain a main and reference loop as a

dual loop system. Both PLLs have equivalent circuits— this

manual describes only the 1st LO PLL A circuit.

The reference loop generates a 10.747 to 10.865 MHz frequency using a DDS circuit, and the main loop generates a

64.485 to 124.455 MHz frequency using the reference loop

frequency.

3 - 6

Page 15

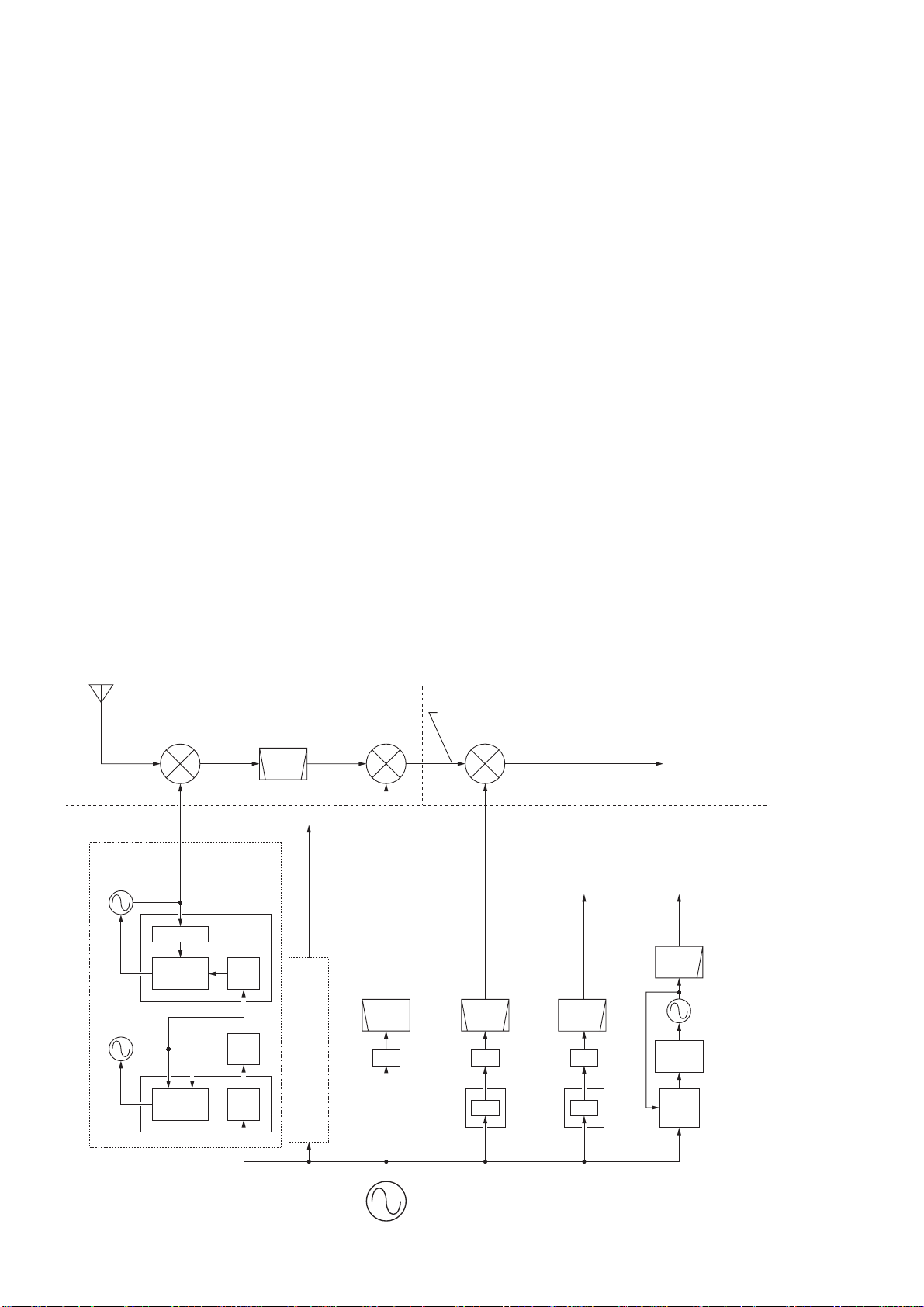

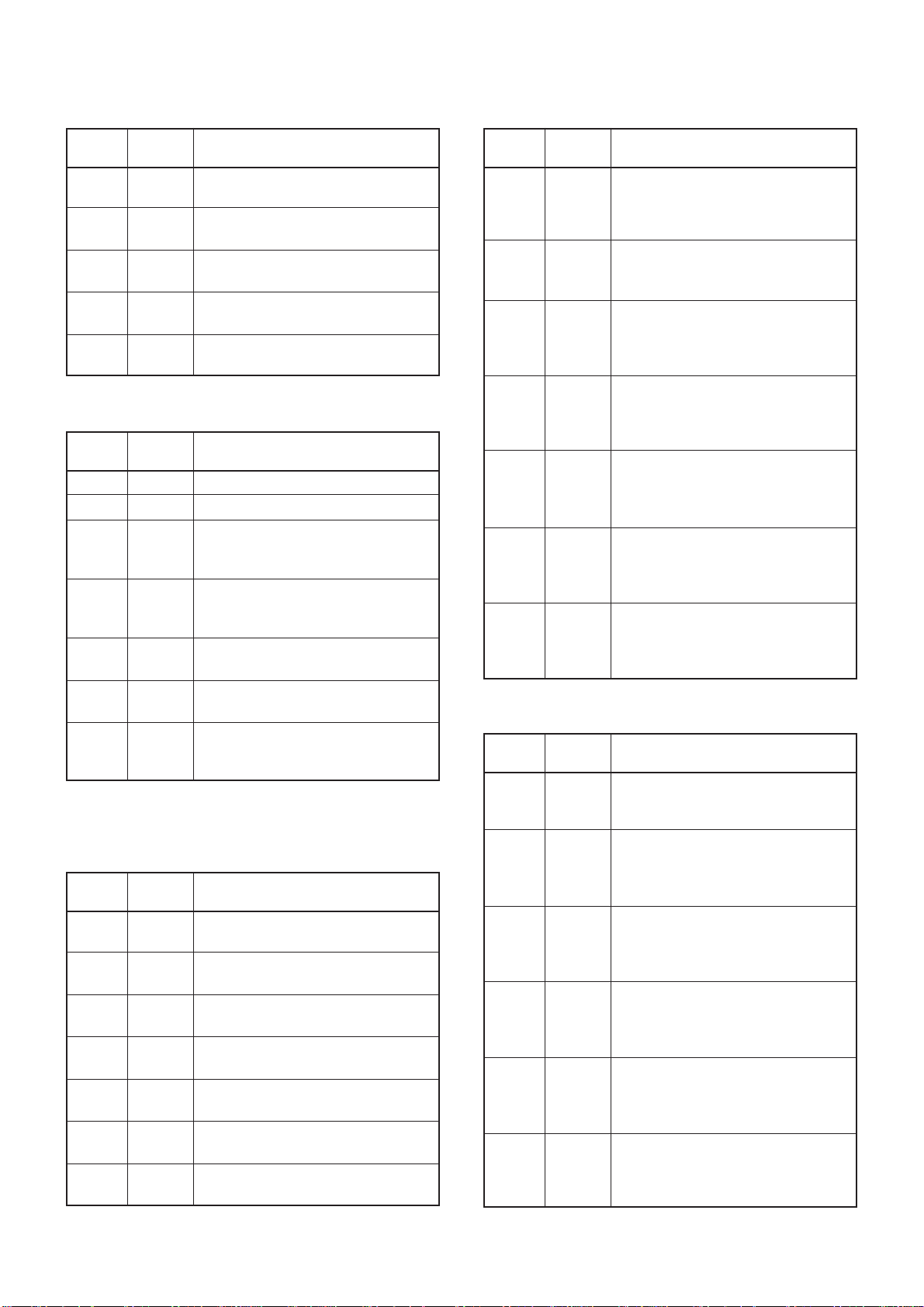

(1) REFERENCE LOOP PLL

• PLL CIRCUIT

64.485–

124.455 MHz

0.03–

60.0 MHz

455 kHz

36 kHz

10.747–

10.865 MHz

64.485–

124.455 MHz

64.0 MHz

77.8 MHz

ANT

1st mixer A

Q1203–Q1206

491 kHz

to scope circuit

(RF-B unit, D2101)

to scope circuit

(RF-B unit, IC2001)

IC801IC701

IC101

IC381

IC901

Q71

Q81

Q902

S2LOS3LO

3LO

X2

2LO

1LOB

1LOA

77.8 MHz

RF-B unit

PLL unit

MAIN-A unit

Q201

Q221

Q251

Q271

Q151

1st LO PLL A

circuit

Phase

detector

1/N divider

1/22

Phase

detector

12 bit

D/A

Main loop PLL

Ref. loop PLL

DDS

1st mixer B

1st LO

PLL B

circuit

DDS

D/A

DDS

D/A

PLL

IC

Crystal

filter

2nd mixer

D1752

3rd mixer

IC151

FI1701

64.455 MHz

to DSP-A board

Reference oscillator

X52: 32.0 MHz

BPFBPF

Loop

filter

LPF

LPF

The oscillated signal at the reference VCO (Q151, D151) is

amplified at the buffer amplifiers (Q102, Q152) and is then

applied to the DDS IC (IC101, pin 46). The signal is then

divided and detected on phase with the DDS generated

frequency.

The detected signal output from the DDS IC (IC101, pin

56) is converted into DC voltage (lock voltage) at the loop

filter (R135–R137, C121, C151) and then fed back to the

reference VCO circuit (Q151, D151).

(2) MAIN LOOP PLL

The oscillated signal at one of the main loop VCOs (Q201,

D201, D202), (Q221, D221, D222), (Q251, D251–D254)

and (Q271, D271–D274) is amplified at the buffer amplifiers (Q301, IC320) and is then applied to the PLL IC (IC381,

pin 6) via the low-pass filter (L303, C304–C307). The signal

is then divided and detected on phase with the reference

loop output frequency.

The detected signal output from the PLL IC (IC381; pin 2)

is converted into a DC voltage (lock voltage) at the loop

filter and then fed back to one of the VCO circuits (Q201,

D201, D202), (Q221, D221, D222), (Q251, D251–D254)

and (Q271, D271–D274).

The oscillated signal is amplified at the buffer amplifiers

(Q301, IC320) and then applied to the RF-B unit as a 1st

LO A signal after being passed through the low-pass filters

(L303, C304–C307 and L351–L353, C351–C356) and highpass filter (L354, C358–C360) and mute circuit (D361).

3-3-3 2ND LO AND REFERENCE OSCILLATOR

CIRCUITS

The reference oscillator (X52, Q51) generates a 32.0 MHz

frequency for the 4 DDS circuits as a system clock and

for the LO output. The oscillated signal is doubled at the

doubler circuit (Q71, Q81) and the 64.0 MHz frequency is

picked up at the double tuned filter (L81, L82). The 64.0

MHz signal is applied to the RF-B unit as a 2nd LO signal.

3-3-4 3RD LO CIRCUIT

The DDS IC (IC701) generates a 10-bit digital signal using

the 32 MHz system clock. The digital signal is converted

into an analog wave signal at the D/A converter (R701–

R720). The converted analog wave is passed through the

bandpass filter (L702, L703, C709–C713) and then applied

to the MAIN-A unit as the 3rd LO signal.

3-3-5 MARKER CIRCUIT

The divided signal at the DDS circuit (IC101) is used for

the marker signals with the IC-756PROIII.

The reference signal for the DDS circuit (32.0 MHz) is

divided to produce an acceptable frequency signal, 16

MHz, with the programmable divider then divided again by

160 to obtain 100 kHz cycle square-wave signals.

The generated marker signals are output from pin 66 of the

DDS IC (IC101), and are then applied to the RF-B unit via

the mute switch (IC192) and J851 as the MKR signal.

3 - 7

Page 16

3-4 ANTENNA TUNER CIRCUITS

3-4-1 MATCHING CIRCUIT (TUNER-A UNIT)

The matching circuit is a T-network. Using 2 tuning motors,

the matching circuit obtains rapid overall tuning speed.

(2) Tuning motors (CTRL-A and TUNER-A units)

A motor controller (Q211–Q218, D211, D213, D215, D217)

rotates the tuning motors (TUNER-A unit; MF1, MF2) to

obtain a low SWR.

Using relays (RL1–RL15), the relay control signals from

the antenna tuner CPU (CTRL-A unit; IC5) via the buffer

amplifier (IC1, IC2) ground one of the taps of L3–L12 and

add capacitors (C34–C43). After selecting the coils and

capacitors, 2 motors (CTRL-A unit; MF1, MF2) adjust C44

and C45 using the antenna tuner CPU (CTRL-A unit; IC5)

and the motor controller (CTRL-A unit; Q211–Q218, D211,

D213, D215, D217) to obtain a low SWR (Standing Wave

Ratio).

3-4-2 DETECTOR CIRCUIT (CTRL-A UNIT)

(1) SWR detector

Forward and reflected power are picked up by a current

transformer (L1), detected by D2 (FOR) and D1 (REF), and

then amplified at IC1a and IC1b, respectively. The amplified

voltages are applied to the antenna tuner CPU (IC5, pins 2,

3). The tuner CPU detects the SWR.

(2) Reactance components detector

Reactance components are picked up by comparing the

phases of the RF current and RF voltage. The RF current is

detected by L4 and R16 and buffer-amplified at IC14e and

IC2a and then applied to the phase comparator (IC3a). RF

voltages are detected by C12–C14 and then applied to the

phase comparator (IC3b) after being amplified at the buffer

amplifiers (IC14c, IC2b). The output signal from the phase

comparator (IC3a, pin 6 for RF current, IC3b pin 7 for RF

voltage) is rectified at D7 and D6 for conversion into DC

voltage. The rectified voltage signals are combined, then

amplified at the inverter amplifier (IC4b), then applied to the

antenna tuner CPU (IC5, pin 64).

A C-MOS IC is used for the buffer amplifier (IC14) to

improve functionable sensitivity; the inverter amplifier

(IC4) is very responsive even with a low signal level input.

Together, these ensure quick and stable signal detection

even at low RF signal level input.

(3) Resistance components detector

Resistance components are picked up by L8, and detected

by D8, D9 and Q5. The detected resistance components

are amplified at the inverter amplifier (IC4a), and then

applied to the antenna tuner CPU (IC5, pin 1).

(3) Tuning relays (TUNER-A unit)

According to the operating frequency band and antenna

condition, tuning relays select the capacitors and coils.

3-

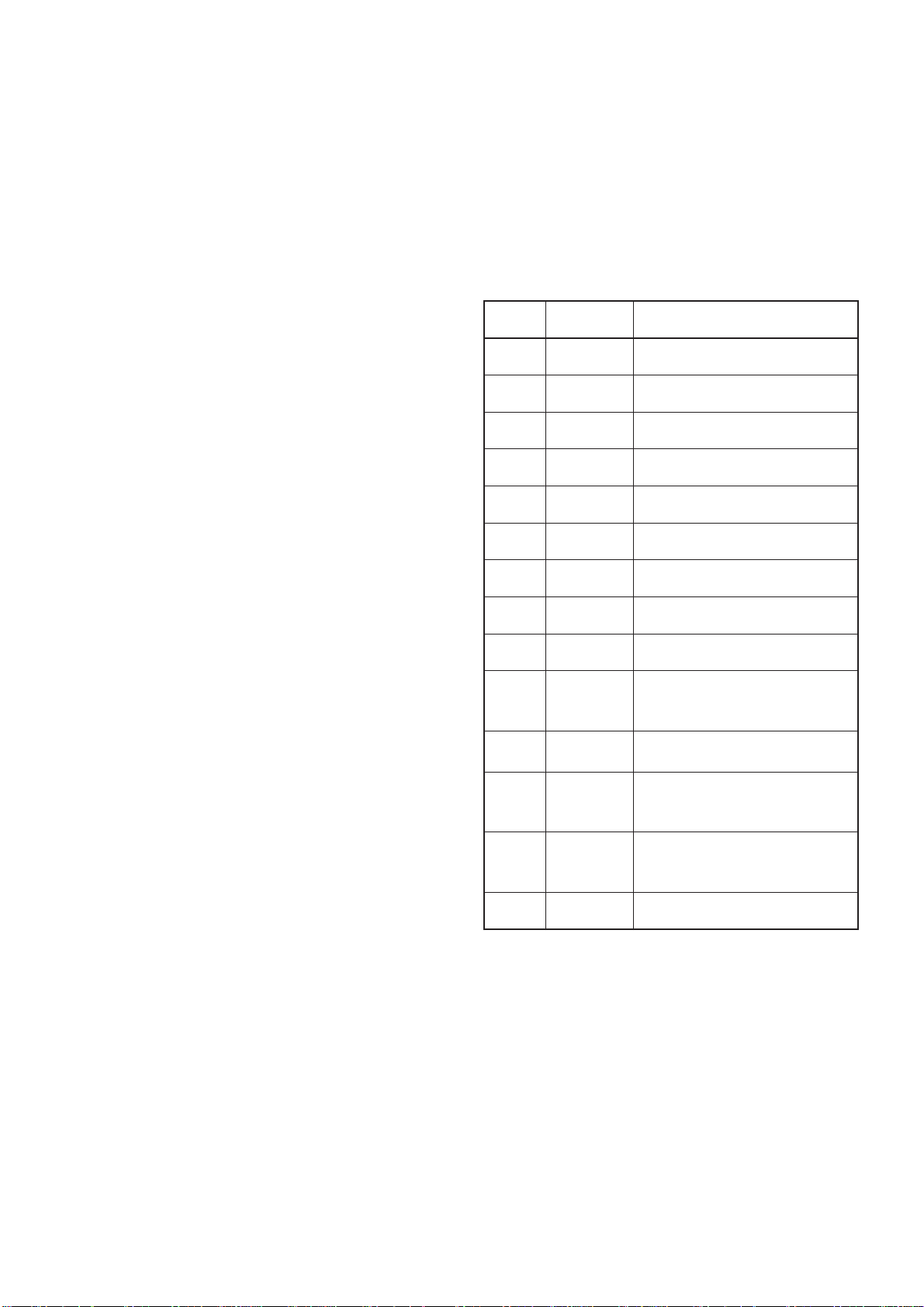

4-4 ANTENNA TUNER CPU PORT ALLOCATION

(CTRL-A unit; IC5)

Pin

number

1AN2

2AN1

3AN0

4PERS

13 IKEY

15 ISTA

17 THRU

21 TRC

26 VHF

27–32

34–40

41–48

27–32

64 AN3

Port

name

24M, 18M,

14M, 10M,

7M, 4M

CO1–CO3,

CI1–CI3

AZ, AY, AX,

AW, PZ, PY,

PX, PW

24M, 18M,

14M, 10M,

7M, 4M

Description

Input port for the resistance components detection voltage.

Input port for the refl ected RF power voltage.

Input port for the forward RF power

voltage.

Input port for the transceiver power

OFF.

Outputs transmit control signal to

the main CPU (IC 3501).

Input port for the antenna tuner

start signal.

Input port for the [TUNER] ON/OFF

signal from main CPU (IC3501)..

Input port for the TX/RX switching

signal.

Output the coil select signals for the

tuner unit.

Output the coil select signals to the

tuner unit.

Output the capacitor select signal

to the tuner unit.

Output pulse-type control signals

for the tuning motors. (MF1, MF2)

Output the coil select signal to the

tuner unit.

Input port for the reactance components detection signal.

3-4-3 MOTOR CONTROL CIRCUIT

(CTRL-A AND TUNER-A UNITS)

The control circuit of the internal antenna tuner consists of

the CPU, EEPROM (Electronically-Erasable Programmable

Read Only Memory), tuning motors and tuning relays.

(1) CPU and EEPROM (CTRL-A unit)

The antenna tuner CPU (IC5) controls the tuning motors

via the motor controller (Q211–Q218, D211, D213, D215,

D217) and tuning relays, and memorizes the best preset

position in 100 kHz steps. The memory contents are stored

in the EEPROM (IC6) without a backup battery.

3 - 8

Page 17

3-5 SCOPE CIRCUITS

3-5-1 SCOPE RECEIVER CIRCUIT (RF-B UNIT)

A portion of the 64.455 MHz 1st IF signal from the 1st

mixer circuit (Q1203–Q1206: while receiving) or IF amplifier (Q1551: while transmitting) is passed through the

PIN attenuator (Q2203) and amplified at the IF amplifiers (Q2202, Q2201), and then mixed with the 77.8 MHz

scope 2nd LO (S2LO) signal at the mixer circuit (D2101)

to produce the 13.345 MHz IF signal. The mixed IF signal

is passed through the ceramic bandpass filters (FI2003,

FI2002) to suppress unwanted signals. The filtered IF signal is applied to the FM IF IC (IC2001, pin 16).

The applied 13.345 MHz IF signal is mixed with the sweep

LO (S3LO) signals from the PLL unit at the FM IF IC

(IC2001). The mixed IF signals are filtered at the ceramic

bandpass filter (FI2001) then applied to the limiter amplifier section in the FM IF IC (IC2001, pin 5). The applied IF

signals are converted into DC voltages according to the

applied IF signal strength at the RSSI section in the IC.

The converted voltages are output from pin12 (IC2001) and

amplified at IC2002, then applied to the MAIN-A unit as the

SCPL signal.

3-6 POWER SUPPLY CIRCUITS

3-6-1 PA UNIT

LINE

PHV

HV

14V

14VA

a8V

5V

H5V

The voltage from an external power supply via

the common filter circuit (FILTER-A unit; L501,

L502).

The same voltage as the PHV line passed

through a fuse (F1).

The same voltage as the HV line passed

through the switching relay (RL1).

The same voltage as the 14 V line is applied to

the AF power amplifier (MAIN-A unit; IC332).

Common 8 V converted from the 14 V line and

regulated by the +8 regulator circuit (IC3).

Common 5 V converted from the 14 V line and

regulated by the +5 regulator circuit (IC2).

Common 5 V converted from the HV line and

regulated by the H5V regulator circuit (IC1).

DESCRIPTION

Some of the DC voltages from the FM IF IC (IC2001) are

amplified at IC2002 to produce AGC voltages for the IF

amplifiers (Q2201, Q2202), producing wider dynamic range.

By sweeping LO signals (S3LO) are applied to the mixer

section in the FM IF IC (IC2001), the spectrum scope function is activated.

3-5-2 SWEEP LO CIRCUIT (PLL UNIT)

The sweep LO signals (S3LO) are generated by the DDS

IC (IC801) using the 32 MHz system clock. A 10-bit digital

signal is converted into analog wave signals at the D/A converter (R801–R820). The converted analog wave is passed

through the bandpass filter (L802, L803, C809–C813) then

applied to the RF-B unit via (J801) after being amplified at

the buffer amplifier (Q802).

• SCOPE CIRCUIT DIAGRAM

1st LO

signal

to 2nd mixer circuit

3-6-2 FRONT UNIT

LINE

5VF

–15V

–7V

–8V

+18V

Common 5 V converted from the 14 V line and

regulated by the +5 regulator circuit (IC861).

Common –15 V converted from the 14 V line

and converted by the –15 DC-DC converter circuit (IC841, Q841, D841). The voltage is applied

to the –7 V, –8 V regulator circuits and etc.

Common –7 V converted from the –15 V line

and regulated by the –7 regulator circuit (IC501).

Common –8 V converted from the –15 V line

and regulated by the –8V regulator circuit

(IC881).

Common 18 V converted from the 14 V line and

converted by the 18 V DC-DC converter circuit

(IC821, Q821, D822).

DESCRIPTION

S3LO signal

(12.79–12.99 MHz*)

RF signals

1st mixer A

Q1203–Q1206

RF-B unit

Q2202

IF

amp.

Q2201

IF

amp.

D2101 FI2003 FI2002

to the MAIN-A unit

S2LO signal

(77.80 MHz)

SCPL signal

3 - 9

Ceramic

BPF

IC2002b

AGC

amp.

IC2002a

Ceramic

BPF

IC2001

Mixer

16

Limiter

amp.

RSSI

12

*depending on sweeping passband width

2

3

5

FI2001

Ceramic

BPF

Page 18

3-6-3 MAIN-A UNIT

LINE

R8V

T8V

Receive 8 V converted from the 14 V line and

regulated by the R8V regulator circuit (Q601,

Q602, D601).

Transmit 8 V converted from the 14 V line and

regulated by the T8V regulator circuit (Q611,

Q612, D611).

DESCRIPTION

3-6-4 CTRL-A AND PLL UNITS

LINE

5V

5V

Common 5 V for the antenna tuner CPU

(CTRL-A unit; IC5), EEPROM (CTRL-A unit;

IC6) and etc. converted from the 14 V line and

regulated by the +5 regulator circuit (CTRL-A

unit; IC13).

Common 5 V for each PLL-A and PLL-B circuits

regulated from the 8 V line and regulated by

the +5 regulator circuit (PLL unit; IC382: PLL-A,

IC682: PLL-B).

DESCRIPTION

3-7 LOGIC CIRCUITS

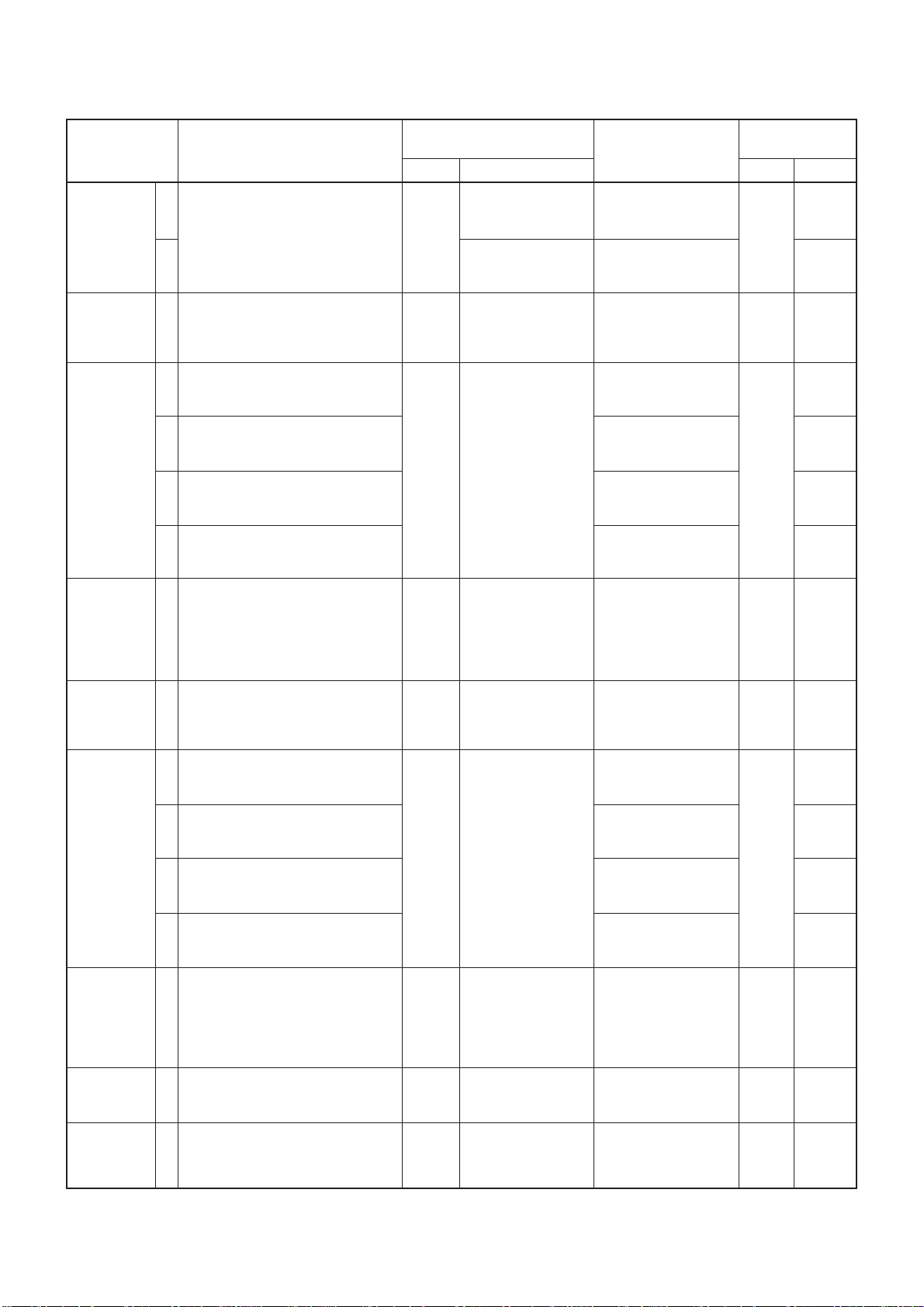

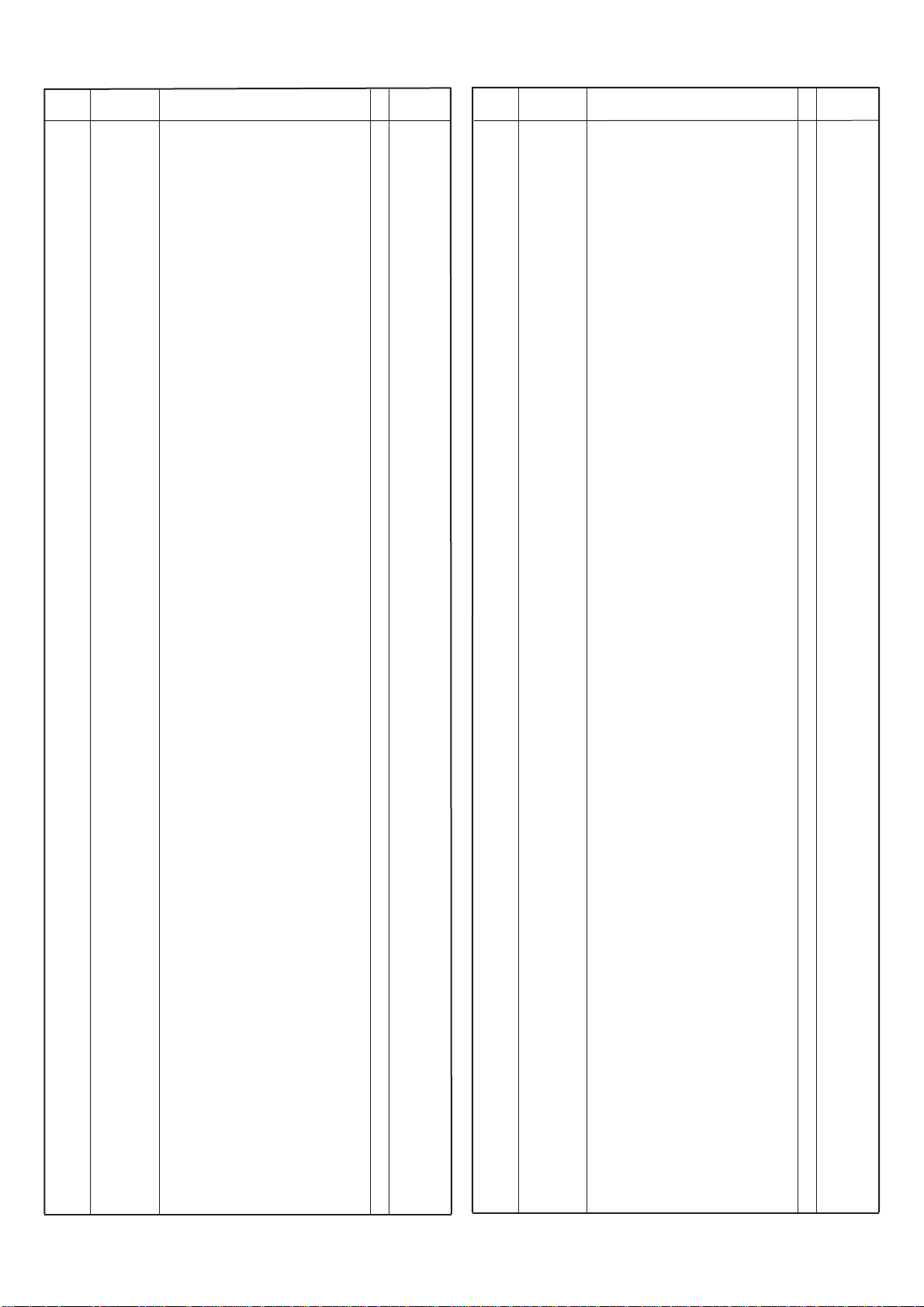

3-7-1 BAND SELECTION DATA

(RF-B, CTRL-A, PLL UNITS)

Frequency

[MHz]

IC401–IC403

(RF-B )

0.03–1.5999999 B0

1.6–1.999999 B1

2.0–2.999999 B2

4.0–4.999999

5.0–5.999999

B4

6.0–6.999999 B5W

7.0–7.299999 B5

7.3–7.999999 B5W

8.0–10.999999 B6

11.0–11.999999

12.0–13.999999

B7W

14.5–14.999999 B7W

15.0–19.999999

20.0–20.999999

B8W

21.0–21.499999 B8

21.5–21.999999 B8W

22.0–29.999999 B9 L7S

30.0–44.999999

45.0–49.999999

B10W

54.0–60.000000 B10W

IC11

(CTRL-A)

L1S

L2S3.0–3.999999 B3

L3S

L4S

L5S14.0–14.499999 B7

L6S

L8S

IC101

(PLL)

IC401

(PLL)

VA1S VB1S

VA2S VB2S

VA3S VB3S

VA4S VB4S50.0–54.000000 B10

3-7-2 SUB-CPU PORT ALLOCATIONS

(DISPLAY BOARD; IC401)

Pin Port

number name

7, 8

12, 83

56, 57

64–66

OSC1,

OSC2

DRES

9

MSB,

MSA

DOTK,

DSHK

MDM0–

MDM2

TNRD, MOND

NBD, NRD

67–75

LOCD, TXD

RXD, PBTD

NOTD

77, 79

81

82, 84

85, 88

86

87

92

93

94

95

96

97

98

99

100

PB1B,

PB1A

METV

RSA,

RSB

PB2A,

PB2B

LMFD

LFMD

BALL

NRL

MIGL

PWRL

CMPL

KYSL

DELL

NOTL

PITL

Input and output ports for the system

clock oscillator (X401; 9.8304 MHz).

Input port for the reset signal.

Input port for the [DIAL]; pulse-type

signals are applied.

Input ports for the [ELEC-KEY] jack.

Output ports for the S/RF meter backlight and function switch activation

indicator brightness control signal.

Port

MDM0

MDM1

MDM2

Control signal output ports for the

activation indicator of function switches.

High : When the function is activated.

Input port for the [TWIN PBT (inner)]

control (PBT board, S1/inner).

Outputs the S/RF meter (ME1) drive

signal.

Input ports for the [RIT/∆TX] control;

pulse-type signals are applied.

Input port for the [TWIN PBT(outer)]

control (PBT board, S1/outer).

Input port for data signal from the

main-CPU (MAIN-A unit; IC3501).

Outputs data signal for the main-CPU

(MAIN-A unit; IC3501).

A/D input port for the [BAL] control

(R702/ inner).

A/D input port for the [NR] control

(R702/ outer).

A/D input port for the [MIC GAIN]

control (R712).

Input port for the [RF POWER] control (R714).

Input port for the [COMP] control

(R716).

Input port for the [KEY SPEED] control (R718).

Input port for the [BK-IN DELAY] control (R720).

Input port for the [NOTCH] control

(PBT board, R1/inner).

Input port for the [CW PITCH] control

(PBT board, R1/outer).

Description

Backlight level

1234567

High

Low High

High High High HighLow Low Low

Low Low Low

Low High HighLow

High High High High

3 - 10

Page 19

3-7-3 MAIN-CPU PORT ALLOCATIONS

(MAIN-A UNIT; IC3501)

Pin Port

number name

29

30

31

32

34

37

59

61

63

64

66

69

70

71

72

73

74

75

76

77

A0–A3,

A4–A11,

A12–A18

SKYS

RTKI

DPGI

DSDR

PWRK

DSKY

DB0–DB3,

DB4–DB11

DB12–DB15

CTXD

CRXD

MCK

MDAT

TRVI

IKEY

RXS

TXS

ISTA

DRES

UNLC

PSTB

PSEL

CON2

6–9,

11–18,

20–26

40–43,

45–52,

54–57

Address signal output ports for the

LCD controller (IC3551).

Input port for the [KEY] jack.

Low : During key down

Input port for the RTTY keying.

Power supply detection input port for

the DSP-A board.

Input port for data signal from DSP-A

board.

Input port for the [POWER] switch.

Low : When the [POWER] is pushed.

Outputs CW/RTTY keying.

Data bus lines for the LCD controller

,

(IC3551) and I/O expander (IC3652–

IC3654).

Outputs the CI-V signal.

Input port for the CI-V signal.

Outputs clock signal.

Outputs data signal.

Input port for the [XVERT] detection

signal.

Input port for transmit control signal

from the antenna tuner CPU (CTRL-A

board; IC5).

Outputs R8V regulator (Q601, Q602,

D601) control signal.

Low : While receiving

Outputs T8V regulator (Q611, Q612,

D611) control signal.

Low : While transmitting

Outputs antenna tuner start signal.

Outputs reset/inhibit signal to the subCPU (DISPLAY board; IC401), DDS

ICs (PLL unit; IC101, IC401), antenna

tuner CPU (CTRL-A board; IC5), and

etc.

Input port for unlock signal from the

PLL unit.

Outputs strobe signals for the I/O

expander IC (PLL unit; IC1).

Outputs strobe selection signals for

the I/O expander (PLL unit; IC1).

Outputs control signal for the DDS circuits (PLL unit; IC101, IC401).

Description

Pin Port

number name

78

79

85, 86

96

97

98

101

105

106

107

108

109

110

111

112

115

116

CON1

(PDAT)

CON0

(PCK)

XTAL,

EXTAL

LRES

LTXD

LRXD

TMD

SCPL

VOXL

AVXL

ASO0

ASO1

ASO2

STON

BEEP

SENI

PWRS

Description

Outputs data signal for the DDS circuits (PLL unit; IC101, IC401).

Outputs clock signal for the DDS circuits (PLL unit, IC101, IC401).

Input ports for the CPU system clock

oscillator (X3501; 19.6608 MHz).

Outputs reset/inhibit signal for the

LCD controller (IC3551), I/O expander

(IC3652–IC3654), and etc.

Outputs data signal for the sub-CPU

(DISPLAY board; IC401).

Input port for data signal from the

sub-CPU (DISPLAY board; IC401).

Outputs [TIMER] indicator control signal.

High : When the timer function is ON

Input port for the scope signal.

A/D input port for the VOX gain.

A/D input port for the anti-VOX level.

A/D input port via the analog switch

(IC3631) for the SML signal from the

S-meter amplifier circuit (IC101a),

and ALCL signal from the ALC meter

amplifier circuit (IC551a).

A/D input port via the analog switch

(IC3631) for the NSQO signal from

the level conveter (DSP-A board;

IC2063), for noise squelch operation, and FORL signal from the power

meter amplifier circuit (IC571a).

A/D input port from the analog switch

(IC3631) for the FNTL signal from

the low-pass filter (DSP-A board;

IC2472a), for tone squelch operation,

and REFL signal from the SWR meter

amplifier circuit (IC571b).

Outputs CW side-tone signals.

Outputs beep audio signals.

Input port for connected microphone’s

PTT switch and SEND signal from the

ACC jacks.

High : While PTT switch is pushed or

activated from an external unit.

Outputs control signal for the power

switching relay (PA unit; RL1) .

High : During power ON

3 - 11

Page 20

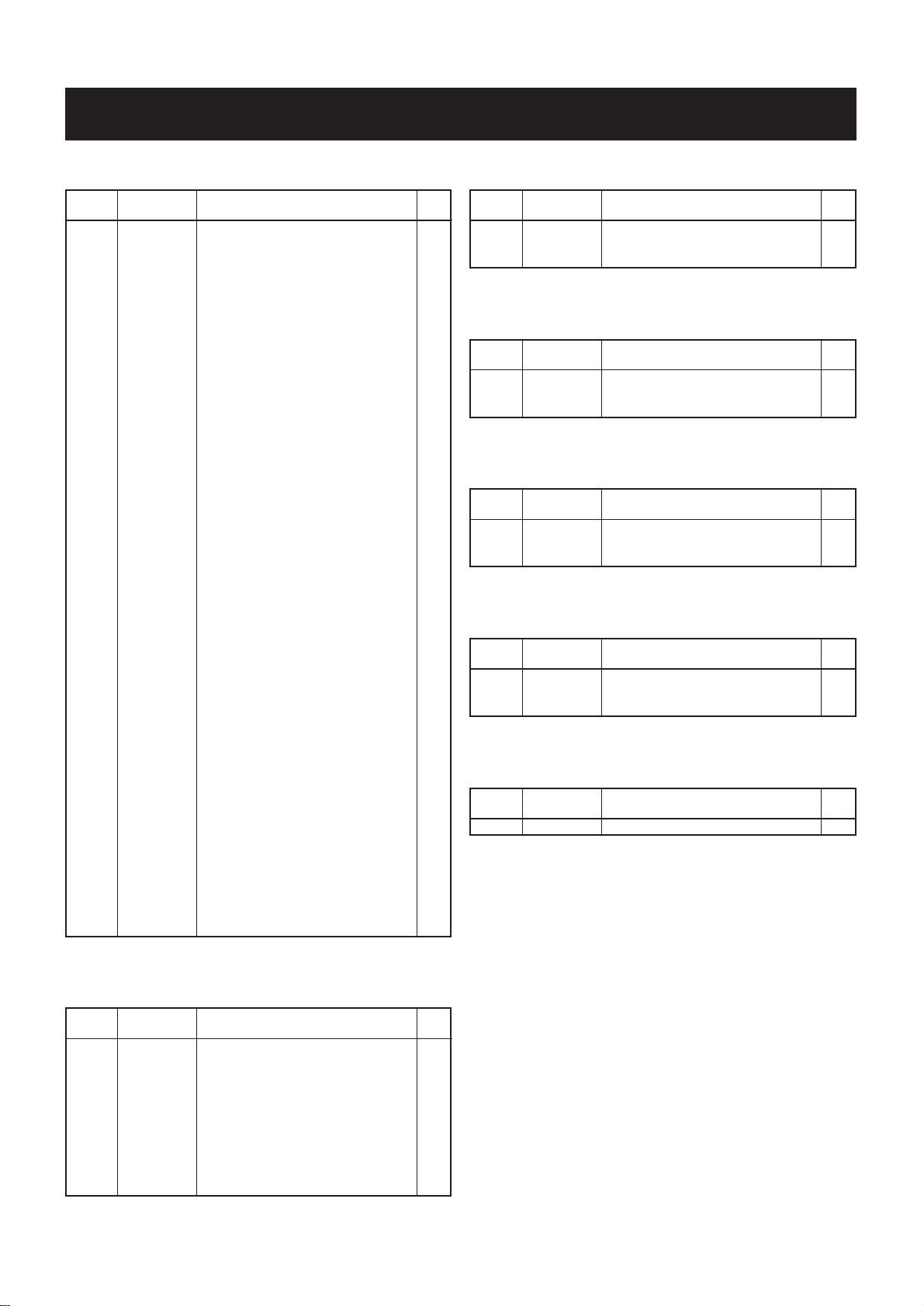

3-7-4 INPUT EXPANDER ALLOCATIONS

(1) DISPLAY board; IC411

Pin Port

number name

1

5

12

13

14, 15

KI4

MUDK

KI3

KI0

KI1, KI2

Input port for the [RIT], [∆TX] and

[CLEAR] switches.

Input port for [UP] and [DN] switches

of the connected microphone.

Input port for the [DUALWATCH],

[CHANGE], [V/M] and [M/S] switches.

Input port for the [TUNER],

[MONITOR], [NB] and [NR] switches.

Input ports for the multi-function

switches.

Description

(2) MAIN-A unit; IC3652

Pin Port

number name

11

12

13

14

16

17

18

CTFL

RTDT

EKEY

TCON

VINT

VRAC

SBSY

Input port transmission status for CW

Input port for RTTY decode data.

Input port for the KEY signal from the

connected AH-3.

Low : While tuning or tune NG

Input port for AH-3 connection detection.

High : When AH-3 is connected.

Input port for interrupting signal

from audio recoder.

Input port for address clock signal

from audio recoder.

Input port for busy signal from

the installed UT-102 SPEECH

SYNTHESIZER.

Description

3-7-5 OUTPUT EXPANDER ALLOCATIONS

(1) PLL unit; IC1

Pin Port

number name

4

5

6

7

12

13

14

PST1

PST2

PST3

PST4

PST5

PST6

PST7

Outputs strobe signals to DDS IC

(IC101) for the 1st LO PLL A circuit.

Outputs strobe signals to PLL IC

(IC381) for the 1st LO PLL A circuit.

Outputs strobe signals to DDS IC

(IC401) for the 1st LO PLL B circuit.

Outputs strobe signals to PLL IC

(IC681) for the 1st LO PLL B circuit.

Outputs strobe signals to DDS IC

(IC701) for the 3rd LO PLL circuit.

Outputs strobe signals to PLL IC

(IC901) for the S2 LO PLL circuit.

Outputs strobe signals to DDS IC

(IC801) for the S3 LO PLL circuit.

Description

(2) PLL unit; IC101

Pin Port

number name

66

68

70

71

73

74

75

MAKS

PAMT

PAFS

VA4S

VA3S

VA2S

VA1S

(3) PLL unit; IC401

Pin Port

number name

68

70

71

73

74

75

PBMT

PBFS

VB4S

VB3S

VB2S

VB1S

Description

Outputs the marker mute switch

(IC192) control signa

High : When the marker ON is select-

ed.

Outputs LO mute switch (Q361) control signal.

Low : Muted

Outputs bandpass filter select switch

(Q351) control signal.

High : When less than 8 MHz is dis-

played on the main band.

Outputs the LO switch (Q121) control

signal.

High : While 45.0–60.0 MHz band is

displayed on the main band.

Outputs the LO switch (Q122) control

signal.

High : While 20.0–44.999999 MHz band

is displayed on the main band.

Outputs the LO switch (Q123) control

signal.

High : While 8.0–19.999999 MHz band

is displayed on the main band.

Outputs the LO switch (Q126) control

signal.

High : While 0.03–7.999999 MHz band

is displayed on the main band.

Description

Outputs LO mute switch (Q661) control

signal.

Low : Muted

Outputs bandpass filter select switch

(Q651) control signal.

High : When less than 8 MHz is dis-

played on the main band.

Outputs the LO switch (Q421) control

signal.

High : While 45.0–60.0 MHz band is

displayed on the main band.

Outputs the LO switch (Q422) control

signal.

High : While 20.0–44.999999 MHz band

is displayed on the main band.

Outputs the LO switch (Q423) control

signal.

High : While 8.0–19.999999 MHz band

is displayed on the main band.

Outputs the LO switch (Q426) control

signal.

High : While 0.03–7.999999 MHz band

is displayed on the main band.

l.

3 - 12

Page 21

(4) CTRL-A board; IC11

Pin Port

number name

Outputs a low-pass filter select signal.

High : When 0.03–1.999999 MHz

Outputs a low-pass filter select signal.

High : When 2.0–4.999999 MHz band

Outputs a low-pass filter select signal.

High : When 5.0–7.999999 MHz band

Outputs a low-pass filter select signal.

High : When 8.0–11.999999 MHz

Outputs a low-pass filter select signal.

High : When 30.0–60.0 MHz band is

Outputs a low-pass filter select signal.

High : When 22.0–29.999999 MHz

Outputs a low-pass filter select signal.

High : When 15.0–21.999999 MHz

Outputs a low-pass filter select signal.

High : When 12.0–14.999999 MHz

11

12

13

14

4

5

6

7

L1S

L2S

L3S

L4S

L8S

L7S

L6S

L5S

Description

band is selected.

is selected.

is selected.

band is selected.

selected.

band is selected.

band is selected.

band is selected.

(6) RF-B unit; IC402

Pin

number

4 B7WS

5 B7S

6 B8WS

7 B8W

12 B10S

13 B10WS

14 B9S

Port

name

Outputs a bandpass filter select signal.

High : When 11–13.999999 MHz or

Outputs a bandpass filter select signal.

High : When 14.0–14.499999 MHz is

Outputs a bandpass filter select signal.

High : When 15.0–20.999999 MHz or

Outputs a bandpass filter select signal.

High : When 21.0–21.499999 MHz is

Outputs a bandpass filter select signal.

High : When 50.0–54.0 MHz is select-

Outputs a bandpass filter select signal.

High : When 30.0–49.999999 MHz or

Outputs a bandpass filter select signal.

High : When 22–29.999999 MHz is

Description

14.5–14.999999 MHz band is

selected.

selected.

21.5–21.999999 MHz band is

selected.

selected.

ed.

54.000001 MHz band is selected.

selected.

(5) RF-B unit; IC401

Pin

number

4 B0S

5 B1S

6 B2S

7 B3S

11 B6S

12 B5S

13 B5WS

14 B4S

Port

name

Outputs a bandpass filter select signal.

High : When 0.03–1.599999 MHz is

Outputs a bandpass filter select signal.

High : When 1.6–1.999999 MHz is

Outputs a bandpass filter select signal.

High : When 2.0–2.999999 MHz is

Outputs a bandpass filter select signal.

High : When 3.0–3.999999 MHz is

Outputs a bandpass filter select signal.

High : When 8.0–10.999999 MHz is

Outputs a bandpass filter select signal.

High : When 7.0–7.299999 MHz is

Outputs a bandpass filter select signal.

High : When 6.0–6.999999 MHz or

Outputs a bandpass filter select signal.

High : When 4.0–5.999999 MHz is

Description

selected.

selected.

selected.

selected.

selected.

selected.

7.3–7.999999 MHz band is

selected.

selected.

(7) RF-B unit; IC403

Pin

number

4 AT1S

5 AT2S

6 PR1S

7 PR2S

Port

name

Outputs control signal for the

attenuator circuit (RL102, R102,

R106, R111).

Low : When 6 dB attenuator is ON.

Outputs control signal for the

attenuator circuit (RL103, R112,

R113, R114).

Low : When 12 dB attenuator is ON.

Outputs control signal for the preamplifier (PRE-AMP board; Q4201,

Q4202).

High : When P.AMP 1 is ON.

Outputs control signal for the preamplifier (PRE-AMP board; Q4302).

High : When P.AMP 2 is ON.

Output the RX antenna select

14 RANS

signal.

High : When RX antenna is selected.

Description

3 - 13

Page 22

(8) MAIN-A unit; IC3653

Pin Port

number name

Outputs strobe signals for the out-

13

14

15

16

17

18

19

BSTB

ANTS

FSTB

ASTB

MSTB

AFMS

SQLS

put expander ICs (RF-B unit; IC301,

IC302).

Outputs the antenna connector

([ANT1] or [ANT2]) select signal.

High : When the [ANT2] is selected.

Outputs strobe signals for the output

expander (CTRL-A board; IC11).

Outputs strobe signals for the D/A

converter (IC3751).

Outputs strobe signals for the output

expander ICs (IC3752, IC3753).

Outputs control signal for the AF mute

switch (IC331).

High : When the [AF] control is set to

Outputs squelch mute control signal,

applied to the squelch gate (IC301).

High : When squelch is closed.

(9) MAIN-A unit; IC3654

Pin Port

number name

Outputs squelch control signal for the

12

13

14

15

16

17, 18

SQSS

SPS

SSTB

VCS

ESTA

DSFR,

DSFW

[MIC] and [ACC1] connectores.

High : Squlch opend. (RX LED ON)

Outputs control signal for the internal

speaker ON/OFF select relay (RL351).

High : Internal speaker is ON.

Outputs strobe signals for the optional

UT-102 SPEECH SYNTHESIZER.

Outputs chip select signal for the

audio recoder (IC3001).

Outputs external antenna tuner (AH-3)

start signal.

Low : When the [TUNE] switch is

Outputs control signal for the DSP IC

(DSP-A board; IC2001).

Description

maximum counter clockwidth.