Page 1

SERVICE

MANUAL

UHF FM TRANSCEIVER

LPD FM TRANSCEIVER

Page 2

INTRODUCTION

DANGER

ORDERING PARTS

REPAIR NOTES

This service manual describes the latest service information

for the at the time of publication.

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 5 V. Such a connection

could cause a fire hazard and/or electric.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when

connecting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100mW)

to the antenna connector. This could damage the transceiver's front end.

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

0910049951 PCB B-5109B IC-4008A MAIN UNIT 5 pieces

8810009780 Screw PH BO M2x6 ZK IC-4008A Chassis 10 pieces

Addresses are provided on the inside back cover for your

convenience.

1. Make sure a problem is internal before disassembling the transceiver.

2. DO NOT open the transceiver until the transceiver is disconnected from its power source.

3. DO NOT force any of the variable components. Turn them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An insulated turning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the transceiver is defective.

6. DO NOT transmit power into a signal generator or a sweep generator.

7. ALWAYS connect a 30 dB to 40 dB attenuator between the transceiver and a deviation meter or spectrum analyzer when

using such test equipment.

8. READ the instructions of test equipment thoroughly before connecting equipment to the transceiver.

To upgrade quality, all electrical or mechanical parts and

internal circuits are subject to change without notice or obligation.

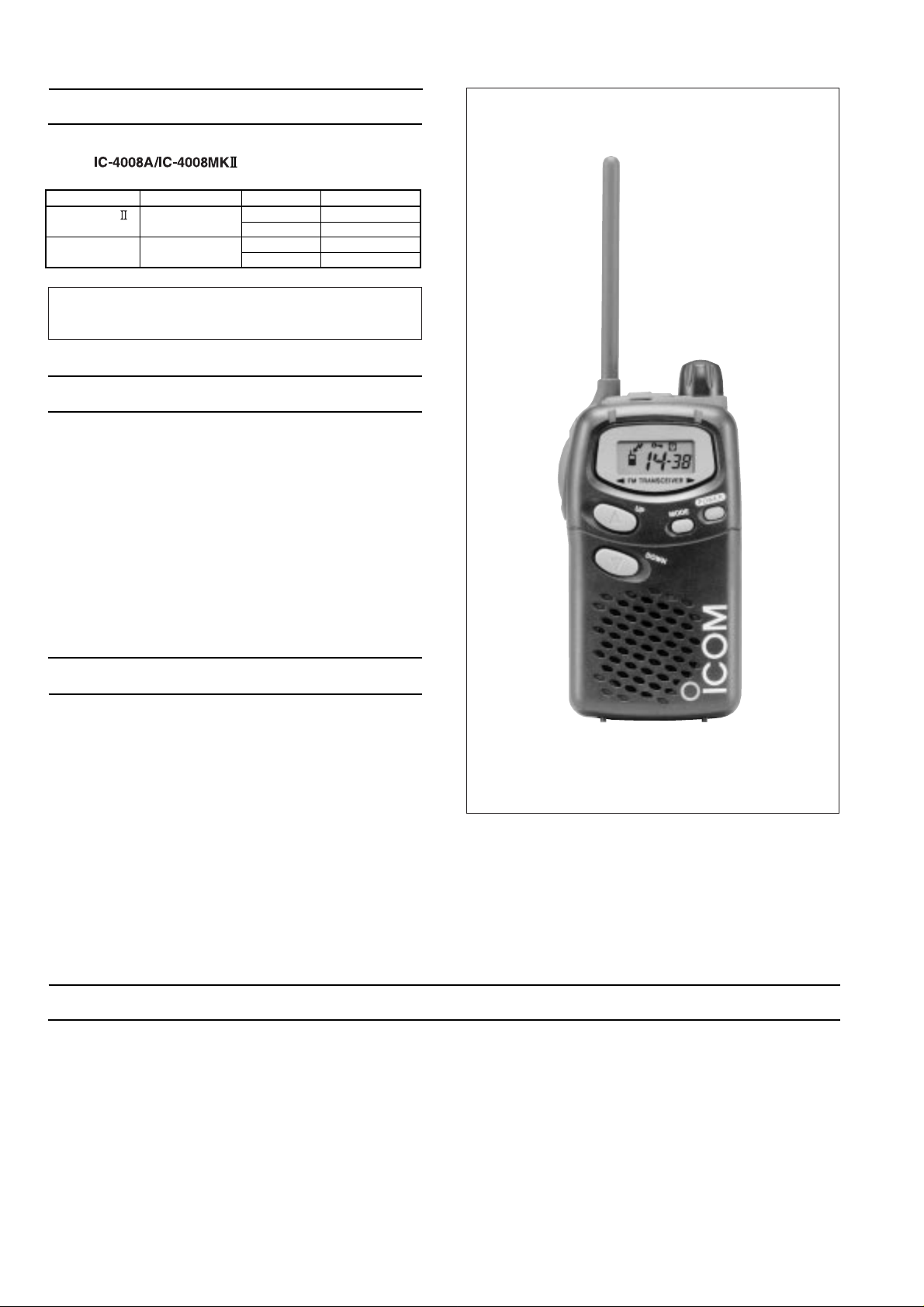

MODEL

IC-4008MK

IC-4008A

VERSION

Italy

C.S.America

SYMBOL

ITA

ITA-1

CSA

CSA-1

BODY COLOR

BLACK

YELLOW

BLACK

YELLOW

Page 3

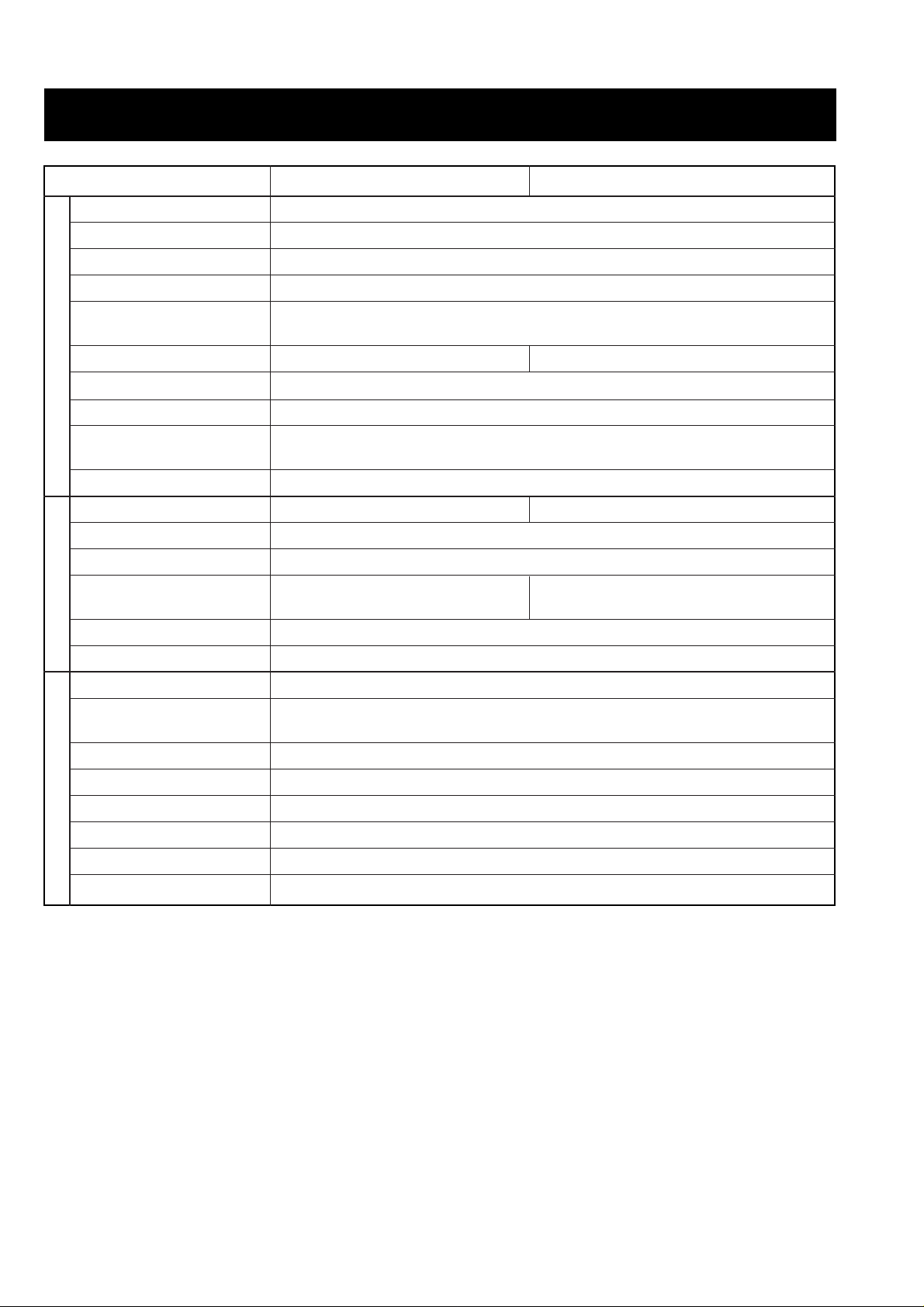

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASEMBLY INSTRUCTION

SECTION 4 CIRCUIT DESCRIPTION

4-1 RECEIVER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4-2 TRANSMITER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

4-3 PLL CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

4-4 POWER SUPPLY CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4-5 PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5-2 ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2

SECTION 6 PARTS LIST

SECTION 7 MECHANICAL PARTS AND DISASSEMBLY

7-1 CABINET PARTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

7-2 ACCESSORIES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

SECTION 8 SEMI-CONDUCTOR INFORMATION

SECTION 9 BOARD LAYOUTS

9-1 MAIN UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9-2 RF UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-5

SECTION 10 BLOCK DIAGRAM

SECTION 11 VOLTAGE DIAGRAM

11-1 MAIN UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

11-2 RF UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-2

Page 4

SECTION 1 SPECIFICATIONS

1 - 1

All stated specifications are subject to change without notice or obligation.

Number of channels

Type of emission

Frequency stability

Frequency resolution

Power supply requirements

(negative ground)

Current drain

Operating temperature range

Number of CTCSS frequency

Dimensions

(proj. not included)

Weight (included 3 cells)

Output power

Modulation system

Max. freqequency deviation

Spurious emissions

Adjacent channel power

External mic.connector

Receiving system

Intermediate frequency

Sensitivity (12 dB SINAD)

Adjacent channel selectivity

Spurious response

Intermoduration

Audio output power

External SP connector

[ITA], [ITA-1] [CSA], [CSA-1]

RECEIVER TRANSMITTER GENERAL

69 channel (simplex; 433.075–434.775)

16K0F3E

±2500 Hz (±5.7 ppm)

25 kHz

3

× AA(R6) dry, alkaline;or optional BP-202

less than 140 mA less than 500 mA

–10˚C to +55˚C (–14˚F to +122˚F)

38 (67.0–250.3 Hz)

55.5(W)

× 102.5(H) × 26.5(D) mm

23⁄16(W) × 41⁄32(H) × 11⁄32(D) inch

180 g; 7.8 oz

10 mW 500 mW

Variable reactance frequency modulation

±5.0 kHz

0.25 µW

–40 dB

50 µW

more than 47 dB

3-conductor 2.5(d) mm/2.2 kΩ

Double conversion superheterodyne

1st: 21.7 MHz

2nd: 450 kHz

0.2 µV ;–14 dBµ

more than 40 dB

more than 40 dB

more than 40 dB

100 mW at 10% distortion with an 8 Ω load

2-conductor 3.5 (d) mm (

1

⁄8")/8 Ω

Page 5

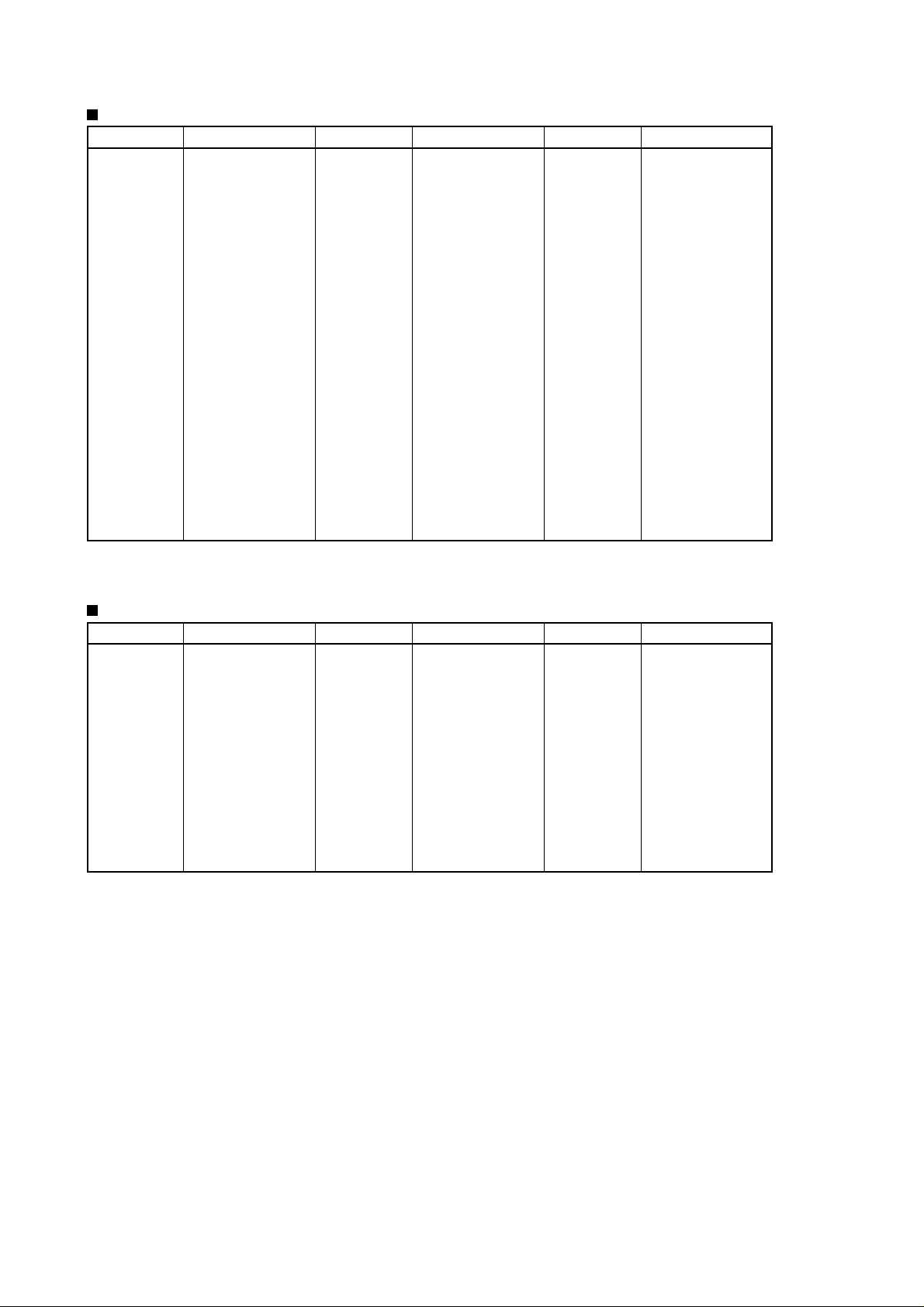

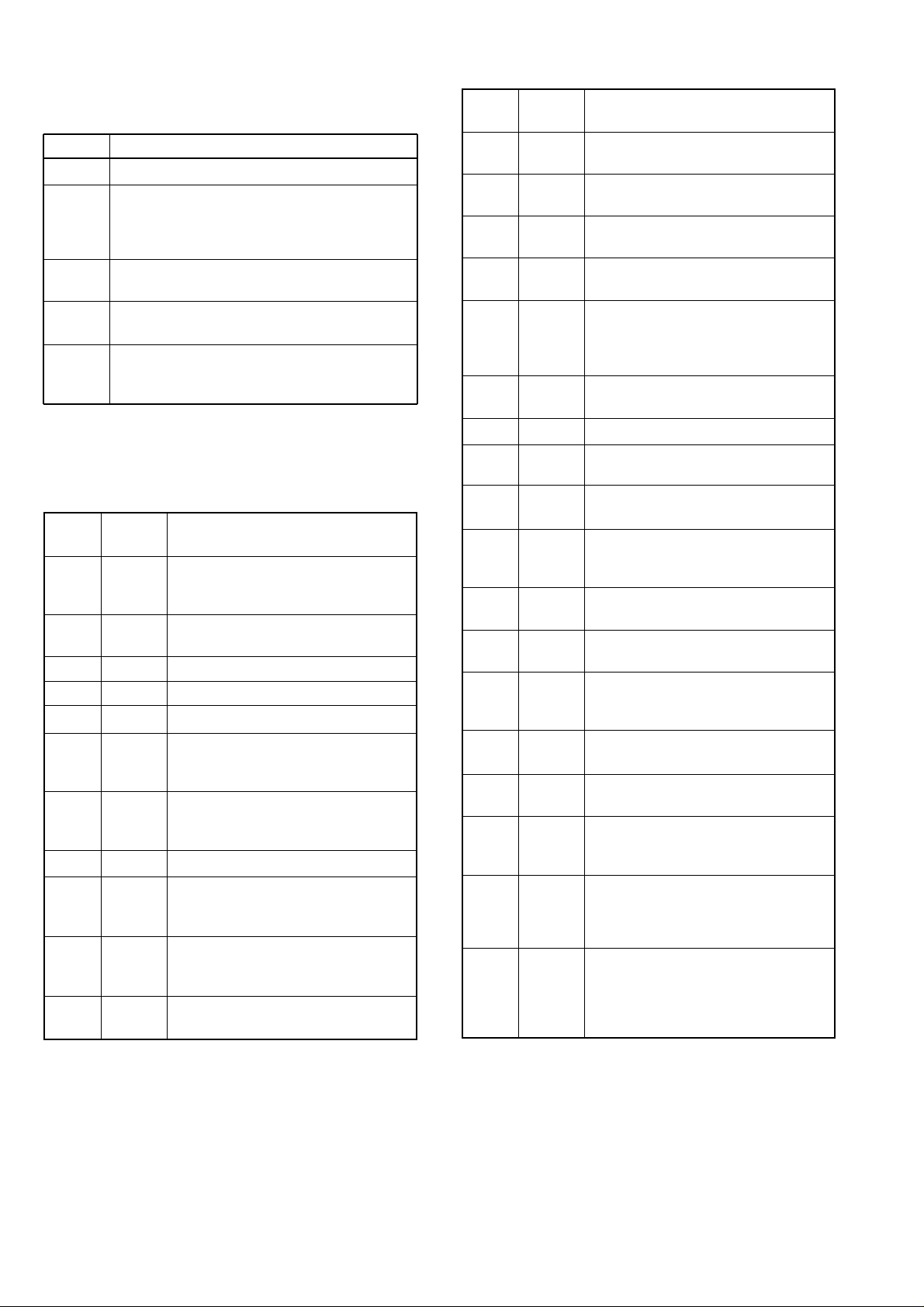

CHANNEL FREQUENCY LIST

CTCSS FREQUENCY LIST

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

433.0750

433.1000

433.1250

433.1500

433.1750

433.2000

433.2250

433.2500

433.2750

433.3000

433.3250

433.3500

433.3750

433.4000

433.4250

433.4500

433.4750

433.5000

433.5250

433.5500

433.5750

433.6000

433.6250

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

433.6500

433.6750

433.7000

433.7250

433.7500

433.7750

433.8000

433.8250

433.8500

433.8750

433.9000

433.9250

433.9500

433.9750

434.0000

434.0250

434.0500

434.0750

434.1000

434.1250

434.1500

434.1750

434.2000

Channel No. Frequency (MHz) Channel No. Frequency (MHz) Channel No. Frequency (MHz)

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

434.2250

434.2500

434.2750

434.3000

434.3250

434.3500

434.3750

434.4000

434.4250

434.4500

434.4750

434.5000

434.5250

434.5500

434.5750

434.6000

434.6250

434.6500

434.6750

434.7000

434.7250

434.7500

434.7750

1

2

3

4

5

6

7

8

9

10

11

12

13

67.0

71.9

74.4

77.0

79.7

82.5

85.4

88.5

91.5

94.8

97.4

100.0

103.5

14

15

16

17

18

19

20

21

22

23

24

25

26

107.2

110.9

114.8

118.8

123.0

127.3

131.8

136.5

141.3

146.2

151.4

156.7

162.2

Channel No. Frequency (Hz) Channel No. Frequency (Hz) Channel No. Frequency (Hz)

27

28

29

30

31

32

33

34

35

36

37

38

---

167.9

173.8

179.9

186.2

192.8

203.5

210.7

218.1

225.7

233.6

241.8

250.3

OFF

1 - 2

Page 6

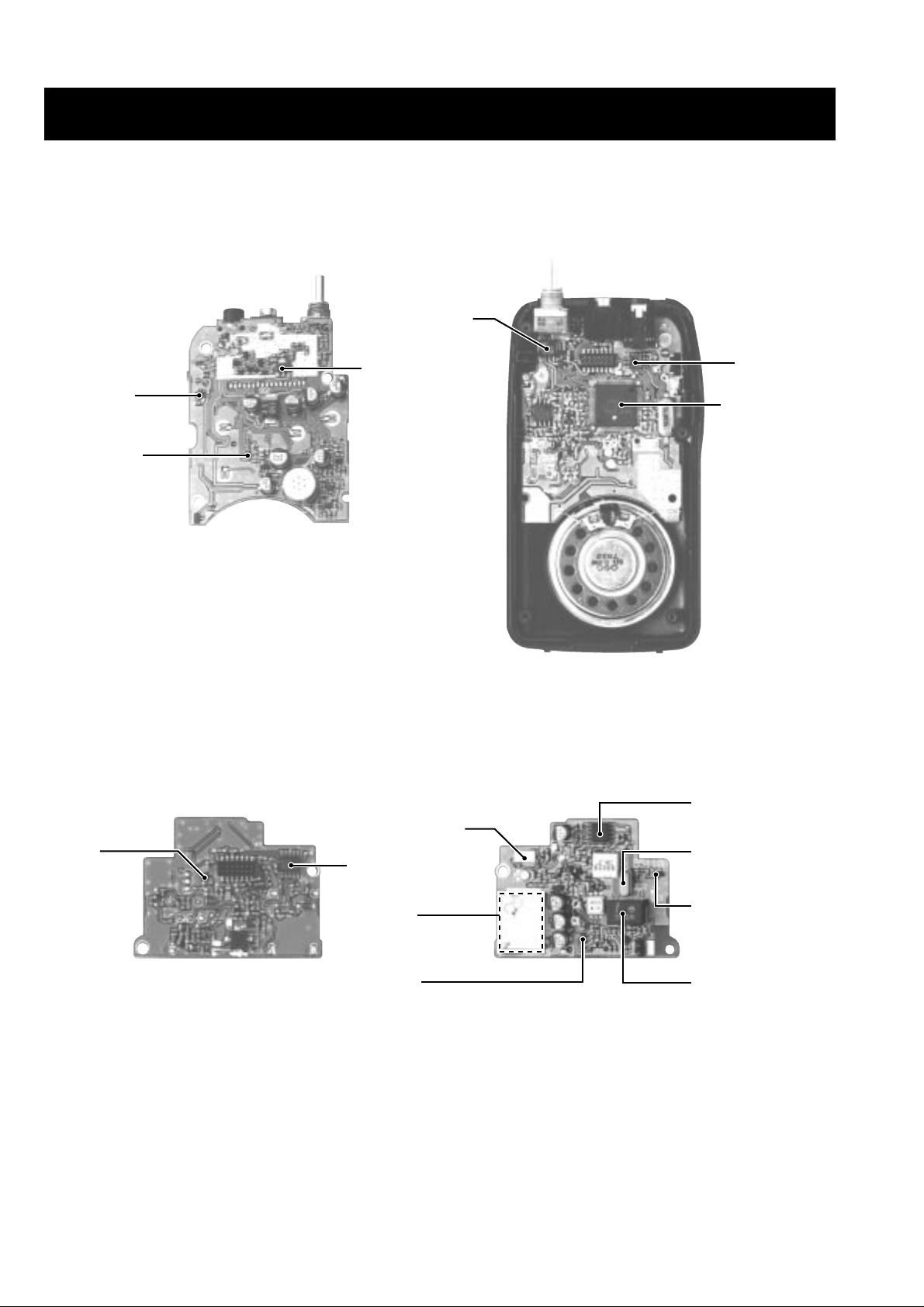

SECTION 2 INSIDE VIEWS

2 - 1

•

MAIN UNIT

•

RF UNIT

T+3 Regurator

(Q28: 2SB798)

+3 Regurator

(IC6: S-81230SG)

R+3 Regurator

(Q18: 2SA1586)

CPU

(IC1: µPD753036GK)

Audio amplifier

(IC9: NJM2070M)

EEPROM

(IC3: X24C01AS)

TOP VEIW BOTTOM VEIW

1st mixer

(Q2: 2SC4226)

PLL IC

(IC1: TB31202FN)

2nd IF filter

(Fl3: CFWM450E)

1st IF amplifier

(Q1: 2SC4215)

FM IF IC

(IC2: TA31136FN)

Reference oscilletor

(X1: CR-633 21.25 MHz)

VCO circuit

RF amplifier

(Q3: 2SC5194)

1st IF filter

(Fl2: FL-298)

TOP VIEW BOTTOM VIEW

Page 7

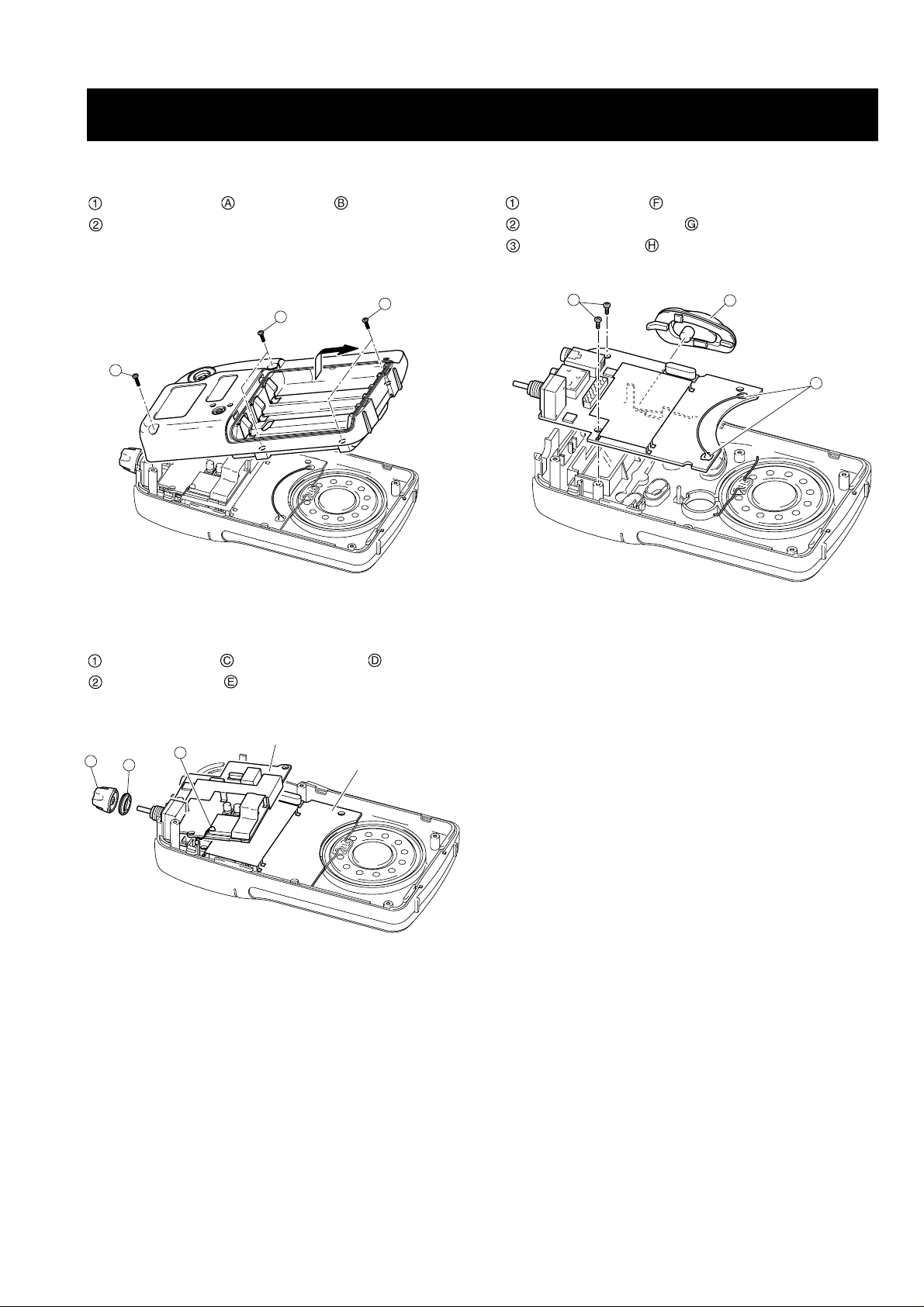

SECTION 3 DISASEMBLY INSTRUCTIONS

3 - 1

A

B

B

MAIN unit

RF unit

E

C

D

F

H

G

•

REMOVING THE REAR PANEL

Unscrew 1 screw , and 4 screws .

Remove the rear panel in the direction of the arrow.

•

REMOVING THE RF UNIT

Remove 1 knob, , and unscrew 1 nut, .

Unsolder 1 point, , and then remove the RF unit.

•

REMOVING THE MAIN UNIT

Unscrew 2 screws, .

Remove the PTT rubber, .

Unsolder 2 points, , and remove the MAIN unit.

Page 8

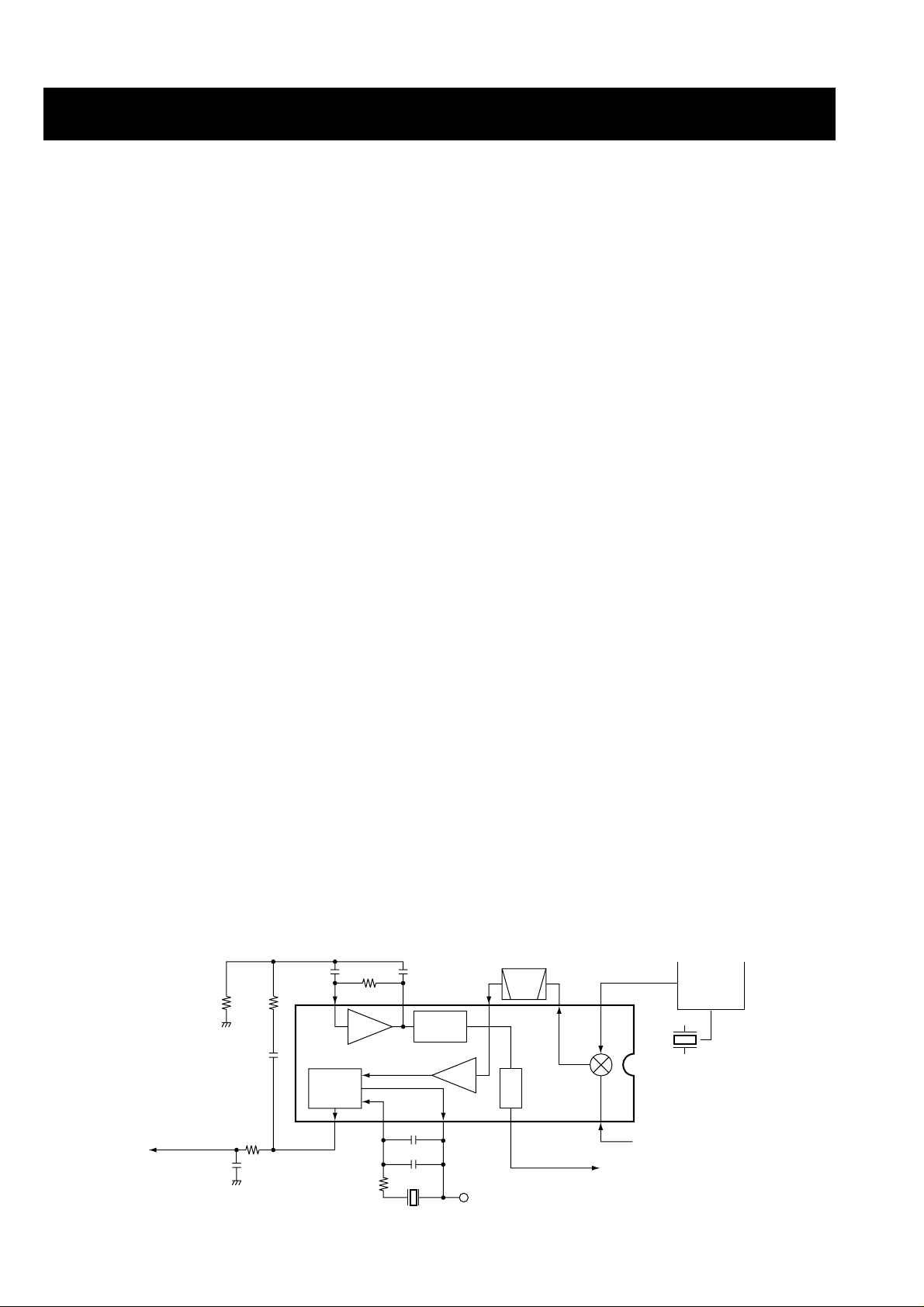

4 - 1

SECTION 4 CIRCUIT DESCRIPTION

4-1 RECEIVER CIRCUITS

4-1-1 ANTENNA SWITCHING CIRCUIT (RF UNIT)

Received signals from the antenna connector are passed

through the low-pass filter (L5, L6, C8–C12). The filtered signals are applied to the λ⁄4 type antenna switching circuit (D7,

D101, D102, L4, L206, C209, C210).

The antenna switching circuit functions as a low-pass filter

while receiving. However, its impedance becomes very high

while D101 and D102 are turned ON (while transmitting).

Thus transmit signals are blocked from entering the receiver

circuits. The passed signals are then applied to the RF amplifier circuit.

4-1-2 RF CIRCUIT (RF UNIT)

The RF circuit amplifies signals within the range of frequency coverage and filters out-of-band signals.

The signals from the antenna switching circuit are amplified

at the RF amplifier (Q3) and passed through the bandpass filter (FI1) to suppress out-of-band signals. The filtered signals

are applied to the 1st mixer circuit (Q2).

4-1-3 1st MIXER AND 1st IF CIRCUITS (RF UNIT)

The 1st mixer circuit converts the received signals to a fixed

frequency of the 1st IF signal with a PLLoutput frequency. By

changing the PLL frequency, only desired signals will be

passed through a crystal filter at the next stage of the 1st

mixer.

The signals from the bandpass filter are mixed at the 1st

mixer circuit (Q2) with a 1st LO signal coming from the VCO

circuit to produce a 21.7 MHz 1st IF signal.The 1st IF signal

is applied to a crystal filter (FI2) to suppress out-of-band signals. The filtered 1st IF signal is applied to the IF amplifier

(Q1), then applied to the 2nd mixer circuit (IC2, pin 16).

4-1-4 2nd MIXER AND DEMODULATOR CIRCUITS

(RF UNIT)

The 2nd mixer circuit converts the 1st IF signal to a 2nd IF

signal. Adouble conversion superheterodyne system (which

converts receive signals twice) improves the image rejection

ratio and obtains stable receiver gain.

The 1st IF signal from the IF amplifier (Q1) is applied to the

2nd mixer section in the FM IF IC (IC2, pin 16), and is mixed

with the 2nd LO signal to be converted into a 450 kHz 2nd IF

signal.

The FM IF IC contains a 2nd mixer, quadrature detector,

noise amplifier and a limiter amplifier, etc. The PLLreference

oscillator (X1) is used for the 2nd LO signal via the PLL IC

(IC1, pins 1 1, 9), and is applied to pin 1 of the FM IF IC (IC2).

The mixed 2nd IF signal is output from pin 3 and passed

through the ceramic bandpass filter (FI3) to remove unwanted heterodyne frequencies. It is then amplified at the limiter

amplifier section (IC2, pin 5) and applied to the quadrature

detector section (IC2, pins 10, 11) to demodulate the 2nd IF

signal into AF signals.

4-1-5 AF CIRCUIT (RF AND MAIN UNITS)

AF signals from the FM IF IC (RF unit; IC2, pin 9) are passed

through the high-pass filter (RF unit; Q15, Q16) to remove

CTCSS signals then applied to the MAIN unit via J2 pin 10 as

the “VOL” signal.

The “VOL” signal (AF signals) from the RF unit is applied to

the [VOL] control (MAIN unit; R58) to control the audio level

via the volume mute switch (Q23). The level controlled AF

signals are applied to the AF power amplifier (IC9, pin 2) to

drive an internal speaker (SP1) via the [SP] jack (J1).

• 2nd IF AND DEMODULATOR CIRCUITS

Mixer

16

Limiter

amp.

2nd IF filter

450 kHz

PLL IC

IC1

X1

21.25 MHz

X2

(21.25 MHz)

RSSI

IC2 TA31136FN

14

1st IF (21.7 MHz)

from Q1

"SQL" signal to the CPU pin 59

11109

87 5 3

AF signal "AF"

R+3

1

9

11

Active

filter

FI3

Noise

detector

FM

detector

C74

C75

C76

C67

C77

C78

R51

R52

R53

R57

R58

Page 9

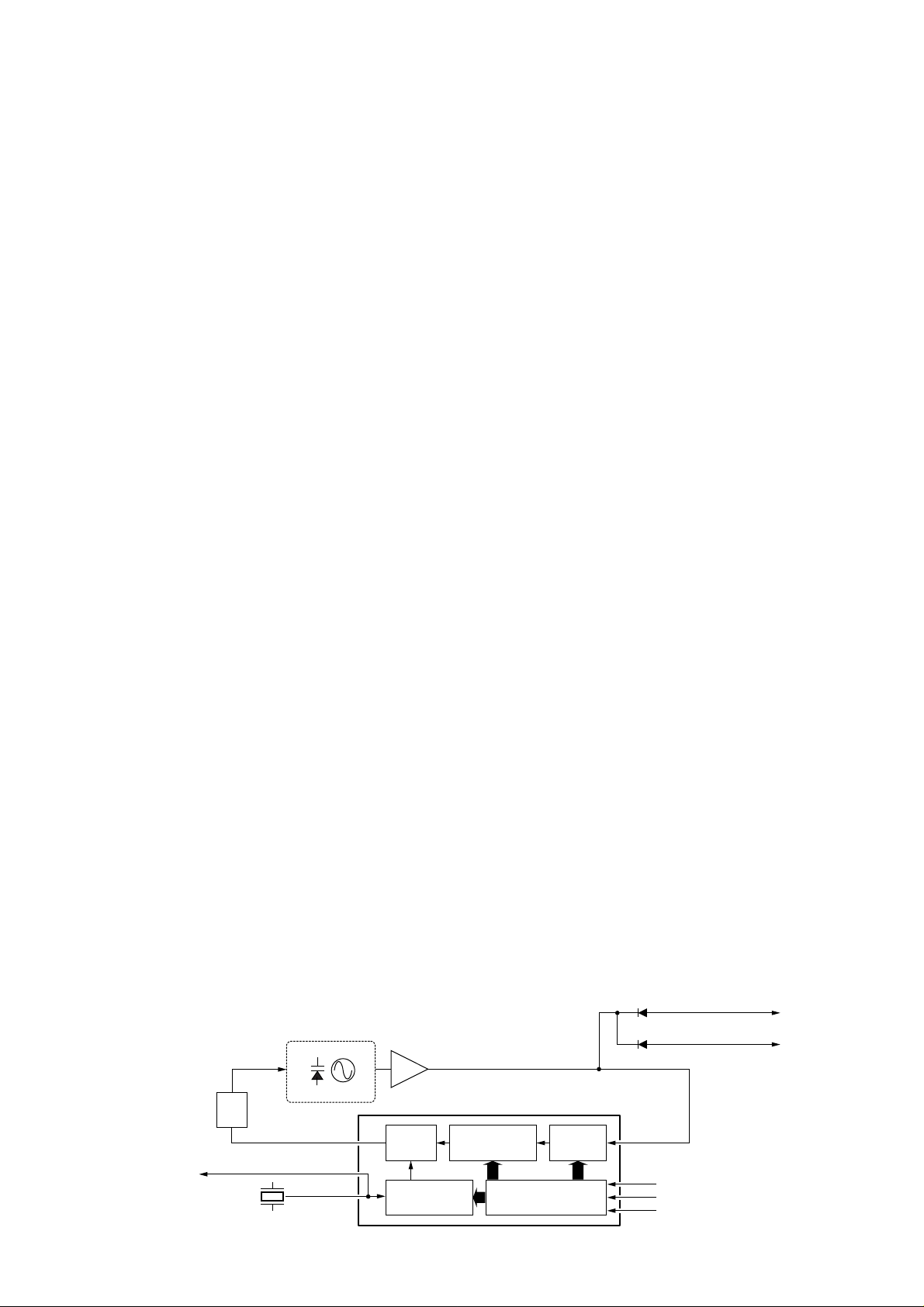

4 - 2

• PLL circuit

Shift register

Prescaler

Phase

detector

Loop

filter

Programmable

counter

Programmable

divider

X1

21.25 MHz

to the FM IF IC

(IC2, pin 1)

VCO

Buffer

Q7

6

7

8

STB

IC1 (PLL IC)

CK

DATA

to transmitter circuit

to 1st mixer circuit

D2

D1

9

11

14

16

Q6, D4, D5

4-1-6 SQUELCH CIRCUIT (RF AND MAIN UNITS)

(1) NOISE SQUELCH

The noise squelch circuit cuts out AF signals when no RF signals are received. By detecting noise components in the AF

signals, the squelch circuit switches the AF mute switch.

A portion of the AF signals from the FM IF IC (RF unit; IC2,

pin 9) are applied to the active filter section (RF unit; IC2, pin

8). The active filter section amplifies and filters noise components. The filtered signals are applied to the noise detector

section and output from pin 14 as the “SQL” signal.

The “SQL” signal from IC2 (pin 14) passes through J2 pin 9,

and is then applied to the CPU (MAIN unit; IC1, pin 59). The

CPU analyzes the noise condition and outputs the “RMUT”

and “AFON” signals to toggle the volume mute (MAIN unit;

Q23) and AF mute (MAIN unit; Q5, Q10, Q11) switches.

(2) TONE SQUELCH

The tone squelch circuit detects AF signals and opens the

squelch only when receiving a signal containing a matching

subaudible tone (CTCSS). When tone squelch is in use, and

a signal with a mismatched or no subaudible tone is

received, the tone squelch circuit mutes the AF signals even

when noise squelch is open.

A portion of the AF signals from the FM IF IC (RF unit; IC2,

pin 9) passes through the tone low-pass filter (MAIN unit; Q7,

Q12) to remove AF (voice) signals and is applied to the

CTCSS decoder inside the CPU (MAIN unit; IC1, pin 58) via

the “CTCIN” line to control the volume mute and AF mute

switches.

4-2 TRANSMITTER CIRCUITS

4-2-1 MICROPHONE AMPLIFIER CIRCUIT

(MAIN UNIT)

AF signals from the internal/external microphone are applied

to the microphone amplifier circuit (IC2b) via the microphone

switch (Q6). The amplified signals are passed through the

low-pass filter (IC2a) and applied to the modulation circuit in

the RF unit via J4 pin 5 as the MOD signal.

4-2-2 MODULATION CIRCUIT (RF UNIT)

The filtered audio signals from J4, pin 5 (On the MAIN unit)

are passed through the deviation adjustment pot (R50) then

applied to the modulation circuit (D4, D5) to modulate transmit signals at the VCO circuit (Q6).

The modulated signal is applied to the drive amplifier circuit.

4-2-3 DRIVE/POWER AMPLIFIER CIRCUITS

(RF UNIT)

The amplifier circuit amplifies the VCO oscillating signal to

the output power level.

The amplified transmit signal is passed through the antenna

switching circuit (D6) and low-pass filter, and is then applied

to the antenna.

The modulated transmit signal is amplified at the pre-drive

and drive amplifiers (Q8, Q201) after being amplified at the

buffer amplifier (Q7). The amplified signal is power amplified

at the power amplifier (Q202) to obtain 500 mW or

(IC–4008A) 10 mW (IC–4008MK2) of RF power.

The power amplified signal is then applied to the antenna via

the low-pass filter circuits.

4-3 PLL CIRCUITS (RF UNIT)

A PLL circuit provides stable oscillation of the transmit frequency and receive 1st LO frequency. The PLL output compares the phase of the divided VCO frequency to the reference frequency. The PLL output frequency is controlled by

the divided ratio (N-data) of a programmable divider.

The PLL circuit consists of the VCO circuit (Q6, D4, D5). An

oscillated signal from the VCO passes through the buffer

amplifier (Q7) is applied to the PLL IC (IC1, pin16) and is

prescaled in the PLL IC based on the divided ratio (N-data).

The reference signal is generated at the reference oscillator

(X1) and is also applied to the PLLIC. The PLLIC detects the

out-of-step phase using the reference frequency and outputs

it from pin 14. The output signal is passed through the loop

filter (R45, C68) and is then applied to the VCO circuit as the

lock voltage.

If the oscillated signal drifts, its phase changes from that of

the reference frequency, causing a lock voltage change to

compensate for the drift in the oscillated frequency.

Page 10

4 - 3

LINE

BATT

3V

+3V

R+3

T+3

DESCRIPTION

The voltage from the connected battery pack.

Common 3 V converted from the BATT line at

the 3V regulator circuit (IC6). The circuit outputs

the voltage regardless of the power ON/OFF

condition.

Common 3 V converted from the BATT line at

the +3V regulator circuit (Q25, D4).

Receive 3 V cotrolled by the R+3 regulator circuit

(Q18) using the “RXV” signal from CPU (IC1).

Transmit 3 V converted from the BATT line at the

T+3 regulator circuit (Q27, Q28, D5, etc.) using

the “TXV” signal coming from CPU (IC1).

Outputs data signals to the PLL IC (RF

unit; IC1).

Outputs strobe signals for the PLL IC

(RF unit; IC1).

Outputs control signal for the +3V regulator circuit (MAIN unit; Q25, D4).

Output port for the CTCSS signals.

Outputs control signal for the MIC

amplifier (IC2).

Low : While microphone amplifier is

ON.

Input port for the CTCSS decode signals.

Input port for squelch level signal.

Input ports for the control signal from

the external remote microphone.

Input port form the connected battery

pack for low battery indication.

Input port for the RSSI signal from the

FM IF IC (RF unit; IC2) to detect receiving signal strength level.

Outputs clock signal to the EEPROM

(IC3).

Outputs data signals to the EEPROM

(IC3).

Output port for power save function,

applied to VCO regurator circuit (RF

unit; Q13, Q14, D8, D9).

Outputs the R+3 regulator control signal (Q18).

Outputs the T+3 regulator control signal (Q27, Q28, D5, etc.).

Outputs control signal for LCD backlight.

Low : While LCD backlight is ON.

Outputs internal microphone control

signal.

High : While internal PTT switch is

pushed.

Outputs MIC mute signal for RING

function.

High : While RING signals are out-

put, etc.

51

52

53

54–56

57

58

59

60

61

62

73

74

75

76

77

78

79

80

PLLDA

PLLST

POWER

CTCO0–

CTCO2

TXMOD

CTCIN

SQLIN

REMIN

BATIN

SENIN

EEPCK

EEPDA

PSC

RXV

TXV

LAMPC

MICSW

MMUTE

Pin Port

Description

number name

Input port for the PTT switch from the

external mic jack (MAIN unit; J1).

Low : External PTT switch is ON.

Input port for the internal PTT switch.

Low : While PTT switch is pushed.

Input port for the [DOWN] switch.

Input port for the [UP] switch.

Input port for the [MODE] switch.

Input port for the POWER switch.

Low : While POWER switch is

pushed.

Input port for PLL unlock signal from

the PLL IC (RF unit; IC1).

Low : During unlock.

Outputs beep audio signal.

Outputs volume mute switch (Q23)

control signal.

High : While squelched

Outputs control signal for the AF amplifier regulator circuit (Q5, Q10, Q11).

High: When squelch is open.

Outputs clock signal to the PLL IC (RF

unit; IC1).

31

34

35

36

37

38

45

46

48

49

50

PTT2

PTT1

DOWN

UP

MODE

POWSW

UNLK

BEEP

RMUTE

AFON

PLLCK

Pin Port

Description

number name

4-4 POWER SUPPLY CIRCUITS

VOLTAGE LINE

4-5 PORT ALLOCATIONS

4-5-1 CPU (MAIN unit; IC1)

Page 11

5 - 1

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION

REQUIRED TEST EQUIPMENT

EQUIPMENT

DC power supply

RF power meter

(terminated type)

Frequency counter

FM deviation meter

DC voltmeter

GRADE AND RANGE

Output voltage : 4.5 V DC

Current capacity : 1 A or more

Measuring range : 1 mW–1 W

Frequency range : 300–600 MHz

Impedance : 50 Ω

SWR : Less than 1.2 : 1

Frequency range : 0.1–600 MHz

Frequency accuracy: ±1 ppm or better

Sensitivity : 100 mV or better

Frequency range : 30–600 MHz

Measuring range : 0 to ±10 kHz

Input impedance : 50 kΩ/V DC or better

EQUIPMENT

Audio generator

Standard signal

generator (SSG)

Oscilloscope

AC millivoltmeter

External speaker

Attenuator

GRADE AND RANGE

Frequency range : 300–3000 Hz

Measuring range : 1–500 mV

Frequency range : 0.1–600 MHz

Output level : 0.1 µV–32 mV

(–127 to –17 dBm)

Frequency range : DC–20 MHz

Measuring range : 0.01–10 V

Measuring range : 10 mV–10 V

Input impedance : 8 Ω

Capacity : 300 mW or more

Power attenuation : 30 or 40 dB

Capacity : 1 W or more

ENTERING THE ADJUSTMENT MODE

Turn the transceiver power OFF.

While connecting the “TEST” on the RF board to “GND”, then turn power ON.

(See location at page 5-3)

CONNECTIONS

CAUTION:

DO NOT transmit while SSG is

connected to the antenna connector.

FM deviation

meter

DC power supply

4.5 V /1.0 A

Standard signal

generator

–17 to –125 dBm

(32 mV to 0.1 µV)

RF power meter

Attenuator

50 Ω / 1–500 mW

30 dB or 40 dB

Frequency

counter

to the RF test port J1

–

+

Page 12

5 - 2

5-2 ADJUSTMENT

REFERENCE

FREQUENCY

OUTPUT

POWER

FM

DEVIATION

SQUELCH

ADJUSTMENT

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

POINT

UNIT LOCATION UNIT ADJUST

433.925000 MHz

9 mW [ITA/–1]

470 mW [CSA/–1]

±4.8 kHz

10 mV ±3 dB

Audio signal

disappears.

1

1

1

2

1

2

• Operating channel : Ch 35

• Transmitting

• Operating channel : Ch 35

• Transmitting

• Operating channel : Ch 01

• Connect an audio generator to the

[MIC] jack and set as:

1 kHz/100 mV rms

• Set an FM deviation meter as:

HPF : OFF

LPF : 20 kHz or 15 kHz

De-emphasis : OFF

Detector : (P–P)/2

• Set group No. : 01

• Transmitting

• Set group No. : OFF (– –)

• Set an audio generator output level

until the deviation is ±3.5 kHz.

• Transmitting

• Operating channel : Ch 35

• Connect an SSG to J1 on the RF unit

and set as:

Level : 0.14 µV*

(–124 dBm)

Modulation : OFF

• Receiving

• Set an SSG as :

Level : OFF

• Receiving

Top

panel

RF

RF

Front

panel

Loosely couple a frequency counter to the

antenna.

Connect an RF power

meter to the RF test

port J1.

Connect an FM deviation meter to the RF

test port J1.

Internal speaker

RF

RF

RF

Front

panel

C63

R206

R50

Verify

Push

and hold

[MODE]

and

[DOWN]

Verify

Page 13

5 - 3

RF

GND

J1

RF test por

R50

FM deviati

Reference frequency

adjustment

R206

Output power

adjustment

TEST

C63

ENTERING THE ADJUSTMENT MODE

q Turn the transceiver power OFF.

w While connecting the "TEST" to GND,

then turn power ON.

Page 14

SECTION 6 PARTS LIST

6 - 1

IC1 1140006881 S.IC µPD753036GK-524-BE9

IC2 1110002820 S.IC NJM2100M-T1

IC3 1140004450 S.IC X24C01AS-3.0T6

IC5 1110004710 S.IC S-80928ANMP-DDR-T2

IC6 1180001150 S.IC S-81230SG-QB-T1

IC9 1110002810 S.IC NJM2070M-T1

Q1 1590000720 S.TRANSISTOR DTA144EUA T106

Q2 1590001860 S.TRANSISTOR UN9215 (TX)

Q3 1590000800 S.TRANSISTOR UN5119 (TX)

Q5 1510000580 S.TRANSISTOR 2SA1362-GR (TE85R)

Q6 1560000840 S.FET 2SK1829 (TE85R)

Q7 1530002280 S.TRANSISTOR 2SC4081 T107 S

Q10 1530002280 S.TRANSISTOR 2SC4081 T107 S

Q11 1530003090 S.TRANSISTOR 2SC4213-B (TE85R)

Q12 1530002280 S.TRANSISTOR 2SC4081 T107 S

Q14 1590001330 S.TRANSISTOR DTA114EUAT106

Q18 1510000770 S.TRANSISTOR 2SA1586-GR (TE85R)

Q23 1590001390 S.FET 2SJ144-Y (TE85R)

Q25 1590002490 S.TRANSISTOR UMZ2N TR

Q27 1530002280 S.TRANSISTOR 2SC4081 T107 S

Q28 1520000200 S.TRANSISTOR 2SB798-T2 DK

Q29 1590000680 S.TRANSISTOR DTC114EUA T106

Q101 1590002630 S.TRANSISTOR UMZ1N TR

[CSA], [CSA-1] only

D2 1750000550 S.DIODE 1SS355 TE-17

D4 1750000550 S.DIODE 1SS355 TE-17

D5 1750000550 S.DIODE 1SS355 TE-17 [CSA], [CSA-1]

1790001250 S.DIODE MA2S111-(TX) [ITA], [ITA-1]

D101 1750000550 S.DIODE 1SS355 TE-17 [CSA], [CSA-1]

1790001250 S.DIODE MA2S111-(TX) [ITA], [ITA-1]

D303 1790001250 S.DIODE MA2S111-(TX)

[ITA], [ITA-1] only

X1 6050010450 S.XTAL CR-627 (5.8368 MHz)

R2 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ)

R4 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ)

R5 7030003810 S.RESISTOR ERJ3GEYJ 125 V (1.2 MΩ)

R6 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

R7 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

R9 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R10 7030003310 S.RESISTOR ERJ3GEYJ 820 V (82 Ω)

R12 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω)

R13 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R14 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R22 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R23 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R24 7030003820 S.RESISTOR ERJ3GEYJ 155 V (1.5 MΩ)

R25 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R26 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R27 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R30 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R31 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R32 7030003780 S.RESISTOR ERJ3GEYJ 684 V (680 kΩ)

R33 7030003540 S.RESISTOR ERJ3GEYJ 682 V (6.8 kΩ)

R34 7030003540 S.RESISTOR ERJ3GEYJ 682 V (6.8 kΩ)

R35 7030003530 S.RESISTOR ERJ3GEYJ 562 V (5.6 kΩ)

R36 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R37 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R38 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R39 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ)

R40 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R41 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R42 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ)

R43 7030003650 S.RESISTOR ERJ3GEYJ 563 V (56 kΩ)

R45 7030003840 S.RESISTOR ERJ3GEYJ 225 V (2.2 MΩ)

R46 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R49 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R50 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R51 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ)

REF ORDER

DESCRIPTION

NO. NO.

R52 7030003740 S.RESISTOR ERJ3GEYJ 334 V (330 kΩ)

R53 7030003820 S.RESISTOR ERJ3GEYJ 155 V (1.5 MΩ)

R54 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

R55 7030003330 S.RESISTOR ERJ3GEYJ 121 V (120 Ω)

R56 7030004050 S.RESISTOR ERJ3GEYJ 1R0 V (1 Ω)

R57 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R58 7210001970 VARIABLE RV-244 (RK0971110) 10KA

R60 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R61 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R62 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R63 7030003530 S.RESISTOR ERJ3GEYJ 562 V (5.6 kΩ)

R64 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R65 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R66 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R67 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R68 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R69 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R70 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R71 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R72 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R74 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R76 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R77 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R78 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R79 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R80 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R81 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R86 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R87 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R88 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R89 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R90 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R94 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R95 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R96 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R97 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R98 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R99 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R100 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R101 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R102 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R103 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R105 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R106 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R108 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R110 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R112 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

[CSA], [CSA-1]

7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

[ITA], [ITA-1]

R114 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

[ITA], [ITA-1]

7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

[CSA], [CSA-1]

R115 7030003410 S.RESISTOR ERJ3GEYJ 561 V (560 Ω)

[CSA], [CSA-1]

R118 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R119 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

[CSA], [CSA-1] only

R200 7030003840 S.RESISTOR ERJ3GEYJ 225 V (2.2 MΩ)

[CSA], [CSA-1] only

R201 7030003370 S.RESISTOR ERJ3GEYJ 271 V (270 Ω)

[CSA], [CSA-1] only

R202 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R301 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

[ITA], [ITA-1] only

R302 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

[ITA], [ITA-1] only

C1 4030009980 S.CERAMIC C1608 JB 1H 152K-T-A

C3 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C4 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C5 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C6 4030008680 S.CERAMIC C2012 JF 1C 105Z-T-A

C7 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

REF ORDER

DESCRIPTION

NO. NO.

S.=Surface mount

[MAIN UNIT]

[MAIN UNIT]

Page 15

6 - 2

C8 4510004630 S.ELECTROLYTIC ECEV1CA100SR

C9 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C10 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C11 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C15 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C17 4550006880 S.TANTALUM TEMSVD2 0J 157M-12R

C18 4510004630 S.ELECTROLYTIC ECEV1CA100SR

C20 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C21 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C24 4030008900 S.CERAMIC C1608 JB 1C 333K-T-A

C25 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C26 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C27 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C28 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C29 4030011280 S.CERAMIC C1608 CH 1H 271J-T-A

C31 4030008880 S.CERAMIC C1608 JB 1C 223K-T-A

C32 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C34 4030006880 S.CERAMIC C1608 JB 1H 472K-T-A

C35 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C36 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C40 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C42 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C44 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C45 4030009650 S.CERAMIC C1608 CH 1H 240J-T-A

C46 4030009650 S.CERAMIC C1608 CH 1H 240J-T-A

C47 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C48 4510005430 S.ELECTROLYTIC ECEV0JA220SR

C49 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C50 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C51 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C52 4510005860 S.ELECTROLYTIC ECEV1HA2R2SR

C53 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C54 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C55 4510005870 S.ELECTROLYTIC ECEV1HA3R3SR

C56 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C57 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C59 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C60 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C61 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C62 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C63 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C64 4510005430 S.ELECTROLYTIC ECEV0JA220SR

C65 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C67 4030009590 S.CERAMIC C2012 JF 1C 225Z-T-A

C71 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C72 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C73 4030008650 S.CERAMIC C1608 JB 1H 332K-T-A

C74 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C75 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C79 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C80 4510005900 S.ELECTROLYTIC ECEV0GA101SR

C81 4030008900 S.CERAMIC C1608 JB 1C 333K-T-A

C82 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C83 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C85 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C86 4030009590 S.CERAMIC C2012 JF 1C 225Z-T-A

C87 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C88 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C89 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C90 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C91 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C92 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C93 4030010760 S.CERAMIC C1608 CH 1H 331J-T-A

C94 4030010760 S.CERAMIC C1608 CH 1H 331J-T-A

C95 4030010760 S.CERAMIC C1608 CH 1H 331J-T-A

C96 4030010760 S.CERAMIC C1608 CH 1H 331J-T-A

C97 4030010760 S.CERAMIC C1608 CH 1H 331J-T-A

C98 4030010760 S.CERAMIC C1608 CH 1H 331J-T-A

J1 6450000130 CONNECTOR HSJ1102-01-540

J3 6450001060 CONNECTOR HSJ1493-01-010

J4 6510017950 S.CONNECTOR 4-175638-4

DS1 5010000120 S.LED LN1371G-(TR)

DS2 5030001580 LCD LD-BU10185J (E-10185-1)

MC1 7700002160 MICROPHON KUC3523-040245

S1 2260001900 SWITCH SW-149

REF ORDER

DESCRIPTION

NO. NO.

S.=Surface mount

[MAIN UNIT]

W1 7030003860 S.JUMPER ERJ3GE JPW V

W3 7030003860 S.JUMPER ERJ3GE JPW V

W4 7030003860 S.JUMPER ERJ3GE JPW V

W5 9001502002 WIRE 72/98/030/X98/X98

W6 7120000470 JUMPER ERDS2T0

W7 7030003860 S.JUMPER ERJ3GE JPW V

EP1 8930045510 LCD CONTACT SRCN-2045-SP-N-W

EP2 0910050341 PCB B 5161A [ITA], [ITA-1]

0910050792 PCB B 5109B [CSA], [CSA-1]

IC1 1110004150 S.IC TB31202FN (ER)

IC2 1110003200 S.IC TA31136FN (EL)

Q1 1530002600 S.TRANSISTOR 2SC4215-O (TE85R)

Q2 1530002920 S.TRANSISTOR 2SC4226-T2 R25

Q3 1530003620 S.TRANSISTOR 2SC5194-T1

Q6 1530003320 S.TRANSISTOR 2SC5108-Y (TE85R)

Q7 1530003320 S.TRANSISTOR 2SC5108-Y (TE85R)

Q8 1530002940 S.TRANSISTOR 2SC4228-T2 R44

Q12 1530003260 S.TRANSISTOR 2SC5006-T1

Q13 1530002280 S.TRANSISTOR 2SC4081 T107 S

Q14 1510000770 S.TRANSISTOR 2SA1586-GR (TE85R)

Q15 1530002280 S.TRANSISTOR 2SC4081 T107 S

Q16 1530002280 S.TRANSISTOR 2SC4081 T107 S

Q201 1530000372 S.TRANSISTOR 2SC3356 R24-T2B

Q202 1590002600 S.FET MRF9745 T1

D1 1790000620 S.DIODE MA77 (TX)

D2 1790000620 S.DIODE MA77 (TX)

D4 1720000640 S.VARICAP 1SV284 (TPH3)

D5 1720000640 S.VARICAP 1SV284 (TPH3)

D7 1790001260 S.DIODE MA2S077-(TX)

D8 1750000550 S.DIODE 1SS355 TE-17

D9 1750000550 S.DIODE 1SS355 TE-17

D101 1790001260 S.DIODE MA2S077-(TX)

D102 1790001260 S.DIODE MA2S077-(TX)

D103 1790001240 S.DIODE MA2S728-(TX)

FI1 2040001330 S.SAW NSVA468 (433.92MHZ)

FI2 2010002330 MONOLITH FL-298 (21.700 MHz)

FI3 2020001270 CERAMIC CFWM450E

X1 6050010480 S.XTAL CR-633 (21.250 MHz)

X2 6070000210 S.DISCRIMINATORCDBCA450CX24

L1 6200002240 S.COIL ELJFC 2R2K-F

L3 6200004380 S.COIL LL1608-F18NK

L4 6200005670 S.COIL ELJRE 12NG-F

L5 6200008270 S.COIL 0.26-1.0-5TL17N

L6 6200008270 S.COIL 0.26-1.0-5TL17N

L10 6200005700 S.COIL ELJRE 22NG-F

L11 6200003640 S.COIL MLF1608K 100K-T

L12 6200003640 S.COIL MLF1608K 100K-T

L13 6200002350 S.COIL LQN 1A27NJ04

L14 6200005720 S.COIL ELJRE 33NG-F

L15 6200007000 S.COIL ELJRE 82NG-F

L19 6200005710 S.COIL ELJRE 27NG-F

L21 6200005700 S.COIL ELJRE 22NG-F

L23 6200008430 S.COIL 0.20-1.0-4TL15N

L25 6200002190 S.COIL MLF2012A4R7K-T

L105 6200007000 S.COIL ELJRE 82NG-F

L201 6200005700 S.COIL ELJRE 22NG-F

L202 6200005720 S.COIL ELJRE 33NG-F

L203 6200008440 S.COIL LQN21A 8N2D04

L204 6200008440 S.COIL LQN21A 8N2D04

L205 6200006670 S.COIL ELJRE 68NG-F

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

REF ORDER

DESCRIPTION

NO. NO.

[RF BOARD]

Page 16

6 - 3

L206 6200005690 S.COIL ELJRE 18NG-F

L207 6200005690 S.COIL ELJRE 18NG-F

L208 6200003640 S.COIL MLF1608K 100K-T

R1 7030003430 S.RESISTOR ERJ3GEYJ 821 V (820 Ω)

R2 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ)

R3 7030003470 S.RESISTOR ERJ3GEYJ 182 V (1.8 kΩ)

R4 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

R5 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R6 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R7 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R10 7030003550 S.RESISTOR ERJ3GEYJ 822 V (8.2 kΩ)

R12 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R16 7030003260 S.RESISTOR ERJ3GEYJ 330 V (33 Ω)

R19 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R25 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R27 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R29 7030003350 S.RESISTOR ERJ3GEYJ 181 V (180 Ω)

R30 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R31 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R32 7030003540 S.RESISTOR ERJ3GEYJ 682 V (6.8 kΩ)

R33 7030003550 S.RESISTOR ERJ3GEYJ 822 V (8.2 kΩ)

R34 7030003420 S.RESISTOR ERJ3GEYJ 681 V (680 Ω)

R35 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R36 7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω)

R37 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R45 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R50 7310003630 S.TRIMMER EVM-1XSX50 BQ4 (473)

R51 7030003770 S.RESISTOR ERJ3GEYJ 564 V (560 kΩ)

R52 7030003410 S.RESISTOR ERJ3GEYJ 561 V (560 Ω)

R53 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R54 7510000930 S.THERMISTOR NTCCF2012 3NH 103KC-T

R55 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R56 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R57 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

R58 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R59 7030003470 S.RESISTOR ERJ3GEYJ 182 V (1.8 kΩ)

R60 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R61 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R62 7030003230 S.RESISTOR ERJ3GEYJ 180 V (18 Ω)

R64 7030003650 S.RESISTOR ERJ3GEYJ 563 V (56 kΩ)

R65 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R66 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R67 7030003780 S.RESISTOR ERJ3GEYJ 684 V (680 kΩ)

R68 7030003750 S.RESISTOR ERJ3GEYJ 394 V (390 kΩ)

R69 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ)

R70 7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ)

R71 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R72 7030003550 S.RESISTOR ERJ3GEYJ 822 V (8.2 kΩ)

R73 7030003780 S.RESISTOR ERJ3GEYJ 684 V (680 kΩ)

R74 7030003750 S.RESISTOR ERJ3GEYJ 394 V (390 kΩ)

R75 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R76 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ)

R83 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R86 7030003300 S.RESISTOR ERJ3GEYJ 680 V (68 Ω)

R88 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R93 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω)

R202 7030003540 S.RESISTOR ERJ3GEYJ 682 V (6.8 kΩ)

R205 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

[ITA], [ITA-1]

7510001180 S.THERMISTOR NTCCM1608 3NH 221KC

[CSA], [CSA-1]

R206 7310003610 S.TRIMMER EVM-1XSX50 B14 (103)

R207 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R208 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R209 7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω)

R210 7030003350 S.RESISTOR ERJ3GEYJ 181 V (180 Ω)

R211 7030003250 S.RESISTOR ERJ3GEYJ 270 V (27 Ω)

R212 7030003350 S.RESISTOR ERJ3GEYJ 181 V (180 Ω)

R213 7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω)

R301 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

[CSA], [CSA-1]

7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

[ITA], [ITA-1]

C1 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C2 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C3 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C4 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C5 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

REF ORDER

DESCRIPTION

NO. NO.

S.=Surface mount

C6 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C7 4030007050 S.CERAMIC C1608 CH 1H 220J-T-A

C8 4030006970 S.CERAMIC C1608 CH 1H 060D-T-A

C9 4030010780 S.CERAMIC C1608 CH 1H 1R5C-T-A

C10 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C11 4030009470 S.CERAMIC C1608 CH 1H R75C-T-A

C12 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C13 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C15 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C16 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C17 4030008880 S.CERAMIC C1608 JB 1C 223K-T-A

C18 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C20 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C21 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C23 4030006940 S.CERAMIC C1608 CH 1H 030C-T-A

C26 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C28 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C30 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C31 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C32 4030006970 S.CERAMIC C1608 CH 1H 060D-T-A

C35 4030006910 S.CERAMIC C1608 CH 1H 0R5C-T-A

C36 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C42 4030007070 S.CERAMIC C1608 CH 1H 330J-T-A

C43 4030007030 S.CERAMIC C1608 CH 1H 150J-T-A

C44 4030007060 S.CERAMIC C1608 CH 1H 270J-T-A

C45 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C46 4030007050 S.CERAMIC C1608 CH 1H 220J-T-A

C48 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C50 4030007020 S.CERAMIC C1608 CH 1H 120J-T-A

C51 4030007020 S.CERAMIC C1608 CH 1H 120J-T-A

C52 4030006930 S.CERAMIC C1608 CH 1H 020C-T-A

C53 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T-A

C54 4030009350 S.CERAMIC C1608 CH 1H 3R5B-T-A

C55 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C56 4030006910 S.CERAMIC C1608 CH 1H 0R5C-T-A

C57 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T-A

C60 4510005430 S.ELECTROLYTIC ECEV0JA220SR

C61 4030006960 S.CERAMIC C1608 CH 1H 050C-T-A

C62 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C63 4610002150 S.TRIMMER CTZ3S-10A-W1-AF

C64 4030009660 S.CERAMIC C1608 JF 1C 224Z-T-A

C65 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C67 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C68 4550006150 S.TANTALUM ECST1CY105R

C69 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C70 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C72 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C73 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C74 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C75 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C76 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C77 4030007050 S.CERAMIC C1608 CH 1H 220J-T-A

C78 4030007110 S.CERAMIC C1608 CH 1H 680J-T-A

C79 4510004630 S.ELECTROLYTIC ECEV1CA100SR

C80 4030009660 S.CERAMIC C1608 JF 1C 224Z-T-A

C81 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C82 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C83 4030008680 S.CERAMIC C2012 JF 1C 105Z-T-A

C84 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C85 4510004650 S.ELECTROLYTIC ECEV1EA4R7SR

C86 4030011810 S.CERAMIC C1608 JB 1A 224K-T-N

C87 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C88 4510004650 S.ELECTROLYTIC ECEV1EA4R7SR

C89 4030009880 S.CERAMIC C1608 JB 1H 682K-T-A

C90 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C91 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C92 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C93 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C95 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C96 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C100 4030007050 S.CERAMIC C1608 CH 1H 220J-T-A

C102 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T-A

C201 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C202 4030007050 S.CERAMIC C1608 CH 1H 220J-T-A

C203 4030007050 S.CERAMIC C1608 CH 1H 220J-T-A

C204 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C205 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C206 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C207 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C208 4030007000 S.CERAMIC C1608 CH 1H 090D-T-A

C209 4030006970 S.CERAMIC C1608 CH 1H 060D-T-A

C210 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

REF ORDER

DESCRIPTION

NO. NO.

[RF UNIT]

[RF UNIT]

Page 17

6 - 4

C211 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

J1 6910007660 CONNECTOR IMSA-9210B-1-02T

J2 6510018170 S.CONNECTOR 4-175643-4

W4 7030003860 S.JUMPER ERJ3GE JPW V

W5 7030003860 S.JUMPER ERJ3GE JPW V

W6 7030003860 S.JUMPER ERJ3GE JPW V

W8 7030003860 S.JUMPER ERJ3GE JPW V

W201 7030003860 S.JUMPER ERJ3GE JPW V

W202 7030003860 S.JUMPER ERJ3GE JPW V

EP1 0910050351 PCB B 5162A [ITA], [ITA-1]

0910050781 PCB B 5162A [CSA], [CSA-1]

REF ORDER

DESCRIPTION

NO. NO.

[RF UNIT]

S.=Surface mount

Page 18

SECTION 7 MECHANICAL PARTS AND DISASSEMBLY

7 - 1

Screw abbreviations A, B0, BT: Self-tapping

PH: Pan head

FH: Flat head

BiH: Bind head

NI: Nickel

SUS: Stainless

ZK: Black

SP1 2510000960 Speaker K036NA500-26A27 1

EP1 3310002090 Antenna 2045ANT 1

MP1 8210015181 Panel 2045 Front Panel-1 [ITA], [CSA] 1

8210016101 Panel 2045 Front Panel (A)-1 1

[ITA-1], [CSA-1]

MP2 8210015191 Panel 2045 Rear Panel-1 [ITA], [CSA] 1

8210016111 Panel 2045 Rear Panel (A)-1 1

[ITA-1], [CSA-1]

MP3 8110006400 Cover 2045 Rear Cover [ITA], [CSA] 1

8110006720 Cover 2045 Rear Cover (A) [ITA-1], [CSA-1] 1

MP4 8110006410 Cover 2045 Lock Cover [ITA], [CSA] 1

8110006730 Cover 2045 Lock Cover (A) [ITA-1], [CSA-1] 1

MP5 8310042680 Plate 2045 Window Plate 1

MP7 8210015220 Panel 2045 Reflector 1

MP8 8610010570 Knob N-265 1

MP9 8930045192 Seal 2045 Top Seal-2 1

MP10 8930045230 Key 2045 4-Key 1

MP11 8930045200 Button 2045 PTT Button 1

MP12 8930046990 Seal 2045 Main Seal (A) 1

MP13 8930045220 Seal 2045 BATT Seal 1

MP14 8930046280 Terminal 2045 ANT Termainal 1

MP20 8830001370 Screw 2045 VR Nut 1

MP22 8930045750 Seal O-ring (X) 1

MP23 8830000110 Screw Nut M4 1

MP24 8810009560 Screw PH BO 2x6 ZK (BT) 4

MP25 8810008640 Screw FH BO 2x4 NI-ZU (BT) 2

MP30 8810008990 Screw PH BO 2x10 ZK (BT) 1

REF. NO. ORDER NO.

DESCRIPTION

QTY.

7-1 CABINET PARTS

[CHASSIS PARTS]

REF. NO. ORDER NO.

DESCRIPTION

QTY.

[MAIN UNIT]

DS2 5030001580 LCD LD-BU10185J 1

EP1 8930045510 LCD contact SRCN-2045-SP-N-W 1

MP1 8930045331 2045 Belt clip-1 1

MP2 8820001040 2045 Screw 1

REF. NO. ORDER NO.

DESCRIPTION

QTY.

REF. NO. ORDER NO.

DESCRIPTION

QTY.

[RF UNIT]

MP1 8510011570 Case 2045 VCO Case 1

7-2 ACCESSORIES

MP1 MP2

Page 19

7 - 2

UNIT abbreviation (C): CHASSIS PARTS, (RF): RF UNIT, (M): MAIN UNIT

MP1 (C)

SP1 (C)

MP10 (C)

MP12 (C)

EP1 (M)

DS2 (M)

MP7 (C)

MP5 (C)

MAIN unit

MP20 (C)

MP25 (C)

MP14 (C)

MP23 (C)

MP11 (C)

MP13 (C)

MP4 (C)

MP2 (C)

MP25 (C)

MP9 (C)

MP8 (C)

RF unit

MP24 (C)

MP30 (C)

MP24 (C)

MP22 (C)

EP1 (C)

MP3 (C)

MP1 (RF)

Page 20

SECTION 8 SEMI-CONDUCTOR INFORMATION

8 - 1

• DIODES

• TRANSISTOR AND FET’S

2SA1362 GR

(Symbol: AEG)

2SC4213 B

(Symbol: AB)

2SC5108 Y

(Symbol: MC)

DTA114 EU

(Symbol: 16)

UN5119

(Symbol: 6K)

UN9215

(Symbol: 8E)

DTC114 EU

(Symbol: 14)

MRF9745

(Symbol: M745)

UMZ1N

(Symbol: Z1)

UMZ2N

(Symbol: Z2)

2SC5194

(Symbol: T88)

2SJ144 Y

(Symbol: VX)

2SK1829

(Symbol: K1)

2SC4215 O

(Symbol: QO)

2SC4226 R25

(Symbol: R25)

2SC4228 R44

(Symbol: R44)

2SA1586 GR

(Symbol: SG)

2SB798 DK

(Symbol: DK)

2SC3356 R24

(Symbol: R24)

2SC4081 S

(Symbol: BS)

B

E

C

DTA144 EU

(Symbol: 16)

B

E

C

B

E

C

E

C

B

E

C

B

B

E

C

S

D

G

B

E

C

E

C

B

E

C

B

E

C

B

E

C

B

E

C

B

E

E1

B1

C2

C1

B2

E2

E1

B1

B2

C1

E2

C2

B

E

C

B

E

C

B

C

E

C

E

C

B

E

1SS355

(Symbol: A)

MA2S11 1

(Symbol: A)

1SV284

(Symbol: TL )

MA77

(Symbol: 4B)

MA2S077

(Symbol: S)

AK

MA2S728

(Symbol: B)

Page 21

SECTION 9 BOARD LAYOUTS

9-1 MAIN UNIT

•

TOP VIEW (IC-4008A)

9 - 1

C20

R98

R74

R76

C53

C60

IC5

C55

C88

R78

W7

C80

R42

R12

R46

R50

C5

R31

R118

C3

R9

R110

C25

C7

C79

C4

Q6

R13

Q3

R10

R202

C35

C34

R45

R36

C36

C31

R43

R37

R41

C32

R38

C90

C8

Q7

MC1

C64

Q25

D4

C62

C65

C89

R77

C67

R80

Q18

C17

C52

C18

C49

C48

C81

R23

C63

C97

C96

R26

Q11

Q14

Q27

Q101

D5

Q28

DS2

R114

R200

R119

R115

R201

C42

C9

C75

R89

C71

C74

R90

R49

D101

D2

DS1

C95 R22

R27

C50

W3

R24

R25

R55

R56

C15R61

C57

IC6

Page 22

9 - 2

•

BOTTOM VIEW (IC-4008A)

R58

R88

R54

Q10

C21

C47

C44

C72

R87

C59

R106

C82

R112

C46

C87

R103

C51

R62

C92

C94

R97

R63

C45

R79

C86

R68

R69

IC3

Q23

R86

IC9

J4

J1

J3

S1

X1

Q5

C6

C29

R6

R7

R5

R4

R40

R105

R32

R34

C26

C40

C27

C11

R33

R2

R108

W1

W4

R60

Q1

C73

C83

R51

R52

C93

C24

R53

C98

R39

R102

Q2

C28

C91

C10

R14

R95

R35

Q12

Q29

R64

R99

R100

R101

IC1

R65

R66

R81

R72

C56

C54

R94

C61

R96

R57

R70

R71

R67

C1

C85

IC2

R30

PSC

BATT

MOD

T+3

VOL

R+3

GND

UNLK

CK

DATA

STB

SQL

SENS

AF

131

214

J4

to RF unit J2

Page 23

9 - 3

C57

IC6

C20

Q14

IC5

C63

Q27

Q11

R26

R49

W3

C74

D303

D5

DS2

C55

C17

C52

C18

C48

C49

R23

R114

R302

R89

C9

C42

C75R90

C71

Q28

D101

C97

R74

R76

R98

C53

C60

C81

C96

D2

DS1

C95

R61

C15

R22

R27

C50

R24

R25

R56

R55

C88

R78

Q18

Q25

D4

W7

C80

C64

C67

C62

R42

R43

C90

MC1

R37

R46

R13

C79

C4

R50

C5

C7

C8

Q7

Q3

Q6

R12

C34

R45

R36

C36

C31

R202

R10

R118

R31

R110

C25

R9

C3

C35

R41

C32

R38

C65

R77

C89

R80

Page 24

9 - 4

R58

IC9

C6

IC2

C29

C73

R39

R99

R100

R101

R35

C91

C10

R14

R64

W1

W4

Q1

R60

R108

R2

R4

R5

Q2

Q12

Q29

C28

R102

R40

R32

R105

C26

C27

C40

R95

C11

R34

R33

R65

R6

R7

C24

R53

R66

C1

C85

R30

C83

R51

R52

C93

C98

Q10

C59 C72

C82

J1

S1

J3

Q23

R87

R106

R301

R112

R81

R72

C61

C56

C54

R94

C46

R63

C45

R79

C87

X1

C86

IC1

R103

R57

R96

R70

R71

R67

C92

C94

C51

R97

R62

R69

R68

IC3

J4

Q5

Q44

R54

R88

C21

R86

C47

PSC

BATT

MOD

T+3

VOL

R+3

GND

UNLK

CK

DATA

STB

SQL

SENS

AF

131

214

J4

to RF unit J2

Page 25

9 - 5

9-2 RF UNIT

•

TOP VIEW

R69

R67

R71

R66

C89

R68

C96

L6

L204

L203

D103

L5

L23

C90

C36

C4

R12

C70

C23

R86

Q14

Q13

D9

D8

C81 C82

C48

C43

C86

IC1

R64

R65

R32

R27

C13

R60

R19

R4

C28

C3

L25

C67

R58

Q2

J2

R5

C46

L1

C11

C72

R209

R213

R202

W202

W201

L201

C201

C203

C204

L202

C26

Q201

Q202

R205

R93

C87

C62

C61

C18 C17

R10

R45

W4

W6

L15

L208

W5

C68

R62

C206

C202

C65

C208

C9

C30

L205

C44

C31

D7

C207

C12

C10

C8

L10

Q15

GND

R+3

VOL

T+3

MOD

BATT

PSC

AF

SENS

SQL

STB

DATA

CK

UNLK

113

14 2

J2

to MAIN unit J4

Page 26

9 - 6

•

BOTTOM VIEW

C79

C83

X1

C63

R52

R88

C15

C16

C69

C55

R36

C57

L14

C64

R34

C52

R31

C53

Q6

L13

R54

C50

R30

R29

C20

L11

D4

D5

R35

R33

L12

Q7

Q12

C84

C56

C51

R210

Q8

C60

FI1

FI2

W8

Q1

R3

R2

FI3

J1

R50

R206

C88

C85

R211

C211

L207

L105

L19

C102

R212

C21

C42

C100

R208

R6

C35

C45

R53

R55R61

L21

R37

R301

R7

C209

C210

R75

R76

R74

C93

C92

C91

Q16

R83

L3

C6

D102

D101

R207

Q3

C32

R16

C5

R70

R72

R73

C95

C205

R25

L4

L206

C7

C75

C76

R56

R54

X2

D2

D1

R59

IC2

C1

C78

C77

R1

R57

C2

C80C74

R51 C73

Page 27

SECTION 10 BLOCK DIAGRAM

10 - 1

CTCIN

D/A

REMIN

PTT2

MICSW

RMUT

AFON

RXV

TXV

POWER

LCD

DS2

VOLT

SENS

RESET

IC5

X2

CDBCA450CX24

(450 kHz)

FI3: CFWM450E

CERAMIC

BPF

(450 kHz)

FMDET S DET

IF

AMP

NOISE

DET

IC2

TA31136FN

2SC4215

Q13: 2SC4081

Q14: 2SA1586

D8 : 1SS355

D9 : 1SS355

FL-298

Q6: 2SC5108

D4,D5: 1SV284

X1

CR-632

(21.25 MHz)

2nd.Lo: 21.25 MHz

2nd MIX

IC1

TB31202FN

UNLOCK

DATA,CK,STB

Q1

FI2

ATT

Q7

2SC5108

R50

MOD LEVEL SET

VCO

BUFF

LO

SW

D1: MA77

D2: MA77

TX/RX

SW

2SC3356

PWR

AMP

DRIVE

AMP

MA2S728

PRE

DRIVE

D7: MA2S077

D101: MA2S077

D102: MA2S077

POWER SET

R206

IC3

X24C01AS

EEP

ROM

X1

CR-627

5.8368 MHz

POWER

MODE

UP

DOWN

PTT

S1

CPU

AF

VOL

MMUT

TXMOD

Q7

2SC4081

TONE

LPF

TONE

LPF

Q12

2SC4081

MODSW

Q1

DTA144EU

LPF IDC

+3V

IC2A

NJM2100M

Q6

2SK1829

MIC

MUTE

IC2B

NJM2100M

Q23

2SJ144

R58

AF VOL

VOL

MUTE

MIC1

KUC3523

PTT

SENSE

MIC

SW

MIC

Q14

DTA114EU

DS1

LN1371G

S-80928ANMP

LED

DRV

R+3

CURRENT

AMP

R+3 T+3

+3V

CURRENT

AMP

Q25: UMZ2N

D4: 1SS355

+3V TO LOGIC

+3

REG

IC6

S-81230SG

Q18

2SA1586

Q27 : 2SC4081

Q28 : 2SB798

Q101: UMZ1N

D5: 1SS355

D101: 1SS355

T+3

CURRENT

AMP

D2 1SS355

PROTECTOR

Q29: DTC114EU

Q2: UN9215

Q3: UN5119

AF

MUTE

BATT

BATTERY

J3 SP JACK

COMON LINE

TX LINE

RX LINE

DATA BUS LINE

J1 MIC JACK

SP1

AF

AMP

IC9

NJM2070M

Q5 : 2SA1362

Q10: 2SC4081

Q11: 2SC4213

Q2

2SC4226

Q3: 2SC5194

RF

AMP

ANT

SW

HPF LPF

ANT

CHASSIS UNT

Q15: 2SC4081

Q16: 2SC4081

VCO

REG

PLL

IC

AF FIL

1st.IF: 21.7 MHz

1st.LO: 411.375-413.075MHz

TX/RX: 433.075-434.775MHz

TX: 433.075-434.775MHz

1st MIX

FI1: NSVA468

SHIFT

Q12

2SC5108

Q202: MRF9745

D103 Q201

Q8

2SC4228

SQL

SENS

PSC

LOOP

FIL

IF

AMP

XTAL

BPF

BPF

CHASSIS UNIT

RF UNIT

MAIN UNIT

IC1

µPD753036GK

[CSA/-1]

Q27 : 2SC4081

Q28 : 2SB798

D5: MA2S111

D101: MA2S111

D303: MA2S111

[ITA/-1]

Page 28

SECTION 11 VOLTAGE DIAGRAM

11 - 1

11-1 MAIN UNIT

LON: 0

LOF: 3.02

LON: 2.82

LOF: 0

C: 3.02

T: 3.04

R: 2.40

C: 3.82

C: 3.10

C: 1.65

T: 0

R: 0.86

C: 1.95

T: 0

R: 2.97

C: 3.12

T: 0

R: 3.02

C: 3.10

T: 1.58

R: 0

T: 3.05

R: 0

T: 1.46

R: 0

C: 0

C: 3.12

T: 1.48

R: 0

T: 1.45

R: 0

C: 2.50

C: 3.13

T,SC: 0.49

SO: 0.61

T: 0

SO: 2.95

SC: 0

T: 3.94

SO: 3.79

SC: 3.98

T: 0

SO: 2.33

SC: 0

T: 0

SC: 0

SO: 4.50

T,SC: 0.43

SO: 1.93

T: 1.07

R: 0

T: 3.70

R: 4.00

T: 0.43

R: 0

T: 0.50

R: 0

T: 2.77

SO: 0

SC: 2.77

T: 0

R: 3.12

T: 3.00

R: 0

T: 2.75

R: 0

T: 1.60

R: 0

C: 3.02

[ITA/-1]

T: 2.68

R: 0

[CSA/-1]

T: 1.56

R: 0

[ITA/-1]

T: 3.70

R: 0

[CSA/-1]

W4

W1

R101

100 k

R102

100 k

R98

100 k

R60

100 k

R99

100 k

R100

100 k

S1

SW-149

C75

0.001

R68

18 k

R69

18 k

C53

0.1

NC

1

NC

2

NC

3

VSS4SDA

5

SCL

6

NC

7

VCC

8

IC3

X24C01AS

C45

24 P

X1

CR-627

R72

1 M

C46

24 P

R61

47

Q14

DTA114EU

DS1

LN1371G

R96

100 k

R90

1 k

C92

470 P

R67 18 k

R71 33 k

R70 68 k

R89

1 k

R97

100 k

C74

0.001

REMIN

EEPDA

RXV

EEPCK

PSC

RESET

TXV

LAMPC

MICSW

MMUTE

AN3

61

P73/KR7

80

AN4

62

AN5

63

AVSS

64

AVREF

65

VDD

66

XT1

67

XT2

68

IC

69

X1

70

X2

71

RESET

72

P60/KR0

73

P61/KR1

74

P62/KR2

75

P63/KR3

76

P70/KR4

77

P71/KR5

78

P72/KR6

79

SQLIN

CTCIN

TXMOD

CTCO2

CTCO1

CTCO0

POWER

PLLST

PLLDA

PLLCK

AFON

RMUTE

BEEP

UNLK

TEST

CLIN

60595857565554535251504948

47464544434241

AN2

AN1

AN0

P83/AN7

P82/AN6

P31/SYNC

P30/LCDCL

P23/BUZ

P22/PCL/PTO2

P21/PTO1

P20/PTO0

P13/TI0

P12/TNT2

P11/TNT1

P10/TNT0

P03/SI/SB1

P81/TI2

P80/TI1

P33

P32

COM0

21

P02/SO/SB0

40

COM1

22

COM2

23

COM3

24

BIAS

25

VLC0

26

VLC1

27

VLC2

28

P40

29

P41

30

P42

31

P43

32

VSS

33

P50

34

P51

35

P52

36

P53

37

P00/INT4

38

P01/SCK

39

S31/BP7

S30/BP6

S29/BP5

S28/BP4

S27/BP3

S26/BP2

S25/BP1

S24/BP0

S23

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

S25

S24

S23

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

123

45678910111213141516

17

123

45678910111213141516

17

181920

SEG25

SEG24

SEG23

SEG22

SEG21

SEG20

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

COM0

COM1

COM2

COM0

COM1

COM2

DS2

LD-BU10185J

R65

18 k

R66

18 k

R64

18 k

+3 V

UNLK

VOL

CK

DATA

STB

AF

SENS

SQL

MOD

PSC

R+3

T+3

BATT

12

34

5

6

7

8

9

10

11

12

13

14

J4 4-175638-4

to RF unit J2

8

IC2a

NJM2100M

R30

68 k

C73

0.0033

T-ID

1

3

2

4

C1

0.0015

R2

82 k

R39

82 k

C29

270 P

R40

47 k

Q2

UN9215

Q3

UN5119

Q1

DTA144EU

C6

1

PTT2

Q6

2SK1829

RMUTE

AFON

BEEP

Q18

2SA1586

R81

10 k

R74 10 k

C61

0.1

BATIN

C56

0.1

R80

100 k

R94

220 k

C67

2.2

R79 220 k

R76

100 k

OUT

C60

0.1

+3 V

TXV

RXV

C63

0.1

C94

330 P

D4

1SS355

W7

R77

470

C89

470 P

321

654

Q25

UMZ2N

C65

0.1

R78

10 k

GND

1

VIN

2

VOUT

3

NC

NC

R54

1.2 k

R55

120

C49

0.1

C48

22

Q10

2SC4081

Q5

2SA1362

C47

470 P

C55

3.3

R23

15 k

IC9

NJM2070M

C52

2.2

R56

1

C50

0.1

C17

150

Q11

2SC4213

R26

10 k

C18

10

C97

330 P

C96

330 P

W5

J3

HSJ1493-01-010

R58

RV-244

10 k

C98

330 P

SP1

CHASSIS

C20

0.1

D2

1SS355

R25

12 k

1

REMIN

2

3

4

5

6

7

8

R45

2.2 M

C36

0.001

C40

0.1

R46

100

R35

5.6 k

Q12

2SC4081

C51

0.1

R57

15 k

R34

6.8 k

C26

470 P

C27

0.1

C28

0.047

R33

6.8 k

R32

680 k

C32

0.1

C31

0.022

C34

0.0047

R38

22 k

R36

10 k

R37

22 k

R41

4.7 k

Q7

2SC4081

C24

0.033

R53

1.5 M

TO RF unit

BEEP

R42

3.9 k

R43

56 k

C35

0.1

R5

1.2 M

W6

R7

1.2 k

R108

33 k

R4

82 k

7

IC2b

NJM2100M

C85

0.1

R52

330 k

R118

4.7 k

MMUTE

C93

330 P

C3

0.1

R9

100 k

R50

4.7 kC5470 P

C79

0.1

R95 4.7 k

MC1 KUC3523

R14

3.3 k

C10

470 P

C11

470 P

Q29

DTC114EU

C4

0.1

C25

470 P

R110

1 M

C21

0.1

C15

0.1

R22 33 k

R27

100

Q23

2SJ144

R87

1 M

R86

100 k

R88

100 k

C59

470 P

C72

0.01

C57

0.1

R112

33 k [ITA/-1]

10 k [CSA/-1]

R301

118 k

R200

2.2 M

R302

1 k

D101

MA2S111

D101

1SS355

C86

2.2

Q27

2SC4081

BATT

R114

1.2 k

3.3 k

D5

MA2S111 [ITA/-1]

1SS355 [CSA/-1]

R115

560

D303

MA2S111

654

321

Q101

UMZ1N

Q28

2SB798

Q28

2SB798

R+3

SENIN

BATIN

RXD

TEST

R103

100 k

R62

100 k

PTT2

R105

10 k

5

6

R6

180 k

R202

100

R13

4.7 k

R10

82

W3

C8

10

C90

470 P

R12

10

R49

100

C9

470 P

C42

0.01

J1

HSJ-1102-01-540

C95

330 P

C44

0.1

C7

0.1

C91

470 P

R51

470 k

C83

0.1

REMIN

VDD

VSS

NC

NC

IC5 S-80928ANMP

C80

100/4 V

C62

0.1

C88

470 P

C81

0.033

4

5

1

2

3

R31

1 M

C54

0.1

R+3

C64

22

R63

5.6 k

IC6 S-81230SG

4

5

R24 1.5 M

C82

0.047

R106

10 k

[

PTT][DOWN][UP][MOD][POWER

]

C87

470 P

C : COMMON

T: TX

R : RX

SO : SQL OPEN

SC : SQL CLOSE

LON: LIGHT ON

LOF : LIGHT OFF

C71

0.1

R201

270

R119

100 k

[ITA/-1]

[CSA/-1]

[ITA/-1]

[CSA/-1]

[ITA/-1]

[CSA/-1]

[ITA/-1]

[CSA/-1]

[ITA/-1]

[CSA/-1]

Page 29

11-2 RF UNIT

11 - 2

T: 0

R: 2.96

T: 0

R: 0.72

T: 0

R: 1.86

T: 0

R: 2.60

T: 0

R: 1.76

T: 0

R: 0.72

T: 0

R: 1.98

C: 2.83

C: 2.80

T: 0

R: 1.12

T: 1.16

R: 0

T: 0.42

R: 0.36

T: 0.72

R: 0

T: 1.38

R: 0

T: 1.51

R: 0

T: 0.75

R: 0.84

T: 1.20

R: 0

T: 0

R: 0.82

T: 0.57

R: 0

T: 1.47

R: 0

T: 0

R: 2.61

T: 0

R: 0.99

T: 0

R: 1.82

T: 0.18

R: 0.78

T: 0

R: 1.72

T: 0

R: 0.95

T: 2.85

R: 0.01

C: 1.22

C: 2.01

C: 0.75

C: 0.70

T: 1.56

R: 0.02

C: 4.5

T: 0

R: 2.96

C: 3.06

C: 2.49

C: 2.99

C: 3.02

R52

560

R53

100 k

C74

470 P

C73

0.1

C75

470 P

R51 560 k

IC2

TA31136FN

R54

NTCCF20123NH

R55

15 k

1234567

8

9

AFOUT

FILIN

FILOUT

BIAS

IFIN

VDD

MIXOUT

OSCOUT

OSCIN

QUADIN

IFOUT

SOUT

NDET

NOUT

VSS

MIXIN

10111214151613

C76

470 P

R56

15 k

R59

1.8 k

R58

4.7 k

C2

0.047

C79

10

R57

1.2 k

X2

CDBCA450CX24

C77

22 P

C78

68 P

C83

1

C67

0.1

R71

10 k

Q15

2SC4081

R67

680 k

C1

0.001

R2

82 kR31.8 k W8

FI2

FL-298

C36

10 P

R1

820

Q1

2SC4215

1

345

FI3

CFWM450E

L19

27 nH

R5

100 k

R6

4.7 k

C35

0.5 P

L1

2.2 µH

R19

470

C28

470 P

Q2

2SC4226

R4

2.2 k

C46

22 P

(21.25 MHz)

2nd LO

C4

470 P

C48

0.01

C13

0.001

C16

470 P

C61

5 P

C15

0.047

FIN1

1

VCC

2

CP1

3

GND

4

LD

5

CK

6

DATA

7

STB

8

BO

9

XOUT

10

XIN

11

SW

12

GND

13

CP2

14

VCC

15

FIN2

16

R27

47 k

C63

CTZ3S-20C

20 P

R88

10 k

C42

33 P

C43

12P

C100

22 P

X1

CR-633

C62

0.01

C68

1

W4

Q12

2SC5108

C70

470 P

C88

4.7

R86

68

Q8

2SC4228

L21

22 nH

R37

22 k

D2

MA77

D1

MA77

R12

1 k

R208

1 k

L207

18 nH

C211

0.001

R212

180

R211

27

L105

82 nH

C102

1.5 P

W6

R10

8.2 k

C17

0.022

R45

4.7 k

C18

0.001

C54

3.5 P

R210

180

R34

680

C69

8 P

R36

220

L14

33 nH

R31

33 K

C55

470 P

C50

12 P

L13

27 nH

C52

2 P

L12

10 µH

C64

0.22

D4

1SV284

C26

470 P

W201

R205

NTCCM16083NH221KC [CSA/-1]

T+3

C201

470 P

C202

22 P

C204

8 P

L201

22 nH

R202

6.8 k

Q201

2SC3356

R206

EVM-1X B14

10 k

R301

12 k [ITA/-1]

1 k [CSA/-1]

C203

22 P

C23

3 P

C21

470 P

W202

L202