Page 1

CPC700

Memory Controller and PCI Bridge

User’s Manual

Version 1.1

Issue Date: 3/22/00

Preliminary

Page 2

International Business Machines Corporation 1999, 2000.

Printed in the United States of America, March 2000. All Rights reserved.

IBM Microelectronics, PowerPC, PowerPC 603e, RISCWatch, and AIX are trademarks of the IBM corpora-

tion. IBM and the IBM logo are registered trademarks of the IBM corporation. Other company names and

product identifiers are trademarks of the respective companies.

This document contains information which is subject to change by IBM without notice. IBM assumes no

responsibility or liability for any use of the information contained herein. Nothing in this document shall

operate as an express or implied license or indemnity under the intellectual property rights of IBM or third

parties. The products described in this document are not intended for use in implantation or other direct

life-support applications where malfunction may result in physical harm or injury to persons. NO WARRANTIES OF ANY KIND, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE OFFERED IN THIS DOCUMENT.

USA and Canada:

IBM Microelectronics Division

1580 Route 52, Bldg. 504

Hopewell Junction, NY 12533-6531

Tel: (800) PowerPC

Fax: (800) PowerFax

http://www.chips.ibm.com

http://www.ibm.com

ftp://ftp.austin.ibm.com/pub/PPC_support

ii

Page 3

Table of Contents

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iii

Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

Chapter 1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

1.2 CPC700 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

Chapter 2. Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 Processor Interface Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.2 PCI Bus Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.3 Memory Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.4 Internal Peripherals Interface Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.5 System Interface Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

2.6 Test Interface Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Chapter 3. Processor Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3.2 Processor Interface Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3.3 Processor Interface Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

3.4 Processor Interface to Memory, PCI, and Peripherals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

3.5 Supported Processor Transfer Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-5

3.6 Processor to Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.6.1 CPC700 Response for Processor to System Memory Accesses. . . . . . . . . . . . . . . .3-7

3.7 Processor to PLB Master (PCI or Internal Peripherals). . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3.7.1 CPC700 Response for Processor to PLB Accesses . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3.8 Processor - Address Only Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.9 Processor Bus Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

3.10 Broadcast Snoop Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.11 Byte Swapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.11.1 Processor to PLB (PCI) Byte Swapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.11.2 PCI to Memory Byte Swapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-15

3.11.2.1 Byte Lane Preservation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-15

3.11.2.2 Byte Lane Swapping - Value Preservation . . . . . . . . . . . . . . . . . . . . . . . . .3-15

3.11.2.3 PCI to Memory Byte Swapping Examples . . . . . . . . . . . . . . . . . . . . . . . . .3-16

3.12 PLB Slave Interface to Memory (PCI to Memory) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-17

3.13 CPC700 Response for PCI to Memory Accesses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

3.14 Processor to DCR/Configuration Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

3.15 Error Handling and Reporting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-20

3.15.1 Processor transfer type errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-20

3.15.2 Memory Select Error - Processor Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

3.15.3 Flash Write Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

3.15.4 Address Parity Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

3.15.5 Data Parity Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-22

3.15.6 PLB Master Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-22

3.15.7 PLB Slave Error (From PCI Master). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-22

3.15.7.1 PCI Writes to Local Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.15.7.2 PCI Reads From Local Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.15.8 MCP_REQ ERROR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.15.9 ECC Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

3.16 Processor Interface Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

3.16.1 PRIFOPT1 - Processor Interface Options 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-25

CPC700 User’s Manual—Preliminary iii

Page 4

Table of Contents

3.16.2 ERRDET1 - Error Detection 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-26

3.16.3 ERREN1 - Error Detection Enable 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-27

3.16.4 CPUERAD - Processor Error Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-28

3.16.5 CPUERAT - Processor Error Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-28

3.16.6 PLBMIFOPT - PLB Master Interface Options . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-29

3.16.7 PLBMTLSA1 - PLB Master Byte Swap Region 1 Starting Address. . . . . . . . . . . .3-30

3.16.8 PLBMTLEA1 - PLB Master Byte Swap Region 1 Ending Address . . . . . . . . . . . .3-30

3.16.9 PLBMTLSA2 - PLB Master Byte Swap Region 2 Starting Address. . . . . . . . . . . .3-31

3.16.10 PLBMTLEA2 - PLB Master Byte Swap Region 2 Ending Address . . . . . . . . . . .3-31

3.16.11 PLBMTLSA3 - PLB Master Byte Swap Region 3 Starting Address. . . . . . . . . . .3-32

3.16.12 PLBMTLEA3 - PLB Master Byte Swap Region 3 Ending Address . . . . . . . . . . .3-32

3.16.13 PLBSNSSA0 - PLB Slave No Snoop Region Start Address . . . . . . . . . . . . . . . .3-33

3.16.14 PLBSNSEA0 - PLB Slave No Snoop Region End Address. . . . . . . . . . . . . . . . .3-33

3.16.15 BESR - Bus Error Syndrome Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-34

3.16.16 BEAR - Bus Error Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-35

3.16.17 PLBSWRINT - PLB Slave Write Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-35

Chapter 4. Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4.2 Memory Controller Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

4.3 Memory Controller Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.4 Memory Access Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.5 SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.5.1 Initialization Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

4.5.2 Page Mode Accesses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

4.5.3 Memory Timing Parameter Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

4.5.4 SDRAM Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

4.5.5 Physical Address to Memory Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

4.5.5.1 32-Bit Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

4.5.5.2 64-Bit Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-10

4.5.6 Precharge Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-12

4.5.7 Refresh. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-12

4.5.7.1 Self-Refresh operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13

4.5.8 Mode Register Write Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13

4.5.9 Timing Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14

4.5.9.1 SDRAM Timing Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14

4.5.9.2 CPU-to-Memory Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-19

4.5.9.3 PCI-to-Memory Timing Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-23

4.5.9.4 Miscelaneous Memory Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . .4-27

4.6 ROM/Peripheral Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29

4.6.1 Peripheral Bus Behavior. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29

4.6.2 Reads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-30

4.6.3 Writes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-30

4.6.4 Shared Address/Data/Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-31

4.6.5 Device Attachment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-31

4.6.6 ROM / Peripheral Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-32

4.6.7 ROM/Peripheral Attachment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-33

4.6.8 ROM Timing Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-34

4.7 ECC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38

4.7.1 ECC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-39

4.7.2 ECC Erorrs and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-40

4.7.3 ECC Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-40

4.7.4 Dynamic ECC Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41

4.8 Memory Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41

iv Table of Contents

Page 5

Table Of Contents

4.9 Memory Controller Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-43

4.9.1 Global Memory Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-43

4.9.1.1 MCOPT1 - Memory Controller Options 1 . . . . . . . . . . . . . . . . . . . . . . . . . . .4-44

4.9.1.2 MBEN - Memory Bank Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-45

4.9.1.3 MEMTYPE - Installed Memory Type. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-45

4.9.1.4 MB0SA - Memory Bank 0 Starting Address. . . . . . . . . . . . . . . . . . . . . . . . .4-46

4.9.1.5 MB0EA - Memory Bank 0 Ending Address. . . . . . . . . . . . . . . . . . . . . . . . . .4-47

4.9.1.6 MBxSA - Memory Bank 1-4 Starting Address . . . . . . . . . . . . . . . . . . . . . . .4-47

4.9.1.7 MBxEA - Memory Bank 1-4 Ending Address . . . . . . . . . . . . . . . . . . . . . . . .4-47

4.9.2 SDRAM Specific Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-48

4.9.2.1 SDTR1 - SDRAM Timing Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-48

4.9.2.2 RWD - Bank Active Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-50

4.9.2.3 RTR - Refresh Timer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-50

4.9.2.4 DAM - DRAM Addressing Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-51

4.9.3 ROM Specific Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-52

4.9.3.1 RPBxP - ROM/Peripheral Bank Parameters. . . . . . . . . . . . . . . . . . . . . . . . .4-52

4.9.3.2 RBW - ROM Bank Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-54

4.9.3.3 FWEN - Flash Write Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-55

4.9.4 ECC Specific Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-56

4.9.4.1 ECCCF - ECC Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-56

4.9.4.2 ECCERR - ECC Error Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-58

Chapter 5. PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5.3 PCI Bridge Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2

5.4 PCI Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

5.5 PCI Interface Address Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5.5.1 PLB Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5.5.2 PCI Master Map (PMM) Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-6

5.5.3 PCI Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7

5.5.4 PCI Target Map (PTM) Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7

5.6 PCI Target Interface (PLB Master). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.6.1 Commands Generated as PLB Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.6.2 Handling of Reads from PCI Masters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9

5.6.2.1 Read Buffer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9

5.6.2.2 Delayed Reads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9

5.6.2.3 Read Prefetching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

5.6.2.4 Byte Enable Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

5.6.2.5 Handling of Writes from PCI Masters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

5.6.2.6 Byte Enable Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

5.6.3 PCI Request Responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

5.7 PCI Master Interface (PLB Slave) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-13

5.7.1 Commands Generated as a PCI Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-13

5.7.2 PLB Slave Read Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.7.2.1 PLB Reads and Prefetching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.7.2.2 PLB Reads to the PCI interface’s Configuration Registers. . . . . . . . . . . . . .5-14

5.7.3 PLB Slave Write Handling (PLB to PCI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.7.3.1 PLB Slave Write Post Buffer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

5.7.4 PLB Request Responses (CPU to PCI Transactions) . . . . . . . . . . . . . . . . . . . . . . .5-15

5.7.4.1 Aborted PLB Requests. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.8 Other Bridge Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.8.1 Collision Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.8.2 Completion Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

CPC700 User’s Manual—Preliminary v

Page 6

Table of Contents

5.8.2.1 PCI Producer-Consumer Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-18

5.8.3 PCI Frequency Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-18

5.8.3.1 Effects on Performance of the Asynchronous Interface . . . . . . . . . . . . . . . .5-18

5.9 Bridge Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.9.1 PCI Interface Local Configuration Register Descriptions. . . . . . . . . . . . . . . . . . . . .5-20

5.9.1.1 PMM 0 Local Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-20

5.9.1.2 PMM 0 Mask/Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-21

5.9.1.3 PMM 0 PCI Low Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-21

5.9.1.4 PMM 0 PCI High Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-21

5.9.1.5 PMM 1 Local Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

5.9.1.6 PMM 1 Mask/Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

5.9.1.7 PMM 1 PCI Low Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

5.9.1.8 PMM 1 PCI High Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

5.9.1.9 PMM 2 Local Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.9.1.10 PMM 2 Mask/Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.9.1.11 PMM 2 PCI Low Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.9.1.12 PMM 2 PCI High Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.9.1.13 PTM 1 Memory Size/Attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5.9.1.14 PTM 1 Local Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5.9.1.15 PTM 2 Memory Size/Attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5.9.1.16 PTM 2 Local Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5.9.2 PCI Configuration Register and Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5.9.2.1 Configuration Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5.9.2.2 PCI Configuration Address Register (PCICFGADR) . . . . . . . . . . . . . . . . . .5-26

5.9.2.3 PCI Configuration Data Register (PCICFGDATA). . . . . . . . . . . . . . . . . . . . .5-26

5.9.3 PCI Interface Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-26

5.9.3.1 PCI Vendor ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

5.9.3.2 PCI Device ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

5.9.3.3 PCI Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

5.9.3.4 PCI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

5.9.3.5 PCI Revision ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-30

5.9.3.6 PCI Class Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-30

5.9.3.7 PCI Cache Line Size. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-31

5.9.3.8 PCI Latency Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-31

5.9.3.9 PCI Header Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-31

5.9.3.10 PCI Built-in Self Test (BIST) Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.9.3.11 PCI Base Address Register 0 (PCIBAR0) . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.9.3.12 PCI Base Address Register 1 (PCIPTM1BAR) . . . . . . . . . . . . . . . . . . . . .5-32

5.9.3.13 PCI Base Address Register 2 (PCIPTM2BAR) . . . . . . . . . . . . . . . . . . . . .5-33

5.9.3.14 PCI Base Address Registers 3 through 5 (Unused). . . . . . . . . . . . . . . . . .5-33

5.9.3.15 PCI Cardbus CIS Pointer (Unused) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-33

5.9.3.16 PCI Subsystem ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-33

5.9.3.17 PCI Subsystem Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.9.3.18 PCI Unused or Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.9.3.19 PCI Interrupt Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.9.3.20 PCI Interrupt Pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.9.3.21 PCI MIN_GNT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.9.3.22 PCI MAX_LAT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-35

5.9.3.23 PCI Bus Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-35

5.9.3.24 PCI Subordinate Bus Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-35

5.9.3.25 PCI Disconnect Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-35

5.9.3.26 PCI Arbiter Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-36

5.9.3.27 Error Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-37

5.9.3.28 Error Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-38

vi Table of Contents

Page 7

Table Of Contents

5.9.3.29 Bridge Options 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-38

5.9.3.30 PLB Slave Error Syndrome Register (SESR). . . . . . . . . . . . . . . . . . . . . . .5-39

5.9.3.31 PLB Slave Error Address Register 0 (SEAR0). . . . . . . . . . . . . . . . . . . . . .5-41

5.9.3.32 PLB Slave Error Address Register 1 (SEAR1). . . . . . . . . . . . . . . . . . . . . .5-41

5.9.3.33 Bridge Options 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-41

5.9.3.34 PCI Initial Target Latency Timer Duration. . . . . . . . . . . . . . . . . . . . . . . . . .5-42

5.9.3.35 PCI Subsequent Target Latency Timer Duration . . . . . . . . . . . . . . . . . . . .5-43

5.10 Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-43

5.10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-43

5.10.2 Error Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-43

5.10.3 Error Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-44

5.10.3.1 PLB Unsupported Transfer Type. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-44

5.10.3.2 PCI Master Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-44

5.10.3.3 PCI Target Abort Received While PCI Master . . . . . . . . . . . . . . . . . . . . . .5-45

5.10.3.4 PCI Target Data Bus Parity Error Detection . . . . . . . . . . . . . . . . . . . . . . . .5-45

5.10.3.5 PCI Master Data Bus Parity Error Detection. . . . . . . . . . . . . . . . . . . . . . . .5-46

5.10.3.6 PCI Address Bus Parity Error While PCI Target . . . . . . . . . . . . . . . . . . . . .5-46

5.10.3.7 PLB Master PLB_MErr Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-47

5.11 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-47

5.11.1 PCI Register Set Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-47

5.11.1.1 Address Map Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-47

5.11.1.2 Example Address Map Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-48

5.11.1.3 Other Registers that must be Initialized . . . . . . . . . . . . . . . . . . . . . . . . . . .5-50

5.11.1.4 Target Bridge Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-50

Chapter 6. Clock, Power Management, and Reset . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1 CPC700 Clock Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

6.1.1 PLL Tuning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

6.1.2 UART Serial Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2

6.2 Internal Peripheral Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2

6.3 Reset Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2

6.3.1 Reset Connectivity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.3.1.1 Changes from Earlier Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.3.2 Internal Peripheral Reset Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.4 Power on Reset Pin Strapping Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.5 CPR Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-6

6.5.1 Peripheral Power Management Control Register (CPRPMCTRL). . . . . . . . . . . . . . .6-6

6.5.2 Peripheral Reset Control Register (CPRRESET). . . . . . . . . . . . . . . . . . . . . . . . . . . .6-6

6.5.3 GPT Capture Event Generation Register (CPRCAPTEVNT) . . . . . . . . . . . . . . . . . .6-7

6.5.4 PLL Configuration Access Register (CPRPLLACCESS). . . . . . . . . . . . . . . . . . . . . .6-8

6.5.5 PLL Tuning Control Register (CPRPLLTUNE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-8

6.5.6 Strapping Pin Register (CPRSTRAPREAD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

Chapter 7. UART. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1 Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-2

7.2 UART Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.2.1 UART Register Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.2.1.1 Line Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.2.1.2 Line Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

7.2.1.3 FIFO Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7

7.2.1.4 Interrupt Identification Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-8

7.2.1.5 Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-9

7.2.1.6 Scratchpad Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-10

7.2.1.7 Divisor Latch LSB and MSB Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-10

CPC700 User’s Manual—Preliminary vii

Page 8

Table of Contents

7.3 FIFO Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-11

7.3.1 Interrupt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-11

7.3.1.1 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-11

7.3.1.2 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-11

7.3.2 Polled Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-12

7.4 UART Reset and Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-12

Chapter 8. IIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1 Functional Description Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

8.2 Programming Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

8.3 IIC Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.4 IIC Register Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-3

8.4.1 Master and Slave Data Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-3

8.4.2 Lo Master Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-4

8.4.3 Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-5

8.4.4 Mode Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-7

8.4.5 Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-8

8.4.6 Extended Status Register Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-9

8.4.7 Lo Slave Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-10

8.4.8 Hi Slave Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-11

8.4.9 Clock Divide Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-11

8.4.10 Interrupt Mask Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-12

8.4.11 Transfer Count Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-12

8.4.12 Extended Control and Slave Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-13

8.4.13 Direct Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-14

8.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-15

8.6 General Considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-16

Chapter 9. General Purpose Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9.1.1 GPT Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9.1.2 Programmability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-2

9.2 Mode of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-2

9.2.1 Time Base Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-2

9.2.2 Capture Timers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-3

9.2.2.1 Capture Timers Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-3

9.2.3 Compare Timers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-4

9.2.3.1 Compare Timers Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-4

9.2.4 Interrupt Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-5

9.2.5 GPT Register Reset Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-5

9.3 GPT Detailed Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-6

9.3.1 Time Base Counter (TBC) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-6

9.3.2 GPT Capture Enable (GPTCE) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-6

9.3.3 GPT Edge-Detection Control (GPTEC) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . .9-7

9.3.4 GPT Synchronization Control (GPTSC) Register . . . . . . . . . . . . . . . . . . . . . . . . . . .9-7

9.3.5 GPT Interrupt Mask (GPTIM) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-8

9.3.6 GPT Interrupt Status (GPTIS) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-8

9.3.7 GPT Interrupt Enable (GPTIE) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.3.8 Capture Timer (CAPTx) Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.3.9 Compare Timer (COMPx) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.3.10 Compare Mask (MASKx) Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.3.11 GPT Capture Event Generation Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-10

Chapter 10. Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

viii Table of Contents

Page 9

Table Of Contents

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

10.3 Interrupt Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-3

10.4 Programmable Configurability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-3

10.4.1 Interrupt Priority Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-3

10.4.2 Interrupt Vector Base Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.4.3 Interrupt Enable/Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.4.4 INT/MCP Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.4.5 Polarity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.4.6 Edge/Level Sensitivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.5 Universal Interrupt Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.5.1 UICSR — UIC Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-5

10.5.2 UICSRS — UIC Status Register – Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-5

10.5.3 UICER — UIC Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-6

10.5.4 UICCR — UIC Critical Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-6

10.5.5 UICPR — UIC Polarity Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-7

10.5.6 UICTR — UIC Trigger Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-7

10.5.7 UICMSR — UIC Masked Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-8

10.5.8 UICVCR — UIC Vector Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . .10-8

10.5.9 UICVR — UIC Vector Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-9

Chapter 11. JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

Chapter 12. Processor Local Bus (PLB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.1 PLB Master Priority Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

12.2 PLB Arbiter Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.2.1 PLB Arbiter Control Register (PACR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.2.2 PLB Error Address Register (PEAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.2.3 PLB Error Status Register (PESR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-3

Chapter 13. OPB Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

13.1 OPB Bridge Error Address Register (GEAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-1

13.2 OPB Bridge Error Status Register (GESR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-1

Chapter 14. Register Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

14.1 CPC700 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

14.1.1 Processor Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

14.1.2 Memory Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-2

14.1.3 PCI Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-3

14.1.4 CPR Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-5

14.1.5 PLB Macro Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-5

14.1.6 OPB Bridge Macro Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-6

14.1.7 Universal Interrupt Controller Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-6

14.1.8 IIC0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-6

14.1.9 IIC1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-7

14.1.10 UART0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-8

14.1.11 UART1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-8

14.1.12 GPT Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-9

Chapter 15. I/O Driver Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Index-1

CPC700 User’s Manual—Preliminary ix

Page 10

Table of Contents

x Table of Contents

Page 11

Figures

Figure 1. System Block Diagram 1-3

Figure 2. Functional Block Diagram 1-4

Figure 3. Processor Interface Detailed Block Diagram 3-2

Figure 4. Processor to PLB Interface Translation Mechanism 3-13

Figure 5. Processor to PLB Big-Endian to Little-Endian Byte Swapping 3-14

Figure 6. Default Byte Preservation Method 3-15

Figure 7. Alternative Byte Swapping Method 3-16

Figure 8. Memory Controller Block Diagram 4-2

Figure 9. Routing of Memory Access Requests 4-4

Figure 10. Mode Register Write Command 4-14

Figure 11. Read without Auto-Precharge 4-15

Figure 12. Write without Auto-Precharge 4-15

Figure 13. Read with Auto-Precharge 4-16

Figure 14. Write with Auto-Precharge 4-16

Figure 15. Precharge All Command 4-17

Figure 16. CAS-before-RAS Refresh 4-17

Figure 17. Self-Refresh Entry/Exit 4-18

Figure 18. CPU Read - Read 4-19

Figure 19. CPU Read - Write 4-20

Figure 20. CPU Write - Read 4-21

Figure 21. CPU Write - Write 4-22

Figure 22. PCI Continuous Read Burst 4-23

Figure 23. Continuous Write Burst 4-24

Figure 24. PCI Short Burst Read - PCI Short Burst Read 4-25

Figure 25. PCI Short Burst Read - PCI Short Burst Write 4-26

Figure 26. CPU Line Read-PCI Burst Read 4-27

Figure 27. CPU Line Read to PCI Write Burst 4-28

Figure 28. ROM/Peripheral Attachement to Memory Bus 4-33

Figure 29. Single Read/Write (General) 4-34

Figure 30. Burst Mode Read 4-34

Figure 31. Non-Burst Read 4-35

Figure 32. Single Write, Synchronous Ready Enabled 4-35

Figure 33. Single Write, Asynchronous Ready Enabled 4-36

Figure 34. Non-Burst Read, Synchronous Ready Enabled 4-36

Figure 35. Non-Burst Read, Synchronous Ready Enabled 4-37

Figure 36. Burst Mode Read, Asynchronous Ready Enabled 4-37

Figure 37. Burst Mode Read, Asynchronous Ready Enabled 4-38

Figure 38. PCI Interface Macro Block Diagram 5-2

Figure 39. Little-Endian 5-20

Figure 40. Big-Endian 5-20

Figure 41. Format of PCICFGADR Register 5-26

Figure 42. Arbiter Priority Resolution 5-36

Figure 43. Example Address Map 5-49

Figure 44. CPC700 Reset and Strapping Pin Timing 6-3

Figure 45. Typical Reset System 6-3

CPC700 User’s Manual—Preliminary xi

Page 12

Figure 46. 7-Bit Addressing 8-1

Figure 47. 10-Bit Addressing 8-2

Figure 48. Capture Timers Logic/Block Diagram 9-3

Figure 49. Compare Timer Logic/Block Diagram 9-4

Figure 50. Capture Timers Enable Register 9-6

Figure 51. Capture Events Edge Detection Control Register 9-7

Figure 52. Capture Events Synchronization Control Register 9-7

Figure 53. Interrupt Mask Register 9-8

Figure 54. Interrupt Status Register 9-8

Figure 55. Interrupt Enable Register 9-9

Figure 56. UICSR -- UIC Status Register 10-5

Figure 57. UICSRS -- UIC Status Register -- Set 10-5

Figure 58. UICER -- UIC Interrupt Enable Register 10-6

Figure 59. UICCR -- UIC Critical Interrupt Register 10-6

Figure 60. UICPR - UIC Polarity Register 10-7

Figure 61. UICTR -- UIC Trigger Register 10-7

Figure 62. UICMSR -- UIC Masked Status Register 10-8

Figure 63. UICVCR -- IUC Vector Configuration Register 10-8

Figure 64. UICVR -- UIC Vector Register 10-9

Figure 65. PLB Arbiter Control Register (PACR) 12-2

Figure 66. PLB Error Address Register (PEAR) 12-2

Figure 67. PLB Error Status Register (PESR) 12-3

Figure 68. Bridge Error Address Register (GEAR) 13-1

Figure 69. OPB Bridge Error Status Register (GESR) 13-1

Figures

xii List of Figures

Page 13

Tables

Table 1. Address Map 1-6

Table 2. PLL Usage 1-10

Table 3. Processor Interface Register Addressing 3-2

Table 4. Offsets for Processor Interface Registers 3-2

Table 5. CPC700 Address Map - Processor View 3-3

Table 6. CPC700 Address Map - PCI View 3-4

Table 7. Supported Processor Transfer Type Encodings/Response 3-5

Table 8. CPC700 Response for processor to System Memory Transactions 3-7

Table 9. Processor to Memory Cycle Translation 3-7

Table 10. PLB Master Cycles 3-8

Table 11. CPC700 Response to Processor Transactions to the PLB 3-8

Table 12. Processor to PLB Cycle Translation 3-10

Table 13. CPC700 Response to Processor Address Only Cycles 3-11

Table 14. Processor Address Bus Arbitration 3-11

Table 15. Processor Snoop Transfer Types 3-12

Table 16. PLB to Memory Cycle Translation 3-17

Table 17. Processor Interface Response to PLB Transactions 3-18

Table 18. Processor I/F Config Registers Indirect Access Register 3-19

Table 19. CPC700 Response to Processor Interface Configuration Transactions 3-19

Table 20. Valid Address, TBST_N, and TSIZ Combinations 3-20

Table 21. Memory Controller Register Addressing 4-3

Table 22. Offsets for Memory Controller Registers 4-3

Table 23. Determining Maximum Page Size 4-5

Table 24. SDRAM Memory Timing Parameters 4-6

Table 25. SDRAM Configuration Registers 4-8

Table 26. Mode Set Command Vector 4-13

Table 27. ROM Response to Memory Controller Read Cycles 4-30

Table 28. ROM Response to Memory Controller Write Cycles 4-30

Table 29. Processor Address to ROM Address Mapping 4-31

Table 30. Device Attachment to ROM/Peripheral Bus 4-32

Table 31. ROM Configuration Registers 4-32

Table 32. ECC Features 4-38

Table 33. ECC Registers 4-39

Table 34. ECC Enable and Correction Bits 4-40

Table 35. Effect of ECC on Timing 4-40

Table 36. Local Processor to Memory Controller Data Flow 4-41

Table 37. Local processor to PCI Data Flow 4-42

Table 38. PCI to Memory Controller Data Flow 4-42

Table 39. PCI Interface Local Configuration Registers 5-3

Table 40. PCI Interface Configuration Register Offsets 5-3

Table 41. PLB Address Map 5-5

Table 42. PCI Memory Address Map 5-7

Table 43. PCI Interface Responses to PCI Requests 5-11

Table 44. PCI interface Responses to PLB Requests 5-15

Table 45. Collision Resolution 5-17

Table 46. PCI Frequency Modes 5-18

CPC700 User’s Manual—Preliminary xiii

Page 14

Table 47. PMM 0 Mask/Attribute Register Bits 5-21

Table 48. PTM 1 Size/Attribute Register Bits 5-24

Table 49. PTM 2 Size/Attribute Register Bits 5-25

Table 50. PCI Command Register Bits 5-28

Table 51. PCI Status Register Bits 5-29

Table 52. PCI BAR 1 5-32

Table 53. PCI Arbiter Control Register Bits 5-36

Table 54. Error Enable Register Bits 5-37

Table 55. Error Status Resister Bits 5-38

Table 56. Bridge Options Register Bits 5-39

Table 57. Slave Error Syndrome Register Bits 5-40

Table 58. Bridge Options 2 Register Bits 5-42

Table 59. Register Settings 5-43

Table 60. PLB Unsupported Transfer Types 5-44

Table 61. PLL Usage 6-1

Table 62. General Strapping Options 6-4

Table 63. PCI Frequency Modes 6-5

Table 64. Power Management Control Register 6-6

Table 65. Peripheral Reset Control Register 6-7

Table 66. GPT Event Generation Register 6-7

Table 67. PLL Configuration Access Register 6-8

Table 68. PLL Tuning Control Register 6-8

Table 69. Strapping Pin Register 6-9

Table 70. UART Core Configuration Registers 7-3

Table 71. Summary of UART Registers (Big Endian Notation) 7-4

Table 72. Line Control Register Description 7-5

Table 73. Line Status Register Description 7-6

Table 74. FIFO Control Register Description 7-7

Table 75. Interrupt Identification Register Description 7-8

Table 76. Interrupt Enable Register Description 7-9

Table 77. UART Divisor Latch Settings for Certain Baud Rates 7-10

Table 78. IIC Registers 8-2

Table 79. Master Data Buffer 8-4

Table 80. Master Data Buffer 8-4

Table 81. Lo Master Address Register 8-5

Table 82. Hi Master Address Register 8-5

Table 83. Control Register 8-6

Table 84. IIC Response to Control Settings 8-6

Table 85. Mode Control Register 8-7

Table 86. Status Register 8-8

Table 87. Extended Status Register 8-10

Table 88. Lo Slave Address Register 8-10

Table 89. Hi Slave Address Register 8-11

Table 90. Clock Divide Register 8-11

Table 91. IIC Clock Divide Programming 8-12

Table 92. Interrupt Mask Register 8-12

Tables

xiv List of Tables

Page 15

Tables

Table 93. Transfer Count Register 8-13

Table 94. Extended Control and Slave Status Register 8-14

Table 95. Direct Control Register 8-15

Table 96. GPT Registers 9-1

Table 97. GPT Registers Reset Values 9-5

Table 98. Interrupt Assignments 10-3

Table 99. UIC Core Configuration Registers 10-5

Table 100. CPC700 PLB Master Assignments 12-1

Table 101. Registers Controlling PLB Master Priority Assignments 12-1

Table 102. PLB Arbiter Registers 12-2

Table 103. OPB Bridge Registers 13-1

Table 104. Processor Interface Register Addressing 14-1

Table 105. Offsets for Processor Interface Registers 14-1

Table 106. Memory Controller Register Addressing 14-2

Table 107. Offsets for Memory Controller Registers 14-2

Table 108. PCI Interface Registers 14-3

Table 109. PCI Configuration Register Offsets 14-4

Table 110. Clock, Power Management and Reset Control Registers 14-5

Table 111. PLB Macro Configuration Registers 14-5

Table 112. OPB Macro Configuration Registers 14-6

Table 113. UIC Configuration Registers 14-6

Table 114. IIC0 Configuration Registers 14-6

Table 115. IIC1 Configuration Registers 14-7

Table 116. UART0 Configuration Registers 14-8

Table 117. UART1 Configuration Registers 14-8

Table 118. GPT Configuration Registers 14-9

Table 119. I/O Driver Specifications 11

CPC700 User’s Manual—Preliminary xv

Page 16

Tables

xvi List of Tables

Page 17

Chapter 1. Introduction

1.1 Overview

The CPC700 Memory Controller and PCI Bridge (CPC700) contains a bridge from the PowerPC processor

to the PCI bus, as well as a high-speed memory controller, internal peripherals, and control for external

ROM and external peripherals. The CPC700 is meant to be a general purpose solution to the problem of

interfacing a high performance, superscalar, PowerPC 603e, 740, and 750 microprocessors to any PCI

bus. These microprocessors feature multiple, independent execution units and large onboard instruction

and data caches.

The CPC700 adds the following features:

• PowerPC 60x/7xx bus with operation to 66 MHz (CPC700-66) or to 83 MHz (CPC700-83).

• Synchronous DRAM interface operating at the processor bus speed.

- 64-bit interface for non-ECC applications.

- 72-bit interface (64 bits of data plus 8 checkbits) for ECC applications.

- ECC protection applied to address as well as data.

• ROM/SRAM/External Peripheral Controller.

- Flash ROM/Boot ROM interface.

- Direct support for 8-, 16-, 32-, or 64-bit SRAM or external peripherals.

• PCI Revision 2.1 Compliant Interface (32-bit, 25 to 66 MHz).

- PCI Bus Interface may be configured to operate synchronously or asynchronously to the processor

bus (synchronous clock is limited to 33 MHz PCI bus operation).

- Internal PCI Bus Arbiter for up to six external devices at PCI bus speeds up to 33 MHz.

• Interrupt Controller supports interrupts from a variety of sources.

- Internal Peripherals (UARTs, IICs, Timers).

- External Peripherals.

- ECC correctable error.

- PCI writes to PCI Command Register.

- PCI writes to a specific memory address range.

• Programmable Timers.

• Two 2-wire 8-bit Serial Ports (16550 compatible UART).

• Two IIC interfaces.

• Supports JTAG for board level testing.

• Byte swapping supported for bi-endian operation.

With versions that support processor bus speeds up to 66 MHz and 83 MHz, the CPC700 allows the PowerPC to realize its full potential. To complement this operation, the CPC700 memory subsystem keeps up

with the processor by providing an optimized memory controller. The memory architecture focuses on performance, cost, and board space. Support is provided for 16-bit wide SDRAMs, reducing the number of

memory devices that are needed to support the 64-bit PowerPC bus size. The device will support four

banks of SDRAM, with up to 512 Mbytes per bank.

CPC700 User’s Manual—Preliminary 1-1

Page 18

For mission critical, zero down time operations , the CPC700 incorporates Error Correction Code (ECC) circuitry with the ability to correct data errors as well as detect address errors. The device also supports the

processor’s address and data parity scheme. If processor data parity is not required, the unused pins can

be configured to provide PCI arbitration.

A complement of internal peripherals are available, including an interrupt controller, programmable timers,

dual UARTs, and two independent IIC ports. If the design requires additional functionality, an integrated

peripheral bus supports 8-, 16-, 32-, or 64-bit device operations for external peripherals. This bus also supports the Boot ROM. Additional chip selects are provided to eliminate the need for external glue logic. A

total of five chip selects are provided that may be programmed to support ROM banks, SDRAM banks, or

peripherals, providing a very flexible system environment.

Critical to intelligent embedded applications, the PCI interface offers features that allow the CPC700 to

operate in a host role, as an intelligent add-in card, or in stand-alone operating modes. The following diagram shows the CPC700 in a typical system configuration.

1-2 CPC700 User’s Manual—Preliminary

Page 19

PowerPC

60x/7xx

Processor

Interrupts

60x/7xx Bus

CPC700

Timers

2 UARTs

2

C

2 I

ROM/SRAM

External

Peripheral

PCI Devices

PCI arbiter

PCI Bus

SDRAM

Figure 1. System Block Diagram

CPC700 User’s Manual—Preliminary 1-3

Page 20

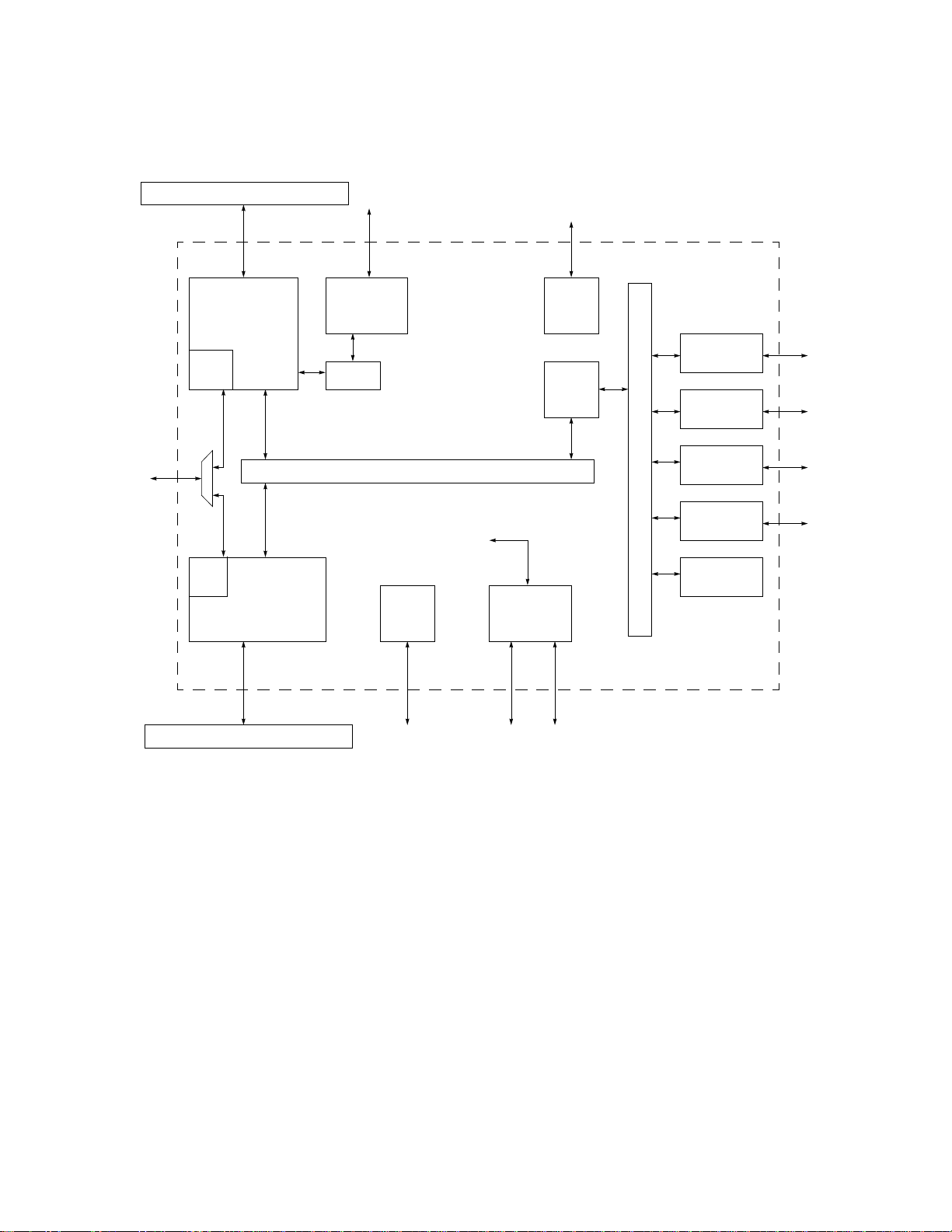

1.2 CPC700 Block Diagram

8

Parity

or

Arbiter

66MHz Processor Bus

119

Processor

Interface

Data

Parity

PCI

Arb

PCI

Interface

104

SDRAM

ROM

Peripherals

ECC

66MHz Processor Local Bus (PLB)

DCR Bus

JTAG

Misc.

(interrupts)

UIC

5

System

&

PLL

1/2X

OPB

Bridge

CPC700 ASIC

UART

UART

2

I

I2C

33MHz On Chip Peripheral Bus (OPB)

GPT

(Timers)

2

2

C

2

2

52

25 to 66MHz PCI Bus

1219

Figure 2. Functional Block Diagram

The block diagram illustrates the internal and external bus frequencies of the CPC700, given a 66MHz processor bus. Each of the blocks in the diagram represents a core from the IBM Blue Logic core library. The

architecture is based on two primary busses, the Processor Local Bus (PLB) and the On Chip Peripheral

Bus (OPB). The PLB operates at the same frequency as the local processor bus. The OPB operates at half

of the frequency of the PLB.

1-4 CPC700 User’s Manual—Preliminary

Page 21

Processor to PLB Interface

The CPC700 provides an interface to attach a 60x or 7xx processor to the internal PLB and to provide the

processor with a low latency access path to local memory. Through this interface, the processor may

access the PCI bus, local memory, external peripherals, and internal peripherals (UARTs, I2Cs, Timers,

and interrupt controller).

Processor interface features:

• Supports PowerPC 603e, 740, and 750 families.

• One level processor address pipelining.

• Support for processor “no-DR

• Processor bus arbiter arbitrates between local processor and internal snoop engine.

• L1 cache coherency support during PCI access to local memory.

• 32-byte write buffer to memory.

• 32-byte write buffer to PLB.

• lwarx/stwx. support (reservation cancelling snoops).

• Address only cycle support.

• External MCP_REQ input may be programmed to drive MCP to processor.

• Error tracking/status for processor transactions.

• Provides low latency access path to local memory.

Address Map Support

The CPC700 incorporates a simple fixed processor address map that serves the PowerPC family of processors. The address map has provisions for ROM, RAM, and I/O. Mapping does not require flexibility

because the CPC700 has the ability to map primary and secondary resources independently. This mapping can be performed solely from the processor side or from a combination of the processor and the PCI

side. This mechanism lets the same fixed secondary resources become flexible to the primary side, while

providing local processor operating space stability.

TRY” mode.

Through the use of “Mapping Port Windows,” either the PowerPC or PCI can gain access to the other

side’s resources. There are three local windows available to the PowerPC to access PCI memory. These

windows can be programmed to powers of 2 boundaries, are variable in size, and may be used to access

any location in a 64-bit PCI address space yet are invisible to the PCI bus.

PCI to local processor memory access “Port Windows” are handled in the PCI standard method, through

the programming of the Base Address Registers (BARs) in PCI configuration space. These registers are

defined to allow the PowerPC processor to request allocation of resources on the PCI side. There are

some fundamental differences though, that differentiate the CPC700 from other embedded solutions. The

first of these differences is that the PowerPC can program the size of the allocation as well as the type: I/O

or Memory. The second difference is that the actual location allocated by the host is translated to the PowerPC space via secondary registers allowing the PowerPC to maintain its local allocation independent of

PCI mappings.

There are two BARs available in the CPC700 for this function.

CPC700 User’s Manual—Preliminary 1-5

Page 22

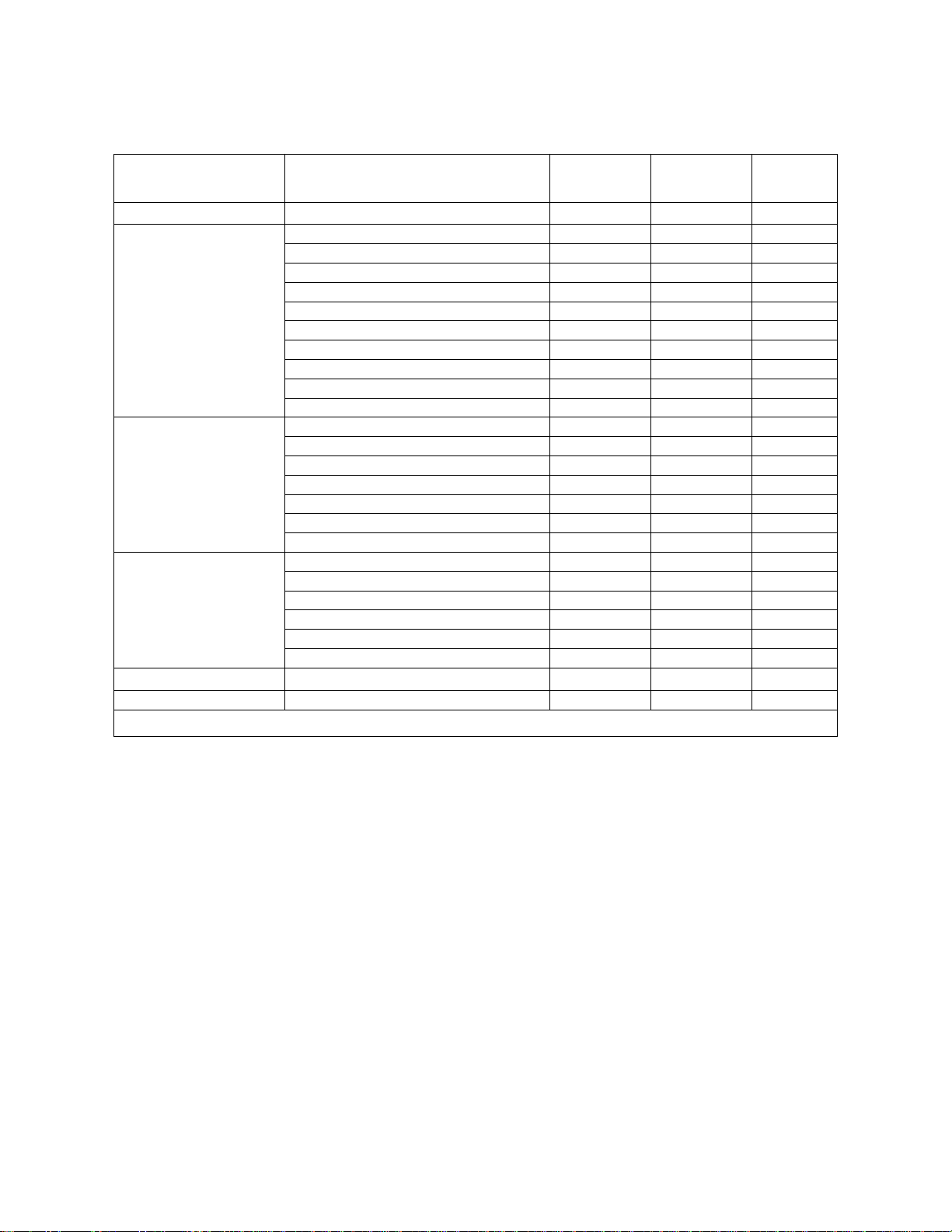

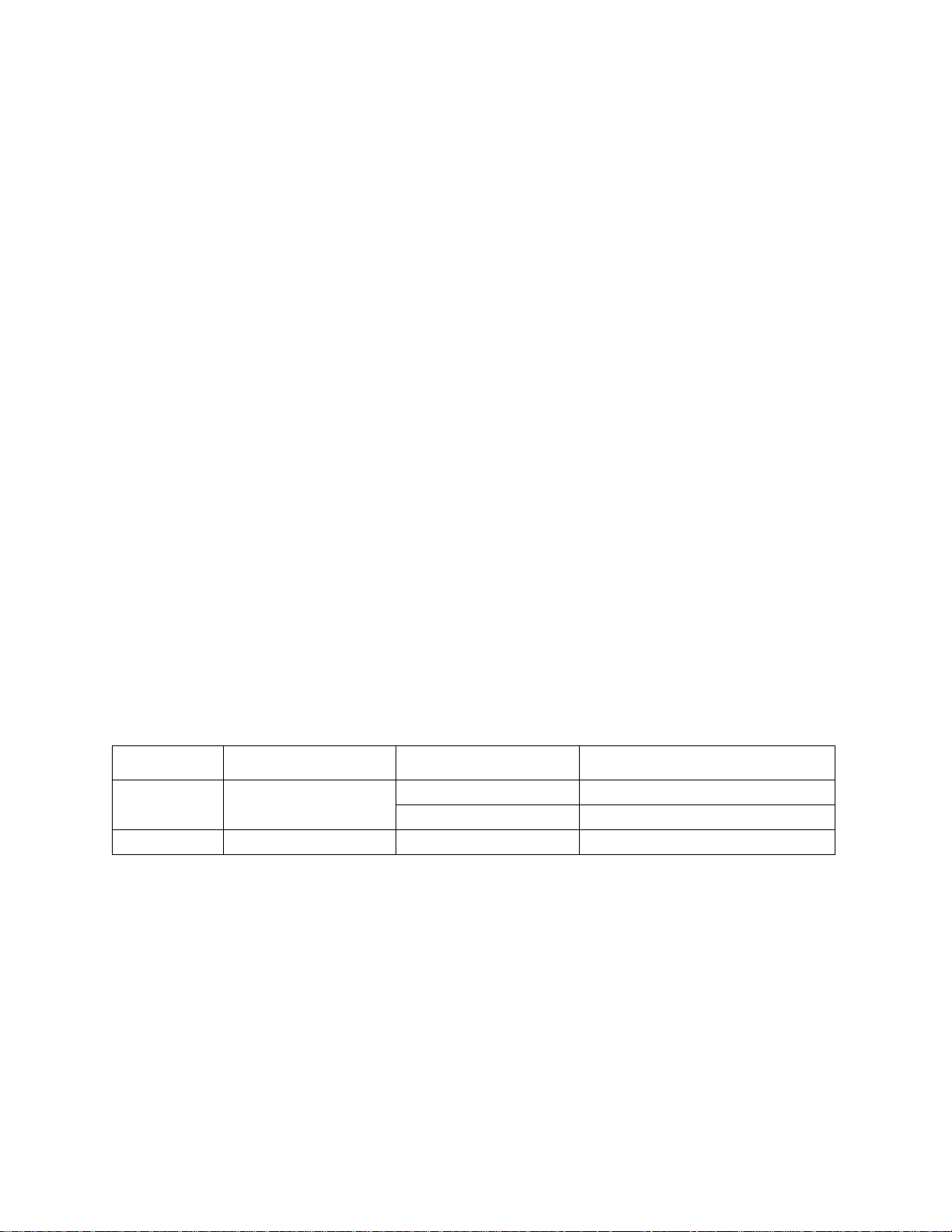

Table 1. Address Map

Start

Function Sub Function

Local Memory/Peripherals

PCI Core Space

Device Configuration

Register (DCR) Space

Internal Peripherals

Local Memory/Peripherals

Boot ROM FFE0 0000 FFFF FFFF 2MB

1. The Local Memory/Peripheral areas of the memory map may be configured for SDRAM, ROM, or Peripherals.

1

PCI Memory 8000 0000 F7FF FFFF

PCI I/O F800 0000 F800 FFFF

Reserved F801 0000 F87F FFFF

PCI I/O F880 0000 FBFF FFFF

Reserved FC00 0000 FEBF FFFF

PCI Configuration Registers FEC0 0000 FEC0 0004

PCI Interrupt Acknowledge FED0 0000 FEDF FFFF

Reserved FEE0 0000 FF3F FFFF

PCI local Configuration Registers FF40 0000 FF40 003C

Processor Interface Registers FF50 0000 FF50 0004

Memory Controller Registers FF50 0008 FF50 000C

OPB Macro Registers FF50 0810 FF50 0818

PLB Macro Registers FF50 0850 FF50 085C

Interrupt Controller FF50 0880 FF50 08A0

Clock and Power Management FF50 0900 FF50 0914

UART0 FF60 0300 FF60 0307

UART1 FF60 0400 FF60 0407

IIC0 FF62 0000 FF62 0010

IIC1 FF63 0000 FS63 0010

Timers FF65 0000 FF65 00FC

1

Address

0000 0000 7FFF FFFF 2GB

8000 0000 FF4F FFFF 2GB - 11MB

FF50 0000 FF5F FFFF 1MB

FF60 0000 FF7F FFFF 2MB

FF80 0000 FFDF FFFF 6MB

End

Address Size

PLB to PCI Interface

The PLB to PCI interface core provides a mechanism for connecting PCI devices to the local PowerPC

processor and local memory. This interface is compliant with version 2.1 of the PCI Specification. Features

of this core include:

• 32-bit PCI address bus

• PCI bus clock frequency from 25 to 66MHz

• Supports processor access to all PCI address spaces:

- Single-beat PCI I/O reads and writes

- PCI memory single-beat and prefetch-burst reads and single-beat writes.

- Single-beat PCI configuration reads and writes (type 0 and type 1)

- PCI interrupt acknowledge

- PCI special cycle

• Buffering between PLB and PCI:

- PCI target 32-byte write post buffer

- PCI target 32-byte read prefetch buffer

- PCI master 32-byte write post buffer

1-6 CPC700 User’s Manual—Preliminary

Page 23

- PCI master 64 byte read prefetch buffer

• Error tracking/status

• Internal PCI bus arbiter for up to six external devices at PCI bus speeds up to 33MHz. Internal arbiter

use is optional and may be disabled for systems which employ an external arbiter.

• Support for synchronous and asynchronous clocking between Processor and PCI busses. Support for

synchronous clocking is limited to a 33MHz PCI bus operation.

Memory Controller

The CPC700 Memory Controller provides the local PowerPC processor with a low latency access path to

local memory and external peripherals. In addition, it supports hardware coherent accesses to the processor’s local memory from the PCI bus. Coherency is maintained on PCI accesses to local memory by

snooping the processor’s L1 cache and posted write buffers before allowing the PCI interface to complete

the requested access.

Industry standard 72-pin and 168-pin modules are supported, allowing for a variety of system memory configurations. The memory controller supports up to five banks (five Chip Select outputs). Bank 0 is dedicated to Boot ROM, while banks 1-4 may be programmed to support either SDRAM, ROM, SRAM, or

external peripherals. Up to 512 MBytes per bank, are supported up to a maximum of 2 GBytes. Memory

timings, starting and ending address ranges, and memory addressing modes are programmable. During

reset, Bank 0 defaults to ROM and is enabled while all other banks are disabled.

Synchronous DRAM:

• Up to 4 banks (Bank 0 defaults to ROM).

• 11x9 to 13x11 addressing for SDRAM (2 and 4 bank internal SDRAM chip architecture supported).

• 8 MByte to 512 MByte per bank.

• Programmable timings and address mapping.

• CAS before RAS refresh w/programmable refresh timer.

• Supports hardware coherency.

• Page mode accesses.

• Sync DRAM configuration via mode set command.

• Memory bus operates at same frequency as processor bus.

• 64-bit and 32-bit memory interface options (72-bit or 40-bit if implementing ECC).

• Support for auto-precharge.

• Support for SRAM self-refresh mode (bank 4 only).

ROM/Peripheral:

• ROM, EPROM, SRAM, and Peripherals supported.

• Burst and Non-Burst devices.

• 1-5 banks (shared with SDRAM).

• 8-, 16-, 32-, and 64-bit data bus widths supported.

CPC700 User’s Manual—Preliminary 1-7

Page 24

• Programmable timing per bank.

• Shared address/data/control with SDRAM interface.

• External latch control for shared address bus support.

• Programmable address mapping.

• Peripheral Device pacing with external “Ready”.

ECC

The CPC700 generates, checks, and corrects ECC bits on their way to and from the memory controller.

Write cycles to memory that are less than a word in width require the ECC controller to generate a read

cycle to fetch the appropriate word, modify that word, generate the ECC bits, and write the word back out

to memory.

The ECC controller implements a 64-bit, single-error-correct, double-error-detect, over data and address.

ECC data is 8 bits wide.

• Corrects single-bit data errors.

• Detects double-bit data errors.

• Detects single-bit address errors.

• Detects concurrent single-bit address and single-bit data errors.

• Detects any errors within an aligned nibble.

• Eight check bits support 32- or 64-bit data bus widths.

• Support for mixing ECC and non-ECC DIMMs in the same system.

• ECC checking may be disabled.

UART

The CPC700 contains two UARTs that provide two wire, full duplex serial interfaces to support communications with serial peripheral devices. Each UART is compatible with the NS 16550 and includes a 16-byte

send and a 16-byte receive FIFO. Features of the UART include:

• Compatible with the NS 16550.

• 16-byte send FIFO, 16-byte receive FIFO.

• Full duplex operation.

• Programmable baud rate generator.

• Supports 5- to 8-bit word size, 1/2 stop bits, even/odd/no parity.

• Two wire transmit/receive external interface.

The UARTs perform serial-to-parallel conversion on data characters received from a peripheral device and

parallel-to-serial conversion on data characters received from the processor. The processor can read the

complete status of the UARTs at any time during the functional operation. Status information reported

includes the type and condition of the transfer operations being performed by the UARTs, as well as any

error conditions, such as parity, overrun, framing and break interrupt.

1-8 CPC700 User’s Manual—Preliminary

Page 25

The CPC700 UARTs are functionally identical to NS16450 in character mode (on power up they will be in

this mode). The UARTs can be put into FIFO mode to relieve the processor of excessive software overhead. Here internal FIFOs are activated, allowing 16 bytes (plus three bits per byte of error data in the

RCVR FIFO) to be stored in both receive and transmit modes. The timing reference clock is the CPC700

SYS_CLOCK input divided by 4. This will generally be 8.333MHz in a typical application (PowerPC local

processor operating with a 66MHz bus frequency).

The UARTs include a programmable baud rate generator capable of dividing the timing reference clock by

a divisor of 1 to (2

16

-1), and they produce a 16x clock for driving the internal transmitter logic. This 16x

clock can also be used to drive the receiver logic.

The UARTs have a processor interrupt system. Interrupts can be programmed to the user’s requirements,

minimizing the computing required to handle the communications link.

IIC Bus Interface

The CPC700 provides two fully independent IIC bus interfaces. The IIC bus is a two wire, bidirectional,

open-drain, low speed serial interface. Both the serial clock (SCL) and the serial data (SDA) lines are bidirectional to support multiple bus masters and to mix “fast“ and “slow” devices on the same bus. The

CPC700 IIC interfaces support the following standard and/or enhanced features of the Philips

ductors I

2

C Specification , dated 1995:

• 100 or 400 kHz operation.

• 8-bit data.

• 10- or 7-bit address.

• Slave transmitter and receiver.

• Master transmitter and receiver.

• Multiple bus masters.

®

Semicon-

• Two independent 4x1 byte data buffers.

• 12 memory mapped and fully programmable configuration registers.

• One programmable interrupt request signal.

• Provides full management of all IIC bus protocol

.

General Purpose Timers (GPT)

The General Purpose Timer (GPT) provides a separate time base counter and system timers for the

CPC700. Five capture timers and five compare timers are implemented in the GPT macro. Features of the

GPT core include:

• 32-bit time base.

- Updated once every CPC700 SYS_CLOCK.

• Five capture event timers.

• Five compare timers.

• 10 interrupt outputs, one for each capture and compare timer.

CPC700 User’s Manual—Preliminary 1-9

Page 26

Universal Interrupt Controller (UIC)

The Universal Interrupt Controller (UIC) provides the control, status, and communications necessary

between the various sources of interrupts and the local PowerPC processor. Features of the UIC include

the following:

• 29 interrupt sources.

- 12 external interrupts.

- 10 timer interrupts - five compare and five event capture.

- Two UART interrupts.

- Two IIC interrupts.

- PCI access to config register interrupt.

- PCI access to local memory interrupt.

- ECC correctable error interrupt.

• Interrupts are individually maskable.

• Interrupts can be individually programmed to generate a Machine Check Exception (MCP) or an External Interrupt (INT) to the processor.

• Interrupt types supported.

- Synchronous level sensitive.

- Synchronous edge-capture.

- Asynchronous- Choice of edge or level sensitive triggering is programmable.

• Polarity is programmable for all types.

• Prioritized interrupt handler vector generation.

• Status registers provide both of the following for interrupts.

- Current state of interrupts.

- Current state of all enabled interrupts (masked with Enable register).

Phase Locked Loop (PLL)

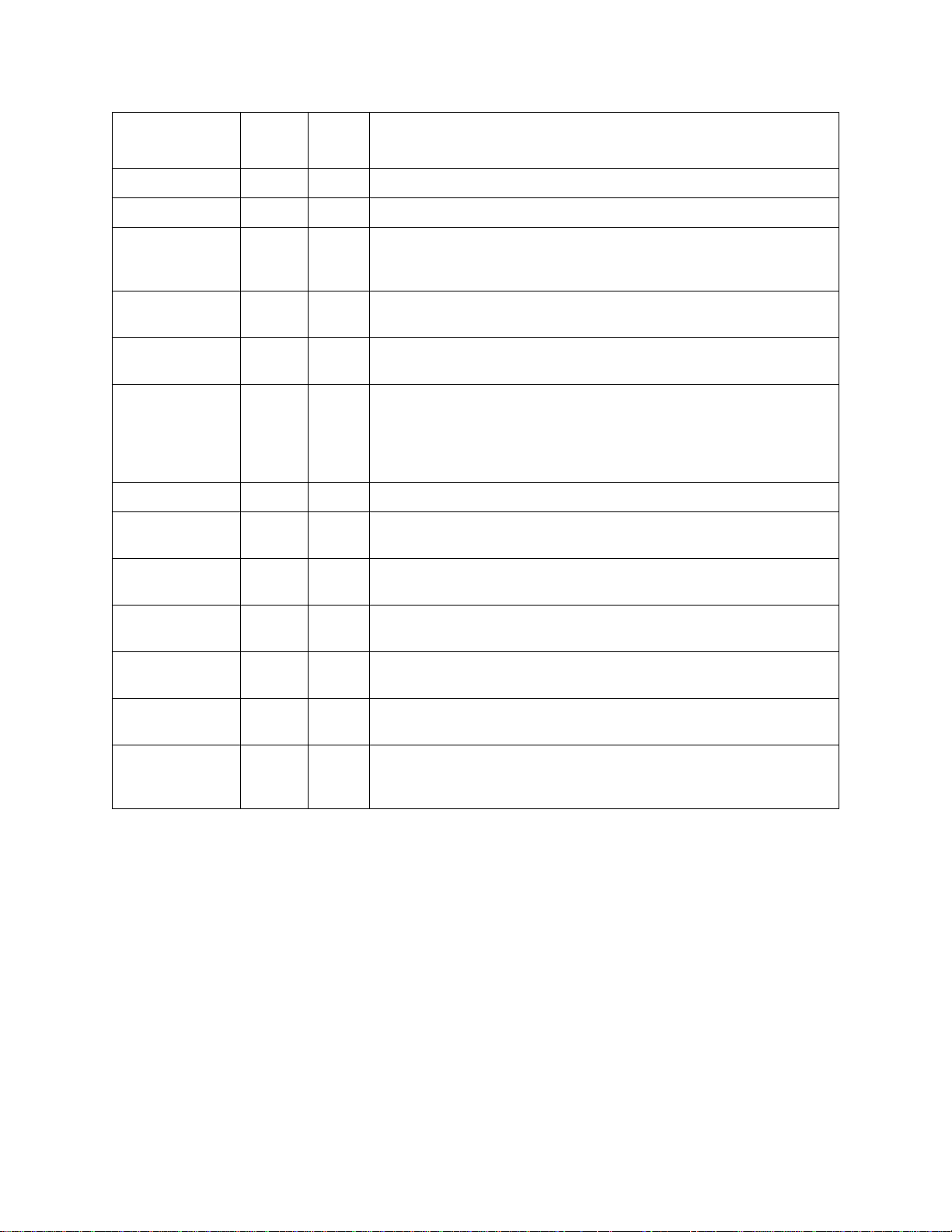

Table 2. PLL Usage

PLL Input Frequency Output Frequency Usage

PLL 0 33MHz

PLL 1 25MHz to 66MHz Same as input Async PCI Interface

The CPC700 clocking is controlled by two PLLs that minimize clock skew between the internal latches of

the CPC700 and the external devices in the system. PLL1 is only used when the PCI interface is used in

asynchronous mode. When in synchronous mode, PLL1 is placed in bypass mode via pin strappings, and

the PCI clock input pin must be pulled to ground.

33MHz UART, IIC, and Timers

66MHz All Other Cores

1-10 CPC700 User’s Manual—Preliminary

Page 27

JTAG

The IEEE 11.49.1 (JTAG) Boundary scan is included to facilitate tester requirements as well as for the

support of board level testing and debug.

The following JTAG commands are supported by the CPC700 JTAG TAP controller:

1. EXTEST

2. SAMPLE/PRELOAD

3. BYPASS

4. CLAMP

5. IDCODE

6. USERCODE

The CPC700 IDCODE value is 14940049. The CPC700 USERCODE value is 0.

Refer to IEEE 1149.1 specification for details on JTAG operation.

CPC700 User’s Manual—Preliminary 1-11

Page 28

1-12 CPC700 User’s Manual—Preliminary

Page 29

Chapter 2. Signal Descriptions

2.1 Processor Interface Signals

Active

Signal Name

Level I / O Description

DH[0:31] High I/O

DL[0:31] High I/O

DP[0:3] /

REQ[2:5]_N

DP[4:7] /

GNT[2:5]_N

- / Low I/O

- / Low I/O

Data Bus High: Processor Data bus - High 32 bits. The correspondence

of the processor data paths to byte lanes is as follows:

[DH0 - DH7] - Byte Lane 0

[DH8 - DH15] - Byte Lane 1

[DH16 - DH23] - Byte Lane 2

[DH24 - DH31] - Byte Lane 3

Data Bus Low: Processor Data bus - Low 32 bits. The correspondence

of the processor data paths to byte lanes is as follows:

[DL0 - DL7] - Byte Lane 4

[DL8 - DL15] - Byte Lane 5

[DL16 - DL23] - Byte Lane 6

[DL24 - DL31] - Byte Lane 7

Data Parity[0-3] / Request[2-5]: When the internal PCI arbiter is

disabled these signals carry the Processor Data Parity bits [0-3]. Odd

Parity is driven / received on the processor bus. The correspondence of

the Data parity pin to processor data paths is as follows:

DP0 - [DH0 - DH7]

DP2 - [DH8 - DH15]

DP3 - [DH16 - DH23]

DP4 - [DH24 - DH31]

If the internal PCI arbiter is enabled these signals carry the PCI Request

inputs [2-5] providing for a total of 6 PCI Request inputs.

Data Parity[4-7] / Grant[2-5]: When the internal PCI arbiter is disabled

these signals carry the Processor Data Parity bits [4-7]. The

correspondence of the Data parity pin to processor data paths is as

follows:

DP4 - [DL0 - DL7]

DP5 - [DL8 - DL15]

DP6 - [DL16 - DL23]

DP7 - [DL24 - DL31]

If the internal PCI arbiter is enabled these signals carry the PCI Grant

outputs [2-5] providing for a total of 6 PCI Grant outputs.

AP[0:3] - I/O

A[0:31] High I/O