Page 1

Page 2

Systems

GC20-2021-2

File No. 4300

A Guide to the IBM 4381

Processor

This guide presents hardware, 1/0 device, programming

systems, and other pertinent information describing the

significant new features and advantages

Processor. Knowledge

and 1/0 devices

intended

and

to

to

acquaint the reader with the 4381 Processor

be

of

benefit in planning for its installation.

of

System/370 or 4300 hardware

is

assumed. The content

of

the

of

IBM

4381

the guide

is

___

--...- -

----

---

-

_

- --

---

-.-

-.

---

_..._,_

---

--

Page 3

Third Edition (April

1986)

This edition

Model Groups 11, 12, 13, and 14. New and changed information

rule in the left margin.

This guide

however, the readers should remember that the authoritative sources of system

information are the system library publications for the 4381 Processor, its associated

components and its programming support. These publications will first reflect any

changes.

References in this publication to IBM products, programs, or services do not imply that

IBM intends to make these available in all countries in which IBM operates.

Publications are

publications should be made to your IBM representative or to the IBM branch office

servicing your locality.

A form for readers' comments has been provided at the back of this publication.

form has been removed, address comments to: IBM Corporation, Department 824, 1133

Westchester Avenue, White Plains, New York 10604. IBM may use or distribute

whatever information you supply in any way it believes appropriate without incurring any

obligation to you.

is

a major revision obsoleting

is

intended for planning purposes only.

not

stocked

at

the address given below. Requests for copies of IBM

GC20-2021-l.

It

discusses 4381 Processor

is

indicated by a vertical

It

will

be updated from time to time;

If

the

© Copyright International Business Machines Corporation 1984, 1985, 1986

Page 4

Preface

This publication

architecture (as implemented in a System/370 or 4300 processor), and

4300/System/370

4381 Processor model groups that are like the same features in 4341 Processors are

identified, and only those hardware and programming systems features of 4381

Processors that are different from those of 4341 Processors are described in detail.

Compatibility among the architectures implemented in 4381, other 4300, and

System/370 processors and their programming systems support

Information about the currently available 4381 model groups (11, 12, 13, and 14)

and the withdrawn model groups (

is

designed for readers who are knowledgeable about System/370

channels,

1/0

devices, and programming systems. Features of

is

also discussed.

1,

2, and 3)

is

given in this guide.

Preface

iii

Page 5

iv A Guide to the IBM 4381 Processor

Page 6

Contents

Section

Section 10: Technology and Architecture 14

10:05 Technology 14

10: 10 Architecture

Section 20: 4381 Processor Uniprocessor Model Groups 27

20:05 Instruction Processing Function

20: 10 Storage 34

20:

20:20 Channels 47

20:25 Standard and Optional Features 58

01

: Highlights 1

Introduction 14

Logic Chip, Module, and Board Design

Logic Cooling 19

Storage Technology

System/370 Architecture

System/370 Extended Architecture 23

General Description 28

Instruction Set 30

Multiply and Add Facility 32

Elementary Math Library Facility 32

Square Root Facility and Mathematical Function Facility 32

ECPS:MVS 33

ECPS:VM/370

Preferred Machine Assist 34

Processor Storage 35

Auxiliary Storage 3 7

Storage Control Function 39

15

Support Processor Subsystem 42

Components and Functions 42

System Diskette Drives 44

System Initialization 45

Natively Attached Devices 46

Support Bus Adapter 46

General Description 4 7

Device Addresses and Unit Control Words

Subchannels

General Operation of the Channels 52

Byte Multiplexer Channels 54

Block Multiplexer Channels 55

SIOF Instruction

Standard Features 58

Optional Features 60

For

21

21

21

34

System/370-XA Mode 50

For

System/370 Mode 57

28

15

For

System/370 Mode 48

Contents

V

Page 7

Section 30: 4381 Processor Multiprocessor Model Groups

30:05 Configuration Description

30:10 Instruction Processing Function

General Description

Instruction Set

63

65

61

63

61

Other Features 66

30:15 Storage 66

Processor Storage 66

Auxiliary Storage

68

Storage Control Function 70

30:20 Support Processor Subsystem 74

Components and Functions 7 4

30:25 Channels 74

General Description 74

Device Addresses and Unit Control Words For System/370 Mode 76

Subchannels For System/370-XA Mode

General Operation of the Channels

78

78

Byte Multiplexer Channels 79

Block Multiplexer Channels 79

SIOF Instruction For System/370 Mode 80

30:30 Standard and Optional Features

Standard Features

Optional Features

81

83

81

Section 40: Operator Console 84

40:05 General Description 84

Operator/Operating System Communication Modes

Operator Control Panel

Keyboard

88

86

System Configuration Displays 89

40: 10 Operator Displays 90

General Selection Display 90

40:15 Remote Operator Console Facility (ROCF)

40:20 Maintenance

Section

~O:

Virtual Storage and Address Translation 94

93

91

Virtual Storage Organization 94

Address Translation

Section 60: Reliability, Availability, and Serviceability (RAS)

60:05 Introduction

60: 10 Recovery Features

Automatic Instruction Retry

95

97

98

98

ECC Validity Checking On Processor Storage 99

1/0 Operation Retry

Machine Check Facilities

101

101

Machine Check Analysis and Logging 108

Functional Diskette 1 Logouts 109

Power System 110

15

60:

Diagnostic and Remote Support Facilities

Problem Analysis

113

113

Support Processor Subsystem Diagnostics 115

Power Controller Adapter Diagnostics 116

85

97

vi

A Guide

to

the IBM 4381 Processor

Page 8

Instruction Processing Function Diagnostics 116

Error Logout Analysis Program

11

7

System Test 117

Remote Support Facility 117

Section 70: Programming Systems Support 119

70:05

70: 10

70:15

70:20

70:25

DOS/VSE

OS/VSl

MVS/370

VM/370

MVS/XA

119

120

120

120

121

70:30 VM/Extended Architecture Migration Aid 122

70:35 Virtual Machine/System Product-Entry 123

70:40 Virtual Machine/Extended Architecture Systems Facility 124

70:45 Programming Systems Support Table 125

Section 80: Comparison Table of Hardware - 4341 Model Group 12 and 4381

Processors 127

80:05 Hardware Features of the 4341 Model Group 12 Processor and 4381 Model

Group 11, 12, 13, and 14 Processors 128

Index 134

Contents vii

Page 9

Figures

1.

The 4381 Processor and console

2.

Two 64-mm MCMs

3.

A 64-mm MCM being hand held

4.

The 4381 MCM board without any modules mounted

5.

64-mm MCMs mounted on the MCM board

MCM board mounted within the 4381 Processor

6.

7.

64-mm MCM with a portion of the heat sink cut away 20

8.

An impingement cooling nozzle · 20

9.

Logical components in a 4381 Processor Model Group 11, 12, 13,

27

2

10.

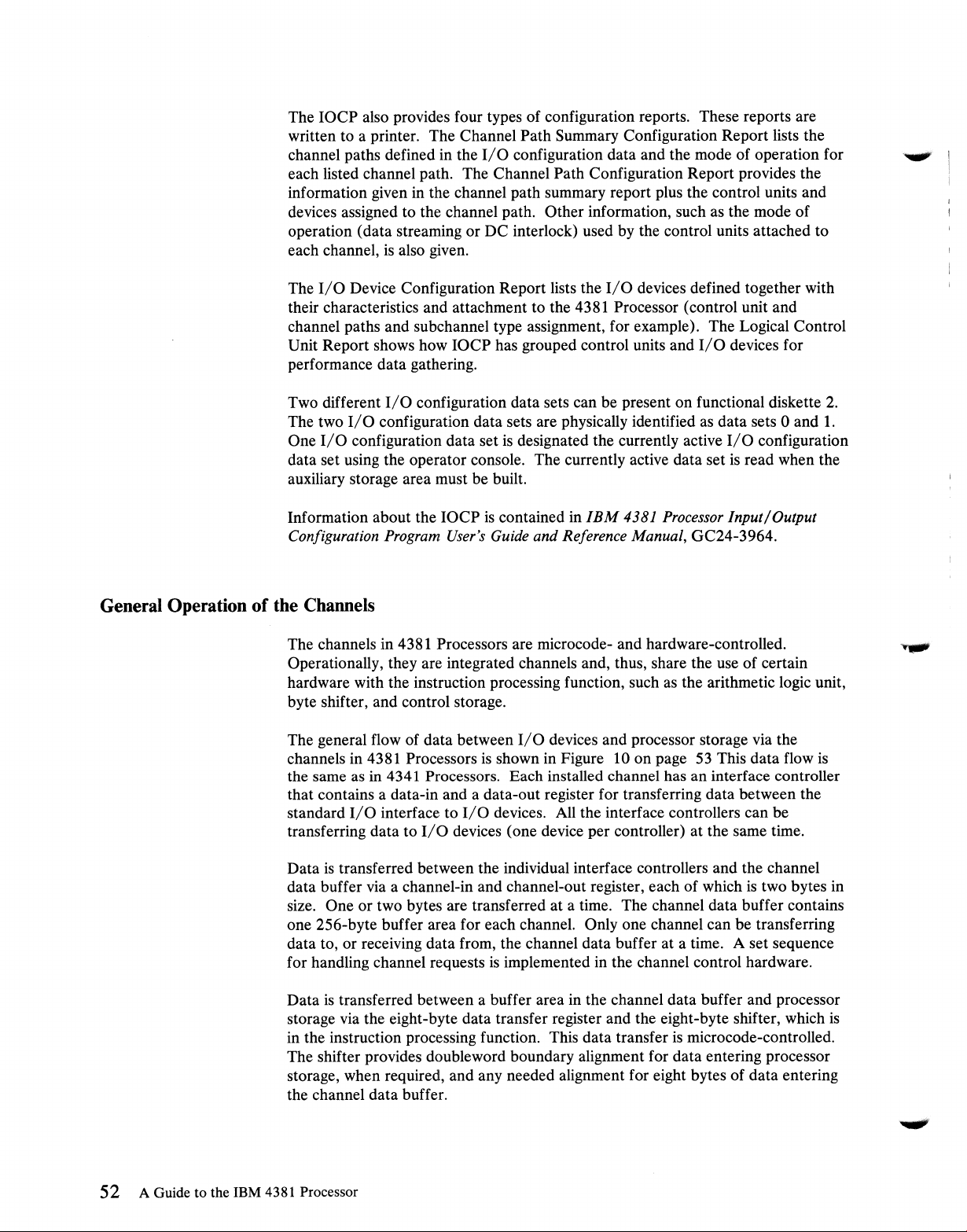

General flow of data between the channels and processor storage 53

11.

Logical components in a 4381 Processor Model Group

12.

Data flow to and from processor storage

Model Group

13. The General Selection display 90

14. Dialup of a remote 4381 Processor via a 3275 display

15. Dialup of a remote 4381 Processor

display 92

16.

4381 Processor machine check code 103

17. 4381 Processor machine check interruptions

14

or 3

16

71

12

17

18

18

19

14

or 3 62

via

the high-speed buffers in a 4381

91

via

a host processor emulating a 3275

105

1,

or

viii

A Guide to the IBM 4381 Processor

Page 10

.

..._....

Section 01: Highlights

The 4381 Processor, available in four model groups,

is

general purpose processor that

It

30XX processors.

4300, and 30XX processors) and System/370 extended architecture (as in 308X

and 3090 processors).

Model Groups 11, 12, 13, and 14 of the 4381 Processor, which offer a wide range

of performance, are provided. Model Group 11, 12, and

are uniprocessors containing one instruction execution function. The Model Group

14 4381 Processor unit

functions each of which has its own channels. The Model Group

as

operates

operating system in which processor storage

Field upgrades of 4381 Processor model groups

Group

4381 Model Group 12 can be field upgraded to a 4381 Model Group 13, and a

4381 Model Group

support provides significant performance growth. The 4381 Model Group 14 has

an internal throughput rate of up to 4.9 times that of a 4381 Model Group

commercial processing and of up to 5.4 times that of a 4381 Model Group

scientific processing.

Model Groups

performance relative to Model Groups

withdrawn from marketing,

groups. However, optional features, including processor storage upgrades, can be

installed in 4381 Model Group

withdrawn model groups can be field upgraded to the current 4381 model groups

as follows: 4381 Model Group

Group 2 to a 4381 Model Group

Model Group

a tightly coupled multiprocessing configuration under the control of one

11

Processor can be field upgraded to a 4381 Model Group 12 Processor, a

14.

implements System/370 architecture (as in System/370,

is

a dual processor that contains two instruction execution

13

can be field upgraded to a 4381 Model Group 14. This

11through14

compatible with System/370, other 4300, and

is

of the 4381 Processor offer improved price

1,

2, and 3 of the 4381 Processor, which are

as

are model upgrades within these withdrawn model

1,

2,

and 3 Processors. In addition, these

1toa4381

13

Model Group 12 or 13, 4381 Model

or 14, and 4381 Model Group 3 to a 4381

is

an intermediate-scale,

13

4381 Processor units

14

shared.

is

supported. A 4381 Model

processor unit

11

for

11

for

The 4381 Processors offer higher internal performance and improved price

performance for intermediate system users relative to 4341 Processors. This

is

improved performance

technology for logic and processor storage. The logic packaging and cooling

designs implemented in 4381 Processors provide increased logic density without the

need for water cooling.

43

81

The

data processing capabilities offered by System/370, 4300, and 30XX processors,

as

well

extended architectures.

Processors support the range of commercial and engineering/ scientific

as

the advanced functions provided by System/370 and System/370

made possible by the use of large-scale integrated

Section

01

: Highlights 1

Page 11

The 4381 Processor Model Group

processors (such

Groups 12, 13, and

larger 4341 Processor model groups, System/370 Models 155 to 168, and 303X

processors.

Relative to 4341 Processors, 4381 Processors offer intermediate system users

increased internal performance and channel performance; improved price

performance; reliability, availability, and serviceability improvements; hardware

and programming systems compatibility; System/370 extended architecture

advantages; and a wide range of operating system support.

The 4381 Processors can be utilized in decentralized and distributed processing

environments that require higher internal performance and more channel capability

than

is

provided by 4341 Processors. They can also be used in 30XX installations

to support application offloading.

The 4381 Processors are particularly well suited to handle engineering/ scientific

applications, such as

of floating-point and binary multiply operations in 4381 Processors

improved. Standard engineering/ scientific assist features can be used to further

improve floating-point arithmetic performance for selected functions.

The 4381 Processors operate with a broad spectrum of IBM products that support

engineering/ scientific applications, including the 3251 Display Station and 5080

Graphics System, 3838 Array Processor, 7350 Image Processing System, Series/1

processors, and IBM personal computers. The 4381 Processors can also be used

with the IBM Device Attachment Control Unit and 7171 ASCII Device

Attachment Control Unit to implement engineering/scientific applications that

require the use of non-IBM devices. The IBM 4994 ASCII Device Control Unit

can be channel-attached to 4381 Processors. The 3044 Fiber Optic Channel

Extender Link can be used to extend the distance between terminals/ devices and

the 4381 Processor (up to two kilometers) while providing near local terminal

response time.

as

Models

14

of the

CAD/CAM,

11

is

a logical growth processor for System/370

135

to 148) and smaller 4341 Processors. Model

43

81

Processor provide a growth path for users of

graphics, and problem solving. The performance

is

significantly

System/370 extended architecture, which

processors,

MYS/Extended Architecture (MVS/XA) operating system. Therefore, a 4381

Processor can be used for

the entry

3090 processor and MVS/XA.

The 4381 Processors have extensive operating system support. When operating

with System/370 architecture

supported by the same operating systems

System/370 mode. When operating with System/370 extended architecture in

effect (in System/370 extended architecture mode), 4381 Processors are supported

by the same operating systems

System/370 extended architecture mode.

2 A Guide to the IBM 4381 Processor

is

implemented in 308X and 3090

is

also implemented in 4381 Processors, which are supported by the

MVS/XA

MVS/XA

processor in installations that expect growth to a 308X or

testing in a 308X or 3090 installation or

in

effect (in System/370 mode), 4381 Processors are

as

4341 Processors operating in

as

308X and 3090 processors operating in

as

Page 12

Model Groups 11, 12, and

13

of the 4381 Processor operating in System/370

mode are supported by the following IBM-supplied virtual storage programming

systems (which also support 4381 Processor Model Groups 1 and 2):

• Disk Operating System/Virtual Storage Extended (DOS/VSE) with

VSE/

Advanced Functions

VSE/System Package (VSE/SP)

as

of Release 1.3.5 (the VSE System) or

as

of Release 1.3.5

• Operating System/Virtual Storage 1

(OS/VSl)

Release 7 with

OS/VSl

Basic

Programming Extensions Release 4

• Operating System/Virtual Storage 2 Multiple Virtual Storage (OS/VS2 MYS)

Release 3.8 with an MYS/System Product (MYS/SP) Version 1 Release 3.3

or 3.5 program product (MYS/System Product-JES2 or MYS/System

Product-JES3) installed and the appropriate PTF applied. This version of

is

MYS

MVS/370

• Virtual Machine/370

(VM/SP) Release 3 or later and without or with

Option Release 3.2 or later.

(MYS with MYS/SP Version 1).

(VM/370)

Release 6 with VM/System Product

VM/SP

VM/SP

High Performance Option

High Performance

is

required to

support more than l 6Mb of processor storage.

• Virtual Machine/Entry (VM/Entry)

• Airline Control Program/Transaction Processing Facility

(ACP/TPF)

Version

2.3

13

Model Groups 11, 12, and

of the 4381 Processor operating in System/370

extended architecture mode are supported by the following (which also support

4381 Processor Model Groups 1 and 2):

• MYS Release 3.8 with MYS/SP (MVS/SP-JES2 or MVS/SP-JES3) Version 2

Releases 1.2 and 1.3 and (with the appropriate PTF applied) and

Data Facility Product (the

MVS/XA

operating system)

MVS/XA

• Virtual Machine/Extended Architecture

(VM/XA)

Migration Aid Release 2

or later

Virtual Machine/Extended Architecture

(VM/XA)

The 4381 Processor Model Group 14 operating in System/370 mode

Systems Facility Release 1

is

by the following (which also support the 4381 Model Group 3):

• MVS/SP-JES2 or MVS/SP-JES3 Version 1 Releases 3.3 and 3.5

VM/SP

•

Release 3.4 or later.

Release 3 or later without or with

VM/SP

High Performance Option

VM/SP

High Performance Option

is

required to support

more than 16Mb of processor storage.

The 4381 Processor Model Group 14 operating in System/370 extended

is

architecture mode

supported by the following (which also support the 4381

Model Group 3):

1.1

or

1.3

• MVS/SP-JES2 or MVS/SP-JES3 Version 2 Release

with the

appropriate PTFs applied.

Section

01

: Highlights 3

supported

Page 13

•

•

VM/XA

VM/XA

Migration Aid Release 2 or later

Systems Facility Release 1

The hardware facilities of, and

effectively be used by the MVS/370, MVS/XA, and

To aid in the transition from

Processor, two migration aids are provided (see discussion in Section 70:05). Less

effort

is

required to convert from

MVS/370

operating systems.

Highlights of 4381 Processor Model Groups 11, 12, 13, and 14 are as follows:

• Upward compatibility with 4300 System/370 mode, System/370, and 30XX

operate in 4341 Processors under a

implemented in 4341 Processors

The System/370 extended architecture mode of operation, not provided in

4341 Processors,

compatibility for most 4300, 30XX, and System/370 problem programs and

most

extended architecture support, such as MVS/XA.

because of the basic compatibility between the

architecture and programming systems has been maintained in 4381 Processors

through implementation of the System/370 mode of processor operation. This

mode provides compatibility for 4300 System/370 mode, System/370, and

30XX control programs and problem programs. Problem programs that

can also operate in a 4381 Processor under a

supervisor if they are not processor- or time-dependent. The ECPS:VSE mode

is

also implemented in 4381 Processors. This mode provides

MVS/370

subsystems but requires a control program with System/370

1/0

devices for, 4381 Processors can most

VM/370

DOS/VSE

to

MVS/370

OS/VSl

to

MVS/370

DOS/VSE

is

not implemented in 4381 Processors.

with installation of a 4381

than from

OS/VSl

ECPS:VSE mode supervisor

DOS/VSE

operating systems.

DOS/VSE

and

OS/VS2

System/370 mode

to

• The following are instruction processing function features of 4381 Processors.

is

Instruction processing function logic

technology. Logic chips (704-circuit) with faster circuit speeds than the

704-circuit chip used in most 4300 Processors are used in 4381 Processors.

However, the logic packaging and cooling technique implemented

Processors significantly increase the logic circuit density on a logic board

without the need for water cooling. (See Section 10:05 for a detailed logic

technology discussion.)

Implementation of a System/370 mode and a System/370 extended

architecture (System/370-XA) mode

architecture implemented for System/370 mode operations includes nearly all

the extensions implemented in large-scale processors, such as the 308X and

3090.

System/370 extended architecture

changes and additions. The major new functions provided by this architecture

are 31-bit addressing and dynamic channel subsystem architecture. The 31-bit

addressing capability enables two gigabytes (over 2 billion bytes) of virtual

storage and real storage to be addressed, versus a maximum of over 16 million

bytes for the 24-bit addressing supported by System/370 architecture. A

bimodal operation

addressing and programs that use 31-bit addressing to operate concurrently

when System/370-XA mode

is

supported that permits programs that use 24-bit

is

in effect.

implemented in large-scale integrated

in 4381

is

standard. The System/370

is

System/370 architecture with certain

4 A Guide to the IBM 4381 Processor

Page 14

The dynamic channel subsystem architecture eliminates channel addressing,

all

1/0

supports queuing of

requested

interruption mechanism and extended

1/0

operations in hardware, and supports an expanded

requests, provides channel path selection for

1/0

device addressing.

1/0

all

The mode in which the 43

operator at initial microcode load (IML) time. The mode selected remains in

effect until another IML

System/370-XA mode microcode to be used for this IML.

The cycle time of 4381 Model Group

For 4381 Model Groups

The instruction processing function design provides increased instruction

execution performance. Instruction prefetching

the overlap of instruction fetching with instruction execution during sequential

instruction processing. In addition, an eight-byte-wide arithmetic logic unit

used that enhances the performance of decimal and floating-point operations.

Improvements in the number of functions performed during the instruction

cycle of 4381 instruction execution (like those in 4341 Processors) result in the

faster execution of many other instructions, most of which are among the more

frequently used instructions.

The standard instruction set for 4381 System/370 mode of operation provides

decimal, binary, and floating-point arithmetic operations (including the

extended floating-point format that provides the equivalent of up to 34 decimal

digits).

instruction set defined for System/370 except for direct control and RESUME

1/0

Section

are also standard.

For

4381 Model Groups 11, 12, and 13, it consists of the entire

instructions and those associated with multiprocessing (as discussed in

10: 10). For the 4381 Model Group 14, multiprocessing instructions

81

Processor

is

performed and causes the System/370 mode or

13

and 14, cycle time

is

to operate

11

and 12 Processors

is

56 nanoseconds.

is

implemented that results in

is

determined by the

is

68

nanoseconds.

is

The standard instruction set for 4381 System/370-XA mode of operation

includes all the instructions defined for System/370 extended architecture. All

the semiprivileged and all the nonprivileged instructions in System/370

architecture are also defined for System/370 extended architecture but

differences exist in the set of privileged instructions supported by the two

architectures (see Section 10:

Three engineering/scientific assists are provided for 4381 Processors. The

Multiply and Add Facility

It

is

14.

computations, such as matrix inversion, decomposition, and multiplication.

These computations are used, for example, in finite element analysis, linear

programming, and statistical analysis. This feature supports only long-format

(64-bit) floating-point numbers and can provide a reduction in instruction

processing function busy time of up to

by the MULTIPLY AND ADD instruction (see Section 20:05).

The Square Root Facility

to improve the performance of square root operations involving long- or

short-precision floating-point arithmetic.

designed to improve the performance of certain mathematical

10).

is

standard in 4381 Model Groups 11, 12, 13, and

35

percent for the instructions replaced

is

standard in 4381 Model Groups 11, 12, 13, and 14

Section

01:

Highlights 5

Page 15

The Mathematical Function Facility (not implemented in 4341 Processors)

standard in 4381 Model Group 12, 13, and

of eight register-to-register floating-point instructions that perform elementary

mathematical functions. The supported functions are exponentiation and

natural and common logarithms. The instructions support short and long

precision for the two operands involved (see Section 20:05). This facility

reduces processor busy time by up to

permits selected scientific subroutines to be executed faster than with

conventional programming (FORTRAN subroutines).

Timing and debugging features like those in System/370, 30XX, and other

4300 Processors (3.3-ms-resolution interval timer, time-of-day clock, CPU

timer, clock comparator, monitoring feature, and program event recording) are

standard in 4381 Processors. The time-of-day clock and CPU timer have a

one-microsecond resolution.

The standard byte-oriented operands facility permits byte boundary alignment

for the operands of nonprivileged instructions, making it unnecessary to add

padding bytes within records or to blocked records to align fixed- or

floating-point data. In 4381 Processors, minimal performance degradation

results from the use of unaligned data.

Functions of the System/370 Extended Facility/Feature for 30XX Processors

are standard in 4381 Processors. These facilities are low address protection (to

protect the contents of locations 0 to 511 from accidental modification), the

TEST PROTECTION and INVALIDATE PAGE TABLE ENTRY

instructions (for control program use), the common segment facility (to

improve address translation performance for

environments), MYS-dependent instructions (ECPS:MVS feature in 4381

Processors), and Virtual Machine Extended Facility Assist.

14

Processors and provides a group

65

percent for the assisted functions.

MYS

and

VM/370

is

It

The facilities provided by the 3033 Extension feature for 30XX Processors are

standard in 4381 Processors. The Dual Address Space Facility for both modes

(which improves the performance of MYS/SP Cross Memory Services),

1/0

START

(which

MYS assists (included in the 4381 ECPS:MVS feature) are implemented in

4381 Processors. The suspend and resume facility provided by the 3033

Extension feature

but a comparable function

System/370-XA mode.

Dynamic address translation and channel indirect data addressing features to

support a virtual storage

For System/370 mode (which uses 24-bit addressing), one virtual storage of

16,777,216 bytes (16Mb) maximum or multiple virtual storages up to

16M-bytes each can be supported. For System/370-XA mode (which uses

31-bit addressing), one virtual storage of up to 2,147,483,648 bytes (2

gigabytes) or multiple virtual storages of up to 2 gigabytes each can be

supported.

A segment protection facility (not provided for 4341 Processors) that provides

the ability to prevent stores to protected virtual storage segments

for System/370 mode. For System/370-XA mode, a page protection facility

FAST RELEASE instruction queuing for System/370 mode only

is

basic to the System/370-XA mode channel subsystem), and two

is

not implemented for 4381 System/370 mode of operation

is

basic to the channel subsystem defined for

and/

or virtual machine environment are standard.

is

standard

is

6 A Guide to the IBM 4381 Processor

Page 16

provided instead of the segment protection facility. Page protection can be

used to prevent any writing in protected 4K pages of virtual storage.

A

VM/370

hardware assist function (ECPS:VM/370) and an MVS hardware

assist facility (ECPS:MVS) are standard in 4381 Processors. ECPS:VM/370

and ECPS:MVS can be used concurrently to improve performance when

MVS/SP Version 1 executes in a virtual machine under the control of

VM/370

with the VM/System Product.

ECPS:VM/370 consists of the Virtual Machine Assist, Control Program

Assist, Expanded Virtual Machine Assist, Virtual Interval Timer Assist, and

It

Shadow-Table Bypass Assist components.

System/370 mode

ECPS:MVS consists of

is

in effect.

13

privileged instructions and the page fault assist

function, all of which are operative during System/370 mode operations.

of the

13

instructions are operative for System/370-XA mode operations. The

can be used only when

Six

standard Virtual Machine Extended Facility Assist enables the ECPS:MVS

instructions to be executed directly by an MVS virtual machine to improve

performance.

is

Preferred Machine Assist (not provided for 4341 Processors)

standard in

4381 Processors and can be used only during System/370 mode operations.

is

designed to improve the performance of MVS/SP Version 1 running in a

preferred virtual machine.

It

is

Instruction retry

standard to attempt to correct errors that occur during

instruction execution without programming assistance. For certain hardware

facilities (reloadable control storage, channel buffers, and the high-speed

buffer and its swap buffer), the instruction retry facility provides automatic

hardware reconfiguration to assign spare storage when a retry does not correct

an error. The reconfiguration facility permits continued system operation,

is

without performance degradation in some cases. Maintenance

is

when reconfiguration

no longer possible.

performed

The following are significant storage features of 4381 Processors.

All storage in a 4381 Processor-processor, control, high-speed buffer, and

local-is

implemented using monolithic technology. The technology used for

processor storage in 4381 Processors provides much denser storage chips (64K

as

bits per chip

above 16Mb) than

in 4341 Processors and a 256K-bit chip for processor storage

is

used in System/370, 303X, or 308X processors (2K, 4K,

or 16K bits per chip).

is

A two-level storage system

as

storage used

backing storage for a smaller high-speed buffer storage. The

implemented, consisting of large processor

instruction processing function works mostly with the high-speed buffer so that

is

the effective processor storage cycle

a fraction of the actual processor

storage cycle.

4K bytes for a 4381 Model Group 11, 32K bytes for a 4381 Model Group 12,

13

and 64K bytes for a Model Group

K=

1024) are standard. The full buffer size

is

effect

4K bytes. When page size

12, only half of the high-speed buffer

of high-speed buffer storage (where

is

used when the page size in

is

2K bytes in a 4381 Model Group

is

used. A doubleword of data

11

is

fetched

or

Section

01

: Highlights 7

Page 17

from the buffer in 68 nanoseconds and stored in the buffer in 102 nanoseconds

for 4381 Model Groups

11

and 12.

For

a 4381 Model Group 13,

56

or

84

nanoseconds are required for a fetch or store, respectively.

For

the 4381 Model Group 14, each of the two instruction processing

functions has its own dedicated 64K-byte high-speed buffer as a standard

feature. These two high-speed buffers operate using 4K-byte pages only.

Facilities for the required high-speed buff

er

communication in a

multiprocessing environment are implemented in the Model Group 14,

er

data

including buffer-to-buff

transfer.

4Mb, 8Mb, and 16Mb of processor storage are available for the 4381 Model

Group

(where

M=l,048,576).

For

4381 Model Group 12 and 13

11

Processors, 8Mb, 16Mb, 24Mb, and 32Mb are available. A Model Group 14

or

can have 16Mb, 24Mb,

32Mb of processor storage. Store and fetch

protection and reference and change recording are standard. Store and fetch

protection are provided

processors with up to 16Mb installed.

16Mb installed, store and fetch protection are provided

of

A portion

not

will

highest addressed installed processor storage in a 4381 Processor

be accessible to programs, as in 4341 Processors. The amount of

on

a 2Kb basis (one key for each 2Kb) for 4381

For

4381 processors with more

on

a 4Kb basis.

than

unavailable processor storage for 4381 Processors (called auxiliary storage) is a

of

minimum

64Kb (104Kb for the Model Group 14) for

operation for the minimum number

System/370-XA

mode, a minimum of l 12Kb (220Kb for the Model Group

of

UCWs (128) defined.

System/370

For

mode

of

14) of auxiliary storage is required for zero subchannels and 128 control units

defined.

Reloadable control storage

instruction processing function

writable, instead

of

read-only, control storage offers the advantages of

contain all the microcode required

of

4381 Processors is standard. Use

by

the

of

to

improved system serviceability and ease of optional feature and engineering

change installation.

The TEST BLOCK instruction (not implemented in

to

provided to enable the control program

processor storage

unusable because

and/

or

their associated one

of

uncorrectable errors. Known unusable blocks and keys

determine which 4Kb blocks of

4341 Processors) is

or

two storage protect keys are

are saved across power-offs. This instruction can also be used for processor

storage validation.

The TEST BLOCK instruction enables the operating system

of

4Kb blocks from its list

assignable page frames and prevents abnormal

program terminations that could result from the uncorrectable storage errors.

Error checking and correction

(ECC)

hardware

is

standard.

corrects all single-bit processor storage errors, and detects

all double-bit and most multiple-bit errors. Correction

consist

4341 Processors)

of

one solid and one intermittent error (which

is

also provided via microcode (see discussion in Section

to

delete unusable

<

It

automatically

but

does

not

of

double-bit errors that

is

not

implemented in

correct

60:10).

8 A Guide to the IBM 4381 Processor

Page 18

The following channel features are provided for 4381 Processors.

Two channel groups are available for Model Groups 11, 12, and 13. The

standard channel group consists of one byte multiplexer and five block

5.

multiplexer channels addressed 0 through

consists of six block multiplexer channels addressed 6 through

The optional channel group

B.

Block

multiplexer channel 5 in the standard channel group can be configured as a

as

byte multiplexer instead of

For

the 4381 Model Group 14, one channel group consisting of one byte

multiplexer channel (0) and five block multiplexer channels

a block multiplexer channel.

(1

through 5)

is

standard for each of the two instruction processing functions. The fifth block

as

multiplexer channel in each channel group can be configured

a byte

multiplexer channel. Optionally, one additional channel group, which provides

three additional block multiplexer channels for each channel group (a total of

six additional channels) can be installed.

is

Functionally, a byte multiplexer channel for a 4381 Processor

equivalent to

that for System/370, 30XX, and other 4300 processors. The standard

(channel 0) and optional (channel 5) byte multiplexer channels in Model

Groups 11, 12, and

each have a

24Kb/sec

maximum data rate (28Kb/sec

13

for the Model Group 14) for one-byte transfer operations for byte mode

mod.e

1/0

operations. Unbuffered.burst

devices cannot be attached to the

byte multiplexer channels in a 4381 Processor.

is

Functionally, a block multiplexer channel in a 4381 Processor

equivalent to

that for System/370, 30XX, and 4300 processors. A block multiplexer

channel in 4381 Processors can also operate in selector channel mode.

is

The data streaming mode of channel operation that

is

30XX Processors

standard for all the block multiplexer channels in a 4381

provided for 4341 and

Processor. Data streaming mode enables certain 4381 channels to handle

faster data rates (up to 3Mb/sec) over a longer channel-to-control unit cable

length for attached control units that are also capable of operating in data

streaming mode (see discussion in Section 20:20). Both data streaming and

nonstreaming devices can be attached to the block multiplexer channels in a

4381 Processor.

For

the standard channel group in a 4381 Model Group 11, 12, or 13, the

is

maximum aggregate data rate

a Model Group 11, the maximum aggregate data rate

22Mb/sec

maximum aggregate for eleven block multiplexer channels.

14 Mb/sec. For the optional channel group in

is

8Mb/sec, providing a

For

a

Model Group 12, the optional channel group has a maximum aggregate data

rate of lOMb/sec, providing a 24Mb/sec maximum aggregate for the eleven

block multiplexer channels. The maximum aggregate data rate for the optional

channel group in a Model Group

16Mb/sec, with a

30Mb/sec

maximum

13

is

aggregate data rate for eleven block multiplexer channels.

For

the Model Group 14, a maximum aggregate data rate of

ten block multiplexer channels (15Mb/sec for each channel group)

The maximum aggregate data rate for 16 block multiplexer channels

36Mb/sec

(18Mb/sec

for each eight-channel group).

30Mb/sec

is

possible.

is

for the

Channels with data rates of up to 3

Mb/sec

and the block multiplexing

capability support attachment to the 4381 Processor of 3380, 3375, 3370,

Section 01: Highlights 9

Page 19

3330-series,

have rotational position sensing capability and can be used only with block

multiplexer channels.

Optionally, one Channel-to-Channel Adapter can be installed in a 4381

Processor (any model group) and attached to any block multiplexer channel.

The adapter can be used to connect a channel in a 4381 Processor to a channel

in a System/360, System/370, 30XX, 4321, 4331, 4341, 4361, or another

4381 Processor. Alternatively, the 3088 Multisystem Channel Communication

Unit can be used to interconnect the 4381 Processor with certain other

processors via channels.

3340/3344,

and 3350 direct access storage. These disk devices

The fast release function of the START

instruction (implemented only in Model Group 12 4341 Processors) and

queuing of SIOF instructions (not implemented in 4341 Processors) are

standard features in 4381 Processors. These functions are designed to reduce

I/

0 processing time.

A 3205 Color Display Console, or a 3278 Model 2A Display Console or 3279

Model 2C Color Display Console equipped with an operator console keyboard

and operator control panel feature

4381 Processor. Display mode and (for System/370 mode only) a

printer-keyboard mode are standard. The display console natively attaches to

4381 Processors. The display console

operator-to-operating system communication, and by the customer engineer to

perform diagnostic functions.

Up to three displays

Processor in addition to the required 3205, 3278 Model 2A, or 3279 Model 2C

console. The additional three units can be 3205 Color Display Consoles, 3278

Model 2A Display Consoles, 3279 Color Display Consoles Model 2C, 3268

Model 2 Printers, 3268 Model 2C Color Printers,

1,

2, 1 C,

and/

cannot be installed together with 3278 Model 2A or 3279 Model 2C displays.

The additional displays can be used

The 3287 or 3268 Printer can be used for hard-copy backup of an operator

console that operates in display mode. Models

3268 Model 2C provide color printing. A printer

hard-copy output when the display console operates in printer-keyboard mode.

and/

or printers can be natively attached to a 4381

or 2C in any combination with the restriction that 3205 displays

1/0

FAST RELEASE (SIOF)

is

required as the operator console for a

is

used for manual operations,

as

alternate

and/or

and/

lC

is

3287 Printers Models

or additional consoles.

and 2C of the 3287 and the

recommended for

10 A Guide to

the

IBM 4381 Processor

The Remote Operator Console Facility (ROCF), a no-charge specify option

that requires the Remote Support Facility, gives an operator at a host location

the ability to dial up and control a powered-on remote 4381 Processor using a

3275 Display Terminal or an emulated 3275 attached to a host processor.

Host processor program support for ROCF

MVS/XA, and

discussion in Section 40:15).

1/0

devices that attach to 4341 Processors and that are available from IBM

will also attach to 4381 Processors.

The Device Attachment Control Unit (DACU) can be attached to a block

multiplexer channel in 4381 Processors. The DACU provides two commonly

used industry interfaces for the attachment of non-IBM

VM/370

with the appropriate program products installed (see

is

provided by MVS/370,

1/0

devices: UNIBUS

Page 20

(a registered trademark of the Digital Equipment Corporation), which provides

a parallel direct memory access (DMA) interface, and EIA RS-232C, which

an industry standard serial communication interface. The DACU permits

attachment of a wide variety of non-IBM

sensors, graphic devices, laboratory instruments, and minicomputers. This

control unit makes a 4381 Processor suitable for a variety of engineering and

scientific applications.

• The large-scale integrated technology implemented in 4381 Processors for

most logic and all processor storage provides higher internal performance,

increased reliability, and compact processor unit design. The module-on-board

logic packaging eliminates one entire level of packaging (logic cards), and the

impingement cooling technique assures adequate cooling of the high-density

logic modules using only room-temperature air

technology discussion in Section 10:05.)

• The power system hardware in 4381 Processors

power hardware used in most 4341 Processors. The 4381 power hardware

increases reliability, reduces space requirements, and aids serviceability.

Improvements in the fault-locating ability and the usability of power

diagnostics have also been made.

• Extensive hardware and programming systems error recovery and repair

features for 4381 Processor hardware errors are provided to improve system

availability and serviceability. These features include enhanced facilities

implemented in other 4300 Processors, such

data after a hardware error occurs to generate a reference code that identifies

the field-replaceable unit or the procedure to follow to attempt to locate the

malfunction. Additional recovery facilities (such as double-bit error correction

and hardware reconfiguration) are implemented.

1/0 devices, such

as

the cooling medium. (See

is

totally different from the

as

automatic diagnosis of logout

as

plotters,

is

is

The Problem Analysis facility

designed to be used by the operator to aid in problem determination and can

result in faster fault isolation and reduced system downtime.

usability and functional improvements over the Problem Analysis facility

provided for 4341 Processors (see discussion in Section 60: 15).

Inquiry into a remote data bank by the on-site customer engineer and remote

diagnosis of hardware failures by IBM support center personnel are supported

via the recommended, no-charge Remote Support Facility (RSF), which

functionally like RSF for 4341 Processors.

The physical components of a 4381 Processor configuration are a 4381

Processor, an operator console (a 3205 Color Display Console, 3278 Model

2A Display Console, or 3279 Model 2C Color Display Console), and

devices. The 4381 Processor, which

page 12.

The 4381 Processor unit contains two diskette drives (instead of one

4341 Processor). These drives (shown in Figure 1 on page 12 are easily

accessible to the operator and space

store diskettes not in use. The second diskette drive

System/370 extended architecture functions and operations and enables more

as

diagnostics (such

Problem Analysis) to be online for ease of use. Two

provided for 4381 Processors. This facility

It

provides

is

air-cooled,

is

provided to the left of the two drives to

is

shown in Figure 1 on

is

required to support

1/0

as

is

is

in a

Section

01

: Highlights

11

Page 21

different operational diskettes (called functional diskette 1 and functional

diskette 2) are provided for the two diskette drives.

Figure 1. The 4381 Processor and console

While the logical designs of the functional components of a 43

very similar to

physical components in a 4381

The

logic package, the cooling components,

support processor, the diskette drives, and the

hardware are different in 4381

improve speed

The

upright design

the

4381 Processor unit is the same size for all 4381 model groups

3

and

11through14).

a raised floor and thus

The

4381 Model

provides twice the internal performance

occupies

the heat,

Model

Group 1 but

dissipates

Group

69%

and

weighs

Group

occupies

99%

1.

These comparisons assume a 4341 without a Channel-to-Channel

the

designs in a 4341 Processor, the physical design

and

4341 Processor are different.

power

and

4341 Processors. These differences

and

reliability, reduce cost,

of

the 4381 Processor also reduces space requirements

Any

4381 model group can

can

be

placed in end-user work areas.

Group

of

11

provides twice the internal performance

of the heat, and weighs

12 has

about

the floor space, uses

84%

as much as a 4341 Model

69%

of the floor space, uses

and/

twice the number of logic circuits

of

the 4341 Model

89%

of the power, dissipates

95%

hardware components, the

Channel-to-Channel

or reduce space requirements.

be

installed with

Group

107%

as much as the 4341 Model

81

Processor are

and

Adapter

(1

or

Group 2 but

83%

2.

The

4381

of

the

4341 Model

of the power,

most

and

through

without

and

of

12 A Guide to the IBM

4381

Processor

Page 22

Adapter, which requires an additional frame in a 4341 Processor but not in a

4381 Processor.

In summary, 4381 Processors offer intermediate system users:

• Improved internal performance, price performance, and channel performance

relative to 4341 Processors

• Improved engineering/ scientific performance relative to 4341 Processors

• Implementation of nearly all System/370 architecture facilities and all the new

facilities of System/370 extended architecture

• Compatibility with other 4300, 30XX, and System/370 processors

• A full range of operating system support for both System/370 and

System/370-XA modes

• Improved reliability and availability characteristics and the expanded

serviceability functions implemented in 4341 Processors

• Evolutionary logic technology packaging that provides greater logic chip

densities with air cooling

• Reduced floor space requirements relative to 4341 Processors

• Four field upgradeable models that provide a wide range of performance and

nondisruptive growth

Section

01

: Highlights

13

Page 23

Section 10: Technology

10:05 Technology

Introduction

The price performance and compact size of the 4381 Processor unit have been

achieved in part through the use of large-scale integrated bipolar semiconductor

technology for logic chips and large-scale integrated packaging of logic chips. In

addition, a 64K-bit and 256K-bit dynamic storage chip are used for processor

storage.

Large-scale integrated technology and packaging are utilized to increase logic

circuit density. The major benefits of increased circuit density are faster logic

speed and higher logic reliability. In addition, logic cost and space requirements are

reduced.

The speed of logic circuitry

shorter the distance, the less the time it takes for the signals to travel from one

circuit to another, and

power reduces the total amount of heat generated by the circuitry, which reduces

the total amount of cooling required. However, the higher density of circuits

concentrates the heat that

and

Architecture

is

affected by the distance signals have to travel. The

at

the same time less power

is

generated in a smaller area.

is

consumed. The use of less

14 A

Guide

to the

IBM

is

The reliability of logic circuitry

interconnections and (2) level of packaging (location and wire length) at which the

interconnections occur (which determines the number of times an electrical current

must flow between dissimilar materials). External connections (the wiring among

circuits) are the least reliable part of logic circuitry. Thus, circuit connections made

on a chip are more reliable than those made off a chip. Reductions in the number

and length of external connections (those made off the chip via a card or board, for

example) improve reliability.

The large-scale integrated (LSI) technology in which the logic in the 43

Processor

4341 Processors but provides faster circuit speeds. The packaging of 4381 logic

chips on a ceramic substrate

Processors and

fewer chips are placed on a substrate for the 4381 Processor than for the 308X

Processor Unit to reduce cooling requirements. The packaging of a logic module

4381

Processor

is

implemented

is

similar to the packaging used for 308X logic modules; however,

is

related to the ( 1) number of circuit

81

very similar to the LSI technology implemented in

is

an extension of the packaging used in 4341

Page 24

and the cooling process used in 4381 Processors had not been implemented in IBM

processors before the 4381.

is

The multilayer logic board design first used in the 3081 Processor Unit

in the 43

for the 4381 Processor eliminate

and increase logic speed relative to the 4341 implementation. Logic in the 4381

utilizes advanced features that were first used to package logic chips in other 4300

Processors but extends these features to significantly increase the circuit density of

a substrate.

Logic wiring in IBM processors other than the 4381, 308X, and 3090 occurs at

several levels. First, elementary components (transistors, diodes, and resistors) on

a chip are connected to form circuits, which are then interconnected at the chip

level. Additional circuit connections are then made at the logic module level (that

is,

(card-on-board packaging) and circuit connections among the cards on the same

board and among cards on different boards are made via cabling. This design

used in 4300 Processors other than 4381 Processors.

81

Processor. The logic module packaging and logic module board design

an

entire level of packaging, aid logic reliability,

within the substrate) and at the card level. Cards are mounted

on

also used

boards

is

Logic

Chip,

Module,

Card-on-board packaging

unit. Instead, logic modules are mounted directly on a multilayered board, which

provides the ability to interconnect the logic modules

wiring, thus eliminating most intraboard cabling.

and

Board

The logic chip used in the 4381 Processor unit

(approximately

components (resistors, diodes, and transistors). The 7000 elementary compone,1ts

on

The logic chip for the

(704) as the chip used in other 4300 Processors. However, a slightly different

technology than

4381 chip. This technology reduces the size of the transistors

more power

1.15 nanoseconds for 4381 Model Groups 11, 12,

one-half that of the 4341 Model Group 2 logic chip) and a chip circuit speed of

nanoseconds for 4381 Model Groups

Of the 704 circuits available

in the logic implemented in the

per chip

interconnections on the chip itself. A logic chip in the

several feet of wire that interconnects the elementary components and circuits

the chip.

Design

3/16

a chip can be connected to form a maximum of 704 logic circuits.

is

used for the 704-circuit chip in 4341 Processors

is

used. These differences result in a 4381 chip circuit speed that

is

made possible in part because three layers of wiring are used for

is

not used for most of the logic in the 4381 Processor

on

the board via imbedded

is

4.57 by 4.57 millimeters

of an inch square) and contains over 7000 elementary

43

81

Processor has the same maximum logic circuit capacity

is

used for the

on

a 4381 chip and

1,

2, and 3 (approximately

13

and 14.

on

a single chip, the average number actually utilized

43

81

Processor

is

650. The high circuit utilization

43

81

Processor can contain

is

.7

on

The

43

81

logic chips are mounted on a multilayer ceramic substrate that

millimeters (about 2.5 inches) square and 5.5 millimeters (.2 of an inch) thick,

which

is

larger than the ceramic substrate for 4341 Processor logic

by 50 millimeters or approximately 2 inches square) but smaller than the ceramic

substrate for the 3081 logic module (90 millimeters, about 3.5 inches, square).

Section 10: Technology and Architecture

is

(SO

millimeters

64

15

Page 25

The 64-millimeter (mm) ceramic substrate for the 4381 has 36 chip positions,

which compares to 9 positions maximum per 4341 ceramic substrate.

On

average,

30 logic chips are mounted on a ceramic substrate in a 4381 Processor. The

64-mm substrate, which

is

called a multichip module (MCM),

is

shown in Figure

Logic and array chips can be intermixed on the ceramic substrate used in the 4381

logic module. The mixing of logic and array chips on a substrate was first done in

4331 and 4341 Processors. This approach permits arrays to be located closer to

the logic that utilizes them and, therefore, increases logic speed.

""1llJlf

2.

Figure 2. Two

16

A Guide to the IBM 4381 Processor

64-mm

MCMs

The 4381 ceramic substrate contains from 20 to 32 layers for interconnecting the

mounted chips. The ceramic substrate has 882 pins brazed to the bottom of it to

input/

provide

output and power capabilities. This compares with 361 pins in the

SO-millimeter logic module in a 4341 Processor.

The MCM

(including the attached heat sink used for cooling as described later)

is

the basic field-replaceable unit (FRU) for 4381 logic. The module

is

35

millimeters (about 1.4 inches) high and weighs 250 grams (a little over one-half a

pound). An MCM can be quickly and easily removed from the MCM board and

replaced with another MCM. Figure 3 on page

17

shows an MCM being hand

held.

The advances implemented in the ceramic substrate for 4381 logic can be seen by

23

layers

comparing it with the substrate for 4341 Processors. A maximum of

present in the 50-mm ceramic substrate used in 4341 Processor logic.

On

is

average,

six chips are contained in the 50-mm module.

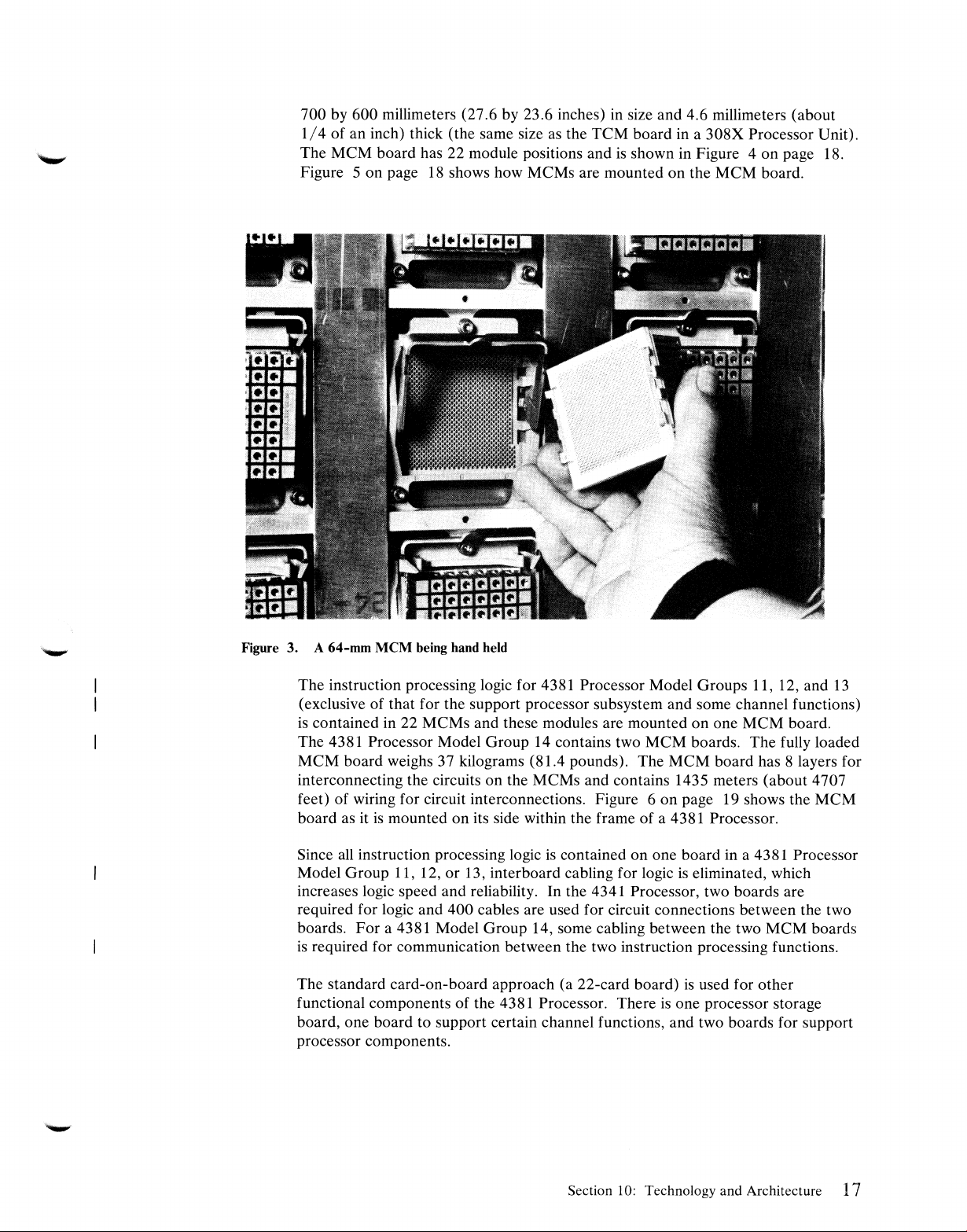

The MCMs for the 4381 Processor are mounted directly on a multilayer board

similar to that used in 308X processors. The MCM board for a 4381 Processor

is

Page 26

700 by 600 millimeters (27.6 by 23.6 inches) in size and 4.6 millimeters (about

1/4

of an inch) thick (the same size as the TCM board in a 308X Processor Unit).

is

The MCM board has 22 module positions and

Figure 5 on page

18

shows how MCMs are mounted on the MCM board.

shown in Figure 4 on page 18.

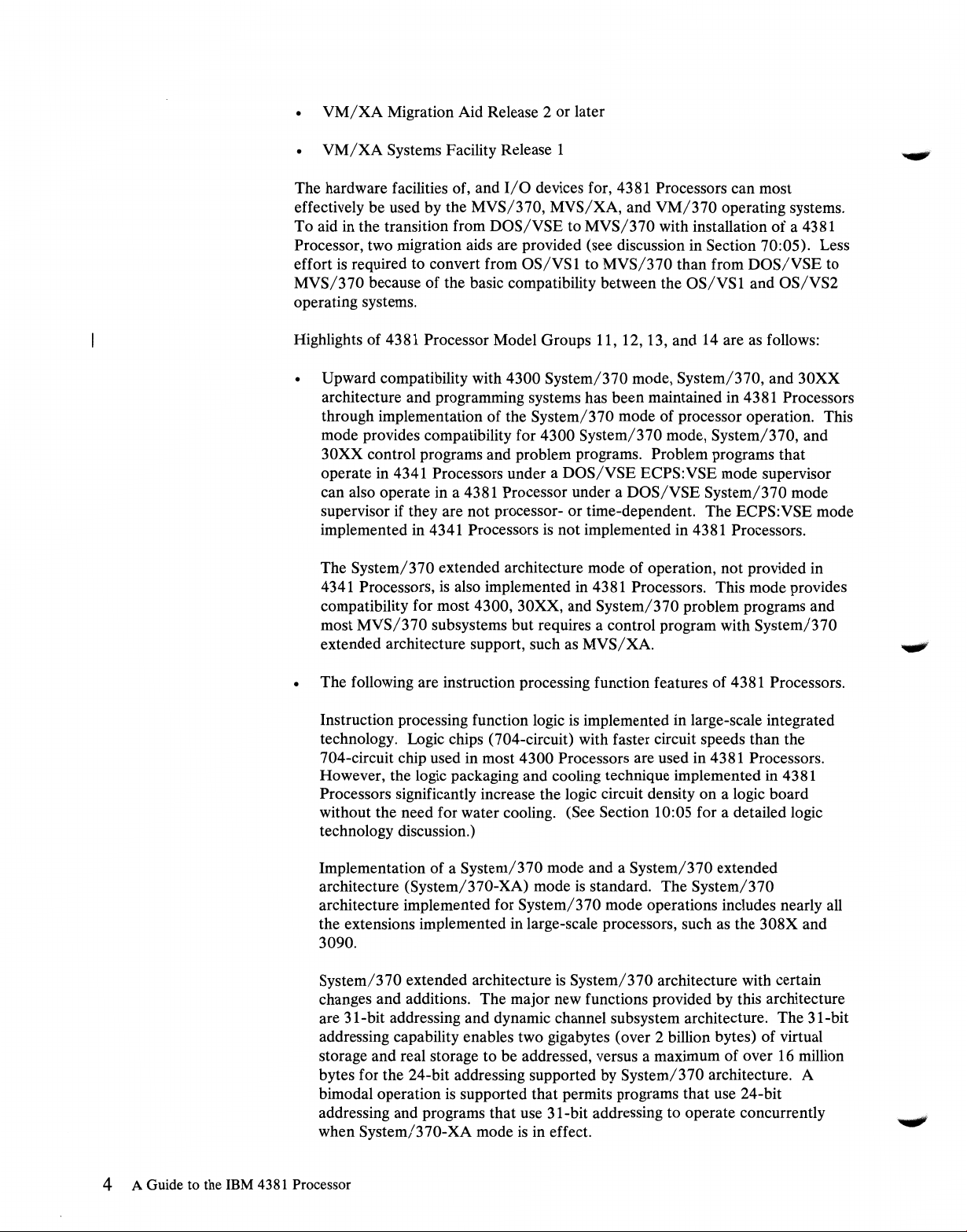

Figure 3. A 64-mm

The instruction processing logic for 4381 Processor Model Groups 11, 12, and

(exclusive of that for the support processor subsystem and some channel functions)

is

contained in 22 MCMs and these modules are mounted on one MCM board.

The 4381 Processor Model Group 14 contains two MCM boards. The fully loaded

MCM

board weighs 37 kilograms (81.4 pounds). The MCM board has 8 layers for

interconnecting the circuits on the MCMs and contains 1435 meters (about 4707

feet) of wiring for circuit interconnections. Figure 6 on page 19 shows the MCM

board as it

Since all instruction processing logic

Model Group 11, 12, or 13, interboard cabling for logic

increases logic speed and reliability. In the 4341 Processor, two boards are

required for logic and 400 cables are used for circuit connections between the two

boards. For a 4381 Model Group 14, some cabling between the two MCM boards

is

required for communication between the two instruction processing functions.

The standard card-on-board approach (a 22-card board)

functional components of the 4381 Processor. There

board, one board to support certain channel functions, and two boards for support

processor components.

MCM

being hand held

is

mounted on its side within the frame of a 4381 Processor.

is

contained on one board in a 4381 Processor

is

eliminated, which

is

used for other

is

one processor storage

13

Section 10: Technology and Architecture 1 7

Page 27

Figure 4. The 4381

MCM

board without any modules mounted

Figure 5. 64-mm MCMs mounted on the MCM board

18

A Guide to the IBM 4381 Processor

Page 28

Figure 6.

MCM

board mounted within the 4381 Processor

Logic

Cooling

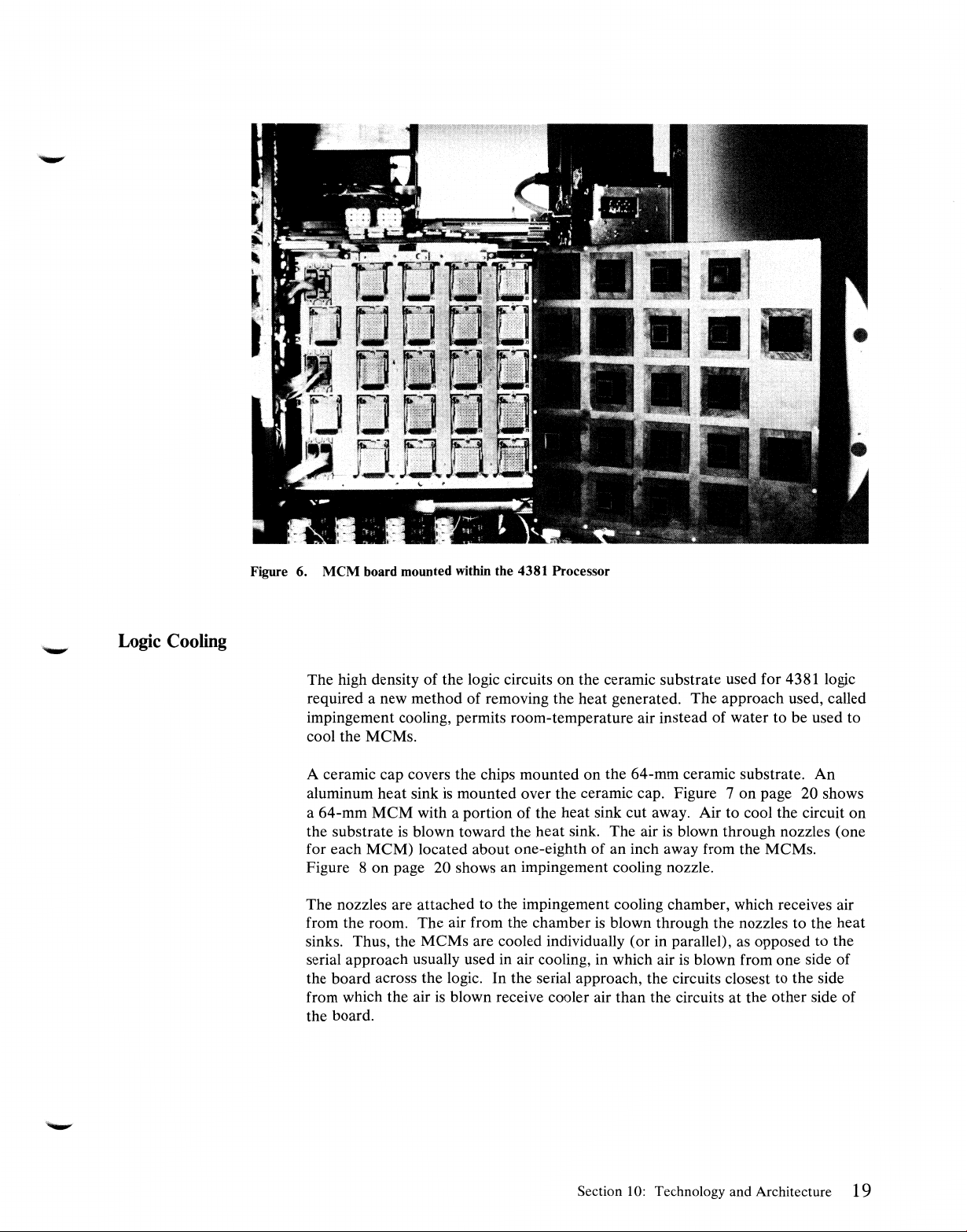

The high density of the logic circuits on the ceramic substrate used for 4381 logic

required a new method of removing the heat generated. The approach used, called

impingement cooling, permits room-temperature air instead of water to be used to

cool the MCMs.

A ceramic cap covers the chips mounted on the 64-mm ceramic substrate. An

aluminum heat sink

is

mounted over the ceramic cap. Figure 7 on page 20 shows

a 64-mm MCM with a portion of the heat sink cut away. Air to cool the circuit on

the substrate

blown toward the heat sink. The air

is

blown through nozzles (one

is

for each MCM) located about one-eighth of an inch away from the MCMs.

Figure 8 on page 20 shows an impingement cooling nozzle.

The nozzles are attached to the impingement cooling chamber, which receives air

is

from the room. The air from the chamber

blown through the nozzles to the heat

sinks. Thus, the MCMs are cooled individually (or in parallel), as opposed to the

serial approach usually used in air cooling, in which air

is

blown from one side of

the board across the logic. In the serial approach, the circuits closest to the side

from which the air

is

blown receive cooler air than the circuits at the other side of

the board.

Section 10: Technology and Architecture 19

Page 29

Figure 7. 64-mm

MCM

with a portion

of

the heat sink cut away

20 A Guide

8. An impingement cooling nozzle

Figure

to

the IBM 4381 Processor

Page 30

Storage Technology

10:

10

Architecture

The 64K-bit SAMOS (Silicon and Aluminum Metal Oxide Semiconductor)

(Field Effect Transistor) storage chip that

Processors

Processors. The 64K-bit chips are packaged to provide

per storage card. For processor storage above 16Mb in a 4381 processor, a

256K-bit enhanced SAMOS

storage card. The speed of the 256K-bit chip

(250 ns versus 370 ns).

An array chip that had not previously been used in other IBM processors

implement reloadable control storage and high-speed buffer storage in 4381

Processors. This array chip has a capacity of

faster, lower capacity chip that

implement the high-speed buffer directory and local storage in a 4381 instruction

processing function.

Two architectures are implemented in 4381 Processors: System/370 architecture

and System/370 extended architecture. The mode of processor operation selected

during an initial microcode load (IML) of a 4381 Processor determines the

architecture that

architecture

extended architecture

is

used to implement processor storage of up to 16Mb in 4381

FET

chip

is

contained in other IBM processors

is

functional. When System/370 mode

is

functional. When System/370-XA mode

is

functional.

is

used for processor storage in 4341

lMb

of processor storage

is

used and its packaging provides 2Mb per

is

faster than that of the 64K-bit chip

lK

bytes and a 20-ns cycle time. A

is

selected, System/370

is

selected, System/370

is

used to

FET

is

used to

System/370

Architecture

The System/370 architecture implemented in 4381 Processors includes nearly all

the facilities defined for System/370,

of

are implemented.

The System/370 architecture implemented in 4381 Processors does not include the

following facilities that are defined for optional implementation in System/370

processors:

• Extended machine check logout (that processor-dependent data logged

• Direct Control (READ DIRECT and WRITE DIRECT) instructions. The

• Suspend and resume

as

described in

Operation (GA22-7000). Basic control (BC) and extended control (EC) modes

beginning at the processor storage address specified in control register

15-normally

to 3 51, and the processor-dependent

beginning at the address in the word

external signals facility in 4381 Processors provide the six external interruption

lines included in the Direct Control facility without the two instructions READ

DIRECT and WRITE DIRECT

location 512), the processor-dependent logout to locations 256

I/

0 extended logout (that data logged

at

processor storage location 172)

IBM

System/

3 70 Principles

Section 10: Technology and Architecture

21

Page 31

• Multiprocessing (includes SET PREFIX, STORE PREFIX, SIGNAL

PROCESSOR, and STORE CPU ADDRESS instructions)-implemented in

14

4381 Model Groups

and 3 only

• Channel Set Switching (CONNECT CHANNEL SET and DISCONNECT

CHANNEL SET instructions)

• Compatibility features for emulation of other processors

(1401/1440/1400

Compatibility, for example)

• Certain control program assists (such

OS/DOS

Emulation)

OS/VSl

assist, APL assist, and

as

• Certain processor dependencies

Control and problem programs written for System/370, 4300 System/370 mode,

or 30XX Processors can be run without modification in a 4381 Processor operating

in System/370 mode that has a comparable hardware configuration, with the

following exceptions:

1.

Programs that depend on facilities that are not defined in the System/370

architecture for 4381 Processors (READ DIRECT, WRITE DIRECT, Channel

Set Switching instructions, for example)

2.

Time-dependent programs. (They may or may not run correctly.)

3.

Programs that depend on results defined in the

Operation (GA22-7000) to be unpredictable or processor-dependent

4.

Programs that use unassigned fields in processor formats (instruction formats,

System/370

Principles

of

for example) that are not explicitly made available for program use

5.

Programs that depend on interruptions caused by errors, such

as

unassigned

operation codes or command codes

System/370 architecture

as

implemented in 4381 Processors provides the ability to

execute:

• 4300 System/370 mode control and problem programs that are not

time-dependent or 4300 Processor-dependent

• 4300 problem programs that are designed to operate with 4300 ECPS:VSE

mode control programs and that are not time-dependent or 4300

Processor-dependent. (A 4300 ECPS:VSE mode control program cannot

execute in a 4381 Processor.)

• System/370 or 30XX control and problem programs that are not

time-dependent or System/370 processor-dependent

• System/360 control and problem programs that are not time-dependent or

System/360 processor-dependent

22 A Guide to the IBM 4381 Processor

Page 32

System/370

Extended

Architecture

System/370 extended architecture

exclusions and a set of functional extensions. The new facilities provided by

System/370 extended architecture

following:

A 31-bit addressing capability that provides for addressing more than two

gigabytes (2G-bytes) of virtual and real storage

• Dynamic channel subsystem architecture that provides additional channel

control functions that are designed to improve

• An expanded trace capability that provides for branch tracing, address space

tracing, and explicitly initiated tracing

• Page protection, which can be used to prevent storing into selected virtual

storage pages (see Section 50)

• An instruction (START INTERPRETIVE EXECUTION) to handle

interpretive instruction execution that provides a mechanism for implementing

virtual machine support

A sort microcode assist

The new capabilities provided in System/370 extended architecture are designed to

extend the functional capabilities of System/370 architecture while maintaining

compatibility between the two architectures for problem programs. The instruction

set for System/370 extended architecture includes all the problem state and

semiprivileged instructions defined for System/370 mode of operation (including

MOVE INVERSE).

is

System/370 architecture with certain

as

implemented in the 4381 Processor are the

1/0

performance

The instruction set for System/370 extended architecture contains all the privileged

instructions defined for System/370 architecture except the following:

• INSERT STORAGE KEY (ISK)

• SET STORAGE KEY (SSK)

RESET REFERENCE BIT (RRB)

CLEAR CHANNEL (CLRCH)

I/

CLEAR

• HALT DEVICE (HDV)

HALT

RESUME

START

START

0 ( CLRIO)

1/0

(HIO)

I/O

(RIO)

1/0

(SIO)

1/0

FAST RELEASE (SIOF)

Section

10:

Technology and Architecture

23

Page 33

STORE CHANNEL ID (STIDC)

TEST CHANNEL (TCH)

TEST

1/0

(TIO)

The following instructions are implemented in System/370 extended architecture

but not in System/370 architecture:

• BRANCH AND SA VE AND SET MODE (BASSM)

BRANCH AND SET MODE (BSM)

DIVIDE-extended (DXR)

INSERT PROGRAM MASK (IPM)

START INTERPRETIVE EXECUTION (SIE)

TRACE

CLEAR

•

HALTSUBCHANNEL(HSCH)

MODIFY SUBCHANNEL (MSCH)

• RESET CHANNEL PA TH (RCHP)

RESUME SUBCHANNEL (RSCH)

SET ADDRESS LIMIT (SAL)

SET

START

STORE CHANNEL PATH STATUS (STCPS)

STORE CHANNEL REPORT WORD (STCRW)

STORE SUBCHANNEL (STSCH)

TEST PENDING INTERRUPTION (TPI)

(TRACE)

SUB CHANNEL ( CSCH)

CHANNEL

SUBCHANNEL

MONITOR (SCHM)

(SSCH)

TEST SUBCHANNEL (TSCH)

24 A Guide to the IBM 4381 Processor

Page 34

31-Bit

Addressing

The 31-bit addressing capability significantly increases the amount of virtual and

real storage that can be addressed in a virtual storage

bytes versus over 16 million bytes for the 24-bit addressing capability used in 4381

System/370 mode of operation. To maintain problem program compatibility for

System/370 and System/370-XA modes, bimodal operation

System/370-XA mode that permits concurrent execution of problem programs that

use 24-bit addressing and those that use 31-bit addressing.

is

The addressing mode in effect

is

bit 32

addressing

address generated for instructions and instruction operands. It does not control the

size of PER addresses or of the addresses used to access DAT, ASSN, linkage,

entry, and trace tables. These addresses are always

zero, 24-bit addressing mode

is

in effect. The addressing mode controls the size of the effective

determined by bit 32 in the current PSW. When

is

in effect. When bit 32

environment-over

is

supported for

is

one, 31-bit

31

bits in size.

2 billion

Dynamic Channel Subsystem

as

is

in

is

Note that the 24-bit addresses that are generated when 24-bit addressing mode

in effect are converted to 31-bit addresses by the addition of seven high-order

zeros.

The dynamic channel subsystem defined for System/370-XA mode of operation

provides improvements and additional functional capabilities. The major

differences between the channel architecture for System/370-XA mode and

System/370 mode in 4381 Processors are the following:

• Channels are not assigned a channel number. The instruction processor issues

1/0

requests that specify the

specified. All types of

System/370 mode of operation), and instruction processing function execution

continues after any

information from channel control hardware. A new set of

defined for handling

• Channel path management

than by the

to be used to access an

When multiple channel paths exist to a device, the set of paths specified for the

device

Input/Output

Processor supports up to four paths per

1/0

is

inspected in the sequence defined by the installation using the

1/0

1/0

supervisor portion of the control program. The channel path

Control Program, which

1/0

device to be used. A channel

1/0

requests are queued (not just SIOF requests,

request

1/0

is

issued without waiting for any status

1/0

instructions

operations.

is

performed by the channel control function rather

device

is

selected by the channel control function.

is

discussed in Section 20:20. The 4381

1/0

device.

is

not

is

• A dynamic reconnection capability

reconnect a disconnected channel program to the first available channel path to

the device when multiple paths to the device exist, rather than only to the

channel path from which the channel program disconnected. This capability

utilized, for example, by 3880 Storage Control Models 2 and 3 with attached

3380 Model AA4 Direct Access Storage (which has dynamic path selection).

For

devices without dynamic path selection, reconnection occurs only to the

path from which the channel program disconnected.

supported that permits an

Section

10:

Technology and Architecture 25

1/0

device to

is

Page 35

• Faster restart of

1/0

device when ending status for a completed

0 devices

is

provided by dequeuing the next request for an

I/

passed to the instruction processing function.

I/O

operation on the device

is

..,,,.,,,

• A reformatted channel command word (CCW)

is

defined that uses 31-bit

addressing. However, channel programs that use the CCW format defined for

System/370 mode of operation

will

operate in System/370-XA mode for

compatibility purposes. This implementation enables existing programs that

have their own channel programs and that use the

request

1/0

operations to operate with System/370-XA mode in effect

OS/VS

EXCP

macro to

without modification.

• Device addressing

in one configuration. However, in a 4381 Processor, a maximum of 2048

is

expanded to permit up to 65,535 devices to be addressed

1/0