HYNIX HY51V17403HGLJ-5, HY51V17403HGLJ-6, HY51V17403HGLJ-7, HY51V17403HGLT-5, HY51V17403HGLT-6 Datasheet

...

HY51V(S)17403HG/HGL

4M x 4Bit EDO DRAM

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. No patent licenses are implied.

Rev.0.1/Apr.01

DESCRIPTION

FEATURES

• Fast access time and cycle time

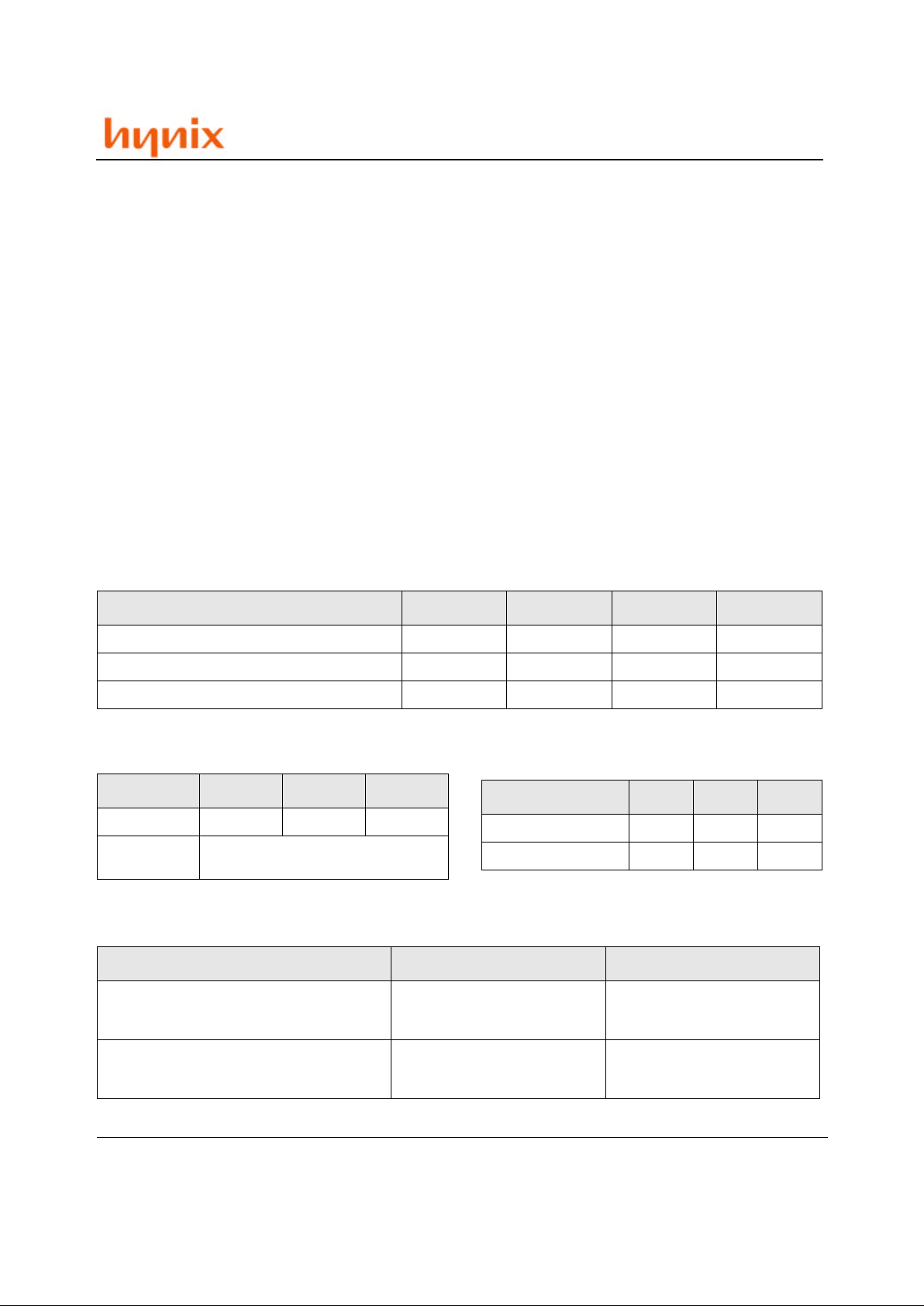

ORDERING INFORMATION

Part No tRAC tCAC tRC tHPC

HY51V(S)17403HG/HGL-5 50ns 13ns 84ns 20ns

HY51V(S)17403HG/HGL-6 60ns 15ns 104ns 25ns

HY51V(S)17403HG/HGL-7 70ns 18ns 124ns 30ns

50ns 60ns 70ns

Active 432mW 369mW 360mW

Standby

7.2mW(CMOS level Max)

0.36mW (L-version : Max)

Part Number Access Time Package

HY51V(S)17403HGJ/HG(L)J-5

HY51V(S)17403HGJ/HG(L)J-6

HY51V(S)17403HGJ/HG(L)J-7

50ns

60ns

70ns

300mil 24(26)pin SOJ

HY51V(S)17403HGT/HG(L)T-5

HY51V(S)17403HGT/HG(L)T-6

HY51V(S)17403HGT/HG(L)T-7

50ns

60ns

70ns

300mil 24(26)pin TSOP-II

PRELIMINARY

The HY51V(S)17403HG/HGL is the new generation dynamic RAM organized 4,194,304 words x 4bit.

HY51V(S)17403HG/HGL has realized higher density, higher performance and various functions by utilizing advanced CMOS process technology. The HY51V(S)17403HG/HGL offers Extended Data Out PageMode as a high speed access mode. Multiplexed address inputs permit the HY51V(S)17403HG/HGL to be

packaged in standard 300mil 24(26)pin SOJ and 24(26) pin TSOP-II. The package size provides high system bit densities and is compatible with widely available automated testing and insertion equipment.

System oriented features include single power supply 3.3V +/- 0.3V tolerance, direct interfacing capability

with high performance logic families such as Schottky TTL.

• Extended Data Out Mode capability

• Read-modify-write capability

• Multi-bit parallel test capability

• TTL(3.3V) compatible inputs and outputs

• /RAS only, CAS-before-/RAS, Hidden and self

refresh(L-version) capability

• JEDEC standard pinout

• 24(26)pin plastic SOJ / 24(26)pin TSOP-II

• Single power supply of 3.3V +/- 0.3V

• Battery back up operation(L-version)

• Power dissipation

• Refresh cycle

Part No Ref Normal L-part

HY51V17403HG 2K 32ms

HY51V17403HGL 2K 128ms

(S) : Self refresh, (L) : Low power

HY51V(S)17403HG/HGL

Rev.0.1/Apr.01 2

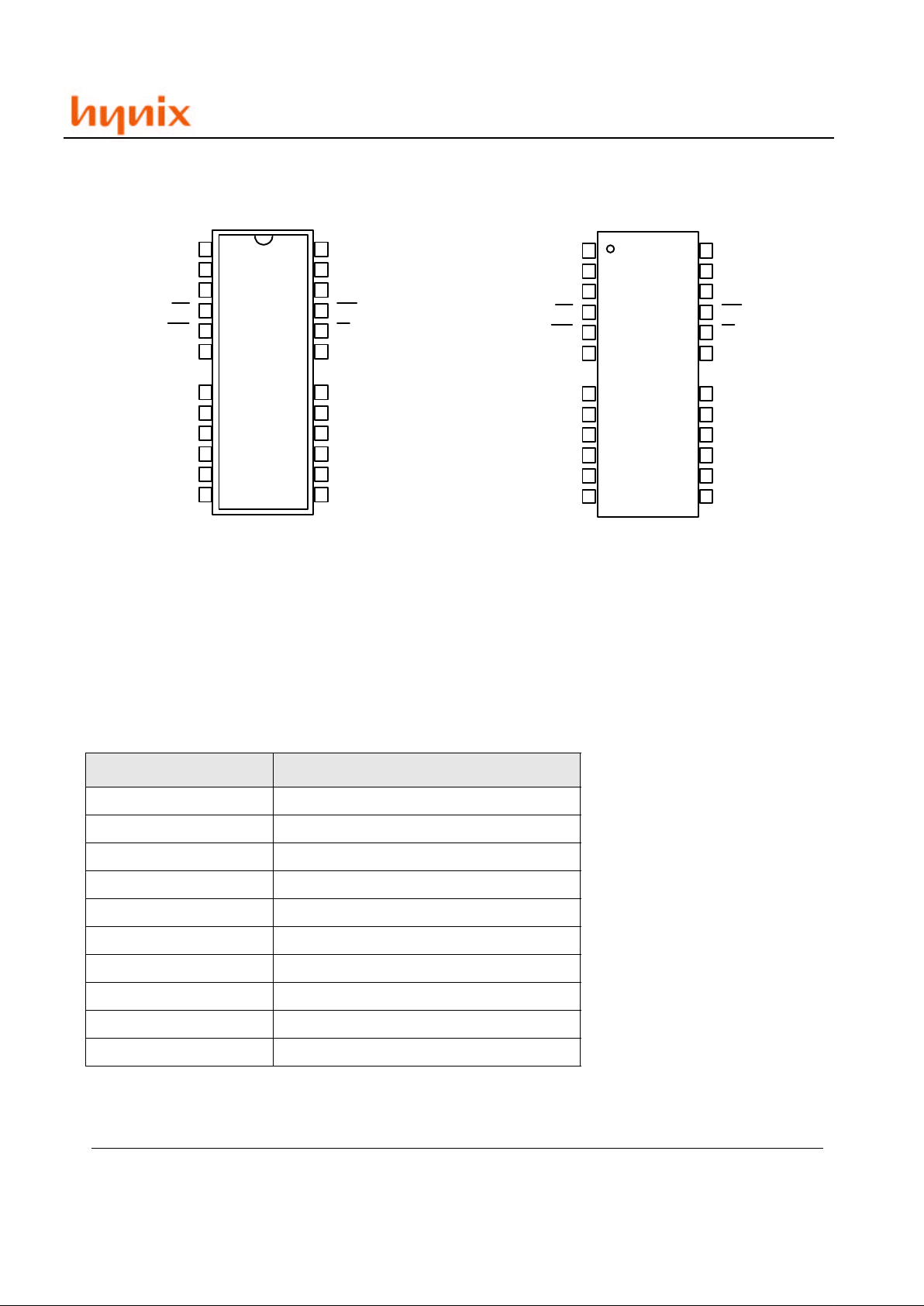

PIN CONFIGURATION

Pin Function

/RAS Row Address Strobe

/CAS Column Address Strobe

/WE Write Enable

/OE Output Enable

A0-A11 Address Inputs

A0-A11 Refresh Address Inputs

I/O 1- I/O 4 Data Input / Output

Vcc Power (3.3V)

Vss Ground

NC No connection

PIN DESCRIPTION

VCC

I/O1

I/O2

WE

RAS

A11

A10

A0

A1

A2

A3

VCC

VSS

I/O4

I/O3

CAS

OE

A9

A8

A7

A6

A5

A4

VSS

1

2

3

4

5

6

8

9

10

11

12

13 14

15

16

17

18

19

21

22

23

24

25

26

24(26) Pin Plastic SOJ

VCC

I/O1

I/O2

WE

RAS

A11

A10

A0

A1

A2

A3

VCC

VSS

I/O4

I/O3

CAS

OE

A9

A8

A7

A6

A5

A4

VSS

1

2

3

4

5

6

8

9

10

11

12

13 14

15

16

17

18

19

21

22

23

24

25

26

24(26) Pin Plastic TSOP-II

HY51V(S)17403HG/HGL

Rev.0.1/Apr.01 3

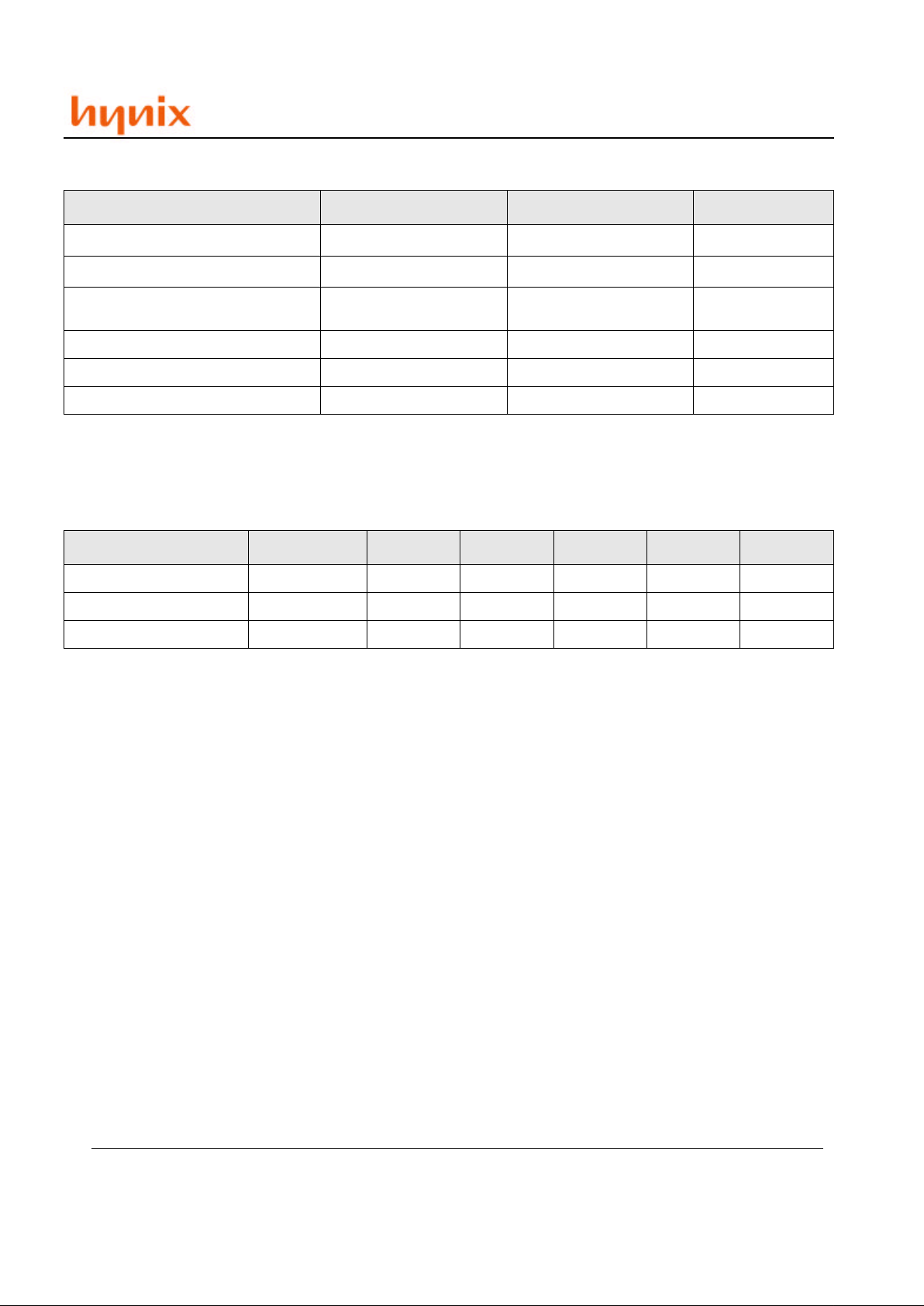

ABSOLUTE MAXIMUM RATINGS

Recommended DC OPERATING CONDITIONS (TA=0 to 70

o

C)

Note : All voltages are referenced to Vss

Parameter Symbol Rating Unit

Ambient Temperature TA 0 ~ 70

o

C

Storage Temperature TSTG -55 ~ 125

o

C

Voltage on Any Pin relative to Vss VT

-0.5 ~ Vcc + 0.5

(Max 4.6V)

V

Voltage on Vcc relative to Vss Vcc -0.5 ~ 4.6 V

Short Circuit Output Current IOUT 50 mA

Power Dissipation PT 1 W

Parameter Symbol Min Typ. Max Unit Note

Power Supply Voltage Vcc 3.0 3.3 3.6 V

Input High Voltage VIH 2.0 - Vcc + 0.3 V

Input Low Voltage VIL -0.3 - 0.8 V

HY51V(S)17403HG/HGL

Rev.0.1/Apr.01 4

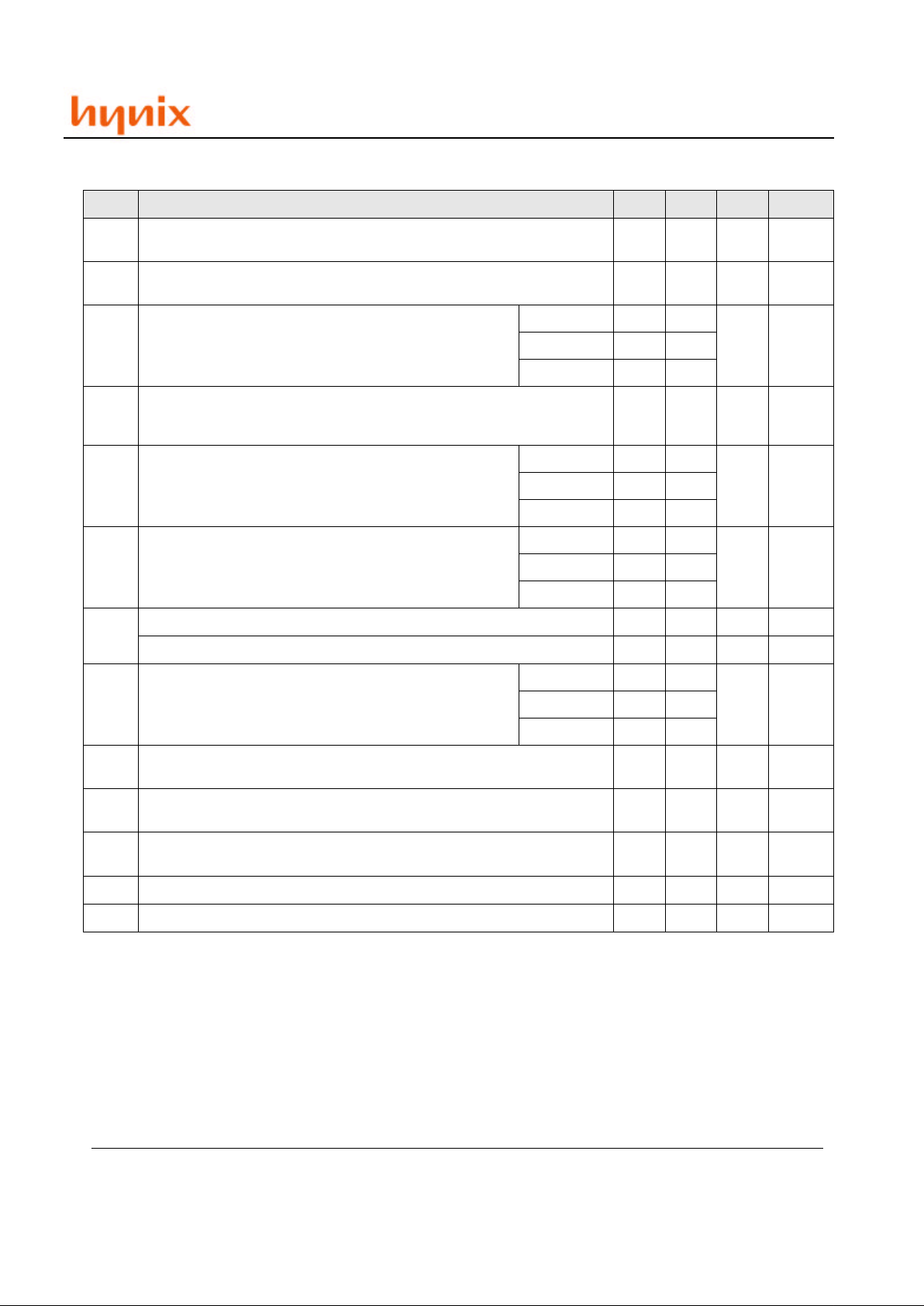

DC CHARACTERISTICS (Vcc = 3.3V +/- 10%, TA=0 to 70°C)

Note :

1. Icc depends on output load condition when the device is selected, Icc(max) is specified at the output open condition

2. Address can be changed once or less while /RAS=VIL

3. Address can be changed once or less while /CAS=VIH

4. /CAS = L (<=0.2) while /RAS=L (<=0.2)

5. L-Version

Symbol Parameter Min Max Unit Note

VOH

Output Level

Output Level voltage(Iout= -2mA)

2.4 Vcc V

VOL

Output Level

Output Level voltage(Iout=2mA)

0 0.4 V

ICC1

Operating current

Average power supply operating current

( /RAS, /CAS Cycling : tRC = tRC min)

50ns - 100

mA 1, 260ns - 90

70ns - 80

ICC2

Standby current (TTL interface)

Power supply standby current

(/RAS, /CAS=VIH, Dout = High-Z)

- 2 mA

ICC3

/RAS only refresh current

Average power supply current

/RAS only refresh mode

(tRC= tRC min)

50ns - 100

mA 260ns - 90

70ns - 80

ICC4

Fast page mode current

Average power supply current

Fast page mode (tPC=tPC min)

50ns - 90

mA 1, 3

60ns

- 80

70ns

- 75

ICC5

CMOS interface ( /RAS, /CAS >= Vcc-0.2V, Dout = High-Z) - 1 mA

Standby current ( L-version) - 100 uA 4

ICC6

/CAS-before-/RAS refresh current (tRC=tRC min)

50ns

- 100

mA

60ns

- 90

70ns

- 80

ICC7

Battery back up operating current (standby with CBR refresh)

(tRC=31.3us, tRAS<=0.3us, Dout=High-Z)

- 300 uA 4

ICC8

Standby current

( /RAS = VIH, /CAS = VIL, Dout=Enable)

- 5 uA 1

ICC9

Self refresh current

(/RAS, /CAS <=0.2V, Dout=High-Z, CMOS interface)

- 200 uA 4

II(L) Input leakage current, Any input (0V<= Vin<=4.6V)

-10 10 uA

IO(L) Output leakage current, (Dout is disabled, 0V<= Vout<=4.6V)

-10 10 uA

Loading...

Loading...