HYNIX HMS91C7132, HMS91C7132K, HMS91C7134, HMS91C7134K, HMS97C7132 Datasheet

...

May. 2001 ver1.1

8-BIT SINGLE-CHIP MONITOR MICROCONTROLLERS

HMS9xC7132

HMS9xC7134

User’s Manual

Additional information of this manual may be s erved by HYNIX Semiconductor offices in Korea or Distributors

and Representat ives listed at address di rec tory.

HYNIX Semiconductor reserves the rig ht to make changes to an y information here in at any time without notic e.

The information, diagrams and other data in this manual are correct and reliable; however, HYNIX Semicon-

ductor is in no way respons ible for any violations of patents or other rights of the third party gener ated by the use

of this manu al.

Version 1.1

Published by

MCU Application Team bjinlim@hynix.com blackjoe@ hynix.com

2001 HYNIX Semiconductor All right reserved.

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

1. OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

2. BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . 2

3. PIN ASSIGNMENT . . . . . . . . . . . . . . . . . 3

3.1 40PDIP pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

3.2 42SDIP pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

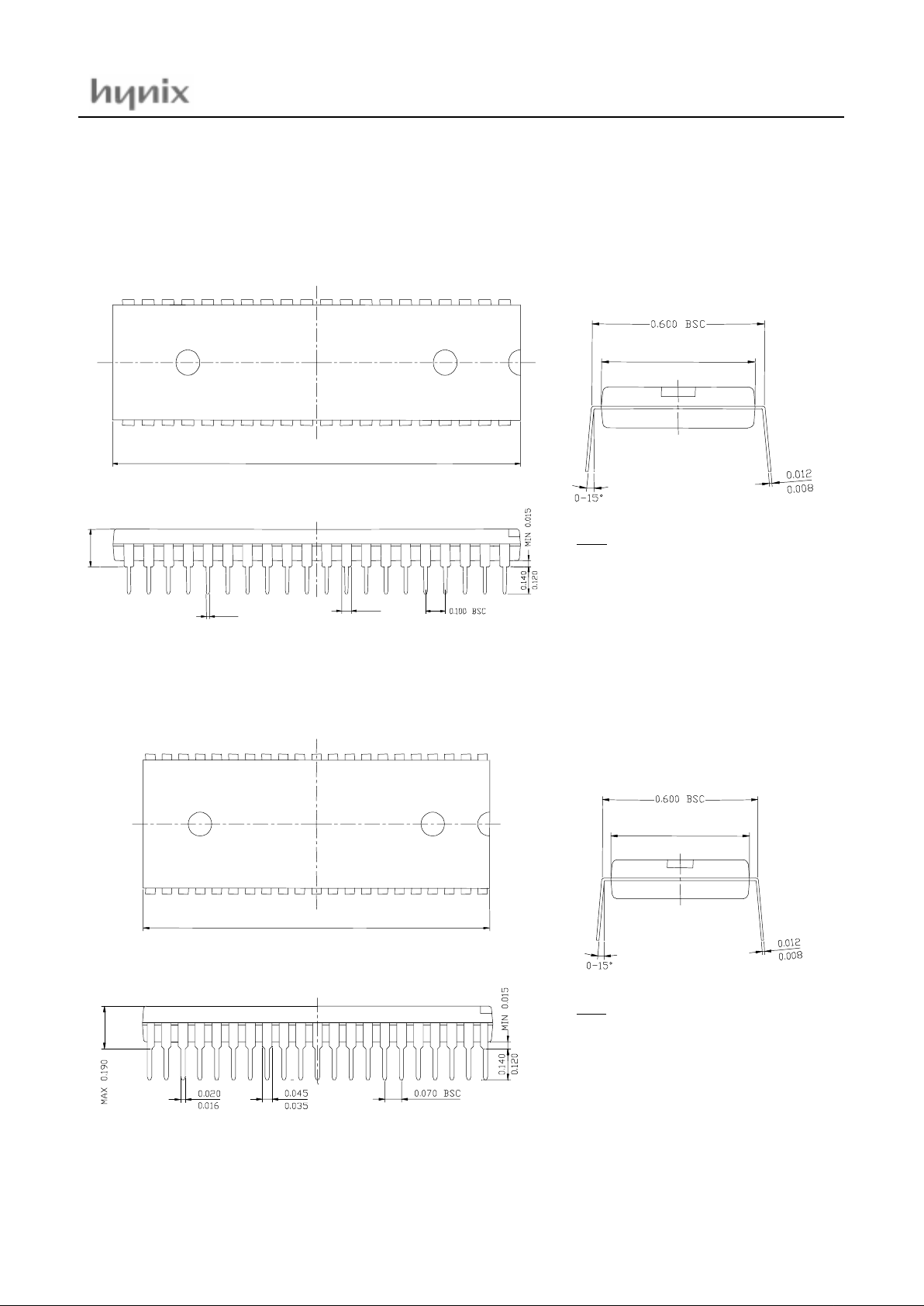

4. PACKAGE DIMENSIONS . . . . . . . . . . . . 5

4.1 40 PDIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

4.2 42 SDIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

5. PIN FUNCTION . . . . . . . . . . . . . . . . . . . . 6

5.1 40DIP Pin Description . . . . . . . . . . . . . . . . . . . . . . .7

5.2 42SDIP Pin Description . . . . . . . . . . . . . . . . . . . . . .8

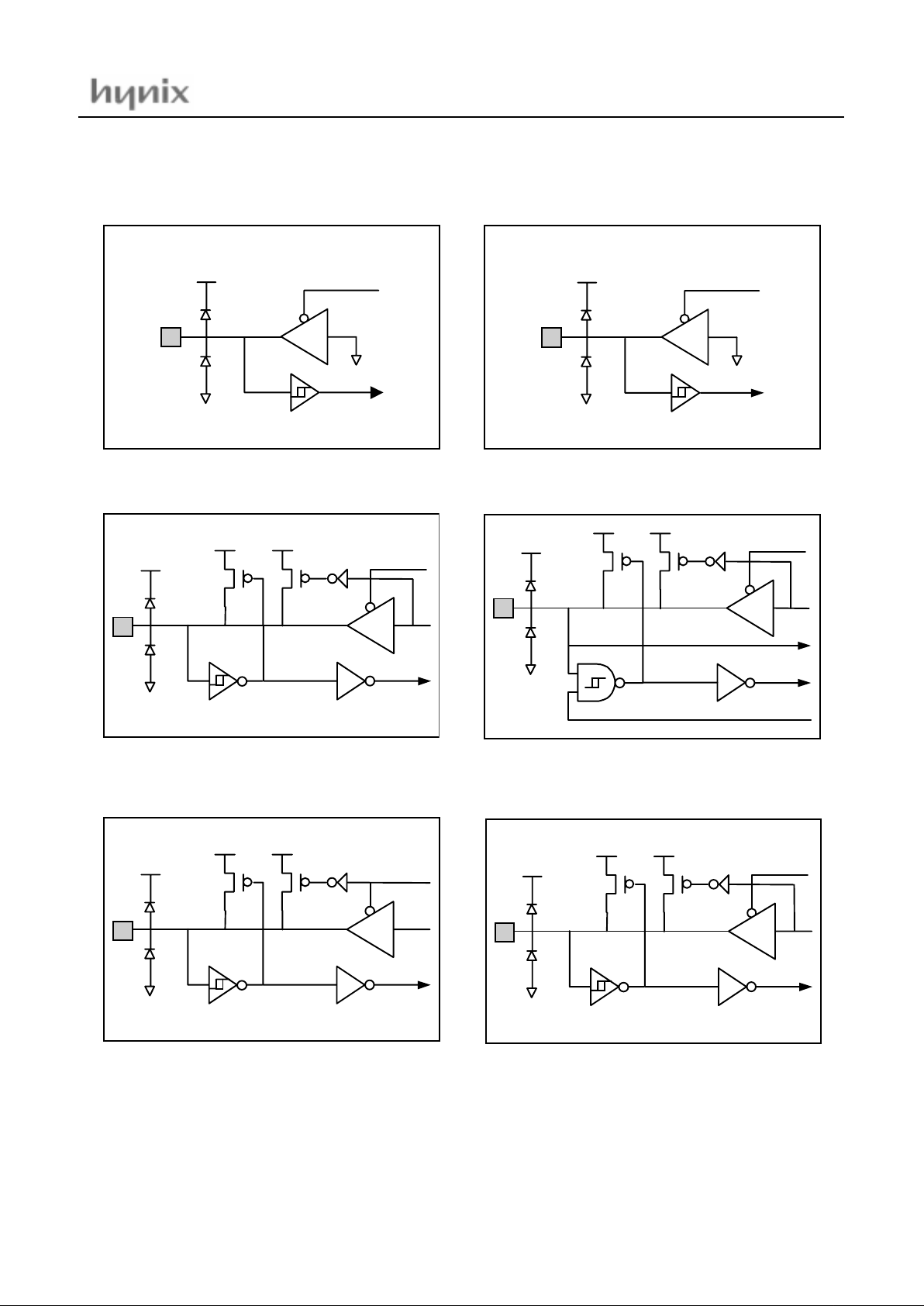

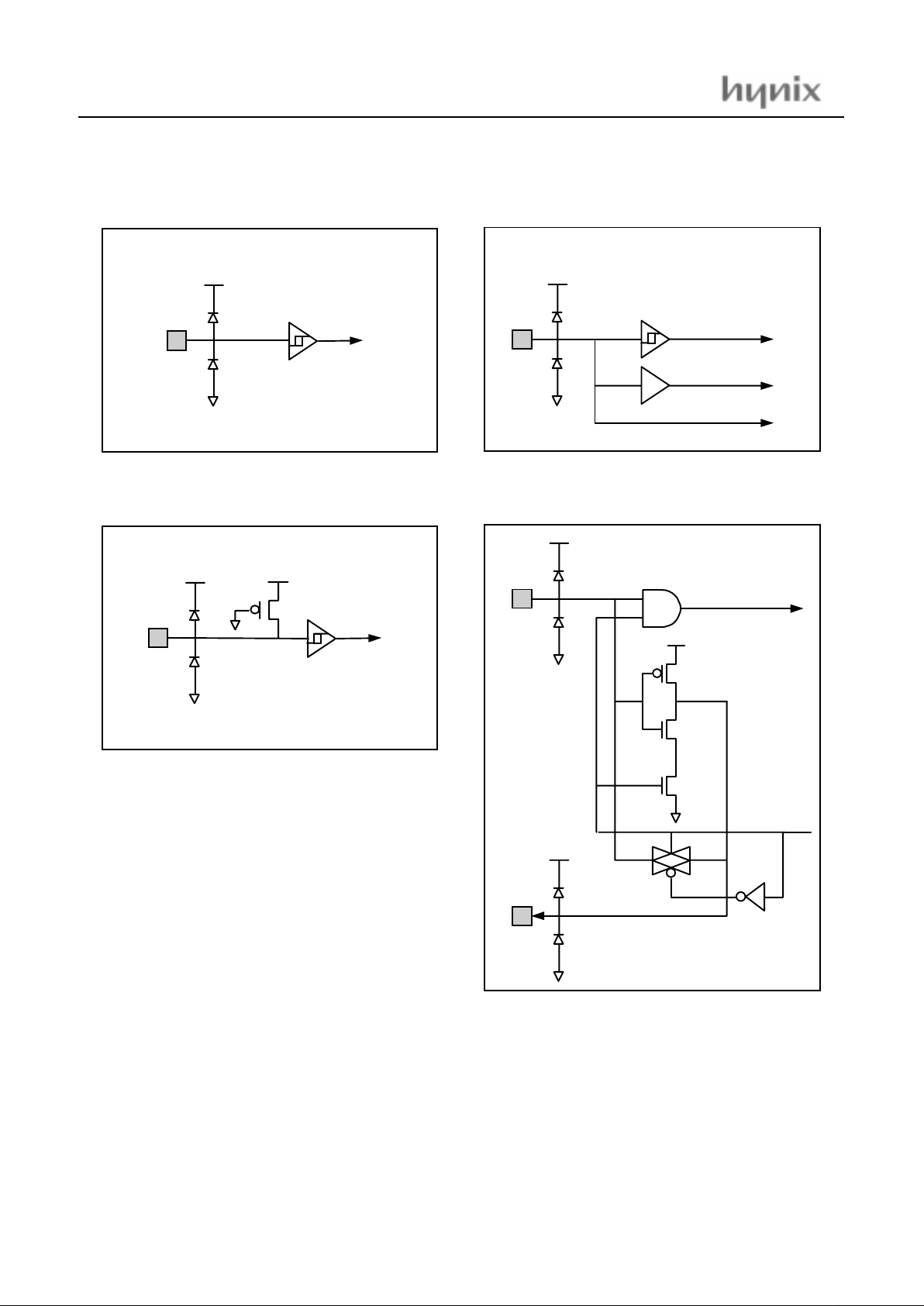

6. PORT STRUCTURES . . . . . . . . . . . . . . . 9

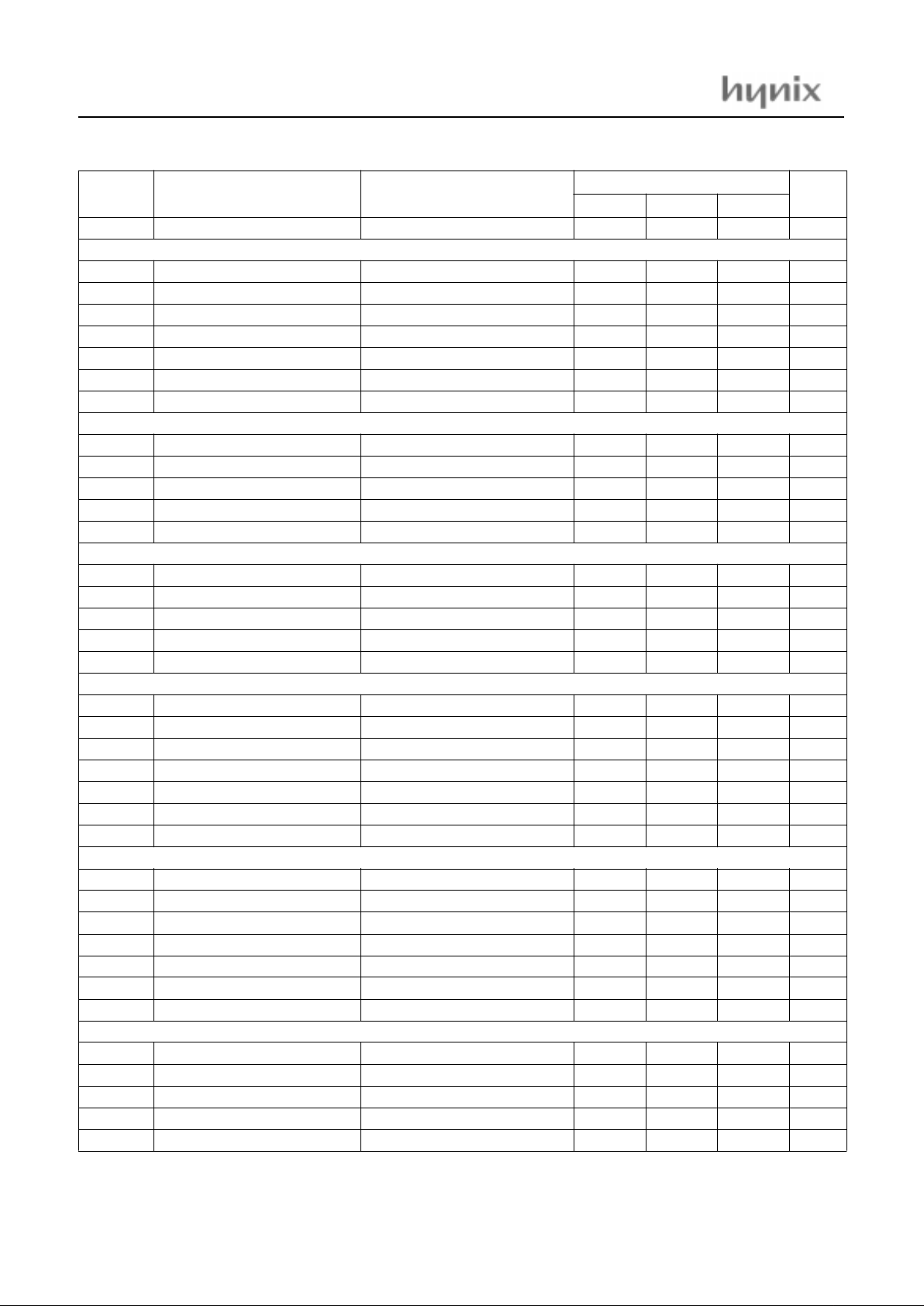

7. ELECTRICAL CHARACTERISTICS . . . 11

7.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . .11

7.2 Recommended Operating Conditions . . . . . . . . . .11

7.3 DC Electrical Characteristics . . . . . . . . . . . . . . . . .11

7.4 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . .13

8. MEMORY ORGANIZATION . . . . . . . . . 16

8.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

8.2 Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . .17

8.3 Data memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

8.4 List of SFRS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

8.5 Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . .22

9. INTERRUPTS . . . . . . . . . . . . . . . . . . . . 24

9.1 Interrupt sources . . . . . . . . . . . . . . . . . . . . . . . . . .24

9.2 Interrupt Enable structure . . . . . . . . . . . . . . . . . . .26

9.3 Interrupt Priority structure . . . . . . . . . . . . . . . . . . .27

9.4 How Interrupt are handled . . . . . . . . . . . . . . . . . . .29

10. POWER-SAVING MODE . . . . . . . . . . . 30

10.1 Power control register . . . . . . . . . . . . . . . . . . . . .30

10.2 Idle mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

10.3 Power-down mode . . . . . . . . . . . . . . . . . . . . . . . .31

11. I/O PORTS . . . . . . . . . . . . . . . . . . . . . . 32

11.1 Pin function selection . . . . . . . . . . . . . . . . . . . . . .33

12. OSCIALLTOR . . . . . . . . . . . . . . . . . . . 36

13. RESET . . . . . . . . . . . . . . . . . . . . . . . . . 37

13.1 External reset . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

13.2 Watchdog timer overflow . . . . . . . . . . . . . . . . . . .37

13.3 Low VDD voltage reset . . . . . . . . . . . . . . . . . . . .37

14. WATCHDOG TIMER . . . . . . . . . . . . . . 38

15. TIMER . . . . . . . . . . . . . . . . . . . . . . . . . 39

15.1 Timer0 and Timer1 . . . . . . . . . . . . . . . . . . . . . . .39

15.2 TIMER2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

16. DDC INTERFACE . . . . . . . . . . . . . . . . 42

16.1 The SFRs for DDC Interface . . . . . . . . . . . . . . . .43

16.2 DDC1 protocol . . . . . . . . . . . . . . . . . . . . . . . . . . .46

16.3 DDC2B protocol . . . . . . . . . . . . . . . . . . . . . . . . . .46

16.4 DDC2AB/DDC2B+ protocol . . . . . . . . . . . . . . . . .47

16.5 The RAM Buffer and DDC application . . . . . . . . .48

17. I2C INTERFACE . . . . . . . . . . . . . . . . . 51

17.1 The SFRs for I2C Interface . . . . . . . . . . . . . . . . .52

17.2 Programmer’s Guide for I2C and DDC2 . . . . . . .54

18. PULSE WIDTH MODULATION . . . . . . 57

18.1 Static PWM . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

18.2 Dynamic PWM . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

19. SYNC PROCESSOR . . . . . . . . . . . . . . 60

19.1 Sync input signals . . . . . . . . . . . . . . . . . . . . . . . .60

19.2 Horizontal polarity correcti on . . . . . . . . . . . . . . . .60

19.3 Vertical polarity correction . . . . . . . . . . . . . . . . . .60

19.4 Vertical sync separation . . . . . . . . . . . . . . . . . . . . 60

19.5 Horizontal sync. detection . . . . . . . . . . . . . . . . . . 62

19.6 Vertical sync. detection . . . . . . . . . . . . . . . . . . . .62

19.7 Horizontal sync. generator . . . . . . . . . . . . . . . . . .65

19.8 Vertical sync. generator . . . . . . . . . . . . . . . . . . . .66

19.9 HSYNC / VSYNC output driver . . . . . . . . . . . . . . 66

19.10 Clamp pulse gener ator . . . . . . . . . . . . . . . . . . .67

19.11 Pattern generator . . . . . . . . . . . . . . . . . . . . . . . .67

19.12 Suspend mode . . . . . . . . . . . . . . . . . . . . . . . . . .67

20. AD-CONVERTOR (ADC) . . . . . . . . . . . 71

21. OPERATION MODE . . . . . . . . . . . . . . 73

21.1 OTP MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

21.2 64MQFP pinning and Package Dimensions . . . . 78

21.3 64MQFP Pin Description . . . . . . . . . . . . . . . . . . .79

21.4 Development Tools . . . . . . . . . . . . . . . . . . . . . . .81

22. INSTRUCTION SET . . . . . . . . . . . . . . . 82

HMS9 xC 7132 / HMS9xC 7134

May.2001 ver1.1

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

1

HMS9xC7132 / HMS9xC7134

CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

FOR MONITOR

1. OVERVIEW

1.1 Description

The HMS9xC7132/4 is a single-chip microcontroller of the 80C51 family, which is dedicated for monitor application. It is particula r ly

suitable for multi-sync computer monitor controller. This contains DDC interfaces to the PC host, sync-detector and sync-processor for

auto-sync application, ADC, static PWM, dynamic PWM and I

2

C bus i nt erfa ce f or con trol of th e vide o an d de fl ect ion f unc ti ons of th e

monitor.

1.2 Features

• 80C51 core

• 32K bytes of ROM for HMS91C7132/4

(32K bytes of OTP ROM for HMS97C7132/4)

• 256 bytes of RAM and 256 bytes of XRAM for

DDC operation

• Uses an external crystal of 12 MHz

• One DDC compliant interface :

-

Fully supports DDC1 with dedicated hardware

- DDC2B, DDC2AB and DDC2B+ compliant dedicated hardware based on an I

2

C bus interface

- RAM buffer with programmable size, 128 bytes

or 256 bytes, which can be used for DDC operation or shared as system RAM

• On-chip sync processor

-

HSYNC frequency with 12-bit resolution

- VSYNC frequency with 12-bit resolution

- HSYNC and VSYNC polarity

- HSYNC and VSYNC presence detection

- Composite sync separation

- Free running sync. generation

- Clamping pulse output

- Pattern generation

- Separate input for a SOG signal

- Missing pulse insertion option

- HSYNC/ VSYNC change interrupt

• One multi-master/slave I2C interface (up to

400K bit/s) for control of other system IC’s

• Eight 8-bit Static PWM outputs for digital control applications

• Two 8-bit Dynamic PWM outputs for variou s

waveform generation

• One 8-bit ADC with 4 input channels

• LED dri ver port ; two port lines wit h

15 mA drive capability

• One 8-bi t port only for I/O func ti on

• 24 derivative I/O ports configurable for alternative functions

• Watchdog timer (524ms max. )

• On-chip low VDD voltage detect and reset

(reset period: 524ms)

• Operating temperature : 0 to 70

• Special idle and power-down modes with low

power consumption

• Single power supply : 4.5V to 5.5V

Device name ROM Size

RAM

Size

I/O OTP Package

HMS91C7132/4

32K bytes

Mask ROM

512 bytes

30(42DIP)

32(42SDIP)

HMS97C7132/4

40DIP(HMS91C7132/4),

42SDIP(HMS91C7132/4K)

HMS9 xC 7132 / HMS9xC7134

2 May.2001 ver1.1

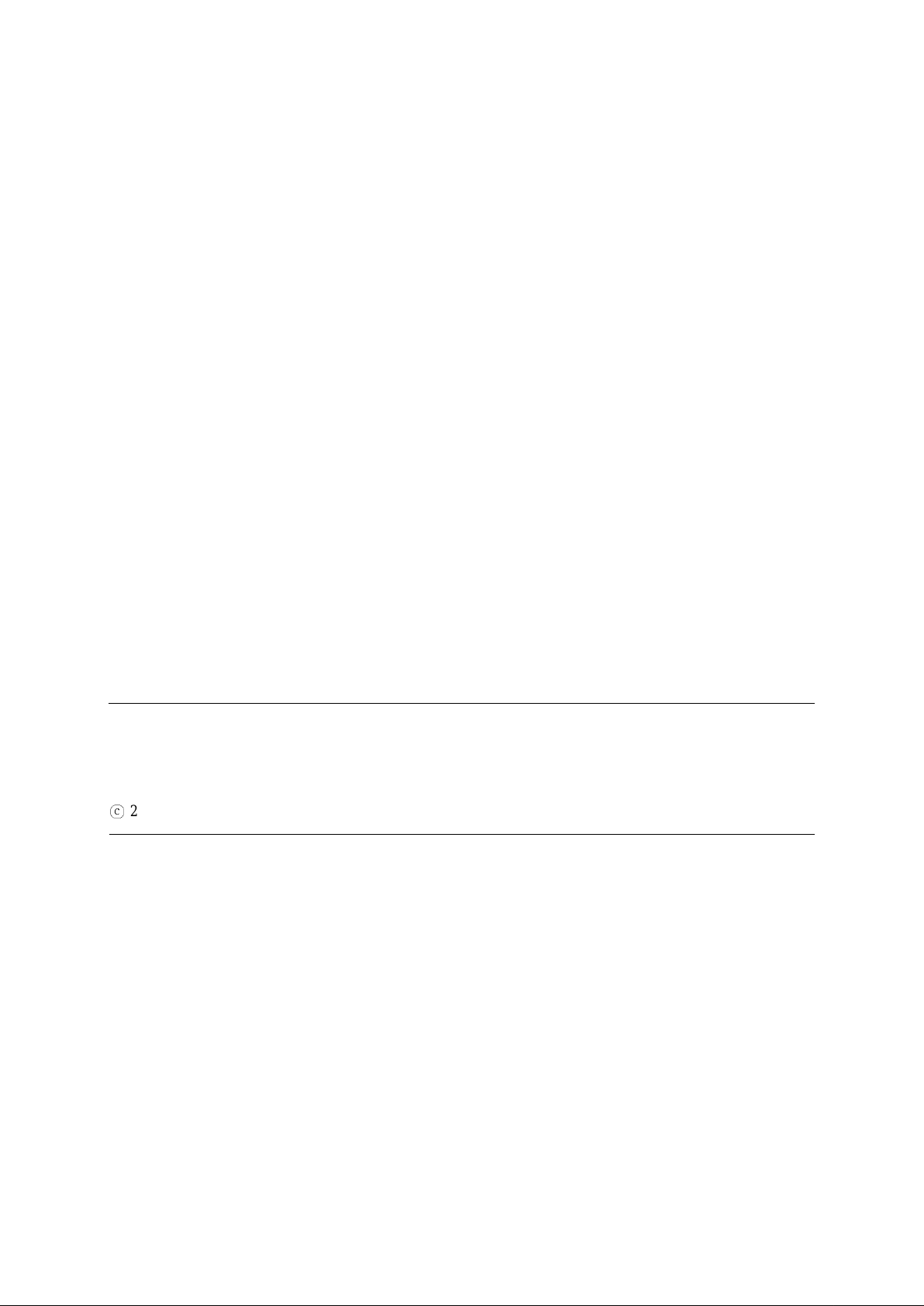

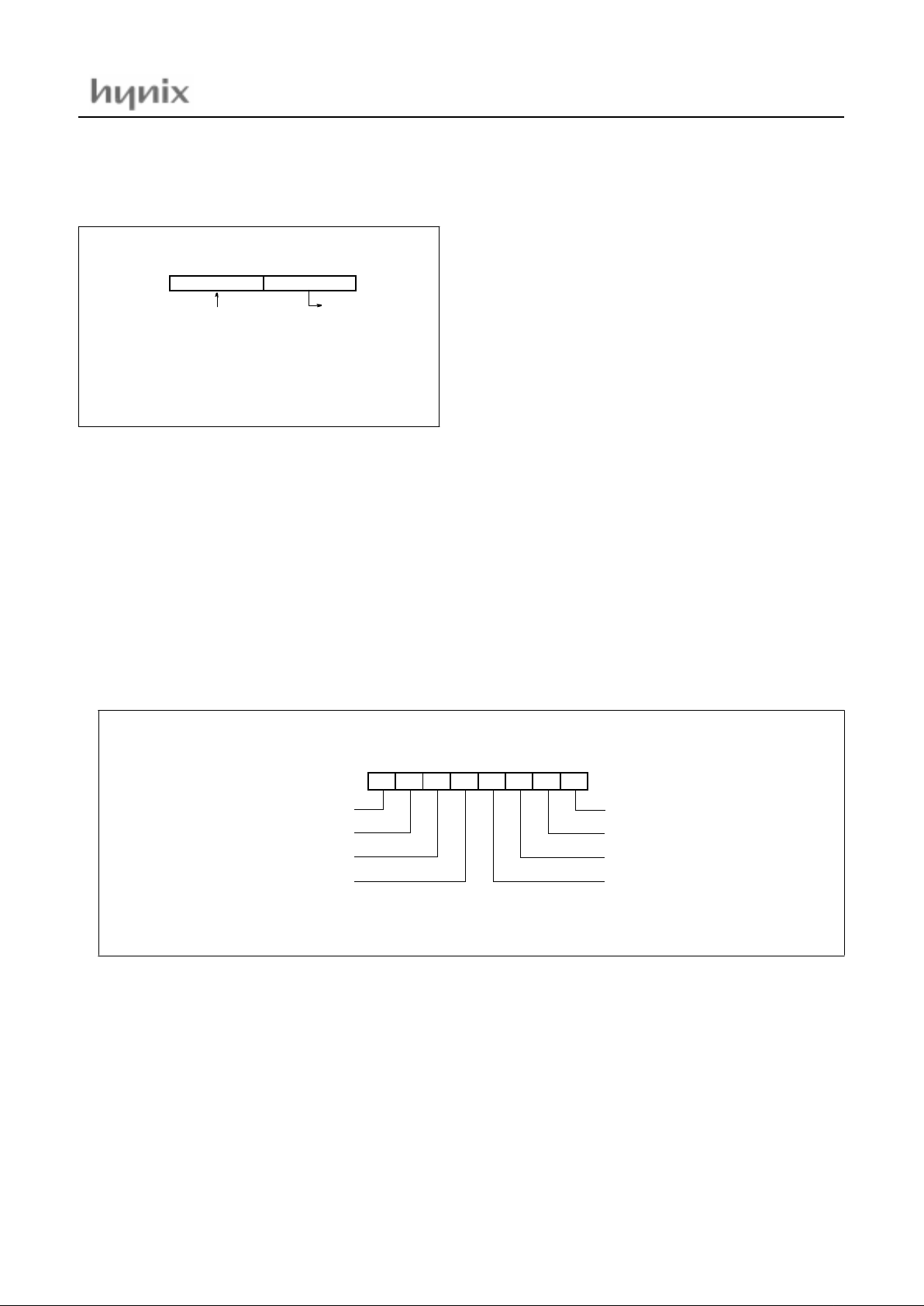

2. BLOCK DIAGRAM

VDD2 VSS2

RESET

SDA2 SCL2

A CH [3:0]

VDD1

VSS1

IN T0

XTAL1

XTAL2

DPWM 0

to

DPWM 1

PW M 0

to

PW M 7

SDA1

SCL1

P 0 P1 P2 P3

PATOUT

CLAMP

HSYNCout

VSYNCout

VSYNCin

HSYNCin

SOGin

Th ree 16-Bit

Ti mers

( T0, T1, T2 )

CPU

Program

Memory

(64KB)

D a ta

Memory

(64KB)

8-Bit

ADC

I2C-Bus

Se rial I/O

Watch Dog

T imer

Pa ra lle l

I/O P orts

&

External Bus

Sy n c . De tec tio n

& S ync. Process

DDC

Interface

8x8-Bit

Sta tic

PW M

2x8-Bit

Dynam ic

PW M

L o w

V o ltag e

R e se t

80C51 core

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

3

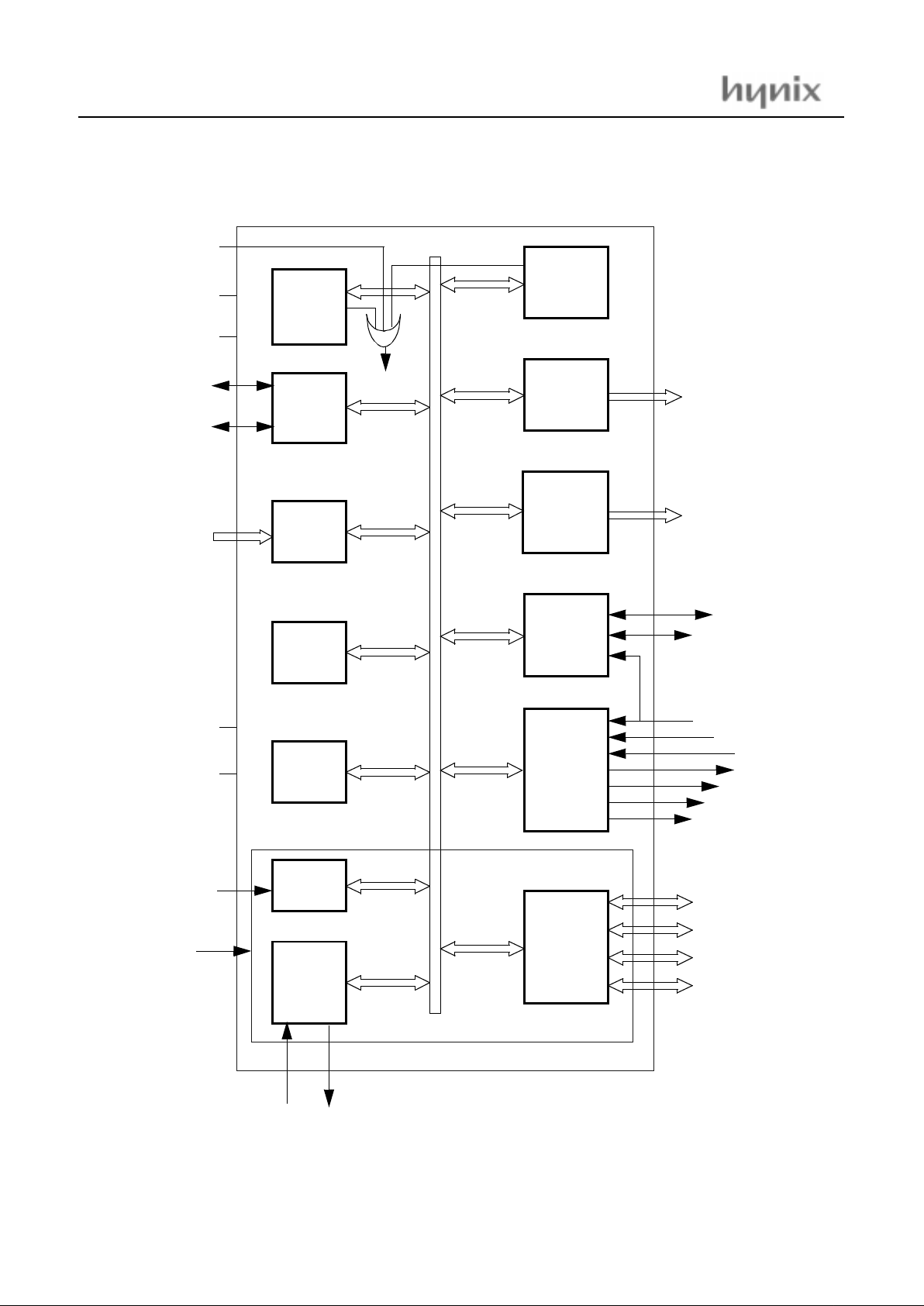

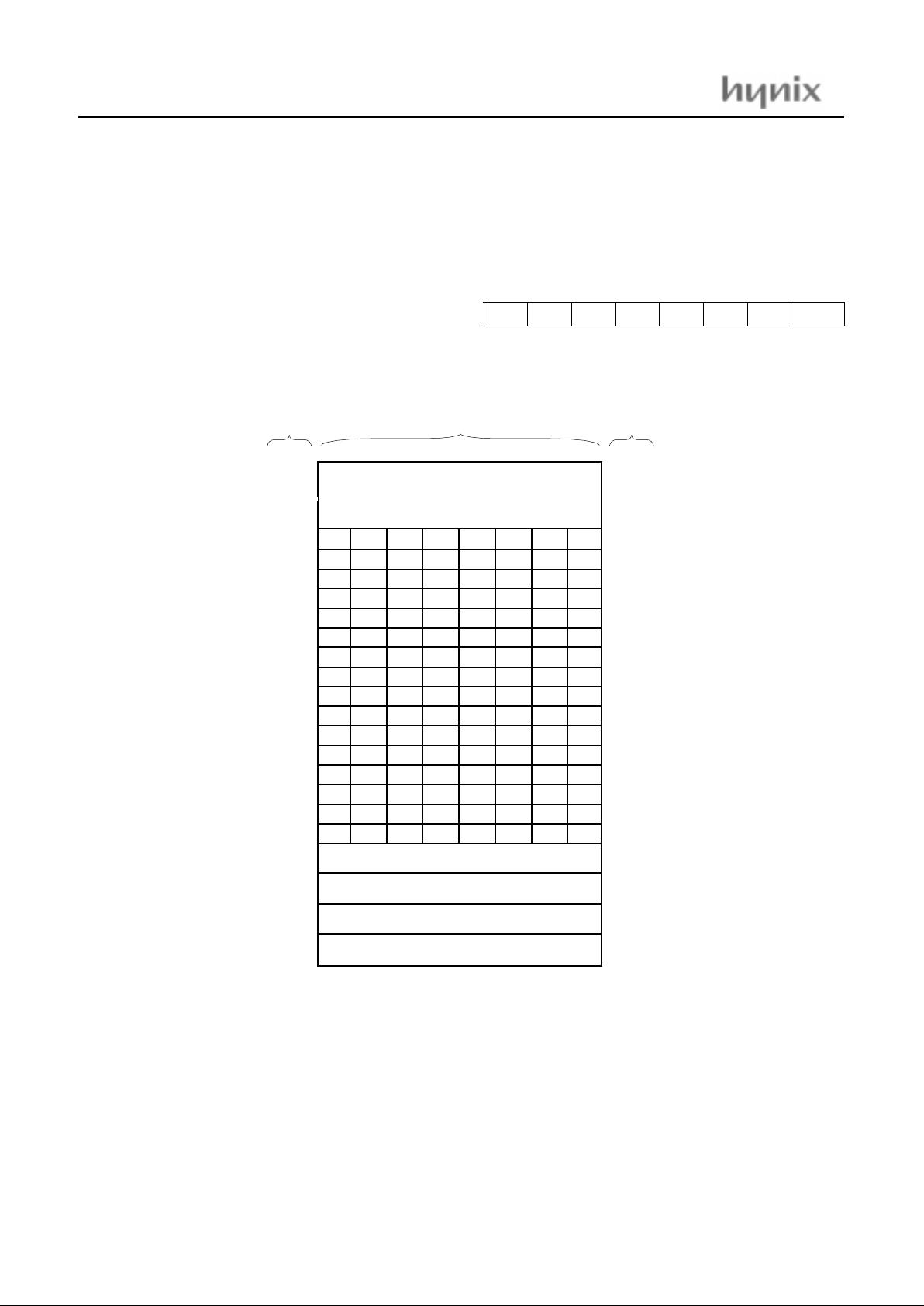

3. PIN ASSIGNMENT

3.1 40PDIP pinning

Vsync-IN

Hsync-IN

PWM1* /P2.3

PWM2* /P2.4

PWM3* /P2.5

PWM4* /P2.6

PWM5* /P2.7

Hsync-OUT /P3.2

Vsync-OUT /P3.3

PWM6* /IN T 1 /P3.4

CLAMP/PWM /P3.5

PADOUT /P3.6

SOG /P3.7

V

DD2

V

SS2

SCL1** /P1.0

SDA1** /P1.1

ACH0 /P1.2

ACH1 /P1.3

ACH2 /P1.4

PWM0* /P2.2

DPWM0* /P2.1

DPWM0* /P2.0

RESET

V

DD1

V

SS1

XTAL2

XTAL1

SDA2** /P1.7

SCL2** /P1.6

P0.7**

P0.6**

P0.5**

P0.4**

INT0/VPP

P0.3**

P0.2**

P0.1**

P0.0**

ACH3 /P1.5

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

HMS9xC7132

* : Open-drain opti on

** : Open-drain type pin

40DIP

(Top View)

Vsync-IN

Hsync-IN

PWM1* /P2.3

PWM2* /P2.4

PWM3* /P2.5

PWM4* /P2.6

PWM5* /P2.7

Hsync-OUT /P3.2

Vsync-OUT /P3.3

PWM6* /INT1 /P3.4/CLAMP

PWM /P3.5

PADOUT /P3.6

SOG /P3.7

P3.0

P3.1

SCL1** /P1.0

SDA1** /P1.1

ACH0 /P1.2

ACH1 /P1.3

ACH2 /P1.4

PWM0* /P2.2

DPWM0* /P2.1

DPWM0* /P2.0

RESET

V

DD1

V

SS1

XTAL2

XTAL1

SDA2** /P1.7

SCL2** /P1.6

P0.7**

P0.6**

P0.5**

P0.4**

INT0/VPP

P0.3**

P0.2**

P0.1**

P0.0**

ACH3 /P1.5

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

HMS9xC7134

* : Open-drain opti on

** : Open-drain type pin

40DIP

(Top View)

HMS9 xC 7132 / HMS9xC7134

4 May.2001 ver1.1

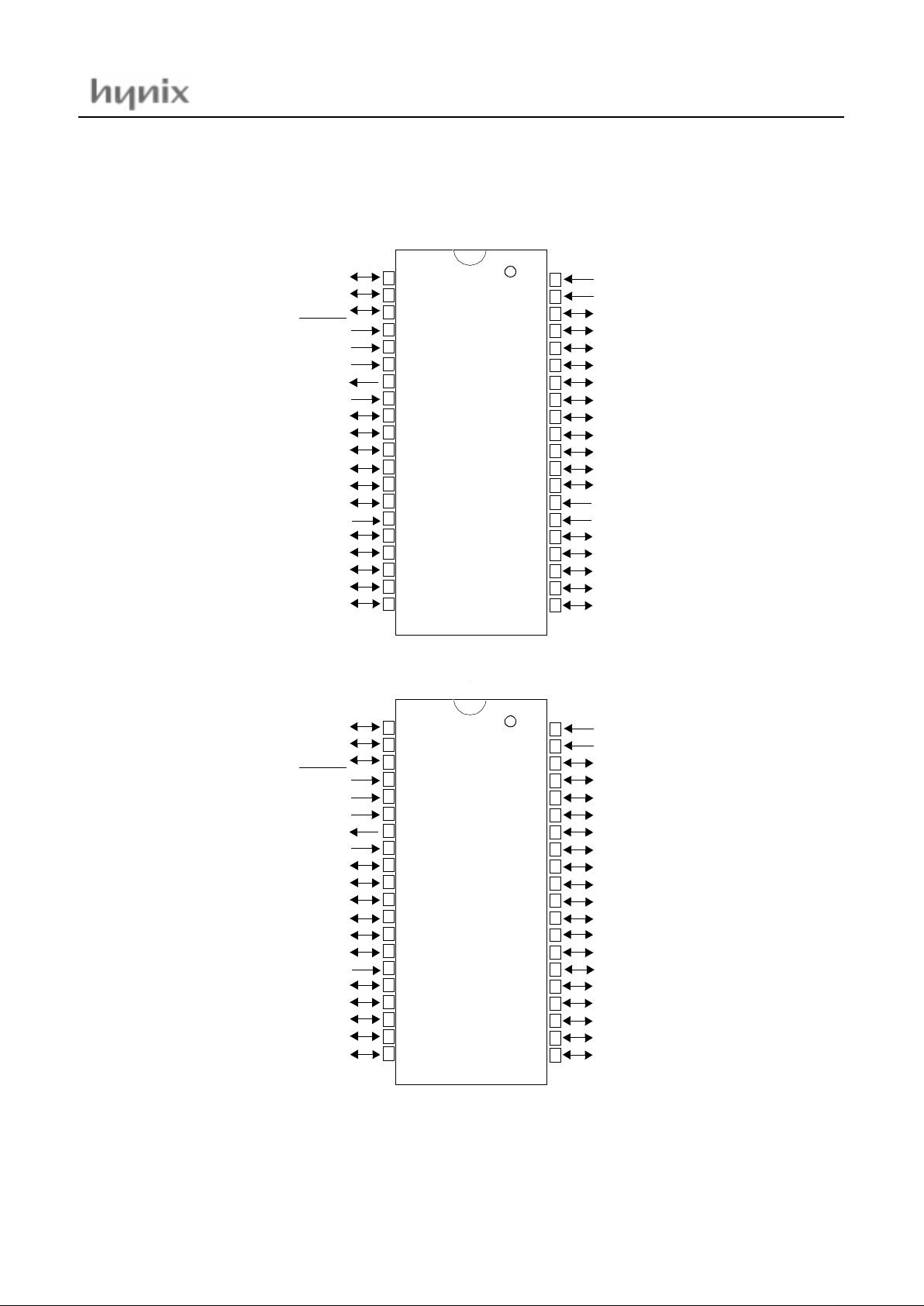

3.2 42SDIP pinning

Vsync-IN

Hsync-IN

PWM1* /P2.3

PWM2* /P2.4

PWM3* /P2.5

PWM4* /P2.6

PWM5* /P2.7

Hsync-OUT /P3.2

Vsync-OUT /P3.3

PWM6* /IN T 1 /P3.4

CLAMP/PWM /P3.5

PADOUT /P3.6

SOG /P3.7

V

DD2

V

SS2

SCL1** /P1.0

SDA1** /P1.1

ACH0 /P1.2

ACH1 /P1.3

ACH2 /P1.4

ACH3 /P1.5

PWM0* /P2.2

DPWM0* /P2.1

DPWM0* /P2.0

P3.1

P3.0

RESET

V

DD1

V

SS1

XTAL2

XTAL1

SDA2** /P1.7

SCL2** /P1.6

P0.7**

P0.6**

P0.5**

P0.4**

INT0/VPP

P0.3**

P0.2**

P0.1**

P0.0**

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

HMS9xC7132K

* : Open-drain option

** : Open-drain type pin

42SDIP

(Top View)

NC

Vsync-IN

Hsync-IN

PWM1* /P2.3

PWM2* /P2.4

PWM3* /P2.5

PWM4* /P2.6

PWM5* /P2.7

Hsync-OUT /P3.2

Vsync-OUT /P3.3

PWM6* /INT1 /P3.4/CLAMP

PWM /P3.5

PADOUT /P3.6

SOG /P3.7

P3.0

P3.1

SCL1** /P1.0

SDA1** /P1.1

ACH0 /P1.2

ACH1 /P1.3

ACH2 /P1.4

NC

PWM0* /P2.2

DPWM0* /P2.1

DPWM0* /P2.0

RESET

V

DD1

V

SS1

XTAL2

XTAL1

SDA2** /P1.7

SCL2** /P1.6

P0.7**

P0.6**

P0.5**

P0.4**

INT0/VPP

P0.3**

P0.2**

P0.1**

P0.0**

ACH3 /P1.5

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

HMS9xC7134K

* : Open-drain option

** : Open-drain type pin

42SDIP

(Top View)

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

5

4. PACKAGE DIMENSIONS

4.1 40 PD I P

4.2 42 SD I P

2.075

2.045

MAX 0.200

0.022

0.015

0.065

0.045

NOTE

1. DIMENSIONS DO NOT INCLUDE MOLD

FLASH AND DAMBAR PROTRUSION.

ALLOWABLE MOLD FLASH IS 0.010 INCH.

2. CONTROLLING DIMENSION : INCH.

0.550

0.530

1.470

1.450

NOTE

1. DIMENSIONS DO NOT INCLUDE MOLD

FLASH AND DAMBAR PROTRUSION.

ALLOWABLE MOLD FLASH IS 0.010 INCH.

2. CONTROLLING DIMENSION : INCH.

0.550

0.530

HMS9 xC 7132 / HMS9xC7134

6 May.2001 ver1.1

5. PIN FUNCTION

V

DD1

: Supply voltage (Di gital).

V

SS1

: Circuit ground (Digital).

V

DD2

: Supply vo ltage (Analog).

V

SS2

: Circuit ground (Analog).

RESET

: Reset the MCU.

XTAL1

: Input to the inverting oscillator amplifier and input to

the internal main clock operating circuit.

XTAL2

: Output from the invert ing oscill ator amplifi e r.

HSYNC

IN

: Horizo ntal sync input

VSYNC

IN

: Vertical sync input

INT0/V

PP

: External Interrupt input. Programming supply volt-

age(during O TP programming)

PORT:

The HMS9xC7132 has four 8-bit ports (Port0, Port1, Port2,

and Port3). Port0 - Port3 are the same as in the 80C51, with

the exception of the additional functions of Port1, Port2 and

Port3. Each has latch, SFR P0~P3’ output driver and input

buffer.

P0.0~P0.7

: P0 is an 8-bit CMOS bidirectional I/O port. P0 pins

have not pull -up res iste r a nd open- dr ain port. It has th e ca pabi lit y

of drive LED. How ever, while the alternative function is performed, th e por t type w ill remai n th e same. In ca se of appli cat ion

to extention of external memory, P0 outputted Write/Read byte

and lower byt e of external memory address. Therefore when it is

used as normal I/O port, P0 is open-d rain driver and when it used

as bus port, P0 is 3-state driver.

P1.0~P1.7

: P1 is an 8-bit CMOS bidirectional I/O port. Because

P1 pins have pull-up resister, it is called as Quasi-Bidirectional

port.

P2.0~P2.7

: P2 is an 8-bit CMOS bidirectional I/O por t. Because

P2 pins have pull-up resister, it is called as Quasi-Bidirectional

port. .

P3.0~P3.7

: P3 is an 8-bit CMOS bidirectional I/O por t. Because

P3 pins have pull-up resister, it is called as Quasi-Bidirectional

port.

Port pin Alternate funct ion

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

No (Only for I/O functi on)

No (Only for I/O functi on)

No (Only for I/O functi on)

No (Only for I/O functi on)

No (Only for I/O functi on)

No (Only for I/O functi on)

No (Only for I/O functi on)

No (Only for I/O functi on)

Port pin Alternate function

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

SCL1 (DDC-SCL)

SDA1 (DDC-SDA)

ACH0

ACH1

ACH2

ACH3

SCL2 (I

2

C-SCL)

SDA2 (I

2

C-SDA)

Port pin Alternate function

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

DPWM0*

DPWM1*

PWM0*

PWM1*

PWM2*

PWM3*

PWM4*

PWM5*

Port pin Alternate function

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

Reserved

Reserved

HSYNC

OUT

VSYNC

OUT

PWM6*

CLAMP/PWM7

PATOUT

SOG

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

7

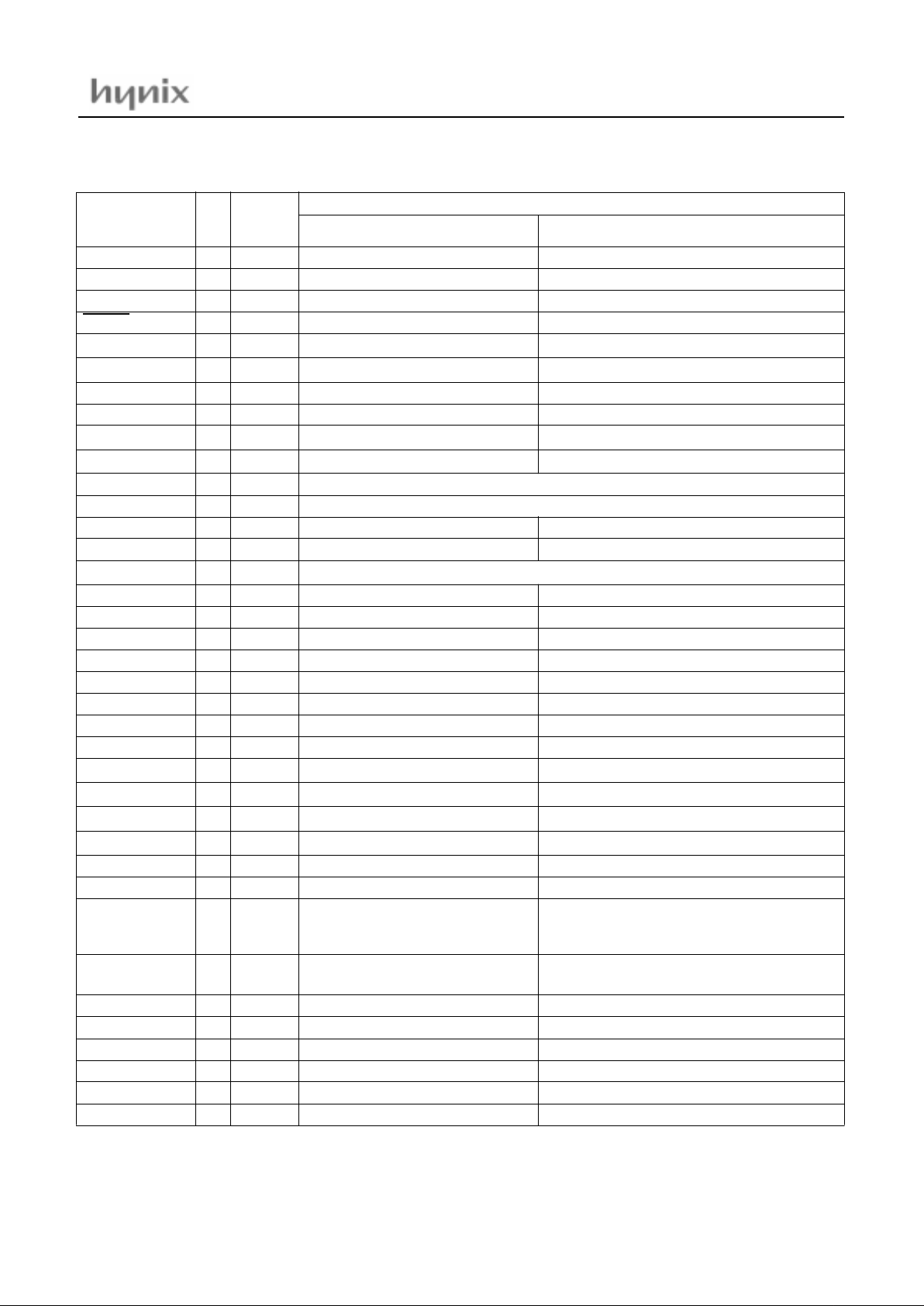

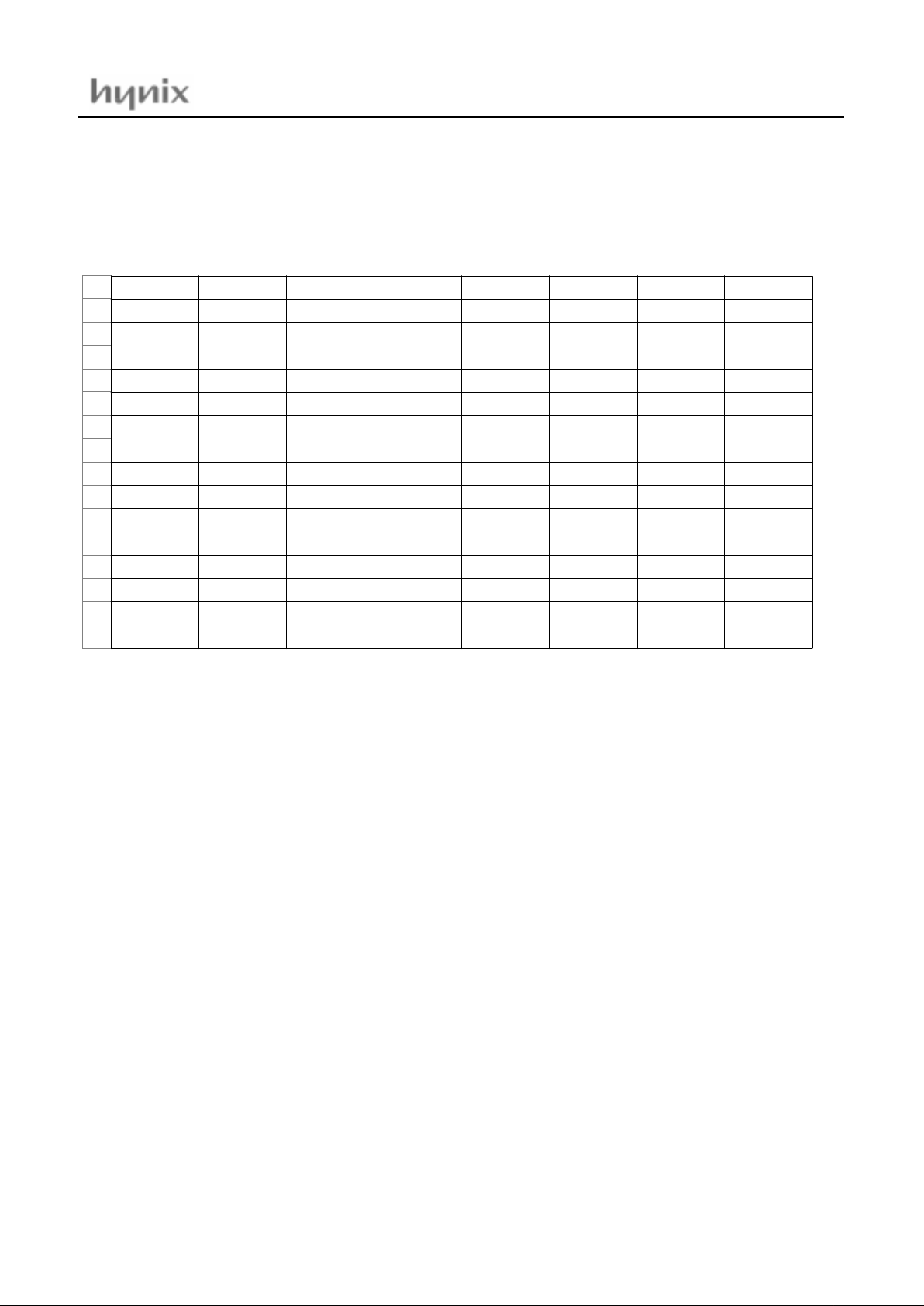

5.1 40DIP Pin Description

PIN NAME

(Alternate)

Pin

No.

In/Out

(Alter-

nate)

Function

Basic Alternate

PWM0 /P2.2 1 I/O General I/O port P2.2 8-bit Pulse Width Modulation output0

DPWM0 /P2.1 2 I /O General I/O port P2.1 8-bit Dynamic Pulse Width Modulation output0

DPWM0 /P2.0 3 I /O General I/O port P2.0 8-bit Dynamic Pulse Width Modulation output1

RESET

4 I Reset input

V

DD1

5 - Power supply1(+5V)

V

SS1

6 - Ground1

XTAL2 7 O Oscillat or out put pin for system clock

XTAL1 8 I Oscillator input pin f or system clock

SDA2 /P1.7 9 I/O General I/O port P1.7

I2C serial data I/O port

SCL2 /P1.6 10 I/O General I/O port P1.6

I

2

C serial clock I/O port

P0.7 11 I/O Gen eral I/O port P0.7; adapted for LED driver

P0.6 12 I/O Gen eral I/O port P1.6; adapted for LED driver

P0.5 13 I/O General I/O port P0.5

P0.4 14 I/O General I/O port P0.4

INT0 /V

PP

15 I External interrupt input 0; Pr ogramming supply voltage ( duri ng OTP programming)

P0.3 16 I/O General I/O port P0.3

P0.2 17 I/O General I/O port P0.2

P0.1 18 I/O General I/O port P0.1

P0.0 19 I/O General I/O port P0.0

ACH3 /P1.5 20 I/O General I/O port P1.5 ADC channel3 input

ACH2 /P1.4 21 I/O General I/O port P1.4 ADC channel2 input

ACH0 /P1.3 22 I/O General I/O port P1.3 ADC channel1 input

ACH0 /P1.2 23 I/O General I/O port P1.2 ADC channel0 input

SDA1 /P1.1 24 I/O General I/O port P1.1

I

2

C serial data I/O port for DDC interf ace

SCL1 /P1.0 25 I/O General I/O port P1.0

I

2

C serial clock I/O port for DDC interface

V

SS2

26 - Ground2

V

DD2

27 - Power supply2(+5 V)

SOGin /P3.7 28 I/O General I/ O port P3.7 Sync on Green input

PATOUT /P3.7 29 I/O General I/O port P3.6 Pattern out

CLAMP /PWM7 /

P3.5 /PR O G

30 I/O

General output only port P3.5

Program pulse input(during OTP

programming)

Clamp out ; 8-bit Pulse Widt h Modu lation

output7

PWM6 /P3.4 /

INT1

31 I/O General I/O port P3.4

8-bit Pulse Width Modu lat ion output6; External

interrupt input 1

VSYNCout /P3.3 32 I/O General I/O port P3.3 Vertical sync output

HSYNCout /P3.2 33 I/O General I/O port P3.2 Horizontal sync output

PWM5 /P2.7 34 I/O General I/O port P2.7 8- bit Pulse Width Modulation output5

PWM4 /P2.6 35 I/O General I/O port P2.6 8- bit Pulse Width Modulation output4

PWM3 /P2.5 36 I/O General I/O port P2.5 8- bit Pulse Width Modulation output3

PWM2 /P2.4 37 I/O General I/O port P2.4 8- bit Pulse Width Modulation output2

Table 5-1 Port Function Descri ption(40DIP)

HMS9 xC 7132 / HMS9xC7134

8 May.2001 ver1.1

5.2 42SDIP Pin Description

The 42SDIP type pin description is the same as The 40DIP type pin description except for adding two pins(P3.1, P3.0) to it

between pin no.4 and 5.

PWM1 /P2.3 38 I/O General I/O port P2.3 8-bit Pulse Width Modulation output1

HSYNCin 39 I Horizontal sync input

VSYNCin 40 I Vertical sync input

PIN NAME

(Alternate)

Pin

No.

In/Out

(Alter-

nate)

Function

Basic Alternate

Table 5-1 Port Function Descri ption(40DIP)

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

9

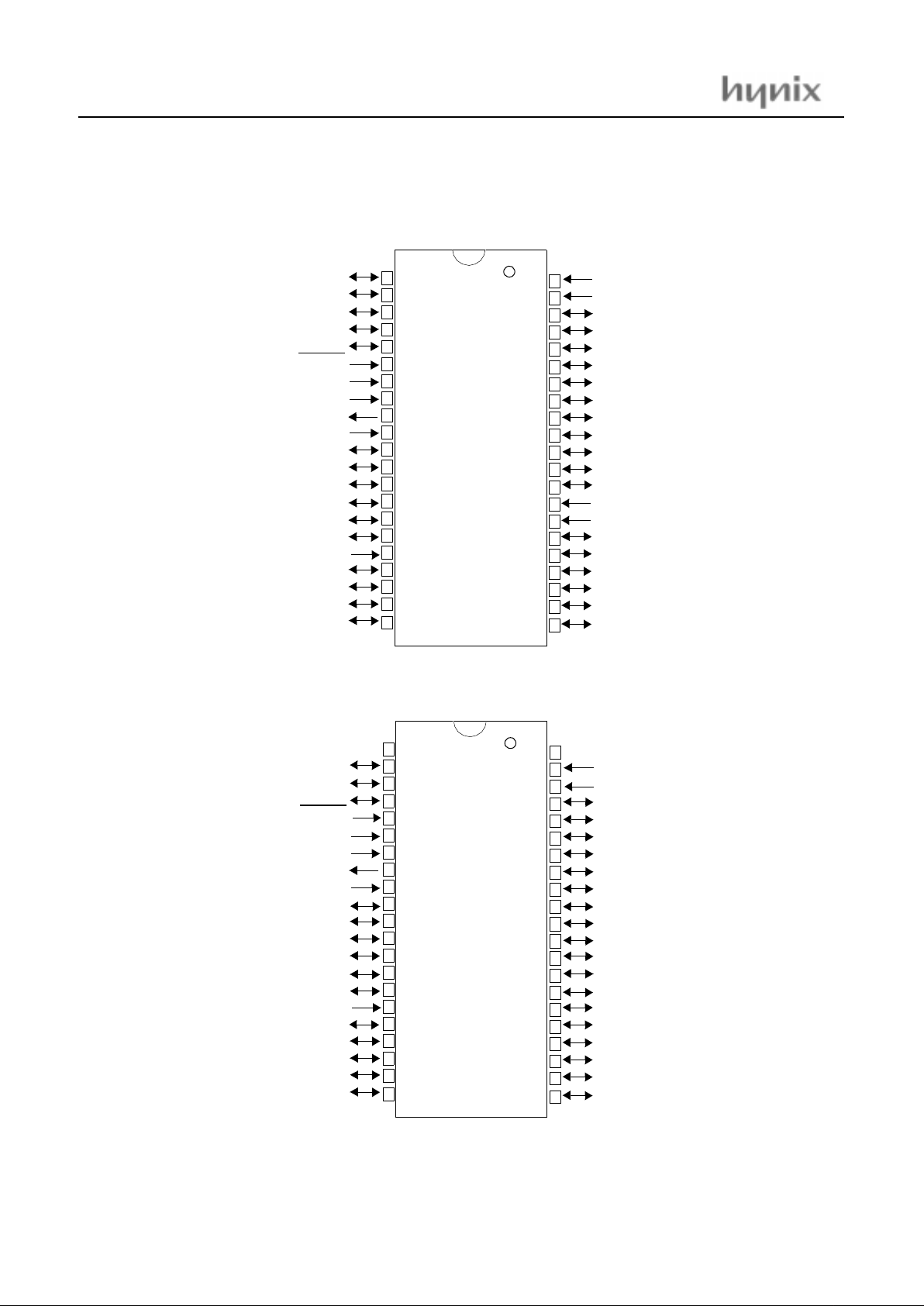

6. PORT STRUCTURES

P0.0 - P0.5 P0.6 - P0.7

P1.0, P1.1, P1.6, P1.7, P2.0~7, P3.0, P3.1, P3.4, P3.6 P1.2 - P1.5

P3.2, P3 .3, P3.5 P3.7

data

CMOS

5mA

data

CMOS

10mA

oen

data

CMOS

adc_enb

oen

data

adc_in

CMOS

internal reset

data

TTL

oen

data

TTL

HMS9 xC 7132 / HMS9xC7134

10 May.2001 ver1.1

HSYNCIN, VSYNCIN INT0/VPP

RESET XTAL1, XTAL2

TTL

H

TTL

VPP detector

VPP

CMOS

pdb

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

11

7. ELECTRICAL CHARACTERISTICS

7.1 Absolute Maximum Ratings

Supply voltage......................................................-0.5 to +6.5 V

Storage Temperature .......................................... -65 to +150 °C

Voltage on any pin with respect to Ground (V

SS

)

..........................................................................-0.5 to V

DD

+0.5

Note: Stresses above those listed under "Absolute Maxi-

mum Ratings" may cause pe rmanent dam age to the device. This is a stress rating only and functional operation of

the device at a ny other conditio ns above those indicated in

the operational sections of this specification is not implied.

Exposure to abso lute maximum rati ng conditions for extended periods may aff ect device reliability.

7.2 Recommended Operating Conditions

7.3 DC El ectrical Char acteristics

(TA= 0~70°C, VDD=4.5~5.5V, VSS=0V )

,

Parameter Symbol Condition

Specifications

Unit

Min. Max.

Supply Voltage

V

DD

f

XIN

=12MHz

4.5 5.5 V

Operating Frequency

f

XIN

VDD=4.5~5.5V

10 16 MHz

Operating Temperature

T

OPR

-070

°

C

Symbol Parameter Condition

Specifications

Unit

Min. Typ. Max.

SUPPLY

VDD power supply volt age - 4.5 5.0 5.5 V

IDD power suppl y current Fosc - 12MHz

-

TBD

-

mA

VLVR low voltage reset - 3.3 3.7 4.1 V

OTP SUPPLY

VDD power supply volt age - 4.5 5.0 5.5 V

VPP programming voltage - - 12.75 - V

IDDP power supply current Fosc - 4MHz

-

TBD

-

mA

IPP programming current Fosc - 4MHz

-

TBD

-

mA

RESET

IRST RESET input pull-up resistance VIN - 0V

-

33 -

µ

A

IIH input leakage current VIN - VDD

-

01µA

VIL1 LOW-level input volt age - VSS-0.5 - 0.3VDD V

VIH1 HIGH-level input volt age - 0.7VDD - VDD+0.5 V

XTAL

VOP open bias voltage - - 2.5 - V

IFR feedback resistor current VIN - 5V - 10 -

µ

A

VIL1 LOW-level input volt age - VSS-0.5 - 0.3VDD V

VIH1 HIGH-level input volt age - 0.7VDD - VDD+0.5 V

INT0, HSYNCIN, VSYNCIN

IIL input leakage current VIN - VSS -1 0 -

µ

A

IIH input leakage current VIN - VDD - 0 1

µ

A

VIL LOW-level input voltage - VSS-0.5 - 0.3VDD V

HMS9 xC 7132 / HMS9xC7134

12 May.2001 ver1.1

VIH HIGH-level input voltage - 2.0 - VDD+0.5 V

SOG/P3.7

IIL1 input leakage current VIN - 0.45V -55 - -10

µ

A

ITL input transition current VIN - 2.0V -650 - -65

µ

A

IIH input lea kage current VIN - VDD - 0 1

µ

A

VIL LOW-level input voltage - VSS-0.5 - 0.8 V

VIH HIGH-level input voltage - 2.0 - VDD+0.5 V

VOL LOW-level output vol ta ge IOL - 5mA 0 - 0.4 V

VOH HIGH-level input voltage IOH - 5mA 3.5 - VDD V

P0.0 to P0.5

IIL input leakage current VIN - VSS -1 0 -

µ

A

IIH input lea kage current VIN - VDD - 0 1

µ

A

VIL1 LOW-level i nput voltage - VSS-0.5 - 0.3VDD V

VIH1 HIGH-level input voltage - 0.7VDD - VDD+0.5 V

VOL LOW-level output vol ta ge IOL - 5mA 0 - 0.4 V

P0.6 to P0.7

IIL input leakage current VIN - VSS -1 0 -

µ

A

IIH input lea kage current VIN - VDD - 0 1

µ

A

VIL1 LOW-level i nput voltage - VSS-0.5 - 0.3VDD V

VIH1 HIGH-level input voltage - 0.7VDD - VDD+0.5 V

VOL1 LOW-level output voltage IOL - 10mA 0 - 0.4 V

P2.0 to P2.7(BP2.0 to BP2.7)

IIL1 input leakage current VIN - 0.45V -55 - -10

µ

A

ITL1 input transition current VIN - 3.5V -650 - -65

µ

A

IIH input lea kage current VIN - VDD - 0 1

µ

A

VIL1 LOW-level i nput voltage - VSS-0.5 - 0.3VDD V

VIH1 HIGH-level input voltage - 0.7VDD - VDD+0.5 V

VOL LOW-level output vol ta ge IOL - 5mA 0 - 0.4 V

VOH HIGH-level input voltage IOH - 5mA 3.5 - VDD V

P1.0 to P1.7,P3.0,P3.1,P3.4,P3.6,P3.7

IIL1 input leakage current VIN - 0.45V -55 - -10

µ

A

ITL1 input transition current VIN - 3.5V -650 - -65

µ

A

IIH input lea kage current VIN - VDD - 0 1

µ

A

VIL1 LOW-level i nput voltage - VSS-0.5 - 0.3VDD V

VIH1 HIGH-level input voltage - 0.7VDD - VDD+0.5 V

VOL LOW-level output vol ta ge IOL - 5mA 0 - 0.4 V

VOH HIGH-level input voltage IOH - 5mA 3.5 - VDD V

P3.2 to P3.3,P3.5

IIL2 input leakage current VIN - 0.45V -960 -320

µ

A

ITL2 input transiti on current VIN - 2.0V -1240 -350

µ

A

IIH input lea kage current VIN - VDD 0 1

µ

A

VIL LOW-level input voltage - VSS-0.5 0.8 V

VIH HIGH-level input voltage - 2.0 VDD+0.5 V

Symbol Parameter Condition

Specifications

Unit

Min. Typ. Max.

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

13

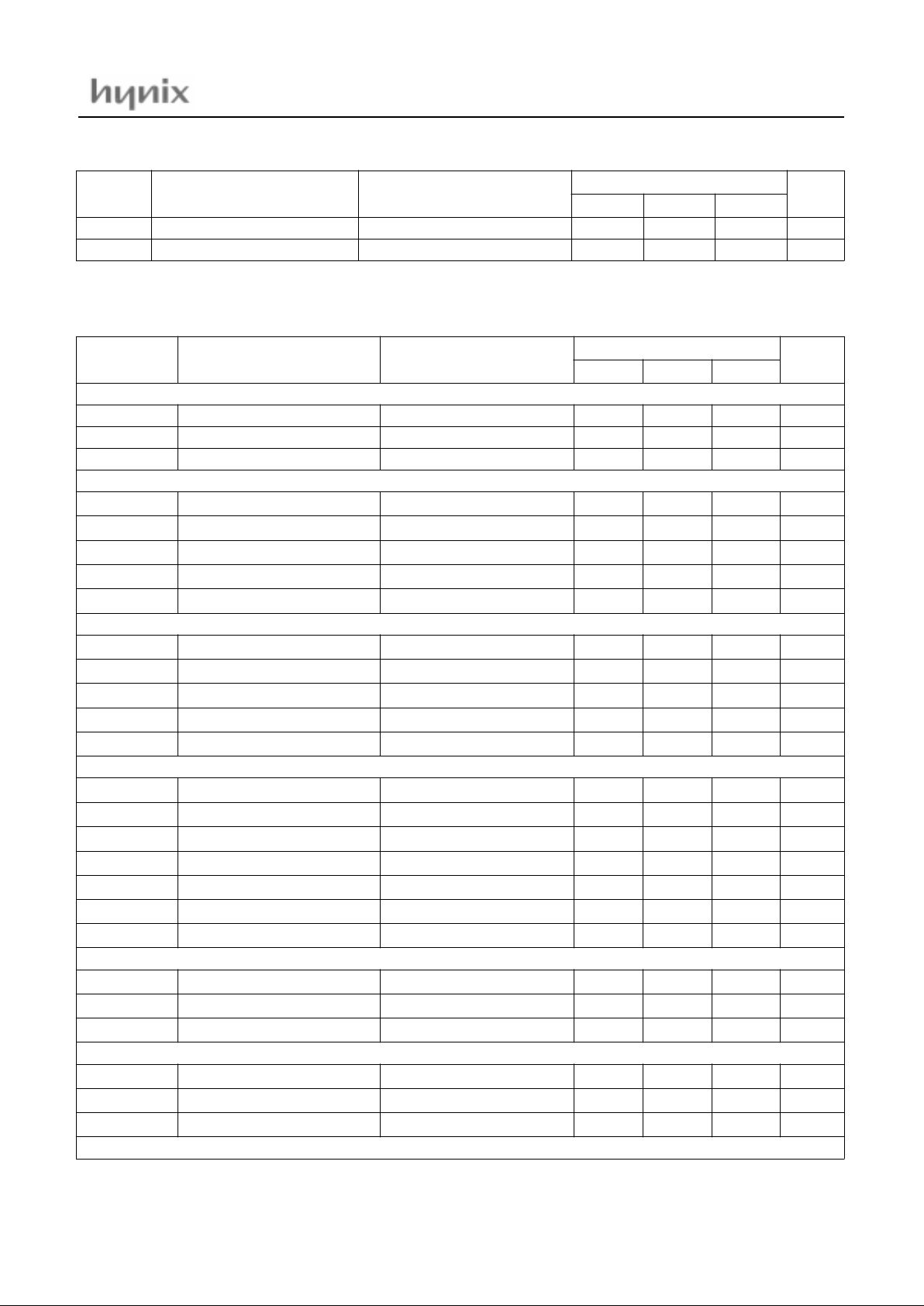

7.4 AC Characteristics

(TA=-0~70°C, VDD=5.0V, VSS=0V)

VOL LOW-level output voltage IOL - 5mA 0 0.4 V

VOH HIGH-level input voltage IOH - 5mA 3.5 VDD V

Symbol Parameter Condition

Specifications

Unit

Min. Typ. Max.

Symbol Parameter Condition

Specifications

Unit

Min. Typ. Max.

XTAL

fosc oscillator frequency VDD - 5V 10 12 16 MHz

C1 xtal1 external Cap. - - 20 - pF

C2 xtal2 external Cap. - - 20 - pF

A/D Converter

V

AIN

analog input voltage - VSS - VDD V

n

AOFF

zero offset error - - - TBD LSB

n

FS

full scale error - - 20 TBD LSB

n

ACC

overall acc uracy - - - TBD LSB

t

CONV

conversion tim e fosc - 12MHz - 13 -

µ

s

DDC1 Mode

t

H(VCLK)

VCLK high time - 20 - -

µ

sV

t

L(VCLK)

VCLK low time - 20 - -

µ

s

t

DOV

VCLK to output valid fosc - 12MHz - - 680

µ

s

t

SU(DDC1)

DDC1 mode setup time - - TBD -

µ

s

t

NC(IN)

cancelled noi se input fosc - 12MHz - - 300

µ

s

DDC2 Mode

f

SCL

SCL clock frequency - 0 - 100 kHz

t

HD(SDA)

Start condition hold time - 4.0 - -

µ

s

t

SU(STO)

Stop conditi on setup time - 4.0 - -

µ

s

t

HD(DAT)

Data hold time - 300 - -

µ

s

t

SU(STA)

Rstart(1) condition setup time - 4.7 - -

µ

s

t

H(SCL)

SCL high period - 4.0 - -

µ

s

t

L(SCL)

SCL low period - 4.7 - -

µ

s

HSYNCin

f

(HSYNC)

HSYNC input frequency - 12 - 120 kHz

t

W(HSYNC)

HSYNC input pulse width - 0.25 - 8

µ

s

d

(HSYNC)

HSYNC duty cycle - - - 25

%

VSYNCin

f

(VSYNC)

VSYNC input frequency - 32 - 200 Hz

t

W(VSYNC)

VSYNC input pulse width - 1 - 24

t

P(H)

d

(VSYNC)

VSYNC duty cycle - - - 25

%

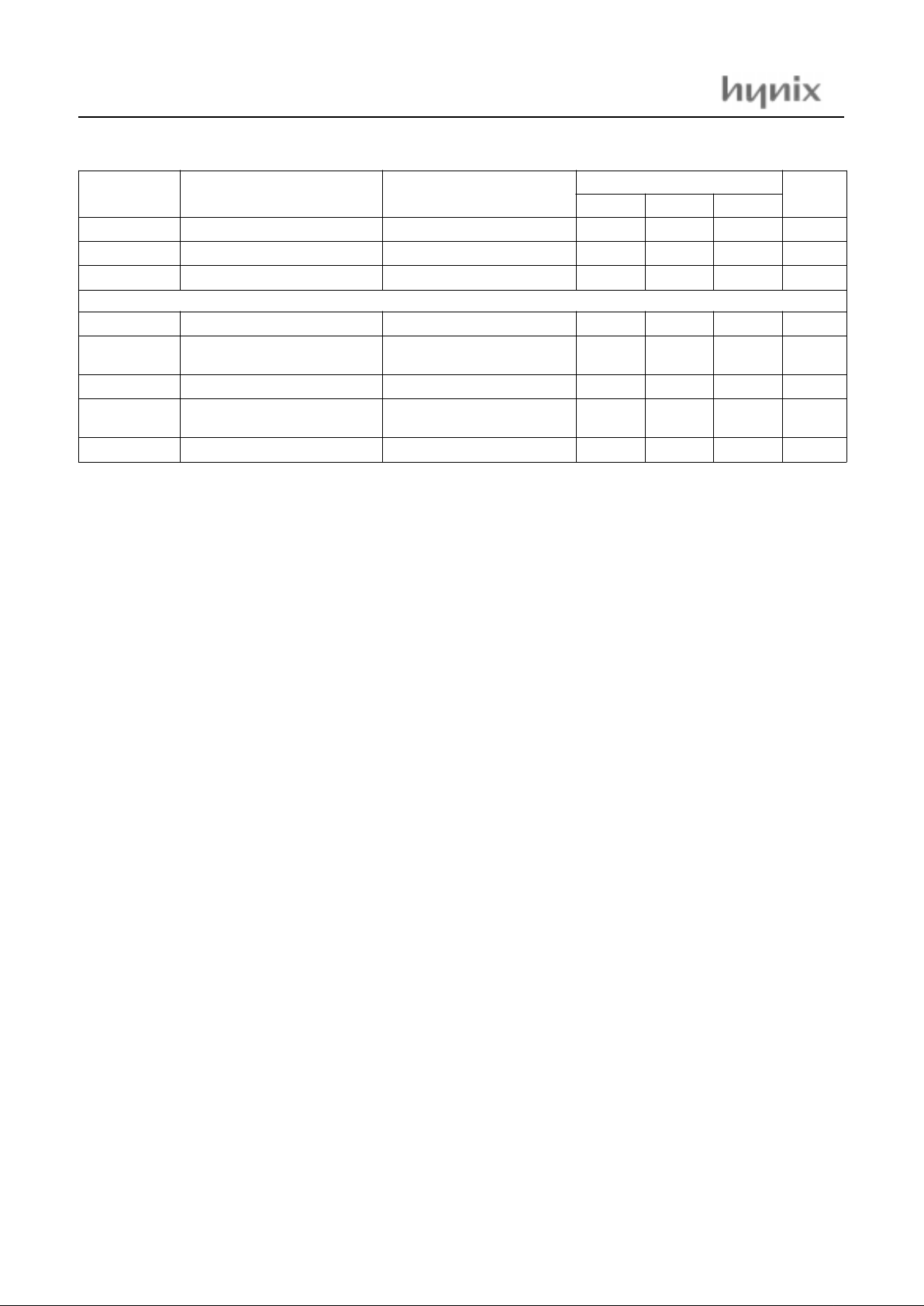

SOGin

HMS9 xC 7132 / HMS9xC7134

14 May.2001 ver1.1

t

P(EQ)

equalizing pulse period - - 0.5 -

t

P(H)

t

W(EQ)

equalizing pulse widt h - - 0.5 -

t

W(H)

n

(EQ)

equalizing pulse interval - - - 30

t

P(H)

HSYNCout, VSYNCout

t

D(HSYNC)

HSYNC input to output - - - 100 ns

t

D,MAX(HSYNC)

HSYNC input to output

after missing HSYNCin

- - - 250 ns

t

D(HSYNC)

VSYNC input to output - - - 180 ns

t

D,MAX(VSYNC)

VSYNC input to output

after missing VSYNCin

---1

t

P(H)

t

D(CLAMP)

HSYNCin to CLAMP - - - 100 ns

Symbol Parameter Condition

Specifications

Unit

Min. Typ. Max.

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

15

Figure 7-1 timing on the I2C- bus

Figure 7-2 SYNC timing

SDA

SCL

t

HD(SDA)

t

HD(DAT)

t

SU(DAT)

t

SU(STA)

t

SU(STO)

HSYNCin

HSYNCout

t

D(HSYNC)

t

D,MAX(HSYNC)

t

W(HSYNC)

CLAMP

(front porch)

t

D(CLAMP)

t

D(CLAMP)

CLAMP

(back porch)

VSYNCin

VSYNCout

t

D(VSYNC)

t

D,MAX(VSYNC)

t

W(VSYNC)

HMS9 xC 7132 / HMS9xC7134

16 May.2001 ver1.1

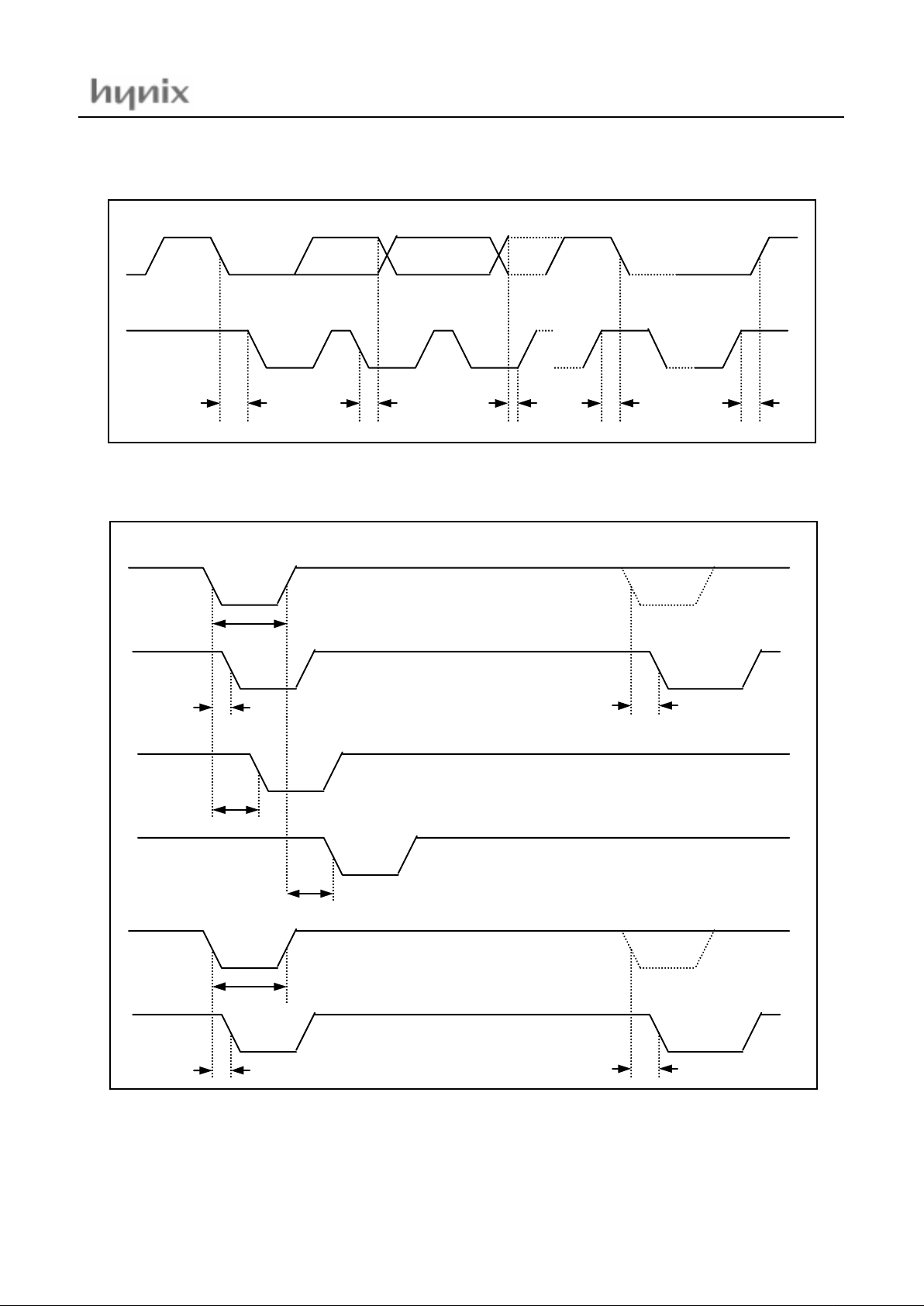

8. MEMORY ORGANIZATION

The HMS91C7132 has separate address spaces for Program

memory, Data Memory. Program memory can only be read, not

written to. It can be up to 32K bytes of Program memory.(OPT

type: HMS97C7132 32K bytes)

Data memory can be read and written to up to 256 bytes including

the stac k area.(In ternal R AM) and 256b ytes (Ex ternal RAM :

256bytes of XRAM0).

Figure 8-1 Memory map and address spaces

8.1 Registers

This device has several registers that are the Program Counter

(PC), A cc umul at or (A) , B regis te r( B), t he St ack P o inte r ( SP ), th e

Program Status Word(PSW), General purpose register(R0~R7)and DPTR(Data poi nter register).

Figure 8-2 Configuration of Registers

Accumulator:

The Accumu lator is the 8-bit gen eral pur pose reg-

ister, used for data operation such as transfer, temporary saving,

and condit ional judgement, etc. Th e A ccumulator can be used as

a 16-bit register with B Register as shown below.

Figure 8-3 Configuration of BA 16-bit Registers

B Register:

The B Regi ster is the 8-bit pu rpose register, used for

an arithm atic ope ration su ch as multi p ly, division with A ccumulator

Stack Pointer

: The Stack Pointer is an 8-bi t register used for occurrence interrupts and calling out subroutines. Stack Pointer

identifies the location in the stack to be access (save or restore).The stack can be located at any position within 0000

H

to

007F

H

of the internal data memory. The SP is not initialized by

hardware, requiring to write the initial value (the location with

32K ROM

Indirec t

only

(“mov @ri”)

Direct(“m ov”)

or Indirect

(“mov @ri”)

0

127

255

Direct

(“mov”) or

Indirect

(“mov @ri” )

Indirect

(“movx @ri” or

movx @dptr)

(XRAMS = 0)

data memoryprogram memory

SFR XRAMRAM

A

ACCUMULATOR

STACK POINTER

PROGRAM COUNTER

PROGRAM STATUS

WORD

SP

PCLPCH

PSW

R0~R7

GENERAL PURPOSE

B

B REGISTER

REGISTER (BANK0~3)

DPTR(DPL)DPTR(DPH)

DATA POINTER

REGISTER

Two 8-bit Registers can be used as a "BA" 16-bit Register

B

A

B A

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

17

which the use of the stack starts) by using the initialization routine. Normally, the initial value of “07

H

” is used and the stack

area is 00

H

to 7FH .

Program Counter

: The Program Counter is a 16-bit wide which

consists of two 8-bit registers, PCH and PCL. This counter indicates the address of the next instruction to be executed. In reset

state, the program counter has reset routine address (PC

H

:0FFH,

PC

L

:0FEH).

Program Status Word

: The Program Status Word (PSW) contains several bits that reflect the cur rent stat e of the CPU an d select Internal RAM(00H~1FH:Bank0~Bank3). The PSW is

described in Figure 8-4. It contains the Carry flag, the Auxiliary

carry flag, the Half Carry (for BCD operation), the General purpose flag, the Register bank select flags, the Overflow flag, the

undefine d flag and Parity flag.

[Carry flag CY]

This flag stores any carry or not borrow from the ALU of CPU

after an arithmetic operation and is also changed by the Shift Instruction or Rotate Instruction.

[Auxiliary carry flag AC]

After operation, this is set when there is a carry from bit 3 of ALU

or there is no borrow from bit 4 of ALU.

[Register bank select flags RS0, RS1]

This flags s elect one of four bank(0 0~07H:b ank0, 08~ 0fH:bank 1,

10~17H:bank2, 17~1FH:bank3)in Internal RAM.

[Overflow flag OV]

This flag is set to “1” when an overflow occurs as the result of an

arithmetic operation involving signs. An overflow occurs when

the result of an addition or subtraction exceeds +127(7F

H

) or -

128(80

H

). The CL R V in structio n cl ea rs the ov er fl ow flag. There

is no set instruction. When the BIT instruction is executed, bit 6

of memor y is cop i ed to th is flag.

[Parity flag P]

This flag r ef lect on nu mber of Accu mula to r’s 1. I f num ber of Ac-

uumulator’s 1 is odd, P=0. otherwise P=1. Sum of adding Acuumulator’s 1 to P is always even.

R0~R7

: Genera l purpos e re gister.

Data Pointer Register

:Data Pointer Register is 16-bit wide

which consi sts of two- 8bit re gi st ers, DPH an d DPL. This re gi st er

is used as a d ata pointer for the data transmission with external

data memory.

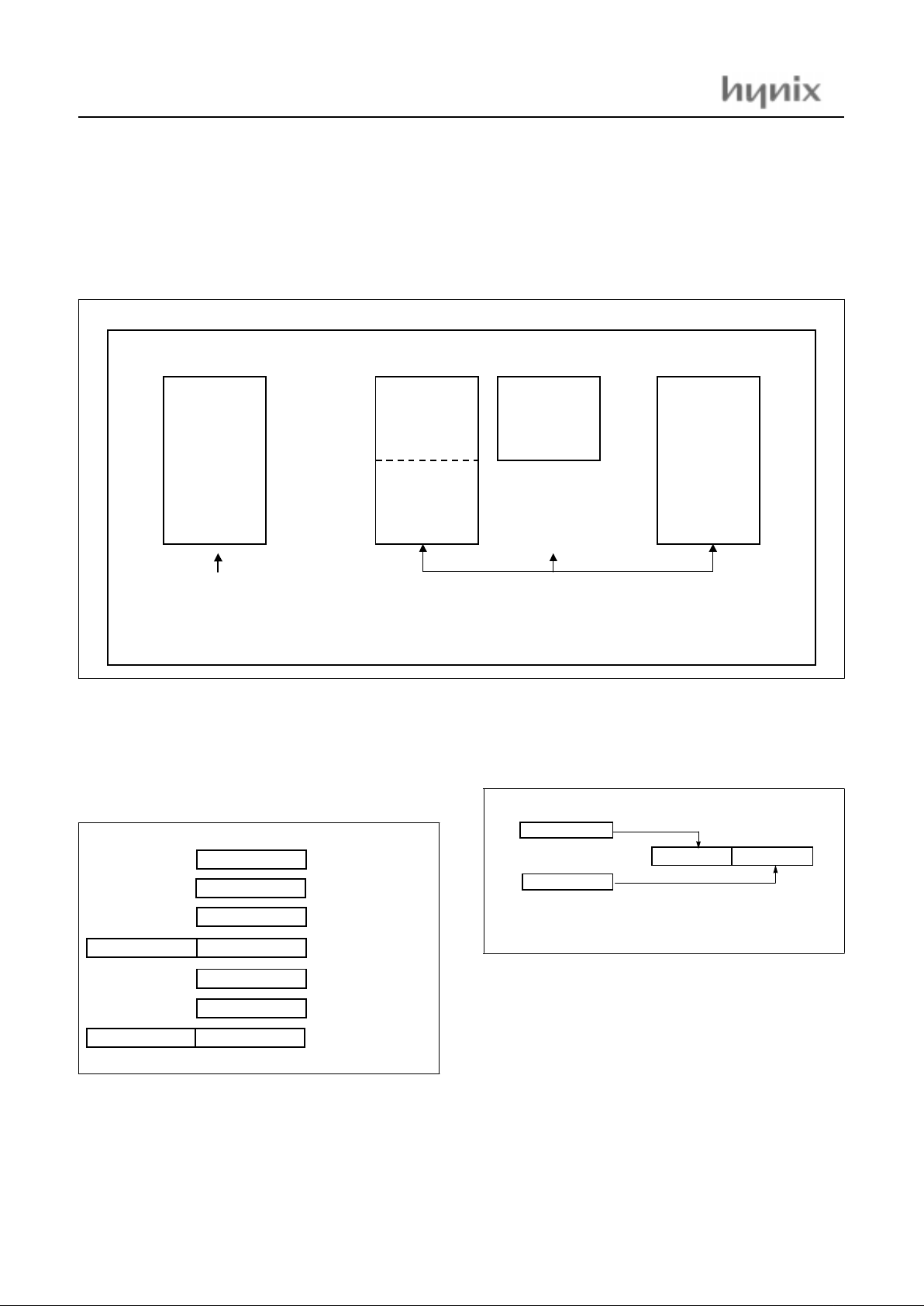

Figure 8-4 PSW(Program Stat us Wo rd)Register

8.2 Program Memory

The program memory consists of ROM : 32K bytes (HMS91C7132) and 32K bytes (HMS97C7132)

8.3 Data memory

The inte rnal data memory is d ivided into four phys ically sep arated part : 256 bytes of RAM, 256 byte s of XRAM0 , and 128 by te s

of Special Function Registers (SFRs) areas.

RAM

Four register banks, each 8 registers wide, occupy locations 0

through 3 1 in the lower RAM area. Only one of the se banks may

be enabled at a time. The next 16 bytes, locations 32 through 47,

SP

00

H

Stack Area (30H ~ 7FH)

Bit 15 Bit 087

Hardware fixed

00H~7F

H

SP (Stack Pointer) could be in 00H~7FH.

CARRY FLAG

MSB

LSB

RESET VALUE: 00

H

PSW

AUXILIARY CARRY FLAG

REGISTER BANK SELECT FLAG

PARITY FLAG

NOT ASSIGNED BIT

OVERFLOW FLAG

REGISTER BANK SELECT FLAG

GENERAL PURPOSE FLAG

CY AC F0 RS1 RS0 0V P

(to select Bank0~3 with RS0)

(to select Bank0~3 with RS1)

HMS9 xC 7132 / HMS9xC7134

18 May.2001 ver1.1

contain 128 directly addressable bit locations.The stack depth is

only limited by the available internal RAM space of 256 bytes.

XRAM0

The 256 bytes of XRAM0 used to support DDC interface is also

available fo r sys tem usa ge by ind irec t addr essi ng thr ou gh the address pointer DDCADR and data I/O buffer RAMBUF. The address pointer(D DCADR ) is e quippe d with the po stincre ment

capability to facilitate the transfer of data in bulk (for details refer

to DDC I nte rfac e p ar t) . H oweve r, it is a ls o poss ibl e to ad dre ss th e

DRAM through MOVX command as usually used in the internal

RAM extensi on of 80C51 de ri va tives . XRAM0 0 to 255 is di rect ly addressable as external data memory locations 0 to 255 via

MOVX-DPTR instruction or via MOVX-Ri instruction when the

EXCON’s LSB is zero. S ince exte rnal acc ess func tion is n ot

available, any ac cess to XRAM 0 0 to 255 w ill not affect the

ports.

7 6 5 4 3 2 1 0

Table 8-1 Extended control Register(EXCON)

Figure 8-5 RAM ADDRESS

-------

XRAMS

BANK 3

BANK 2

BANK 1

BANK 0

00H

07H

08H

0FH

10H

17H

1FH

18H

2FH

2EH

2DH

2CH

2BH

2AH

29H

28H

27H

26H

25H

24H

23H

22H

21H

20H

FFH

0

7

8

15

16

23

31

24

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

255

(MSB)

(LS B)

1F 1E 1D 1C 1B 1A 19 18

17 16 15 14 13 12 11 10

0F 0E 0D 0C 0B 0A 09 08

07 06 05 04 03 02 01 00

3F 3E 3D 3C 3B 3A 39 38

37 36 35 34 33 32 31 30

2F 2E 2D 2C 2B 2A 29 28

27 26 25 24 23 22 21 20

5F 5E 5D 5C 5B 5A 59 58

57 56 55 54 53 52 51 50

4F 4E 4D 4C 4B 4A 49 48

47 46 45 44 43 42 41 40

7F 7E 7D 7C 7B 7A 79 78

77 76 75 74 73 72 71 70

6F 6E 6D 6C 6B 6A 69 68

67 66 65 64 63 62 61 60

~

~

BYTE

ADDRESS

(HEX)

BIT

ADDRESS

(HEX )

BYTE

ADDRESS

(DECIMAL)

~

~

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

19

SFR

The SFRs can only be ad dressed directly in the address range

from 128 to 2 55. Tab le 8.2 gi ves an ov erview of the Spe cial F unction Regi sters spac e. Sixteen a ddress in th e SFRs space are both-

byte and bit-addre ssable. The bit-a ddressable SFRs are tho se

whose address ends in 0H and 8H. The bit addresses in this area

are 80H to FFH.

Table 8-2 SFR Memory Map

Note: * The register that can be bit-addressing.

F8

- HVGEN CPGEN VFH VFL HFH HFL

FF

F0

*B MDCON MDST VPH HPH VHPL

F7

E8

*EXCON - - -

EF

E0

*ACC-- ----

E7

D8

*S1CON S1STA S1DAT S1ADR0 S2CON S2STA S2DAT S2ADR

DF

D0

*PSW S1SDR1 RAMBUF DDCDAT DDCADR DDCCO N

D7

C8

*T2CON - RC2L RC2H - -

CF

C0

- -

C7

B8

*IP -

BF

B0

*P3 DPWMCON DPWM0 DPWM 1 - IPA -

B7

A8

*IE - PWM4 PWM5 PWM6 PWM7 WDTKEY

AF

A0

*P2 PWMCON PWM0 PWM1 PWM2 PWM3 WDTRST IEA

A7

98

--

9F

90

*P1 P1SFS P2SFS P3SFS ADAT ACON

97

88

*TCON TMOD TL0 TL1 TH0 TH1

8F

80

*P0 SP DPL DPH PCON

87

HMS9 xC 7132 / HMS9xC7134

20 May.2001 ver1.1

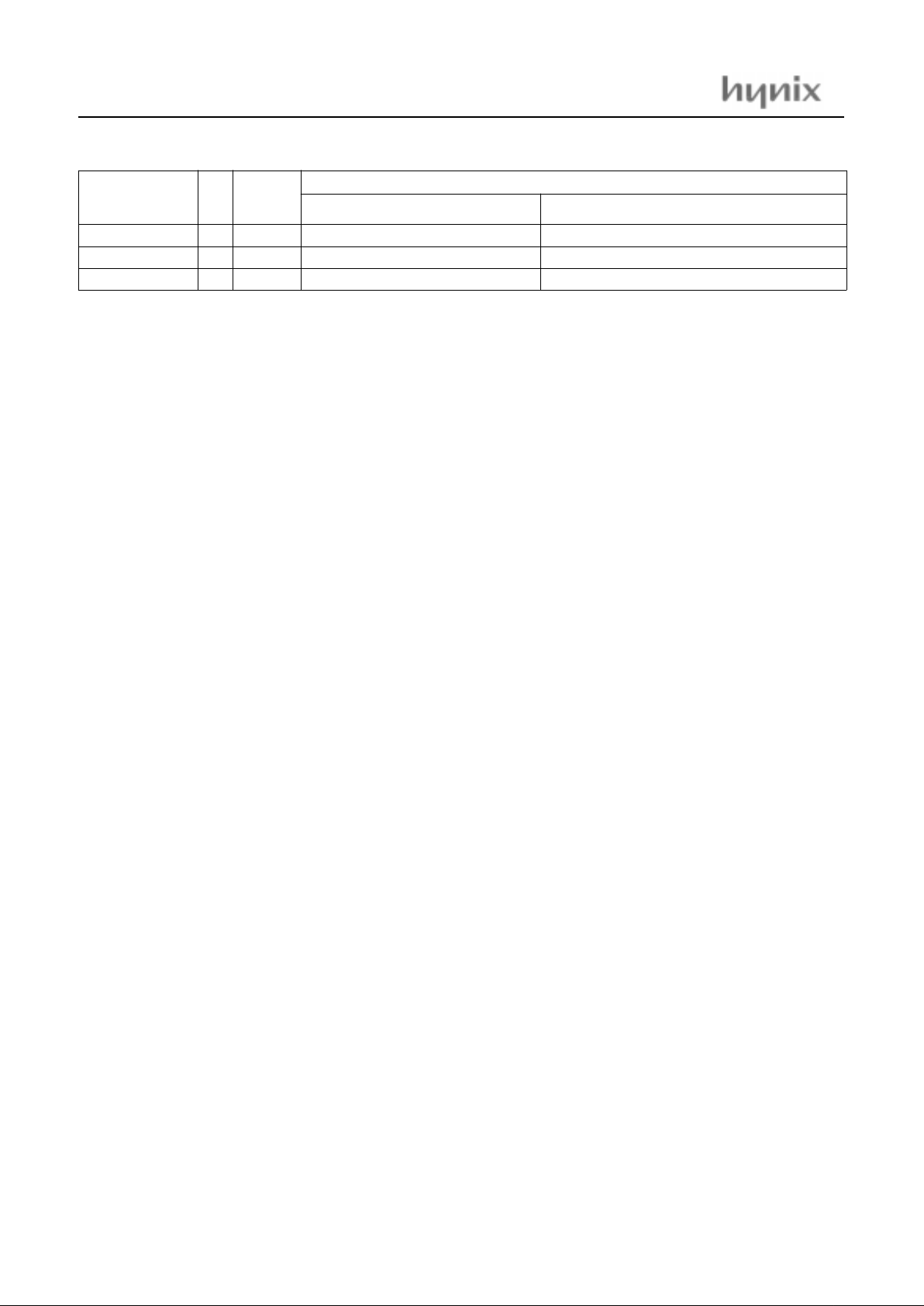

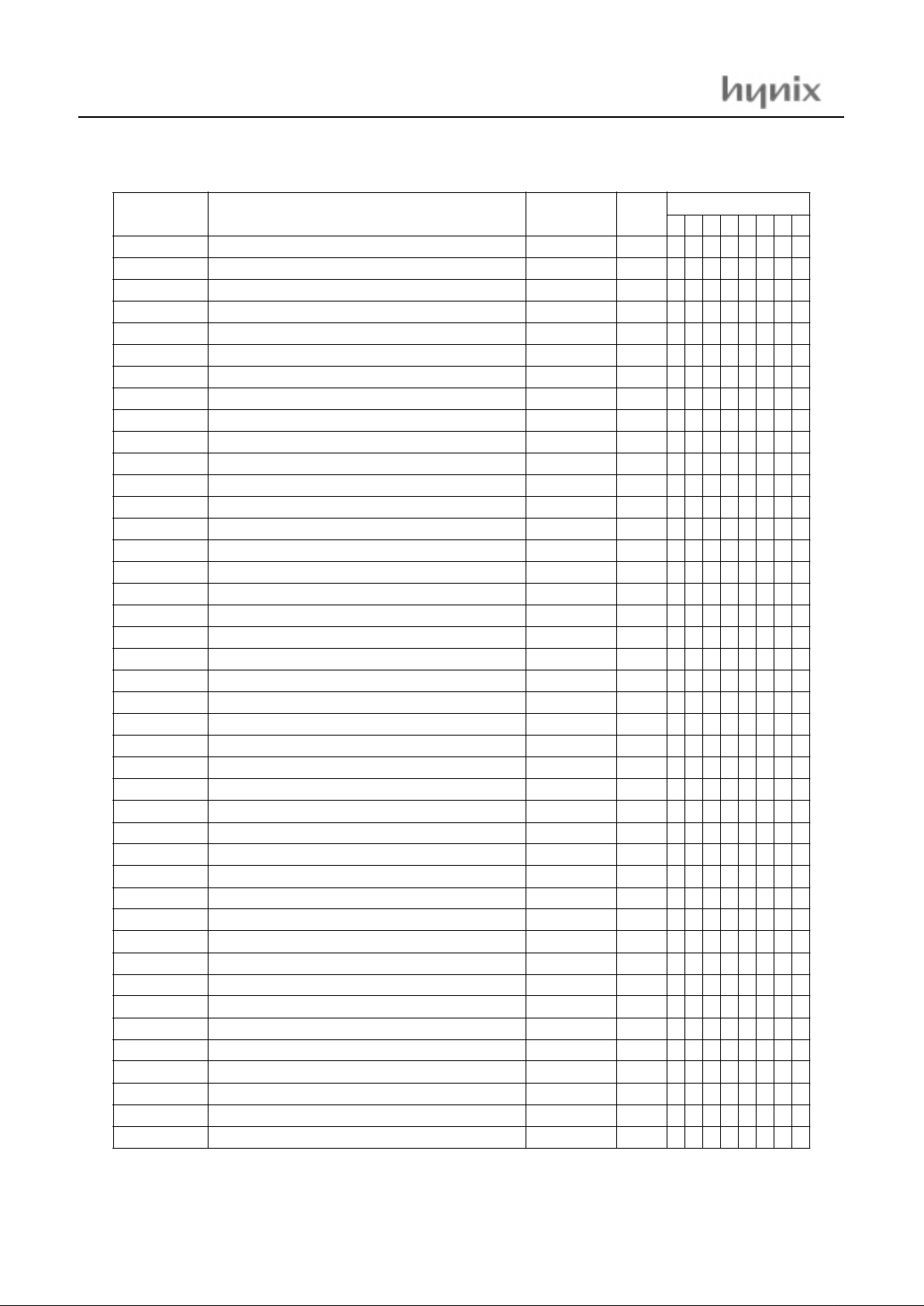

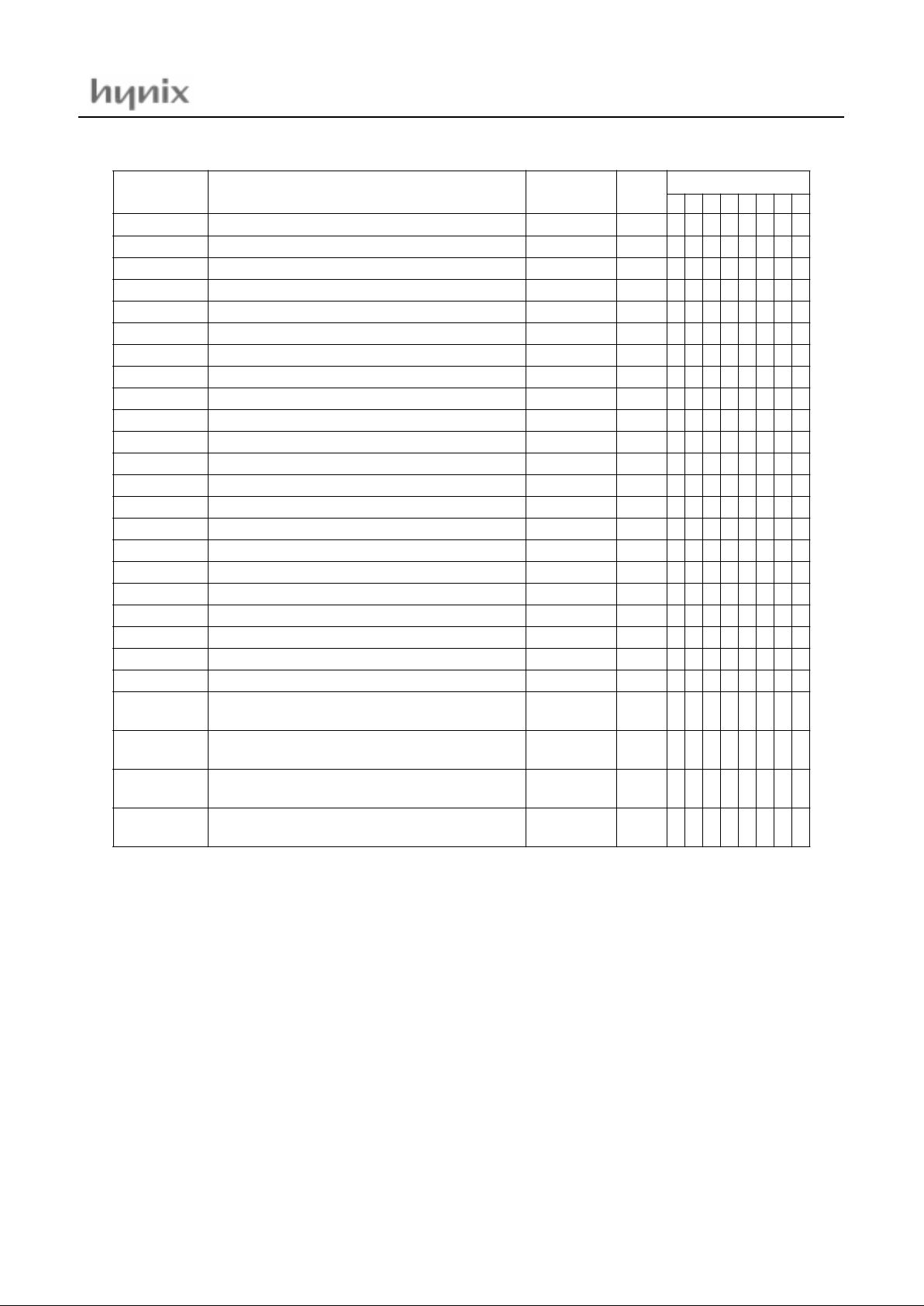

8.4 List of SFRS

Register Description Address R/W

Initial V a lu e

76543210

P0 Port0 Register 80H R/W 11111111

SP Stack Point register 81H R/W 00000111

DPL Data Pointer(Low byte) Register 82H R/W 00000000

DPH Data Pointer(High byte) Register 83H R/W 00000000

PCON Power Control Register 87H R/W xx 000000

TCON Timer/Counter Control Register 88H R/W 00000000

TMOD Timer/Counter Mode Control Register 89H R/W 00000000

TL0 Timer/Counter0 Low byte Register 8AH R/W 00000000

TL1 Timer/Counter1 Low byte Register 8BH R/W 00000000

TH0 Timer/Count er0 High byte Register 8CH R/W 00000000

TH1 Timer/Count er1 High byte Register 8DH R/W 00000000

P1 Port1 Register 90H R/W 11111111

P1SFS Port1 Special Function Selection Register 91H R/W 00000000

P2SFS Port2 Special Function Selection Register 92H R/W 00000000

P3SFS Port3 Special Function Selection Register 93H R/W 00000000

ADAT ADC Data Register 96H R/W 00000000

ACON ADC Control Register 97H R/W xx 0 x0001

P2 Port2 Register 0A0H R/W 11111111

PWMCON PWM Control Register 0A1H R/W 00000000

PWM0 PWM0 Output Register 0A2H R/W 11111111

PWM1 PWM1 Output Register 0A3H R/W 11111111

PWM2 PWM2 Output Register 0A4H R/W 11111111

PWM3 PWM3 Output Register 0A5H R/W 11111111

PWM4 PWM4 Output Register 0AAH R/W 11111111

PWM5 PWM5 Output Register 0ABH R/W 11111111

PWM6 PWM6 Output Register 0ACH R/W 11111111

PWM7 PWM7 Output Register 0ADH R/W 11111111

WDTKEY Watchdog Key Register 0AEH R/W 00000000

WDTRST Watchdog Timer Reset Register 0A6H R/W 00000000

IEA Interrupt Enable Register 0A7H R/W 0 xxxxx00

IE Interrupt Enable Register 0A8H R/W 00000000

P3 Port3 Register 0B0H R/W 11111111

DPWMCON Dynamic PWM Control Register 0B1H R/W 0xxxxx00

DPWM0 Dynamic PWM0 Output Register 0B2H R/W 11111111

DPWM1 Dynamic PWM1 Output Register 0B3H R/W 11111111

IPA Interrupt Priority Register 0B6H R/W 0xxxxx00

IP Interrupt Priority Register 0B8H R/W x0000000

T2CON Timer2 Control Register 0C8H R/W 0xxxx0xx

RC2L Reload Low Register 0CAH R/W 00000000

RC2H Reload High Register 0CBH R/W 00000000

PSW Program Status Word Register 0D0H R/W 00000000

RAMBUF RAM Buffer I/O Interface Register 0D4H R/W xxxxxxxx

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

21

DDCDAT Data Shift Register for DDC1 0D5H R/W 00000000

DDCADR DDC Address Pointer Register 0D6H R/W 00000000

DDCCON DDC Mode Status and DDC1 Control Register 0D7H R/W x 0 0 x 0000

S1CON Serial Control Register for DDC2 0D8H R/W 00000000

S1STA Serial Status Regist er for DDC2 0D9H R 0 x 0 0 xxxx

S1DAT Data Shift Register for DDC2 0DAH R/W 00000000

S1ADR0 Serial Address0 Register for DDC2 0DBH R/W 0000000x

S1ADR1 Serial Address1 Register for DDC2 0D3H R/W 0000000x

S2CON Serial Control Register 0DCH R/W 00000000

S2STA Serial Status Register 0DDH R 0x00xxxx

S2ADR Serial Address Register for I2C 0DFH R/W 0000000x

S2DAT Data Shift Register for I2C 0DEH R/W 00000000

ACC Accumulator 0E0H R/W 00000000

EXCON Extended Control Register 0E8H R/W xxxxxxx0

B B Register 0F0H R/W 00000000

MDCON Mode Indication Register 0F1H R/W 0 0 0 x x 0 0 0

MDST Mode Status Register 0F2H R x0000000

VPH Vertical scan period High byte Register 0F3H R/W 00000000

HPH Horizontal scan period High byte Register 0F4H R/W 00000000

VHPL V/H scan period High byte Register 0F5H R/W 00000000

HVGEN H/V pulse Control Register 0F9H R/W x 0 0 0 x 0 0 0

CPGEN Clamping pulse and Pattern Control register 0FAH R/W 00000x 00

VFH

Vertical free- running outp ut pulse period Hi gh byte

register

0FBH R/W 00100000

VFL

Vertical free-running output pulse period Low byte

register

0FCH R/W 00001010

HFH

Horizontal free-running output pulse per iod High

byte register

0FDH R/W 01100000

HFL

Horizontal free-running output pulse per iod Low

byte register

0FEH R/W 00x11111

Register Description Address R/W

Initial V a lu e

76543210

HMS9 xC 7132 / HMS9xC7134

22 May.2001 ver1.1

8.5 Addressing Mode

The address ing modes in HMS9xC7 132 instruct ion set are as fo llows

• Direct addressing

• Indirect addressing

• Register addressing

• Register-specific addressing

• Immediate constants addr essing

• Indexed addressing

Note that refer to “Chapter 22. Instruction Set” those addressing modes and related instructio ns.

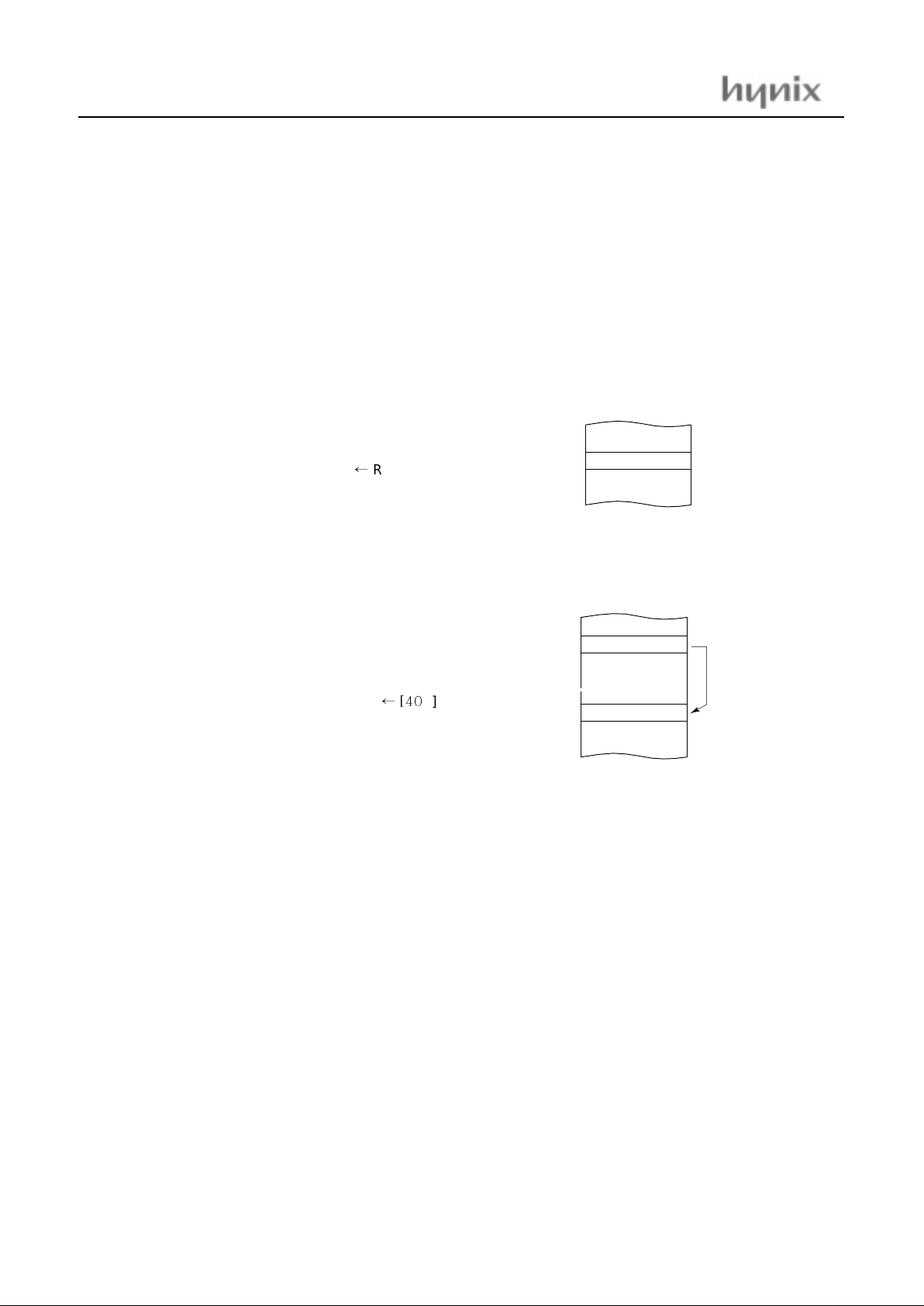

(1) Direct addressing

In a direct a ddr essi ng th e op erand is s pecif ie d by an 8-bi t a ddres s

field in the instruction. Only internal Data RAM and

SFRs(80~FFH RAM) can be directly addressed.

Example:

mov A, 3EH ; A RAM[3E]

(2) Indirect addressing

In indirect addressing the instruction specifies a register which

contains the address of the operand. Both internal and external

RAM can be indirectly addressed. The address register for 8-bit

addresses can be R0 or R1 of the selected register bank, or the

Stack Pointer. The address register for 16-bit addresses can only

be the 16-bit “data pointer” registe r, DPTR.

Example:

mov @R1, 40 H ;[R1]

H]

(3) Register addressing

The register banks, containing registers R0 through R7, can be

accessed by certain inst ructions which car ry a 3-bit register spec ificat ion with in the opco de of the ins truct ion. Inst ruct ions th at access the registers th is way are cod e efficient, since th is mode

eliminates an address byte. When t h e instr uction is execute d, one

of four banks is sel ected at e xecution t im e by the two bank select

bits in the PSW.

Example; mov PSW, #0001000B ; sele ct Bank0

mov A, #30H

mov R1, A

(4) Register-specific addressing

Some instructions are specific to a certain register. For example,

some instructions always operate on the Accumulator, or Data

Pointer, etc., so no address b yte is needed to point it . The opcode

itself does that.

→ A

04

PROG. MEMOR Y

3E

H

55

40

H

~

~

~

~

55

R1

PROG. MEMORY

HMS9xC7132 / HMS9xC7134

May.2001 ver1.1

23

(5) Immediate constants addressing

The valu e of a constant can follow the opcode in Program mem ory.

Example; mov A, #100H.

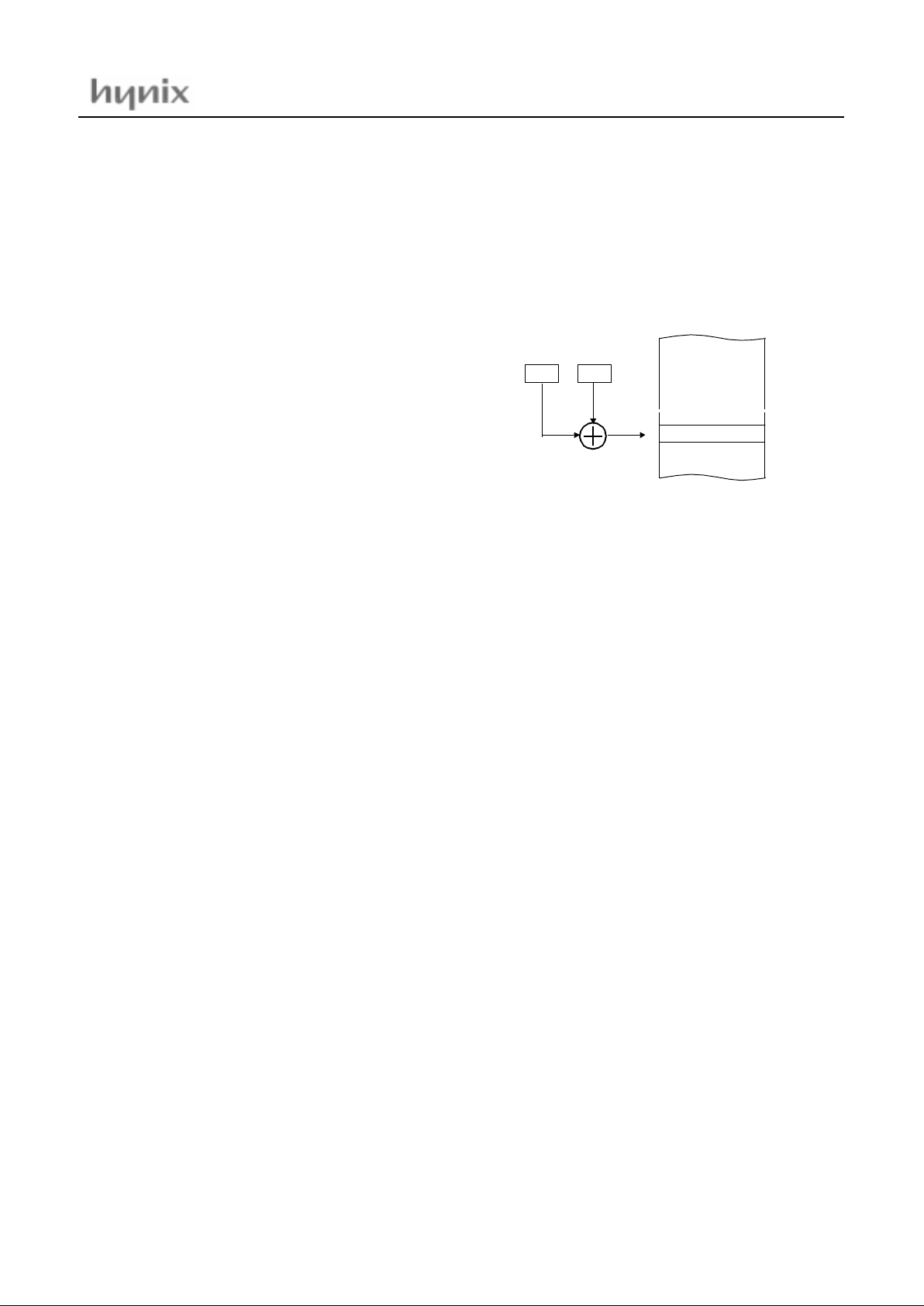

(6)Indexed addressing

Only Progra m memor y ca n be acces se d wit h indexe d add res sing,

and it can only be read. This addressing mode is intended for

reading l ook-up tab les in Progra m memory . A 16-bi t base registe r

(either DPTR or PC) points to the base of the table, and the Accumulator is set up with the table entry number. The address of

the table entry in Program memory is formed by adding the Accumu la to r data to the bas e p oi nt er.

Example; movc A, @A+DPTR

1EAD

H

~

~

~

~

ACC DPTR

3A 1E73

PROG. MEMORY

Loading...

Loading...