1

www.schematic-x.blogspot.com

2

3

4

5

6

7

8

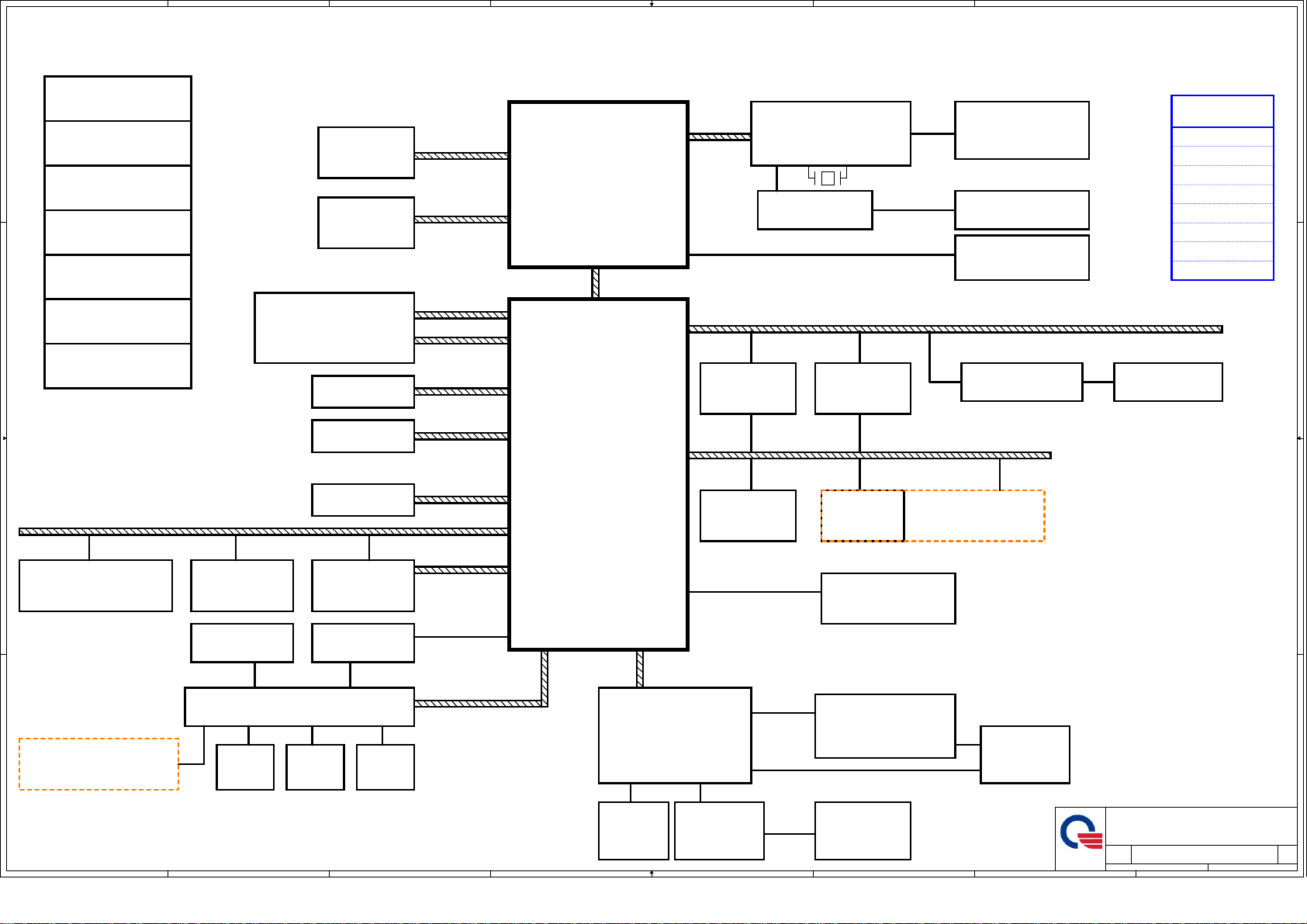

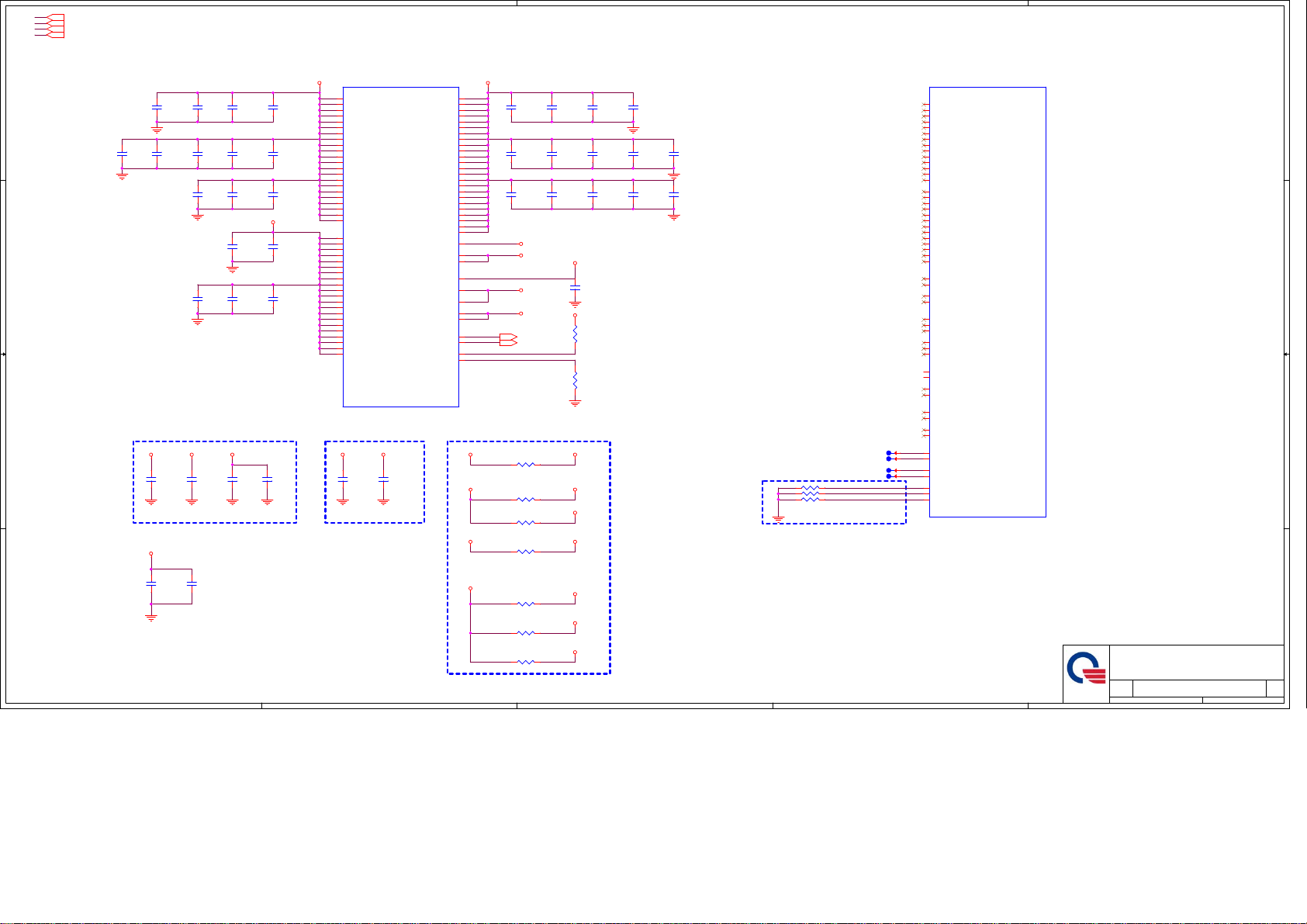

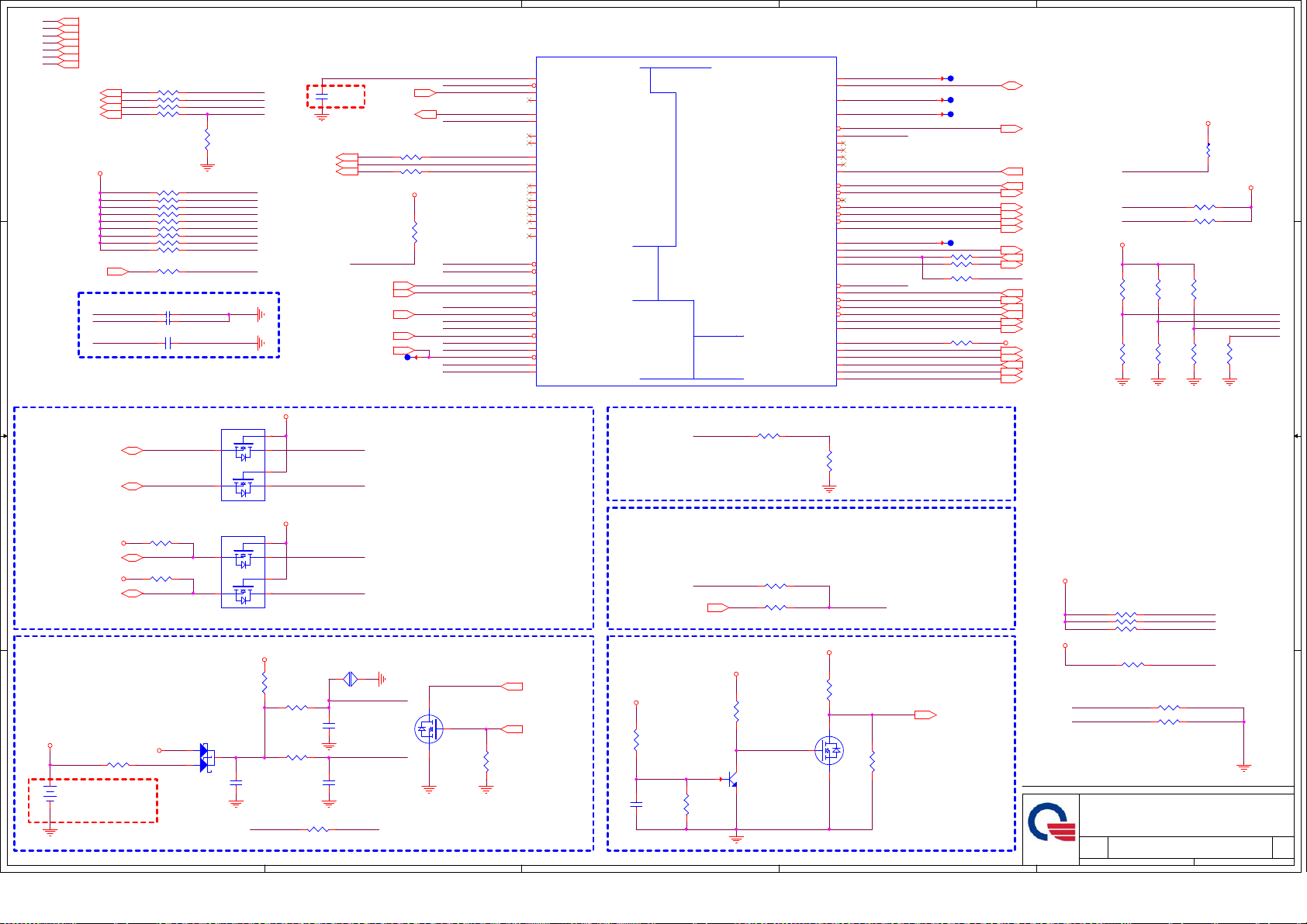

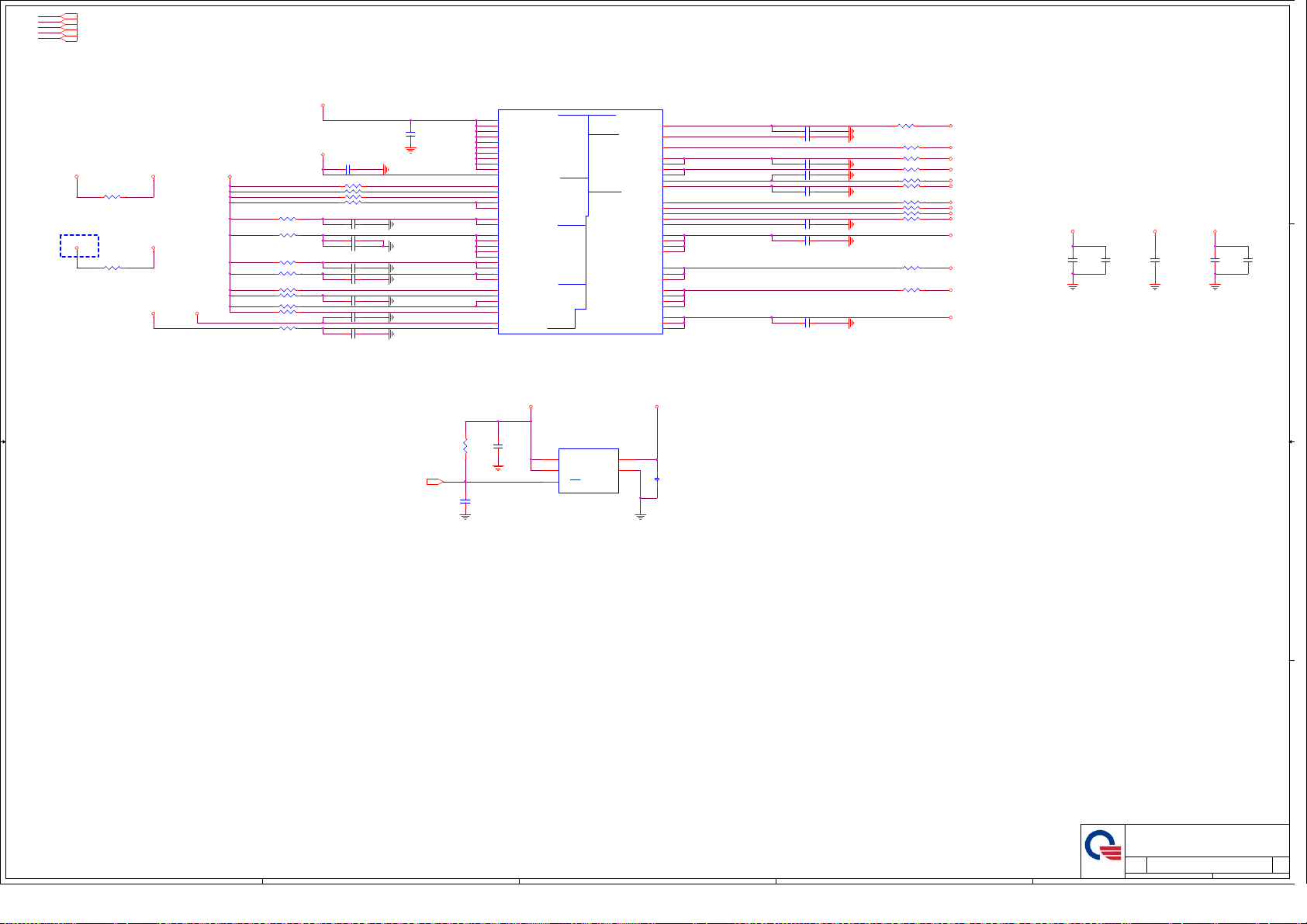

POWER PAVILION PARFAIT INTEL SKL / KABY -H SYSTEM DIAGRAM

01

LPC

FAN

PG.17

PG.18

PG.33

PG.32

PG.32

PG.32

PG.33PG.35

PG.12

PG.37

PG.38PG.38PG.38

For Layout Review

DDR4 2133MHz

Channel A

DDR4 2133MHz

Channel B

SATA 6GB/s

SATA0A

PCIEx4 4GB/s

LANE9,10,11,12

SATA 6GB/s

SATA 6GB/s

SATA 1.5GB/s

PCI-E x 1 Gen1

USB 2.0

PORT7

SPI

LPC

SATA1B

SATA2

SATA3

INTEL

Sky Lake - H4+2

Kaby Lake - H4+2

Processor : Quad Core

Power : 45 (Watt)

Package : BGA1440

Size : 42 x 28 (mm)

Die Size : 13.6 x 9.1 (mm)

PG.2~8

DMI

INTEL PCH

Lynx Point

Power : Watt

Package : FCBGA837

Size : 23 x 23 (mm)

PG.9~16

Azalia

AUDIO CODEC

ALC3258-CG

PEG

X8 Lane

DP portE

eDP (5.4Gb/s)

USB 3.0

USB 3.0 Ports

USB 2.0

(DB)

I2C

I2C0

PG.28

NVIDIA N16P-GX / N16E-GR

Package 29 x 29mm

40W

PS8409 re-driver IC

eDP

PORT1

PG.27

PG.19~23

27MHz

PAGE 21

PORT2

USB 3.0 Ports

(DB)

PG.30

PORT1

PG.30

PORT2

PORT4PORT3

HD CAMUSB 2.0 Ports

PG.30

PG.26

Touch Screen

Synaptics S7817

Headphone amplifier

HPA0022642RTJR

VRAM gDDR5 x 4pcs

256M x16 / 256M x32

2.5GHz

PORT4

PG.26

Hp

PG.29

MIC

PG.14~25

HDMI v2.0

PG.27

17" eDP Panel

HD/FHD/UHD

USB3.0 Re-Driving IC

PTN36241G

PORT5

PG.26

HD+ IR CAM

(OPTION)

PG.26 +PG.34

Combo Jack

(DB)

PG.30

STACKUP

3D CAM

Intel SR300 3D

TOP

GND

IN1

IN2

VCC

IN3

GND

BOT

PG.31PG.31

Charge

A A

PG.40

DDR4

PG.42

Config#3 SODIMM 1DPC

SODIMM1

Max. 8GB

STD

CPU Core

PG.43~45

+1.0V/+1.2VSUS

+3V/+5V S5

B B

+VGACORE

+1.35V_GFX

PG.47~48

PG.41

PG.49

PG.50

M.2 2280-S3 SSD

SODIMM2

Max. 8GB

RSV

HDD

HDD

ODD

C C

LANE7

LAN

RTL8111HSH/ Gbe

TPM 2.0 SLB9665TT2.0

D D

(OPTION)

PG.34

LANE5 LANE6

Card Reader

RTS5237S-GR

PG.36

G-Sensor

HP2DC

PG.34

SMBUS

KBC

ITE IT8987E/BX

KB TP

WLAN

BT COMBO

ROM

1

2

Dual Digital MICSpeaker

PG.28 PG.28

3

4

5

3D CAM MIC

/ INT CAM MIC

PG.26

6

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

01 -- Block Diagram

01 -- Block Diagram

01 -- Block Diagram

Date: Sheet of

Date: Sheet of

7

Date: Sheet of

1 51Monday, December 28, 2015

1 51Monday, December 28, 2015

1 51Monday, December 28, 2015

8

1A

1A

1A

5

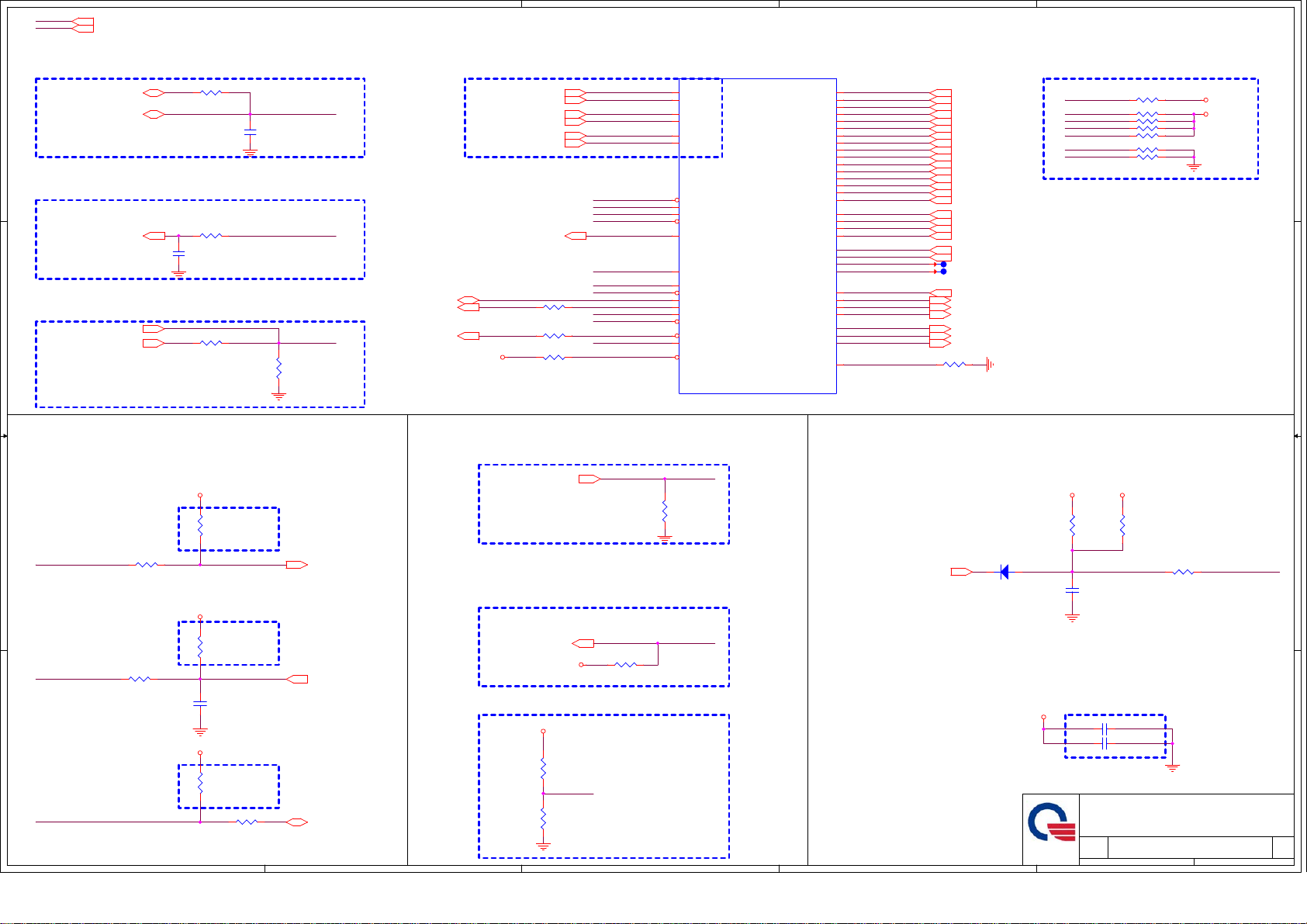

+1.0V 5,6,10,16,37,48

+VCCSTPLL 6,43,47

H_PECI (50ohm)

Trace Length: <0.5 iches

Ra,Ca need placement close to PCH.

PCH_PECI11

D D

PROCHOT# (50ohm)

Trace Length <11 inches

Cb need placment near VR

CPU_PLTRST# (50ohm)

Trace Length: 10~17 inches

C C

EC_PECI37

H_PROCHOT#37,43

CPU_PLTRST#R11

PLTRST#12,16,19,33,34,35,36,37

Ra

R213/F_4

R4 499/F_4

C3

Cb

*47P/50V_4

R11 *1.5K/F_4

EC_PECI

C2

Ca

*47P/50V_4

H_PROCHOT#_R

CPU_PLTRST#R

R13

*750/F_4

4

Host CLK:

Trace length < 11000 mils

Trace spacing = 15 / 20 mils, Impendence 85 ohm

PM_SYNC (50ohm)

Trace Length: 1~11.25 inches

PM_SYNC11

H_PM_DOWN11

SKTOCC_N_R13

+VCCSTPLL

CLK_CPU_BCLKP11

CLK_CPU_BCLKN11

CPU_PCI_BCLKP11

CPU_PCI_BCLKN11

CLK_DPLL_NSCCLKP11

CLK_DPLL_NSCCLKN11

DDR_VTT_CNTL18

R19 20_4

R16 *10K_4

R15 0_4

3

2

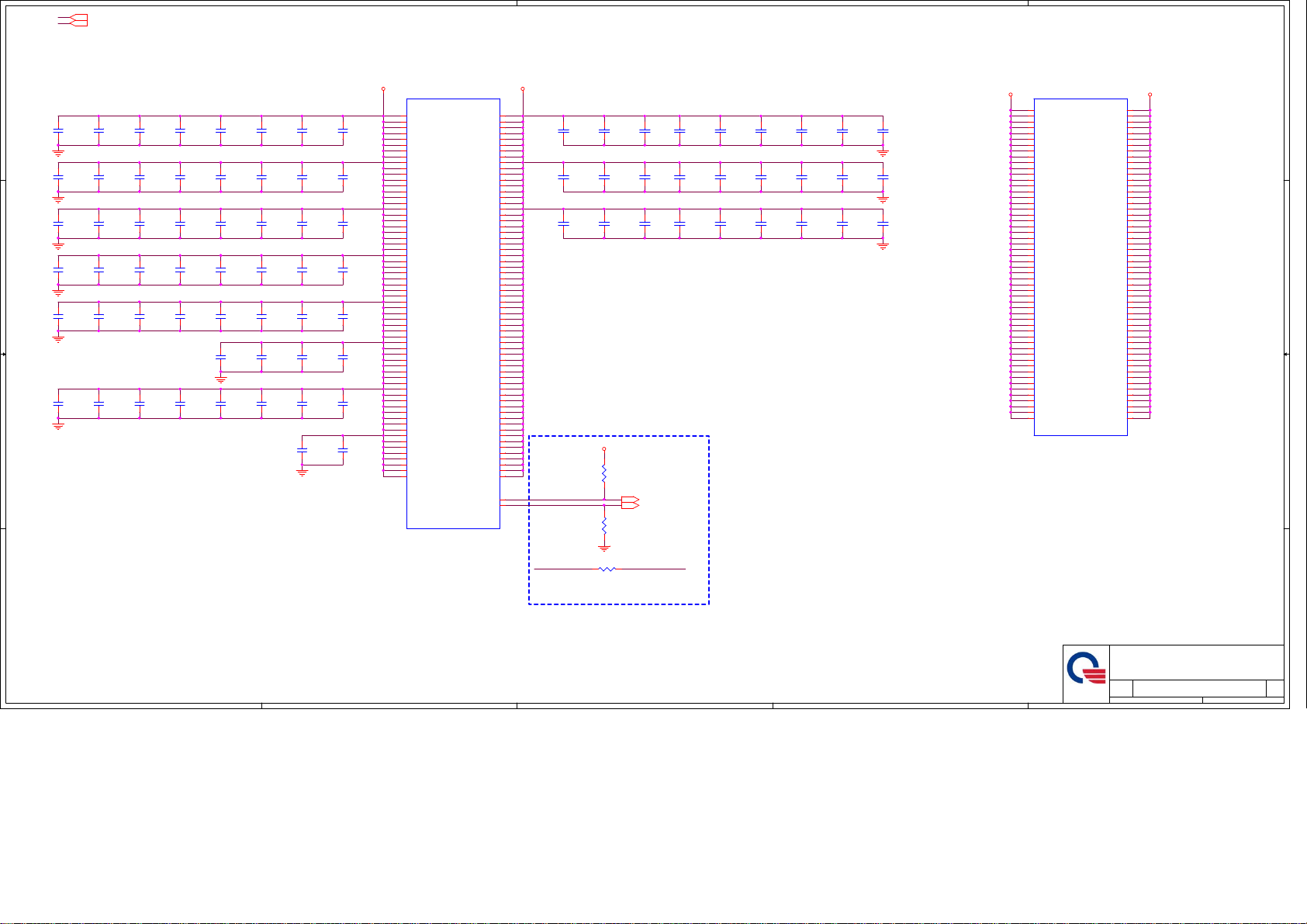

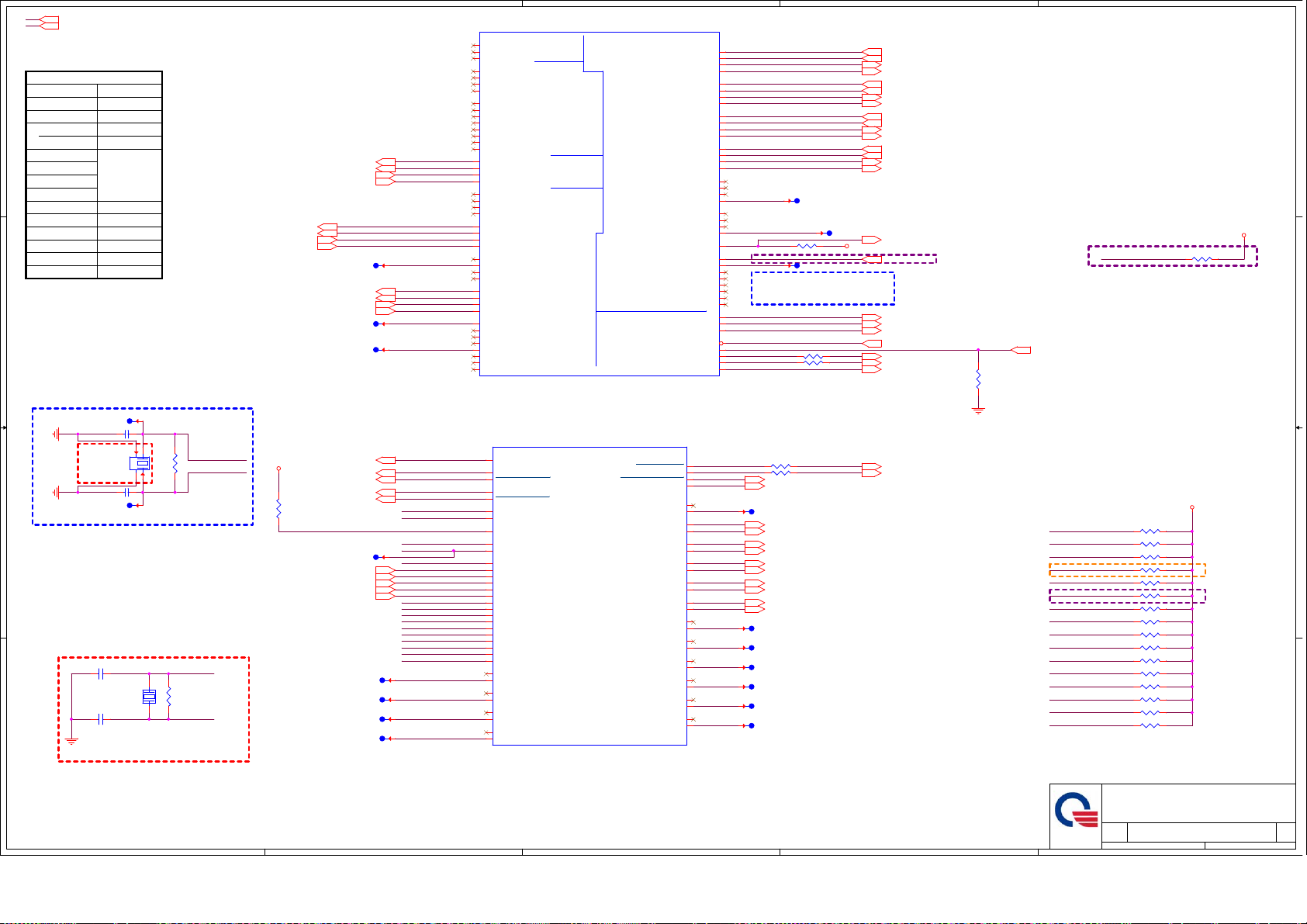

SKYLAKE Processor (CLK,MISC,JTAG)

SKYLAKE_HALO

U1E

CLK_CPU_BCLKP

CLK_CPU_BCLKN

CPU_PCI_BCLKP

CPU_PCI_BCLKN

CLK_DPLL_NSCCLKP

CLK_DPLL_NSCCLKN

H_CPU_SVIDALRT#

VR_SVID_CLK_R

H_CPU_SVIDDAT

H_PROCHOT#_R

DDR_VTT_CNTL

H_VCCST_PWRGD

PROCPWRGD

CPU_PLTRST#R

H_PM_DOWN_R

EC_PECI

PM_THRMTRIP#

SKTOCC_NSKTOCC_N_R

PROC_SEL#

CATERR#

D35

C36

D31

BH31

BH32

BH29

BR30

BT13

H13

BT31

BP35

BM34

BP31

BT34

BR33

BN1

BM30

B31

A32

E31

J31

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

*SKL_H_BGA_BGA

BGA1440

5 OF 14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

BN25

CFG0

BN27

CFG1

BN26

CFG2

BN28

CFG3

BR20

CFG4

BM20

CFG5

BT20

CFG6

BP20

CFG7

BR23

CFG8

BR22

CFG9

BT23

CFG10

BT22

CFG11

BM19

CFG12

BR19

CFG13

BP19

CFG14

BT19

CFG15

BN23

CFG16

BP23

CFG17

BP22

CFG18

BN22

CFG19

XDP_BPM0

BR27

XDP_BPM1

BT27

XDP_BPM2

BM31

XDP_BPM3

BT30

XDP_TDO_CPU

BT28

XDP_TDI_CPU

BL32

XDP_TMS_CPU

BP28

XDP_TRST#_CPU

BR28

XDP_TRST#

BP30

XDP_PREQ#

BL30

XDP_PRDY#

BP27

CFG_RCOMP

BT25

Design Note(CFG_RCOMP):

DEFENSIVE DESIGN 50-OHM FOR R40PR (SV REQ)

CFG0 16

CFG1 16

CFG2 8,16

CFG3 8,16

CFG4 8,16

CFG5 8,16

CFG6 8,16

CFG7 16

CFG8 16

CFG9 16

CFG10 8,16

CFG11 16

CFG12 8,16

CFG13 8,16

CFG14 16

CFG15 16

CFG16 16

CFG17 16

CFG18 16

CFG19 16

XDP_BPM0 16

XDP_BPM1 16

TP2

TP1

XDP_TDO_CPU 16

XDP_TDI_CPU 16

XDP_TMS_CPU 16

XDP_TRST#_CPU 16

XDP_TRST# 15,16

XDP_PREQ# 15,16

XDP_PRDY# 15,16

R1749.9/F_4

1

Processor pull-up (CPU)

H_PROCHOT#

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TDI_CPU

XDP_PREQ#

XDP_TRST#_CPU

XDP_TRST#

R3 1K_4

R5 51_4

R6 *51_4

R7 *51_4

R8 *51_4

R10 51_4

R12 51_4

02

+1.0V

+1.0V

CPU CORE SVID

Layout note:

1.Need routing together

2.ALERT need between CLK and DATA.

+VCCSTPLL

PLACE THE PU RESISTORS

CLOSE TO VR

PULL UP IS IN THE VR MODULE

B B

VR_SVID_CLK_R

CLOSE TO CPU

PLACE THE PU RESISTORS

H_CPU_SVIDALRT#

CLOSE TO CPU

PLACE THE PU RESISTORS

A A

R27 0_4

R25 220/F_4

R26

*54.9/F_4

+VCCSTPLL

+VCCSTPLL

R23

56.2/F_4

C5

*0.1U/10V_4

R28

100/F_4

Close to CPU

SVID CLK

VR_SVID_CLK 43

Close to CPU

SVID ALERT

VR_SVID_ALERT# 43

Close to CPU

SVID DATA

H_CPU_SVIDDAT

5

R29 0_4

VR_SVID_DATA 43

4

PROCPWRGD (50ohm)

Trace Length: 1~11.25 inches

PROCPWRGD10

THERMTRIP# (50ohm)

Trace Length: 1.1~12 inches

Rb need placment near PCH

PM_THRMTRIP#5,11,37

+VCCSTPLL

Rb

R14 1K_4

Ra(R10804) Not install in SKL-H

+VCCSTPLL

Ra

R18

*10K_4

PROC_SEL#

R20

*0_4

PM_THRMTRIP#

3

PROCPWRGD

R9

*10K_4

HWPG10,16,37,41,42,47,48

2

HWPD

Ra close to CPU side

H_VCCST_PWRGD trace 0.3" - 1.5"

+1.0V

+VCCSTPLL

R21

1K_4

D2 RB500V-40

21

H_VCCST_PWRGD_R H_VCCST_PWRGD

C4

*10P/50V_4

CPU VDDQ

Note: please keep plane is enough for VDDQ 2.8A

Placement close to CPU.

+1.2VSUS

C60.1U/16V_4

C7*0.1U/10V_4

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

02 -- SKL 1/7 (JTAG/MISC)

02 -- SKL 1/7 (JTAG/MISC)

02 -- SKL 1/7 (JTAG/MISC)

Date: Sheet of

Date: Sheet of

Date: Sheet of

R22

*1K_4

Ra

R24 60.4/F_4

1

1A

1A

1A

2 51Monday, December 28, 2015

2 51Monday, December 28, 2015

2 51Monday, December 28, 2015

+VCCIO 6,16,48

D D

C C

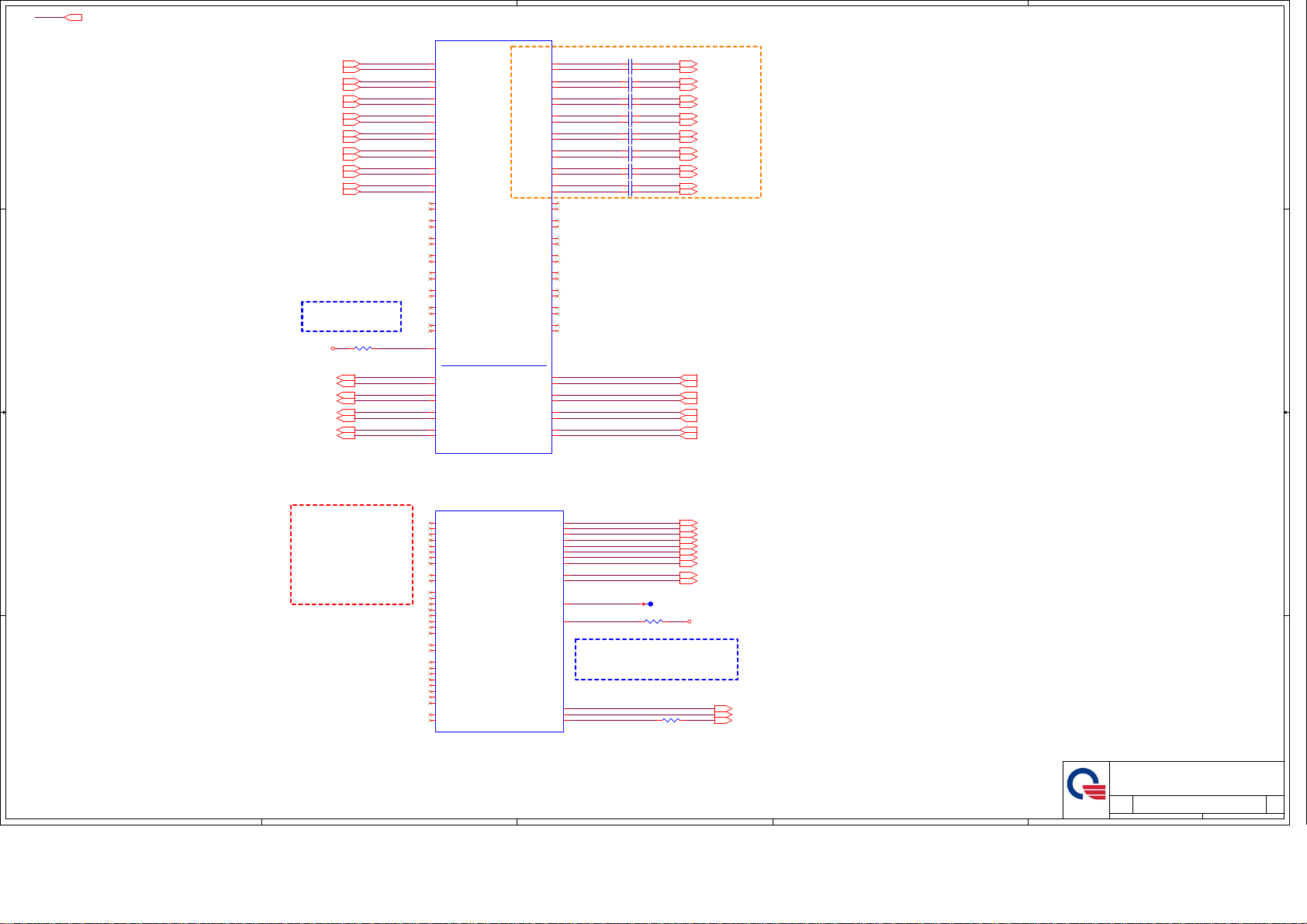

5

PEG_RXP019

PEG_RXN019

PEG_RXP119

PEG_RXN119

PEG_RXP219

PEG_RXN219

PEG_RXP319

PEG_RXN319

PEG_RXP419

PEG_RXN419

PEG_RXP519

PEG_RXN519

PEG_RXP619

PEG_RXN619

PEG_RXP719

PEG_RXN719

PEG_RCOMP

Trace length < 400 MILS

Trace width = 12 MILS

Trace spacing = 15 MILS

+VCCIO

DMI_RXP09

DMI_RXN09

DMI_RXP19

DMI DMI

DMI_RXN19

DMI_RXP29

DMI_RXN29

DMI_RXP39

DMI_RXN39

4

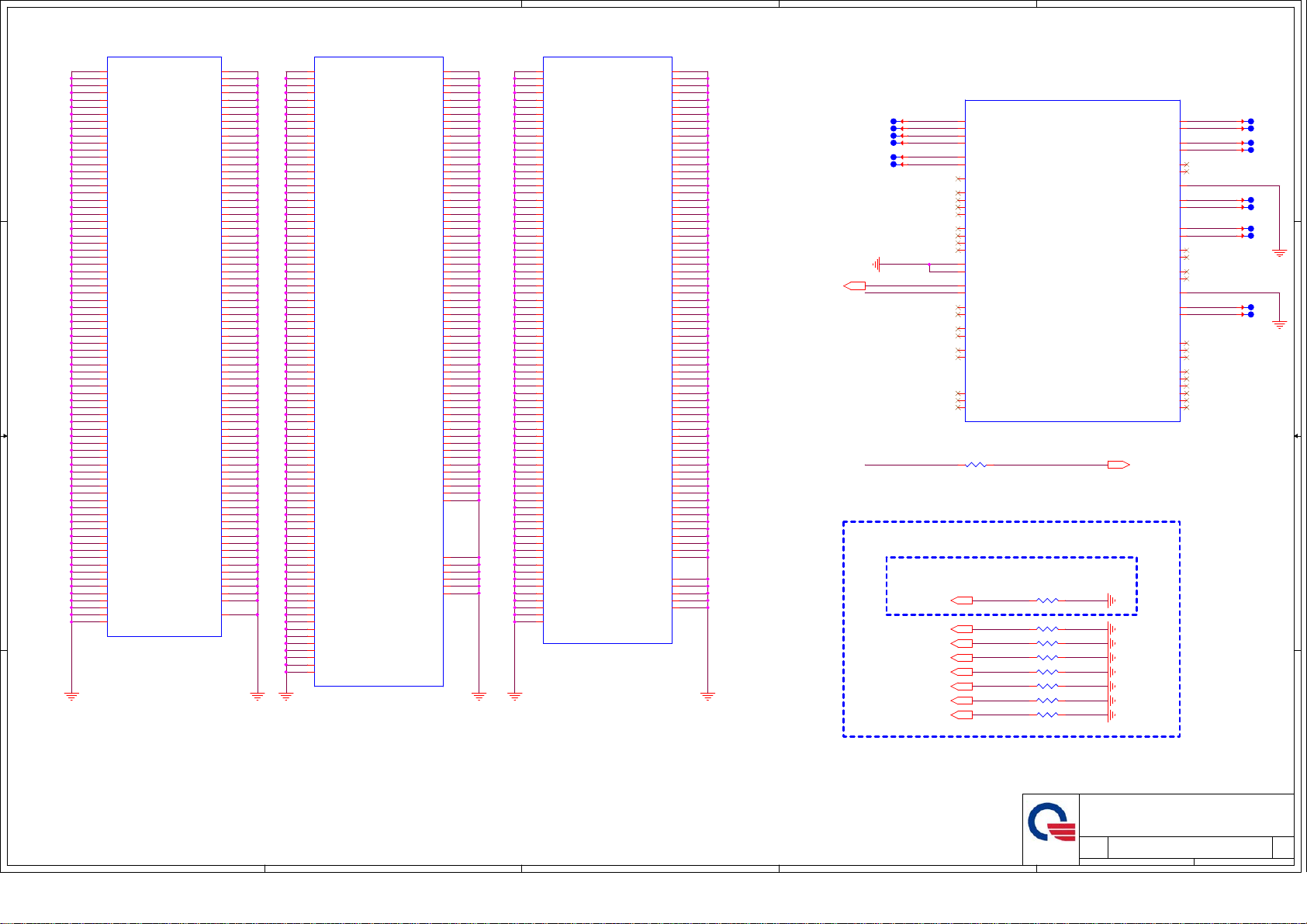

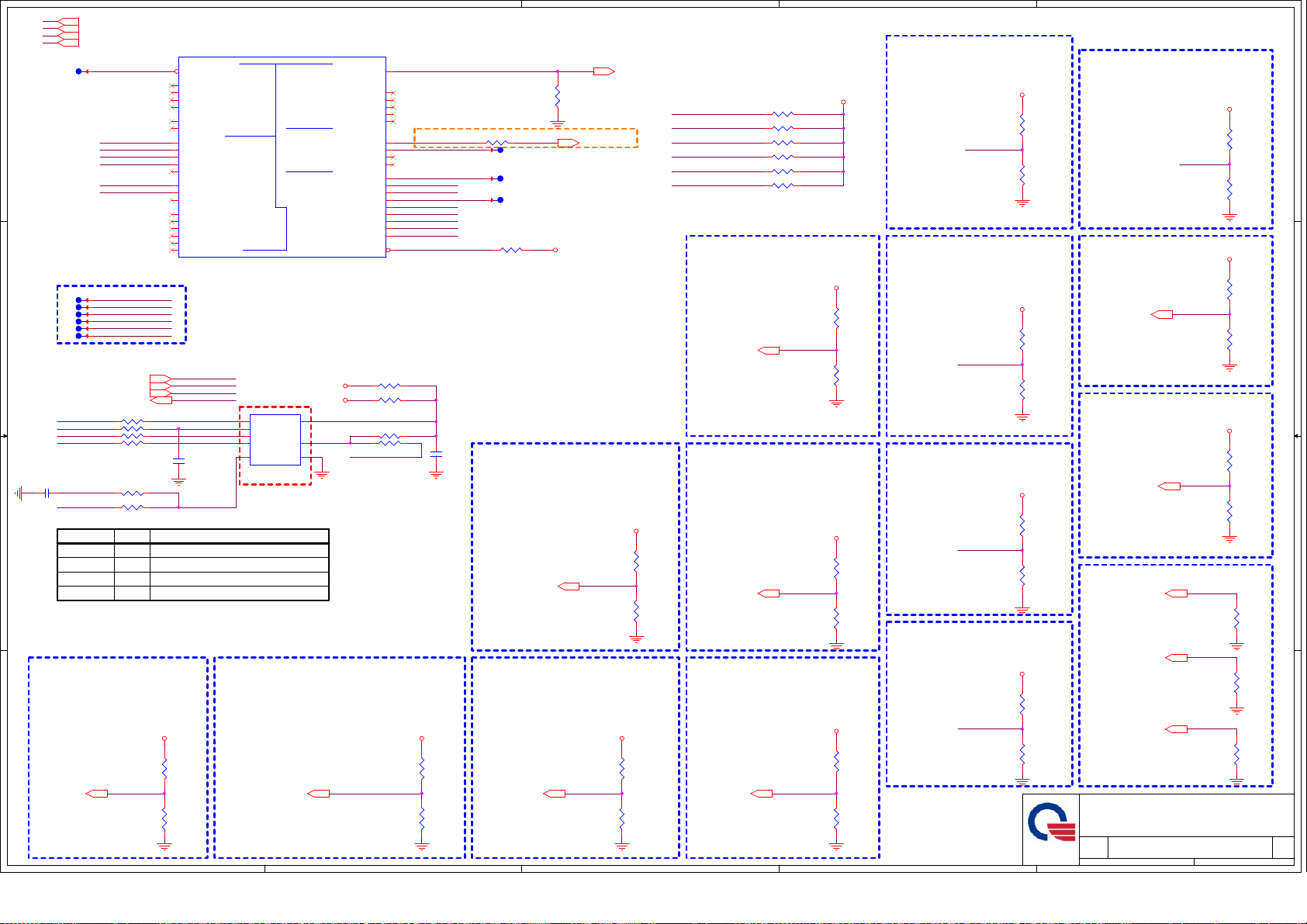

SKYLAKE Processor (DMI,PEG,FDI)

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

R30 24.9/F_4

PEG_COMP

U1C

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

G2

PEG_RCOMP

D8

DMI_RXP[0]

E8

DMI_RXN[0]

E6

DMI_RXP[1]

F6

DMI_RXN[1]

D5

DMI_RXP[2]

E5

DMI_RXN[2]

J8

DMI_RXP[3]

J9

DMI_RXN[3]

*SKL_H_BGA_BGA

SKYLAKE_HALO

BGA1440

3 OF 14

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

PEG_TXP0_C

PEG_TXN0_C

PEG_TXP1_C

PEG_TXN1_C

PEG_TXP2_C

PEG_TXN2_C

PEG_TXP3_C

PEG_TXN3_C

PEG_TXP4_C

PEG_TXN4_C

PEG_TXP5_C

PEG_TXN5_C

PEG_TXP6_C

PEG_TXN6_C

PEG_TXP7_C

PEG_TXN7_C

3

C80.22U/10V_4

C90.22U/10V_4

C10 0.22U/10V_4

C11 0.22U/10V_4

C12 0.22U/10V_4

C13 0.22U/10V_4

C14 0.22U/10V_4

C15 0.22U/10V_4

C16 0.22U/10V_4

C17 0.22U/10V_4

C18 0.22U/10V_4

C19 0.22U/10V_4

C20 0.22U/10V_4

C21 0.22U/10V_4

C22 0.22U/10V_4

C23 0.22U/10V_4

PEG_TXP0 19

PEG_TXN0 19

PEG_TXP1 19

PEG_TXN1 19

PEG_TXP2 19

PEG_TXN2 19

PEG_TXP3 19

PEG_TXN3 19

PEG_TXP4 19

PEG_TXN4 19

PEG_TXP5 19

PEG_TXN5 19

PEG_TXP6 19

PEG_TXN6 19

PEG_TXP7 19

PEG_TXN7 19

DMI_TXP0 9

DMI_TXN0 9

DMI_TXP1 9

DMI_TXN1 9

DMI_TXP2 9

DMI_TXN2 9

DMI_TXP3 9

DMI_TXN3 9

BOM:

DIS : Stuff

UMA: Un-Stuff

dGPUdGPU

2

1

03

SKYLAKE_HALO

U1D

*SKL_H_BGA_BGA

BGA1440

4 OF 14

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

INT_EDP_TXP0

D29

INT_EDP_TXN0

E29

INT_EDP_TXP1

F28

INT_EDP_TXN1

E28

INT_EDP_TXN2

B29

INT_EDP_TXP2

A29

INT_EDP_TXN3

B28

INT_EDP_TXP3

C28

INT_eDP_AUXP

C26

INT_eDP_AUXN

B26

EDP_DISP_UTIL

A33

EDP_RCOMP

D37

DP & PEG Compensation

y

eDP_RCOMP

Trace length < 100 Mils

Trace Width 20 Mils Tr ace Spacing 25 Mils

AUD_AZACPU_SCLK

G27

AUD_AZACPU_SDO_R

G25

AUD_AZACPU_SDI_R

G29

TP3

R31 24.9/F_4

R32 20_4

3

INT_EDP_TXP0 26

INT_EDP_TXN0 26

INT_EDP_TXP1 26

INT_EDP_TXN1 26

INT_EDP_TXN2 26

INT_EDP_TXP2 26

INT_EDP_TXN3 26

INT_EDP_TXP3 26

INT_eDP_AUXP 26

INT_eDP_AUXN 26

+VCCIO

eDP

AUD_AZACPU_SCLK 10

AUD_AZACPU_SDO_R 10

AUD_AZACPU_SDI 10

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

03 -- SKL 2/7 (DMI/EDP/PEG)

03 -- SKL 2/7 (DMI/EDP/PEG)

03 -- SKL 2/7 (DMI/EDP/PEG)

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

3 51Monday, December 28, 2 015

3 51Monday, December 28, 2 015

3 51Monday, December 28, 2 015

1A

1A

1A

B B

11/05 change HDMI from APU to GPU

A A

5

K36

DDI1_TXP[0]

K37

DDI1_TXN[0]

J35

DDI1_TXP[1]

J34

DDI1_TXN[1]

H37

DDI1_TXP[2]

H36

DDI1_TXN[2]

J37

DDI1_TXP[3]

J38

DDI1_TXN[3]

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP[0]

H33

DDI2_TXN[0]

F37

DDI2_TXP[1]

G38

DDI2_TXN[1]

F34

DDI2_TXP[2]

F35

DDI2_TXN[2]

E37

DDI2_TXP[3]

E36

DDI2_TXN[3]

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP[0]

D34

DDI3_TXN[0]

B36

DDI3_TXP[1]

B34

DDI3_TXN[1]

F33

DDI3_TXP[2]

E33

DDI3_TXN[2]

C33

DDI3_TXP[3]

B33

DDI3_TXN[3]

A27

DDI3_AUXP

B27

DDI3_AUXN

4

5

4

3

2

1

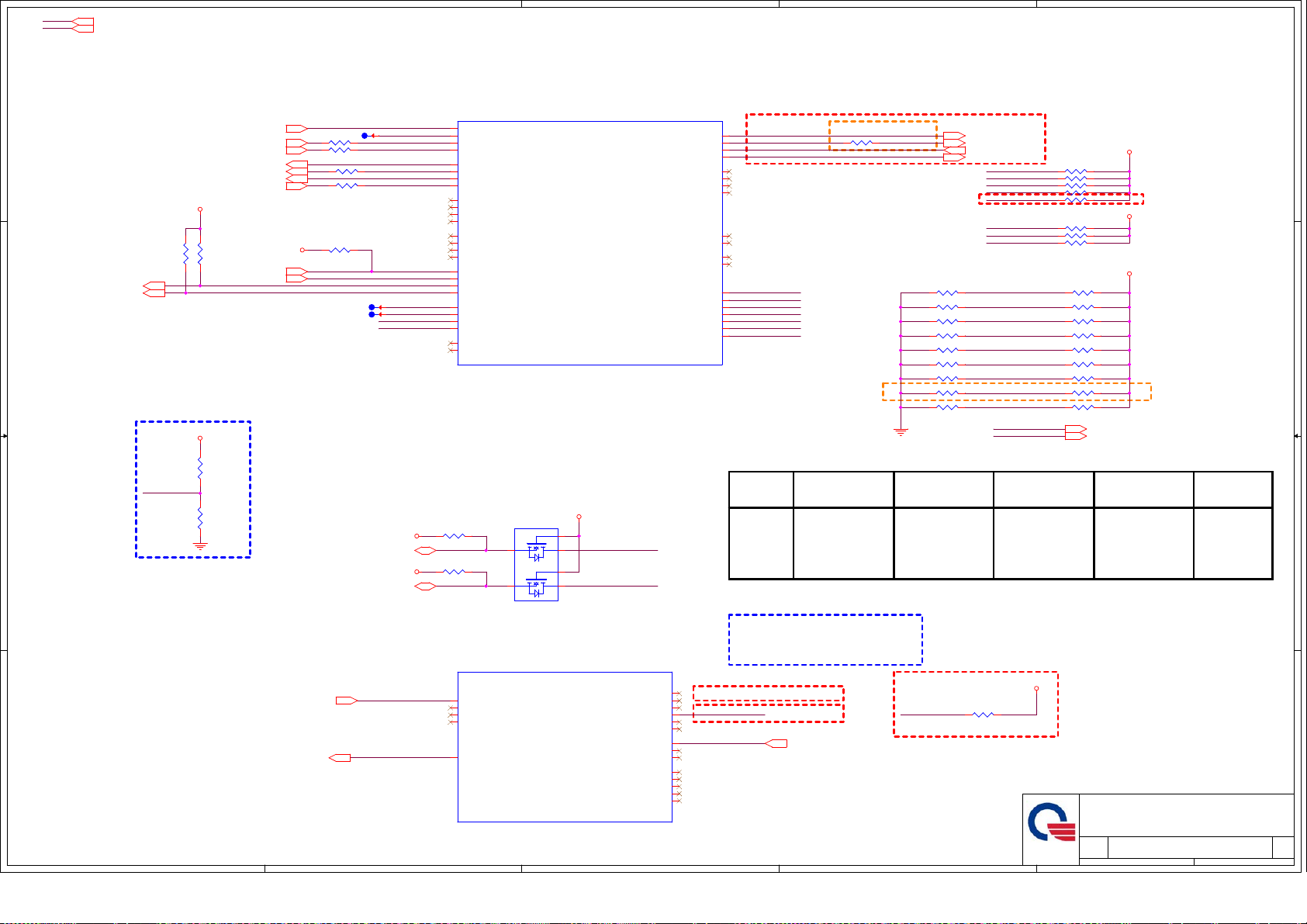

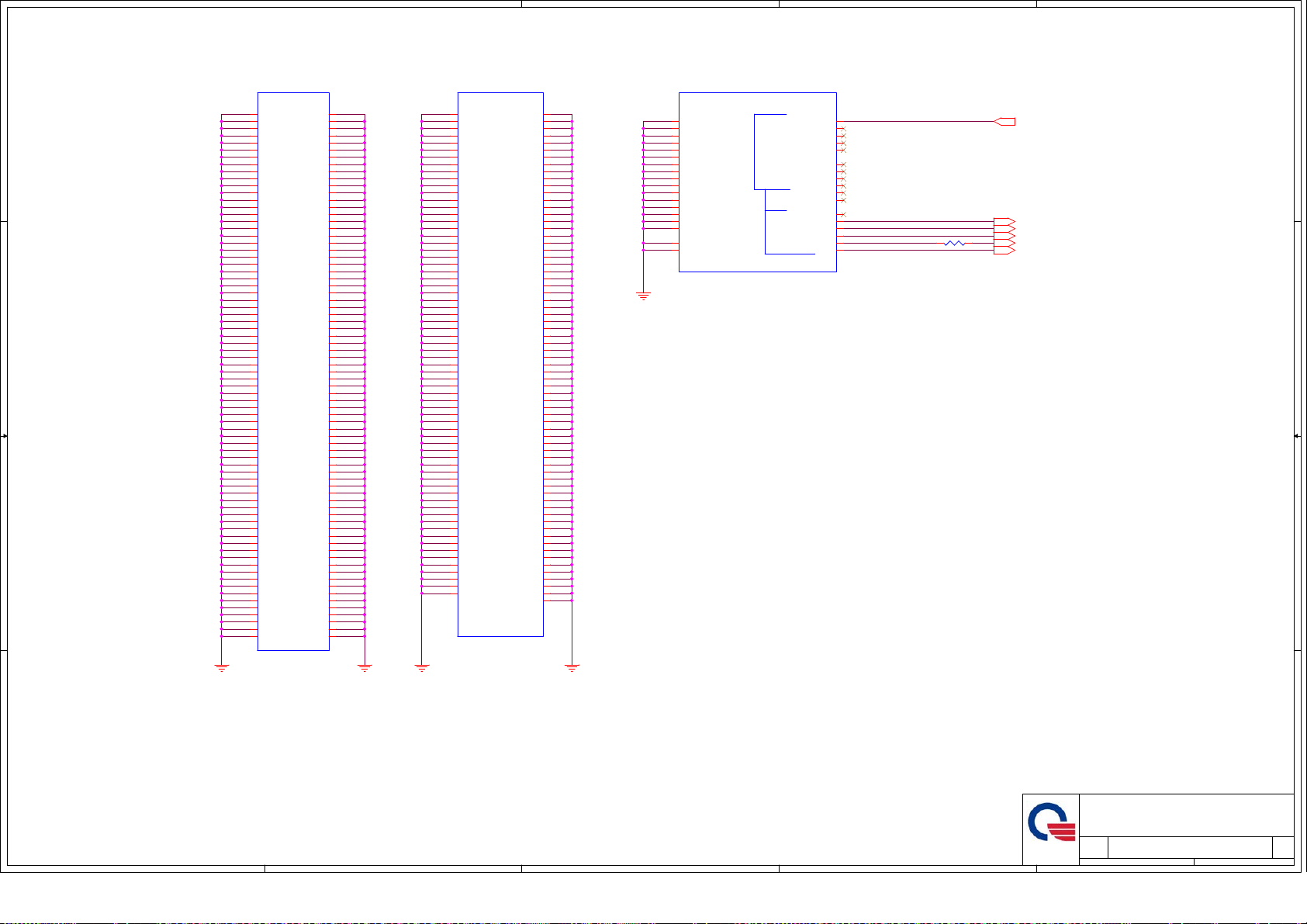

SKYLAKE Processor (DDR4)

D D

C C

B B

M_A_DQ[63:0]17

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

U1A

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

DDR CHANNEL A

*SKL_H_BGA_BGA

SKYLAKE_HALO

BGA1440

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

1 OF 14

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKP[1]

DDR0_CKN[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

AG1

AG2

AK2

AK1

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AA3

U3

P3

L3

BP5

BK3

BF3

BC3

AB3

V3

R3

M3

AY3

BA3

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_B_DQ[63:0]18

M_A_CLKP0 17

M_A_CLKN0 17

M_A_CLKP1 17

M_A_CLKN1 17

M_A_CKE0 17

M_A_CKE1 17

M_A_CS#0 17

M_A_CS#1 17

M_A_DIM0_ODT0 17

M_A_DIM0_ODT1 17

M_A_BS#0 17

M_A_BS#1 17

M_A_BG#0 17

M_A_RAS# 17

M_A_WE# 17

M_A_CAS# 17

M_A_A[13:0] 17

M_A_BG#1 17

M_A_ACT# 17

M_A_PARITY 17

M_A_ALERT# 17

M_A_DQSN[7:0] 17

M_A_DQSP[7:0] 17

R33 121/F_4

R34 75/F_4

R35 100/F_4

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

U1B

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

*SKL_H_BGA_BGA

DDR CHANNEL B

SKYLAKE_HALO

BGA1440

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKP[1]

DDR1_CKN[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM9

AN9

AM7

AM8

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

M_B_A0

AJ9

M_B_A1

AK6

M_B_A2

AK5

M_B_A3

AL5

M_B_A4

AL6

M_B_A5

AM6

M_B_A6

AN7

M_B_A7

AN10

M_B_A8

AN8

M_B_A9

AR11

M_B_A10

AH7

M_B_A11

AN11

M_B_A12

AR10

M_B_A13

AF9

AR7

AT9

AJ7

AR8

M_B_DQSN0

BP9

M_B_DQSN1

BL9

M_B_DQSN2

BG9

M_B_DQSN3

BC9

M_B_DQSN4

AC9

M_B_DQSN5

W9

M_B_DQSN6

R9

M_B_DQSN7

M9

M_B_DQSP0

BR9

M_B_DQSP1

BJ9

M_B_DQSP2

BF9

M_B_DQSP3

BB9

M_B_DQSP4

AA9

M_B_DQSP5

V9

M_B_DQSP6

P9

M_B_DQSP7

L9

AW9

AY9

+SM_VREF

BN13

BP13

SMDDR_VREF_DQ1_M3

BR13

M_B_CLKP0 18

M_B_CLKN0 18

M_B_CLKP1 18

M_B_CLKN1 18

M_B_CKE0 18

M_B_CKE1 18

M_B_CS#0 18

M_B_CS#1 18

M_B_DIM0_ODT0 18

M_B_DIM0_ODT1 18

M_B_RAS# 18

M_B_WE# 18

M_B_CAS# 18

M_B_BS#0 18

M_B_BS#1 18

M_B_BG#0 18

M_B_A[13:0] 18

M_B_BG#1 18

M_B_ACT# 18

M_B_PARITY 18

M_B_ALERT# 18

M_B_DQSN[7:0] 18

M_B_DQSP[7:0] 18

SM_VREF 17

TP8503

SMDDR_VREF_DQ1_M3 18

04

A A

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

04 -- SKL 3/7 (DDR4 I/F)

04 -- SKL 3/7 (DDR4 I/F)

04 -- SKL 3/7 (DDR4 I/F)

1

4 51Monday, December 28, 2015

4 51Monday, December 28, 2015

4 51Monday, December 28, 2015

1A

1A

1A

5

+3VPCU 10,30,33,37,38,40,41

+3V 9,10,11,12,13,14,16,17,18,19,22,26,27,28,29,30,32,33,34,35,36,37,38,43,46,49

+1.0V 2,6,10,16,37,48

+VCCGT 7,43,45

4

SKYLAKE Processor (POWER)

3

2

1

05

Follow SKL H EDS page 133 to 45W(GT2): +VCCGT=55A

1123 Change C27, C29, C33 PN and FP from 0805 to 0603

1022 Change C27, C29, C33 PN and FP from 0603 to 0805

D D

C24

22U/6.3V_6

C27

22U/6.3V_6

C38

22U/6.3VS_6

C48

C C

B B

22U/6.3VS_6

C55

10U/6.3V_6

C64

1U/6.3V_4

C71

1U/6.3V_4

C78

1U/6.3V_4

C30

22U/6.3V_6

C34

22U/6.3V_6

C39

22U/6.3VS_6

C49

22U/6.3VS_6

C56

10U/6.3V_6

C65

1U/6.3V_4

C72

1U/6.3V_4

C79

1U/6.3V_4

C31

22U/6.3V_6

C35

22U/6.3V_6

C40

22U/6.3VS_6

C50

22U/6.3VS_6

C57

10U/6.3V_6

C66

1U/6.3V_4

C73

1U/6.3V_4

C80

1U/6.3V_4

C25

22U/6.3V_6

C36

22U/6.3V_6

C41

22U/6.3VS_6

C51

22U/6.3VS_6

C58

10U/6.3V_6

C67

1U/6.3V_4

C74

1U/6.3V_4

C81

1U/6.3V_4

C32

22U/6.3V_6

C28

22U/6.3V_6

C42

22U/6.3VS_6

C52

22U/6.3VS_6

C59

10U/6.3V_6

C68

1U/6.3V_4

C75

1U/6.3V_4

C82

1U/6.3V_4

C26

22U/6.3V_6

C29

22U/6.3V_6

C43

22U/6.3VS_6

C53

22U/6.3VS_6

C60

10U/6.3V_6

C62

47U/6.3V_8

C69

1U/6.3V_4

C76

1U/6.3V_4

C83

1U/6.3V_4

+VCCGT

C33

22U/6.3V_6

C37

22U/6.3V_6

C44

22U/6.3VS_6

C54

22U/6.3VS_6

C61

10U/6.3V_6

C63

47U/6.3V_8

C70

1U/6.3V_4

C77

1U/6.3V_4

C84

1U/6.3V_4

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

SKYLAKE_HALO

U1N

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

*SKL_H_BGA_BGA

BGA1440

14 OF 14

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGT_SENSE

VSSGTX_SENSE

VSSGT_SENSE

VCCGTX_SENSE

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

AH38

AH35

AH37

AH36

VCCGT_SENSE 43

VSSGT_SENSE 43

IO Thrm Protect

Location need thermal confirm

+3VPCU +3VPCU

R36

20K/F_4

For 75 degree, 1.2v limit, (HW)

THRM_MOINTOR2 37 THRM_MOINTOR1 37

R39

100K_4 NTC

C45

0.1U/16V_4

1 2

CPU Thermal Sensor

Location need thermal confirm

MBCLK210,18,37

MBDATA210,18,37

+3V

+1.0V

PM_THRMTRIP#2,11,37

MBCLK2

MBDATA2

CPU_THRMTRIP#

R42 *10K/F_4

R43 *4.7K_4

1 3

*METR3904-G

For PIPE USEFor CPU USE

R38

20K/F_4

For 75 degree, 1.2v limit, (HW)

R41

100K_4 NTC

U4

8

7

6

4

2

Q3

SCLK

SDA

ALERT#

OVERT#

*G781P8

CPU_THRMTRIP#

VCC

DXP

DXN

GND

C47

0.1U/16V_4

1 2

C1*0.01U/50V_4

1

2

3

5

CPU_THERMDA

C85

*2200P/50V_4

CPU_THERMDC

AL000431014

+3V

2

Q2

*METR3904-G

1 3

TMP431ADGKR(98h)

A A

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

05 -- SKL 4/7 (POWER)

05 -- SKL 4/7 (POWER)

05 -- SKL 4/7 (POWER)

1

5 51Monday, December 28, 2015

5 51Monday, December 28, 2015

5 51Monday, December 28, 2015

1A

1A

1A

+1.2VSUS 2,10,17,18,42,46,48,51

+VCCIO 3,16,48

+VCCSTPLL 2,43,47

+VCCSA 43,45

5

4

3

2

1

06

Follow SKL H EDS page 135 to 45W(GT2): VCCSA=11.1A

D D

Follow SKL H EDS P136 to 45W: VCCIO

+VCCIO = 0.95V

C C

B B

C93

C86

10U/6.3V_6

C91

10U/6.3V_6

C100

1U/6.3V_4

C114

1U/6.3V_4

C119

1U/6.3V_4

C94

22U/6.3VS_6

C92

10U/6.3V_6

C101

1U/6.3V_4

C112

22U/6.3VS_6

C115

1U/6.3V_4

C120

1U/6.3V_4

10U/6.3V_6

C90

C106

10U/6.3V_6

10U/6.3V_6

+VDDQC +VCCSTG +VCCPLL_OC +VCCPLL+VCCIO

C118

10U/6.3V_6

+VCCIO

+VCCIO

C87

22U/6.3VS_6

C107

10U/6.3V_6

C110

1U/6.3V_4

C113

22U/6.3VS_6

C116

10U/6.3V_6

C121

1U/6.3V_4

+VCCSA

AG12

Close CPUUnder CPU

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

M35

M36

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

SKYLAKE_HALO

U1I

BGA1440

VCCSA

11.1 A 2.8 A

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

5.5 A

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

*SKL_H_BGA_BGA

C122

1U/6.3V_4

0.26 A

9 OF 14

C123

1U/6.3V_4

0.12 A

0.145 A

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCPLL_OC

VCCPLL_OC

Follow SKL H EDS page 135 45W: VDDQ=2.8A

+1.2VSUS

AA6

VDDQ

AE12

VDDQ

AF5

VDDQ

AF6

VDDQ

AG5

VDDQ

AG9

VDDQ

AJ12

VDDQ

AL11

VDDQ

AP6

VDDQ

AP7

VDDQ

AR12

VDDQ

AR6

VDDQ

AT12

VDDQ

AW6

VDDQ

AY6

VDDQ

J5

VDDQ

J6

VDDQ

K12

VDDQ

K6

VDDQ

L12

VDDQ

L6

VDDQ

R6

VDDQ

T6

VDDQ

W6

VDDQ

Y12

VDDQC

BH13

G11

H30

VCCST

H29

VCCSTG

G30

VCCSTG

H28

VCCPLL

J28

VCCPLL

M38

M37

H14

J14

+VCCPLL_OC +1.2VSUS

+VCCPLL +VCCSTPLL

C95

22U/6.3VS_6

C108

10U/6.3V_6

C102

10U/6.3V_6

+VDDQC

+VCCPLL_OC

+VCCSTG

+VCCPLL

VCCSA_SENSE 43

VSSSA_SENSE 43

VCCIO_VCCSENSE

VSSIO_VSSSENSE

R44 0_6

R45 *0_6

R47 0_6

R48 0_6

C88

22U/6.3VS_6

C109

10U/6.3V_6

C103

10U/6.3V_6

+VCCSTPLL

+VCCIO

+1.2VSUS+VDDQC

+1.2V_VCCPLL_OC

C117

1U/6.3V_4

R46

100_4

R49

100_4

C96

22U/6.3VS_6

C97

10U/6.3V_6

C104

10U/6.3V_6

C89

22U/6.3VS_6

C98

10U/6.3V_6

C105

10U/6.3V_6

C99

10U/6.3V_6

C111

10U/6.3V_6

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

BL15

BM16

BL22

BM22

BP15

BR15

BT15

BP16

BR16

BT16

BN15

BM15

BP17

BN16

BM14

BL14

BJ35

BJ36

AT13

AW13

AU13

AY13

BT29

BR25

BP25

R53 *49 .9/F_4

R54 *49 .9/F_4

R55 *49 .9/F_4

TP76

TP77

TP6

TP7

CPU_OPC_COMP

CPU_OPCE_COMP

CPU_OPCE_COMP2

Unconnected for Processors without OPC.

SKYLAKE_HALO

U1J

BGA1440

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCOPC_SENSE

VSSOPC_SENSE

RSVD

RSVD

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO_SENSE

VSSEOPIO_SENSE

RSVD

RSVD

VCC_OPC_1P8

VCC_OPC_1P8

RSVD

RSVD

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

10 OF 14

*SKL_H_BGA_BGA

C125

C124

*22U/6.3V_6

*1U/6.3V_4

A A

5

4

+VCCSTG

R50 0_4

R51 *0_4

R52 *0_4

+VCCSTPLL

+1.0V

+VCCIO

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Docu ment Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

06 -- SKL 5/7 (POWER&GND )

06 -- SKL 5/7 (POWER&GND )

06 -- SKL 5/7 (POWER&GND )

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

6 51Monday, December 28, 2 015

6 51Monday, December 28, 2 015

6 51Monday, December 28, 2 015

1A

1A

1A

+VCC_CORE 44

+VCCGT 5,43,45

5

4

3

2

1

07

+VCC_CORE

U1G

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

SKYLAKE_HALO

BGA1440

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

*SKL_H_BGA_BGA

7 OF 14

D D

C C

B B

Follow SKL H EDS page 131 to 45W(GT2): VCC_CORE=68A

C127

22U/6.3V_6

C140

22U/6.3V_6

C161

22U/6.3V_6

C178

22U/6.3V_6

C186

10U/6.3V_6

C198

1U/6.3V_4

C128

22U/6.3V_6

C159

22U/6.3V_6

C162

22U/6.3V_6

C179

22U/6.3V_6

C187

10U/6.3V_6

C199

1U/6.3V_4

C129

22U/6.3V_6

C141

22U/6.3V_6

C163

22U/6.3V_6

C180

22U/6.3V_6

C188

10U/6.3V_6

C200

1U/6.3V_4

C126

22U/6.3V_6

C139

22U/6.3V_6

C160

22U/6.3V_6

C177

22U/6.3V_6

C185

10U/6.3V_6

C197

1U/6.3V_4

C130

22U/6.3V_6

C149

22U/6.3V_6

C164

22U/6.3V_6

C181

22U/6.3V_6

C189

10U/6.3V_6

C193

10U/6.3V_6

C201

1U/6.3V_4

C131

22U/6.3V_6

C142

22U/6.3V_6

C165

22U/6.3V_6

C182

22U/6.3V_6

C190

10U/6.3V_6

C194

10U/6.3V_6

C202

1U/6.3V_4

C132

22U/6.3V_6

C143

22U/6.3V_6

C166

22U/6.3V_6

C183

22U/6.3V_6

C191

10U/6.3V_6

C195

10U/6.3V_6

C203

1U/6.3V_4

C205

47U/6.3V_8

C145

22U/6.3V_6

C144

22U/6.3V_6

C167

22U/6.3V_6

C184

22U/6.3V_6

C192

10U/6.3V_6

C196

10U/6.3V_6

C204

1U/6.3V_4

C206

47U/6.3V_8

VCC_SENSE

VSS_SENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

+VCC_CORE

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

AG37

AG38

VCC_SENSE

VSS_SENSE

C133

0.1U/16V_4

1 2

C150

0.1U/16V_4

1 2

C168

0.1U/16V_4

1 2

1 2

1 2

1 2

+VCC_CORE

C134

0.1U/16V_4

C151

0.1U/16V_4

C169

0.1U/16V_4

R56

100/F_4

R57

100/F_4

C135

0.1U/16V_4

1 2

1 2

C152

0.1U/16V_4

1 2

1 2

C170

0.1U/16V_4

1 2

1 2

VCC_SENSE 43

VSS_SENSE 43

C146

0.1U/16V_4

C153

0.1U/16V_4

C171

0.1U/16V_4

1 2

1 2

1 2

C136

C147

0.1U/16V_4

1 2

C154

0.1U/16V_4

1 2

C172

0.1U/16V_4

1 2

Sense resistor should be placed within 2

inches (50.8 mm) of the processor socket

0.1U/16V_4

C155

0.1U/16V_4

C173

0.1U/16V_4

1 2

1 2

1 2

C148

0.1U/16V_4

C156

0.1U/16V_4

C174

0.1U/16V_4

Trace Impendence 50 ohm

C137

0.1U/16V_4

1 2

C157

0.1U/16V_4

1 2

C175

0.1U/16V_4

1 2

C138

0.1U/16V_4

1 2

C158

0.1U/16V_4

1 2

C176

0.1U/16V_4

1 2

+VCCGT

BM36

BM37

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ37

BJ38

BL36

BL37

BN36

BN37

BN38

BP37

BP38

BR37

BT37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

U1H

SKYLAKE_HALO

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

*SKL_H_BGA_BGA

BGA1440

8 OF 14

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

+VCCGT

VCC_SENSE VSS_SENSE

R58 *49 .9/F_4

A A

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

07 -- SKL 6/7 (POWER&GND )

07 -- SKL 6/7 (POWER&GND )

07 -- SKL 6/7 (POWER&GND )

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

7 51Monday, December 28, 2 015

7 51Monday, December 28, 2 015

7 51Monday, December 28, 2 015

1A

1A

1A

5

4

3

2

1

SKL-HProcessor (GND)

BT32

BT26

BT24

BT21

BT18

BT14

BT12

BR36

BR34

BR29

BR26

BR24

BR21

BR18

BR14

BR12

BP34

BP33

BP29

BP26

BP24

BP21

BP18

BP14

BP12

BN34

BN31

BN30

BN29

BN24

BN21

BN20

BN19

BN18

BN14

BN12

BM38

BM35

BM28

BM27

BM26

BM23

BM21

BM13

BM12

BM9

BM6

BM2

BL29

BK29

BK15

BK14

BJ32

BJ31

BJ25

BJ22

BH14

BH12

BH9

BH8

BH5

BH4

BH1

BG38

BG13

BG12

BF33

BF12

BE29

BD9

BC34

BC12

BB12

C17

C13

BT9

BT5

BR7

BP7

BN9

BN7

BN4

BN2

BE6

C9

U1L

SKYLAKE_HALO

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_H_BGA_BGA

12 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

C25

C23

C21

C19

C15

C11

C8

C5

BM29

BM25

BM18

BM11

BM8

BM7

BM5

BM3

BL38

BL35

BL13

BL6

BK25

BK22

BK13

BK6

BJ30

BJ29

BJ15

BJ12

BH11

BH10

BH7

BH6

BH3

BH2

BG37

BG14

BG6

BF34

BF6

BE30

BE5

BE4

BE3

BE2

BE1

BD38

BD37

BD12

BD11

BD10

BD8

BD7

BD6

BC33

BC14

BC13

BC6

BB30

BB29

BB6

BB5

C2

BT36

BT35

BT4

BT3

BR38

BA38

BA37

BA12

BA11

BA10

AY34

AY33

AY14

AY12

AW30

AW29

AW12

AW5

AW4

AW3

AW2

AW1

AV38

AV37

AU34

AU33

AU12

AU11

AU10

AT30

AT29

AR38

AR37

AR14

AR13

AP34

AP33

AP12

AP11

AP10

AN30

AN29

AN12

AM38

AM37

AM12

AM5

AM4

AM3

AM2

AM1

AL34

AL33

AL14

AL12

AL10

BB4

BB3

BB2

BB1

BA9

BA8

BA7

BA6

AU9

AU8

AU7

AU6

AT6

AR5

AR4

AR3

AR2

AR1

AP9

AP8

AN6

AN5

AL9

AL8

AL7

AL4

B9

U1M

SKYLAKE_HALO

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_H_BGA_BGA

13 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

AK30

AK29

AK4

AJ38

AJ37

AJ6

AJ5

AJ4

AJ3

AJ2

AJ1

AH34

AH33

AH12

AH6

AG30

AG29

AG11

AG10

AG8

AG7

AG6

AF14

AF13

AF12

AF4

AF3

AF2

AF1

AE34

AE33

AE6

AD30

AD29

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AC38

AC37

AC12

AC6

AC5

AC4

AC3

AC2

AC1

AB34

AB33

AB6

AA30

AA29

AA12

A30

A28

A26

A24

A22

A20

A18

A16

A14

A12

A10

A9

A6

B37

B3

A34

A4

A3

SKL-H Processor (RESERVED, CFG)

U1K

TP8

TP12

TP14

TP9

TP17

TP10

PCH_2_CPU_TRIG15

CPU_2_PCH_TRIG_R

CPU_2_PCH_TRIG_R CPU_2_PCH_TRIG

D1

RSVD_TP

E1

RSVD_TP

E3

RSVD_TP

E2

RSVD_TP

BR1

RSVD_TP

BT2

RSVD_TP

BN35

RSVD

J24

RSVD

H24

RSVD

BN33

RSVD

BL34

RSVD

N29

RSVD

R14

RSVD

AE29

RSVD

AA14

RSVD

A36

RSVD

A37

RSVD

H23

PROC_TRIGIN

J23

PROC_TRIGOUT

F30

RSVD

E30

RSVD

B30

RSVD

C30

RSVD

G3

RSVD

J3

RSVD

BR35

RSVD

BR31

RSVD

BH30

RSVD

*SKL_H_BGA_BGA

R59 30_4

Processor Strapping

The CFG signals have a default value of '1' if not terminated on the board.

0 Enable; SET DFX ENABLED BIT IN DEBUG

1 , Disable;

CFG32,16

CFG22,16

CFG42,16

CFG52,16

CFG62,16

CFG102,16

CFG122,16

CFG132,16

CFG3

CFG2

CFG4

CFG5

CFG6

CFG10

CFG12

CFG13

SKYLAKE_HALO

BGA1440

R60 *1K_4

R61 *1K_4

R62 1K_4

R63 *1K_4

R64 *1K_4

R65 *1K_4

R66 *1K_4

R67 *1K_4

11 OF 14

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

VSS

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

NCTF

NCTF

NCTF

NCTF

NCTF

NCTF

CPU_2_PCH_TRIG 15

U1F

SKYLAKE_HALO

BGA1440

Y38

VSS

Y37

VSS

Y14

VSS

Y13

VSS

Y11

VSS

Y10

VSS

Y9

D D

C C

B B

W34

W33

W12

U38

U37

R29

R12

N34

N33

N12

N10

M14

M13

M12

Y8

Y7

W5

W4

W3

W2

W1

V30

V29

V12

V6

U6

T34

T33

T14

T13

T12

T11

T10

T9

T8

T7

T5

T4

T3

T2

T1

R30

P38

P37

P12

P6

N11

N9

N8

N7

N6

N5

N4

N3

N2

N1

M6

L34

L33

L30

L29

K38

K11

K10

K9

K8

K7

K5

K4

K3

K2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_H_BGA_BGA

6 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

K1

J36

J33

J32

J25

J22

J18

J10

J7

J4

H35

H32

H25

H22

H18

H12

H11

G28

G26

G24

G23

G22

G20

G18

G16

G14

G12

G10

G9

G8

G6

G5

G4

F36

F31

F29

F27

F25

F23

F21

F19

F17

F15

F13

F11

F9

F8

F5

F4

F3

F2

E38

E35

E34

E9

E4

D33

D30

D28

D26

D24

D22

D20

D18

D16

D14

D12

D10

D9

D6

D3

C37

C31

C29

C27

D38

BM33

BL33

BJ14

BJ13

BK28

BJ28

BJ18

BJ16

BK16

BK24

BJ24

BK21

BJ21

BT17

BR17

BK18

BJ34

BJ33

G13

AJ8

BL31

B2

B38

BP1

BR2

C1

C38

08

TP11

TP13

TP15

TP16

TP18

TP19

TP20

TP21

TP22

TP23

A A

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

08 -- SKL 7/7 (GND)

08 -- SKL 7/7 (GND)

08 -- SKL 7/7 (GND)

1

8 51Monday, December 28, 2015

8 51Monday, December 28, 2015

8 51Monday, December 28, 2015

1A

1A

1A

5

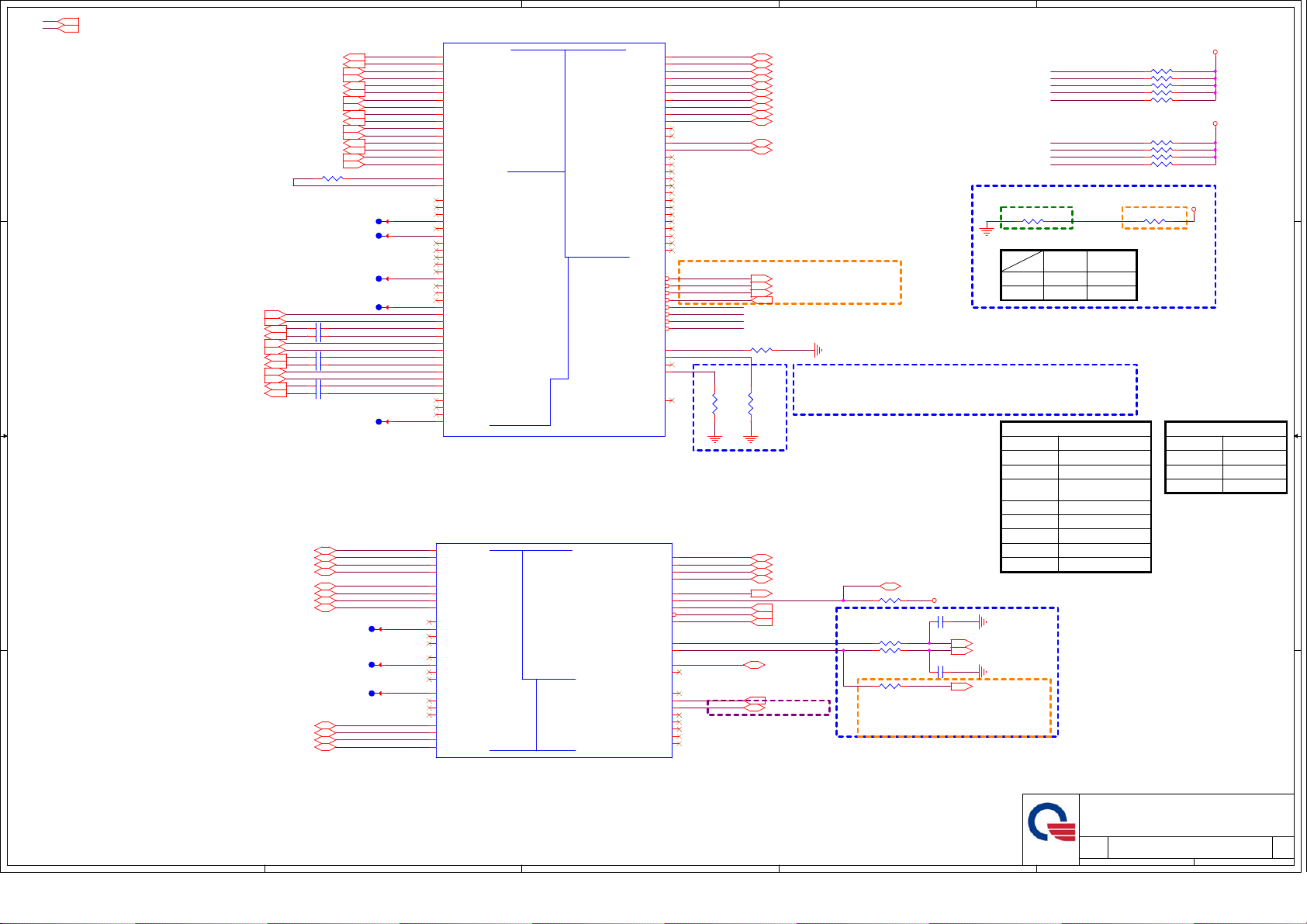

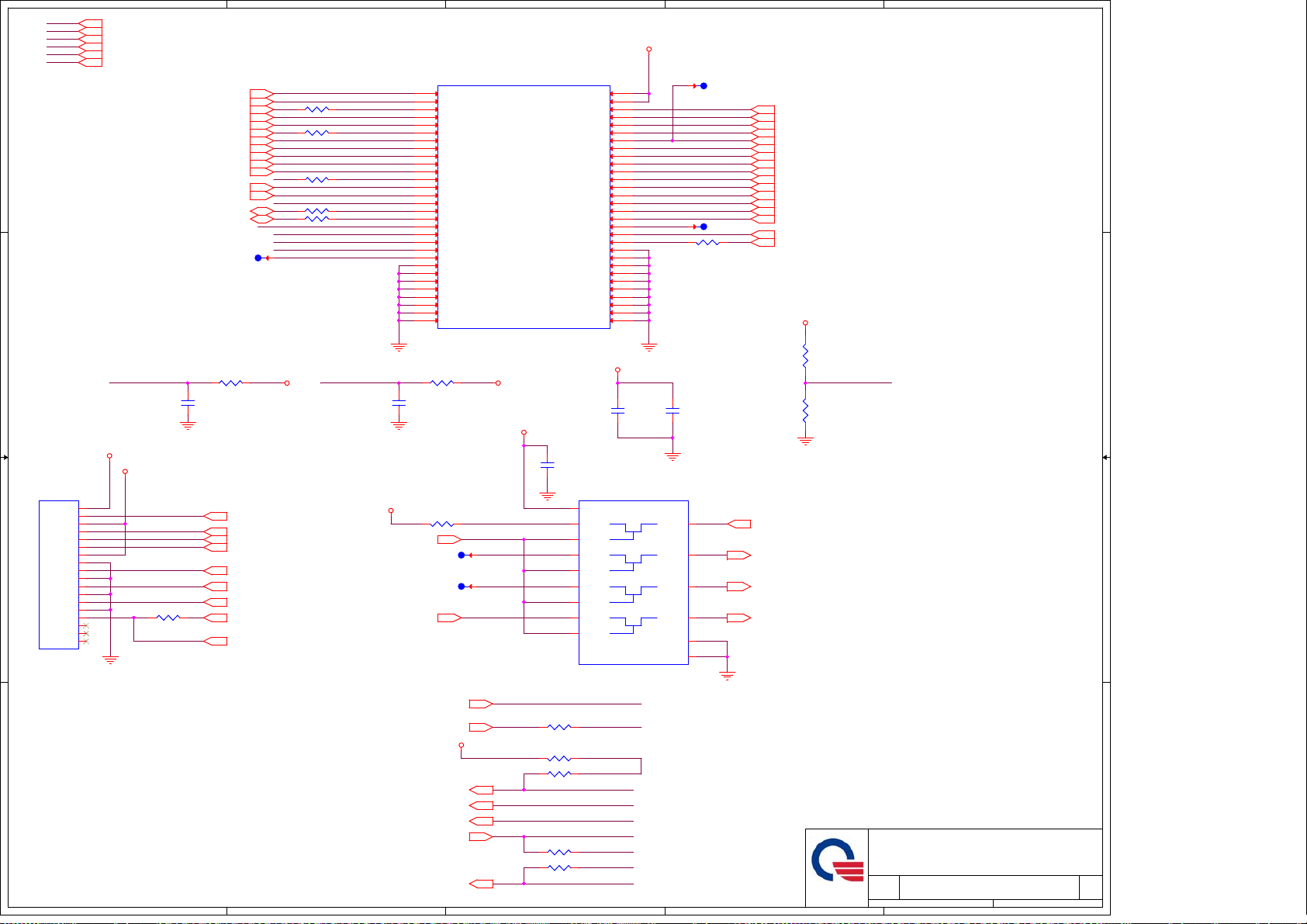

+3V_DEEP_SUS 10,12,13,14,16,18

+3V 5,10,11,12,13,14,16,17,18,19,22,26,27,28,29,30,32,33,34,35,36,37,38,43,46,49

DMI_TXN03

DMI_TXP03

DMI_RXN03

DMI_RXP03

DMI_TXN13

DMI_TXP13

DMI_RXN13

DMI_RXP13

D D

PCIE_RXN5_CARD36

PCIE_RXP5_CARD36

C C

Cardreader

WLAN

LAN

B B

PCIE_TXN5_CARD36

PCIE_TXP5_CARD36

PCIE_RXN6_WLAN33

PCIE_RXP6_WLAN33

PCIE_TXN6_WLAN33

PCIE_TXP6_WLAN33

PCIE_RXN7_LAN35

PCIE_RXP7_LAN35

PCIE_TXN7_LAN35

PCIE_TXP7_LAN35

USB3.0 (M/B-1)

USB3.0 (Small Board)

USB3.0 (3D Camera)

A A

DMI_TXN23

DMI_TXP23

DMI_RXN23

DMI_RXP23

DMI_TXN33

DMI_TXP33

DMI_RXN33

DMI_RXP33

C207 0.1U/16V_4

C208 0.1U/16V_4

C209 0.1U/16V_4

C210 0.1U/16V_4

C211 0.1U/16V_4

C212 0.1U/16V_4

USB30_TX1-30

USB30_TX1+30

USB30_RX1-30

USB30_RX1+30

USB30_TX2-30

USB30_TX2+30

USB30_RX2-30

USB30_RX2+30

USB30_TX4+31

USB30_TX4-31

USB30_RX4+31

USB30_RX4-31

R73 100/F_4

4

PCIECOMP_N

PCIECOMP_P

TP24

TP25

TP26

TP27

PCIE_TXN5_CARD_C

PCIE_TXP5_CARD_C

PCIE_TXN6_WLAN_C

PCIE_TXP6_WLAN_C

PCIE_TXN7_LAN_C

PCIE_TXP7_LAN_C

TP28

TP29

TP30

TP8515

U2B

L27

DMI_RXN0

N27

DMI_RXP0

C27

DMI_TXN0

B27

DMI_TXP0

E24

DMI_RXN1

G24

DMI_RXP1

B28

DMI_TXN1

A28

DMI_TXP1

G27

DMI_RXN2

E26

DMI_RXP2

B29

DMI_TXN2

C29

DMI_TXP2

L29

DMI_RXN3

K29

DMI_RXP3

B30

DMI_TXN3

A30

DMI_TXP3

B18

PCIE_RCOMPN

C17

PCIE_RCOMPP

H15

PCIE1_RXN/USB3_7_RXN

G15

PCIE1_RXP/USB3_7_RXP

A16

PCIE1_TXN/USB3_7_TXN

B16

PCIE1_TXP/USB3_7_TXP

B19

PCIE2_TXN/USB3_8_TXN

C19

PCIE2_TXP/USB3_8_TXP

E17

PCIE2_RXN/USB3_8_RXN

G17

PCIE2_RXP/USB3_8_RXP

L17

PCIE3_RXN/USB3_9_RXN

K17

PCIE3_RXP/USB3_9_RXP

B20

PCIE3_TXN/USB3_9_TXN

C20

PCIE3_TXP/USB3_9_TXP

E20

PCIE4_RXN/USB3_10_RXN

G19

PCIE4_RXP/USB3_10_RXP

B21

PCIE4_TXN/USB3_10_TXN

A21

PCIE4_TXP/USB3_10_TXP

K19

PCIE5_RXN

L19

PCIE5_RXP

D22

PCIE5_TXN

C22

PCIE5_TXP

G22

PCIE6_RXN

E22

PCIE6_RXP

B22

PCIE6_TXN

A23

PCIE6_TXP

L22

PCIE7_RXN

K22

PCIE7_RXP

C23

PCIE7_TXN

B23

PCIE7_TXP

K24

PCIE8_RXN

L24

PCIE8_RXP

C24

PCIE8_TXN

B24

PCIE8_TXP

SPT_PCH_H

U2F

C11

USB3_1_TXN

B11

USB3_1_TXP

B7

USB3_1_RXN

A7

USB3_1_RXP

B12

USB3_2_TXN/SSIC_1_TXN

A12

USB3_2_TXP/SSIC_1_TXP

C8

USB3_2_RXN/SSIC_1_RXN

B8

USB3_2_RXP/SSIC_1_RXP

B15

USB3_6_TXN

C15

USB3_6_TXP

K15

USB3_6_RXN

K13

USB3_6_RXP

B14

USB3_5_TXN

C14

USB3_5_TXP

G13

USB3_5_RXN

H13

USB3_5_RXP

D13

USB3_3_TXP/SSIC_2_TXP

C13

USB3_3_TXN/SSIC_2_TXN

A9

USB3_3_RXP/SSIC_2_RXP

B10

USB3_3_RXN/SSIC_2_RXN

B13

USB3_4_TXP

A14

USB3_4_TXN

G11

USB3_4_RXP

E11

USB3_4_RXN

SPT_PCH_H

SPT-H_PCH

USB

SPT-H_PCH

DMI

USB 2.0

PCIe/USB 3

2 OF 12

LPC/eSPI

GPP_A5/LFRAME#/ESPI_CS0#

GPP_A6/SERIRQ/ESPI_CS1#

GPP_A7/PIRQA#/ESPI_ALERT0#

GPP_A0/RCIN#/ESPI_ALERT1#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

SATA

6 OF 12

3

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2N_11

USB2P_11

USB2N_12

USB2P_12

USB2N_13

USB2P_13

USB2N_14

USB2P_14

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_F15/USB2_OCB_4

GPP_F16/USB2_OCB_5

GPP_F17/USB2_OCB_6

GPP_F18/USB2_OCB_7

USB2_COMP

USB2_VBUSSENSE

RSVD_AB13

USB2_ID

GPD7/RSVD

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A10/CLKOUT_LPC1

GPP_G19/SMI#

GPP_G18/NMI#

GPP_E6/DEVSLP2

GPP_E5/DEVSLP1

GPP_E4/DEVSLP0

GPP_F9/DEVSLP7

GPP_F8/DEVSLP6

GPP_F7/DEVSLP5

GPP_F6/DEVSLP4

GPP_F5/DEVSLP3

AF5

AG7

AD5

AD7

AG8

AG10

AE1

AE2

AC2

AC3

AF2

AF3

AB3

AB2

AL8

AL7

AA1

AA2

AJ8

AJ7

W2

W3

AD3

AD2

V2

V1

AJ11

AJ13

DIS only

DGPU_HOLD_ RST#

AD43

GPU_EVENT#

AD42

DGPU_PW R_EN

AD39

DGPU_PW ROK

AC44

USB_OC4#

Y43

USB_OC5#

Y41

USB_OC6#

W44

PCH_AOCS#

W43

USB2_COMP

AG3

AD10

AB13

AG2

BD14

AT22

AV22

AT19

BD16

BE16

BA17

SERIRQ

BOARD_ID8

AW17

AT17

BOARD_ID7

BC18

CLK_PCI_EC_R

BC17

CLK_PCI_LPC_R

AV19

M45

N43

AE45

GC6_FB_EN

AG43

AG42

DEVSLP0

AB39

AB36

For SSD (SATA0A)

AB43

AB42

AB41

DGPU_HOLD_ RST# 12,1 9

GPU_EVENT# 12,22

DGPU_PW R_EN 12,51

R80 113/F_4

R405

R406

*1K_4

*1K_4

2

USBP1- 30

USBP1+ 30

USBP2- 30

USBP2+ 30

USBP3- 30

USBP3+ 30

USBP4- 26

USBP4+ 26

USBP5- 34

USBP5+ 34

USBP7- 33

USBP7+ 33

USB2.0 Combo USB3.0 MB-1

USB2.0 Combo USB3. 0 Small Board

USB2.0 USB2.0 Small Board

HD / IR CAM

IR CAM

WLAN

GFX Present

R78 *100K_4

BOM:UMA only

Stuff

DGPU_PW ROK 12,23,37,50

If OTG is not implemented on the platform,

then USB2_ID and USB2_VBUSSENSE should both

be connected to ground.

NC

PORT1

PORT2

PORT3

PORT4

PORT5

PORT6

PORT7

LAD0 33,34,37

LAD1 33,34,37

LAD2 33,34,37

LAD3 33,34,37

LFRAME# 33,34,37

BOARD_ID8 13

EC_RCIN# 37

BOARD_ID7 13

SIO_EXT_SMI# 37

GC6_FB_EN 22

DEVSLP0 33

SERIRQ 34,37

R81 8.2K_4

R82 22/F_4

R83 22/F_4

R84 *22/F_4

Ra

+3V

EC1 18P/50V_4

EC2 18P/50V_4

PORT8

PORT9-14

CLK_24M_KBC 37

CLK_24M_DEBUG 33

EMI(near PCH)

CLK_PCI_TPM 34

BOM: HW TPM need Ra, Rc Stuff

DGPU_HOLD_ RST#

DGPU_PW R_EN

DGPU_PW ROK

SIO_EXT_SMI#

EC_RCIN#

USB_OC4#

USB_OC5#

USB_OC6#

PCH_AOCS#

GPU_EVENT#

SG(Default)

Ra

Rb

USB 2.0 PORT

USB2 MB

USB2 DB

USB2 DB

HD /IR CAM

(OPTION)

IR CAM (OPT ION)

NC

WLAN

NC

NC

Place to PCH

R68 *10K_4

R69 10K_4

R70 10K_4

R71 10K_4

R72 10K_4

R74 10K_4

R75 10K_4

R76 10K_4

R77 10K_4

RaRb

R79 10K_4

BOM:DIS only

UMA

Rb

Ra

1

PORT1

PORT2

PORT3

PORT4

+3V

09

+3V_DEEP_SUS

+3V

USB 3.0 PORT

USB3 MB

USB3 DB

NC

3D CAMERA

PROJECT : G37A/G37B

PROJECT : G37A/G37B

PROJECT : G37A/G37B

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

09 -- PCH 1/7 (DMI/USB/PCIE)

09 -- PCH 1/7 (DMI/USB/PCIE)

09 -- PCH 1/7 (DMI/USB/PCIE)

1

9 51Monday, December 28, 2015

9 51Monday, December 28, 2015

9 51Monday, December 28, 2015

1A

1A

1A

5

+5VS5 26,28,30,41,42,43,44,45,46,47,48,49,50,51

+3V_RTC_2 12,14

+3VS5 12,14,16,26,33,37,41,42,46,47,48,51

+3V_DEEP_SUS 9,12,13,14,16,18

+3V 5,9,11,12,13,14,16,17,18,19,22,26,27,28,29,30,32,33,34,35,36,37,38,43,46,49

+1.2VSUS 2,6,17,18,42,46,48,51

+1.0V 2,5,6,16,37,48

HDA Bus(CLG)

BIT_CLK_AU DIO28

ACZ_RST#_AUDIO28

ACZ_SDOUT_AUDIO28

ACZ_SYNC_AUDIO28

D D

+3V_DEEP_SUS

GPIO33_EC37

RSMRST#

C C

EC_PWROK

BIT_CLK_AU DIO

R85 33_4

R86 33_4

R88 33_4

R89 33_4

R92 2.2K_4

R94 2.2K_4

R95 2.2K_4

R96 2.2K_4

R97 2.2K_4

R98 2.2K_4

R101 10K_4

R103 *10K_4

R104 *10K_4

R110 1K_4

C215 *220P/50V_4

C216 *220P/50V_4

C214 *33P/50V_4

ACZ_BCLK

ACZ_RST#

ACZ_SDOUT

ACZ_SYNC

R87

*1M_4

SMB_ME0_CLK

SMB_ME0_DAT

SMB_ME1_CLK

SMB_ME1_DAT

SMB_PCH_CLK

SMB_PCH_DAT

RF_OFF_PCH

SUSWARN#

SUSACK#

ACZ_SDOUT

1126 Correct des. from CAP CHIP 10P

16V(+-20%,X7R,0402) to CAP CHIP 10P

50V(+-5%,C0G,0402)

C213

*10P/50V_4

Reserve for EMI

AUD_AZACPU_SDO_R3

AUD_AZACPU_SDI3

AUD_AZACPU_SCLK3

DRAMRST_CNTRL_PCH12

SML1ALERT#_R12

EMI

Q1

MBCLK25,18,37

MBDATA25,18,37

R122 4.7K_4

B B

+3V