Page 1

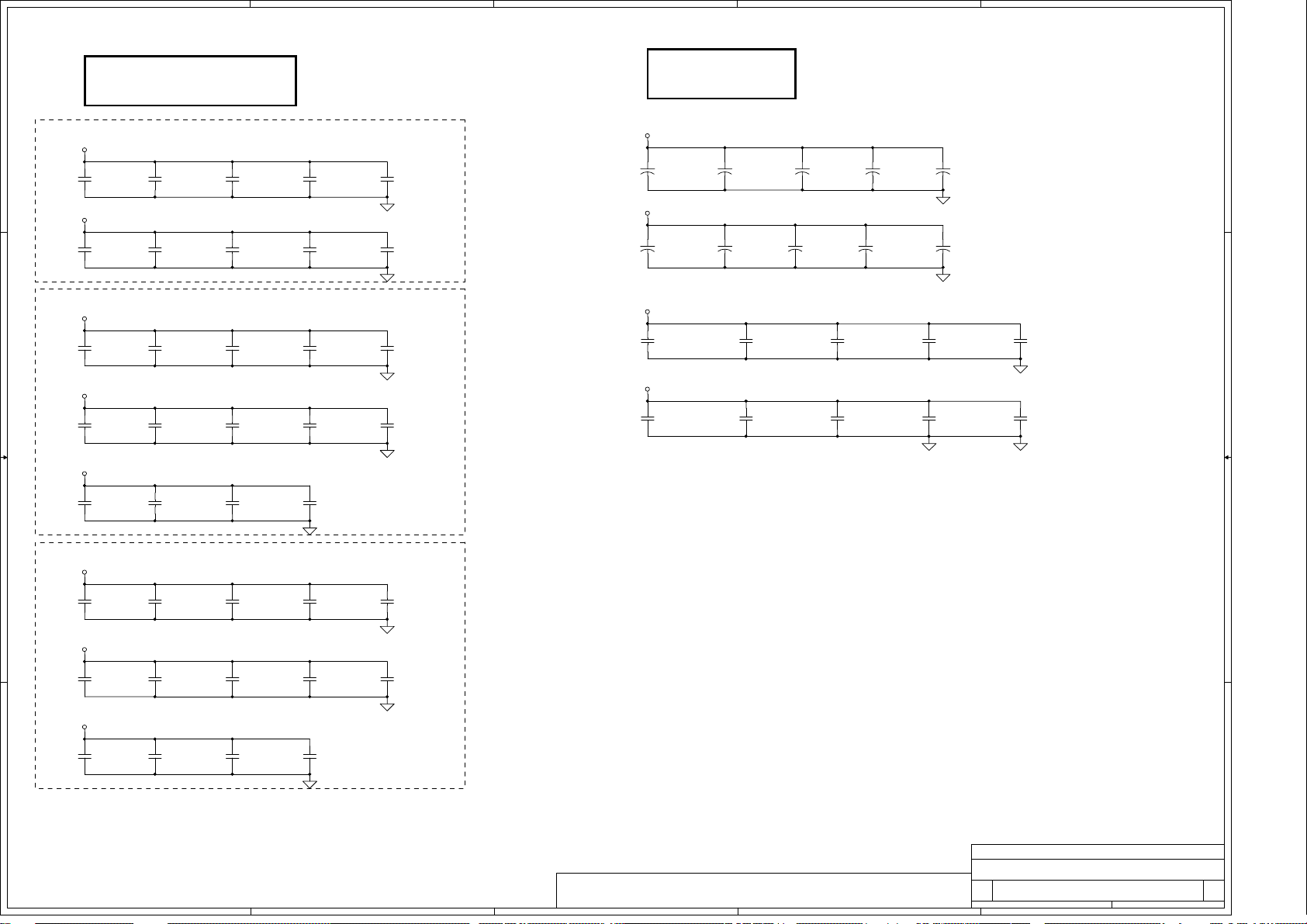

A

1 1

B

C

D

E

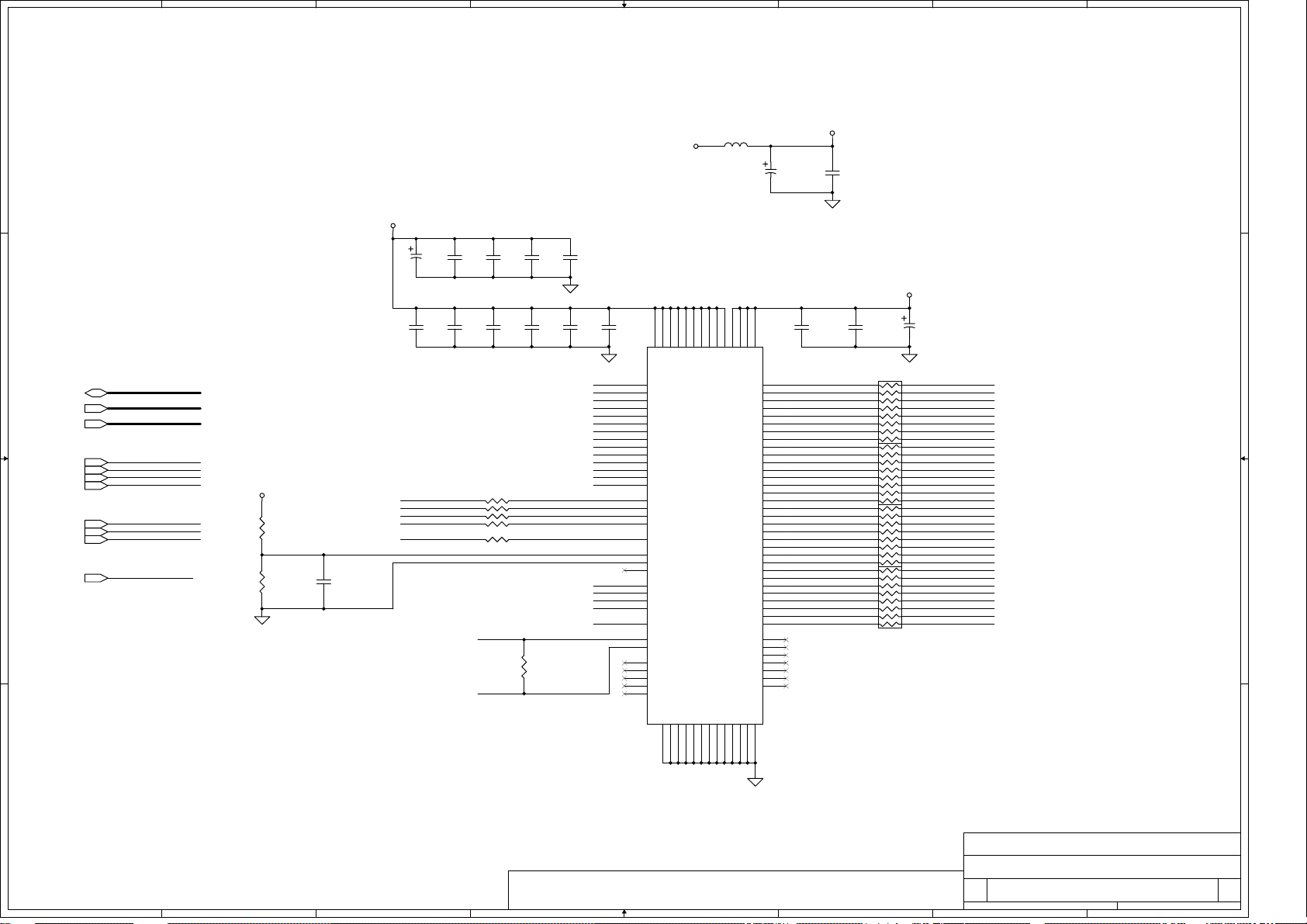

SAPPORO M (BTW20)

2 2

LA-1691 REV0.4 Schematic Document

Intel Mobile P4 uFCBGA/uFCPGA Northwood Celeron

MCH-M(845MZ)+ICH3-M+M6-C(16MB VRAM)

2002-12-12

3 3

4 4

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCH EMATIC, M/B LA-1691

Size Docu ment Number Re v

Custom

401241

Date: Sheet

星期二 一月

07, 2003

E

of

153,

1A

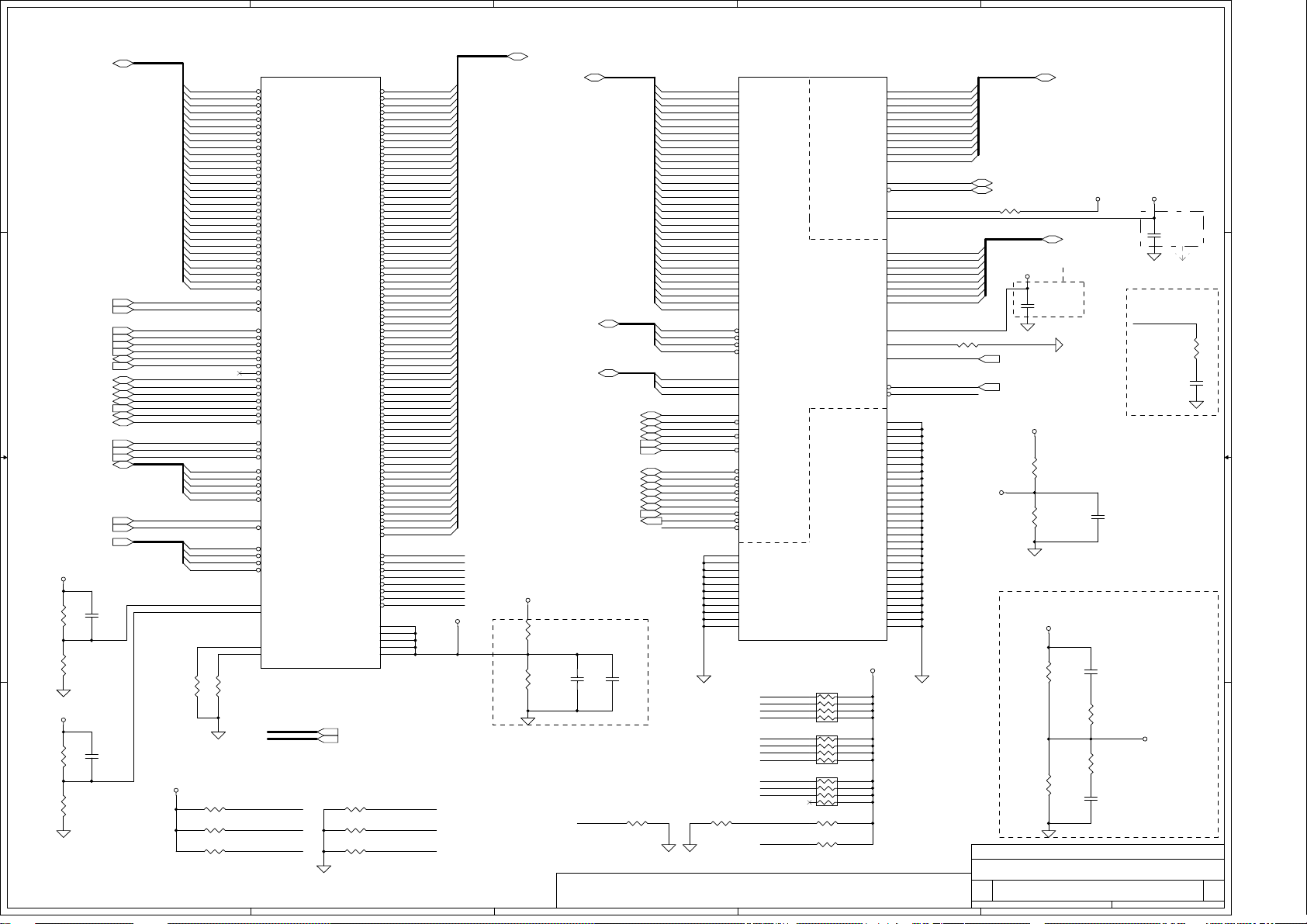

Page 2

A

B

C

D

E

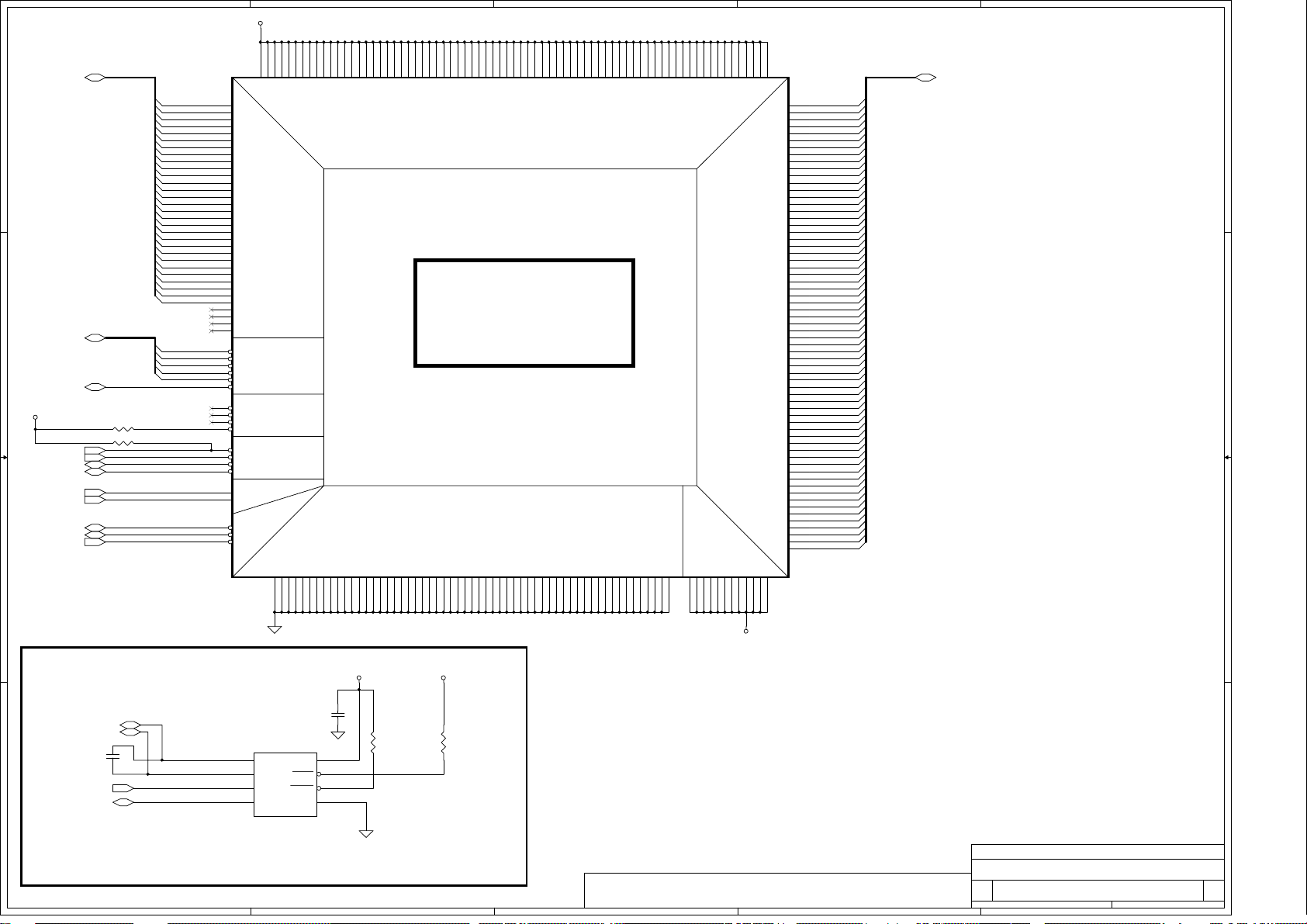

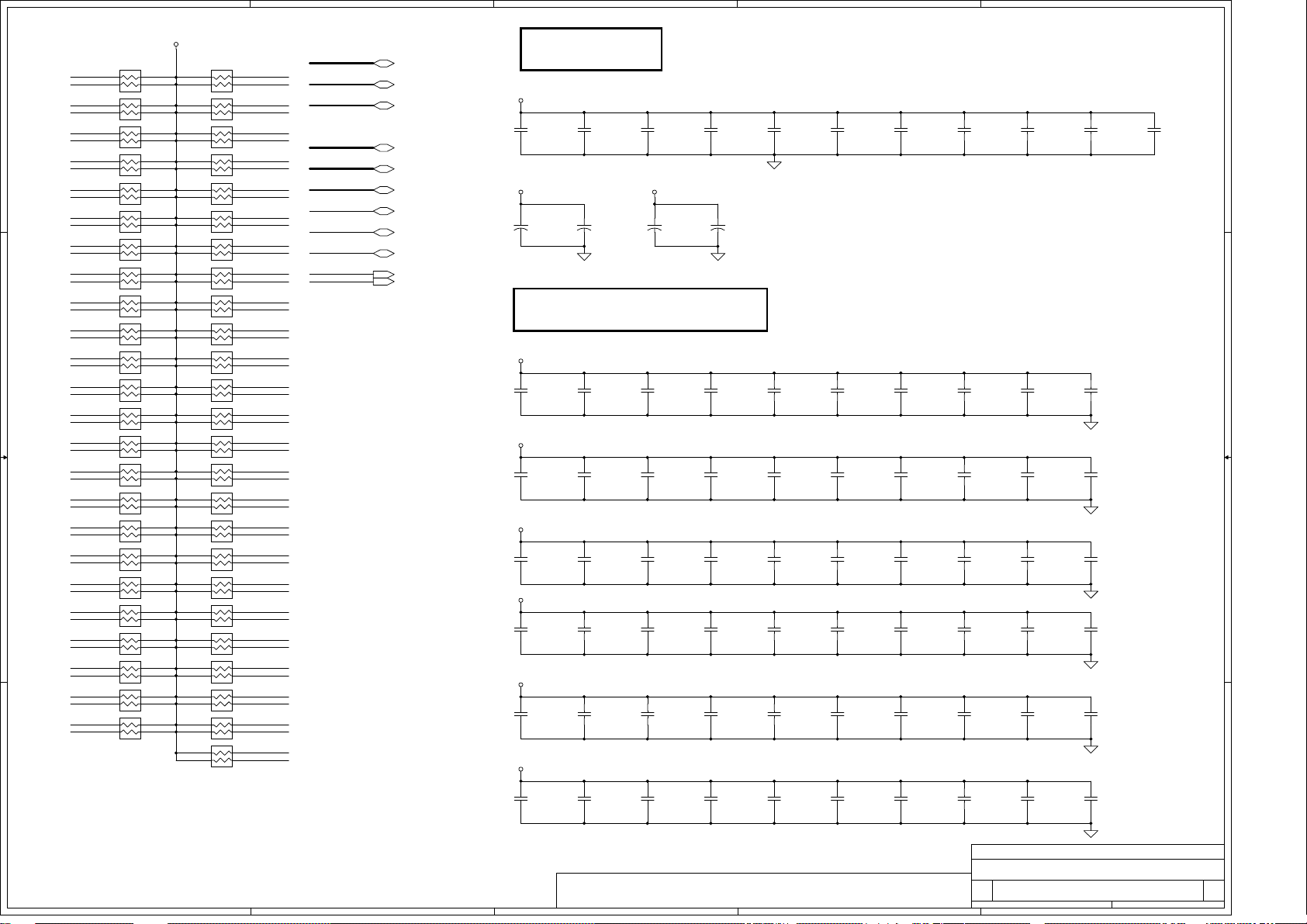

BTW20 LA-1691 BLOCK DIAGRAM

4 4

Mobile

Northwood

(uFCBGA/uFCPGA)

PSB

CRT&LVDS

Connector

TV-OUT

3 3

Connector

PAGE 19

ATI-M6-C

PAGE 18

AGP

PAGE 14,15,16,17

Mini PCI

PAGE 28

AGP Bus

Brookdale-M

MCH-M 845MZ

625 BGA

REV B1

HUB Interface

266MHz

(1.8V)

PAGE 4,5,6

400MHz

PAGE 7,8,9

48MHz (3.3V)

Thermal S ensor

ADM1032

200MHz

(2.5V)

Memory Bus

Clock Generator

ICS9508-10

PAGE 4

SO-DI M M x 2(DDR)

BANK 0,1,2,3

USB 1.1 Port *4

PAGE 33

PAGE13

PAGE 10,11,12

BlueToot h Connector

CPU VID

PAGE 5

PAGE 33

FANController

PAGE 40

DC/DC Interface

RTC Battery

PAGE 42

BATTERY

Charger

PAGE 44

Power Interface &

TEMP. sensing circuit

PAGE 46,47,48

24.576MHz

(3.3V)

C

ATA 66/100

2nd IDE

AC-LINK

PAGE 39

IDE HDD

Audio CD-DJ

AC97 CODEC

ALC 202

OZ168T

MDC

Connector

PAGE 30

PAGE 29

PAGE 34

PAGE 31

CD-ROM/DVD

Audio Hardware

EQ

RJ-11

PAGE 27

D

PAGE 30

PAGE 35

Aud i o A m p lifier

TPA0232

Compal Electronics, inc.

Title

SCH EMATIC, M/B LA-1691

Size Docu ment Number Re v

Custom

Date: Sheet

星期二 一月

07, 2003

401241

PAGE 36

E

of

253,

1A

RJ-45

PAGE 27

2 2

Slot 0/1

PAGE 25

SD Reader

Winbond

W83L518D

1 1

A

PAGE 37

LAN

RTL8100-B(L)

CARDBUS

IEEE1394

TSB43AB21

OZ6933

PAGE 26

PAGE 24

PAGE 23

Super I/O

LPC47N227

REV B

Parallel

PAGE 31

33MHz (3.3V)

PAGE 32

B

PCI BUS

ICH3-M

LPC BUS 3 3MHz (3.3V)

Embedded

Controller

NS PC87591L

PAGE 38

421 BGA

REV B1

PAGE 38

PAGE 20,21,22

BIOS & I/O PORTScan KB

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

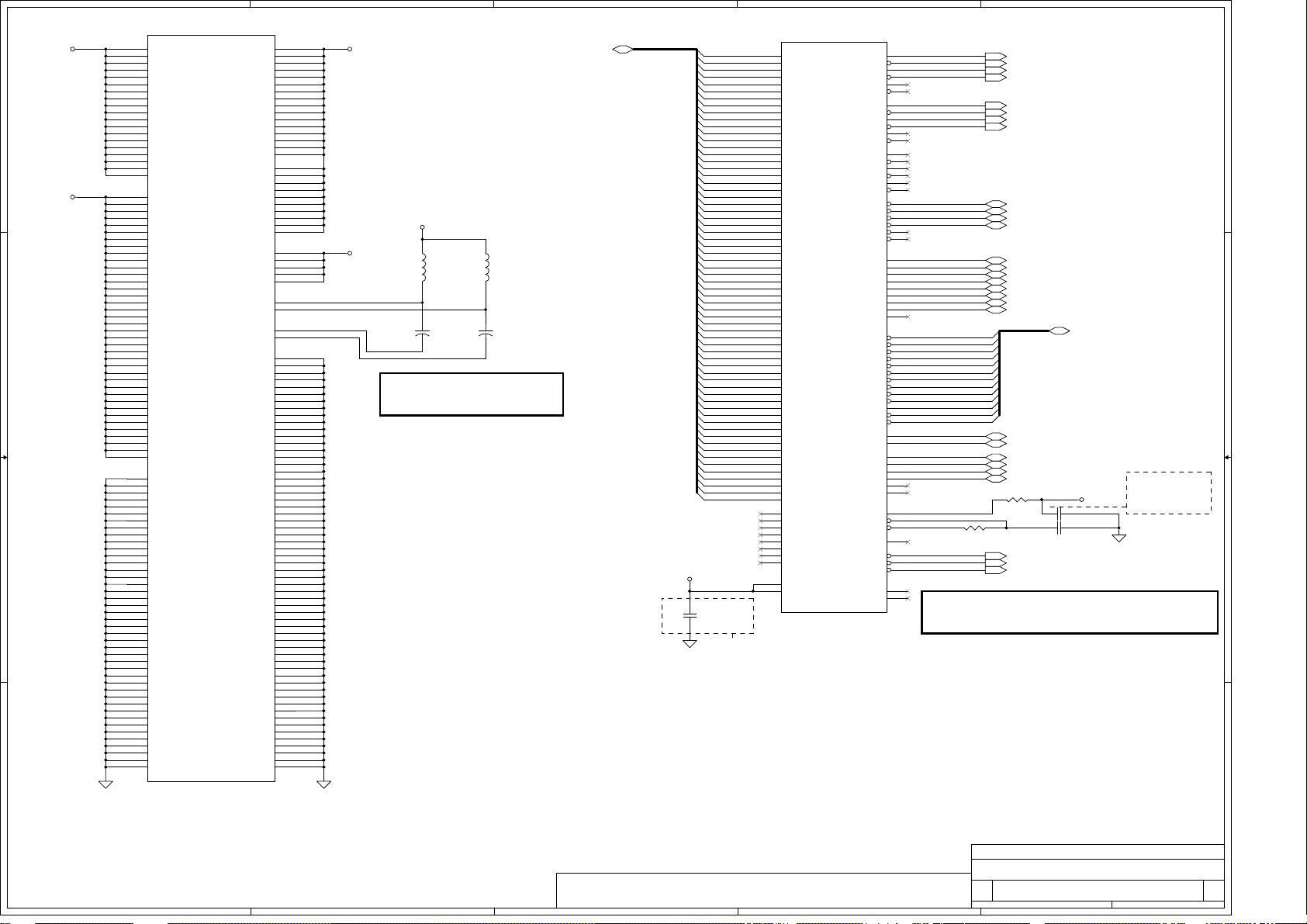

Page 3

A

B

C

D

E

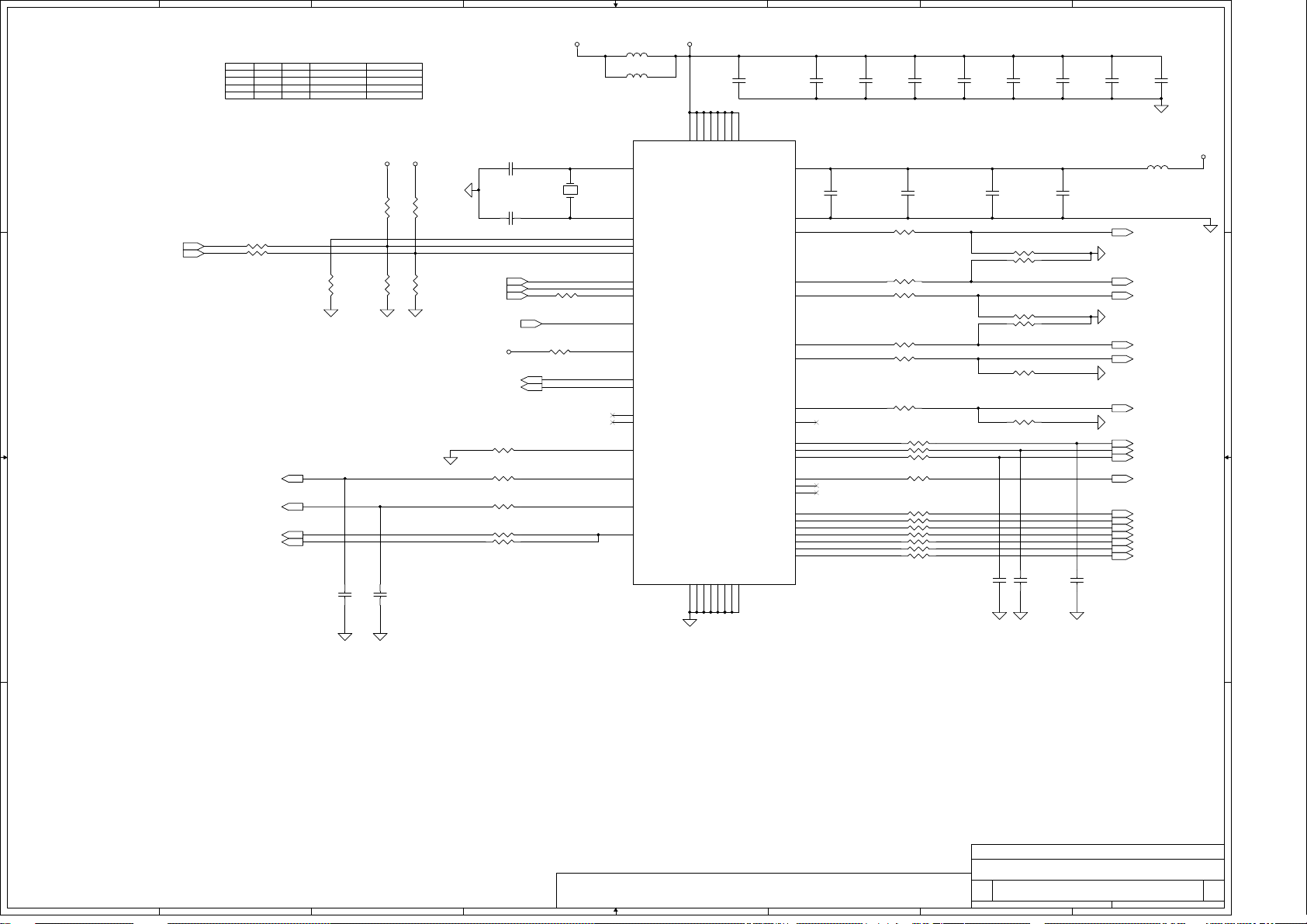

Voltage Rails

STATE

Power Plane Description

1 1

VIN

B+

+CPU_VCC

+1.2VP

+1.2VS 1.2V switched power rail for Montara core ON OFF OFF

+1.25VS 1.25V switched power rail ON OFF OFF

**

+1.8VS

**

+2.5V

+3VALW

+3V

+3VS

+5VALW

+5V

2 2

+5VS

+12VALW

RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

AGP 4X ON OFF OFF+1.5VS

1.8V always power rail ON ON

2.5V power rail

2.5V switched power rail+2.5VS

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail

5V switched power rail

12V always on power rail

RTC power

S1 S3 S5

N/A N/A N/A

ON O F F

ON O F F

OFF1.8V switched power rail ON OFF

ON

ON

OFF

ON

ON

ON

ON

OFF

ON

ON

ON

ON

ON

OFF

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

ON*+1.8VALW

OFF

OFF

ON*ON

OFF

OFF

ON*

OFF

OFF

ON*

ON

Exter n al PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

CardBus

LAN

Mini-PCI

1394

AD20

AD17

AD18

AD16 0

2

3 PIRQB(PIRQD)

1/4

PIRQA / PIRQB(PIRQ E/PIRQF)

PIRQC/PIRQD(PIRQ G/PIRQH)

PIRQA

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7NC

Board ID

SIGNAL

100K +/- 5%Ra

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

0

1

2

3

4

5

SLP_S1# SLP_S3#

SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH H IGH HIGH HIGH

LOW

LOW

HIGH

LOW

LOWLOWLOW

LOW LOW LOW LOW

Rb V min

0

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

PCB Revision

0.1 , 0.2

0.3

NO DIRECT CD PLAY

ONONON ON

ON

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

V typ

AD_BID

ON

OFF

OFF

0 V 0 V

0.503 V

0.819 V

1.185 V 1.264 V

2.200 V

3.300 V

ON

OFF

OFF

OFF

V

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

LOW

OFF

OFF

OFF

max

6

1394

CardBus

LAN

MINIPCI

7

Topology

Mount R458 RP122

Unmount R474 RP125 R533

Trace: PIRQA#_1394

Use IRQA

Trace:PIRQA#/E#

PIRQB#/F#/D#

Use IRQA IRQB

Trace:PIRQB#/F#/D#

Use IRQB

Trace:PIRQC#/G#

PIRQD#/H#

Use IRQC IRQD

3 3

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

0001 011X b

1010 000X b

1011 000Xb

EC SM Bus2 address

Device

ADM1032

OZ168

Smart Battery

Docking

DOT Board

1001 110X b

0011 0100 b

0001 011X b

0011 011X b

XXXX XXXXb

ICH3 SM Bus address

Device

Clock Generator (

ICS-950810)

4 4

Address

1101 001X

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCH EMATIC, M/B LA-1691

Size Docu ment Number Re v

Custom

401241

Date: Sheet

星期二 一月

07, 2003

E

of

353,

1A

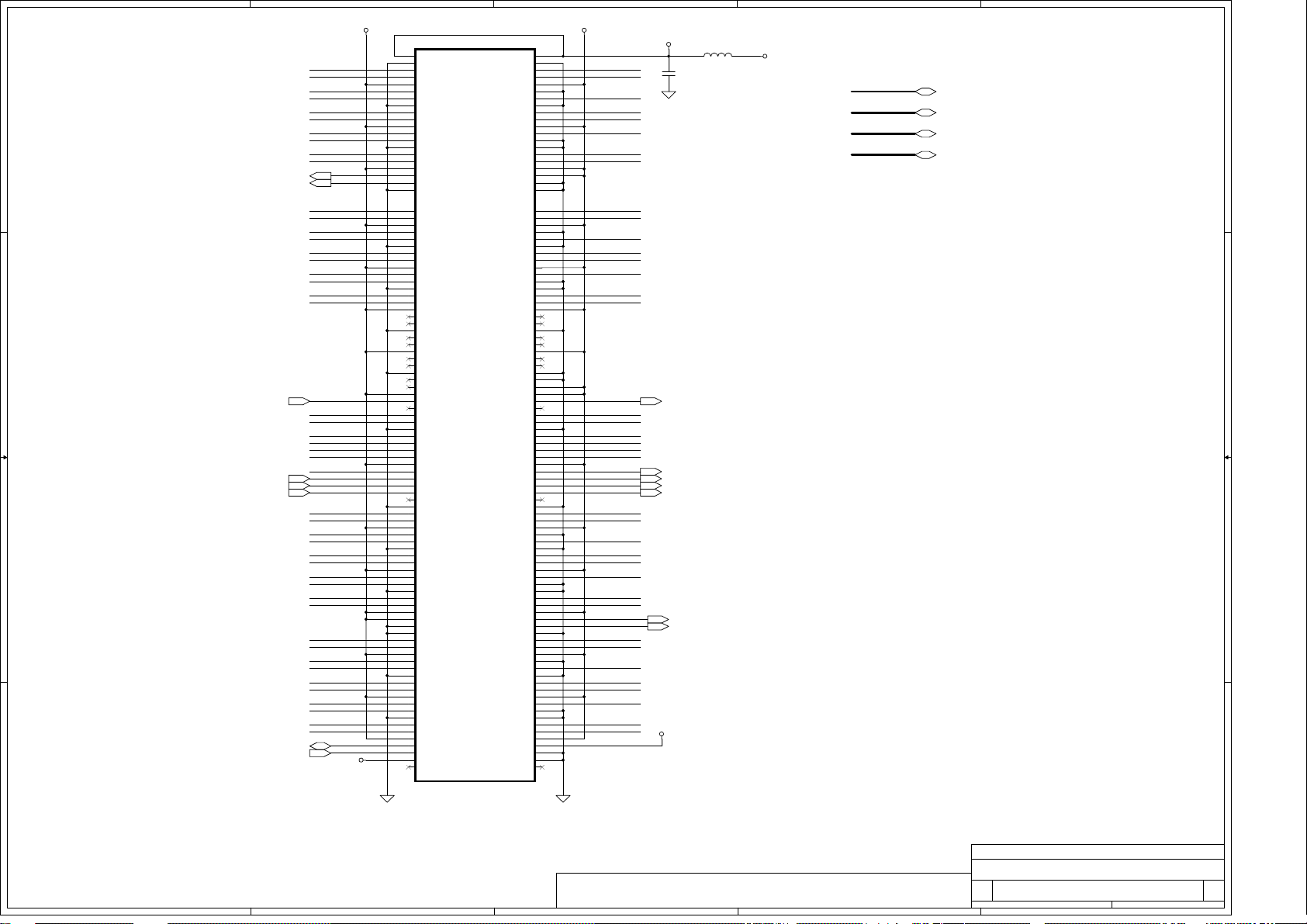

Page 4

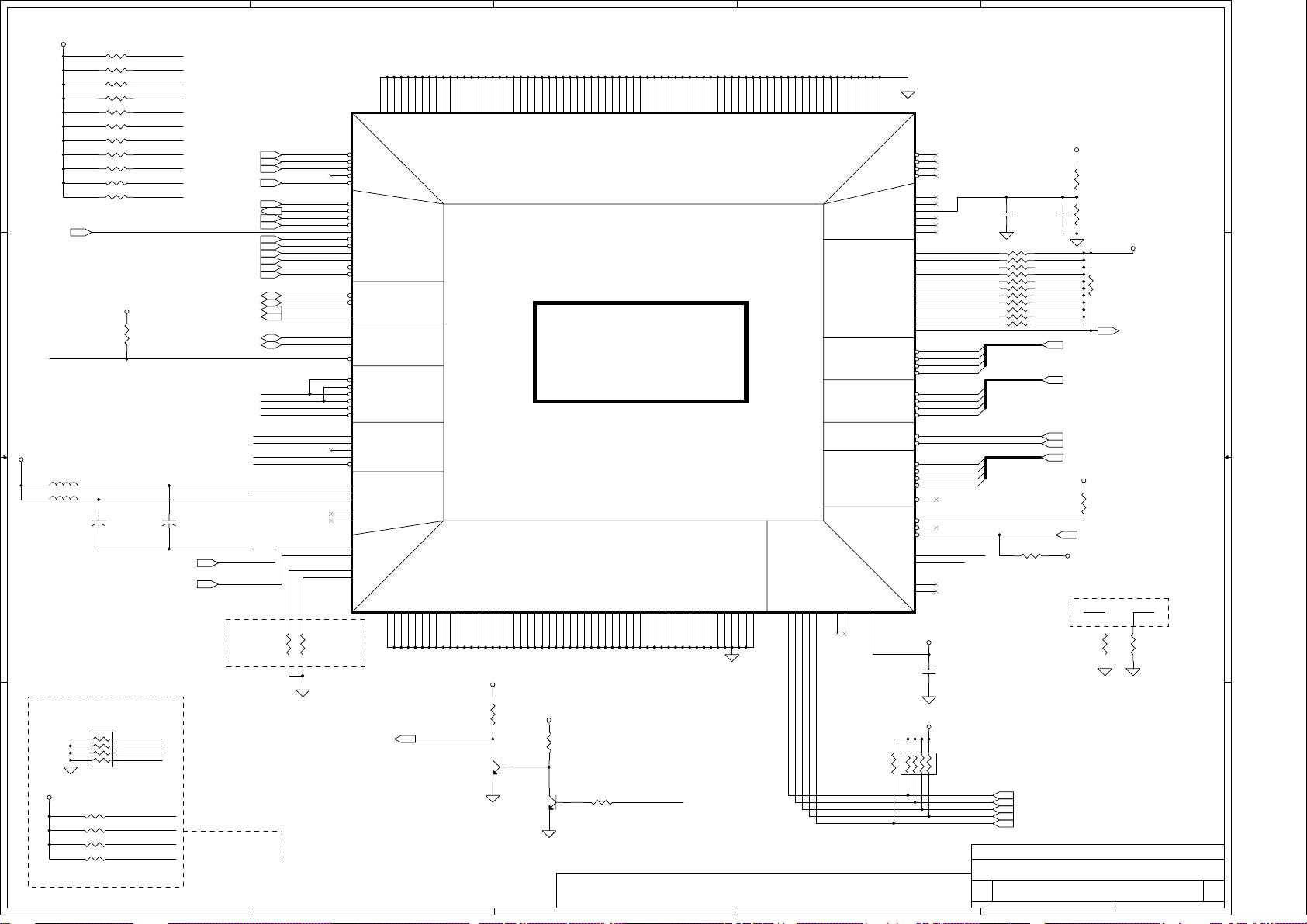

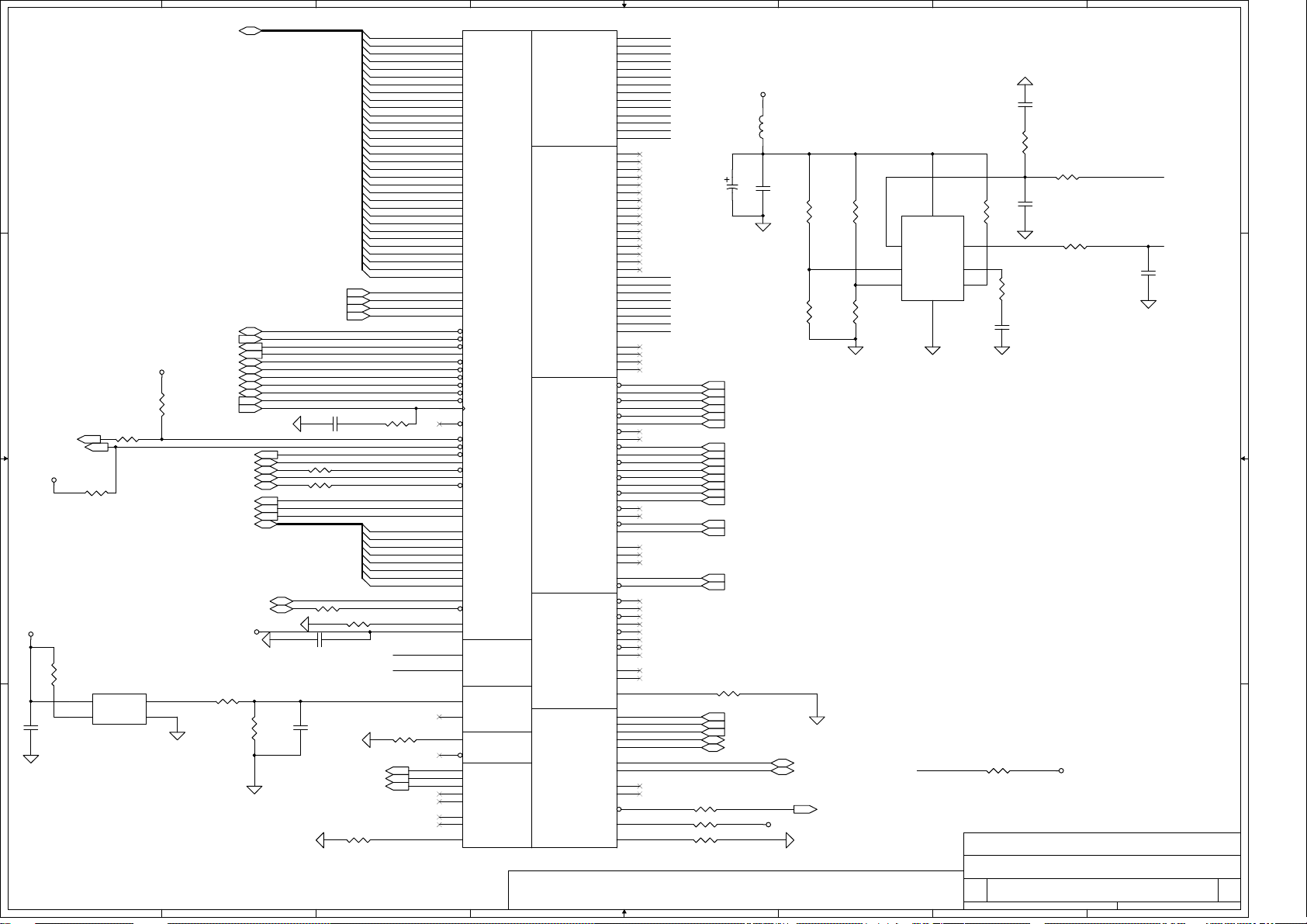

A

HA#[3..31]7

1 1

HRE Q#[0 ..4 ]7

2 2

H_ADS#7

+CPU_CORE

H_BREQ0#7

H_BPRI#7

H_BNR#7

H_LOCK#7

CLK_CPU_BCLK13

CLK_CPU_BCLK#13

H_HIT#7

H_HITM#7

H_DEFER#7

3 3

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#[0..4]

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

R91 Close to U37 pinM23

R31 10K_0402_5%

**

R74 220_0402_5%

CLK_CPU_BCLK

CLK_CPU_BCLK#

AF22

AF23

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

W1

T5

U4

V3

W2

Y1

AB1

J1

K5

J4

J3

H3

G1

AC1

V5

AA3

AC3

H6

D2

G2

G4

F3

E3

E2

+CPU_CORE

A10

U37A

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

BCLK0

BCLK1

HIT#

HITM#

DEFER#

A12

A14

A16

A18

A20

AA10

AA12

AA14

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6A8VCC_7

VCC_8

VSS_0H1VSS_1H4VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

A11

A13

A15

A17

H23

H26

B

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

Mobile

NorthWood

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12A3VSS_13A9VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

A19

A21

A24

A26

AA1

AA11

AA4

AA7

AA13

AA15

AA9

AA17

AA19

AA23

AA26

AB10

AB12

AB3

AB6

AB8

AB14

AB16

AB18

AB20

AB21

AB24

AC2

AC11

AC13

AC15

AC17

AC19

C

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

D9

E10

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56B7VCC_57B9VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65C8VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71D7VCC_72

VCC_73

B21

D#0

B22

D#1

A23

D#2

A25

D#3

C21

D#4

D22

D#5

B24

D#6

C23

D#7

C24

D#8

B25

D#9

G22

D#10

H21

D#11

C26

D#12

D23

D#13

J21

D#14

D25

D#15

H22

D#16

E24

D#17

G23

D#18

F23

D#19

F24

D#20

E25

D#21

F26

D#22

D26

D#23

L21

D#24

G26

D#25

H24

D#26

M21

D#27

L22

D#28

J24

D#29

K23

D#30

H25

D#31

M23

D#32

N22

D#33

P21

D#34

M24

D#35

N23

D#36

M26

D#37

N26

D#38

N25

D#39

R21

D#40

P24

D#41

R25

D#42

R24

D#43

T26

D#44

T25

D#45

T22

D#46

T23

D#47

U26

D#48

U24

D#49

U23

D#50

V25

D#51

U21

D#52

V22

D#53

V24

D#54

W26

D#55

Y26

D#56

W25

D#57

Y23

D#58

Y24

D#59

Y21

D#60

AA25

D#61

AA22

D#62

AA24

D#63

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

AC5

AC7

AC9

AD1

AC22

AC25

AD10

AD4

AD12

AD8

AD14

AD16

AD18

AD21

AD23

VCC_79E8VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

F9

F11

F13

F15

F17

F19

NorthWood

E12

E14

E16

E18

E20

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5HA#8

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

D

HD#[0..63]

E

HD#[0..63] 7

+CPU_CORE

Thermal Sensor

ADM1032AR

H_THERMDA5

H_THERMDC5

2200P_0402_25V7K

4 4

C534

EC_SMC229,38

EC_SMD229,38

H_THERMDA

H_THERMDC

0.1U_0402_16V4Z

U34

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032AR_SOP-8

VDD1

ALERT

THERM

GND

W=15mil

C537

1

6

4

5

+3VS

R370

4.7K_0402_5%

+3VS

R369

4.7K_0402_5%

Address:1001_100X

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PRO PERTY OF COMPAL ELECTRO NICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED F RO M T HE CUSTO DY OF THE COM PETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, I NC. NEI THER THI S SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCH EMATIC, M/B LA-1691

Size Docu ment Number Re v

Custom

401241

Date: Sheet

星期二 一月

07, 2003

E

of

453,

1A

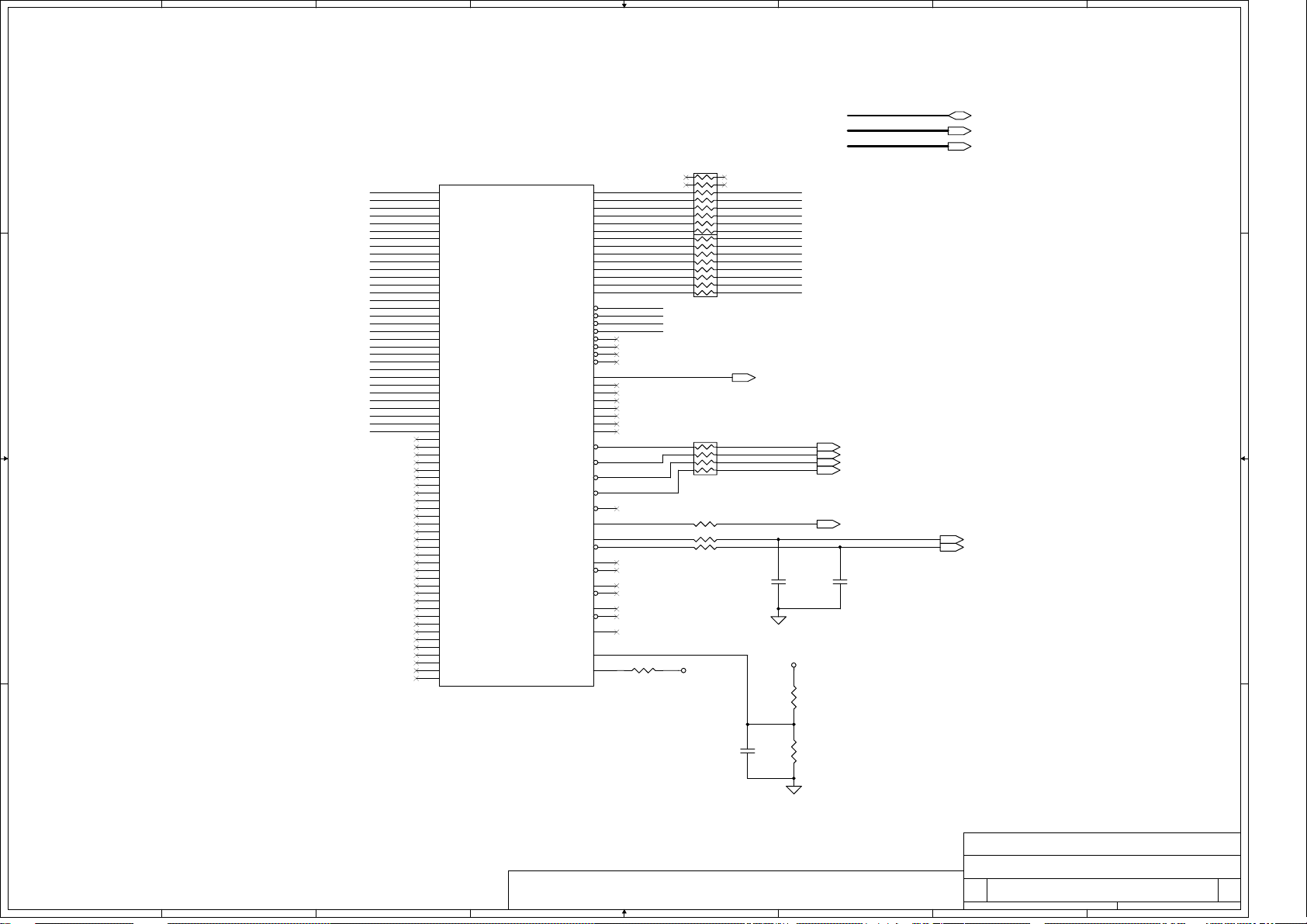

Page 5

A

B

C

D

E

+CPU_CORE

R164 200_0402_5%

R174 200_0402_5%

R169 200_0402_5%

R165 200_0402_5%

H_THERMTRIP#

Murata

LQG21F4R7N00

L3

4.7UH_80mA_0805

4.7UH_80mA_0805

L2

1 8

2 7

3 6

4 5

R68 51_0603

R66 51_0603

R56 51_0603

R62 51_0603

R177 200_0402_5%

R162 200_0402_5%

R171 200_0402_5%

R167 200_0402_5%

R181 56_0402_5%

R21 51.1_1%_0603

R48 300_0402_5%

12

+

RP6

1.5K_8P4R_0804_5%

1 1

H_PWRGD20

Place R65 near to U40 pinAB23

Place R420 near to U12 pinW20

2 2

+1.2VP

1 2

1 2

3 3

R84 R87 placed with in 0.5" of processor,

and at least 25mils away from other signals

+CPU_CORE

4 4

12

+CPU_CORE

C3

33UF_D2_16V

ITP_TMS

ITP_TCK

ITP_TRST#

ITP_TDI

ITP_PREQ#

12

ITP_PRDY#

12

ITP_BPM0

12

ITP_BPM1

12

A

H_INIT#

H_A20M#

H_SMI#

H_IGNNE#

H_STPCLK#

H_DPSLP#

H_NMI

H_INTR

H_FERR#

H_RESET#

H_PWRGD

R85

56_0402_5%

CLK_CPU_ITP13

CLK_CPU_ITP#13

H_RS#07

H_RS#17

H_RS#27

H_TRDY#7

ITP_BPM0

ITP_BPM1

ITP_PRDY#

ITP_PREQ#

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

+H_VCCA

TP1

+H_VCCIOPLL

R69

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_DPSLP#

H_INTR

H_NMI

H_INIT#

H_RESET#

H_THERMDA

H_THERMDC

COMP0

COMP1

1 2

1 2

51.1_1%_0603

12

C473

+

33UF_D2_16V

H_A20M#20

H_FERR#20

H_IGNNE#20

H_STPCLK#20

H_DPSLP#20

H_CPURST#7

H_DBSY#7

H_DRDY#7

H_BSEL013

H_BSEL113

H_THERMDA4

H_THERMDC4

H_VSSA

CLK_CPU_ITP

CLK_CPU_ITP#

H_SMI#20

H_INTR20

H_NMI20

H_INIT#20

51.1_1%_0603

Place pull up resistors near processor

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

C11

C13

C15

C17

C19

C22

C25

D10

VSS_67

VSS_68

VSS_139

K24

VSS_69

VSS_70

VSS_71

VSS_140K3VSS_141K6VSS_142L1VSS_143

Q53

3904

AF26

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85B4VSS_86B8VSS_87

VSS_88

VSS_89

VSS_90

SKTOCC#

VSS_91

Mobile

NorthWood

VSS_144

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

VSS_160

VSS_161R4VSS_162

L23

L26

M22

M25

+5V

12

R551

10K

2

3 1

Q47

3904

P22

N21

N24

+CPU_CORE

12

R552

470

2

R469 470

3 1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

T21

R23

R26

12

C

T24

H_THERMTRIP#

P25

U37B

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

G24

VSS_66

VSS_136

VSS_137J5VSS_138

J22

J25

K21

F1

RS#0

G5

RS#1

F4

RS#2

AB2

RSP#

J6

TRDY#

C6

A20M#

B6

FERR#

B2

IGNNE#

B5

SMI#

AB23

PWRGOOD

Y4

STPCLK#

AD25

DPSLP#

D1

LINT0

E5

LINT1

W5

INIT#

AB25

RESET#

H5

DBSY#

H2

DRDY#

AD6

BSEL0

AD5

BSEL1

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AC6

BPM#0

AB5

BPM#1

AC4

BPM#2

Y6

BPM#3

AA5

BPM#4

AB4

BPM#5

D4

TCK

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

AD20

VCCA

A5

VCCSENSE

AE23

VCCIOPLL

AF25

NC7

AF3

NC8

AC26

ITP_CLK0

AD26

ITP_CLK1

L24

COMP0

P1

COMP1

VSS_129F8VSS_130

R67

G21

***

EC_CPUPD#38

B

VSS_92C2VSS_93

VSS_94

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_95C5VSS_96C7VSS_97C9VSS_98

U22

U25

VSS_168

VSS_169U5VSS_170V1VSS_171

D12

D14

D16

D18

D20

D21

D24

E11

E13

E15

E17

E19

E23

E26

F10

F12

F14

F16

F18

F22

F25

F5

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125F2VSS_126

VSS_127

VSS_128

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

PROCHOT#

MCERR#

VSSSENSE

VID0

VID1

VID2

VID3

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

VSS_180

VSS_181

V23

V26

W21

Y5

Y22

Y25

W24

VID4

AE5

AE4

AE3

AE2

AE1

NC5

NC6

AF24

AE21

1K_0402_5%

D

VCCVID

AF4

R324

Layout note :

1. Place R381 and R382 within 0.5" of processor pin F20

2. Place decoupling cap 220PF near CPU.(Within 500mils)

3. GTLREF trace width 7 mils, and keep 10mils separated

from other signals

J26

DP#0

K25

DP#1

K26

DP#2

L25

DP#3

NC1

NC2

GHI#

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

SLP#

VSSA

NC3

NC4

NorthWood

+3VS

1 8

2 7

AA21

AA6

F20

F6

A22

A7

TESTTHI0_1

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

TESTTHI8_10

U6

W4

Y3

GHI#

A6

H_DSTBN#0

E22

H_DSTBN#1

K22

H_DSTBN#2

R22

H_DSTBN#3

W22

H_DSTBP#0

F21

H_DSTBP#1

J23

H_DSTBP#2

P23

H_DSTBP#3

W23

L5

R5

H_DBI#0

E21

H_DBI#1

G25

H_DBI#2

P26

H_DBI#3

V21

AE25

H_PROCHOT#

C3

V6

AB26

H_VSSA

AD22

A4

AD2

AD3

+1.2VP

C24

0.1U_0402_16V4Z

1K_8P4R_0804_5%

RP118

3 6

4 5

+GTLREF

220P_0402_25V8K

H_CPUSLP#

TP2

Title

Size Docu ment Number Re v

Custom

Date: Sheet

2/3VCORE

C544

R36 56_0402_5%

R40 56_0402_5%

R351 56_0402_5%

R352 56_0402_5%

R39 56_0402_5%

R45 56_0402_5%

R350 56_0402_5%

R349 56_0402_5%

R359 56_0402_5%

R357 56_0402_5%

R49 56_0402_5%

H_DSTBN#[0..3]

H_DSTBP#[0..3]

H_DBI#[0..3]

1U_0603_10V6K

**

R546

200_0402_5%

C149

TP1 and TP2 must have test points

@0_0402_5%

CPU Voltage ID

CPU_VID0 48

CPU_VID1 48

CPU_VID2 48

CPU_VID3 48

CPU_VID4 48

Compal Electronics, inc.

SCH EMATIC, M/B LA-1691

401241

星期二 一月

07, 2003

+CPU_CORE

R378

49.9_0402_1%

R381

100_0402_1%

R79

300_0402_5%

H_DSTBN#[0..3] 7

H_DSTBP#[0..3] 7

H_ADSTB#0 7

H_ADSTB#1 7

H_DBI# [0 ..3 ] 7

+CPU_CORE

R78

56_0402_5%

H_CPUSLP# 20

+CPU_CORE

TP1

R86

E

+CPU_CORE

PM_CPUPERF# 20

TP2

R83

@0_0402_5%

553,

1A

of

Page 6

A

B

C

D

E

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

1 1

Please place these cap in the socket cavity area

+CPU_CORE

C70

10U_1206_6.3V6M

+CPU_CORE

C151

10U_1206_6.3V6M

Please place these cap on the socket north side

+CPU_CORE

2 2

+CPU_CORE

+CPU_CORE

C34

10U_1206_6.3V6M

C42

10U_1206_6.3V6M

C25

10U_1206_6.3V6M

C69

10U_1206_6.3V6M

C150

10U_1206_6.3V6M

C33

10U_1206_6.3V6M

C36

10U_1206_6.3V6M

C15

10U_1206_6.3V6M

C68

10U_1206_6.3V6M

C540

10U_1206_6.3V6M

C32

10U_1206_6.3V6M

C26

10U_1206_6.3V6M

C13

10U_1206_6.3V6M

C67

10U_1206_6.3V6M

C148

10U_1206_6.3V6M

C31

10U_1206_6.3V6M

C16

10U_1206_6.3V6M

C6

10U_1206_6.3V6M

C66

10U_1206_6.3V6M

C147

10U_1206_6.3V6M

C30

10U_1206_6.3V6M

C14

10U_1206_6.3V6M

0.22U_0603_16V7K_V1

0.22U_0603_16V7K_V1

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

+CPU_CORE

12

C153

+

220UF_D2_4V_25m

+CPU_CORE

12

C155

+

220UF_D2_4V_25m

+CPU_CORE

C144

0.22U_0603_16V7K_V1

+CPU_CORE

C511

0.22U_0603_16V7K_V1

Used ESR 25m ohm cap total ESR=2.5m ohm

12

C128

+

220UF_D2_4V_25m

12

C140

+

220UF_D2_4V_25m

C122

C530

12

C103

+

220UF_D2_4V_25m

12

C106

+

220UF_D2_4V_25m

0.22U_0603_16V7K_V1

0.22U_0603_16V7K_V1

C75

C541

12

C80

+

220UF_D2_4V_25m

12

C84

+

220UF_D2_4V_25m

0.22U_0603_16V7K_V1

0.22U_0603_16V7K_V1

C74

C510

12

C53

+

220UF_D2_4V_25m

12

C54

+

220UF_D2_4V_25m

0.22U_0603_16V7K_V1

0.22U_0603_16V7K_V1

C512

C509

Please place these cap on the socket south side

3 3

4 4

+CPU_CORE

+CPU_CORE

+CPU_CORE

C208

10U_1206_6.3V6M

C183

10U_1206_6.3V6M

C173

10U_1206_6.3V6M

A

C199

10U_1206_6.3V6M

C191

10U_1206_6.3V6M

C174

10U_1206_6.3V6M

C187

10U_1206_6.3V6M

C158

10U_1206_6.3V6M

C160

10U_1206_6.3V6M

C179

10U_1206_6.3V6M

C163

10U_1206_6.3V6M

C170

10U_1206_6.3V6M

B

C178

10U_1206_6.3V6M

C175

10U_1206_6.3V6M

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Compal Electronics, inc.

Title

SCH EMATIC, M/B LA-1691

Size Docu ment Number Re v

Custom

401241

Date: Sheet

星期二 一月

07, 2003

E

of

653,

1A

Page 7

A

3

B

C

D

E

HD#[0..63]

+V_MCH_GTLREF

GTL Reference Vol tage

Layout note :

1. Place R_E and R_F near MCH

2. Place decoupling cap 220PF near MCH pin.(Within

500mils )

C50

.01UF

C19

.01UF

A

HA#[3..31]

HREQ#[0..4]

H_DBI#[0..3]

R37

24.9_0603_1%

+1.5VS

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

CLK_GHT

CLK_GHT#

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_SWNG0

H_SWNG1

12

R59 8.2K

R33 8.2K

R317 8.2K

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

AE17

AD15

AD13

AC13

12

R35

24.9_0603_1%

12

12

12

U33A

T4

T5

T3

U3

R3

P7

R2

P4

R6

P5

P3

N2

N7

N3

K4

M4

M3

L3

L5

K3

J2

M5

J3

L2

H4

N5

G2

M6

L7

R5

N6

U7

Y4

Y7

W5

J27

H26

V5

V4

Y5

Y3

V7

V3

W3

W2

W7

W6

U6

T7

R7

U5

U2

J8

K8

AD5

AG4

AH9

AA7

AC2

AGP_ADSTB0

AGP_ADSTB1

AGP_SBSTB

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HADSTB#0

HADSTB#1

CPURST#

HTRDY#

DEFER#

BPRI#

HLOCK#

RSTIN#

TESTIN#

DBSY#

DRDY#

HIT#

HITM#

BREQ#0

ADS#

BNR#

RS#0

RS#1

RS#2

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

BCLK

BCLK#

DBI#0

DBI#1

DBI#2

DBI#3

HSWNG0

HSWNG1

HRCOMP0

HRCOMP1

H_DSTBN#[0..3]

H_DSTBP#[0..3]

HOST

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

BROOKDALE(MCH-M)

H_DSTBN#[0..3] 5

H_DSTBP#[0..3] 5

R54 @8.2K

R34 @8.2K

R318 @8.2K

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AD7

AC7

AC6

AC3

AC8

AE2

AG5

AG2

AE8

AF6

AH2

AF3

AG3

AE5

AH7

AH3

AF4

AG8

AG7

AG6

AF8

AH5

AC11

AC12

AE9

AC9

AE10

AD9

AG9

AC10

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

AD4

AE6

AE11

AC15

AD3

AE7

AD11

AC16

M7

R8

Y8

AB11

AB17

12

12

12

B

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

AGP_ADSTB0#

AGP_ADSTB1#

AGP_SBSTB#

HA#[3..31]4

1 1

H_ADSTB#05

H_ADSTB#15

H_CPURST#5

H_TRDY#5

HREQ#[0 ..4 ]4

CLK_MCH_BCLK13

CLK_MCH_BCLK#13

+CPU_CORE

12

R44

12

R51

+CPU_CORE

12

R17

12

R18

H_DEFER#4

H_BREQ0#4

H_DBI#[0..3]5

H_BPRI#4

H_LOCK#4

PCIRST#

H_DBSY#5

H_DRDY#5

H_HIT#4

H_HITM#4

H_ADS#4

H_BNR#4

H_RS#05

H_RS#15

H_RS#25

12

12

2 2

,24,25,26,28,30,32,37,38

3 3

301_1%_0603

150_1%_0603

301_1%_0603

4 4

150_1%_0603

HD#[0 ..6 3 ] 4

AGP_AD[0..31]14

AGP_C/BE#[0..3]14

AGP_ST[0..2]14

+CPU_CORE

12

R42

R_E

49.9_1%_0603

12

R43

R_F

100_1%_0603

AGP_ST0

0=System memory is DDR

1=System memory is SDR

AGP_AD[0..31] HUB_PD[0..10]

AGP_ADSTB014

F_AGP_ADSTB0#14

AGP_ADSTB114

F_AGP_ADSTB1#14

AGP_SBSTB14

F_AGP_SBSTB#14

AGP_FRAME#14

AGP_DEVSEL#14

AGP_IRDY#14

AGP_TRDY#14

AGP_STOP#14

AGP_PAR14

AGP_REQ#14

AGP_GNT#14

Trace

width>=7mila

C57

C55

1UF_0603

220PF

AGP_ST0 AGP_ST1

R313 2K

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

12

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_ST0

AGP_ST1

AGP_ST2

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_SBSTB

AGP_SBSTB#

AGP_FRAME#

AGP_DEVSEL#

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_PAR

AGP_REQ#

AGP_GNT#

AGP_PIPE#

U33B

R27

R28

T25

R25

T26

T27

U27

U28

V26

V27

T23

U23

T24

U24

U25

V24

Y27

Y26

AA28

AB25

AB27

AA27

AB26

Y23

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

V25

V23

Y25

AA23

AG25

AF24

AG26

R24

R23

AC27

AC28

AF27

AF26

Y24

W28

W27

W24

W23

W25

AG24

AH25

AF22

N22

K27

K5

L24

M23

K7

J26

A3

A7

A11

A15

12

R316 @8.2K

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE#0

G_C/BE#1

G_C/BE#2

G_C/BE#3

ST0

ST1

ST2

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

SB_STB

SB_STB#

G_FRAME#

G_DEVSEL#

G_IRDY#

G_TRDY#

G_STOP#

G_PAR

G_REQ#

G_GNT#

PIPE#

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

AGP_FRAME#

AGP_TRDY#

AGP_PAR

AGP_STOP#

AGP_GNT#

AGP_REQ#

AGP_IRDY#

AGP_DEVSEL#

AGP_WBF#

AGP_PIPE#

AGP_RBF#

AGP_ST2

HUB

HLRCOMP

AGP

GRCOMP

BROOKDALE(MCH-M)

RP121 @8P4R_8.2K

1 8

2 7

3 6

4 5

RP120 @8P4R_8.2K

1 8

2 7

3 6

4 5

RP119 @8P4R_8.2K

1 8

2 7

3 6

4 5

12

R311 8 .2K

12

R312 8 .2K

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HI_7

HI_8

HI_9

HI_10

HI_STB

HI_STB#

HI_REF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

AGPREF

66IN

RBF#

WBF#

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

+1.5VS

D

P25

P24

N27

P23

M26

M25

L28

L27

M27

N28

M24

N25

N24

P27

P26

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AA21

AD25

P22

AE22

AE23

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J29

AGP_ST1

0=533Mhz

1=400Mhz

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HLRCOMP

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

R20 36.5_1%_0603

CLK_MCH_66M

AGP_RBF#

AGP_WBF#

+AGP_REF

HUB_PD[0..10] 20

HUB_PSTRB 20

HUB_PSTRB# 20

1 2

R368 36.5_1%_0603

AGP_SBA[0..7]

Place this cap near MCH

+AGP_REF

12

CLK_MCH_66M 13

AGP_RBF# 14

301_1%_0603

301_1%_0603

Compal Electronics, inc.

Title

Size Docu ment Number Re v

Date: Sheet

星期二 一月

AGP_SBA[0..7] 14

12

C52

.1UF

+1.5VS

12

R346

1K_1%_0603

12

R340

1K_1%_0603

HUB Interface Reference

Layout note :

+1.8VS

1. Pla c e R_C and R_D in middle of Bus.

2. Place capacitors near MCH.

12

R428

R_C

12

R429

R_D

SCHEMATIC, M/B LA-1691

401241

07, 2003

+1.8VS

12

C504

.1UF

12

C533

@470PF_0603

12

R376

@56.2_1%_0603

12

R64

0

12

C94

.01UF

E

+VS_HUBREF

12

C97

.01UF

Place closely

ball P26

Place closely pin P22

CLK_MCH_66M

R63

@33

1 2

C102

@10PF

+VS_HUBREF

of

753,

1A

Page 8

A

B

C

D

E

U33D

M8

+CPU_CORE

1 1

+2.5V

2 2

3 3

4 4

VTT_0

U8

VTT_1

AA9

VTT_2

AB8

VTT_3

AB18

VTT_4

AB20

VTT_5

AC19

VTT_6

AD18

VTT_7

AD20

VTT_8

AE19

VTT_9

AE21

VTT_10

AF18

VTT_11

AF20

VTT_12

AG19

VTT_13

AG21

VTT_14

AG23

VTT_15

AJ19

VTT_16

AJ21

VTT_17

AJ23

VTT_18

A5

VCCSM1

A9

VCCSM2

A13

VCCSM3

A17

VCCSM4

A21

VCCSM5

A25

VCCSM6

C1

VCCSM7

C29

VCCSM8

D7

VCCSM9

D11

VCCSM10

D15

VCCSM11

D19

VCCSM12

D23

VCCSM13

D25

VCCSM14

F6

VCCSM15

F10

VCCSM16

F14

VCCSM17

F18

VCCSM18

F22

VCCSM19

G1

VCCSM20

G4

VCCSM21

G29

VCCSM22

H8

VCCSM23

H10

VCCSM24

H12

VCCSM25

H14

VCCSM26

H16

VCCSM27

H18

VCCSM28

H20

VCCSM29

H22

VCCSM30

H24

VCCSM31

K22

VCCSM32

K24

VCCSM33

K26

VCCSM34

L23

VCCSM35

K6

VCCSM36

J5

VCCSM37

J7

VCCSM38

L1

VSS41

L4

VSS42

L6

VSS43

L8

VSS44

L22

VSS45

L26

VSS46

N1

VSS47

N4

VSS48

N8

VSS49

N13

VSS50

N15

VSS51

N17

VSS52

N29

VSS53

P6

VSS54

P8

VSS55

P14

VSS56

P16

VSS57

R1

VSS58

R4

VSS59

R13

VSS60

R15

VSS61

R17

VSS62

R26

VSS63

T6

VSS64

T8

VSS65

T14

VSS66

T16

VSS67

T22

VSS68

U1

VSS69

U4

VSS70

U15

VSS71

U29

VSS72

V6

VSS73

V8

VSS74

V22

VSS75

W1

VSS76

W4

VSS77

W8

VSS78

W26

VSS79

Y6

VSS80

Y22

VSS81

AA1

VSS82

BROOKDALE(MCH-M)

POWER/GND

VCC1_5_0

VCC1_5_1

VCC1_5_2

VCC1_5_3

VCC1_5_4

VCC1_5_5

VCC1_5_6

VCC1_5_7

VCC1_5_8

VCC1_5_9

VCC1_5_10

VCC1_5_11

VCC1_5_12

VCC1_5_13

VCC1_5_14

VCC1_5_15

VCC1_5_16

VCC1_5_17

VCC1_5_18

VCC1_5_19

VCC1_5_20

VCC1_5_21

VCC1_5_22

VCC1_5_23

VCC1_5_24

VCC1_5_25

VCC1_8_0

VCC1_8_1

VCC1_8_2

VCC1_8_3

VCC1_8_4

VCCGA1

VCCHA1

VSSGA2

VSSHA2

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

R22

R29

U22

U26

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

L29

N26

L25

M22

N23

T17

T13

U17

U13

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ3

AJ5

AJ7

AJ9

AJ11

AJ13

AJ15

AJ17

AJ27

VCC_MCH_PLL1

VCC_MCH_PLL0

VSS_MCH_PLL1

VSS_MCH_PLL0

+1.5VS

+1.5VS

+1.8VS

"Trace A"

"Trace A"

12

L10

4.7UH_30mA

"Trace A"

12

C96

+

33UF_D2_16V

"Trace A"

Layout note :

Trace width 5mil ; Spacing 10mil

Trace A to ball U7/T13 or U7/T7 =1.5" Max

12

L7

4.7UH_30mA

12

C95

+

33UF_D2_16V

Murata

LQG21N4R7K10

DDR_SDQ[0..63]10

DDR_SDQ[0..63]

DDR_SDQ0

DDR_SDQ1

DDR_SDQ2

DDR_SDQ3

DDR_SDQ4

DDR_SDQ5

DDR_SDQ6

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ10

DDR_SDQ11

DDR_SDQ12

DDR_SDQ13

DDR_SDQ14

DDR_SDQ15

DDR_SDQ16

DDR_SDQ17

DDR_SDQ18

DDR_SDQ19

DDR_SDQ20

DDR_SDQ21

DDR_SDQ22

DDR_SDQ23

DDR_SDQ24

DDR_SDQ25

DDR_SDQ26

DDR_SDQ27

DDR_SDQ28

DDR_SDQ29

DDR_SDQ30

DDR_SDQ31

DDR_SDQ32

DDR_SDQ33

DDR_SDQ34

DDR_SDQ35

DDR_SDQ36

DDR_SDQ37

DDR_SDQ38

DDR_SDQ39

DDR_SDQ40

DDR_SDQ41

DDR_SDQ42

DDR_SDQ43

DDR_SDQ44

DDR_SDQ45

DDR_SDQ46

DDR_SDQ47

DDR_SDQ48

DDR_SDQ49

DDR_SDQ50

DDR_SDQ51

DDR_SDQ52

DDR_SDQ53

DDR_SDQ54

DDR_SDQ55

DDR_SDQ56

DDR_SDQ57

DDR_SDQ58

DDR_SDQ59

DDR_SDQ60

DDR_SDQ61

DDR_SDQ62

DDR_SDQ63

+SDREF

12

C117

.1UF_0402_X5R

Layout note

Please closely pinJ21 and J9

U33C

G28

SDQ0

F27

SDQ1

C28

SDQ2

E28

SDQ3

H25

SDQ4

G27

SDQ5

F25

SDQ6

B28

SDQ7

E27

SDQ8

C27

SDQ9

B25

SDQ10

C25

SDQ11

B27

SDQ12

D27

SDQ13

D26

SDQ14

E25

SDQ15

D24

SDQ16

E23

SDQ17

C22

SDQ18

E21

SDQ19

C24

SDQ20

B23

SDQ21

D22

SDQ22

B21

SDQ23

C21

SDQ24

D20

SDQ25

C19

SDQ26

D18

SDQ27

C20

SDQ28

E19

SDQ29

C18

SDQ30

E17

SDQ31

E13

SDQ32

C12

SDQ33

B11

SDQ34

C10

SDQ35

B13

SDQ36

C13

SDQ37

C11

SDQ38

D10

SDQ39

E10

SDQ40

C9

SDQ41

D8

SDQ42

E8

SDQ43

E11

SDQ44

B9

SDQ45

B7

SDQ46

C7

SDQ47

C6

SDQ48

D6

SDQ49

D4

SDQ50

B3

SDQ51

E6

SDQ52

B5

SDQ53

C4

SDQ54

E5

SDQ55

C3

SDQ56

D3

SDQ57

F4

SDQ58

F3

SDQ59

B2

SDQ60

C2

SDQ61

E2

SDQ62

G5

SDQ63

C16

SDQ64/CB0

D16

SDQ65/CB1

B15

SDQ66/CB2

C14

SDQ67/CB3

B17

SDQ68/CB4

C17

SDQ69/CB5

C15

SDQ70/CB6

D14

SDQ71/CB7

J21

SDREF0

J9

SDREF1

BROOKDALE(MCH-M)

MEMORY

SMA0/CS#11

SMA1/CS#10

SMA2/CS#6

SMA3/CS#9

SMA4/CS#5

SMA5/CS#8

SMA6/CS#7

SMA7/CS#4

SMA8/CS#3

SMA9/CS#0

SMA11/CS#2

SMA12/CS#1

SMRCOMP

RCVENIN#

RCVENOUT#

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

SCK4

SCK#4

SCK5

SCK#5

SCK6

SCK#6

SCK7

SCK#7

SCK8

SCK#8

SCS#0

SCS#1

SCS#2

SCS#3

SCS#4

SCS#5

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SMA10

SBS0

SBS1

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SSI_ST

SRAS#

SWE#

SCAS#

NC0

NC1

E14

F15

J24

G25

G6

G7

G15

G14

E24

G24

H5

F5

K25

J25

G17

G16

H7

H6

DDR_SCS#0

E9

DDR_SCS#1

F7

DDR_SCS#2

F9

DDR_SCS#3

E7

G9

G10

DDR_SDQS0

F26

DDR_SDQS1

C26

DDR_SDQS2

C23

DDR_SDQS3

B19

DDR_SDQS4

D12

DDR_SDQS5

C8

DDR_SDQS6

C5

DDR_SDQS7

E3

E15

DDR_SMA0

E12

DDR_SMA1

F17

DDR_SMA2

E16

DDR_SMA3

G18

DDR_SMA4

G19

DDR_SMA5

E18

DDR_SMA6

F19

DDR_SMA7

G21

DDR_SMA8

G20

DDR_SMA9

F21

DDR_SMA10

F13

DDR_SMA11

E20

DDR_SMA12

G22

DDR_SBS0

G12

DDR_SBS1

G13

DDR_CKE0

G23

DDR_CKE1

E22

DDR_CKE2

H23

DDR_CKE3

F23

J23

K23

+SM_RCOMP

J28

RCVIN#

G3

RCVOUT#

H3

H27

F11

G11

G8

AD26

AD27

R75

DDR_SRAS#

DDR_SWE#

DDR_SCAS#

Layout note

Place R_J closely Ball H3<40mil,Ball H3 to G3 trace must

routing 1"

R73 30.1_1%

12

0_0402

R_J

DDR_CLK0 10

DDR_CLK0# 10

DDR_CLK1 10

DDR_CLK1# 10

DDR_CLK3 11

DDR_CLK3# 11

DDR_CLK4 11

DDR_CLK4# 11

DDR_SCS#0 10,12

DDR_SCS#1 10,12

DDR_SCS#2 11,12

DDR_SCS#3 11,12

DDR_SDQS0 10

DDR_SDQS1 10

DDR_SDQS2 10

DDR_SDQS3 10

DDR_SDQS4 10

DDR_SDQS5 10

DDR_SDQS6 10

DDR_SDQS7 10

DDR_SMA[0..12]

DDR_SBS0 10,11,12

DDR_SBS1 10,11,12

DDR_CKE0 10,12

DDR_CKE1 10,12

DDR_CKE2 11,12

DDR_CKE3 11,12

12

C120 .1UF_0402_X5R

C146 @47PF

DDR_SRAS# 10,11,12

DDR_SWE# 10,11,12

DDR_SCAS# 10,11,12

DDR_SMA[0..12] 10,11,12

+1.25VS

Layout note

Place R563 closely

pinJ28

Compal Electronics, inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Docu ment Number Re v

Date: Sheet

SCHEMATIC, M/B LA-1691

401241

星期二 一月

07, 2003

E

1A

of

853,

Page 9

5

4

3

2

1

Layout note :

Distr ib ute as cl ose as possib le

to M CH Processor Qu adrant.(b etween VTTFSB and VSS pin)

+CPU_CORE

D D

12

C45

.1UF_0402_X5R

+CPU_CORE

12

C108

.1UF_0402_X5R

+CPU_CORE

12

C9

10UF_6.3V_1206_X5R

C C

Layout note :

Distr ib ute as cl ose as possib le

to MCH Processor Quadrant.(between VCCAGP/VCCCORE

and VSS pin)

Processor system bus

12

C46

.1UF_0402_X5R

12

C51

.1UF_0402_X5R

12

C8

10UF_6.3V_1206_X5R

12

C28

.1UF_0402_X5R

12

C18

.1UF_0402_X5R

AGP/CORE

12

C27

.1UF_0402_X5R

12

C17

.1UF_0402_X5R

12

C10

10UF_6.3V_1206_X5R

12

C47

.1UF_0402_X5R

12

C20

.1UF_0402_X5R

Layout note :

Distr ib ute as cl ose as possib le

to MCH Processor Quadrant.(between VCCSM and VSS pin)

+2.5V

12

C113

.1UF_0402_X5R

+2.5V

12

C116

.1UF_0402_X5R

+2.5V

12

C145

.1UF_0402_X5R

+2.5V

12

C181

+

150UF_D2_6.3V

DDR Memory interface

12

C126

.1UF_0402_X5R

12

C131

.1UF_0402_X5R

12

C161

.1UF_0402_X5R

12

C127

.1UF_0402_X5R

12

C121

.1UF_0402_X5R

12

C129

.1UF_0402_X5R

12

C156

.1UF_0402_X5R

12

C152

.1UF_0402_X5R

12

C130

.1UF_0402_X5R

12

C119

.1UF_0402_X5R

12

C142

.1UF_0402_X5R

12

C162

.1UF_0402_X5R

12

C124

22UF_10V_1206

12

C123

22UF_10V_1206

+1.5VS

12

C101

.1UF_0402_X5R

B B

+1.5VS

12

C11

10UF_6.3V_1206_X5R

Layout note :

Distr ib ute as cl ose as possib le

to MC H P roce ssor Quadrant.(between VCCHL and VSS pin)

+1.8VS

A A

12

C546

10UF_6.3V_1206_X5R

12

C111

.1UF_0402_X5R

12

C12

10UF_6.3V_1206_X5R

Hub-Link

12

C109

.1UF_0402_X5R

5

12

C93

.1UF_0402_X5R

12

C114

.1UF_0402_X5R

12

C23

+

150UF_D2_6.3V

12

12

C78

.1UF_0402_X5R

C110

.1UF_0402_X5R

12

C49

.1UF_0402_X5R

4

12

C71

.1UF_0402_X5R

Compal Electronics, inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Title

Size Doc u men t Numbe r R e v

Dat e : Sheet

SCH E MATIC, M/B LA-1691

401241

期二 一月

1

1A

of

953¬P , 07, 2003

Page 10

5

4

3

2

1

+2.5V

JP22

1

VREF

3

DDR_DQ0

DDR_DQ1

DDR_DQS0

D D

DDR_CLK08

DDR_CLK0#8

C C

DDR_SCS#08,12 DDR_SCS#1 8,12

B B

SMB_DATA11,13,20,22

SMB_CLK11,13,20,22

A A

DDR_DQ6

DDR_DQ7

DDR_DQ12

DDR_DQ15

DDR_DQS1

DDR_DQ14

DDR_DQ11

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ21

DDR_DQ23

DDR_DQ28

DDR_DQ26

DDR_DQS3

DDR_DQ27

DDR_DQ29

DDR_F_SMA12

DDR_F_SMA9

DDR_F_SMA7

DDR_F_SMA3

DDR_F_SMA1

DDR_F_SMA10

DDR_F_SBS0

DDR_F_SWE#

DDR_SCS#0 DDR_SCS#1

DDR_DQ38

DDR_DQ37

DDR_DQS4

DDR_DQ35

DDR_DQ34

DDR_DQ40

DDR_DQ46

DDR_DQS5

DDR_DQ41

DDR_DQ42

DDR_DQ53

DDR_DQ55

DDR_DQS6

DDR_DQ50

DDR_DQ54

DDR_DQ57

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ62

SMB_DATA

SMB_CLK

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

AMP1376408_STANDARD

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

VSS

VDD

BA1

RAS#

CAS#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

A11

A8

A6

A4

A2

A0

S1#

DU

DU

DIMM0

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DDR_DQ4

DDR_DQ5

DDR_DQ3

DDR_DQ2

DDR_DQ9

DDR_DQ13

DDR_DQ10

DDR_DQ8

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ22

DDR_DQ25

DDR_DQ24

DDR_DQ31

DDR_DQ30

DDR_CKE0DDR_CKE1

DDR_F_SMA11

DDR_F_SMA8

DDR_F_SMA6

DDR_F_SMA4DDR_F_SMA5

DDR_F_SMA2

DDR_F_SMA0

DDR_F_SBS1

DDR_F_SRAS#

DDR_F_SCAS#

DDR_DQ32

DDR_DQ33

DDR_DQ36

DDR_DQ39

DDR_DQ45

DDR_DQ44

DDR_DQ47

DDR_DQ43

DDR_DQ49

DDR_DQ52

DDR_DQ51

DDR_DQ48

DDR_DQ56

DDR_DQ60

DDR_DQ61

DDR_DQ63

+SDREF_R

C241

0.1U_0402_16V4Z

DDR_CKE0 8,12DDR_CKE18,12

DDR_CLK1# 8

DDR_CLK1 8

L17

1 2

MurataBLM21A601S_0805

DDR_SDQ0 DDR_DQ0

DDR_SDQ1 DDR_DQ1

DDR_SDQ6 DDR_DQ6

DDR_SDQ7 DDR_DQ7

DDR_SDQ14 DDR_DQ14

DDR_SDQ11 DDR_DQ11

DDR_SDQ16

DDR_SDQ21 DDR_DQ21

DDR_SDQ26 DDR_DQ26

DDR_SDQ29 DDR_DQ29

DDR_SDQ37

DDR_SDQ34

DDR_SDQ40 DDR_DQ40

DDR_SDQ41 DDR_DQ41

DDR_SDQ42 DDR_DQ42

DDR_SDQ53 DDR_DQ53

DDR_SDQ55 DDR_DQ55

DDR_SDQ50 DDR_DQ50

DDR_SDQ54 DDR_DQ54

DDR_SDQ58 DDR_DQ58

DDR_SDQ62

+SDREF

RP50 4P2R_10

1 4

2 3

RP49 4P2R_10

1 4

2 3

RP48 4P2R_10

1 4

2 3

RP47 4P2R_10

1 4

2 3

RP46 4P2R_10

1 4

2 3

RP45 4P2R_10

1 4

2 3

RP44 4P2R_10

1 4

2 3

RP43 4P2R_10

1 4

2 3

RP39 4P2R_10

1 4

2 3

RP38 4P2R_10

1 4

2 3

RP37 4P2R_10

1 4

2 3

RP36 4P2R_10

1 4

2 3

RP35 4P2R_10

1 4

2 3

RP34 4P2R_10

1 4

2 3

RP33 4P2R_10

1 4

2 3

RP32 4P2R_10

1 4

2 3

DDR_DQ12DDR_SDQ12

DDR_DQ15DDR_SDQ15

DDR_DQ20DDR_SDQ20

DDR_DQ16

DDR_DQ23DDR_SDQ23

DDR_DQ28DDR_SDQ28

DDR_DQ27DDR_SDQ27

DDR_DQ38DDR_SDQ38

DDR_DQ37

DDR_DQ35DDR_SDQ35

DDR_DQ34

DDR_DQ46DDR_SDQ46

DDR_DQ57DDR_SDQ57

DDR_DQ59DDR_SDQ59

DDR_SDQ4 DDR_DQ4

DDR_SDQ5 DDR_DQ5

DDR_SDQ2

DDR_SDQ13 DDR_DQ13

DDR_SDQ10 DDR_DQ10

DDR_SDQ8 DDR_DQ8

DDR_SDQ17 DDR_DQ17

DDR_SDQ18

DDR_SDQ22

DDR_SDQ25 DDR_DQ25

DDR_SDQ24

DDR_SDQ33

DDR_SDQ36 DDR_DQ36

DDR_SDQ39 DDR_DQ39

DDR_SDQ47 DDR_DQ47

DDR_SDQ56 DDR_DQ56

DDR_SDQ60 DDR_DQ60

DDR_SDQ61

DDR_SDQ63

RP27 4P2R_10

1 4

2 3

RP26 4P2R_10

1 4

2 3

RP25 4P2R_10

1 4

2 3

RP24 4P2R_10

1 4

2 3

RP23 4P2R_10

1 4

2 3

RP22 4P2R_10

1 4

2 3

RP21 4P2R_10

1 4

2 3

RP20 4P2R_10

DDR_SDQ31 DDR_DQ31

1 4

DDR_SDQ30

2 3

RP16 4P2R_10

1 4

2 3

RP15 4P2R_10

1 4

2 3

RP14 4P2R_10

1 4

2 3

RP13 4P2R_10

1 4

2 3

RP12 4P2R_10

1 4

2 3

RP11 4P2R_10

1 4

2 3

RP10 4P2R_10

1 4

2 3

RP9 4P2R_10

1 4

2 3

DDR_DQ3DDR_SDQ3

DDR_DQ2

DDR_DQ9DDR_SDQ9

DDR_DQ18

DDR_DQ19DDR_SDQ19

DDR_DQ22

DDR_DQ24

DDR_DQ30

DDR_DQ32DDR_SDQ32

DDR_DQ33

DDR_DQ45DDR_SDQ45

DDR_DQ44DDR_SDQ44

DDR_DQ43DDR_SDQ43

DDR_DQ49DDR_SDQ49

DDR_DQ52DDR_SDQ52

DDR_DQ51DDR_SDQ51

DDR_DQ48DDR_SDQ48

DDR_DQ61

DDR_DQ63DDR_DQ62

DDR_SRAS#8,11,12

DDR_SCAS#8,11,12

DDR_SWE#8,11,12

DDR_SMA10 DDR_F_SMA10

DDR_SBS1 DDR_F_SBS1

DDR_SMA8

DDR_SMA0 DDR_F_SMA0

DDR_SBS0 DDR_F_SBS0

DDR_SMA12 DDR_F_SMA12

DDR_SMA11

DDR_SCAS# DDR_F_SCAS#

DDR_SWE# DDR_F_SWE#

DDR_SMA2 DDR_F_SMA2

DDR _ S DQS[0..7]

DDR_SMA[0..12]

DDR_SDQS1 DDR_DQS1

DDR_SDQS2 DDR_DQS2

DDR_SDQS3 DDR_DQS3

DDR_SDQS4 DDR_DQS4

RP18 4P2R_10

1 4

2 3

RP31 4P2R_10

1 4

2 3

RP41 4P2R_10

1 4

2 3

RP40 4P2R_10

1 4

2 3

RP29 4P2R_10

1 4

2 3

RP28 4P2R_10

1 4

2 3

RP17 4P2R_10

1 4

2 3

RP19 4P2R_10

1 4

2 3

RP42 4P2R_10

1 4

2 3

DDR_SDQ[0..63]

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_SBS[0..1]

R151 10_0402_5%

R150 10_0402_5%

R149 10_0402_5%

R148 10_0402_5%

R147 10_0402_5%

R146 10_0402_5%

R145 10_0402_5%

R144 10_0402_5%

DDR_F_SMA9DDR_SMA9

DDR_F_SMA8

DDR_F_SMA3DDR_SMA3

DDR_F_SRAS#DDR_SRAS#

DDR_F_SMA11

DDR_F_SMA7DDR_SMA7

DDR_F_SMA6DDR_SMA6

DDR_F_SMA1DDR_SMA1

DDR_F_SMA4DDR_SMA4

DDR_F_SMA5DDR_SMA5

DDR_SDQ[0..63] 8

DDR_DQ[0..63] 11,12

DDR_DQS[0..7] 11,12

DDR_SDQS[0..7] 8

DDR_SMA[0..12] 8,11,12

DDR_SBS[0..1] 8,11,12

DDR_DQS0DDR_SDQS0

DDR_DQS5DDR_SDQS5

DDR_DQS6DDR_SDQS6

DDR_DQS7DDR_SDQS7

Bottom Side

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

SCH EMATIC, M/B LA-1691

Size Docu ment Number Re v

Custom

401241

Date: Sheet

星期二 一月

07, 2003

1

of

10 53,

1A

Page 11

5

DDR_DQ0

DDR_DQ1

DDR_DQS0

DDR_DQ6

DDR_DQ7

D D

DDR_CLK38

DDR_CLK3#8

C C

DDR_CKE38,12

DDR_SBS08,10,12

DDR_SWE#8,10,12

DDR_SCS#28,12 DDR_SCS#3 8,12

B B

SMB_DATA10,13,20,22

SMB_CLK10,13,20,22

A A

DDR_DQ12

DDR_DQ15

DDR_DQS1

DDR_DQ14

DDR_DQ11

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ21

DDR_DQ23

DDR_DQ28

DDR_DQ26

DDR_DQS3

DDR_DQ27

DDR_DQ29

DDR_CKE3

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SBS0

DDR_SWE#

DDR_SCS#2 DDR_SCS#3

DDR_DQ38

DDR_DQ37

DDR_DQS4

DDR_DQ35

DDR_DQ34

DDR_DQ40

DDR_DQ46

DDR_DQS5

DDR_DQ41

DDR_DQ42

DDR_DQ53

DDR_DQ55

DDR_DQS6

DDR_DQ50

DDR_DQ54

DDR_DQ57

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ62

+3VS

+2.5V

4

JP24

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

VREF

VSS

DQ0

DQ1

VDD

DQS0

DQ2

VSS

DQ3

DQ8

VDD

DQ9

DQS1

VSS

DQ10

DQ11

VDD

CK0

CK0#

VSS

DQ16

DQ17

VDD

DQS2

DQ18

VSS

DQ19

DQ24

VDD

DQ25

DQS3

VSS

DQ26

DQ27

VDD

CB0

CB1

VSS

DQS8

CB2

VDD

CB3

DU

VSS

CK2

CK2#

VDD

CKE1

DU/A13

A12

A9

VSS

A7

A5

A3

A1

VDD

A10/AP

BA0

WE#

S0#

DU

VSS

DQ32

DQ33

VDD

DQS4

DQ34

VSS

DQ35

DQ40

VDD

DQ41

DQS5

VSS

DQ42

DQ43

VDD

VDD

VSS

VSS

DQ48

DQ49

VDD

DQS6

DQ50

VSS

DQ51

DQ56

VDD

DQ57

DQS7

VSS

DQ58

DQ59

VDD

SDA

SCL

VDD_SPD

VDD_ID

AMP1376408_REVERSE

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

VSS

VDD

BA1

RAS#

CAS#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

+2.5V

3

DDR_DQ4

DDR_DQ5

DDR_DQ3

DDR_DQ2

DDR_DQ9

DDR_DQ13

DDR_DQ10

DDR_DQ8

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ22

DDR_DQ25

DDR_DQ24

DDR_DQ31

DDR_DQ30

DDR_CKE2

DDR_SMA11

DDR_SMA8

DDR_SMA6

DDR_SMA4DDR_SMA5

DDR_SMA2

DDR_SMA0

DDR_SBS1

DDR_SRAS#

DDR_SCAS#

DDR_DQ32

DDR_DQ33

DDR_DQ36

DDR_DQ39

DDR_DQ45

DDR_DQ44

DDR_DQ47

DDR_DQ43

DDR_DQ49

DDR_DQ52

DDR_DQ51

DDR_DQ48

DDR_DQ56

DDR_DQ60

DDR_DQ61

DDR_DQ63

+SDREF_R

1 2

C264

MurataBLM21A601S_0805

0.1U_0402_16V4Z

DDR_CKE2 8,12

DDR_SBS1 8,10,12

DDR_SRAS# 8,10,12

DDR_SCAS# 8,10,12

DDR_CLK4# 8

DDR_CLK4 8

+3VS

2

L19

+SDREF

DDR_DQ[0..63]

DDR_SMA[0..12]

DDR_DQS[0..7]

DDR_CKE[0..3]

DDR_DQ[0..63] 10,12

DDR_SMA[0..12] 8,10,12

DDR_DQS[0..7] 10,12

DDR_CKE[0..3] 8,10,12

1

DIMM1

Bottom Side

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

SCH EMATIC, M/B LA-1691

Size Docu ment Number Re v

Custom

401241

Date: Sheet

星期二 一月

07, 2003

1

of

11 53,

1A

Page 12

A

B

C

D

E

+1.25VS

RP104 4P2R_56

DDR_DQ0

1 4

DDR_DQ1

2 3

RP81 4P2R_56

DDR_DQ2

1 4