Page 1

查询HCNW2601供应商

HCMOS Compatible, High CMR,

10 MBd Optocouplers

Technical Data

H

HCPL-261A HCPL-061A

HCPL-263A HCPL-063A

HCPL-261N HCPL-061N

HCPL-263N HCPL-063N

Features

• HCMOS/LSTTL/TTL

Performance Compatible

• 1000 V/µs Minimum

Common Mode Rejection

(CMR) at VCM = 50 V (HCPL261A Family) and 15 kV/µs

Minimum CMR at VCM =

1000 V (HCPL-261N Family)

• High Speed: 10 MBd Typical

• AC and DC Performance

Specified over Industrial

Temperature Range -40°C to

+85°C

• Available in 8 Pin DIP,

SOIC-8 Packages

• Safety Approval

UL Recognized per UL1577

2500 V rms for 1 minute and

5000 V rms for 1 minute

(Option 020)

CSA Approved

VDE 0884 Approved with

V

= 630 V peak for

IORM

HCPL-261A/261N

Option 060

• Computer-Peripheral

Interface

• Digital Isolation for A/D,

D/A Conversion

• Switching Power Supplies

• Instrumentation

Input/Output Isolation

• Ground Loop Elimination

• Pulse Transformer

Replacement

Description

The HCPL-261A family of optically

coupled gates shown on this data

sheet provide all the benefits of the

industry standard 6N137 family

with the added benefit of HCMOS

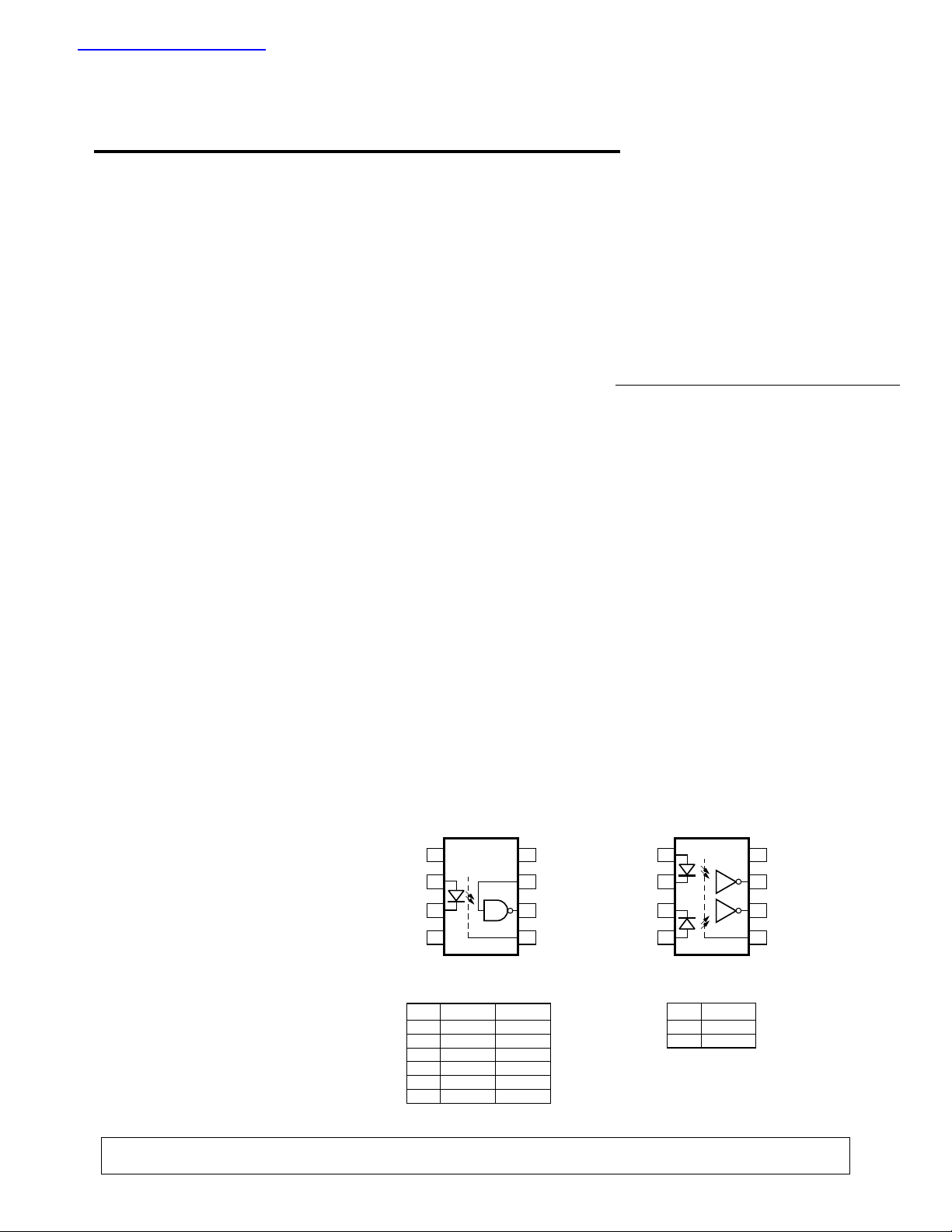

Functional Diagram

HCPL-261A/261N

HCPL-061A/061N

NC

ANODE

CATHODE

NC

1

2

3

4

SHIELD SHIELD

V

8

CC

V

7

E

V

6

O

GND

5

compatible input current. This

allows direct interface to all

common circuit topologies without

additional LED buffer or drive

components. The AlGaAs LED

used allows lower drive currents

and reduces degradation by using

the latest LED technology. On the

single channel parts, an enable

output allows the detector to be

strobed. The output of the detector

IC is an open collector schottkyclamped transistor. The internal

shield provides a minimum

common mode transient immunity

of 1000 V/µs for the HCPL-261A

family and 15000 V/µs for the

HCPL-261N family.

ANODE

CATHODE

CATHODE

ANODE

Applications

• Low Input Current (3.0 mA)

HCMOS Compatible Version

of 6N137 Optocoupler

• Isolated Line Receiver

• Simplex/Multiplex Data

Transmission

The connection of a 0.1 µF bypass capacitor between pins 5 and 8 is required.

TRUTH TABLE

(POSITIVE LOGIC)

ENABLE

LED

ON

OFF

ON

OFF

ON

OFF

H

H

L

L

NC

NC

OUTPUT

L

H

H

H

L

H

HCPL-263A/263N

HCPL-063A/063N

1

1

2

1

3

2

4

2

TRUTH TABLE

(POSITIVE LOGIC)

LED

ON

OFF

OUTPUT

L

H

V

8

CC

V

7

O1

V

6

O2

GND

5

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to

prevent damage and/or degradation which may be induced by ESD.

1-166

5965-3593E

Page 2

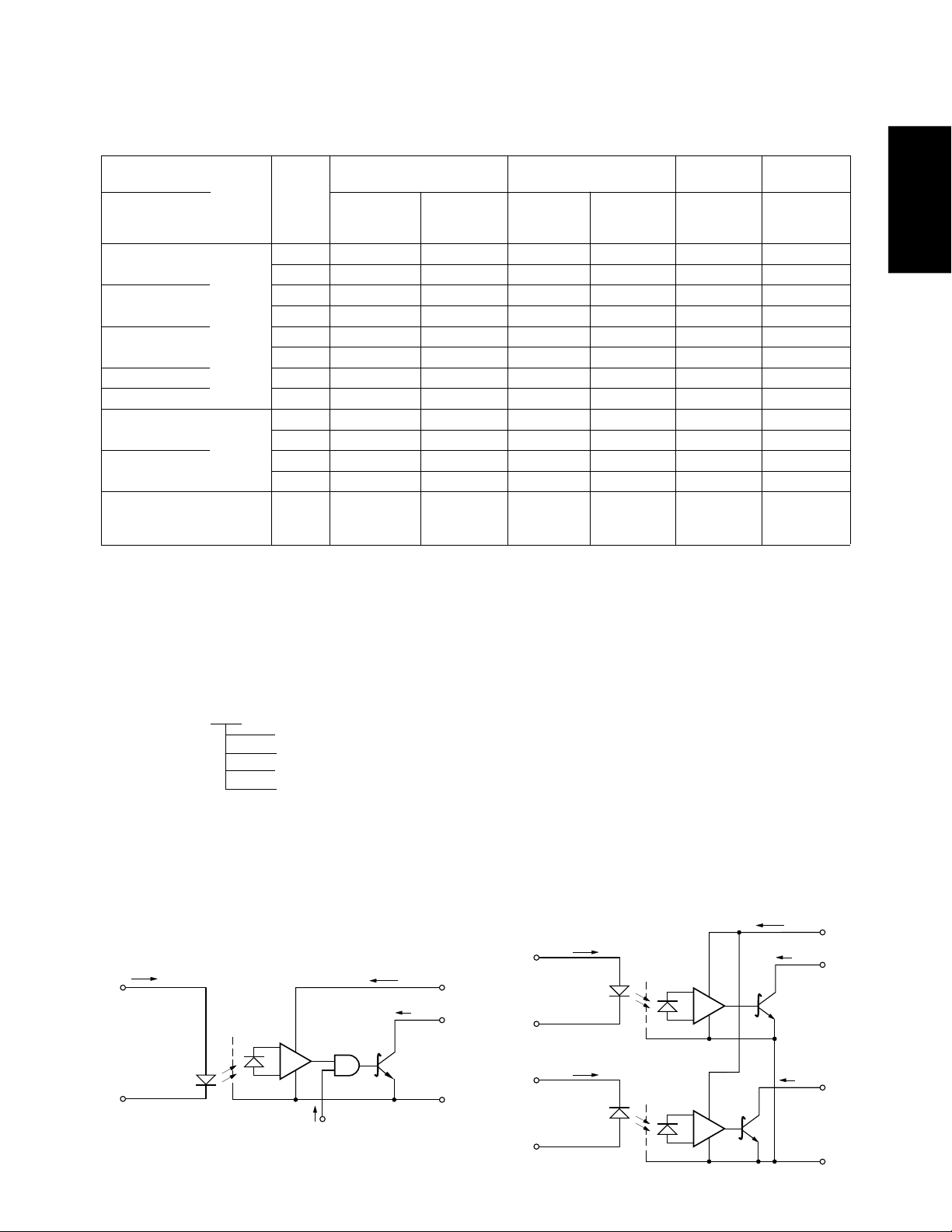

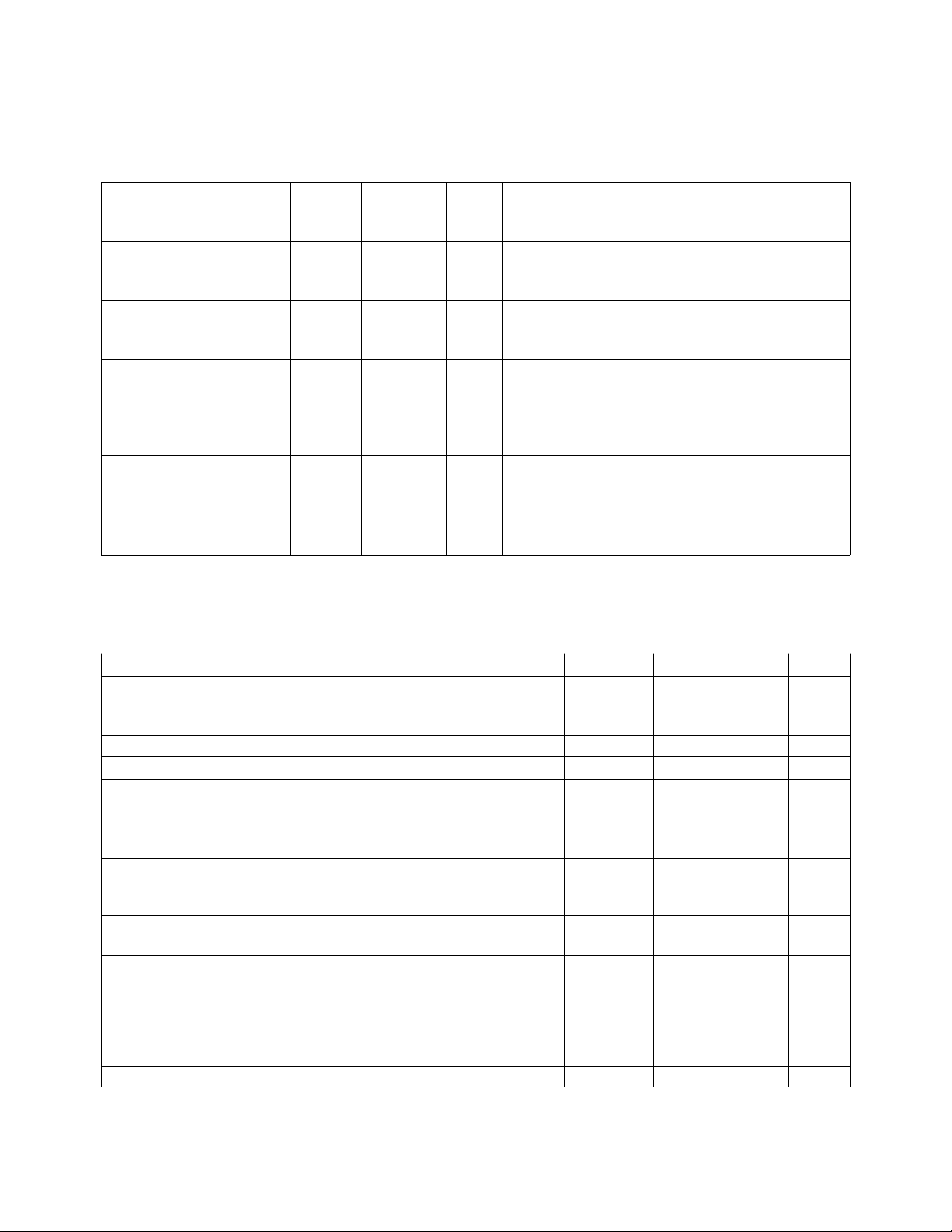

Selection Guide

[1]

HCNW2601

[1]

HCNW2611

[1]

Widebody

HCNW137

[1]

[1]

[1]

HCPL-193X

HCPL-56XX

HCPL-66XX

Minimum CMR 8-Pin DIP (300 Mil) Small-Outline SO-8 (400 Mil) Hermetic

Input

On- Single Dual Single Dual Single Single and

dV/dt V

Current Output Channel Channel Channel Channel Channel Dual Channel

CM

(V/µs) (V) (mA) Enable Package Package Package Package Package Packages

NA NA 5 YES 6N137

[1]

NO HCPL-2630

5,000 50 YES HCPL-2601

NO HCPL-2631

10,000 1,000 YES HCPL-2611

NO HCPL-4661

1,000 50 YES HCPL-2602

3,500 300 YES HCPL-2612

HCPL-0600

[1]

[1]

[1]

[1]

[1]

HCPL-0601

[1]

HCPL-0611

[1]

[1]

HCPL-0630

[1]

HCPL-0631

[1]

HCPL-0661

1,000 50 3 YES HCPL-261A HCPL-061A

NO HCPL-263A HCPL-063A

[2]

1,000

1,000 YES HCPL-261N HCPL-061N

NO HCPL-263N HCPL-063N

1,000 50 12.5

[3]

Notes:

1. Technical data are on separate HP publications.

2. 15 kV/µs with VCM = 1 kV can be achieved using HP application circuit.

3. Enable is available for single channel products only, except for HCPL-193X devices.

OPTOCOUPLERS

[1]

[1]

[1]

Ordering Information

Specify Part Number followed by Option Number (if desired).

Example:

HCPL-261A#XXX

020 = 5000 V rms/1 minute UL Rating Option*

060 = VDE 0884 V

300 = Gull Wing Surface Mount Option***

500 = Tape and Reel Packaging Option

Option data sheets available. Contact your Hewlett-Packard sales representative or authorized distributor for

information.

*For HCPL-261A/261N/263A/263N (8-pin DIP products) only.

**For HCPL-261A/261N only. Combination of Option 020 and Option 060 is not available.

***Gull wing surface mount option applies to through hole parts only.

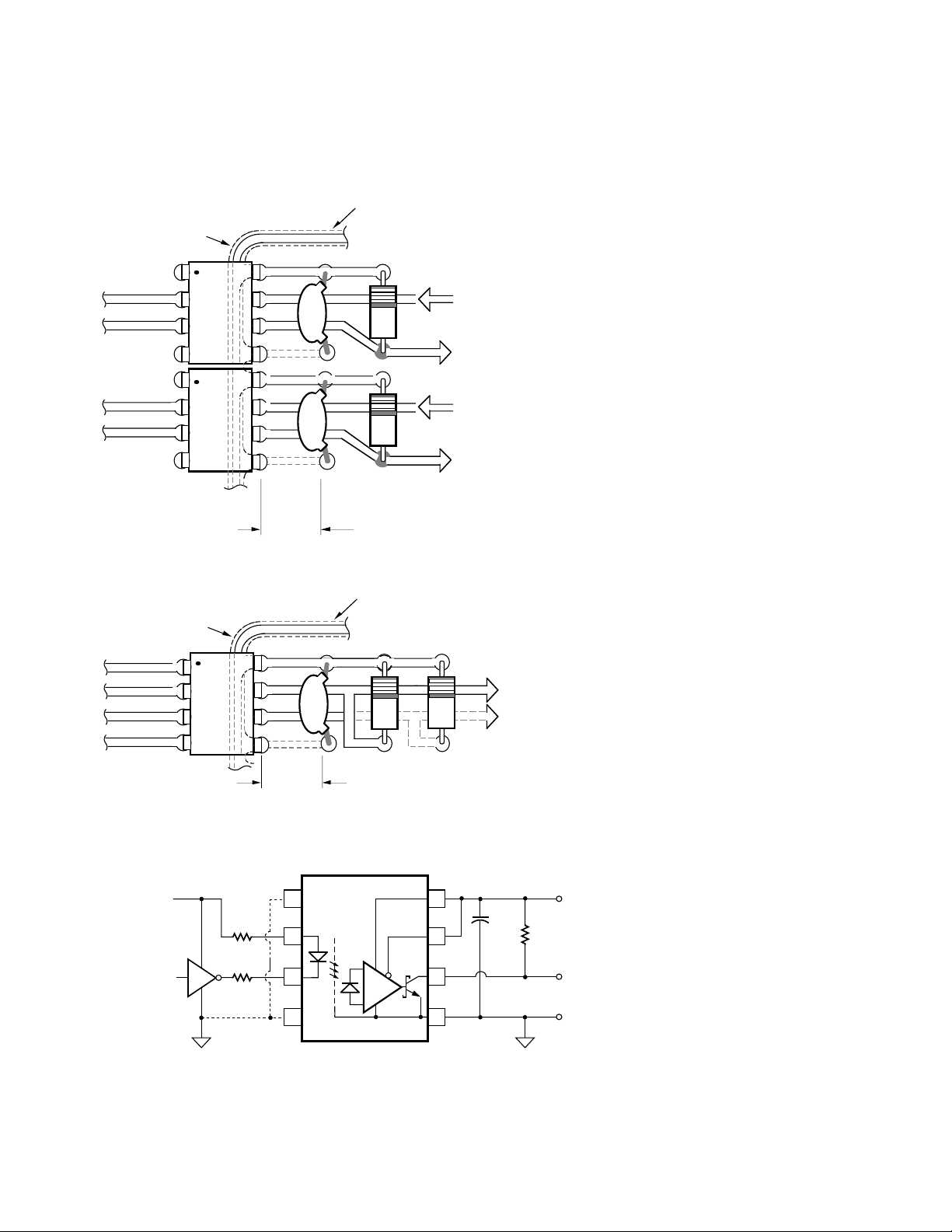

Schematic

HCPL-261A/261N

I

F

2+

V

F

–

3

USE OF A 0.1 µF BYPASS CAPACITOR CONNECTED

BETWEEN PINS 5 AND 8 IS RECOMMENDED (SEE NOTE 16).

HCPL-061A/061N

SHIELD

I

7

E

V

E

= 630 Vpeak Option**

IORM

I

CC

V

CC

8

I

O

V

O

6

GND

5

HCPL-263A/263N

HCPL-063A/063N

1

I

F1

+

V

F1

–

2

3

I

F2

–

V

F2

+

4

SHIELD

SHIELD

I

CC

V

8

I

O1

V

7

I

O2

V

6

GND

5

CC

O1

O2

1-167

Page 3

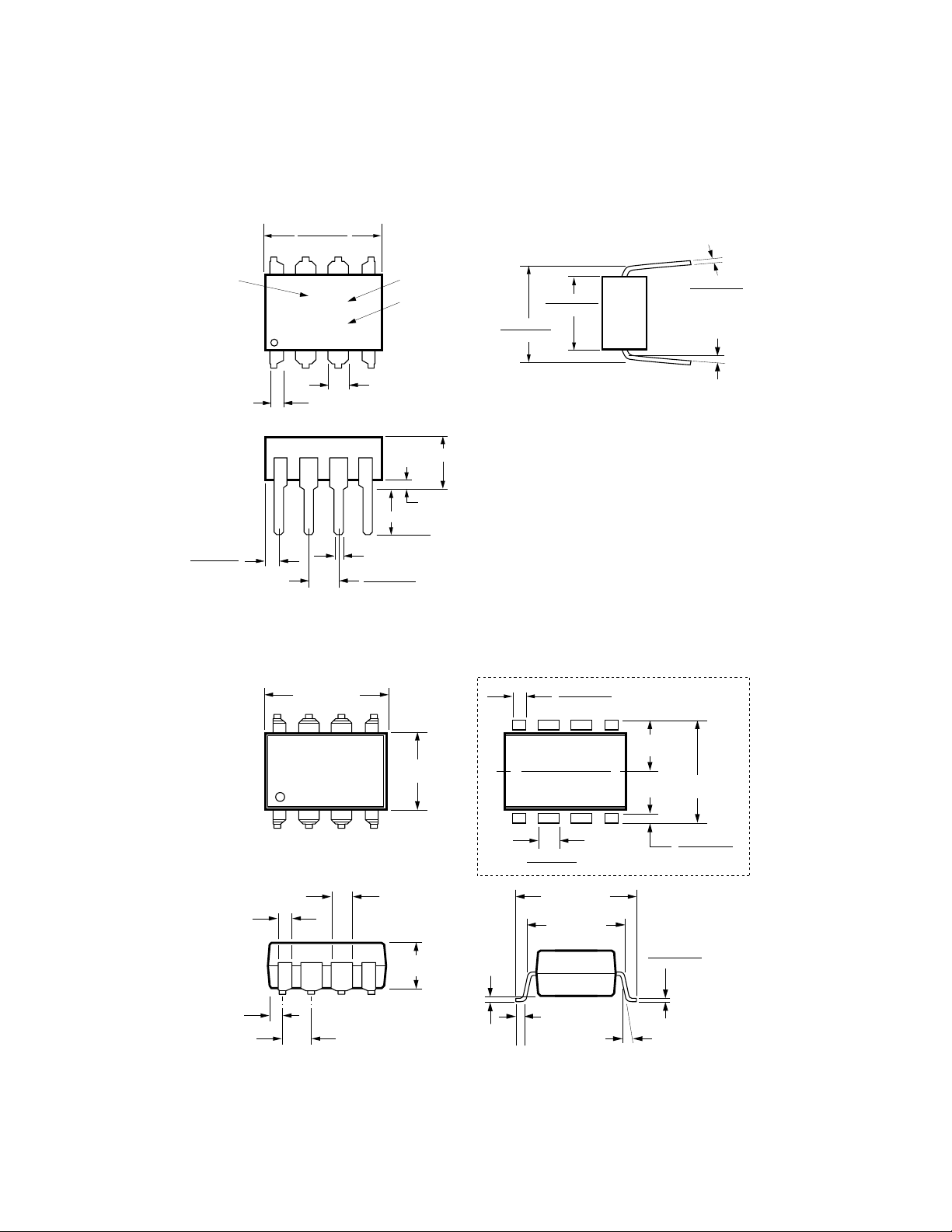

HCPL-261A/261N/263A/263N Outline Drawing

Pin Location (for reference only)

9.40 (0.370)

9.90 (0.390)

5678

TYPE NUMBER

HP XXXXZ

YYWW

PIN ONE

1.19 (0.047) MAX.

OPTION CODE*

DATE CODE

4321

1.78 (0.070) MAX.

7.36 (0.290)

7.88 (0.310)

6.10 (0.240)

6.60 (0.260)

0.20 (0.008)

0.33 (0.013)

5° TYP.

4.70 (0.185) MAX.

0.51 (0.020) MIN.

2.92 (0.115) MIN.

0.76 (0.030)

1.40 (0.056)

0.65 (0.025) MAX.

2.28 (0.090)

2.80 (0.110)

Figure 1. 8-Pin Dual In-Line Package Device Outline Drawing.

9.65 ± 0.25

(0.380 ± 0.010)

6

5

6.350 ± 0.25

(0.250 ± 0.010)

3

4

1.780

(0.070)

MAX.

4.19

MAX.

(0.165)

1.19

(0.047)

MAX.

7

8

1

2

DIMENSIONS IN MILLIMETERS AND (INCHES).

* MARKING CODE LETTER FOR OPTION NUMBERS.

"L" = OPTION 020

"V" = OPTION 060

OPTION NUMBERS 300 AND 500 NOT MARKED.

PIN LOCATION (FOR REFERENCE ONLY)

1.02 (0.040)

1.19 (0.047)

4.83

TYP.

(0.190)

9.65 ± 0.25

(0.380 ± 0.010)

0.38 (0.015)

1.19 (0.05)

1.78 (0.07)

9.65 ± 0.25

(0.380 ± 0.010)

7.62 ± 0.25

(0.300 ± 0.010)

0.64 (0.025)

0.20 (0.008)

0.33 (0.013)

1.080 ± 0.320

(0.043 ± 0.013)

2.540

(0.100)

BSC

DIMENSIONS IN MILLIMETERS (INCHES).

TOLERANCES (UNLESS OTHERWISE SPECIFIED):

LEAD COPLANARITY

MAXIMUM: 0.102 (0.004)

Figure 2. Gull Wing Surface Mount Option #300.

1-168

0.635 ± 0.130

(0.025 ± 0.005)

xx.xx = 0.01

xx.xxx = 0.005

0.635 ± 0.25

(0.025 ± 0.010)

12° NOM.

Page 4

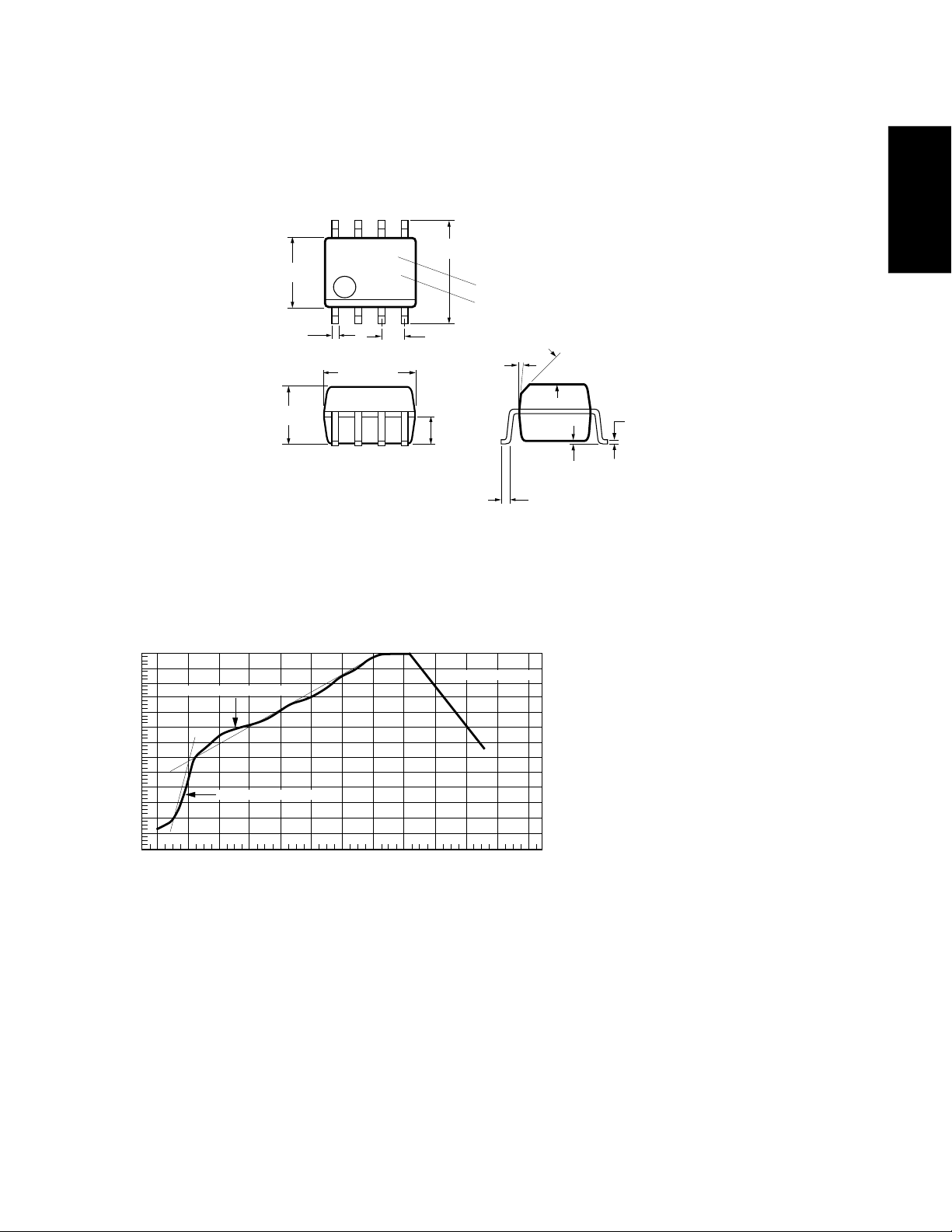

HCPL-061A/061N/063A/063N Outline Drawing

87

65

5.842 ± 0.203

(0.236 ± 0.008)

3.937 ± 0.127

(0.155 ± 0.005)

0.381 ± 0.076

(0.016 ± 0.003)

PIN

ONE

XXX

YWW

2

3

1

5.080 ± 0.005

(0.200 ± 0.005)

4

1.270

(0.050)

TYPE NUMBER (LAST 3 DIGITS)

DATE CODE

BSG

7°

45° X

0.432

(0.017)

OPTOCOUPLERS

3.175 ± 0.127

(0.125 ± 0.005)

DIMENSIONS IN MILLIMETERS AND (INCHES).

LEAD COPLANARITY = 0.10 mm (0.004 INCHES).

1.524

(0.060)

0.152 ± 0.051

(0.006 ± 0.002)

0.305

MIN.

(0.012)

0.228 ± 0.025

(0.009 ± 0.001)

Figure 3. 8-Pin Small Outline Package Device Drawing.

Solder Reflow Temperature Profile (HCPL-06XX and Gull Wing Surface Mount

Option 300 Parts)

260

240

220

200

180

160

140

120

100

80

60

TEMPERATURE – °C

40

20

0

∆T = 115°C, 0.3°C/SEC

0

123 456789101112

∆T = 100°C, 1.5°C/SEC

TIME – MINUTES

∆T = 145°C, 1°C/SEC

Note: Use of Nonchlorine Activated Fluxes is Recommended.

Regulatory Information

The HCPL-261A and HCPL-261N

families have been approved by

the following organizations:

UL

Recognized under UL 1577,

Component Recognition

Program, File E55361.

CSA

Approved under CSA Component

Acceptance Notice #5, File CA

88324.

VDE

Approved according to VDE

0884/06.92. (HCPL-261A/261N

Option 060 only)

1-169

Page 5

Insulation and Safety Related Specifications

8-Pin DIP

(300 Mil) SO-8

Parameter Symbol Value Value Units Conditions

Minimum External Air L(101) 7.1 4.9 mm Measured from input terminals to

Gap (External output terminals, shortest distance

Clearance) through air.

Minimum External L(102) 7.4 4.8 mm Measured from input terminals to

Tracking (External output terminals, shortest distance

Creepage) path along body.

Minimum Internal Plastic 0.08 0.08 mm Through insulation distance, conductor

Gap (Internal Clearance) to conductor, usually the direct

distance between the photoemitter and

photodetector inside the optocoupler

cavity.

Tracking Resistance CTI 200 200 Volts DIN IEC 112/ VDE 0303 Part 1

(Comparative Tracking

Index)

Isolation Group IIIa IIIa Material Group (DIN VDE 0110, 1/89,

Table 1)

Option 300 – surface mount classification is Class A in accordance with CECC 00802.

VDE 0884 Insulation Related Characteristics

(HCPL-261A/261N Option 060 ONLY)

Description Symbol Characteristic Units

Installation classification per DIN VDE 0110/1.89, Table 1

for rated mains voltage ≤ 300 V rms I-IV

for rated mains voltage ≤ 450 V rms I-III

Climatic Classification 55/85/21

Pollution Degree (DIN VDE 0110/1.89) 2

Maximum Working Insulation Voltage V

IORM

630 V

Input to Output Test Voltage, Method b*

V

x 1.875 = VPR, 100% Production Test with tm = 1 sec, V

IORM

PR

1181 V

Partial Discharge < 5 pC

Input to Output Test Voltage, Method a*

V

x 1.5 = VPR, Type and sample test, tm = 60 sec, V

IORM

PR

945 V

Partial Discharge < 5 pC

Highest Allowable Overvoltage*

(Transient Overvoltage, t

= 10 sec) V

ini

IOTM

6000 V

Safety Limiting Values

(Maximum values allowed in the event of a failure,

also see Figure 18, Thermal Derating curve.)

Case Temperature T

Input Current I

Output Power P

Insulation Resistance at TS, VIO = 500 V R

*Refer to the front of the optocoupler section of the current catalog, under Product Safety Regulations section (VDE 0884), for a

detailed description.

Note: Isolation characteristics are guaranteed only within the safety maximum ratings which must be ensured by protective circuits in

application.

S

S,INPUT

S,OUTPUT

S

175 °C

230 mA

600 mW

9

≥ 10

peak

peak

peak

peak

Ω

1-170

Page 6

Absolute Maximum Ratings

Parameter Symbol Min. Max. Units Note

Storage Temperature T

Operating Temperature T

Average Input Current I

F(AVG)

Reverse Input Voltage V

Supply Voltage V

Enable Input Voltage V

Output Collector Current (Each Channel) I

Output Power Dissipation (Each Channel) P

Output Voltage (Each channel) V

S

A

R

CC

E

O

O

O

-55 125 °C

-40 +85 °C

10 mA 1

3 Volts

-0.5 7 Volts 2

-0.5 5.5 Volts

50 mA

60 mW 3

-0.5 7 Volts

Lead Solder Temperature 260°C for 10 s, 1.6 mm Below Seating Plane

(Through Hole Parts Only)

Solder Reflow Temperature Profile See Package Outline Drawings section

(Surface Mount Parts Only)

Recommended Operating Conditions

Parameter Symbol Min. Max. Units

Input Voltage, Low Level V

Input Current, High Level I

Power Supply Voltage V

High Level Enable Voltage V

Low Level Enable Voltage V

FL

FH

CC

EH

EL

Fan Out (at RL = 1 kΩ) N 5 TTL Loads

Output Pull-up Resistor R

Operating Temperature T

L

A

-3 0.8 V

3.0 10 mA

4.5 5.5 Volts

2.0 V

CC

Volts

0 0.8 Volts

330 4k Ω

-40 85 °C

OPTOCOUPLERS

1-171

Page 7

Electrical Specifications

Over recommended operating temperature (TA = -40°C to +85°C) unless otherwise specified.

Parameter Symbol Min. Typ.* Max. Units Test Conditions Fig. Note

High Level Output I

OH

Current VF = 0.8 V, VE = 2.0 V

Low Level Output V

OL

Voltage (sinking), IF = 3.0 mA,

High Level Supply I

CCH

Current

Low Level Supply I

CCL

Current

High Level Enable I

EH

Current**

Low Level Enable I

EL

Current**

Input Forward V

F

1.0 1.3 1.6 V IF = 4 mA 6 4

Voltage

Temperature Co- ∆VF/∆T

A

efficient of Forward

Voltage

Input Reverse BV

R

Breakdown Voltage

Input Capacitance C

*All typical values at TA = 25°C, VCC = 5 V

**Single Channel Products only (HCPL-261A/261N/061A/061N)

***Dual Channel Products only (HCPL-263A/263N/063A/063N)

IN

3.1 100 µAVCC = 5.5 V, VO = 5.5 V, 4 18

0.4 0.6 V VCC = 5.5 V, IOL = 13 mA 5, 8 4, 18

VE = 2.0 V

710mAV

9 15 Dual Channel

= 0.5 V** VCC = 5.5 V 4

E

IF = 0 mA

Products***

813mA V

12 21 Dual Channel

= 0.5 V** VCC = 5.5 V

E

IF = 3.0 mA

Products***

-0.6 -1.6 mA VCC = 5.5 V, VE = 2.0 V

-0.9 -1.6 mA VCC = 5.5 V, VE = 0.5 V

-1.25 mV/°CIF = 4 mA 4

35 VI

= 100 µA4

R

60 pF f = 1 MHz, VF = 0 V

1-172

Page 8

Switching Specifications

Over recommended operating temperature (TA = -40°C to +85°C) unless otherwise specified

Parameter Symbol Min. Typ.* Max. Units Test Conditions Fig. Note

Input Current Threshold I

THL

High to Low IO >13 mA (Sinking)

Propagation Delay t

PLH

Time to High Output VCC = 5.0 V, 12 18

Level VE = Open,

Propagation Delay t

PHL

Time to Low Output 12 18

Level

Pulse Width Distortion PWD 11 45 ns 9, 13 17, 18

|t

- t

PSK

R

F

EHL

PLH

|

PHL

Propagation Delay Skew t

Output Rise Time t

Output Fall Time t

Propagation Delay t

Time of Enable VCC = 5.0 V, 16

from VEH to V

Propagation Delay t

EL

ELH

Time of Enable 16

from VEL to V

*All typical values at TA = 25°C, VCC = 5 V.

EH

1.5 3.0 mA VCC = 5.5 V, VO = 0.6 V, 7, 10 18

52 100 ns IF = 3.5 mA 9, 11, 4, 9,

53 100 ns 9, 11, 4, 10,

CL=15pF,

RL = 350 Ω

60 ns 24 11, 18

42 ns 9, 14 4, 18

12 ns 9, 14 4, 18

19 ns IF = 3.5 mA 15, 12

VEL = 0 V, VEH=3 V,

30 ns 15, 12

CL= 15 pF,

RL= 350 Ω

OPTOCOUPLERS

Common Mode Transient Immunity Specifications, All values at T

= 25°C

A

Parameter Device Symbol Min. Typ. Max. Units Test Conditions Fig. Note

Output High HCPL-261A |CMH| 1 5 kV/µsVCM = 50 V VCC = 5.0 V, 17 4, 13,

Level Common HCPL-061A R

Mode Transient HCPL-263A I

Immunity HCPL-063A T

HCPL-261N 1 5 kV/µsVCM = 1000 V

= 350 Ω, 15, 18

L

= 0 mA,

F

= 25°C

A

V

= 2 V

O(MIN)

HCPL-061N

HCPL-263N 15 25 kV/µs Using HP App 20 4, 13,

HCPL-063N Circuit 15

Output Low HCPL-261A |CML| 1 5 kV/µsVCM = 50 V VCC = 5.0 V, 17 4, 14,

Level Common HCPL-061A R

Mode Transient HCPL-263A I

Immunity HCPL-063A V

HCPL-261N 1 5 kV/µsVCM = 1000 V

= 350 Ω, 15, 18

L

= 3.5 mA,

F

= 0.8 V

O(MAX)

TA = 25°C

HCPL-061N

HCPL-263N 15 25 kV/µs Using HP App 20 4, 14,

HCPL-063N Circuit 15

1-173

Page 9

Package Characteristics

All Typicals at TA = 25°C

Parameter Sym. Package* Min. Typ. Max. Units Test Conditions Fig. Note

Input-Output V

Momentary With- t = 1 min.,

stand Voltage** TA = 25° C

Input-Output R

ISO

OPT 020† 5000

I-O

Resistance

Input-Output C

I-O

Capacitance TA = 25° C

Input-Input I

Dual Channel 0.005 µA RH ≤ 45%, 19

I-I

Insulation t = 5 s,

Leakage Current V

Resistance R

Dual Channel 10

I-I

(Input-Input)

Capacitance C

(Input-Input)

*Ratings apply to all devices except otherwise noted in the Package column.

**The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output

continuous voltage rating. For the continuous voltage rating refer to the VDE 0884 Insulation Characteristics Table (if applicable),

your equipment level safety specification or HP Application Note 1074 entitled “Optocoupler Input-Output Endurance Voltage.”

†For 8-pin DIP package devices (HCPL-261A/261N/263A/263N) only.

Dual 8-pin DIP 0.03 pF f = 1 MHz 19

I-I

Dual SO-8 0.25

2500 V rms RH ≤ 50%, 5, 6

5, 7

12

10

Ω V

= 500 Vdc 4, 8

I-O

0.6 pF f = 1 MHz, 4, 8

= 500 V

11

Ω 19

I-I

Notes:

1. Peaking circuits may be used which

produce transient input currents up

to 30 mA, 50 ns maximum pulse

width, provided the average current

does not exceed 10 mA.

2. 1 minute maximum.

3. Derate linearly above 80°C free-air

temperature at a rate of 2.7 mW/°C

for the SOIC-8 package.

4. Each channel.

5. Device considered a two-terminal

device: Pins 1, 2, 3, and 4 shorted

together and Pins 5, 6, 7, and 8

shorted together.

6. In accordance with UL1577, each

optocoupler is proof tested by

applying an insulation test voltage

≥ 3000 V

detection current limit, I

This test is performed before the

100% production test for partial

discharge (method b) shown in the

VDE 0884 Insulation Characteristics

Table, if applicable.

7. In accordance with UL1577, each

optocoupler is proof tested by

applying an insulation test voltage

≥ 6000 V

detection current limit, I

for 1 second (leakage

RMS

for 1 second (leakage

RMS

I-O

I-O

≤ 5 µA).

≤ 5 µA).

8. Measured between the LED anode and

cathode shorted together and pins 5

through 8 shorted together.

9. The t

10. The t

11. Propagation delay skew (t

12. Single channel products only (HCPL-

13. Common mode transient immunity in

propagation delay is

PLH

measured from the 1.75 mA point on

the falling edge of the input pulse to

the 1.5 V point on the rising edge of

the output pulse.

propagation delay is

PHL

measured from the 1.75 mA point on

the rising edge of the input pulse to

the 1.5 V point on the falling edge of

the output pulse.

equal to the worst case difference in

t

and/or t

PLH

between any two units under the

same test conditions and operating

temperature.

261A/261N/061A/061N).

a Logic High level is the maximum

tolerable |dVCM/dt| of the common

mode pulse, VCM, to assure that the

output will remain in a Logic High

state (i.e., Vo > 2.0 V).

that will be seen

PHL

PSK

) is

14. Common mode transient immunity in

a Logic Low level is the maximum

tolerable |dVCM/dt| of the common

mode pulse, VCM, to assure that the

output will remain in a Logic Low

state (i.e., VO < 0.8 V).

15. For sinusoidal voltages

(|dVCM/dt|)max = πfCM V

16. Bypassing of the power supply line is

required with a 0.1 µF ceramic disc

capacitor adjacent to each optocoupler as shown in Figure 19. Total lead

length between both ends of the

capacitor and the isolator pins should

not exceed 10 mm.

17. Pulse Width Distortion (PWD) is

defined as the difference between

t

and t

PLH

18. No external pull up is required for a

high logic state on the enable input of

a single channel product. If the VE pin

is not used, tying VE to VCC will result

in improved CMR performance.

19. Measured between pins 1 and 2

shorted together, and pins 3 and 4

shorted together. For dual channel

parts only.

for any given device.

PHL

CM(P-P)

.

1-174

Page 10

15

V

= 5.5 V

CC

= 5.5 V

V

O

= 2 V

V

E

= 0.8 V

V

10

F

5

– HIGH LEVEL OUTPUT CURRENT – µA

0

-60

-40 0 40 80

OH

I

-20

20

60

TA – TEMPERATURE – °C

100

80

V

= 5 V

CC

= 2 V

V

E

= 0.6 V

V

60

OL

= 3.5 mA

I

F

40

20

– LOW LEVEL OUTPUT CURRENT – mA

0

-60

OL

I

-20

20

60-40 0 40 80

TA – TEMPERATURE – °C

100

100.0

10.0

TA = 85 °C

1.0

TA = 40 °C

T

0.1

+

– INPUT FORWARD CURRENT – mA

F

0.01

I

1.0

1.2

V

–

VF – FORWARD VOLTAGE – V

= 25 °C

A

I

F

F

1.41.1 1.3

OPTOCOUPLERS

1.5

Figure 4. Typical High Level Output

Current vs. Temperature.

5.0

4.0

3.0

RL = 350 Ω

RL = 1 kΩ

2.0

RL = 4 kΩ

– OUTPUT VOLTAGE – V

1.0

O

V

0

0.5 1.5

0

1.0

IF – FORWARD INPUT CURRENT – mA

Figure 7. Typical Output Voltage vs.

Forward Input Current.

HCPL-261A/261N

I

INPUT

NODE

F

1

2

3

R

M

4

PULSE GEN.

Z = 50 Ω

O

t = t = 5 ns

f

r

MONITORING

Figure 5. Low Level Output Current

vs. Temperature.

HCPL-261A fig 5

0.6

0.5

IO = 16 mA

IO = 12.8 mA

0.4

2.0

0.3

– LOW LEVEL OUTPUT VOLTAGE – V

0.2

OL

-60

V

IO = 9.6 mA

IO = 6.4 mA

-20

20 60-40 0 40 80

TA – TEMPERATURE – °C

Figure 8. Typical Low Level Output

Voltage vs. Temperature.

+5 V

8

V

CC

GND

0.1 µF

7

BYPASS

6

5

R

L

OUTPUT V

MONITORING

*C

NODE

L

VCC = 5.5 V

= 2 V

V

E

= 3.0 mA

I

F

O

Figure 6. Typical Diode Input

Forward Current Characteristic.

100

*C IS APPROXIMATELY 15 pF WHICH INCLUDES

L

PROBE AND STRAY WIRING CAPACITANCE.

INPUT

I

F

t

OUTPUT

V

O

Figure 9. Test Circuit for t

PHL

PHL

and t

PLH

V

I = 3.5 mA

F

I = 1.75 mA

F

t

PLH

1.5 V

10%

90% 90%

t

rise

t

fall

OH

10%

V

OL

.

1-175

Page 11

2.0

1.5

1.0

0.5

– INPUT THRESHOLD CURRENT – mA

TH

I

RL = 350 Ω

RL = 1 kΩ

RL = 4 kΩ

0

-20

-60

TA – TEMPERATURE – °C

VCC = 5 V

= 0.6 V

V

O

20 60-40 0 40 80

100

120

100

– PROPAGATION DELAY – ns

p

t

TPLH

R

= 4 k

L

80

TPLH

60

R

= 1 k

L

40

TPLH

20

R

= 350 k

L

0

-20

-60

TA – TEMPERATURE – °C

TPHL

R

= 350 Ω, 1 kΩ, 4 kΩ

L

VCC = 5 V

I

F

20 60-40 0 40 80

= 3.5 mA

100

120

TPLH

= 4 kΩ

R

L

100

80

60

40

20

– PROPAGATION DELAY – ns

p

t

TPHL

RL = 350 Ω, 1 kΩ, 4 kΩ

VCC = 5 V

= 25 °C

T

0

0

IF – PULSE INPUT CURRENT – mA

A

2

68410

TPLH

R

L

TPLH

R

= 350 Ω

L

= 1 kΩ

12

Figure 10. Typical Input Threshold

Current vs. Temperature.

60

50

40

30

PWD – ns

20

10

0

-60

RL = 4 kΩ

VCC = 5 V

= 3.5 mA

I

F

= 1 kΩ

R

L

RL = 350 Ω

-20

TA – TEMPERATURE – °C

20 60-40 0 40 80

Figure 13. Typical Pulse Width

Distortion vs. Temperature.

Figure 11. Typical Propagation Delay

vs. Temperature.

160

VCC = 5 V

= 3.5 mA

I

F

140

R

= 4 kΩ

L

RL = 1 kΩ

RL = 350 Ω

RL = 350 Ω, 1 kΩ, 4 kΩ

-20

T

A

20 60-40 0 40 80

– TEMPERATURE – °C

100

120

60

40

– RISE, FALL TIME – ns

f

, t

20

r

t

0

-60

Figure 14. Typical Rise and Fall Time

vs. Temperature.

t

t

rise

fall

Figure 12. Typical Propagation Delay

vs. Pulse Input Current.

100

1-176

Page 12

PULSE GEN.

Z = 50 Ω

O

t = t = 5 ns

r

f

3.5 mA

I

F

INPUT VE

MONITORING NODE

HCPL-261A/261N

1

2

3

4

V

GND

120

VCC = 5 V

= 3 V

V

EH

= 0 V

V

EL

= 3.5 mA

I

F

90

+5 V

8

CC

0.1 µF

7

BYPASS

6

5

R

L

OUTPUT V

O

MONITORING

*C

NODE

L

60

30

– ENABLE PROPAGATION DELAY – ns

0

E

-60

t

t

, RL = 4 kΩ

ELH

t

, RL = 1 kΩ

ELH

t

ELH

t

, RL = 350 Ω, 1k Ω, 4 kΩ

EHL

-20

20 60-40 0 40 80

OPTOCOUPLERS

, RL = 350 Ω

100

TA – TEMPERATURE – °C

*C IS APPROXIMATELY 15 pF WHICH INCLUDES

L

PROBE AND STRAY WIRING CAPACITANCE.

INPUT

V

E

t

EHL

OUTPUT

V

O

Figure 15. Test Circuit for t

HCPL-261A/261N

1

V

CM

I

F

BA

V

FF

V

CM

V

O

V

O

2

3

4

PULSE GEN.

Z = 50 Ω

O

0 V

SWITCH AT A: I = 0 mA

5 V

SWITCH AT B: I = 3.5 mA

0.5 V

+

F

F

EHL

_

and t

V

CC

GND

t

ELH

ELH

8

7

6

5

V (PEAK)

CM

V (min.)

O

V (max.)

O

.

0.1 µF

BYPASS

3.0 V

1.5 V

1.5 V

350 Ω

+5 V

OUTPUT V

MONITORING

NODE

CM

H

CM

L

Figure 16. Typical Enable Propagation Delay vs. Temperature. HCPL261A/-261N/-061A/-061N Only.

S

HCPL-261A/261N OPTION 060 ONLY

800

700

PS (mW)

I

(mA)

S

600

500

, INPUT CURRENT – I

400

S

300

O

200

100

0

0

OUTPUT POWER – P

TS – CASE TEMPERATURE – °C

12525 75 100 150

175

20050

Figure 18. Thermal Derating Curve,

Dependence of Safety Limiting Value

with Case Temperature per

VDE 0884.

Figure 17. Test Circuit for Common Mode Transient Immunity and

Typical Waveforms.

1-177

Page 13

V BUS (FRONT)

CC

N.C.

N.C.

N.C.

N.C.

SINGLE CHANNEL PRODUCTS

GND BUS (BACK)

0.1µF

0.1µF

10 mm MAX. (SEE NOTE 16)

ENABLE

(IF USED)

OUTPUT 1

ENABLE

(IF USED)

OUTPUT 2

Application Information

Common-Mode Rejection for

HCPL-261A/HCPL-261N

Families:

Figure 20 shows the recommended drive circuit for the

HCPL-261N/-261A for optimal

common-mode rejection

performance. Two main points to

note are:

1. The enable pin is tied to V

rather than floating (this

applies to single-channel parts

only).

2. Two LED-current setting

resistors are used instead of

one. This is to balance I

variation during commonmode transients.

CC

LED

DUAL CHANNEL PRODUCTS

GND BUS (BACK)

V BUS (FRONT)

CC

0.1µF

10 mm MAX. (SEE NOTE 16)

OUTPUT 1

OUTPUT 2

Figure 19. Recommended Printed Circuit Board Layout.

HCPL-261A/261N

*

V

CC

OR ANY TOTEM-POLE

OUTPUT LOGIC GATE

74LS04

*

HIGHER CMR MAY BE OBTAINABLE BY CONNECTING PINS 1, 4 TO INPUT GROUND (GND1).

GND1

357 Ω

(MAX.)

357 Ω

(MAX.)

1

2

3

4

SHIELD

*

8

0.01 µF

7

6

5

GND2

Figure 20. Recommended Drive Circuit for HCPL-261A/-261N Families for HighCMR (Similar for HCPL-263A/-263N).

*Higher CMR May Be Obtainable by Connecting Pins 1, 4 to Input Ground (Gnd1).

350 Ω

V

CC+

V

O

GND

If the enable pin is left floating, it

is possible for common-mode

transients to couple to the enable

pin, resulting in common-mode

failure. This failure mechanism

only occurs when the LED is on

and the output is in the Low

State. It is identified as occurring

when the transient output voltage

rises above 0.8 V. Therefore, the

enable pin should be connected

to either VCC or logic-level high

for best common-mode

performance with the output low

(CMRL). This failure mechanism

is only present in single-channel

parts (HCPL-261N, -261A,

-061N, -061A) which have the

enable function.

Also, common-mode transients

can capacitively couple from the

LED anode (or cathode) to the

output-side ground causing

current to be shunted away from

the LED (which can be bad if the

LED is on) or conversely cause

current to be injected into the

LED (bad if the LED is meant to

be off). Figure 21 shows the

parasitic capacitances which

exists between LED

1-178

Page 14

anode/cathode and output ground

(CLA and CLC). Also shown in

Figure 21 on the input side is an

AC-equivalent circuit. Table 1

indicates the directions of ILP and

ILN flow depending on the

direction of the common-mode

transient.

For transients occurring when the

LED is on, common-mode rejection (CMRL, since the output is in

the “low” state) depends upon the

amount of LED current drive (IF).

For conditions where IF is close

to the switching threshold (ITH),

CMRL also depends on the extent

which ILP and ILN balance each

other. In other words, any

condition where common-mode

transients cause a momentary

decrease in IF (i.e. when

dVCM/dt>0 and |IFP| > |IFN|,

referring to Table 1) will cause

common-mode failure for

transients which are fast enough.

Likewise for common-mode

transients which occur when the

LED is off (i.e. CMRH, since the

output is “high”), if an imbalance

between ILP and ILN results in a

transient IF equal to or greater

than the switching threshold of

the optocoupler, the transient

“signal” may cause the output to

spike below 2 V (which constitutes a CMRH failure).

By using the recommended

circuit in Figure 20, good CMR

can be achieved. (In the case of

the -261N families, a minimum

CMR of 15 kV/µs is guaranteed

using this circuit.) The balanced

I

-setting resistors help equalize

LED

ILP and ILN to reduce the amount

by which I

transient coupling through C

is modulated from

LED

LA

and CLC.

CMR with Other Drive

Circuits

CMR performance with drive

circuits other than that shown in

Figure 20 may be enhanced by

following these guidelines:

1. Use of drive circuits where

current is shunted from the

LED in the LED “off” state (as

shown in Figures 22 and 23).

This is beneficial for good

CMRH.

2. Use of IFH > 3.5 mA. This is

good for high CMRL.

Using any one of the drive

circuits in Figures 22-24 with

IF= 10 mA will result in a typical

CMR of 8 kV/µs for the HCPL261N family, as long as the PC

board layout practices are

followed. Figure 22 shows a

1

1/2 R

LED

2

I

1/2 R

LED

3

4

Figure 21. AC Equivalent Circuit for HCPL-261X.

74L504

(ANY

TTL/CMOS

GATE)

I

LN

SHIELD

V

CC

LP

C

LA

C

LC

+

–

V

CM

420 Ω

(MAX)

2N3906

(ANY PNP)

circuit which can be used with

any totem-pole-output TTL/

LSTTL/HCMOS logic gate. The

buffer PNP transistor allows the

circuit to be used with logic

devices which have low currentsinking capability. It also helps

maintain the driving-gate powersupply current at a constant level

to minimize ground shifting for

other devices connected to the

input-supply ground.

When using an open-collector

TTL or open-drain CMOS logic

gate, the circuit in Figure 23 may

be used. When using a CMOS

gate to drive the optocoupler, the

circuit shown in Figure 24 may

be used. The diode in parallel

with the R

of the optocoupler LED.

8

7

6

5

1

2

3

4

0.01 µF

HCPL-261X

LED

15 pF

speeds the turn-off

LED

V

+

CC

350 Ω

V

O

GND

OPTOCOUPLERS

Figure 22. TTL Interface Circuit for the HCPL-261A/261N Families.

1-179

Page 15

V

V

CC

820 Ω

HCPL-261X

1

CC

1N4148

HCPL-261A/261N

1

2

74HC00

OPEN-COLLECTOR/

Figure 23. TTL Open-Collector/Open Drain Gate Drive Circuit

for HCPL-261A/-261N Families.

(OR ANY

OPEN-DRAIN

LOGIC GATE)

3

4

LED

74HC04

(OR ANY

TOTEM-POLE

OUTPUT LOGIC

GATE)

Figure 24. CMOS Gate Drive Circuit for HCPL-261A/261N Families.

Table 1. Effects of Common Mode Pulse Direction on Transient I

750 Ω

LED

2

3

4

If |ILP| < |ILN|, If |ILP| > |ILN|,

LED IF Current LED IF Current

If dVCM/dt Is: then ILP Flows: and ILN Flows: Is Momentarily: Is Momentarily:

positive (>0) away from LED away from LED increased decreased

anode through C

cathode through C

LA

LC

negative (<0) toward LED toward LED decreased increased

anode through C

cathode through C

LA

LC

LED

Propagation Delay, PulseWidth Distortion and

Propagation Delay Skew

Propagation delay is a figure of

merit which describes how

quickly a logic signal propagates

through a system. The propagation delay from low to high (t

PLH

is the amount of time required for

an input signal to propagate to

the output, causing the output to

change from low to high.

Similarly, the propagation delay

from high to low (t

PHL

) is the

amount of time required for the

input signal to propagate to the

output, causing the output to

change from high to low (see

Figure 9).

Pulse-width distortion (PWD)

results when t

PLH

and t

PHL

differ

in value. PWD is defined as the

difference between t

PLH

and t

PHL

and often determines the

maximum data rate capability of

a transmission system. PWD can

be expressed in percent by

dividing the PWD (in ns) by the

minimum pulse width (in ns)

being transmitted. Typically,

PWD on the order of 20-30% of

the minimum pulse width is

)

tolerable; the exact figure

depends on the particular application (RS232, RS422, T-1, etc.).

Propagation delay skew, t

an important parameter to consider in parallel data applications

where synchronization of signals

on parallel data lines is a concern. If the parallel data is being

sent through a group of optocouplers, differences in propagation delays will cause the data to

arrive at the outputs of the optocouplers at different times. If this

difference in propagation delay is

large enough it will determine the

PSK

, is

maximum rate at which parallel

data can be sent through the

optocouplers.

Propagation delay skew is defined

as the difference between the

minimum and maximum propagation delays, either t

PLH

or t

PHL

, for

any given group of optocouplers

which are operating under the

same conditions (i.e., the same

drive current, supply voltage,

output load, and operating

temperature). As illustrated in

Figure 25, if the inputs of a group

of optocouplers are switched

either ON or OFF at the same

time, t

is the difference

PSK

between the shortest propagation

delay, either t

PLH

or t

, and the

PHL

longest propagation delay, either

t

or t

PLH

As mentioned earlier, t

PHL

.

can

PSK

determine the maximum parallel

1-180

Page 16

data transmission rate. Figure 26

is the timing diagram of a typical

parallel data application with both

the clock and the data lines being

sent through optocouplers. The

figure shows data and clock

signals at the inputs and outputs

of the optocouplers. To obtain the

maximum data transmission rate,

both edges of the clock signal are

being used to clock the data; if

only one edge were used, the

clock signal would need to be

twice as fast.

Propagation delay skew represents the uncertainty of where an

edge might be after being sent

through an optocoupler. Figure

26 shows that there will be

uncertainty in both the data and

the clock lines. It is important

that these two areas of uncertainty not overlap, otherwise the

clock signal might arrive before

all of the data outputs have

settled, or some of the data

outputs may start to change

before the clock signal has

arrived. From these considerations, the absolute minimum

pulse width that can be sent

through optocouplers in a parallel

application is twice t

PSK

. A

cautious design should use a

slightly longer pulse width to

ensure that any additional

uncertainty in the rest of the

circuit does not cause a problem.

I

F

V

O

F

V

O

Figure 25. Illustration of Propagation Delay Skew – t

DATA

INPUTS

CLOCK

DATA

OUTPUTS

CLOCK

Figure 26. Parallel Data Transmission Example.

50%

50%I

1.5 V

t

PSK

1.5 V

TPHL

TPLH

t

PSK

t

PSK

PSK

OPTOCOUPLERS

.

The t

specified optocouplers

PSK

offer the advantages of guaranteed specifications for propagation delays, pulse-width

distortion, and propagation delay

skew over the recommended

temperature, input current, and

power supply ranges.

1-181

Loading...

Loading...