Page 1

Changed by

VF-co-cc

EE1 Friday, April 19, 2002 9:58:54 am

Date Changed Time Changed Model Number

Engineer

Engr_Name

Drawn by

Kevin Tseng

R&D CHK

DOC CTRL CHK

MFG ENGR CHK

QA CHK

INVENTEC

TITLE

Fenway2.0

TABLE OF CONTENTS

VER

110 SI

Sheet

151

Size

A3

of

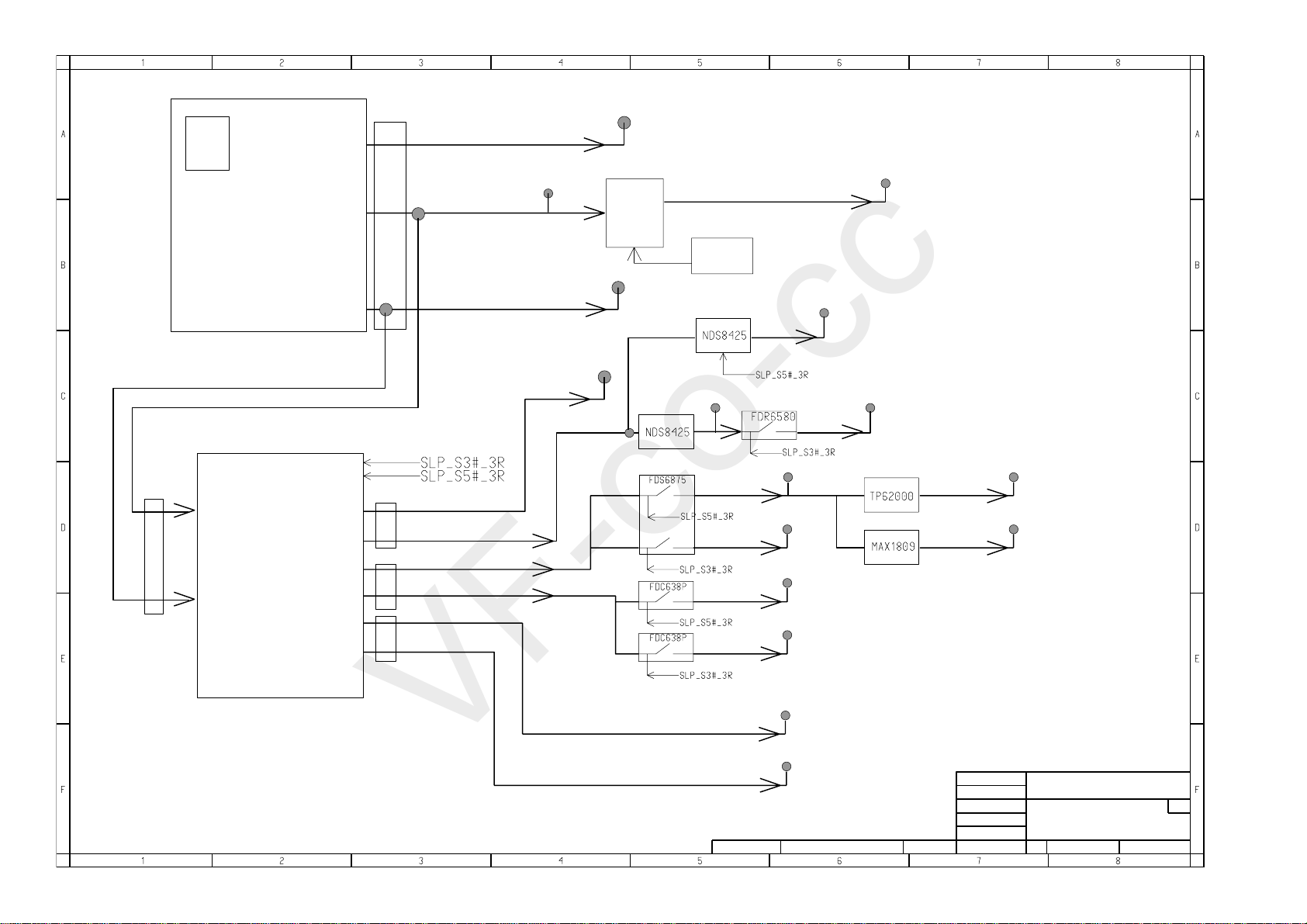

Page 2

AGP/M7-P

VF-co-cc

Display Cache

ITP

Northwood

(Micro-FCPGA)

mPGA478

Brookdale-M

CK TITAN

USB0

CONN A

Multibay

USB1

Dock

USB2

CONN B

HDD

Dock

USB3

System

DC/DC

Module

BATTERY

USB4

Bluetooth

USB

CONTROLLER

ICH3-M

FWH

AC’97 CODEC

Docking

DDR_SODIMM0

LAN Interface

DDR_SODIMM1

PCI 1420

CARDBUS

Mini PCI

SMC/KBC

Changed by Time Changed

EE1 Wednesday, January 23, 2002 10:02:33 pm

Date Changed

Engineer

Engr_Name

Drawn by

Kevin Tseng

R&D CHK

DOC CTRL CHK

MFG ENGR CHK

QA CHK

LOM

INVENTEC

TITLE

Fenway2.0

BLOCK DIAGRAM

VER

Model Number

110 SI

Sheet

251

Size

A3

of

Page 3

ADPT

VF-co-cc

CN506

+VADPTR

+VADPTR

CN512

I/O BOARD

+VBAT

+VADPTR_SW

DC/DC BOARD

3V ON

5V ON

1.5V

2.5VA

3V

5V

12V

5VALWAYS

CN516

CN513

CN512

+VBAT

+VADPTR_SW

+V1.5S

+V2.5A

+V3ALWAYS

+V5a

+V12

+V5ALWAYS

+VBAT

SWICHING

MOSFET

+VADPTR_SW

+V1.5S

+VCC_CORE

ISL6215

ISL6205

+V1.8ALWAYS

+V3

+V3S

+V5

+V5S

+V12

+VCC_CORE

+V2.5

+V1.8S

+VCC_VID

+V1.25

+V5ALWAYS

Changed by

EE1 Wednesday, January 23, 2002 10:03:29 pm

Date Changed

Time Changed

Engineer

Engr_Name

Drawn by

Kevin Tseng

R&D CHK

DOC CTRL CHK

MFG ENGR CHK

QA CHK

INVENTEC

TITLE

Fenway2.0

BLOCK DIAGRAM

Model Number

VER

110 SI

Sheet

351

Size

A3

of

Page 4

SLP_S1#_3R

VF-co-cc

SLP_S3#_3R

VGATE_U

49-,48-,45-,20-

H_BSEL1

H_BSEL0

12

20-,15-

1

49-,47-,41-,28-,26-,20-

OPEN

R580

OPEN

R581

12

0

R578

R579

5-

5-

0

TP19

TP20

2

1

2

Q514

2

C584

1

2

OPEN

+V3S

TP84

1

R600

OPEN

2

R599

12

OPEN

R571

12

OPEN

1

R575

1K

2

TP12

TP4

TP5

TP3

TP1

+V3S

1

R142

10K

2

3

D

G

S

NDS7002A

1

Place crystal within 500

mils of CLK_TITAN

1

R573

1K

2

1

PCISTOP#_3

R572

CPUSTOP#_3

OPEN

2

+V3S

OPENC154

1

12

C153 OPEN

2

12

R577

12

1K

20-

48-,20-

R576

12

10K

ICH_SMDAT_3

ICH_SMCLK_3

R167

475_1%

C582

C583

C567

1

1

1

1

2

2

2

2

0.01UF

0.01UF

0.01UF

U11

1

VDD

8

VDD

14

VDD

19

VDD

32

VDD

37

VDD

46

VDD

50

TP2

TP6

TP10

45-,21-,19-,11-

45-,21-,19-,11-

VDD

2

XTAL_IN

3

XTAL_OUT

40

SEL2

55

SEL1

54

SEL0

25

PWRDWN#

34

PCI_STOP#

53

CPU_STOP#

28

VTT_PWRGD#

43

MULT0

29

SDATA

30

SCLOCK

33

DRCG0

35

DRCG1_VCH

42

IREF

41

VSSIREF

4

VSS

9

VSS

15

VSS

20

VSS

31

VSS

36

VSS

47

VSS

X2

14.318MHZ

R554

12

33

R188

12

0

R574

12

OPEN

1

2

ICS_950805_TSSOP_56P

C581

0.01UF

VDDA

VSSA

CPU2

CPU2#

CPU1

CPU1#

CPU0

CPU0#

66INPUT

66BUF2

66BUF1

66BUF0

PCIF2

PCIF1

PCIF0

PCI6

PCI5

PCI4

PCI3

PCI2

PCI1

PCI0

USB

DOT

REF

1

C568

22UF_6.3V

26

27

45

44

49

48

52

51

24

23

22

21

7

6

5

18

17

16

13

12

11

10

39

38

56

2

1

C570

1

2

8

0.01UF

C152

1

2

0.01UF

CLK_CPU_BCLK_3

CLK_CPU_BCLK#_3

CLK_MCH_BCLK_3

CLK_MCH_BCLK#_3

CLK_ITP_3

TP69

CLK_ITP#_3

TP16

CLK_AGPCONN_3

TP17

CLK_MCH66_3

TP15

CLK_ICHHUB_3

CLK_ICHPCI_3

TP14

CLK_CBPCI_3

CLK_MINIPCI_3

CLK_FWHPCI_3

CLK_MSICPCI_3

CLK_USB_3

CLK_ICH48_3

CLK_MSIO14_3

34

567

1

22UF_6.3V

C569

10NF_16V

C151

33_1%

33_1%

33_1%

33_1%

33_1%

33_1%

12

12

R169

12

R168

12

R171

12

R170

12

R175

12

CLK_ITP_CPU#_3

R771

2

1

R553

33_1%

TP18

R143

TP22

33_1%

12

R552

12

NFM40P12C223

(15/5)

(10/5)

12

BLM11A221S

12

R603

5-

5-

12

CLK_ITP_CPU_3

44-,15-

8-

33_1%

33_1%R148

12

12

12

1

+V3S

L513

12

34

(10/5)

L15

49.9_1%

CLK_CPU_BCLK

CLK_CPU_BCLK#

49.9_1%R604

R435

12

OPEN

12

R598

OPEN

CLK_AGPCONN

CLK_MCH66

TP23

44-,19-

TP21

44-,19-

R144

33_1%

44-,24-

R145

33_1%

44-,36-

R551

33_1%

33_1%12

33_1%

2

33_1%12

33_1%12

33_1%1

2

44-,22-

44-,21-

44-,20-

44-,21-

44-,20-

R146

R147

R166

R172

R173

12

R177

49.9_1%

5-

5-

CLK_ITP_CPU#

R770

49.9_1%

12

CLK_ICHHUB

CLK_ICHPCI_3R

CLK_CBPCI_3R

CLK_MINIPCI_3R

CLK_FWHPCI_3R

CLK_MSIOPCI_3R

50-

CLK_USB_3R

CLK_ICH48_3R

CLK_MSIO14_3R

CLK_ICH14_3R

CLK_ITP_CPU

12

R601

49.9_1%

9-

CLK_MCH_BCLK

9-

CLK_MCH_BCLK#

R602

49.9_1%

12

R433

12

0

R570

12

0

44-,6-

44-,6-

CLK_ITP

CLK_ITP#

Engr_Name

Kevin Tseng

INVENTEC

Fenway2.0

CLK TITAN

110 SI

A3

451

Page 5

H_A#(16:3)

VF-co-cc

H_A#(31:17)

44-,9-

44-,9-

H_ADSTB#0H_REQ#(4:0)

44-,9-

H_ADSTB#1

CN509

N5

A16#

N4

A15#

N2

A14#

M1

A13#

N1

A12#

M4

A11#

M3

A10#

L2

A9#

M6

A8#

L3

A7#

K1

A6#

A5#

A4#

A3#

ADSTB0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

A18#

A17#

ADSTB1#

ADDR GROUP 0ADDR GROUP 1

L6

K4

K2

9-

L5

H3

J3

J4

K5

J1

AB1

Y1

W2

V3

U4

T5

W1

R6

V2

T4

U3

P6

U1

T2

R3

P4

P3

R2

T1

9-

R5

ADS#

AP0#

AP1#

BINIT#

BNR#

BPRI#

DP3#

DP2#

DP1#

DP0#

DEFER#

DRDY#

DBSY#

TESTHI8

TESTHI9

TESTHI10

BR0#

IERR#

INIT#

CONTROL

LOCK#

MCERR#

RESET#

RS2#

RS1#

RS0#

RSP#

TRDY#

HIT#

HITM#

G1

AC1

V5

AA3

G2

D2

L25

K26

K25

J26

E2

H2

H5

U6

W4

Y3

H6

AC3

W5

G4

V6

AB25

F4

G5

F1

AB2

J6

F3

E3

AMP_MPGA479M_C_1376756_479P

(ITL_NORTHWOOD_1200_733MHZ_512K_FC_PGA2_478P)

44-,9-

44-,944-,9-

44-,944-,944-,9-

H_BR1#

H_BR1#

H_BR1#

H_IERR_PU#

44-,19-,5-

44-,9-

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

54.9_1%

12

R134

10K

12

H_INIT#

H_LOCK#

44-,9-

44-,944-,9-

R109

+VCC_CORE

+VCC_CORE

1

2

H_TRDY#

H_HIT#

H_HITM#

+VCC_CORE

R123

51.1_1%

9-,6-

1

R106

220

2

9-

H_CPURST#

H_BR0#

44-,9-

H_RS#(2:0)

H_D#(15:0)

H_D#(31:16)

44-,9-

H_DINV#0

H_DSTBN#0

H_DSTBP#0

H_DINV#1

H_DSTBN#1

H_DSTBP#1

CN509

D25

D15#

J21

D14#

D23

D13#

C26

D12#

H21

D11#

G22

D10#

B25

D9#

C24

D8#

C23

D7#

B24

D6#

D22

D5#

C21

D4#

A25

D3#

D2#

D1#

D0#

DINV0#

STBN0#

STBP0#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

DINV1#

STBN1#

STBP1#

DATA GRP 2

DATA GRP 3

A23

B22

B21

E21

9-

E22

9-

F21

9-

H25

K23

J24

L22

M21

H24

G26

L21

D26

F26

E25

F24

F23

G23

E24

H22

9-

G25

K22

9-

J23

9-

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

DATA GRP 0DATA GRP 1

D34#

D33#

D32#

DINV2#

STBN2#

STBP2#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

DINV3#

STBN3#

STBP3#

T23

T22

T25

T26

R24

R25

P24

R21

N25

N26

M26

N23

M24

P21

N22

M23

P26

R22

P23

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

V22

U21

V25

U23

U24

U26

V21

W22

W23

AMP_MPGA479M_C_1376756_479P

(ITL_NORTHWOOD_1200_733MHZ_512K_FC_PGA2_478P)

999-

999-

44-,9-

H_DINV#2

H_DSTBN#2

H_DSTBP#2

44-,9-44-,9-

H_DINV#3

H_DSTBN#3

H_DSTBP#3

H_D#(47:32)

H_D#(63:48)

CPU_VR_VID(4:0)

+VCC_VID

CN509

AF22

4444-

44-,19-,51944-,19-,5-

44-,19-,544-,19-,544-,19-,544-,19-,5-

39396-

BCLK0

AF23

BCLK1

AC26

ITP_CLK0

AD26

ITP_CLK1

C6

A20M#

B6

FERR#

B2

IGNNE#

D1

LINT0

E5

LINT1

B5

SMI#

Y4

STPCLK#

AE1

VID4

AE2

VID3

AE3

VID2

AE4

VID1

AE5

VID0

AF3

RSVD3

AD20

VCCA

A5

VCCSENSE

AE23

VCCIOPLL

AD22

VSSA

TP78

A4

VSSSENSE

AF4

VCCVID

AD3

RSVD2

AF25

RSVD5

B3

THRMDA

C4

THRMDC

A2

THRMTRIP#

AD2

RSVD1

AF24

RSVD4

AE21

RSVD_PID

A22

RSVD0

A7

RSVD_SMI2#

R127

49-

+V3S

1

1

1

R136

4.7K

4.7K

R130

2

2

2

L11

12

4.7UH

L12

12

4.7UH

4.7K

1

R131

2

4.7K

2

C565

1

22UF_6.3V

1

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_ITP_CPU

CLK_ITP_CPU#

H_A20M#

H_FERR_S#

1

H_IGNNE#

R132

4.7K

H_STPCLK#

H_VCCIOPLL

22UF_6.3V

C564

H_THERMDA

H_THERMDC

H_THRMTRIP_S#

H_INTR

H_NMI

H_SMI#

H_VSSA

+VCC_VID

H_VCCA

AMP_MPGA479M_C_1376756_479P

(ITL_NORTHWOOD_1200_733MHZ_512K_FC_PGA2_478P)

FSBSEL0

FSBSEL1

CLK

HOST

COMP0

COMP1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

LEGACY CPU

TESTHI0

DBRESET

DPSLP#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

TESTHI1

TESTHI2

MISC

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

PWRGOOD

PROCHOT#

TRST#

GHI#

SLP#

TCK

TDO

TMS

TDI

AD6

AD5

A6

L24

P1

AB4

AA5

Y6

AC4

AB5

AC6

AD24

AE25

AD25

AA6

F6

AA21

F20

AA2

AC21

AC20

AC24

AC23

AA20

AB22

AB23

C3

AB26

D4

C1

D5

F7

E6

20-,5-

H_COMP0

H_COMP1

H_DOT

H_DOT

H_MCLK0

H_MCLK0

H_MCLK0

H_MCLK0

19-,5-

1

R52

680

2

4-

H_BSEL0

4-

H_BSEL1

PM_CPUPERF#

12

12

6-

H_BPM5_PREQ#

6-

H_BPM4_PRDY#

6-

H_BPM1_ITP#

6-

H_BPM0_ITP#

21-,6-

44-,19-,5-

54.9_1%

39-

H_PROCHOT_S#

H_CPUSLP#

6-

H_TCK

6-

H_TDI

6-

H_TDO

6-

H_TMS

6-

H_TRST#

R105

51.1_1%

R107

51.1_1%

R149

12

MASTER_RESET#

H_DPSLP#

R126

12

54.9_1%

12

R150

+VCC_CORE

+VCC_CORE

54.9_1%

H_GTLREF_3

H_GTLREF_1

+VCC_CORE

1

2

R122

300

44-,19-

H_PWRGD

R103

49.9_1%

1

R104

100_1%

2

1

2

C78

1

2

1UF_10V

1

R113

49.9_1%

2

1

R110

100_1%

2

C77

1

2

220PF

1

2

C107

1

2

1UF_10V

C76

220PF

1

2

C109

220PF

NORTHWOOD 1 OF 3

1

2

C108

220PF

PM_CPUPERF#

H_A20M#

H_IGNNE#

H_INTR

H_NMI

H_SMI#

H_STPCLK#

H_DPSLP#

H_CPUSLP#

H_INIT#

20-,544-,19-,544-,19-,544-,19-,544-,19-,544-,19-,544-,19-,544-,19-,519-,544-,19-,5-

+VCC_CORE

1

R111

200

2

200 Ohm is recommended

INSTEAD OF 300 Ohm

(RPAK). Placement: 3"

from CPU (Max)

1

1

R125

R124

200

200

2

2

1

R135

200

2

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

1

1

R112

R660

200

200

2

2

1

1

R89

200

2

1

1

R73

R72

200

200

2

2

2

INVENTECINVENTEC

Fenway2.0

Fenway2.0

Northwood(1/3)

SI

110 SI

110

R71

200

A3

A3

551

551

Page 6

H23

VF-co-cc

H26

A11

A13

A15

A17

A19

A21

A24

A26

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF26

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

C11

C13

C15

C17

H1

H4

A3

A9

B4

B8

CN509

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

C19

C2

C22

C25

C5

C7

C9

D10

D12

D14

D16

D18

D20

D21

D24

D3

D6

D8

E1

E11

E13

E15

E17

E19

E23

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

F8

G21

G24

G3

G6

J2

J22

J25

J5

K21

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

P2

P22

P25

P5

R1

R23

R26

R4

T21

T24

T3

T6

U2

U22

U25

U5

V1

V23

V26

V4

W21

W24

W3

W6

Y2

Y22

Y25

Y5

+VCC_CORE

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AMP_MPGA479M_C_1376756_479P

(ITL_NORTHWOOD_1200_733MHZ_512K_FC_PGA2_478P)

AMP_MPGA479M_C_1376756_479P

(ITL_NORTHWOOD_1200_733MHZ_512K_FC_PGA2_478P)

+VCC_CORE

Place close

to CPU

CN509

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

A8

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

AF17

AF19

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

B7

B9

C10

C12

C14

C16

C18

C20

C8

D11

D13

D15

D17

D19

D7

D9

E10

E12

E14

E16

E18

E20

E8

F11

F13

F15

F17

F19

F9

R550

12

AF2

0

H_BPM5_PREQ#

H_BPM4_PRDY#

H_BPM1_ITP#

H_BPM0_ITP#

+VCC_CORE

1

2

5555-

H_THRMTRIP_S#

R133

51

1

R108

51

2

RPAK at later time

1

1

R129

R128

51

51

2

2

+VCC_VID

12

R539

56

1

5-

1

R86

51

2

H_CPURST#

R540

470

In-Target Probe

1

1

R84

R85

51

51

2

2

5-

H_TDO

44-,4-

CLK_ITP

44-,4-

CLK_ITP#

5-,6-

H_TCK

9-,5-

+V3S

12

R666

10K

Q516

3

C

2

2

B

E

1

SST3904

10K

1

2

12

R665

R56

51

VID_PWRGD

U512

1

CK

2

D

3

Q#

4

GND

1

R55

75

2

VCC

CLR#

TC7W74FU

PR#

1

1

R54

R87

1.5K_1%

OPEN

2

2

CN5

23

BPM5DR#

13

BPM5#

11

BPM4#

9

BPM3#

7

BPM2#

5

BPM1#

3

BPM0#

24

STTDO

22

STPWR

19

BCK

21

BCK#

17

FBO

18

FBI

15

RST#

FCI_61698_302TR_ML_25P

+V3S

12

10K

R678

+V3S

R679

8

7

6

5

Q

10K

12

+V3S

1

2

10K

C47

10UF_10V

TRST

GND1

GND2

GND3

GND4

GND5

DSTBN(3:0)

REQ(4:0)

ADSTB(1:0)

12

R261

C44

1

2

0.1UF_25V

TCK

TDI

TMS

DBR

DBA

D(63:0)

DBI(3:0)

DSTP(3:0)

A(35:3)

NORTHWOOD 2 OF 3

+V3S

C45

1

2

0.1UF_25V

1

1

R49

10K

2

2

NEED 39 Ohm 1%

16

10

12

14

6

4

1

2

8

20

need 27 Ohm 1%

25

1.5"~10" , but must be the same length

H_THRMTRIP#

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

1

R50

R51

150

39

2

H_TCK

5-,6-

H_TDI

5-

H_TMS

5-

H_TRST#

5-

MASTER_RESET#

21-,5-

H_DBA#

1

R53

27.4_1%

2

INVENTEC

INVENTEC

Fenway2.0

Fenway2.0

Northwood(2/3)

SI110

SI110

A3

A3

516

516

Page 7

+VCC_CORE

VF-co-cc

(20/5)

C549

1

220UF_2.5V_S18_METAL

C550

1

220UF_2.5V_S18_METAL

C552

220UF_2.5V_S18_METAL1220UF_2.5V_S18_METAL

C545

1

C546

1

220UF_2.5V_S18_METAL

C555

1

220UF_2.5V_S18_METAL

C548

1

220UF_2.5V_S18_METAL

C547

1

220UF_2.5V_S18_METAL

C566

1

220UF_2.5V_S18_METAL

C1231

10UF_6.3V

2

C79

1

2

0.22UF_16V

C92

1

2

C121

1

2

0.22UF_16V

1

C101

2

10UF_6.3V

C91

1

2

0.22UF_16V 0.22UF_16V

C86

1

2

0.22UF_16V

C97

1

2

0.22UF_16V

+VCC_CORE

C61

1

2

1UF_10V

(20/5)

C821

10UF_6.3V

2

C62

1

2

0.22UF_16V

C98

1

2

0.22UF_16V

C132

1

2

0.22UF_16V

1

2

C105

1UF_10V

C80

1

10UF_6.3V

2

C93

1

2

0.22UF_16V

C119

1

2

0.22UF_16V

C94

1

2

0.22UF_16V

C72

1

2

1UF_10V

2

C135

1

2

1UF_10V

C1001

10UF_6.3V

1

2

1

2

1

2

C89

C118

0.22UF_16V0.22UF_16V

C90

0.22UF_16V

C106

1

2

1UF_10V

1

2

1

2

C102

1

10UF_6.3V

2 10UF_6.3V

C103

1

2

0.22UF_16V

C117

1

2

0.22UF_16V

C96

1

2

0.22UF_16V

C124

1

2

1UF_10V

C74

1

2

1UF_10V

C1161

10UF_6.3V

2

C133

1

2

0.22UF_16V

C87

1

2

0.22UF_16V

C85

1

2

0.22UF_16V

C75

1

2

1UF_10V

C83

1

10UF_6.3V

2

C84

1

2

0.22UF_16V

C81

C134

0.22UF_16V

C129

1

2

1UF_10V

C99

1

10UF_6.3V

2

C122

1

2

0.22UF_16V

C130

1

2

1UF_10V

+VCC_CORE

(20/5)

C131

1

2

0.1UF_16V

C104

1

2

0.1UF_16V

C120

1

2

0.1UF_16V

C73

1

2

0.1UF_16V

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

INVENTEC

INVENTEC

Fenway2.0

Fenway2.0

Northwood(3/3)

SI110

SI110

A3

A3

517

517

Page 8

M_A_FR_(12:0)

VF-co-cc

12-,11-

close to DIMM0<750mil

M_A_FR_(0)

M_A_FR_(1)

F17

E12

SMA1_CS#10

SMA0_CS#11

GAD0

GAD1

U17

R27

R28

M_A_FR_(2)

M_A_FR_(3)

M_A_FR_(4)

M_A_FR_(5)

E16

G18

G19

E18

SMA2_CS#6

SMA3_CS#9

SMA4_CS#5

GAD3

GAD4

GAD2

T26

T27

T25

R25

M_A_FR_(6)

M_A_FR_(7)

M_A_FR_(8)

M_A_FR_(9)

F19

G21

G20

F21

SMA5_CS#8

SMA6_CS#7

SMA7_CS#4

SMA8_CS#3

SMA9_CS#0

GAD8

GAD9

GAD5

GAD6

GAD7

V26

V27

U28

U27

M_A_FR_(10)

M_A_FR_(11)

M_A_FR_(12)

F13

E20

G22

SMA10

SMA11_CS#2

SMA12_CS#1

GAD10

GAD11

GAD12

T23

T24

U24

U23

G28

SDQ0

GAD14

GAD13

U25

F27

SDQ1

GAD15

V24

E28

C28

SDQ2

GAD16

Y27

Y26

H25

SDQ4

SDQ3

GAD17

GAD18

AA28

F25

G27

SDQ5

GAD19

AB25

AB27

B28

SDQ7

SDQ6

GAD20

GAD21

AA27

12-

E27

C27

SDQ8

GAD22

Y23

AB26

M_DATA(63:0)

B25

C25

B27

SDQ9

SDQ10

SDQ11

AGP

GAD23

GAD24

GAD25

AB23

AA24

AA25

D27

SDQ12

SDQ13

GAD26

GAD27

AB24

D26

SDQ14

GAD28

AC25

E25

D24

SDQ15

GAD29

AC24

AC22

E23

SDQ16

SDQ17

GAD30

GAD31

AD24

C22

E21

SDQ18

V25

C24

B23

SDQ19

SDQ20

SDQ21

GCBE0#

GCBE1#

GCBE2#

V23

Y25

D22

B21

SDQ22

SDQ23

GCBE3#

AA23

C21

D20

C19

SDQ24

SDQ25

SDQ26

GFRAME#

GIRDY#

GDEVSEL#

Y24

W27

W28

D18

C20

E19

SDQ27

SDQ28

GSTOP#

GTRDY#

W25

W23

W24

M_CB_R(7:0)

C18

E17

E13

C12

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

MEMORY

PRCOMP

GGNT#

GPAR

GREQ#

AGPREF

AA21

AD25

AH25

AG24

B11

C10

SDQ34

SDQ35

GCLKIN

P22

C13

C11

B13

SDQ36

SDQ37

SDQ38

AD_STB#0

AD_STB0

AD_STB1

R23

R24

AC27

13-,11-

D10

E10

D8

SDQ39

SDQ40

SDQ41C9SDQ42

AD_STB#1

SBA0

AH27

AH28

AC28

13-,11-

M_DQS_R(8:0)

22

RS23

4

5

3

6

2

7

18

22

RS22

5

4

6

3

7

2

8

1 11-

E8

SDQ43

E11

B9

SDQ44

B7

SDQ45

SDQ46

C7

C6

SDQ47

D6

SDQ48

D4

SDQ49

SDQ50

B3

E6

SDQ51

B5

SDQ52

SDQ53C4SDQ54

C3

E5

SDQ56D3SDQ57F4SDQ58

SDQ55

close to DIMM0<750mil

M_CB(7:0)

B15

C14

E2

G5

SDQ61C2SDQ62

SDQ63

C16

D16

SDQ65_CB1

SDQ66_CB2

SDQ67_CB3

SDQ64_CB0

B17

SDQ68_CB4

F3

B2

SDQ59

SDQ60

R293

12

22_5%

2

R300

1

22_5%

R299

2

1

22_5%

R298

12

22_5%

R297

2

1

22_5%

2

R292

1

22_5%

R291

2

1

22_5%

R290

12

22_5%

R289

12

22_5%

M_DQS1

M_DQS2

M_DQS0

C26

C23

C17

C15

D14

F26

SDQS0

SDQS1

SDQ69_CB5

SDQ70_CB6

SDQ71_CB7

M_DQS3

B19

SDQS2

SDQS3

M_DQS5

M_DQS6

M_DQS4

D12

C8

C5

SDQS4

SDQS5

SDQS6

M_DQS7

M_DQS8

E3

E15

SDQS7

SDQS8

M_WE_FR#

M_CAS_FR#

M_RAS_FR#

G11

G8

F11

SWE#

SCAS#

HUB

SBA1

AG28

SBA2

AG27

SBA3

AE28

SBA4

AE27

SBA5

AE24

SBA6

AE25

SB_STB

SBA7

AF27

SB_STB#

AF26

RBF#

AE22

WBF#

AE23

PIPE#

AF22

ST0

AG25

ST1

AF24

ST2

AG26

PSTOP

PSTRB

PSTRB#

RQI

N27

PD2

RQM

PD3

PD4

PD5

PD6

PD7

HLRCOMP

L28

L27

N25

N24

N28

P23

M26

M25

M27

M24

P27

PD1

PD0

P24

P25

PREF

P26

RSTIN#

J27

H27

TESTIN#

SSI_ST

H26

close to DIMM0<750mil

E14

J24

G6

G15

G25

SCK1_CLK2

SCK2_CLK4

SCK#0_CLK1

SCK#1_CLK3G7SCK#2_CLK5

G14

SCK3

E24

SCK#3

F15

SRAS#

SCK0_CLK0

MEMORY

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SCS#0F7SCS#1F9SCS#2

SBS0

SBS1

E9

J23

E22

F23

G23

H23

K23

G12

G13

12-,11-

12-,11-

12-,11-

1111111111-

H5

G24

SCK4

SCK5

SCK#4F5SCK#5

SCS#3E7SCS#4

G9

G10

M_WE_FR#

M_CAS_FR#

M_RAS_FR#

M_CLK_DDR0

M_CLK_DDR0#

M_CLK_DDR1

M_CLK_DDR1#

M_CLK_DDR2

M_CLK_DDR2#

K25

G17

J25

G16

SCK6_CLK6

SCK7_CLK10

SCK#6_CLK7

SCS#5

SMRCOMP

RCVENIN#H3RCVENOUT#

G3

J28

111111111111-

C806

0.1UF_16V

J21

J9

H6

H7

SDREF0

SCK8_CLK9

SCK#8_CLK8

SCK#7_CLK11

NC0

NC1

AD26

AD27

M_CLK_DDR3

M_CLK_DDR3#

M_CLK_DDR4

M_CLK_DDR4#

M_CLK_DDR5

M_CLK_DDR5#

SDREF1

1

2

R641

12

C650

1

2

0.1UF_25V

49-,11-

0

SM_VREF

AGP_AD(31:0)

44-,15-

AGP_CBE#(3:0)

44-,15-

AGP_FRAME#

AGP_DEVSEL#

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_PAR

AGP_REQ#

AGP_GNT#

AGPREF

C803

1

10UF_10V

2

45-,44-,1545-,44-,1545-,44-,1545-,44-,1545-,44-,1545-,44-,1545-,44-,1545-,44-,15-

C804

1

2

0.1UF_16V

CLK_MCH66

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_SBA(7:0)

BROOKDALE 1 OF 3

GRCOMP

1

R605 36.5_1%

2

445-,44-,1545-,44-,1545-,44-,1545-,44-,15-

44-,15-

AGP_SBSTB

AGP_SBSTB#

AGP_RBF#

AGP_WBF#

AGP_PIPE#

AGP_ST0

AGP_ST1

AGP_ST2

45-,44-,1545-,44-,15-

45-,44-,1545-,44-,1545-,44-

45-,44-,1545-,44-,1545-,44-,15-

HUB_RCOMP

+V1.8S

1

R646

36.5_1%

2

+V3S

C793

1

2

100PF

1

R644

2

M_RCVIN#

M_RCOMP

13-,1113-,1113-,1113-,11-

13-,1113-,1113-,1113-,11-

44-,1944-,19-

44-,19-

10-

10-

M_RCVOUT#

R238 0

1

M_CS3_R#

M_CS2_R#

M_CS1_R#

M_CS0_R#

12-,11-

12-,11-

M_CKE3_R#

M_CKE2_R#

M_CKE1_R#

M_CKE0_R#

MCH_TEST#

PCI_RESET#_3

HUB_VREF_MCH

HUB_PSTRB#

HUB_PSTRB

HUB_PD(10:0)

M_BS0_FR#

1

R759

10K

2

56

M_BS1_FR#

50-,36-,22-,21-,19-

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

ITL_BROOKDALE_M_FC_BGA_VERA_593P

close to 1"

2

Needs 27.4 ohm 1%

M_BS1_FR#

M_BS0_FR#

+V1.25

R654

12

30_1%

1

2

C682

0.1UF_25V

C213

1

2

OPEN

NO_STUFF_47PF

INVENTECINVENTEC

A3

Fenway2.0

Fenway2.0

Brookdale(1/3)

SI110

SI110

A3

518

518

Page 9

10UF_10V

VF-co-cc

+V1.5S

HXRCOMP

C645

1

2

1UF_10V

44-,5-

44-,5-

H_ADSTB#0

H_ADSTB#1

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_CPURST#

MCH_GTLREF

U17

T4

HA#3

T5

HA#4

T3

HA#5

U3

HA#6

R3

HA#7

P7

HA#8

R2

HA#9

P4

HA#10

R6

HA#11

P5

HA#12

P3

HA#13

N2

HA#14

N7

HA#15

N3

HA#16

K4

HA#17

M4

HA#18

M3

HA#19

L3

HA#20

L5

HA#21

K3

HA#22

J2

HA#23

M5

HA#24

J3

HA#25

L2

HA#26

H4

HA#27

N5

HA#28

G2

HA#29

M6

HA#30

L7

HA#31

U6

HREQ#0

T7

HREQ#1

R7

HREQ#2

U5

HREQ#3

U2

HREQ#4

5-

R5

HADSTB#0

N6

5-

HADSTB#1

4-

K8

HCLKINN

4-

J8

HCLKINP

AC13

HYRCOMP

AD13

HYSWNG

AC2

HXRCOMP

AA7

HXSWNG

5-

AD4

HDSTBN#0

5-

AE6

HDSTBN#1

5-

AE11

HDSTBN#2

5-

AC15

HDSTBN#3

5-

AD3

HDSTBP#0

5-

AE7

HDSTBP#1

5-

AD11

HDSTBP#2

5-

AC16

HDSTBP#3

5-

AD5

DINV#0

5-

AG4

DINV#1

5-

AH9

DINV#2

AD15

5-

DINV#3

AE17

6-,5-

CPURST#

M7

HVREF0

R8

HVREF1

Y8

HVREF2

AB11

HVREF3

AB17

HVREF4

HOST

ITL_BROOKDALE_M_FC_BGA_VERA_593P

C644

1

2

220PF

CLOSE TO MCH

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AD7

AC7

AC6

AC3

AC8

AE2

AG5

AG2

AE8

AF6

AH2

AF3

AG3

AE5

AH7

AH3

AF4

AG8

AG7

AG6

AF8

AH5

AC11

AC12

AE9

AC9

AE10

AD9

AG9

AC10

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

INVENTEC

INVENTEC

Fenway2.0

Fenway2.0

R626

24.9_1%

+VCC_CORE

H_A#(31:3)

H_REQ#(4:0)

HYRCOMP

HYSWING

1

R621

24.9_1%

2

1

R622

49.9_1%

2

1

R625

100_1%

2

U17

R22

VCCAGP0

R29

VCCAGP1

U22

VCCAGP2

U26

VCCAGP3

W22

VCCAGP4

W29

VCCAGP5

AA22

VCCAGP6

AA26

VCCAGP7

AB21

VCCAGP8

AC29

VCCAGP9

AD21

VCCAGP10

AD23

VCCAGP11

AE26

VCCAGP12

AF23

VCCAGP13

AG29

VCCAGP14

AJ25

VCCAGP15

N14

VCCCORE0

N16

VCCCORE1

P13

VCCCORE2

P15

VCCCORE3

P17

VCCCORE4

R14

VCCCORE5

R16

VCCCORE6

T15

VCCCORE7

+V1.8S

+V1.5S

1

L521

4.7UH

2

C647

C620

1

1

2

2

10UF_10V

10UF_10V

U14

VCCCORE8

U16

VCCCORE9

L29

VCCHL1

N26

VCCHL2

L25

VCCHL3

M22

VCCHL4

N23

VCCHL5

1

L522

4.7UH

2

T17

VCCGA1

T13

VCCHA1

C621

C649

1

1

2

2

10UF_10V

U17

VSSGA2

U13

VSSHA2

HTRDY#

DRDY#

DEFER#

HLOCK#

BREQ#0

HOST

DBSY#

VTTFSB1

VTTFSB2

VTTFSB3

VTTFSB4

VTTFSB5

VTTFSB6

VTTFSB7

VTTFSB8

VTTFSB9

VTTFSB10

VTTFSB11

VTTFSB12

VTTFSB13

VTTFSB14

VTTFSB15

VTTFSB16

VTTFSB17

VTTFSB18

VTTFSB19

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

ADS#

HITM#

BNR#

BPRI#

RS#0

RS#1

RS#2

HIT#

V3

U7

V4

Y4

Y3

Y5

W5

V7

W3

Y7

V5

W2

W7

W6

M8

U8

AA9

AB8

AB18

AB20

AC19

AD18

AD20

AE19

AE21

AF18

AF20

AG19

AG21

AG23

AJ19

AJ21

AJ23

A5

A9

A13

A17

A21

A25

C1

C29

D7

D11

D15

D19

D23

D25

F6

F10

F14

F18

F22

G1

G4

G29

H8

H10

H12

H14

H16

H18

H20

H22

H24

K22

K24

K26

L23

K6

J5

J7

44-,544-,544-,544-,544-,544-,544-,5-

544-,544-,544-,5-

+VCC_CORE

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

44-,5-

H_RS#(2:0)

+V2.5

HYSWING, HXSWING 12 mil trace, 10 mil space

+VCC_CORE

1

2

1

2

R623

301_1%

R624

150_1%

+VCC_CORE

1

R628

301_1%

2

1

R627

150_1%

2

C617

1

2

0.01UF

C618

1

2

0.01UF

1

2

HXSWING

ITL_BROOKDALE_M_FC_BGA_VERA_593P

BROOKDALE 2 OF 3

Brookdale(2/3)

110 SI

110 SI

44-,5-

H_D#(63:0)

A3

A3

951

951

Page 10

HUB INTERFACE

VF-co-cc

REFERENCE(1/2)1.8V

+V1.8S

M23

N22

K27

A15

A19

A23

A27

D13

D17

L24

J26

A11

D21

E26

E29

F12

F16

F20

F24

G26

H11

H13

H15

H17

H19

H21

J22

J29

L22

L26

N13

N15

N17

N29

P14

P16

R13

R15

R17

R26

T14

T16

T22

K5

K7

A3

A7

D5

D9

E1

E4

F8

H9

J1

J4

J6

L1

L4

L6

L8

N1

N4

N8

P6

P8

R1

R4

T6

T8

U1

U4

U17

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79VSS8

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

U15

U29

V6

V8

V22

W1

W4

W8

W26

Y6

Y22

AA1

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ3

AJ5

AJ7

AJ9

AJ11

AJ13

AJ15

AJ17

AJ27

+V2.5

1

220UF_4V_S18_METAL

1

2

0.1UF_16V

+VCC_CORE

+V1.5S

C624

1

2

0.1UF_16V

+V1.8S

C1601

10UF_6.3V

2

C232

C668

0.1UF_16V

1

C591

10UF_10V

2

C216

1

2

0.1UF_16V

C653

1

2

0.1UF_16V

1

2

1

2

1

2

1

2

C691

1

10UF_10V

2

C597

1

2

0.1UF_16V

C807

0.1UF_16V

C667

0.1UF_16V

C652

0.1UF_16V

C671

0.1UF_16V

C1611

10UF_6.3V

2

C592

1

2

0.1UF_16V

1

2

1

2

C655

1

2

0.1UF_16V

C808

1

2

0.1UF_16V

C672

1

2

0.1UF_16V

C646

1

2

0.1UF_16V

C674

1

2

220UF_4V_S18_METAL

C215

1

2

0.1UF_16V

C595

1

2

0.1UF_16V

C5981

C599

10UF_10V

2

10UF_10V

C619

C648

1

2

0.1UF_16V

0.1UF_16V

C654

1

2

0.1UF_16V

C809

1

2

0.1UF_16V

C665

1

2

0.1UF_16V

C214

1

2

0.1UF_16V

C231

1

1

2

1

2

1

2

1

2

1

2

C622

0.1UF_16V

C217

0.1UF_16V

C596

1

2

0.1UF_16V

C651

1

2

0.1UF_16V

C810

0.1UF_16V

C666

0.1UF_16V

C212

0.1UF_16V

C692

1

2

10UF_10V

C218

1

2

0.1UF_16V

C623

1

2

0.1UF_16V

C675

1

2

0.1UF_16V

C670

1

2

0.1UF_16V

1

2

1

2

1

2

1

2

C693

10UF_10V

C551

1

10UF_6.3V

2

C594

0.1UF_16V

C669

0.1UF_16V

C673

0.1UF_16V

1

2

C593

0.1UF_16V

+V1.5S

1

R647

301_1%

2

1

R648

301_1%

2

R642

12

OPEN

C625

1

2

OPEN

NO_STUFF_470PF

1

R645

OPEN

NO_STUFF_56.2_1%

2

8-

1

R649

0

2

C656

1

2

0.01UF

8-

HUB_VREF_MCH

MCH_TEST#

ITL_BROOKDALE_M_FC_BGA_VERA_593P

BROOKDALE 3 OF 3

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

INVENTEC

INVENTEC

Fenway2.0

Fenway2.0

Brookdale(3/3)

110

SI110

SI

A3

A3

5110

5110

Page 11

M_A_FR_(12:0)

VF-co-cc

M_CB_R(7:0)

M_DQS_R(8:0)

12-,8-

13-,8-,11-

M_CLK_DDR1

M_CLK_DDR1#

M_CLK_DDR2#

M_CLK_DDR2

M_CLK_DDR0

M_CLK_DDR0#

M_CKE0_R#

M_CKE1_R#

M_CAS_FR#

M_RAS_FR#

ICH_SMCLK_3

ICH_SMDAT_3

13-,8-,11-

CN10

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10_AP

100

A11

99

A12

97

A13_DU

117

M_BS0_FR#

M_BS1_FR#

M_WE_FR#

M_CS0_R#

M_CS1_R#

12-,812-,8-

88888813-,813-,812-,812-,812-,813-,813-,8-

45-,21-,19-,4-,1145-,21-,19-,4-,11-

116

98

71

73

79

83

72

74

80

84

35

37

158

160

89

91

96

95

120

118

119

121

122

194

196

198

195

193

86

12

26

48

62

134

148

170

184

78

11

25

47

61

133

147

169

183

77

BA0

BA1

BA2_DU

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0

CK0#

CK1#

CK1

CK2

CK2#

CKE0

CKE1

CAS#

RAS#

WE#

S0#

S1#

SA0

SA1

SA2

SCL

SDA

RESET_DU

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

AMP_C_1376408_DDR_SODIMM_200P

SO DIMM 0

SCK/SCK#(0)=SCK/SCK#(1)=SCK/SCK#(2)

SCK/SCK#(3)=SCK/SCK#(4)=SCK/SCK#(5)

DQ=CB=DQS

SCK(2:0) be longer than DQS 1"~2"

SCK(5:3) be longer than DQS 1"~2"

SDQ(63:0) from MCH to DIMM0 2"~3.5"

SCS#,SCKE from MCH to DIMM0 2"~4.5"

SMA(12:0),SBS(1:0),SRAS#,SCAS#,SWE# 2"~3.5"

SCK 3"~6.5"

M_DATA_R_(63:0)

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

13-,12-

M_A_SR_(12:0)

M_CB_R(7:0)

M_DQS_R(8:0)

13-,12-

13-,8-,11-

M_CLK_DDR4

M_CLK_DDR4#

M_CLK_DDR5#

M_CLK_DDR5

M_CLK_DDR3

M_CLK_DDR3#

+V3S

ICH_SMCLK_3

ICH_SMDAT_3

13-,8-,11-

M_BS0_SR#

M_BS1_SR#

M_CKE2_R#

M_CKE3_R#

M_CAS_SR#

M_RAS_SR#

M_WE_SR#

M_CS2_R#

M_CS3_R#

45-,21-,19-,4-,1145-,21-,19-,4-,11-

13-,1213-,12-

88888813-,813-,813-,1213-,1213-,1213-,813-,8-

112

111

110

109

108

107

106

105

102

101

115

100

117

116

158

160

120

118

119

121

122

194

196

198

195

193

134

148

170

184

133

147

169

183

99

97

98

71

73

79

83

72

74

80

84

35

37

89

91

96

95

86

12

26

48

62

78

11

25

47

61

77

CN11

AMP_C_1376409_DDR_SODIMM_REV_200P

SO DIMM 1

SCK(2:0) be longer than SCS(1:0),CKE(1:0) 1"~3"

SCK(5:3) be longer than SCS(3:2),CKE(3:2) 1"~3"

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10_AP

A11

A12

A13_DU

BA0

BA1

BA2_DU

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0

CK0#

CK1#

CK1

CK2

CK2#

CKE0

CKE1

CAS#

RAS#

WE#

S0#

S1#

SA0

SA1

SA2

SCL

SDA

RESET_DU

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SMA(12:0),SBS(1:0)

RAS#,CAS#,WE#

SMA(12:0),SBS(1:0)

RAS#,CAS#,WE#

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

+V2.5

CN10

201

202

201GG202

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

DU1

DU2

DU3

DU4

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

DU1

DU2

DU3

DU4

3

15

27

39

51

63

75

87

103

125

137

149

159

161

173

185

4

16

28

38

40

52

64

76

88

90

104

126

138

150

162

174

186

85

123

124

200

3

15

27

39

51

63

75

87

103

125

137

149

159

161

173

185

4

16

28

38

40

52

64

76

88

90

104

126

138

150

162

174

186

85

123

124

200

9

G

G

VDD1

21

VDD2

33

VDD3

45

VDD4

57

VDD5

69

VDD6

81

VDD7

93

VDD8

113

VDD9

131

VDD10

143

VDD11

155

VDD12

5

7

13

17

6

8

14

18

19

23

29

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

R365

12

49-,8-

SM_VREF

0

C305

1

2

0.1UF_25V

C429

1

2

0.1UF_16V

0.1UF_25V

1

2

C430

1

2

0.1UF_16V

C244

157

VDD13

167

VDD14

179

VDD15

191

VDD16

10

VDD17

22

VDD18

34

VDD19

36

VDD20

46

VDD21

58

VDD22

70

VDD23

82

VDD24

92

VDD25

94

VDD26

114

VDD27

132

VDD28

144

VDD29

156

VDD30

168

+V3S

VDD31

180

VDD32

192

VDD33

199

VDDID

197

VDDSPD

1

VREF1

2

VREF2

AMP_C_1376408_DDR_SODIMM_200P

+V2.5

CN11

9

VDD1

21

VDD2

33

VDD3

45

VDD4

57

VDD5

69

VDD6

81

VDD7

93

VDD8

113

VDD9

131

VDD10

143

VDD11

155

VDD12

157

VDD13

167

VDD14

179

VDD15

191

VDD16

10

VDD17

22

VDD18

34

VDD19

36

VDD20

46

VDD21

58

VDD22

70

VDD23

82

VDD24

92

VDD25

94

VDD26

114

VDD27

132

VDD28

144

VDD29

156

VDD30

168

+V3S

VDD31

180

VDD32

192

VDD33

199

VDDID

197

VDDSPD

1

VREF1

2

VREF2

AMP_C_1376409_DDR_SODIMM_REV_200P

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

INVENTEC

INVENTEC

Fenway2.0

Fenway2.0

DDR(1/4)

110

SI110

SI

A3

A3

5111

5111

Page 12

13-,11-

VF-co-cc

M_DATA_R_(63:0)

22

RS12

5

4

6

3

7

2

18

22

RS15

4

5

3

6

2

7

18

22

RS16

4

5

3

6

2

7

18

22

RS17

4

5

3

6

2

7

18

22

RS18

5

4

6

3

7

2

18

22

RS19

4

5

3

6

2

7

18

22

RS20

4

5

3

6

2

7

18

22

RS21

4

5

3

6

2

7

18

8-

22

RS28

4

5

3

6

2

7

18

22

RS27

4

5

3

6

2

7

18

22

RS13

5

4

3

6

2

7

18

22

RS29

4

5

3

6

2

7

18

22

RS14

5

4

6

3

2

7

18

22

RS30

4

5

3

6

2

7

18

22

RS31

5

4

6

3

2

7

18

22

RS32

4

5

3

6

2

7

18

11-,8-

M_BS1_FR#

M_CAS_FR#

M_WE_FR#M_DATA(63:0)

M_RAS_FR#

close to DIMM1<750 mil

10

RS47

5

4

8

1

7

2

36

M_A_FR_(10)

11-,8-

11-,811-,811-,811-,8-

10

R36812

10

RS49

4

5

3

6

1

8

27

10

RS51

4

5

2

7

1

8

36

10

R33912

12

R340

10

RS54

4

1

2

36

M_A_SR_(10)

10

5 13-,118

7

13-,11-

13-,1113-,1113-,11-

M_BS0_SR#M_BS0_FR#

M_BS1_SR#

M_CAS_SR#

M_WE_SR#

M_RAS_SR#

13-,11-

M_A_SR_(12:0)M_A_FR_(12:0)

close to DIMM0<750 mil

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

INVENTECINVENTEC

Fenway2.0

Fenway2.0

DDR(2/4)

SI110

SI110

A3

A3

5112

5112

Page 13

M_DATA_R_(63:0)

VF-co-cc

12-,11-,13-

M_A_SR_(12:0) M_DQS_R(8:0)

12-,11-,13-

11-,8-,13-

M_CKE0_R#

M_CKE1_R#

M_CS0_R#

M_CS1_R#

11-,811-,8-

11-,811-,8-

11-,8-

M_CB_R(7:0)

+V1.25

1234

1234

678

5678

5

RS43

56

RS62

56

1234

4321

21

5

8765

RS40

56

RS60

56

1234

432

5678

8765

RS42

56

RS61

56

1234

43

close to DIMM1< 800mil

5678

1

8765

RS41

56

RS59

56

1234

21

43

5678

8765

RS39

56

RS58

56

1234

4321

RS38

56

5678

RS57

56

8765

1234

RS37

56

5678

4321

RS55

56

8765

M_DATA_R_(63:0)

M_A_SR_(12:0)

1234

5678

4321

87

65

12-,11-,13-

M_DQS_R(8:0)

RS36

56

RS56

56

3421

12-,11-,13-

11-,8-,13-

34

5678

3

6578

RS45

56

RS53

56

1234

RS44

56

5678

4231

56

1

R338

2

5

1243

867

6578

RS50

56

RS46

56

RS48

56

56

87

R335

1

1

1

56_5%R336

56_5%

R342 56_5%

2

2

2

1

1

56_5%

56_5%

R345

R337

2

2

M_CS2_R#

M_CS3_R#

M_CKE3_R#

M_CKE2_R#

M_BS0_SR#

M_BS1_SR#

1

56_5% R334

2

2

1

56_5%

R344

2

R333

1

56_5%

1

56_5%

R343

2

11-,811-,8-

11-,811-,8-

12-,1112-,11-

1234

78

1234

M_WE_SR#

M_RAS_SR#

M_CAS_SR#

56678

5678

RS52

56

RS63

56

12-,11-

12-,11-

12-,11-

1

R341

2

12

56

124

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

INVENTECINVENTEC

Fenway2.0

Fenway2.0

DDR(3/4)

SI110

SI110

A3

A3

5113

5113

Page 14

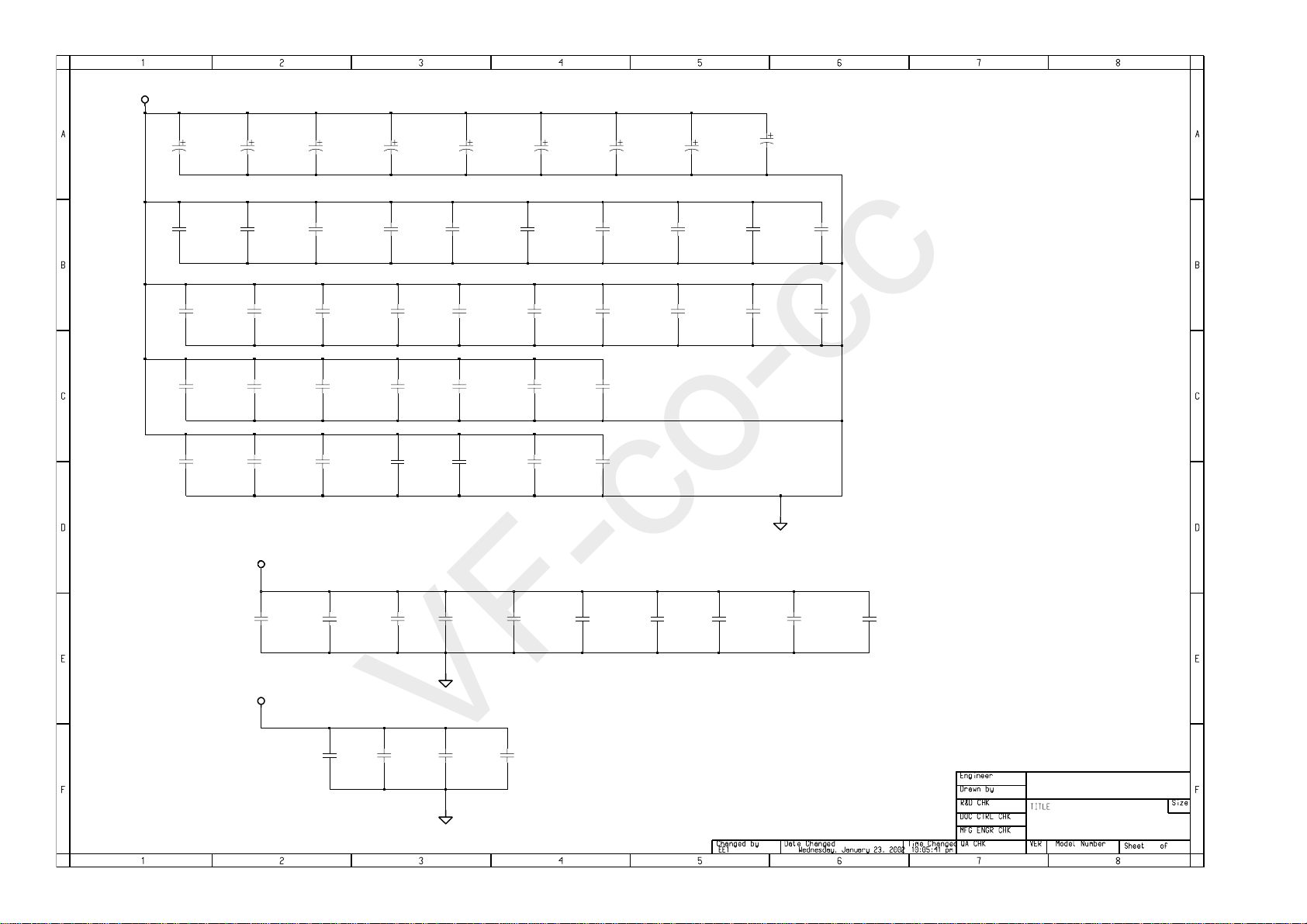

+V2.5

VF-co-cc

C266

0.1UF_16V

1

2

C267

0.1UF_16V

1

2

C246

0.1UF_16V

1

2

C245

0.1UF_16V

1

2

C268

0.1UF_16V

1

2

C248

0.1UF_16V

1

2

C269

0.1UF_16V

1

2

C247

0.1UF_16V

1

2

C270

0.1UF_16V

1

2

C328

0.1UF_16V

1

2

C329

0.1UF_16V

1

2

1

1

C275

C435

150UF_4V_METAL

150UF_4V_METAL

1

2

+V1.25

C315

1

2

0.1UF_16V

C2811C303

150UF_4V_METAL

C431

0.1UF_16V

C320

1

2

C310

1

2

0.1UF_16V

C341

1

2

0.1UF_16V

C336

1

2

0.1UF_16V

1

150UF_4V_METAL

C432

1

2

0.1UF_16V

C306

1

2

0.1UF_16V

C331

1

2

0.1UF_16V

C365

1

2

0.1UF_16V

C324

1

2

0.1UF_16V

1

C362

150UF_4V_METAL

C433

1

2

0.1UF_16V

C312

1

2

0.1UF_16V

C313

1

2

0.1UF_16V

C333

1

2

0.1UF_16V

C319

1

2

0.1UF_16V

1

2

C304

0.1UF_16V

C434

1

2

0.1UF_16V

C366

1

2

0.1UF_16V0.1UF_16V

C321

1

2

0.1UF_16V

C325

1

2

0.1UF_16V

1

2

C316

0.1UF_16V

C322

1

2

0.1UF_16V

C334

1

2

0.1UF_16V

C317

1

2

0.1UF_16V

1

2

C342

0.1UF_16V

C364

1

2

0.1UF_16V

C368

1

2

0.1UF_16V

C330

1

2

0.1UF_16V

C369

1

2

0.1UF_16V

C343

1

2

0.1UF_16V

1

2

C337

0.1UF_16V

C323

1

2

0.1UF_16V

C338

1

2

0.1UF_16V

1

2

C307

0.1UF_16V

C308

1

2

0.1UF_16V

C327

1

2

0.1UF_16V

C339

1

2

0.1UF_16V

C335

1

2

0.1UF_16V

1

2

C318

0.1UF_16V

C311

1

2

0.1UF_16V

C340

1

2

0.1UF_16V

Close to DDR as passible

C332

C326

1

1

2

2

0.1UF_16V

0.1UF_16V

C367

C363

1

1

2

2

0.1UF_16V

0.1UF_16V

C370

C309

1

1

2

2

0.1UF_16V

0.1UF_16V

Engr_Name

Engr_Name

Kevin Tseng

Kevin Tseng

INVENTEC

INVENTEC

Fenway2.0

Fenway2.0

DDR(4/4)

110 SI

110 SI

14 51

14 51

A3

A3

Page 15

AGP_ADSTB0

VF-co-cc

AGP_ADSTB1

AGP_SBSTB

AGPREF

C8051

10UF_10V

2

CHROMA_C

+V3S

1

2

+V1.8S

1

R629

OPEN

2

C637

1

2

0.1UF_25V

LUMA_Y

R163

12

0

C144

0.1UF_25V

R186

12

0

SLP_S1#_3R

20-,4-

AGP_AD(31:0)

AGP_CBE#(3:0)

CLK_AGPCONN

VID_RST#_3

AGP_REQ#

AGP_GNT#

AGP_PAR

AGP_STOP#

AGP_DEVSEL#

AGP_TRDY#

AGP_IRDY#

AGP_FRAME#

PIRQA#_3

AGP_WBF#

C3_STAT#

AGPBUSY#_3

AGP_RBF#

45-,44-,845-,44-,845-,44-,8-

AGP_SBA(7:0)

AGP_SBSTB#

AGP_ADSTB0#

AGP_ADSTB1#

35-,18-

35-,18-

X3

1

OE

27MHZ

OUT34VDD

GND

44-,8-

44-,8-

44-,42145-,44-,845-,44-,845-,44-,845-,44-,845-,44-,845-,44-,845-,44-,845-,44-,845-,19-

45-,44-,8-

45-,2020-,1545-,44-,8-

R634 0

12

12

R607

12

44-,8-

AGP_ST0

AGP_ST1

AGP_ST2

R610

45-,44-,8-

1

1

45-,44-,8-

1

45-,44-,8-

R609 0

12

R217

R555

12

680_1%

LCM_DDCCLK

LCM_DDCDATA

R589

12

120

2

C589

15PF

SUS_STAT#_3

AGP_AD(0)

AGP_AD(1)

AGP_AD(2)

AGP_AD(3)

AGP_AD(4)

AGP_AD(5)

AGP_AD(6)

AGP_AD(7)

AGP_AD(8)

AGP_AD(9)

AGP_AD(10)

AGP_AD(11)

AGP_AD(12)

AGP_AD(13)

AGP_AD(14)

AGP_AD(15)

AGP_AD(16)

AGP_AD(17)

AGP_AD(18)

AGP_AD(19)

AGP_AD(20)

AGP_AD(21)

AGP_AD(22)

AGP_AD(23)

AGP_AD(24)

AGP_AD(25)

AGP_AD(26)

AGP_AD(27)

AGP_AD(28)

AGP_AD(29)

AGP_AD(30)

AGP_AD(31)

AGP_CBE#(0)

AGP_CBE#(1)

AGP_CBE#(2)

AGP_CBE#(3)

R200 0

R198

R199 0

R187 0

OPEN

close to M7-P

AGP_ADSTB0_R

AGP_ADSTB1_R

0R608

AGP_SBSTB_R

0

AGP_SBA(0)

AGP_SBA(1)

AGP_SBA(2)

AGP_SBA(3)

AGP_SBA(4)

AGP_SBA(5)

AGP_SBA(6)

AGP_SBA(7)

45-,44-,845-,44-,845-,44-,8-

AGP_SBSTB#_R

0

2

AGP_ADSTB0#_R

0R635

2

AGP_ADSTB1#_R

2

47

(used 45_1%)

COMP_B

1

1

2

2

K28

L29

L27

L30

L28

M29

M27

M30

N30

N28

P29

P27

P30

P28

R29

R27

U28

U30

V27

V29

V28

V30

W27

W30

AA28

Y30

AA27

AA30

AB28

AA29

AB27

AB30

N27

R30

U29

W28

AG30

AH30

AF29

AF27

R28

T27

2

1

0

T29

2

1

T28

2

1

0R201

T30

2

1

U27

2

1

AH29

R614

1

AE27

2

AG29

0R588

AG28

12

AE30

N29

W29

AC29

AD29

AE28

AD30

AD27

AC30

AC27

AB29

AC28

AF30

AF28

AE29

AD28

M28

Y29

K30

K29

AJ24

AK24

AK23

35-

AK22

AG24

AG25

18-

AH25

18-

AH26

AJ26

AJ25

AJ29

AJ30

R590

150

R613

AH24

12

1K

AJ28

45-,24-,21-,20-

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

PCICLK

RST#

REQ#

GNT#

PAR

STOP#

DEVSEL#

TRDY#

IRDY#

FRAME#

INTA#

WBF_SERR#

STP_AGP#

AGP_BUSY#

RBF#

AD_STB0

AD_STB1

SB_STB

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

SB_STB#

ADSTB0#

ADSTB1#

AGPREF

AGPTEST

U14

PCI / AGP

AGP2X

AGP4XDAC2SSC

ZV_LCDDATA0

ZV_LCDDATA1

ZV_LCDDATA2

ZV_LCDDATA3

ZV_LCDDATA4

ZV_LCDDATA5

ZV_LCDDATA6

ZV_LCDDATA7

ZV_LCDDATA8

ZV_LCDDATA9

ZV_LCDDATA10

ZV_LCDDATA11

ZV_LCDDATA12

ZV_LCDDATA13

ZV_LCDDATA14

ZV_LCDDATA15

ZV_LCDDATA16

ZV_LCDDATA17

ZV PORT/EXT TMDS/GPIO/ROM

ZV_LCDDATA18

ZV_LCDDATA19

ZV_LCDDATA20

ZV_LCDDATA21

ZV_LCDDATA22

ZV_LCDDATA23

ZV_LCDCNTL0

ZV_LCDCNTL1

ZV_LCDCNTL2

ZV_LCDCNTL3

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

TXCLK_LN

TXCLK_LP

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

LVDSDAC1

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXCLK_UN

TXCLK_UP

R2SET

C_R

Y_G

COMP_B

H2SYNC

V2SYNC

CRT2DDCCLK

CRT2DDCDATA

TMDS

DVIDDCCLK

DVIDDCDATA

SSIN

SSOUT

XTALIN

XTALOUT

CLK

VGADDCDATA

VGADDCCLK

TESTEN

STEREOSYNC_SUS_STAT#

ATI_RAGE_M7_P_BGA_576P+120G

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

ROMCS#

DIGON

BLON#

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

HSYNC

VSYNC

RSET

AUXWIN

HPD

R

G

B

AJ2

AK2

AK1

AH3

AH2

AJ1

AF4

AH1

AG3

AF3

AG2

AF2

AG1

AF1

AE2

AE1

AE5

AJ5

AK5

AG6

AH6

AJ6

AK6

AG7

AH7

AJ7

AK7

AG8

AH8