Page 1

June 2000

Compaq Computer

Corporation

ISSD Technology

Communications

ONTENTS

C

Introduction....................... 3

High-Performance

Technologies ..................... 3

ProLiant 8000 Architecture......4

Pentium III Xeon

Processor Technology...........10

High-Availability

Technologies .................... 11

PCI Hot Plug Technology ......11

Redundant Array

Controller Technology........... 1 2

Redundant Network Interface

Controller Technology........... 1 2

Redundant Hot-Plug Fans .....13

Redundant Processor

Power Modules.....................15

Redundant Hot-Plug

Power Supplie s ....................15

Hot-Plug Hard Disk Drives .....18

Storage

Technologies .................... 18

Hard Drive Technology..........18

Array Controller Technology..18

Management

Technologies .................... 19

Remote-Flash

Redundant ROM ................... 19

Auto-Default

ROM Configura tion ...............20

Integrated Management

Display................................. 21

Integrated Remote Console... 21

Remote Insigh t

Board/PCI Optio n .................21

Serviceability

Features ............................22

Conclusion........................ 22

T

ECHNOLOGY

.

.

.

.

.

Compaq ProLiant 8000 Server Technology

.

.

.

.

.

.

This technology brief describes the high-performance, high-availability, storage, and

.

.

.

management technologies built into the Compaq ProLiant 8000 server. The high-

.

.

.

performance technologies include a new 8-way system architecture driven by the

.

.

.

Profusion chipset codeveloped by Compaq, Intel, and Corollary, as well as Intel’s

.

.

.

.

Pentium III Xeon processors. In addition, new disk drive technology and a new extended

.

.

.

SCSI controller with redundancy capability allows the ProLiant 8000 server to deliver

.

.

.

maximum highly available internal storage capacity.

.

.

.

.

.

The high-availability technologies include redundant internal array controllers; PCI Hot

.

.

.

Plug technology; redundant hot-plug power supplies, drives, and fans; and redundant

.

.

.

.

processor power modules. The ProLiant 8000 design also contains easy-access

.

.

.

components that reduce downtime for service or upgrades. Key management

.

.

.

technologies, such as the Integrated Remote Console, Integrated Management Display,

.

.

.

Remote-flash Redundant ROM, and auto-default ROM configuration, further enhance

.

.

.

.

availability.

.

.

.

.

The intended audience for this paper is engineers and system administrators familiar

.

.

.

.

with existing Compaq technology and servers. For those less familiar with Compaq

.

.

.

technology, please see the related technology briefs referenced in this document. For

.

.

.

more information about the ProLiant 8000 server, see the complete list of features at

.

.

.

http://www.compaq.com/products/servers/ProLiant8000/quickspecs.html.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Please direct comments regarding this communication to the ISSD Technology Communications Group at this Internet

.

.

address: TechCom@compaq.com

.

B

RIEF

TC000603TB

1

Page 2

ECHNOLOGY BRIEF

T

.

.

.

OTICE

N

.

.

.

.

.

The information in this publication is subject to change without notice and is provided “AS IS”

.

.

.

WITHOUT WARRANTY OF ANY KIND. THE ENTIRE RISK ARISING OUT OF T HE USE

.

.

.

OF THIS INFORMATION REMAINS WITH RECIP IENT. IN NO EVENT SHALL COMPAQ

.

.

.

BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, SPECIAL, PUNITIVE

.

.

.

OR OTHER DAMAGES WHATSOEVER (INCLUDING WITHOUT LIMITATION,

.

.

.

DAMAGES FOR LOSS OF BUSINESS PROFITS, BUSINESS INTERRUPTION OR LOSS OF

.

.

.

BUSINESS INFORMATION), EVEN IF COMPAQ HAS BEEN ADVISED OF THE

.

.

.

POSSIBILITY OF SUCH DAMAGES.

.

.

.

.

.

The limited warranties for Compaq products are exclusively set forth in the documentation

.

.

.

accompanying such products. Nothing herein should be construed as constituting a further or

.

.

.

additional warranty.

.

.

.

.

This publication does not constitute an endorsement of the product or products that were tested.

.

.

.

.

The configuration or configurations tested or described may or may not be the only available

.

.

.

solution. This test is not a determination of product quality or correctness, nor does it ensure

.

.

.

compliance with any federal state or local requirements.

.

.

.

.

Compaq, Contura, Deskpro, Fastart, Compaq Insight Manager, LTE, PageMarq, Systempro,

.

.

.

Systempro/LT, ProLiant, TwinTray, ROMPaq, LicensePaq, QVision, SLT, ProLinea, SmartStart,

.

.

.

NetFlex, DirectPlus, QuickFind, RemotePaq, BackPaq, TechPaq, SpeedPaq, QuickBack, PaqFax,

.

.

.

Presario, SilentCool, CompaqCare (design), Aero, SmartStation, MiniStation, and PaqRap,

.

.

.

ProSignia, Concerto, Vocalyst, and MediaPilot are registered with the United States Patent and

.

.

.

Trademark Office.

.

.

.

.

.

Change is Good, Compaq Capital, Colinq, Armada, SmartQ, Counselor, CarePaq, Netelligent,

.

.

.

Smart Uplink, Extended Repeater Architecture, Scalable Clock Architecture, QuickChoice,

.

.

.

Systempro/XL, Net1, LTE Elite, PageMate, SoftPaq, FirstPaq, SolutionPaq, EasyPoint, EZ Help,

.

.

.

MaxLight, MultiLock, QuickBlank, QuickLock, UltraView, Innovate logo, and Compaq PC Card

.

.

.

Solution logo are trademarks and/or service marks of Compaq Computer Corporation.

.

.

.

.

Microsoft, Windows, Windows NT, Windows NT Advanced Server, SQL Server for Windows NT

.

.

.

.

are trademarks and/or registered trademarks of Microsoft Corporation.

.

.

.

.

NetWare and Novell are registered trademarks and IntranetWare, NDS, and Novell Directory

.

.

.

Services are trademarks of Novell, Inc.

.

.

.

.

.

Pentium is a registered trademark of Intel Corporation.

.

.

.

.

Other product names mentioned herein may be trademarks and/or registered trademarks of their

.

.

.

respective companies.

.

.

.

.

.

©2000 Compaq Computer Corporation. All rights reserved. Printed in the U.S.A.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Compaq ProLiant 8000 Server Technology

.

.

.

Second Edition (June 2000)

.

.

Document Number TC000603TB

.

.

.

.

.

.

.

.

.

(cont.)

TC000603TB

2

Page 3

PCI – peripheral component

interconnect

SCSI – small computer system

interface

ROM – read only memory

ECHNOLOGY BRIEF

T

.

.

NTRODUCTION

I

.

.

.

.

.

In today’s business environment, enterprise customers require powerful servers with fault-tolerant

.

.

.

features to keep their businesses r unning 24 hours a day, 7 days a week. They also need servers

.

.

.

that are easy to manage and will scale to meet future requirements.

.

.

.

.

Providing breakthrough performance, t he ProLiant 8000 server offers outstanding scalability from

.

.

.

one to eight Intel Pentium III Xeon processors, up to 16 GB of synchronous dynamic random

.

.

.

access memory (SDRAM), and 11 PCI slots. The ProLiant 8000 server delivers massive internal

.

.

.

storage, with capacity for more than 380 GB of internal Wide Ultra-3 SCSI hot-plug storage. A

.

.

.

new extended SCSI array controller provides cable-free connections to the drive cages and allows

.

.

.

all three drive cages to be configured as a single contiguous array or as separate arrays. High-

.

.

.

.

availability features, including optional redundant array controllers, push-button PCI Hot Plug, hot-

.

.

.

plug redundant fans, redundant hot-plug power supplies, Compaq Re mot e-flash Redundant RO M,

.

.

.

and redundant processor power modules (PPMs), keep the ProLiant 8000 server up and running in

.

.

.

the most demanding 7x2 4 environments.

.

.

.

.

The ProLiant 8000 server provides all of the high-availability and manageability features of the

.

.

.

ProLiant 7000 server with added performance and scalability—all in a similar price class. In

.

.

.

addition, Compaq delivers on its commitment to superior investment protection by offering a

.

.

.

ProLiant 7000 in-chassis upgrade to 8-way architecture. Customers can leverage their ProLiant

.

.

.

7000 investment by keeping the chassis and serial number and replacing only select components for

.

.

.

the upgrade. For more information, see the 8-way upgrade website at

.

.

.

http://www.compaq.com/upgrade/8-way.

.

.

.

.

.

This technology brief explains the features of the ProLiant 8000 server and describes the

.

.

.

management and storage technologies that enhance performance and availability. Many of these

.

.

.

technologies are covered in more detail in separate technology briefs, which are referenced in this

.

.

.

document.

.

.

.

.

.

.

.

IGH-PERFORMANCE TECHNOLOGIES

H

.

.

.

.

.

The Compaq ProLiant 8000 server is a powerful, industry-leading technology solution for

.

.

.

distributed enterprise computing. A revolutionary new 8-way system architecture allows the

.

.

.

ProLiant 8000 server to deliver unsurpassed performance. This new architecture is the first

.

.

.

implementation in the industry of the Profusion chipset and features Pentium III Xeon processors.

.

.

.

Compaq servers using this architecture provide new levels of performance without requiring

.

.

.

modifications or special releases of operating systems (OSs) or applications. The Compaq 8-way

.

.

.

architecture provides nearly linear scalab ility for up to eight processors running under Microsoft

.

.

.

Windows NT 4.0, Microsoft Windows 2000, Novell NetWare, or SCO UnixWare. The 8-way

.

.

.

architecture delivers superior performance and price:performance for processor-intensive

.

.

.

applications such as Microsoft Terminal Server and Oracle databases; for memory-intensive

.

.

.

applications such as Lotus Notes, Microsoft Exchange, and SAP solutions; and for input/output

.

.

.

(I/O) intensive applications such as Microsoft SQL Server.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

(cont.)

TC000603TB

3

Page 4

ECHNOLOGY BRIEF

T

.

.

.

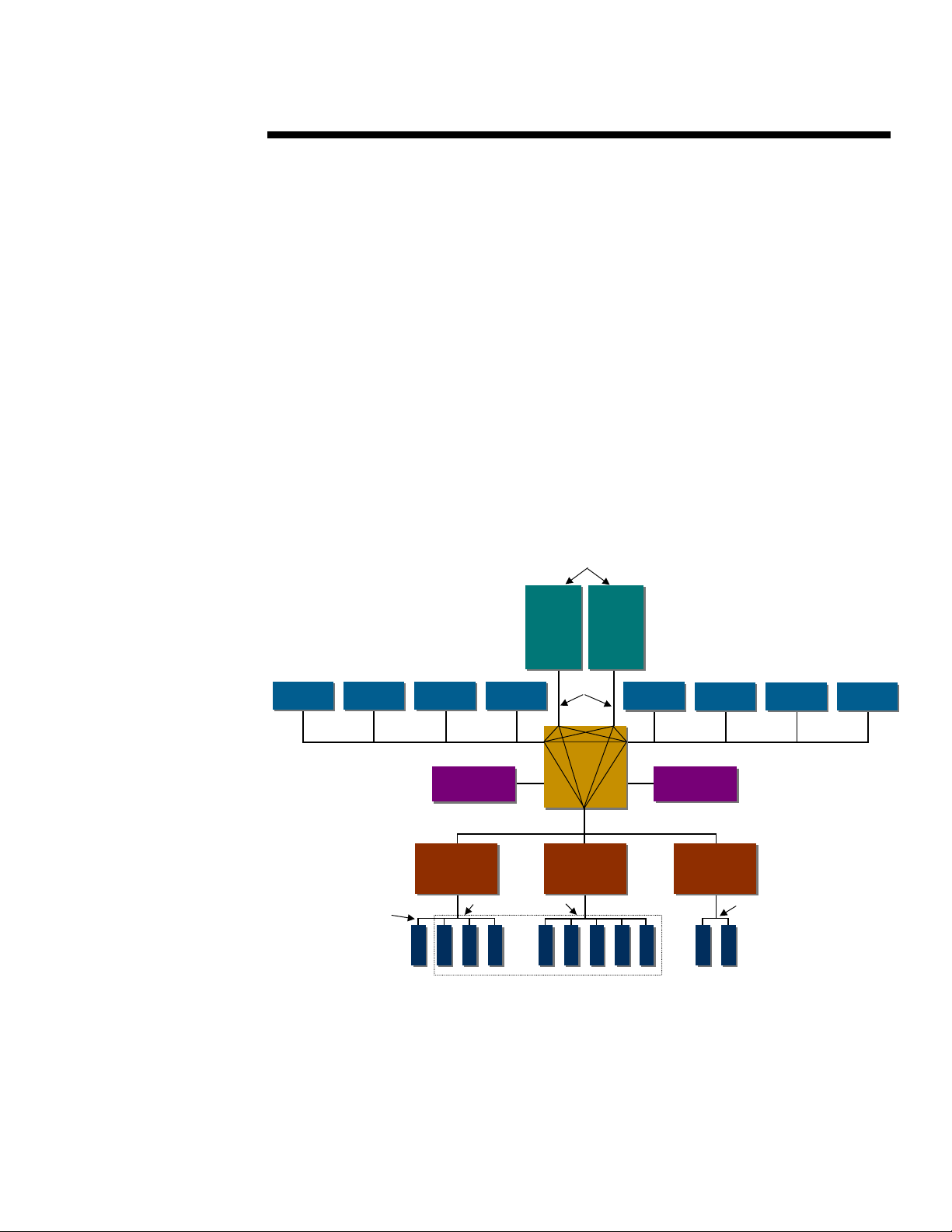

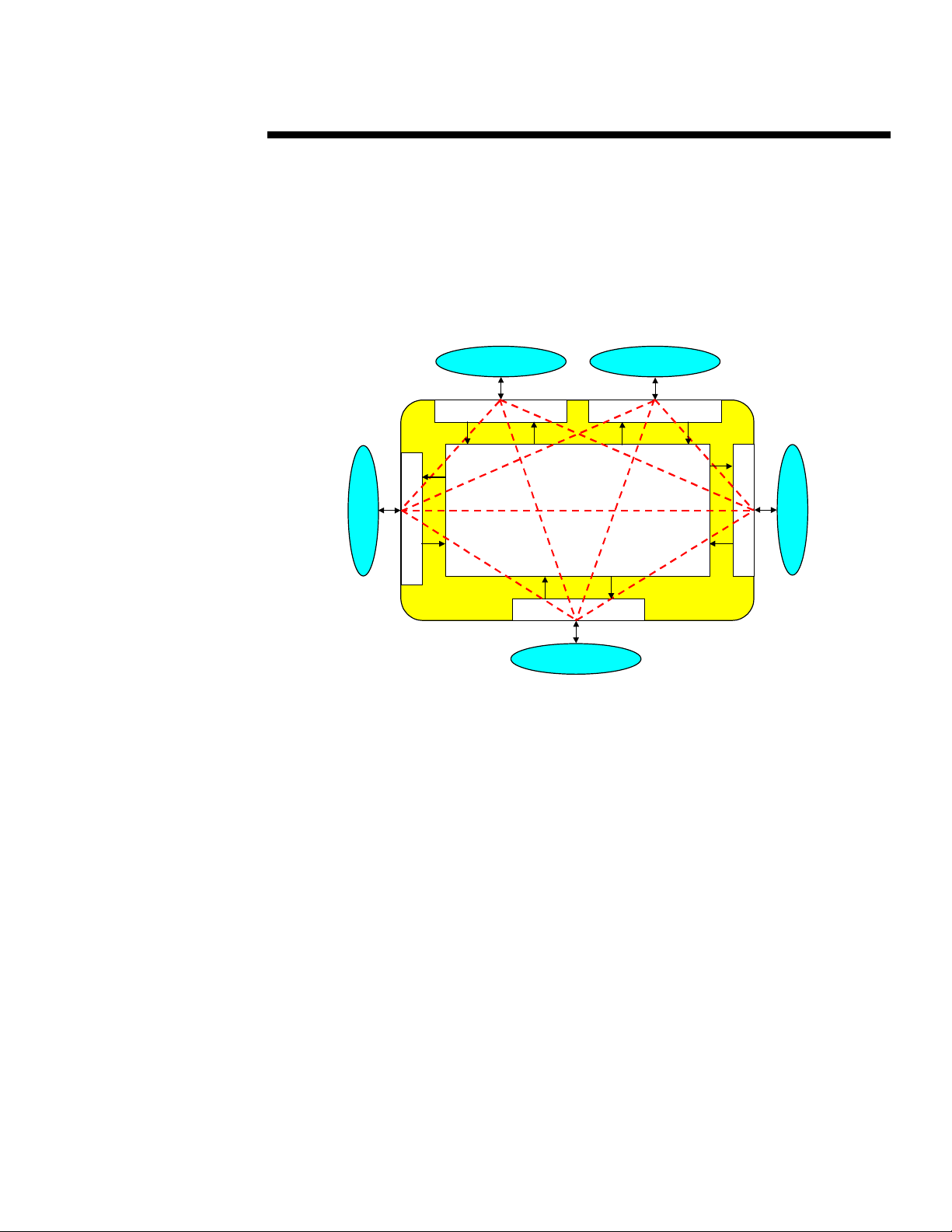

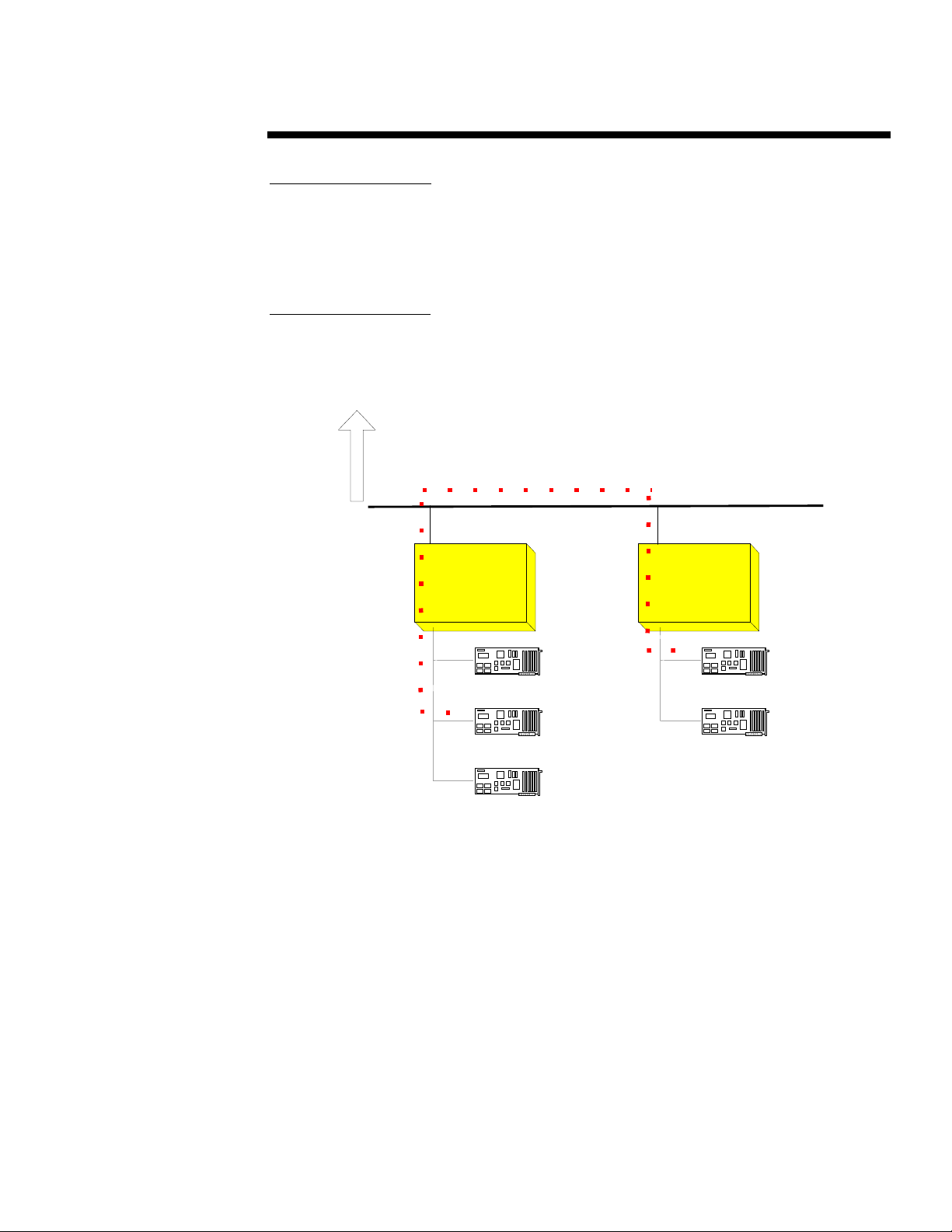

ProLiant 8000 Architecture

.

.

.

.

.

The system architecture is the key to the high level of performance offered by the ProLiant 8000

.

.

.

server. Compaq worked closely with Intel and Corollary for three years to perfect the 8-way

.

.

.

symmetric multiprocessing (SMP) architecture so that the processors, memory, and I/O subsystem

.

.

.

work in harmony to deliver breakthrough levels of performance. Figure 1 illustrates the

.

.

.

architecture used in the ProLiant 8000 server. The essential features of the architecture include:

.

.

.

.

• Profusion five-point crossbar switch

.

.

.

.

.

• Dual 100-MHz processor buses

.

.

.

.

• Dual 100-MHz memory buses, each with its own memory controller

.

.

.

.

.

• Dedicated 100-MHz I/O bus

.

.

.

.

• Support for up to eight Pentium III Xeon processors

.

.

.

.

.

• Support for up to 16 GB of two-way, cache-line interleaved SDRAM

.

.

.

.

• Dual cache accelerators

.

.

.

.

.

• I/O filter

.

.

.

.

.

• Three Compaq designed host-to-PCI bridges

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Pentium III

.

Xeon

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 1: Block diagram of the ProLiant 8000 system architecture.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Pentium III

Xeon

800 MB/s GTL+ left bus 800 MB/s GTL+ right bus

32-bit, 33-MHz PCI

133 MB/s

(cont.)

Pentium III

Xeon

Left Cache

Left Cache

Accelerator

Accelerator

800 MB/s GTL I/O bus

Compaq

Compaq

Host-to-PCI

Host-to-PCI

Bridge

Bridge

2-Way Cache-Line Interleaved

SDRAM

SDRAM

Pentium III

Xeon

64-bit, 33-MHz PCI

266 MB/s

SDRAM

SDRAM

800 MB/s

Profusion

Profusion

Compaq

Compaq

Host-to-PCI

Host-to-PCI

Bridge

Bridge

Pentium III

Xeon

Right Cache

Right Cache

Accelerator

Accelerator

Pentium III

Xeon

Compaq

Compaq

Host-to-PCI

Host-to-PCI

Bridge

Bridge

Pentium III

Xeon

64-bit, 66-MHz PCI

533 MB/s

Pentium III

Xeon

TC000603TB

4

Page 5

ECHNOLOGY BRIEF

T

.

.

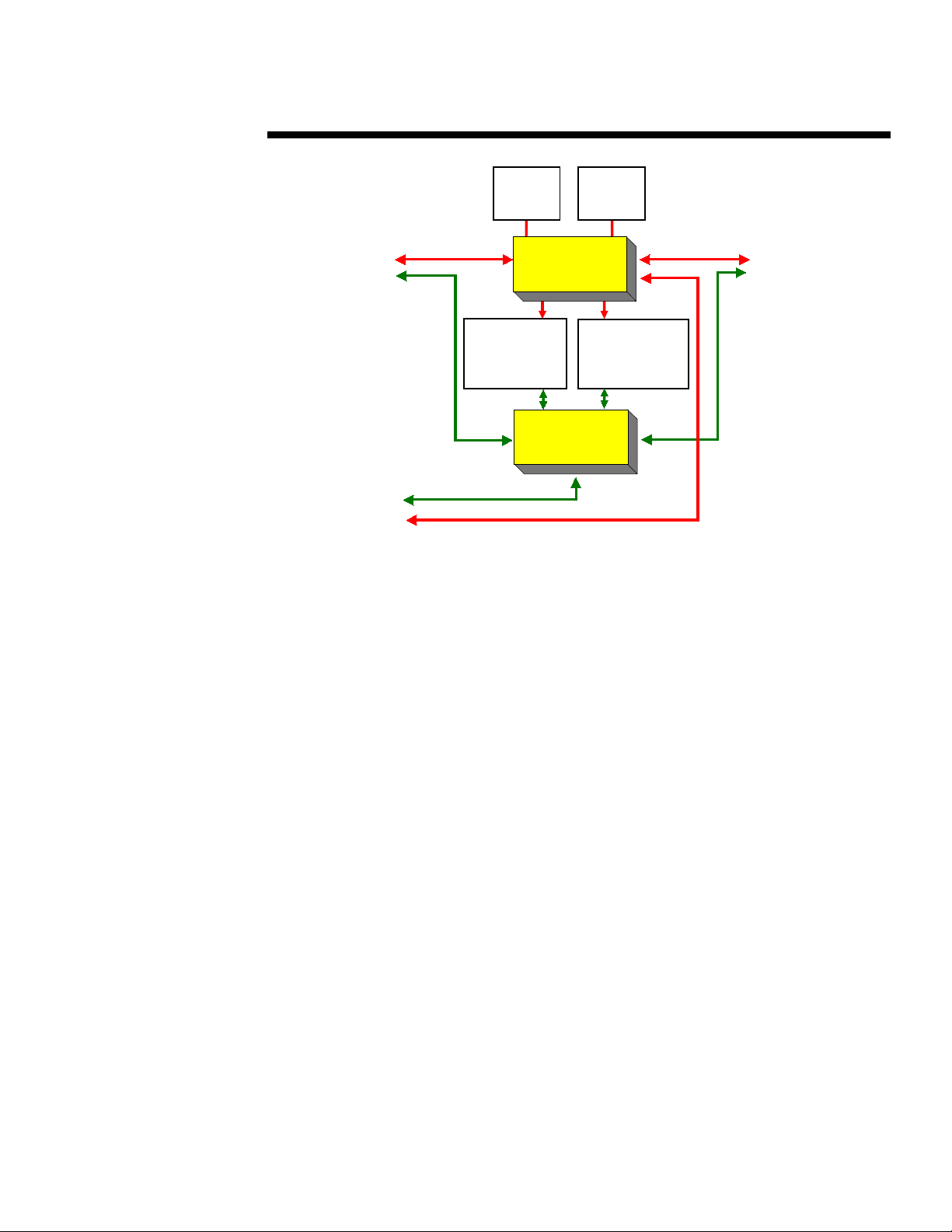

Profusion Chipset

.

.

.

.

.

At the heart of the 8-way architecture is the Profusion chipset. The chipset uses a five-point

.

.

.

crossbar switch (Figure 2) to connect processor buses, memory ports, and the I/O bus. The

.

.

.

crossbar switch contains static random access memory (SRAM) with ten ports—five read and five

.

.

.

write—that appear as five bidirectional ports, one for each of the processor, memory, and I/O

.

.

.

buses. The switch may connect two ports directly or may store data from the originating bus in the

.

.

.

SRAM before it is transferred to the destination bus. This nonblocking design allows simultaneous

.

.

.

read and write accesses from all five buses, which results in better system performance.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 2: Block diagram of the Profusion crossbar switch.

.

.

.

.

The Profusion crossbar switch provides direct paths from each memory bus to each processor bus

.

.

.

and to the I/O bus. Depending on the status of the system, the direct paths can be used to bypass

.

.

.

the SRAM, thus reducing latency and improving performance. The direct paths are used only to

.

.

.

read data. To improve processor utilization and performance, write data is always posted to the

.

.

.

SRAM and written to main memory later.

.

.

.

.

.

The Profusion crossbar switch consists of two physical chips—the memory address controller

.

.

.

(MAC) and the data interface buffer (DIB). This functional partitioning of the application-specific

.

.

.

integrated circuit (ASIC), as shown in Figure 3, improves system performance. For every

.

.

.

transaction from a processor or an I/O controller, the address and command portions are routed

.

.

.

through the MAC and the data is routed through the DIB. The MAC manages the external cache

.

.

.

accelerators and tracks the information stored in the DIB. The DIB allows simultaneous data

.

.

.

transfer on all five ports, has 64-cache-line buffers, and uses error-correcting code to maintain data

.

.

.

integrity. The cache-line buffers can be used by any transaction for any device on any bus; and

.

.

.

since there are no dedicated queues between buses, the efficiency of the buffers is high. This

.

.

.

improves system performance.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Left Processor Bus

(cont.)

Right Memory PortLeft Memory Port

Memory Interface Memory Interface

Processor Interface

10-Port SRAM

I/O Interface

I/O Bus

Processor Interface

Right Processor Bus

TC000603TB

5

Page 6

ECHNOLOGY BRIEF

T

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Processor

bus

I/O bus

Figure 3: ASIC partitioning in the Profusion chipset.

Processor and I/O Buses

The ProLiant 8000 server includes two 64-bit processor buses and a dedicated 64-bit I/O bus. All

three are 100-MHz advanced Gunning transceiver logic plus (AGTL+) buses with a theoretical

maximum throughput of 800 MB/s. AGTL+ buses facilitate higher clock speeds without

significantly reducing the bus length or number of electrical loads. Each 100-MHz AGTL+ bus

can support a maximum of five loads per bus. This allows four processors and one connection to

the memory controller on each processor bus. The use of two processor buses enables the ProLiant

8000 server to support up to eight Pentium III Xeon processors.

The Profusion chipset joins the two processor buses, the I/O bus, and the two memory ports. The

otherwise independent processor and I/O buses are joined by a logical connection that is made only

when required to transfer data. Each of the three AGTL+ buses has independent access to the two

memory ports. This architecture prevents I/O traffic from consuming bandwidth on the processor

bus. In addition, the use of 100-MHz buses and five independent paths allows the crossbar switch

to deliver an aggregate instantaneous peak throughp ut of 4 GB/s—unprecedented high per formance

for customers.

Memory Subsystem

The ProLiant 8000 memory subsystem includes dual 100-MHz buses, each with its own memory

controller. The use of two memory buses increases memory bandwidth, reduces access conflicts,

and increases the quantity of memory supported. Memory attached to each of the buses is cacheline interleaved, which means the buses share a common address range. One memory bus responds

to even-numbered cache lines, and the other bus responds to odd-numbered cache lines. This

configuration allows simultaneous use of both memory buses, which theoretically doubles

throughput. It is especially advantageous for applicatio ns that access memory randomly. In

random accesses, roughly half the requests at any one time are even-numbered lines, while the other

half are odd-numbered lines.

(cont.)

address

data

data

Cache

Accelerator

Memory Access

Controller (MAC)

A

Memory

Array

DD

Data Inter face

Buffer (DIB)

Cache

Accelerator

A

Memory

Array

address

address

data

address

Processor

bus

TC000603TB

6

Page 7

ECHNOLOGY BRIEF

T

.

.

The memory subsystem uses uniform memory access, which reduces latency and gives all

.

.

.

processors equal access times to either memory bus. In systems using nonuniform memory access

.

.

.

architectures, a processor has quick access to one memory bus but incurs a lag time (or latency)

.

.

.

.

when accessing a second memory bus.

.

.

.

.

The ProLiant 8000 server supports up to 16 GB of error checking and correcting SDRAM that

.

.

.

corrects all single-bit errors and detects double-bit errors. Memory is divided into eight banks,

.

.

.

each consisting of two dual inline memory modules.

.

.

.

.

.

Although the Profusion chipset supports up to 32 GB of memory, industry-standard OSs provide

.

.

.

only minimal support and scalability for this memory capacity, and enhanced support will not be

.

.

.

available for an extended period. Also, in discussions with customers, Compaq learned that very

.

.

.

few server implementations are fully configured with memory. With this in mind, Compaq used the

.

.

.

internal server space to provide additional drive capacity in the ProLiant 8000 server. As customer

.

.

.

requirements and OS capabilities increase in the future, Compaq will continue to modify servers to

.

.

.

match these requirements.

.

.

.

.

.

.

Cache Accelerators

.

.

.

.

One of the main challenges of designing an efficient SMP architecture is maintaining cache

.

.

.

coherency. To allow faster access to memory, most processors write data to cache memory rather

.

.

.

than to main memory. When a processor writes data to its cache, the cache has a newer copy of the

.

.

.

data than main memory. Cache coherency ensures that the most recent copy of the data is read by

.

.

.

any device that requests it. The cache coherency protocol essentially makes the cache look like

.

.

.

.

main memory. Cache coherency is critical for the proper operation of an SMP architecture, and the

.

.

.

performance and scalability of the architecture is affected by how efficiently it maintains cache

.

.

.

coherency.

.

.

.

.

With multiple processor buses and a separate I/O bus, it is extremely challenging to maintain cache

.

.

.

coherency in the 8-way architecture. Each memory access must look at, or snoop, the caches on its

.

.

.

local processor bus and snoop all caches on the remote processor bus and the I/O bus. The amount

.

.

.

of snoop traffic can significantly impact the scalability of the system.

.

.

.

.

.

The ProLiant 8000 architecture uses cache accelerators to minimize snoop traffic to the remote

.

.

.

processor bus and I/O bus. The cache accelerators store the address and state of the data for all

.

.

.

caches on their respective buses. The Profusion crossbar switch uses this information to determine

.

.

.

whether to snoop the remote processor and I/O buses. Depending on how often a software

.

.

.

application shares data, the reduction in snoop traffic can significantly improve overall system

.

.

.

performance and scalability.

.

.

.

.

.

.

I/O Filter

.

.

.

.

The ProLiant 8000 server also includes three Compaq host-to-PCI bridges with prefetch buffers, so

.

.

.

they act as caching bridges. The Profusion chipset contains a built-in I/O filter for the caching

.

.

.

bridges on the I/O bus. The I/O filter enhances performance by reducing snoop traffic on the I/O

.

.

.

.

bus. This I/O filter is designed to work with all three of the Compaq host-to-PCI bridges. When a

.

.

.

processor requests a cache line with the intent to modify it, the MAC performs a lookup into the

.

.

.

I/O filter to determine if that line resides in one of the caching bridges. If it does reside there, the

.

.

.

MAC initiates a transaction on the I/O bus to invalidate that cache line. If the cache line is not

.

.

.

present in one of the bridges, then no transaction is run on the bus.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

(cont.)

TC000603TB

7

Page 8

ECHNOLOGY BRIEF

T

.

.

Compaq Host-to-PCI Bridges

.

.

.

.

.

The Compaq host-to-PCI bridges included in the ProLiant 8000 server were engineered to enhance

.

.

.

performance of the Profusion chipset. They include the following features:

.

.

.

.

• 64-bit, 66-MHz PCI support with a theoretical peak throughput of 533 MB/s

.

.

.

.

.

• Delayed transaction support

.

.

.

.

.

• Asynchronous design to accommodate multiple bus frequencies

.

.

.

.

• Multiple prefetch buffers

.

.

.

.

.

• PCI Hot P lug technology

.

.

.

.

• Peer-to-peer transaction support

.

.

.

.

.

64-Bit, 66-MHz PCI Support

.

.

.

.

Compaq licensed the host-to-PCI bridges to Intel, and they will ship with a Compaq logo on top in

.

.

.

servers produced by other original equipment manufacturers. The bridges are compliant with the

.

.

.

PCI 2.2 Specification

.

.

.

.

.

The ProLiant 8000 server supports three bridges with up to eleven I/O expansion slots. PCI Bus 1

.

.

.

operates at 33 MHz and includes one 32-bit PCI Hot Plug slot and three 64-bit PCI Hot Plug slots.

.

.

.

PCI Bus 2 is also a 33-MHz bus and includes five 64-bit PCI Hot Plug slots. PCI Bus 3 operates at

.

.

.

66 MHz with two 64-bit PCI Hot Plug slots.

.

.

.

.

.

The Compaq 8-way architecture will support up to four Compaq host-to-PCI bridges. However, by

.

.

.

incorporating only three host-to-PCI bridges, the ProLiant 8000 server has room on the I/O board

.

.

.

to deliver an additional PCI slot, a meaningful advantage for enterprise customers who consistently

.

.

.

request additional capacity.

.

.

.

.

Delayed Transactions

.

.

.

.

.

One of the most important features of Compaq’s host-to-PCI bridge is that it supports delayed PCI

.

.

.

transactions, which improve bus performance. In a delayed PCI transaction, the device that

.

.

.

initiates the transaction polls the host-to-PCI bridge to determine if the requested data is there,

.

.

.

rather than holding the bus while waiting for the data. This allows other devices to use the bus

.

.

.

while the transaction is completed. To further improve bus efficiency, Compaq built in additional

.

.

.

features to reduce the amount of polling.

.

.

.

.

Asynchronous Design

.

.

.

.

.

The bridge is split into two sections: upstream (host I/O side) and downstream (PCI side). All the

.

.

.

functions on the upstream side are in the host processor clock domain at 100 MHz. All functions

.

.

.

on the downstream side are in the PCI clock domain at up to 66 MHz. This asynchronous design is

.

.

.

a flexible solution for supporting multiple clock speeds.

.

.

.

.

.

Multiple Prefetch Buffers

.

.

.

.

The Compaq host-to-PCI bridge is designed with multiple prefetch buffers to ensure optimum I/O-

.

.

.

to-processor performance. Each buffer can hold multiple cache lines. These buffers are sized to

.

.

.

provide optimal performance at a reasonable and cost-effective die size. Because of the delayed

.

.

.

transaction support, the bridge can get data for multiple PCI devices concurrently. Other

.

.

.

controllers can hold only a single cache line and a single request at a time.

.

.

.

.

.

.

.

.

.

.

.

.

.

1

.

PCI Local Bus Specification, Revision 2.2, announced January 25, 1999, PCI Special Interest

.

.

.

Group.

.

(cont.)

1

and support 64-bit, 66-MHz PCI transactions.

TC000603TB

8

Page 9

ECHNOLOGY BRIEF

T

.

.

PCI Hot P lug Technolo gy

.

.

.

.

.

The host-to-PCI bridges include electronics to support PCI Hot Plug technology, which was

.

.

.

pioneered by Compaq. PCI Hot Plug technology provides the ability to remove, replace, upgrade,

.

.

.

and add PCI adapters without shutting down the server. Any PCI adapter can be placed in a PCI

.

.

.

Hot Plug slot; however, PCI Hot Plug device drivers and OS support are required to enable PCI

.

.

.

Hot Plug functionality.

.

.

.

.

.

Peer-to-Peer Transactions

.

.

.

.

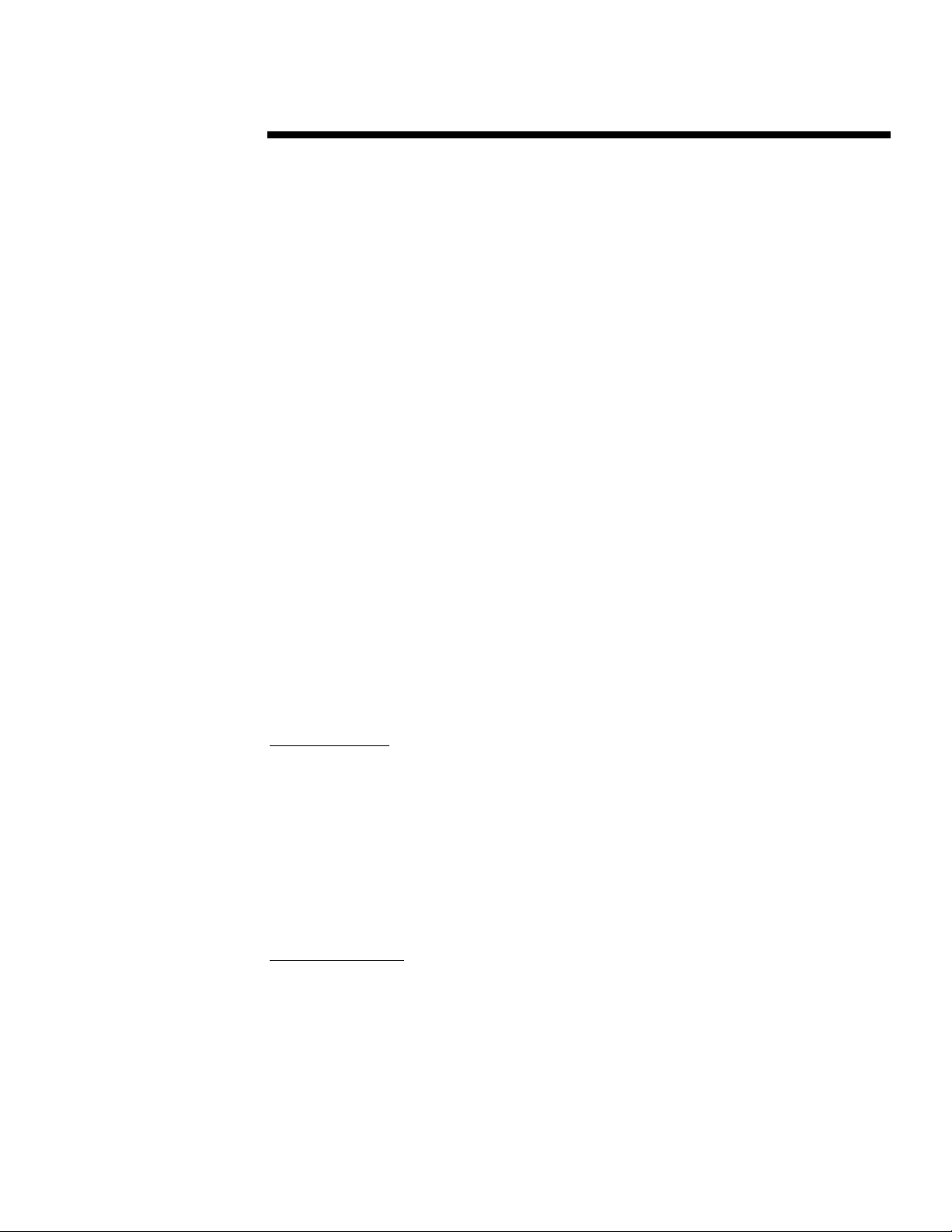

The host-to-PCI bridges also support PCI peer-to-peer transactions. They allow communications

.

.

.

between two devices on the same PCI bus segment. They also allow communication across the I/O

.

.

.

bus between PCI devices on different PCI bus segments (Figure 4).

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 4: Schematic of peer-to-peer communications between PCI devices on different I/O bus segments.

.

.

.

.

.

Microprocessors embedded in the PCI devices make these devices “intelligent” and perform the

.

.

.

communication tasks othe rwise handled by the processors. Thus, the host-to-PCI bridges enhance

.

.

.

performance by freeing the system processors to do other work.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Processor Bus

(cont.)

I/O 100 MHz Bus

Host-to-PCI Bridge

PCI Device 1

PCI Device 2

PCI Bus

PCI Device 3

Host-to-PCI Bridge

PCI Device 4

PCI Bus

PCI Device 5

TC000603TB

9

Page 10

ECHNOLOGY BRIEF

T

.

.

.

Pentium III Xeon Processor Technology

.

.

.

.

.

The Pentium III Xeon processor is based on the Pentium II Xeon processor cartridge form factor.

.

.

.

The Pentium III Xeon processor provides a higher internal core frequency than the Pentium II

.

.

.

Xeon processor and includes 70 new streaming instructions that permit more efficient use of

.

.

.

memory above 4 GB. The Pentium III Xeon processor includes the following features:

.

.

.

.

• Minimum 550-MHz core frequency

.

.

.

.

.

• 330-contact slot connector form factor (formerly called Slot 2)

.

.

.

.

• Full-speed cache on module

.

.

.

.

.

• 512-KB (550-MHz only), 1-MB, or 2-MB Level 2 (L2) cache

.

.

.

.

• Katmai core logic

.

.

.

.

.

.

Level 2 Cache

.

.

.

.

.

Each Pentium III Xeon processor includes an L2 cache sized at 512 KB, 1 MB, or 2 MB that

.

.

.

operates on a full-speed backside bus. The large cache size and full-speed backside bus enable

.

.

.

very efficient access to the most frequently used data. This reduces traffic on the host bus and

.

.

.

notably enhances performance.

.

.

.

.

.

.

Katmai Core Logic

.

.

.

.

Aside from speed and cache size increases, the main difference between the Pentium II Xeon and

.

.

.

Pentium III Xeon processors is the migration to the Katmai core logic. The Katmai core logic adds

.

.

.

.

the following enhancements to the existing Intel core:

.

.

.

.

• Memory streaming

.

.

.

.

.

• Concurrent Single Instruction Multiple Data – Floating Point (SIMD-FP)

.

.

.

.

• Katmai New Instructions (KNI)

.

.

.

.

.

Memory Streaming

.

.

.

.

Memory streaming is a set of techniques that increase the utilization of the memory bus during

.

.

.

memory reads and writes. Processors must frequently wait for data not stored in cache memory to

.

.

.

be retrieved from system memory. Because the system bus connecting the memory to the processor

.

.

.

is slower than the processor core speed, this results in a performance bottleneck. Katmai’s memory

.

.

.

streaming enables the processor to prefetch data from system memory to cache memory.

.

.

.

.

.

During writes to memory, other new instructions can tell the processor to bypass the L2 cache and

.

.

.

write data directly back to memory. Bypassing the L2 cache frees room in the cache for more data.

.

.

.

This technique is useful when the software programmer knows in advance that the data will not be

.

.

.

requested again in the near future.

.

.

.

.

.

Concurrent SIMD -FP

.

.

.

.

Concurrent SIMD-FP applies the same architecture used by MMX for integer operations to

.

.

.

floating-point numbers. Floating-point numbers are used extensively in 3D graphics and sci entific

.

.

.

computations. Katmai processors have eight new registers that can each hold four single-precision

.

.

.

floating-point numbers. Once the registers are filled, a single instruction can be used to add,

.

.

.

subtract, or do other operations between the registers. For example, eight floating-point numbers

.

.

.

could be added together using one instruction call.

.

.

.

.

.

.

.

.

.

.

.

.

.

(cont.)

TC000603TB

10

Page 11

ECHNOLOGY BRIEF

T

.

.

Katmai New Instructions

.

.

.

.

.

KNI refers to the addition of 70 new instructions to the MMX instruction set. The new instructions

.

.

.

primarily refer to the new SIMD-FP registers, but some new integer instructions also have been

.

.

.

added. The new instructions are particularly useful for multimedia applications such as 3D

.

.

.

rendering and video encoding and decoding.

.

.

.

.

.

.

.

IGH-AVAILABILITY TECHNOLOGIES

H

.

.

.

.

.

Tolerance of server downtime continues to decrease, as companies become more global,

.

.

.

decentralized, and aware of downtime costs. The ProLiant 8000 server answers the demand for

.

.

.

high availability by incorporating the following features into the server hardware:

.

.

.

.

.

• PCI Hot P lug technology

.

.

.

.

• Redundant array controller technology

.

.

.

.

.

• Redundant network interface controller (NIC) technology

.

.

.

.

• Redundant, hot-plug fans

.

.

.

.

.

• Redundant PPMs

.

.

.

.

• Redundant, hot-plug power suppli es

.

.

.

.

.

• Hot-plug drives

.

.

.

.

Redundant components help ensure that the server is highly fault tolerant. In redundant

.

.

.

configurations, if a power supply, fan, or PPM fails, the redundant standby component can take

.

.

.

over operation with no downtime to the server. With the addition of hot-plug capabilities, server

.

.

.

downtime can be eliminated while components are being replaced, added, or upgraded.

.

.

.

.

.

.

.

PCI Hot Plug Technology

.

.

.

.

.

The Compaq ProLiant 8000 server incorporates industry-standard PCI Hot Plug technology. This

.

.

.

technology, pioneered by Compaq, adds hot-plug capabilities to existing PCI adapters for increased

.

.

.

system availability and serviceability. Compaq led the industry by licensing its PCI Hot Plug

.

.

.

implementation to Intel, thus broadening customer access to this industry-standard technology.

.

.

.

.

Compaq’s implementation of PCI Hot Plug incorporates electronics into the server to control each

.

.

.

PCI Hot Plug slot individually, so that a single slot can be powered down without affecting the

.

.

.

operation of the other slots. Compaq’s implementation of the PCI Hot Plug standard allows the

.

.

.

following capabilities while the system is running:

.

.

.

.

.

• Hot replacement – replacing a single PCI adapter with a similar adapter

.

.

.

.

• Hot upgrade – replacing a PCI adapter with an upgraded adapter

.

.

.

.

.

• Hot expansion – adding a PCI adapter to an empty slot

.

.

.

.

.

The ProLiant 8000 server supports all three hot-plug capabilities for all 64-bit and 32-bit PCI Hot

.

.

.

Plug slots. These capabilities can be added incrementally, depending on the OS implementation.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

(cont.)

TC000603TB

11

Page 12

ECHNOLOGY BRIEF

T

.

.

For more information about major OS vendors that support PCI Hot Plug, refer to the following

.

.

.

Compaq technology briefs:

.

.

.

.

.

• PCI Hot Plug Technology, document number ECG080/0698

.

.

.

.

.

• PCI Hot Plug Technology with Novell Architecture, document number ECG081/0698

.

.

.

.

• PCI Hot Plug Technology with SCO Software Architecture, document number ECG082/0698

.

.

.

.

.

• PCI Hot Plug Technology with Microsoft Windows Architecture, document number

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

ECG071/0399

Redundant Array Controller Technology

The ProLiant 8000 server supports up to two Compaq Smart Array 4250ES controllers in a

redundant configuration. The Smart Array 4250ES controller is specially designed for use in the

ProLiant 8000 server. See “Storage Technologies” for more information on the array controller

technology in the ProLiant 8000 server.

Smart Array 4250ES controllers may be used in PCI connectors 10 and 11. These connectors

attach the 64-bit PCI bus and four Wide Ultra-3 SCSI buses to the Smart Array 4250ES controllers.

All five buses are common to both connectors, and thus common to both controllers. Three of the

SCSI buses are routed to SCSI connectors on the I/O board. Cables are preinstalled from these

three SCSI connectors to the three SCSI drive cages. The fourth SCSI bus serves as a link between

the two controllers. This link allows two Smart Array 4250ES controllers to be easily installed in

the ProLiant 8000 server to provide controller redundancy. The Smart Array 4250ES controller is

a Wide Ultra SCSI device so the internal drive cages and the Wide Ultra-3 SCSI buses will run in

Wide Ultra SCSI mode.

The two controllers monitor each other’s status and maintain cache coherency between them. Both

controllers (the primary and secondary controller) are attached to the same drives in an activestandby mode. If the primary controller fails, the secondary controller immediately assumes

command of the drive array with no interruption of server operation or loss of data. PCI Hot Plug

technology allows a failed controller to be replaced without rebooting the server.

The SCSI subsystem uses a simplified cable design that allows the drive cages to be connected

directly to the I/O board. The design eliminates cumbersome loop-back cables while allowing

cable-free redundancy and hot-plug capability.

Redundant Network Interface Controller Technology

Compaq’s redundant Netelligent NIC technology allows two similar NICs to share a single instance

of device driver code. One NIC becomes the active network controller and the other NIC acts as a

standby controller. If the active NIC fails, the network traffic is automatically switched to the

standby NIC. This redundancy eliminates the NIC or cable as a single point of failure. With PCI

Hot Plug technology, the failed NIC can be replaced without rebooting the system. Thus, the end

user can have continuous service and the administrator can greatly reduce planned and unplanned

downtime.

The ProLiant 8000 server supports a Compaq NC3131 Fast Ethernet controller on the PCI local

bus. The NIC has two ports for 10BaseT or 100TX Ethernet. The ports are seen as two separate

local area networks, both supporting full-duplex Ethernet (20 Mb/s) and Fast Ethernet (200 Mb/s).

Redundancy is available across the two ports with one NIC. In addition, the NIC is upgradeable

with a daughter card to an additio nal two ports of 100BaseTX Ethernet, a single port of 100

BaseFX, or single-port Gigabit Ethernet SX or LX Fiber support. Redundancy is also available

here; the NIC can be configur ed to failo ver from the Gigabit daughter c ard to the dual 10/100 ports

in the event of a failure, thus allowing continued access to the network.

(cont.)

TC000603TB

12

Page 13

ECHNOLOGY BRIEF

T

.

.

.

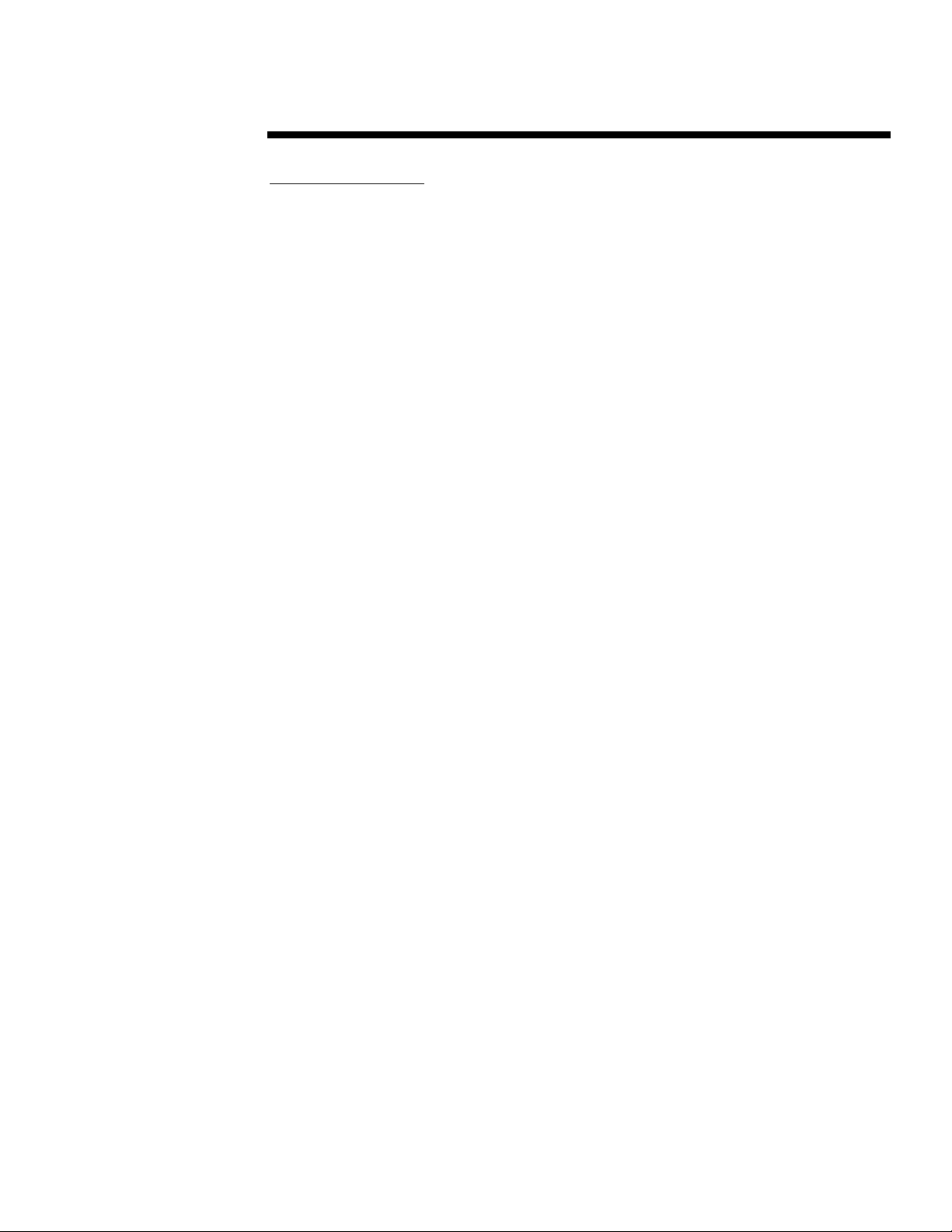

Redundant Hot-Plug Fans

.

.

.

.

.

The ProLiant 8000 server has four primary hot-plug fans (external) and four redundant fans

.

.

.

(internal) for the processor and memory section. The rear pair of primary hot-plug fans for the

.

.

.

processor and memory section is enclosed in a single fan unit (Figure 5). This unit can be easily

.

.

.

removed by means of a single thumbscrew. The front pair of primary hot-plug fans is enclosed in

.

.

.

another single fan unit (Figure 6), which can be easily removed by means of a latch. The primary

.

.

.

hot-plug fans spin under rotor control while the internal, redundant fans spin freely in the server

.

.

.

airflow because they are not required for cooling. If the primary fan unit fails, the redundant fans

.

.

.

will start automatically. The hot-plug light-emitting diodes (LEDs) indicate the status of the fans:

.

.

.

green indicates the fans are functioning properly, and amber indicates the fans have failed.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 5: Rear hot-plug fans for the processor and memory section of the ProLiant 8000 server.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 6: Front hot-plug fans for the processor and memory section of the ProLiant 8000 server.

.

.

.

.

.

Thumbscrew

for removal

Hot-Plug LEDs

Hot-Plug LEDs

Latch for removal

(cont.)

Redundant fan unit

Primary fan unit

Redundant fan unit

Primary fan unit

TC000603TB

13

Page 14

ECHNOLOGY BRIEF

T

.

.

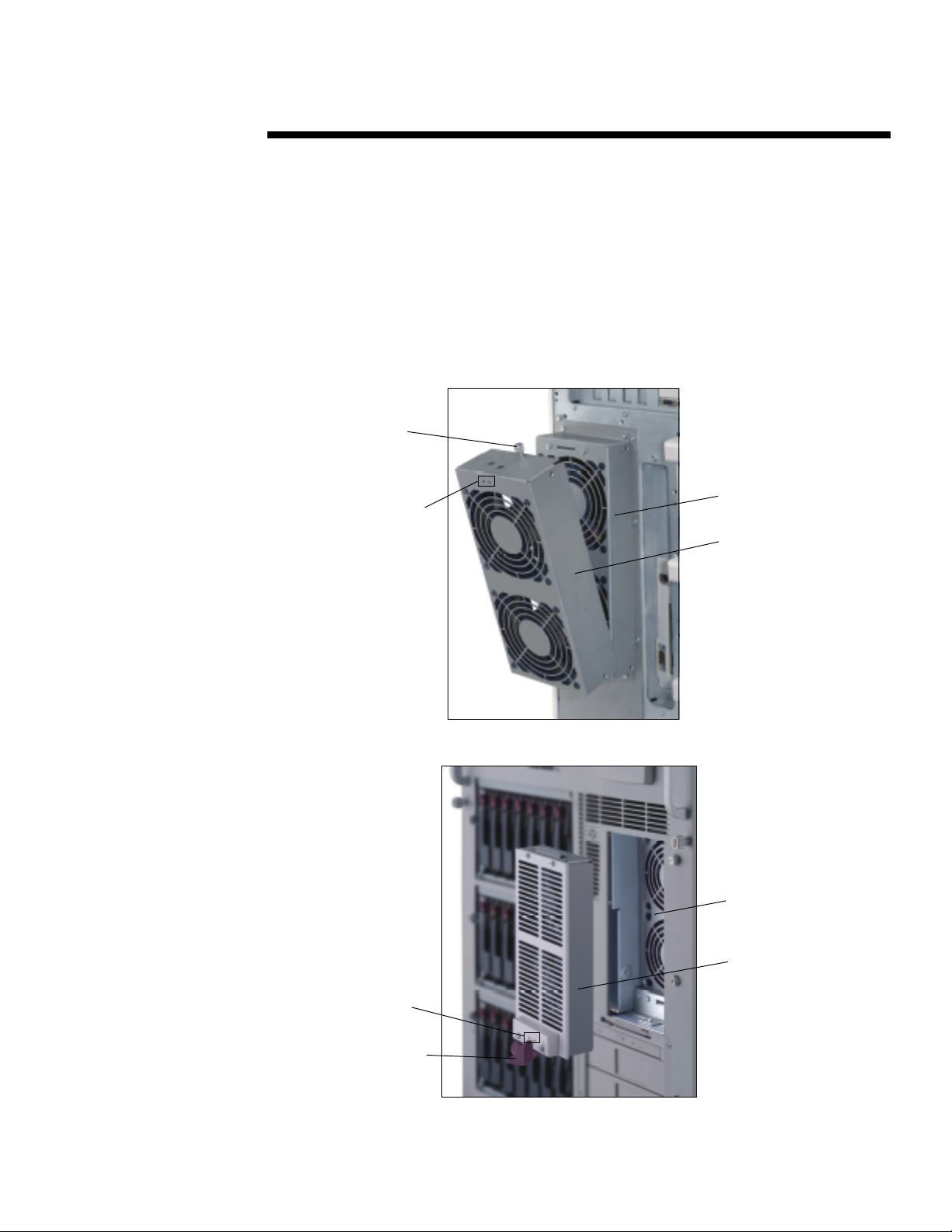

The server also has two hot-plug fans for the I/O board in the upper section of the server (Figure 7).

.

.

.

Only one operating fan is needed to cool the I/O board. The other fan provides redundancy. If the

.

.

.

operating fan should fail, the other fan would start automatically and continue cooling the I/O

.

.

.

.

board. When the failed fan is replaced, redundancy is restored.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 7: Hot-plug fans for the I/O section in the

.

.

.

.

The fan control logic operates independently from the system processor and OS. Regardless of

.

.

.

which OS is running or its condition, the fan control logic and the ser ve r temperature monitoring

.

.

.

circuitry work together to cool the server effectively.

.

.

.

.

.

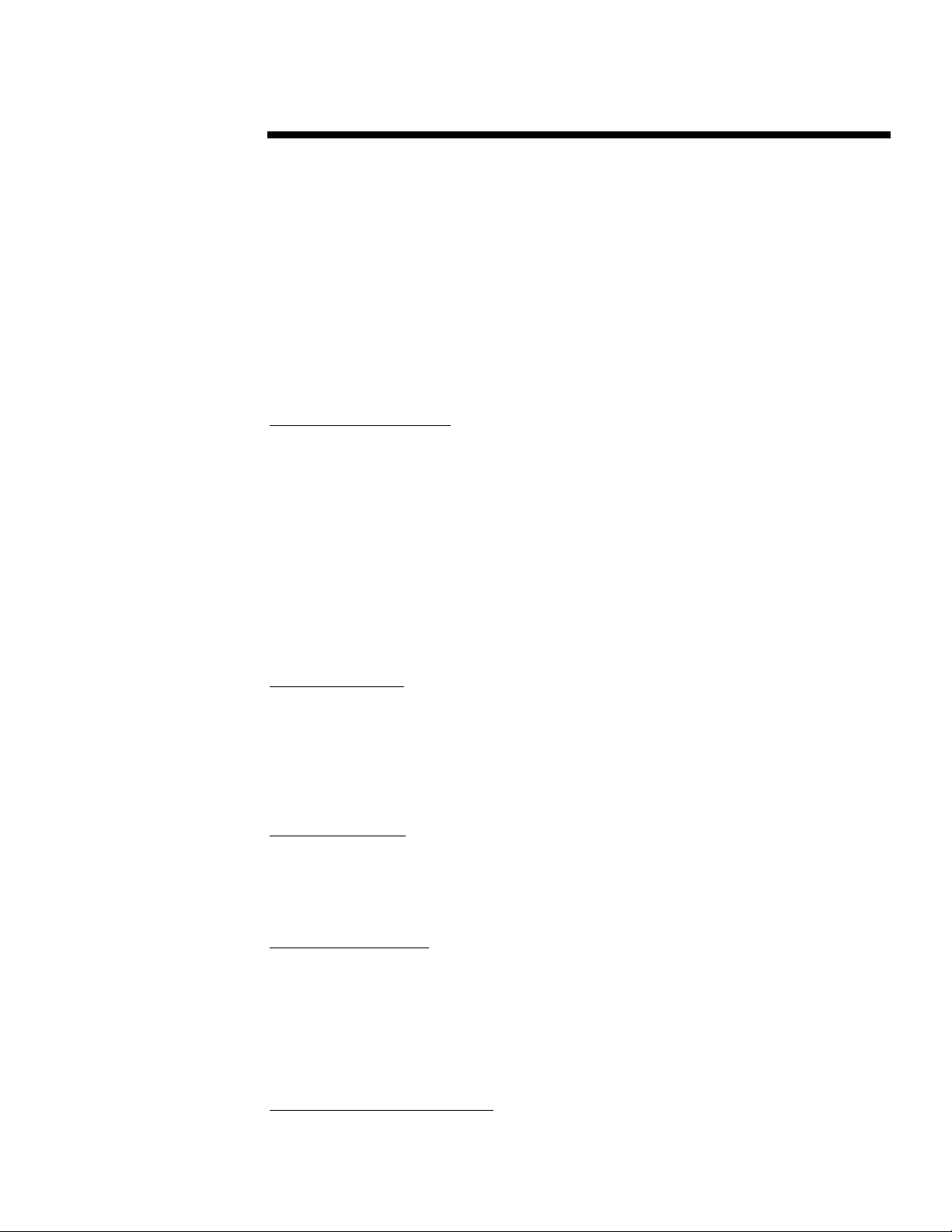

The fans have two speeds: normal and high. Under typical operating conditions, the normal fan

.

.

.

speed is sufficient to cool up to 8 processors, 21 hard disk drives, and 11 I/O expansion boards. As

.

.

.

a precaution against increases in ambient air or localized internal temperatures, Compaq

.

.

.

established three thermal trip points, as shown in Figure 8. If the first thermal trip point is reached,

.

.

.

the fans adjust automatically to high speed to increase cooling.

.

.

.

.

.

Users can select whether to enable a server response to the second thermal trip point. When

.

.

.

enabled, if the internal air temperature exceeds the second trip point, the OS initiates a controlled

.

.

.

shutdown of the server. Si multaneously, a warning message is sent to t he Integrated Management

.

.

.

Display (IMD) and Compaq Insight Manager. The server restarts automatically when it has cooled

.

.

.

sufficiently.

.

.

.

.

Finally, in the unlikely event server temperature continues to rise, a third trip point shuts down the

.

.

.

power supplies to protect critical components from overheating. The server restarts automatically

.

.

.

when it has cooled sufficiently.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

(cont.)

Hot-Plug LEDs

ProLiant

8000 server.

TC000603TB

14

Page 15

ECHNOLOGY BRIEF

e

y

d

s

T

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Power

Supplies

Temperature Monitoring

Circuitry

Fan Control Logic

System Fans

Figure 8: Schematic diagram of fan control logic.

Redundant Processor Power Modules

Each processor in the ProLiant 8000 server has its own redundant PPM. An additional PPM is

included in the server to power the system board. PPMs are also known as voltage regulator

modules. The PPMs deliver the precise voltage required by the processors.

Compaq PPMs are programmable and support all current and future versions of Xeon processors.

Each PPM has redundant circuitry. If a failure occurs in one circuit of the module, the other circuit

automatically takes over the task of regulating power to the processor.

Redundant Hot-Plug Power Supplies

The ProLiant 8000 server uses one of the newest Compaq technologies to reduce downtime:

intelligent, redundant, hot-plug power supplies. The server ships standard with two dual-rated

1150-watt/500-watt power supplies and supports three power supplies for an N+1 redundant

configuration. The power supplies are connected to a separate power backplane in the server and

include new handles for easier insertion and removal. If one of the power supplies fails, its internal

fans will continue to operate and help cool the server.

The power supply has an embedded microcontroller and an inter-integrated circuit bus that

communicates the status back to the system health drivers.

information to the IMD and to Compaq Insight Manager.

2

For additional details about Compaq’s intelligent power supplies, see the technology brief

Intelligent Power Supply Technology, document number ECG016/0198.

(cont.)

System Boards

Ambient Probe

Power Supplies

Processors

OS

- Hardware shutdown

Har

•

- Restart when cool

Re

•

- Graceful OS shutdown

- System alert

- Restart when cool

Sp

•

- Speed up fans

S

•

2

The health drivers then send status

TC000603TB

15

Page 16

ECHNOLOGY BRIEF

T

.

.

The microcontroller performs the following functions:

.

.

.

.

.

• Self-test. The intelligent power supplies perform their own power-on self-test (POST) that

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

checks temperature, RAM integrity, ROM version, analog-to-digital conversion accuracy, and

nonvolatile memory integrity of the power supply.

• Auto Line Sensing. Because the power supplies are rated for both 1150 watts (at 220 volts)

and 500 watts (at 110 volts), a line-sensing feature automatically recognizes which line voltage

is connected. The customer does not need to configure the supply for voltage.

• LED Standby Controls. The microcontroller also drives two status LEDs on the back of the

power supply that indicate power status, as shown in Figure 9. This gives the user vital status

information at a glance.

Figure 9: Power supply LED status indicators.

Power-Down Controls

As shown in Figure 10, the server power switch connects to the Advanced Configuration and Power

Interface (ACPI) controller rather than directly to the power line. This means that turning off the

power switch does not turn off power instantly. Instead, the ACPI controller communicates with

the system board and the OS. The power-down controls can be configured in one of three ways:

• Secure mode – Power supply will not shut down if power switch is pressed.

• Delay mode – Power supply will shut down after a 10-second delay. This allows time to

reactivate the switch if it was mistakenly pressed.

• Graceful shut down – A 10-second delay counter begins as a message warning of an imminent

power-down goes to Compaq Insight Manager and the IMD. Because of the communication

between the ACPI controller and the OS, the OS can delay the power down until all running

applications have properly closed. Should the OS not be running, the power would go down

when the delay counter expired.

The power-down control feature is supported under Microsoft Windows NT and Novell NetWare.

SCO is planning to implement support for the power-down control in the future.

(cont.)

Clear - Front panel power switch off or open inter lock

Flashing Green - Power on delay or software power off

Green - Outputs on and good

Flashing Amber - Failed self test

Amber - Outputs failed

Flashing Amber/Green - Restart failed

Green - AC power good

Clear - AC power not good

TC000603TB

16

Page 17

ECHNOLOGY BRIEF

T

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 10: Power supply schematic.

.

.

.

.

.

.

Load Balancing

.

.

.

.

The power supplies automatically load balance to within 10 percent of the average current of all

.

.

.

supplies. Before the power comes up, the master power supply matches its output load rails to

.

.

.

those of the other power supplies so that the load is automatically balanced across all power

.

.

.

supplies. If one supply fails, the load balancing feature allows the other supplies to pick up the

.

.

.

remaining power load quickly.

.

.

.

.

.

.

Power Factor Correction

.

.

.

.

.

Compaq’s intelligent power supplies have built-in power factor correction to synchronize the

.

.

.

voltage and current phases. This helps ensure that maximum power is available. It also reduces the

.

.

.

return current in the ground line, which reduces the overall power consumption.

.

.

.

.

.

.

Hot-Plug Capability

.

.

.

.

.

When a power supply is hot swapped, the microcontroller governs the power-up and power-down

.

.

.

sequences, enables the health drivers to calculate redundancy “on the fly,” and informs the health

.

.

.

drivers of changes in load. Compaq hot-plug power supplies are readily identifiable by their port-

.

.

.

colored bezel, as shown in Figure 11.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 11: Front view of hot-plug power supply with port-colored bezel.

.

.

.

.

.

OS

Power

Switch

Port-colored bezel

(cont.)

System

Board

ACPI

Controller

Power

Backplane

Soft Power Down

DC

I2C Bus

Power On

Power Supply

AC/DC

Converter

Microcontroller

AC

TC000603TB

17

Page 18

RAID – Redundant Array of

Independent Disks

ECHNOLOGY BRIEF

T

.

.

.

Hot-Plug Hard Disk Drives

.

.

.

.

.

The ProLiant 8000 supports up to three Wide Ultra-3 SCSI internal drive cages. Each ProLiant

.

.

.

8000 internal drive cage can support a maximum of seven 1-inch hot-plug drives (for a total of 21

.

.

.

drives with all three drive cages installed). When the server is configured for maximum capacity, it

.

.

.

can support 382 GB of internal storage. Capacity will increase in the future as new drive

.

.

.

technologies emerge.

.

.

.

.

.

.

.

TORAGE TECHNOLOGIES

S

.

.

.

.

.

As corporations commit more critical information to computers, the requirements for more storage

.

.

.

capacity and faster data movement are increasing at a startling rate. The Compaq ProLiant 8000

.

.

.

server includes new storage technologies that help meet these requirements. New hard drive

.

.

.

technology and a specially designed array controller allow the ProLiant 8000 server to deliver the

.

.

.

highest levels of internal storage capacity faster and with more reliability.

.

.

.

.

.

.

Hard Drive Technology

.

.

.

.

.

The Compaq ProLiant 8000 server uses low-voltage differential (LVD) Ultra-3 SCSI hard drives.

.

.

.

These new one-inch drives allow the ProLiant 8000 server to support 21 total drives—three drive

.

.

.

cages with seven hard drives each—for a maximum internal storage capacity of 382 GB of data.

.

.

.

.

Ultra-3 SCSI hard drives use a 16-bit bus and a double pumped 40-MHz clock rate to achieve

.

.

.

maximum transfer rates of 160 MB/s. This bus speed provides the performance demanded by

.

.

.

today’s data-intensive applications and prevents system performance from becoming I/O limited as

.

.

.

drive throughp uts increase.

.

.

.

.

.

Although the ProLiant 8000 server supports Wide Ultra-3 SCSI hard drives, the internal drive

.

.

.

cages and the Wide Ultra-3 SCSI buses will run in Wide Ultra SCSI mode with the Smart Array

.

.

.

4250ES controller, which is a Wide Ultra SCSI device.

.

.

.

.

.

.

.

Array Controller Technology

.

.

.

.

The ProLiant 8000 server supports up to two Compaq Smart Array 4250ES controllers—providing

.

.

.

high-performance and ease-of-use features. The Smart Array 4250ES controller offers three Wide

.

.

.

Ultra SCSI channels, allowing a single controller to support all three internal hot-plug hard drive

.

.

.

cages in the new ProLiant 8000 server. Since all three drive cages run off the same RAID engine,

.

.

.

all 21 internal hot-plug hard drives can be configured as one massive 382-GB array or multiple

.

.

.

smaller arrays.

.

.

.

.

.

Additionally, the Smart Array 4250ES controller uses a 64-bit PCI Hot Plug extended SCSI

.

.

.

connector and a cable-less design that is optimized for the ProLiant 8000 server. The extended

.

.

.

SCSI connector gives customers the flexibility to accommodate both 64-bit and 32-bit technology.

.

.

.

The cable-less design allows the hard drive cages to be directly connected to the I/O board itself,

.

.

.

not the array controller. This means much easier PCI Hot Plug usage and the elimination of

.

.

.

cumbersome loop-back cables.

.

.

.

.

.

The Smart Array 4250ES controller supports RAID levels 0, 0+1, 1, 4, and 5. In addition, the

.

.

.

controller uses a Compaq developed RAID 5 engine that optimizes RAID 5 performance. The

.

.

.

controller also supports online spares, which improves overall system fault tolerance by

.

.

.

automatically replacing a failed drive and quickly restoring the system to full RAID protection.

.

.

.

.

The Smart Array 4250ES controller includes a robust 64 MB of battery-backed read/write cache.

.

.

.

Rechargeable batteries are integrated into the cache, which is actually a removable card installed

.

.

.

onto the Smart Array 4250ES controller base card. The removable DRAM and batteries keep

.

.

.

posted-write data secure in the unlikely event that the base controller board should fail. If a system

.

.

.

(cont.)

TC000603TB

18

Page 19

ECHNOLOGY BRIEF

T

.

.

power outage occurs while write data is stored in the cache, the data will be protected for at least

.

.

.

four days on power supplied by the battery backup system. If the base controller board should fail,

.

.

.

the cache board can be installed on a replacement base card. Once system power is returned, the

.

.

.

.

posted write data is automatically written to disk.

.

.

.

.

.

.

.

ANAGEMENT TECHNOLOGIES

M

.

.

.

.

Fault-tolerant, redundant features are only part of what makes Compaq servers highly available.

.

.

.

Compaq offers a range of hardware- and software-based server management tools that can be used

.

.

.

to reduce downtime and increase productivity. The ProLiant 8000 server includes the following

.

.

.

standard tools available to all Compaq servers:

.

.

.

.

.

• Automatic Server Recovery. ASR automatically resets the server after a critical hardware or

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

software error. ASR can reset the server to the OS or to the System Partition Utilities. The

ASR reset function is based on a hardware timer working in conjunction with the Server Health

Drivers. If the Server Health Drivers can no longer reset the hardware timer after some userspecified amount of time, the server is automatically reset. ASR can also be configured to

page the administrator when an ASR event occurs.

• System Partition Utilities. These utilities assist the system administrator in diagnosing server

problems, co nfiguring new hardware, and upgrading ROMs. For example, an administrator

can analyze the system configuration files to verify that no interrupts or other conflicts are

causing system failures. The System Partition Utilities are available when the server is reset.

ASR can be configured to reset automatically to the System Partition Utilities; or the

administrator can reboot to the System Partition Utilities through Compaq Insight Manager.

• Compaq Insight Manager. This software-based management tool monitors more than 1,000

management parameters to allow fault prediction and alerting, asset and configuration

inventory, and performance monitoring. Through Compaq Insight Manager, a remote

administrator can request an OS console operation, reset the server, view utilities, and view

system configuration information. See the white paper Compaq Insight Manager, document

number 11CW-1199A-WWEN, for more details.

• Asynchronous Insight Management. Asynchronous Insight Management provides access to

Compaq Insight Manager through a d ial-up networking, o r asynchronous, connection. This

gives an administrator additional flexibility in troubleshooting problems. If the server OS is

still functioning, an administrator can dial in remotely and access Insight Manager through a

point-to-point protocol (PPP) connection.

In addition to these utilities, the ProLiant 8000 server also ships standard with additional

management technologies that reduce downtime and increase productivity even more. Remoteflash Redundant ROM allows administrators to update the ROM remotely, and the auto-default

ROM configurati on provides default configuration settings fo r most devices. The IMD and

Integrated Remote Console (IRC) provide essential information at a glance and allow users easy

remote access to their servers. For additional remote management functionality, customers can

request that the optional Remote Insight Board/PCI be added to the ProLiant 8000 server.