Page 1

HEWLETT-PACKARD

HP

7942

AND

HP

7946

DISC/T

SERVICE

APE

DRIVES

MANUAL

Page 2

CERTIFICATION

Products,

have

Packard

taining

Hewlett-Packard's

the

National

Bureau's

The

ments

materials,

been

provided

specifications.

to

this

order

Bureau

calibration

Hewlett-Packard

of

FAR 52.246-15.

parts,

in

is

calibration

facilities.

and

accordance

Actual

on

file

of

Standards

Quality

services

inspection

and

available

measurements

Program

with

to

the

furnished

all

extent

satisfies

on

applicable

and

test

for

examination.

are

traceable

allowed

the

this

order

Hewlett-

data

by

require-

per-

to

the

Page 3

rlin-

.:~

HEWLETT

PACKARD

The main

and subsequent.

part

7942

DISC/T

PRINTED: FEB 1 987

Prin ted in

of

this manual applies directly to

Refer

to Appendix A

for

In addition to the standard models, this manual

covers

the

SERVICE

AND

APE DRIVES

Manual

Microfiche

U.S.A.

serial numbers prefixed

following options:

part

no.

part

no.

Serial Number Prefix

HP

7942

and

OPTIONS COVERED

FOR U.S.A. ONLY

MANUAL

7946

07942-90903

07942-90803

07942-90903

HP

7946

Disc/Tape

2614

and prior.

01

5 and 550.

E0287

Drives with serial numbers prefixed

2615

The Federal Communications Commission (in 47 CFR 15.838) has specified

lowing notice be brought to

FEDERAL

the

attention

of

the users of this product.

COMMUNICATIONS COMMISSION

RADIO FREQUENCY INTERFERENCE

STATEMENT

Warning:

strict

been

specifications

interference

ticular

by

lowing measures:

ment

the

prepared

Problems".

004-000-00345-4.

This

equipment

accordalllce

type

install~ltion.

turning

away

dealer

by

with

test.~d

and

in

Subpart

ill a

residential

the

equipment

reorient

from

the

or

3,uthorized field

tllte

Federal

This

booklet

generates

the

manufacturer's

found

to comply

J of

If

this

equipment

off

the

receiver;

Communications

is

available

and

with

Part

15 of FCC

installation.

does

and

on,

the

receiving

plug

the

equipment

service

representative

from

P.O.

uses

radio

frequeucy

instructions,

the

limits

Rules,

which

However,

cause

user

antenna;

Commission

the

HEWLETT -PACKARD COMPANY

BOX

there

interference

is

encouraged

relocate

into a different

for

U.S.

Government

39

BOISE,

energy

may

cause

for a Class B

are

designed to provide

is no

guarantee

to

radio

to

try

the

equipment

additional

helpful:

"How to

IDAHO

interference

computing

to

correct

branch

suggestions.

Printing

83707,

and

if

not

installed

to

disc/tape

that

interference

or

television

the

interference

with

respect

circuit.

The

Identify

Office, WashingtoD,

U.S.A.

radio

reasonable

reception,

to

If

necessary,

user

and

and

and

television

drive

the

may

Resolve

that

used

properly,

in

accordance

protection

will

not

which

by one

receiver;

the

user

find

the

Radio-TV

DC

the

reception.

against

occur

can

be

or

more

move

should

following

Interference

20402.

fol-

that

is,

in

It

has

with

the

such

in a par-

determined

of

the

fol-

the

equip-

consult

booklet

Stock

No.

Page 4

PRINTING HISTORY

New editions incorporate all update material since

sued between editions, contain additional and revised information

user. The date on

First Edition

Second Edition

Third

Edition .

..

the

title page changes only when a new edition

FEB 1985

AUG

1986

FEB 1987

the

previous edition. Updating Supplements, which are

to

be incorporated into

is

published.

the

manual

by

is-

the

The information contained in this document

HEWLETT-PACKARD

MATERIAL,

MERCHANTABILITY AND FITNESS FOR A

liable for errors contained herein

ing, performance

This document contains proprietary

part

of

Hewlett-Packard

COREFILE-PARCORE

INCLUDING, BUT NOT LIMITED TO,

or

this document may be photocopied

Company.

MAKES NO

or

for incidental or consequential damages in connection

use of this material.

information

is

WARRANTY

NOTICE

subject to change

OF ANY KIND WITH

PARTICULAR

which

is

or

reproduced

protected by copyright. All rights are reserved. No

without

THE

PURPOSE.

without

notice.

IMPLIED WARRANTIES OF

REGARD

Hewlett-Packard

the

prior

written

with

the

TO THIS

shall not be

furnish-

consent of

11

Page 5

PREFACEI

This publication provides field service

HP

7942

consists of a

an

integrated

in a similar manner.

This publication

• Section I - Contains a general description of

• Section

• Section

• Section

• Section V - Supplies

and parts in the

• Section

• Appendix

number

• Tape Drive - Consists of a Tape Drive Service Manual. This

tion

for

disc/tape

II

- Provides references to

III --Describes the operating principles of

IV

--

VI

--

A-Contains

prefix

the

tape drive portion of

24-megabyte

drive. The

is

divided into

Contains servicing

step-by-step

disc/tape

Lists and illustrates

2614

and prior.

the

drive.

removal

information

disc drive and a tape drive combined in a single desktop cabinet to form

HP

7946 consists of a

following parts:

the

CS/80

information

removal and replacement procedures for field replaceable assemblies

the

field replaceable assemblies and parts in

and

replacement and relaceable parts for

the

disc/tape

for the

the

disc/tape

Instruction Set commands applicable to

the

for

the

drive.

HP

55-megabyte

drive.

disc/tape

disc/tape

7942

drive.

drive.

manual

and

HP

7946 Disc/Tape Drives. The

disc drive and a tape drive combined

the

disc/tape

the

disc/tape

disc/tape

provides detailed service

drive.

drives

drive.

with

informa-

serial

iii/iv

Page 6

Page 7

CONTENTS

Section

GENERAL

I

INFORMATION

Introduction

Documentation

Related

Manuals

Options

Ch

a r

act

e r i s t

il

c s

Section

CHANNEL

Introduction

CS/80

Transaction

Real

II

INTERFACE

......

Instruction

Time

Commands

Structure

Complementary

General Purpose

Diagnostic

Transparent

Commands

Messages .

Hewlett-Packard

HP-IB Communications

Channel Management

Paralll~l

Poll

Universal

Message

Structure

.

Set

Commands

Commands

Interface

Device

Clear

..

Bus

Page

1-1

1-1

1-2

1-2

1-2

Page

2-1

2-1

2-1

2-1

2-1

2-9

2-9

2-9

2-9

2-12

2-13

2-13

2-13

2-13

Section

THEOR

III

Y OF

Introduction

Disc

Drive

Disc Format

HOC

peA-AS

HOC

Internal

HP-IB Data

RAM

Microprocessor

Microprocessor

DMA

Read/Write Data

Data/Control

Control/Status

Control/Status

Control/Status

OPERATION

Introduction

.........

Data

........

Bus

Bus

Bus

.

.

Architecture

........

.

Address

Data

Gate Array Data

Bus

Interface

Data

Read

Write

Bus

Bus

Bus

Bus

Bus

Strobe

Strobe

Page

3-1

3-2

3-4

3-6

3-6

.

3-7

3-7

3-7

3-7

3-7

3-7

3-7

3-8

3-8

3-8

v

Page 8

CONTENTS (continued)

Control/Status

Select

Read/Write

Data

Request

Da

ta

St

robe

HP-IB

Microprocessor

HP-IB

Channel

Sel

Self

DMA

RAM

EXEC

DOC 0 EPROM

DOC

Address

Clocks

ROM

Buffers

Typical

DOC

HOC/DOC

DOC/Disc

Controller

Disc

Phase-

Latch

DMA

Clock

Write

Disc

Disc

Input

Output

Disc

Microprocessor

Microprocessor/PLA

Clock

Head-Disc

Interface

Address

Status

f Tes t Swi

Test

Display

Ga

te

Array

...........

EPROM

1 E

PROM

Multiplexer

And

Sw

i t c h . . . . . . . . . . . . . . . _ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HOC

PCA-A2

Control/Status

Read/Wri

Receiver/Driver

Transceivers

HDA

Self-Test

GPC

DOC

PUPO

Drive

Actuator

.................................................

Commu

Drive

Desc r

Register

Err

0 r s

Register

Controller

Loc

ked

...................................................

Handshake Cont

Generator

Precompensation

A1

Drive

Buffers

Drivers

Drive

Generator

Module

Address

..............

Data

Bus

In/Data

In/Da

ta

IC

.....

Switch

...

tches

IC . . . . . . . . . . . . . . . . . . . . . .

. . . .

..

.........................................

..................................

........................................

Control

Transaction

n i

te

IC and

ipt

Register

Loop

.............................................

A1/DDC

A1/DDC

.....

Logic

cat

ion

Data

Data

Bus

........................................

..........................

A1

Communication

Register

ion

PROM

...........................................

Reg

i s t e r

...........................

IC

....................

IC

rol

.........................................

Control

..........................................

..........................................

Data

and

PLA

Control

...........................................

..........................................

Bus

.

Request

St

robe

.,

................

.......................................

. . . . . . . . . . . . . . . . . . . . . .

......................

......................

....................................

.....................................

..................

and

.....................................

.....................................

.......................

.....................................

.......................................

......................................

....................................

Communication

Communication

.....................................

Out

......

Ou t ........

Address

Decode Logic

Signals

Buses

.............

..........................

.

.

.

.....................

.......

......................

........................

............................

..............

.

..............

.

..............

. . . . . . . . . . . . . . . .

.

..............

.

..............

.

..............

.

.........

.

.........

.....

.

, . . . . .

.

.....

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-8

.

.

.

.

.

3-9

3-9

3-9

3-9

3-9

3-9

3-9

.

.

3-9

3-9

3-9

....

,3-10

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

3-10

3-10

3-10

3-10

3-11

3-11

3-11

3-11

3-12

3-12

3-12

3-12

3-12

3-12

3-12

3-13

3-13

3-13

3-13

3-13

3-14

3-14

3-14

3-14

3-15

3-15

3-15

3-15

3-15

3-15

vi

Page 9

CONTENTS (continued)

Recording

Read/Wri

Read

Preamplifier/Write

Servo

Servo

Spindle

Air

Filtration

Actuator

Spindle

Spindle

Spindle

Speed

Speed Checker

Motor Brake Relay and Relay

Actuator

Demodu

Mode

Select

~Iode

Seek

Velocity

Tachometer

Slclpe

Current

On-Peak

Power

Inverter

Track--Follow

Off-Track

Seek Operation

Restore

Read/Wri

Head

SelE!ct and

Read

Chain

Ampli f

Differential

Wri

te

Line Receiver

Transition

Write

Write

Sel f test

Power Supph'

AC

Input

Swi

tch-Mc)de

Power-On Reset

Medium

te

Heads

Head

........

Preamplifier

Moto r ......

Lock

Driver

Control

Servo

la

Control

to r .....

Switch

DAC

Selector

Inverter

Detector

Amplifier

.....

Mode

Detector

to

Track 0 Operation

t.e

Data Channel

Control

............

ier/Signal

Chain

........

Generator

Current

Fault

......

A4

Circuits

Supply

....

............

............

.

IC

.

.

Components

.

.

.,

.

.

.....

Logic .

Condi

Line

Driver

.

....

.

Source

Detector

.

Driver

.

tioner

.

.

IC

Driver

..

3-15

3-16

3-16

3-16

3-17

3-17

3-17

3-17

3-17

3-17

3-17

3-17

3-18

3-18

3-18

3-18

3-18

3-19

3-19

3-19

3~19

3-19

3-19

3-19

3-19

3-19

3-20

3-20

3-20

3-20

3-20

3-20

3-20

3-20

3-21

3-21

3-21

3-21

3-21

3-22

3-22

Section

SERVICE

IV

INI4'ORMATION

Introduction

Service

FRA

Tools

Locations

Page

4-1

4-1

4-2

vii

Page 10

CONTENTS (continued)

Cable Connections

Signal

Power

Signal

Distribution

Distribution

Notation

Block Diagram

Power Supply

HDC

PCA-AS

Self

Test

Self-Test

A4

...

....

Controls

Tape Drive

Tape Drive

Disc Drive

Se

1 f T

est

Sw

Self-Test

DISPLAY

Internal

Sel

f Test

Self-Test

Display

RESULTS

Diagnostics

...........

Subtests

Self-Test

Fault/On Line

Self-Test

Request

Request

Run

Time

Error

External

Amigo

Cancel

Test

Exerciser

Clear

Transaction

HP-IB

..

..

.

.

FAULT

BUSY

Indicator

Indicator

FAULT/ON

i t c h

Switch

Error

Reporting

Indicator

Display

Status

Status

and

Fault

........

(AMCLEAR)

Channel

....

.....

Example

(CANCEL)

(CHANNEL)

Channel Independent

Clear

Describe

Perform

Output

Exit

Output

Output Help

Initialize

Update Device

Request

Perform Read-Only

Output

Spare

Output Spare Table

Logs

Selected

Internal

Error

Program

Fault

Media (INIT

Status

Run

Sector

(CLEAR

LOGS)

Unit

Diagnostics

Rate

Test

(EXIT)

Log

(FAULT

Information

Logs

(PRESET)

(REQSTAT)

Error

Log

(RUN

(SPARE)

(SPARE

Output Device Table

Perform Servo

Set

Unit

Test

Number

(SERVO)

(UNIT)

Perform Write-Then-Read

Troubleshooting

Disc Drive Maintenance

Tape Drive Maintenance .

LINE

Indicator

.

...

.

.

Reporting

.

Clear

(CICLEAR)

........

(DESCRIBE)

Log

.......

LOG)

(HELP)

MEDIA)

....

Rate

LOG)

.....

........

TABLE)

(TABLES)

......

Error

(DIAG)

(ERT

.

.

Test

Rate

.

.

LOG)

(RO

.

.

.

Test

ERT)

(WRT

ERT)

4-2

4-2

4-2

4-2

4-2

4-2

4-3

4-3

4-3

4-3

4-3

4-4

4-4

4-4

4-4

4-5

4-S

4-6

4-6

4-6

4-7

4-8

4-9

4-9

4-9

4-9

4-10

4-10

4-10

4-10

4-10

4-10

4-10

4-10

4-10

4

-11

4-11

4

-11

4-11

4-11

4-11

4-11

4-11

4-11

4

-11

4-11

4-11

4-11

4-12

4-12

viii

Page 11

CONTENTS (continued)

Section

REMOVAL

Introduction

Preparation

Removal And Replacemen t

Top

EPROM

FRA5

Front

U1-FRA1 (Tape

Fan

UO-FRA4

UO-FRA1

UO-FRA2

U1-FRA2 (Tape

Section

REPLACEABLE

Introduction

Ordering

Appendix

REMOV

V Page

AND

REPLACEMENT

For

Service

ShroUid

Ki

(HDG

Panel

...............................................

LED

Cable

VI

.......................................................

t s

.......................................................

PCA-A5)

......................................................

Drive

(Power

(Disc

(Disc

Supply

Drive

Drive

Drive

Removal

PARTS

Information

A

AL

AND

.....

REPLACEMENT

.

...............................................

...............................................

.................................................

Assembly

Assembly

Assembly

DDC

DDC

...............................................

A1)

A1)

PCA-A2)

PCA-A2)

......................................

A4)

....................................

......................................

......................

...............................

.

...........

.

..............

.

.......

.

........

....

.

5-1

5-2

.

5-2

.

5-2

.

5-2

.

5-3

.

5-3

.

5-3

.

5-4

.

5-5

.

5-5

.

5-6

.

5-6

.

5-7

Page

6-1

6-1

Page

Introduction

Preparation

Removal And

Top

EPROM

FRA5

Front

U1-FRAl (Tape

Fan

UO-FRA4

UO-FRAl

UO-FRA2

U 1 -FRA2 (Tape

Appendix

For

Replacement

Shroud

Ki

ts

(HDC

PCA-A5)

Panel

...........................................................

(Power

(Disc

(Disc

A

REPLACEABLE

Introduction

Ordering

Appendix

Information

B

SER VICE NOTES

Service

......................................................

......................................................

.....................................................

Drive

Supply

Drive

Drive

Dr

i ve

..............................................

..............................................

................................................

Assembly

Assembly

Assembly

DOC

DOC

A1)

A1)

PCA-A2)

PCA-A2)

.....................................

A4)

...................................

.....................................

.....................................

.....................................

PARTS

.....

.

A5-1

A5-1

.

A5-2

.

A5-2

.

A5-2

.

A5-3

.

A5-3

.

A5-3

.

A5-4

.

A5-5

.

A5-5

.

.

A5-6

A5-6

.

Page

A6-1

A6-1

Page

B-1/B-2

ix

Page 12

ILLUSTRATIONS

Figure

Transaction

Hewlett-Packard

Disc Recording Format

Track Recording Format

Disc/Tape

Disc

Drive,

Disc

Drive,

Disc

Drive,

Drive,

Disc

Front

Rear Panel

P8

P8

P8

Field

Power

UO-FRA4

UO-FRA4

FRA5

FRAl

FRA2

Disc/Tape Cabling Diagram

Disc

Panel

Signal

Signal

Signal

Replaceable

Distribution,

(HOC

(Disc Drive

(DOC

Signal

Structure

Interface

Drive,

Self-Test

Source (Sheet 1 of 3)

Source (Sheet 2 of 3)

Source (Sheet 3 of 3)

(Power Supply Assembly A4), Layout and Cable Connections

(Power Supply Assembly A4),

PCA-A5),

PCA-A2),

Block Diagram

Block Diagram

Functional

Functional

Functional

Self-Test

Al),

Distribution

Block

Block

Block

Display

Display

Assembly

Cable Assembly

Layout and Cable Connections

Layout and Cable Connections

Layout and Cable Connections

......

Bus

Signal

Diagram,

Diagram,

Diagram,

(FRA)

.

Lines

(Sheet

(Sheet

(Sheet

Locations

Wl

Test

1 of 3)

2 of

3

Points

3)

of 3)

and

Voltages

Page

2-10

2-11

· 3-5

· 3-6

3-31/3-32

3-33/3-34

3-35/3-36

3-37/3-38

3-39/3-40

4-12

4-13

4-21

4-22

4-23

4-28

4-29

4-30

4-31

4-32

4-33

4-34

4-35/4-36

4-37/4-38

Order of Disassembly

HP

7942/HP

HP

7942/HP

Disc/Tape

Order of Disassembly

Disc/Tape

x

7946

7946

Drive,

Drive,

Cable

Major Assemblies

Exploded

Exploded

Interconnections

View

View

.....

.

5-11/5-12

5-8

5-9/5-10

·

6-3

A5-8

A6-3

Page 13

TABLES

Tables

Disc Drive

Device

Disc Drive

HP-IB

Universal

HP-IB Message

list

of Mnemonics

Host Dependent

Self-Test

Characteristics

Command

Summary

Utilities

Definitions

Command

Structure

Controller

Subtest

Disc Drive (Unit

Disc Drive

Fault

Diagnostic

Code

Error

List

Summary

Disc/Tape Drive

Abb

rev

ia

Code

t ion s

list

.........

o'f

Manufacturers

Disc/Tape Drive

Abbreviations

Code

list

.........

o'f

Manufacturers

.....

Formats

.....

List

0)

Self-Test

......

Condition

.........

Replaceable

.

Replaceable

.

(Unit 2)

Subtest

List

.

Parts

.....

Parts

.....

Page

1

-3/1-4

2-2

2-9

2-12

2-12

2-14

3-23

.

List

4-14

4-15

4-20

4-24

4:-27

6-2

6-4

.

.

6-5/6-6

A6-2

A6-4

A6-5/A6-6

xi

Page 14

SAFETY

CONSIDERATIONS

GENERAL

tion must

safety markings

-

-

- This product

be

WARNING

and

related

reviewed for

and

instructions before operation.

SAFETY SYMBOLS

Instruction

product will be

symbol

the

user to

tion

manual

the

product

Indica tes hazardous voltages.

Indicates

WARNING

The

hazard. It calls

procedure

not

correctly

hered to, could result in personal

injury. Do

WARNING

cated

conditions

stood

and

familiarization

manual

when

it

refer

in

against damage.

earth

(ground) terminal.

or

practice

performed

not

sign

met.

documenta-

with

symbol:

marked

is

to

order

sIgn denotes a

proceed beyond a

until

are

with

necessary for

the

instruc-

to

protect

attention

which,

or

the

indi-

fully

under-

to a

the

this

if

ad-

BEFORE

product

power source according to

figuration

If

this

former

connected to

source.

SERVICING

APPLYING

is

configured to

instructions provided in this manual.

product

make sure

is

the

POWER

match

to be operated

that

earth

terminal

WARNING

Any servlcmg,

tenance'

must

trained

Adjustments

manual

power supplied to

protective

Energy

may,

sonal injury.

Capacitors

still be

has

main

or

be

performed

personnel.

may be

available

if

contacted, result in

charged

been disconnected

power source.

adjustment,

repair

described in

covers

inside this

after

- Verify

the

the

input

with

the

common

of

of this

only

by

performed

the

product

are

at

many

product

the

from

available

power

an

autotrans-

terminal

the

main

main-

product

service-

this

with

while

removed.

points

per-

may

product

the

that

power

the

main

con-

is

CAUTION sign denotes a

CAUTION

SAFETY

class I

earthing

ground must be provided

source to

power cord,

it

is

the

secured against

xii

EARTH

product

terminal. An un

likely

product

The

hazard.

operating procedure

which,

or

damage to

or all

proceed beyond a

un

fully understood

and

the

product

or

supplied power cord set. Whenever

that

the

must be made inoperative

any

if

adhered to, could result in

of

til

the

GROUND - This

is

provided

protection

unintended

It

calls

attention

or

practice

not

correctly

or

destruction

the

product. Do

indica ted conditions

and

with

interruptible

from

the

input

wiring terminals,

has been impaired,

operation.

performed

CAUTION

met.

is

a safety

a protective

safety

main

to

of

earth

power

and

an

part

not

sign

are

be

To avoid a

the

proper

the

specified type (normal blow,

time

delay, etc.)

replacement.

To

install

disconnect

device. Then, using a small

bladed screw driver,

fuseholder

until

either

into

the

and

fuseholder by pressing

ward

until

it

fire

hazard,

current

or

remove a fuse,

the

cap

the

cap

end of a properly

cap. Next,

fuseholder

and

then

locks in place.

rating

must

power cord

counterclockwise

releases.

insert

cap

turning

fuses

be

used

from

turn

rated

the

into

the

cap

it clockwise

with

and

for

first

the

flat-

the

Install

fuse

fuse

the

in-

of

Page 15

GENERAL INFORMA TION

-

[TI

1-1.

The

Drives are medium performance, random access,

data

and

consists of a

drive

an

sists

combined in a similar manner. In this manual,

less otherwise specified, "drive" refers to both

HP

The

and

(5.l2-inch)

Each disc surface employs one movable head to

service its

lowest disc in

prerecorded

precise positioning

Head positioning

tuator

Mechanical and contamination protection for

discs, heads, and

a sealed head-disc module. The head-disc module

includes a

which supplies clean

throughout the module.

The tape drive

removable

lengths are available: 150 feet (16.7 megabyte) and

600 feet (67 megabyte). The tape drive functions

as a back

transfer

megabytes per minute. (The actual

rate

read

as well

The tape drive

1/4-inch

HP

INTRODUCTION

Hewlett'-Packard 7942 and 7946 Disc/Tape

storage devices designed for use

medium sized computer systems. The

24-megabyte

combined in a single desktop cabinet to form

integrated disc/tape drive. The

of

a 55-megabyte disc drive and a tape drive

7942 and

24-

is

-after-write

disc/tape drives.

HP

7946.

and

55-megabyte

four non removable

discs, respectively, for storage media.

data

tracks. The bottom surface of

the

servo

data

of

the

is

accomplished by a

and closed loop servo positioning system.

the

rotary

slelf

-contained

air

is a data

1/

4-inch

-up

device for

rate

for back

host dependent.) The tape drive includes a

capability for

as

data

recovery and automatic sparing.

is

cartridge tape drives contained in

disc drive and a tape

disc drives employ two

stack contains continuous

which

tape cartridge. Two tape

-up

compatible

is

used

read/write

actuator

air

filtration

and equalizes

storage device utilizing a

the

disc drive. The

is

approximately two

data

with

small

HP

7942

HP

7946

con-

130-millimetre

to

ensure

heads.

rotary

is

provided by

system

temperature

data

data

transfer

verification,

with

existing

other

un-

the

the

the

ac-

the

Also included in

Interface

supply.

The drive contains

and a

functions of

tomatically

by the host or by a switch on

drive.

green/red

failure occurs, information on the cause

failure can be determined by viewing a

numeral display on

is

to a

and power supply), followed by field replaceable

sembly or assemblies within

Details

The drive

cabinet. Accessories available include a

height stand -alone cabinet designed to hold

drive and

rack mounting

ment

1 -

The documentation provided in this publication

divided into two parts. The first part, H P

and

(Sections I through

disc drive and tape drive are combined in a single

cabinet to form

Information provided includes circuit description,

servlclng details, removal and replacement

procedures, and replaceable parts information.

Detailed information on the disc drive theory

operation, service information, and replaceable

parts

by the

documentation for

Bus

fault-finding

Go/no-go

unit

of

subtest failures are also provided.

other

rack

is

2.

DOCUMENT A TION

7946

is

also provided. The second part, identified

liT

the

drive are a

(HP-IB)* controller and a power

internal

system which exercise key

the

drive. Self test

at

power on and can also be initiated

test results are indicated by

indica tors on the f ron t panel.

the

rear

level (disc drive, tape drive, controller,

is

packaged in a stand -alone desktop

desktop stack modules. A

the

drive in a standard EIA

also available.

Disc/Tape

an

APE DRIVE" tab, contains service

the

Drives

VI)

provides details of how

integrated disc/tape drive.

tape drive.

Hewlett-Packard

self

-test

is

performed

the

rear panel

panel.

Fault

the

identified unit.

Service

diagnostics

au-

of

the

If

of

the

2-digit

isolation

as-

desk-

the

kit

for

equip-

7942

Manual,

the

a

is

of

*Not just

computation system.

IEEE-488,

but

the hardware, documentation and support

that

delivers the shortest

path

to a

1-1

Page 16

General

Inf

orma tion

7942 and 7946

Note: The two parts of

fit

will

binder,

in a 1

part

no.

equivalent binder may be used.) A

cover and spine insert kit,

07942-90909,

publication

for

the

which identifies

as

the

HP

7942

Disc/Tape Drives,

the

9282-0502

binder.

the

publication

1/2-inch

9282-0502.

part

service

manual

and 7946

is

available for

3-ring

(An

no.

the

1

-4.

OPTIONS

The following options are available for

Option 015. For

selector switch set

non-U.S. shipments. Voltage

at

factory for

operation.

Option 550. Deletion of

the

HP 1083 3A HP-IB

Interface Cable Assembly.

the

drive:

230-Vac

1-3.

RELATED MANUALS

For operating and installation instructions, refer to

the

H P

7942

and

7946

Disc/Tape

Manual,

Environmental

Manual,

information,

Programming

part

part

no.

refer

Manual,

no.

09742-90901,

Requirements

5955-

3456. For instruction set

to

the

part

for

CS/80

no.

additional servicing information,

CS/80

no.

External

5955-3462.

Exerciser

The HP

Reference Manual,

7942

Disc/Tape Drive CE Handbook

Drives

and

Disc/Tape

Instruction

5955-

3442. For

refer

and

HP 7946

is

part

Owner's

the

Site

Drives

Set

to

the

part

no.

07942-90905.

1

-5.

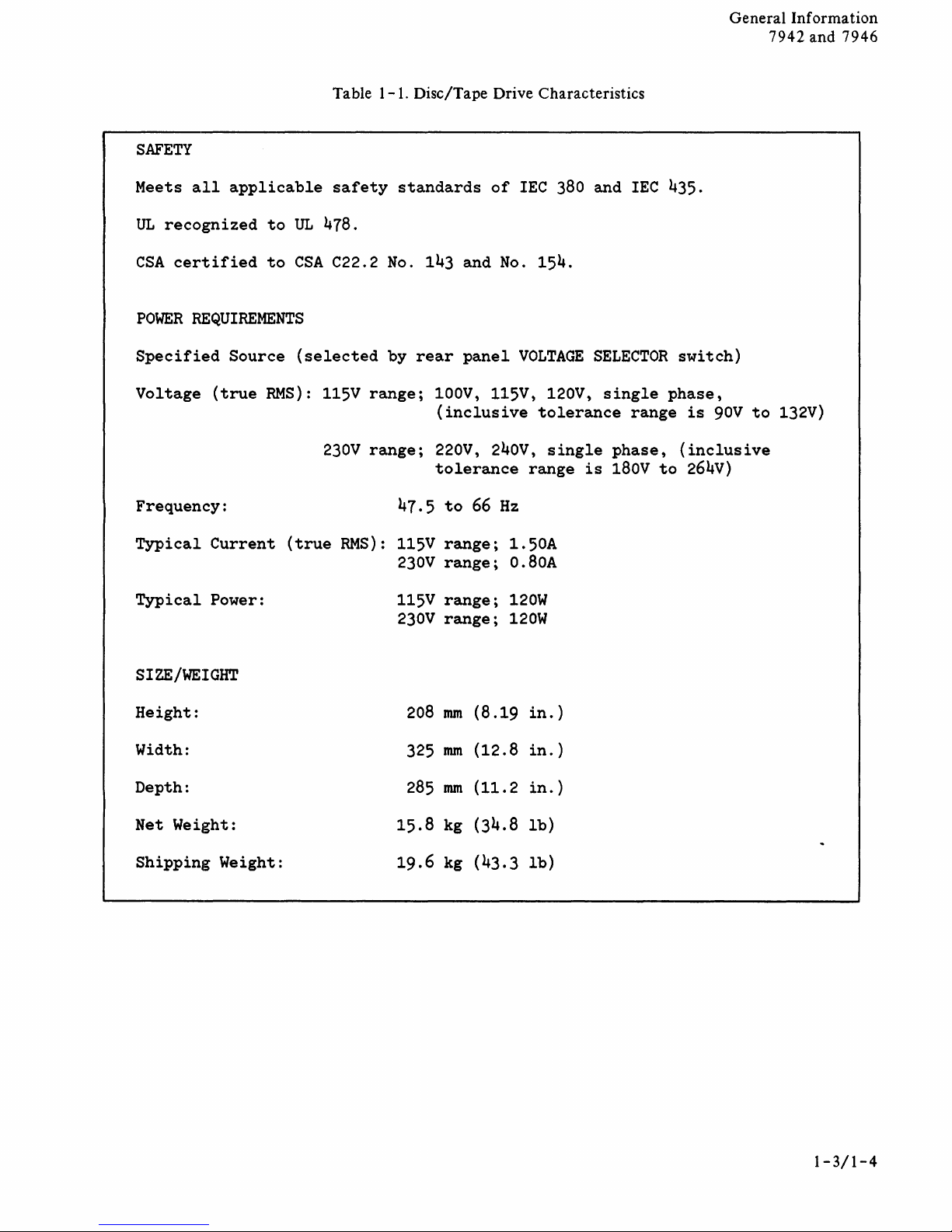

CHARACTERISTICS

Characteristics of the

physical dimensions

listed in table

disc/tape

and

power requirements, are

1-1,

drive, including

Disc/Tape Drive

Characteristics. Detailed specifications for

c/tape

ments, are listed

Requirements

no.

the

Service

tics of

drive, including environmental

in

Site

for

5955-3456.

disc/tape

Manual

the

tape drive.

Disc/Tape

This publication

drive. Refer to

for specifications

Drives Manual,

Environmental

is

supplied

the

H P 9

and

characteris-

the

dis-

require-

part

with

I44A

1-2

Page 17

SAFETY

Table

1-1.

Disc/Tape Drive Characteristics

General Information

7942 and 7946

Meets

UL

CSA

POWER

Specified

Voltage

Frequency:

Typical

Typical

all

recognized

certified

REQUIREMENTS

(true

Current

Power:

applicable

to

UL

to

CSA

Source

(selected

RMS):

(true

safety

47B.

C22.2

115V

230V

RMS):

standards

No.

by

range;

range;

47.5

115V

230V

115V

230V

of

IEC

143 and

rear

100V, 115V, 120V,

(inclusive

220V, 240v,

tolerance

to

range;

range;

range;

range;

panel

66

No.

154.

VOLTAGE

tolerance

range

Hz

1.50A

O.BOA

120W

120W

3BO

single

is

and

IEC

435.

SELECTOR

single

phase,

1Bov

phase,

range

to

switch)

is

90V

(inclusive

264V)

to

132V)

SIZE/WEIGHT

Height:

Width:

Depth:

Net Weight:

Shipping

Weight:

20B

325

2B5

15.B

19.6

nun

nun

nun

kg

kg

(B.19

(12.B

(11.2

(34.B

(43.3

in.

in.

in.

lb)

lb)

)

)

)

1-3/1-4

Page 18

Page 19

CHANNEL

INTERFACE

-

QIJ

2-1.

Interface

through

hardware

commands

The following paragraphs discuss

CS/

HP-IB.

CS/80

no.

CS/80

the

2-2.

The

and

for

Instruction

of

their

Command

CS/80

lows a host

within

in

formed

or

Drive Utilities.

Reference

details.

2-3.

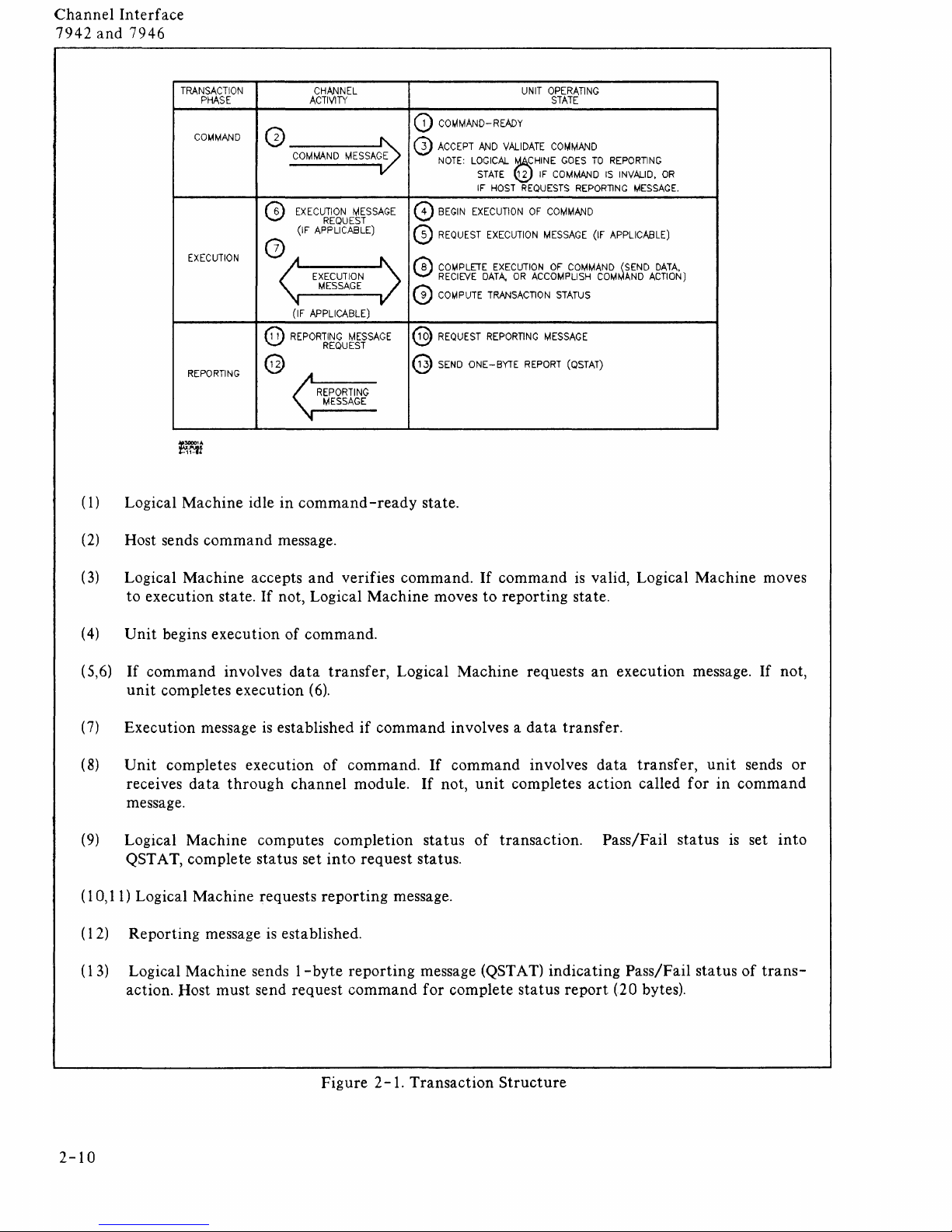

A

tween

device (the disc drive) over a given

(HP-IB).

transaction: command, execute,

transaction

the

indicating

by

structure,

disc drive

relative

INTR~ODUCTION

to

the

disc/tape

Hewlett-Packard

and

the

CS/80

formulated

80 commands. Also provided

For

full details of

Instruction

5955-3442.

instructions apply

H P

9144A

CS/,BO

increase in capabilities of

mass storage devices has emphasized

efficient

Set increases

channel

firmware

logged. Utilities

TRANSACTION

transaction

disc drive,

the

operations between disc memories

associated host computers. Table

Summary, provides a

instructions.

the

disc drive. Utilities

which

and

the

Manual,

a system host

Three

begins

the

host. Figure 2 - 1 ill

and

operating

to

each phase.

Set

For

Service

INSTRUCTION

channel

The

computer

allow

results of such tests

are

Refer

part

is

a logically complete

phases

when a command

and

ends

status

of

shows

the

states and

drive

is

Interface

Instruction

for

mass storage devices.

is

CS/80,

Programming

information

to

the

tape

Manual,

communication.

to

to

STRUCTURE

computer

when a reporting

the

Part

both

the

efficiency

summary

CS/8 0 Instruction

access special utilities

are

error

rate

listed in

the

no.

may

transaction

ustra

relationship between

table

External

5955-

and a peripheral

occur

and

tes

the

the

channel

accomplished

Bus (HP-IB)

Set, a set of

the

an

overview

refer

Manual,

on how

drive

II,

Installation.

host computers

The

2-1,

routines stored

tests

to

be examined

3462,

operation

during

report. A

is

received by

transaction

types of

to

part

refer

SET

the

need

CS/80

and

speed

Device

of

Set

to

be

per-

2-2,

Disc

Exerciser

for

channel

each

message

is

accepted

activity

of

the

the

to

and

all

al-

full

be-

the

A

unit

is

a separately addressable

device (disc drive). A volume

dressable portion of

given unit.

2-4.

REAL

Real

time

time. These commands

host/

device transactions. One

tary

commands

in

order

time

Real

cate

and

2-5.

COMPLEMENTARY

Complementary

date

programmable states in

programmable states

set unit, set address, set block displacement, set

return

retry

set

Rotational

These commands

Time,

messages,

When a complementary

embedded

meters

plementary

duration

complementary

meters or conditions

complementary

until

power-on

plementary

Therefore,

equal

command

used

for

though

porarily override this value

complementary

of 256 bytes (for 1 sector).

TIME

commands

to

modify

commands include: locate

write,

and

addressing mode, set length, set

time, set release, set

Position Sensing (RPS) window size.

General

or

they

within

or

conditions established by

command(s)

of

the

commands to

at

power-on,

the

entire

may

give

an

entire

some special case commands could

the

storage media

COMMANDS

are

optimized

are

may

precede a real

the

operation

cold load read.

COMMANDS

commands

define

may

Purpose, or Diagnostic

may

another

current

command, however, sets

command

occurs.

volume. A

it a lise

sequence of transactions,

command

are

characteristics such

be included

stand

alone.

command (or commands)

command,

are

command. A

until

the

alters

Power-on

length

stand-alone

til

to set a

entity

is a separately

for

used most

or

more com pie

time

of

that

and

used to set

the

disc drive.

burst

status

altered

their

value

same

the

resets all

default

is

of 1 kbyte

with

"current"

mask,

within

only

stand-alone

stand

set value

defaulted

an

within

within

execution

often

men

command

command.

read,

or

upThe

mode,

and

Real

command

the

para-

that

com-

for

the

para-

-alone

com-

values.

Set

Length

to

tem-

embedded

value

ad-

in

lo-

as:

set

is

the

or

to

be

al-

a

a

-

2-1

Page 20

Channel

7942

and

In

terf

7946

ace

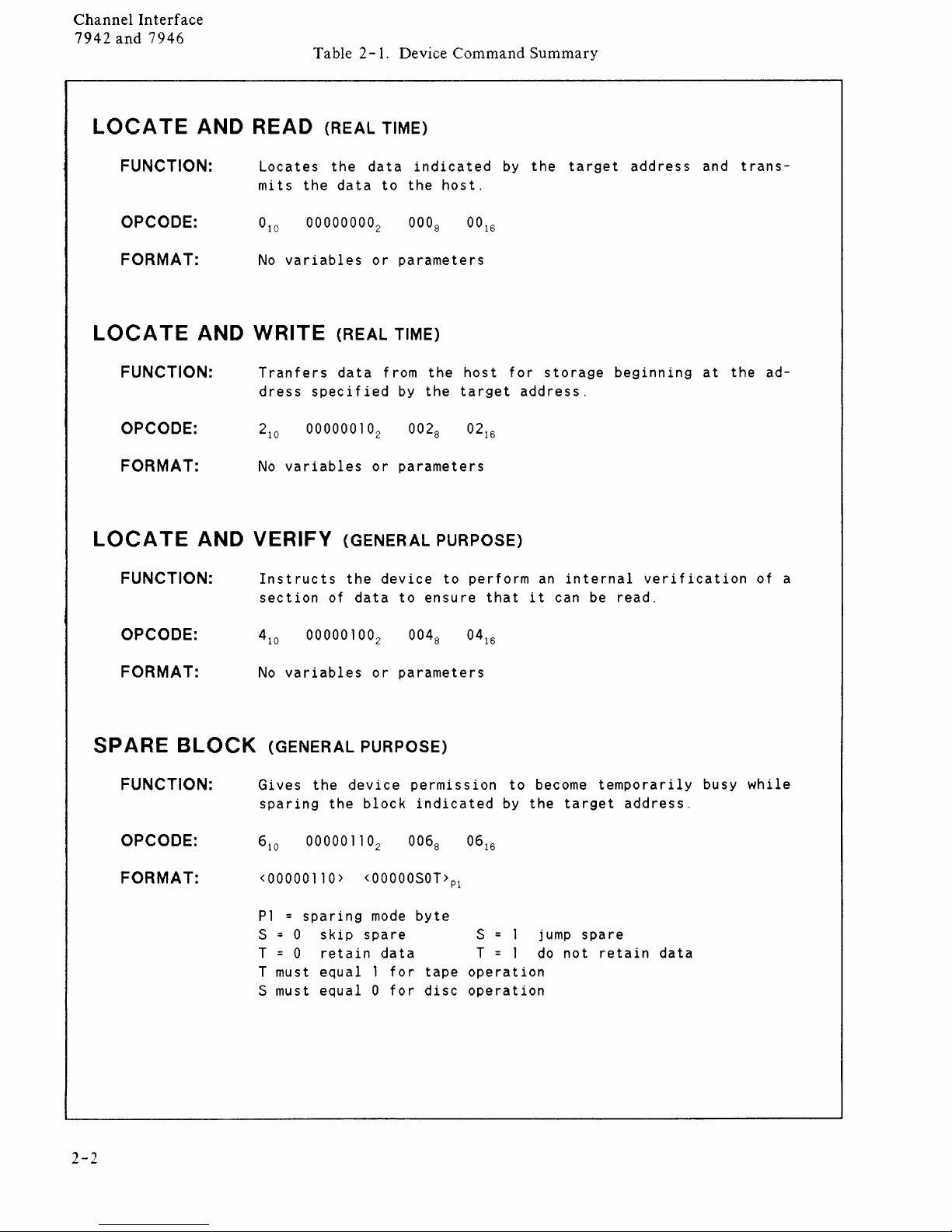

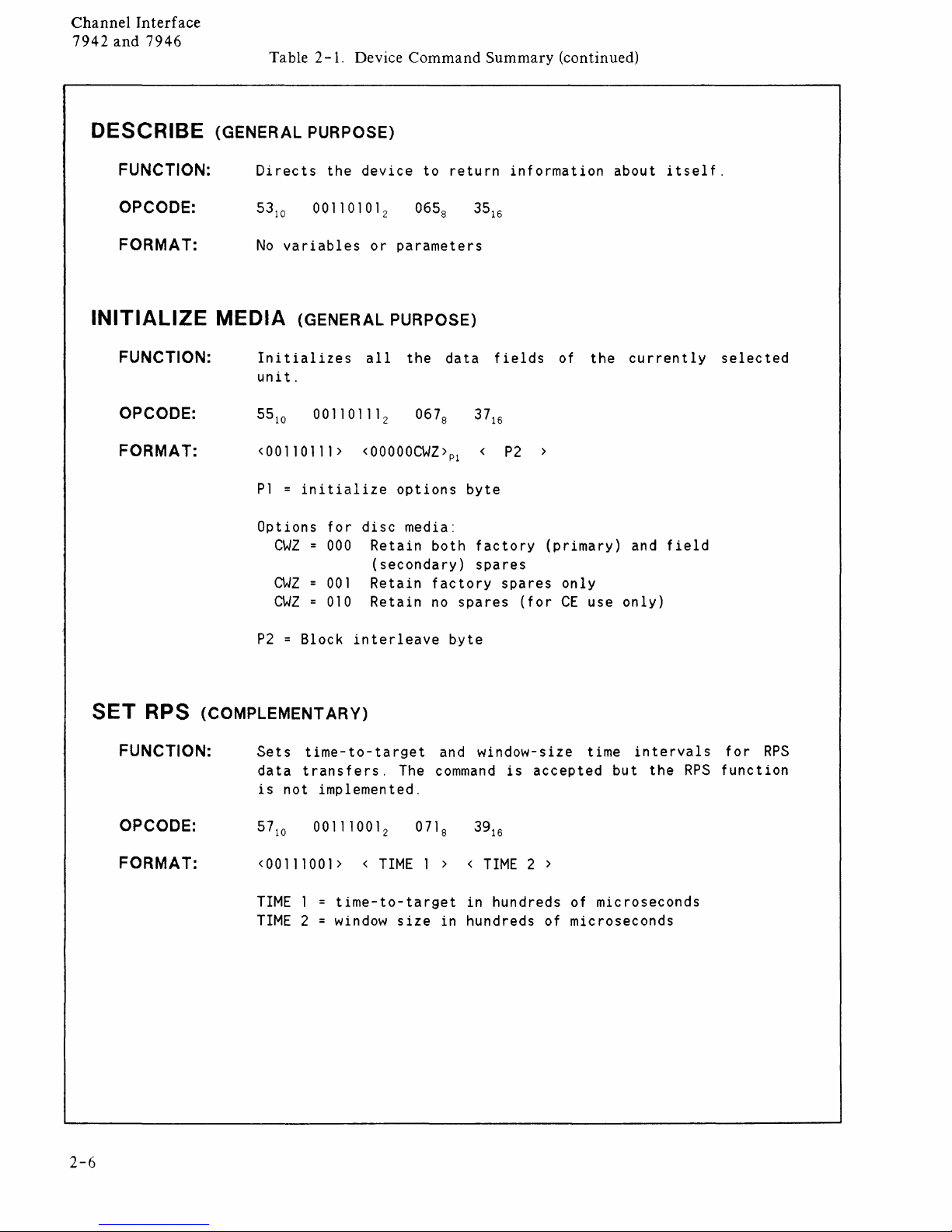

Table 2

-1.

Device

Command

Summary

LOCA

FUNCTION:

OPCODE:

FORMAT:

LOCA

FUNCTION:

OPCODE:

FORMAT:

LOCA

FUNCTION:

TE

AND READ (REAL TIME)

Locates

mits

No

variables

TE

AND

TE

AND VERIFY (GENERAL PURPOSE)

WRITE

Tranfers

dress

No

variables

Instructs

section

the

the

data

(REAL TIME)

data

specified

the

of

data

data

to

the

or

parameters

from

by

or

parameters

device

to

indicated

the

the

ensure

host.

host

target

to

perform

by

that

the

for

storage

address.

an

it

target

internal

can be

address

beginning

verification

read.

and

at

trans-

the

ad-

of a

OPCODE:

FORMAT:

SPARE

FUNCTION:

OPCODE:

FORMAT:

BLOCK

No

variables

(GENERAL PURPOSE)

Gives

sparing

<00000110>

P1 = sparing

S = 0

T = 0

T must

S must

the

skip

retain

equal 1 for

equal 0 for

or

device

the

block

<OOOOOSOT>Pl

mode

spare

data

parameters

permission

indicated

byte

tape

disc

to

by

the

S = 1

T = 1

operation

operation

become

target

jump

do

not

temporarily

address.

spare

retain

data

busy

while

2-2

Page 21

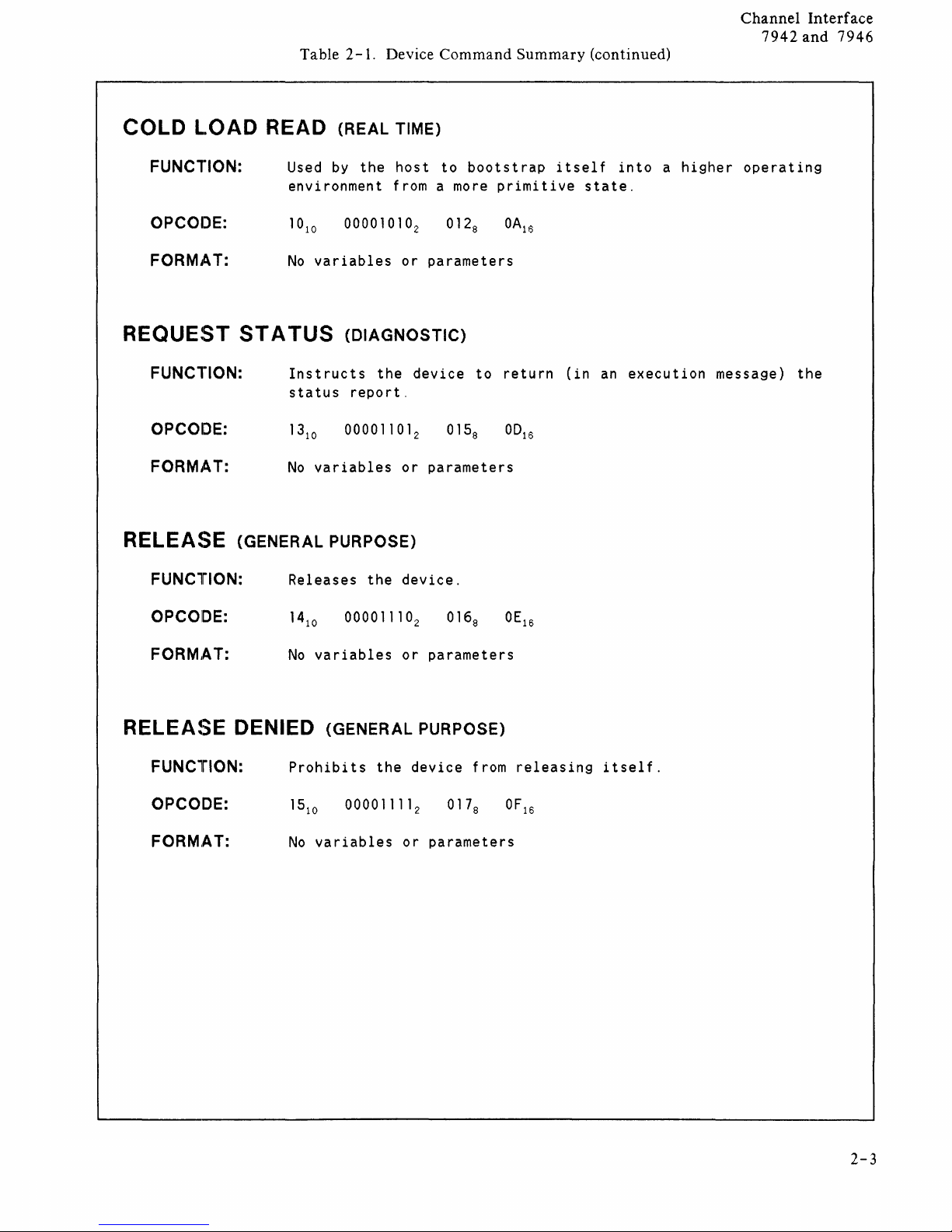

Table

2-1.

Device

Command

Summary

(continued)

Channel

7942

In

and

terf

7946

ace

COLD

L.OAD READ (REAL TIME)

FUNCTION:

OPCOIJE:

FORMAT:

REQUEST

FUNCTION:

OPCOIDE:

FORMj~T:

RELEASE

FUNCTION:

Used

by

the

host

environment from a more

No

variables

ST A TUS

(DIAGNOSTIC)

Instructs

status

No

(GENERAL PURPOSE)

report.

variables

Releases

the

the

or

or

device.

to

bootstrap

parameters

device

parameters

primitive

to

return

itself

state.

(in

into a higher

an

execution

operating

message)

the

OPCOIDE:

FORMAT:

RELEASE

FUNCTION:

OPCODE:

FORM,AT:

No

variables

or

parameters

DENIED (GENERAL PURPOSE)

Prohibits

No

variables

the

device

or

parameters

from

releasing

itself.

2-3

Page 22

Channel

7942

and

Interface

7946

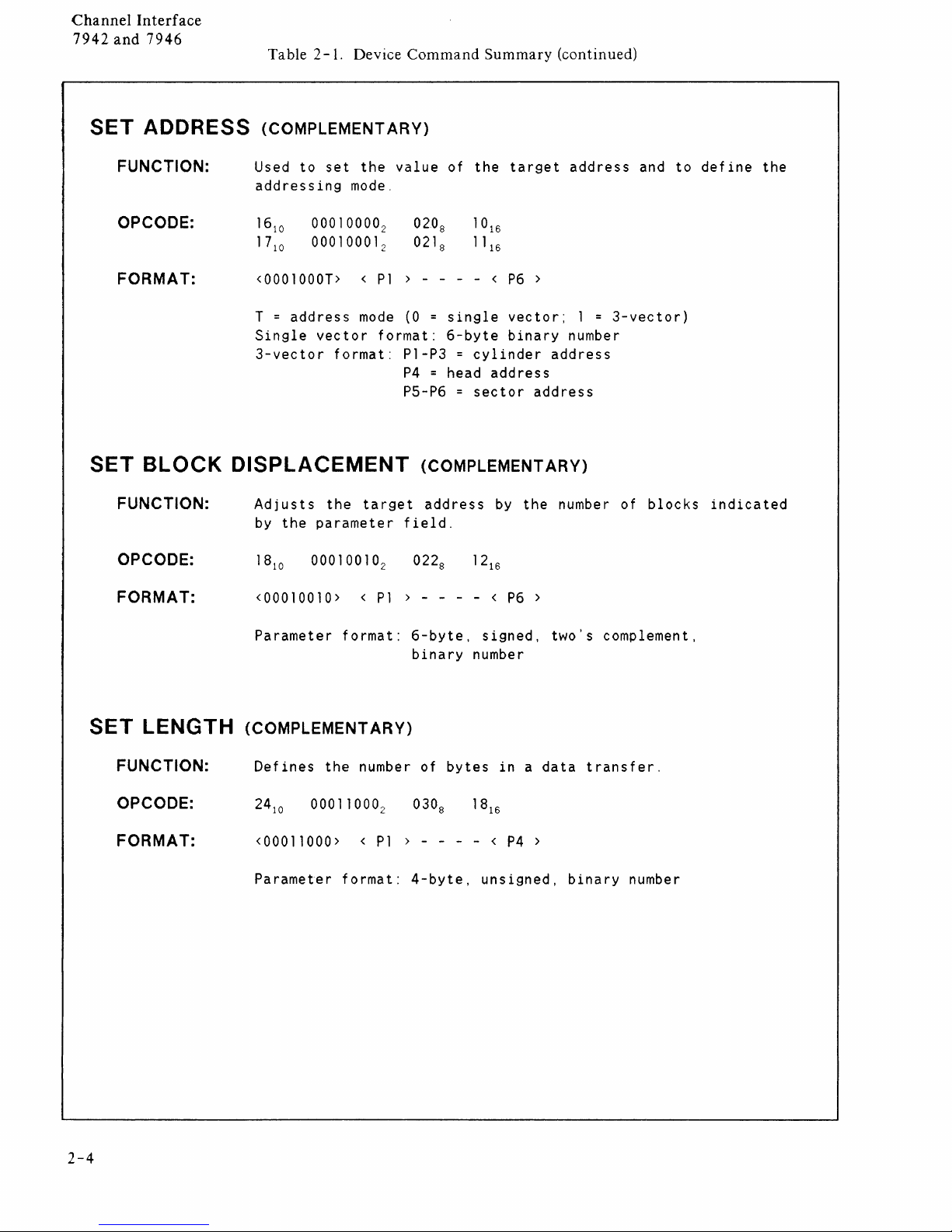

Table 2

-1.

Device

Command

Summary

(continued)

SET

SET

ADDRESS (COMPLEMENT

FUNCTION:

OPCODE:

FORMAT:

BLOCK

FUNCTION:

OPCODE:

ARY)

Used

to

set

the

value

addressing

16

10

17

10

<0001000T> <

T

=

address

Single

3-vector

mode.

00010000

00010001

mode

vector

format:

2

2

P1

format:

DISPLACEMENT

Adjusts

by

the

the

target

parameter

of

the

target

020

8

021

8

> - - - - <

(0 = single

6-byte

P1-P3 =

P4

= head

P5-P6 =

(COMPLEMENTARY)

address

P6

vector;

binary

cylinder

address

sector

by

the

>

address

field.

address

1 =

number

address

number of

and

3-vector)

blocks

to

define

the

indicated

FORMAT:

SET

LENGTH (COMPLEMENTARY)

FUNCTION:

OPCODE:

FORMAT:

<00010010> <

Parameter

Defines

format:

the

<00011000> <

Parameter

format:

P1

> - - - - <

6-byte,

binary

number of

P1

) - - - - <

4-byte,

number

bytes

P6

>

signed,

in a data

P4

>

unsigned,

two's

binary

complement,

transfer.

number

2-4

Page 23

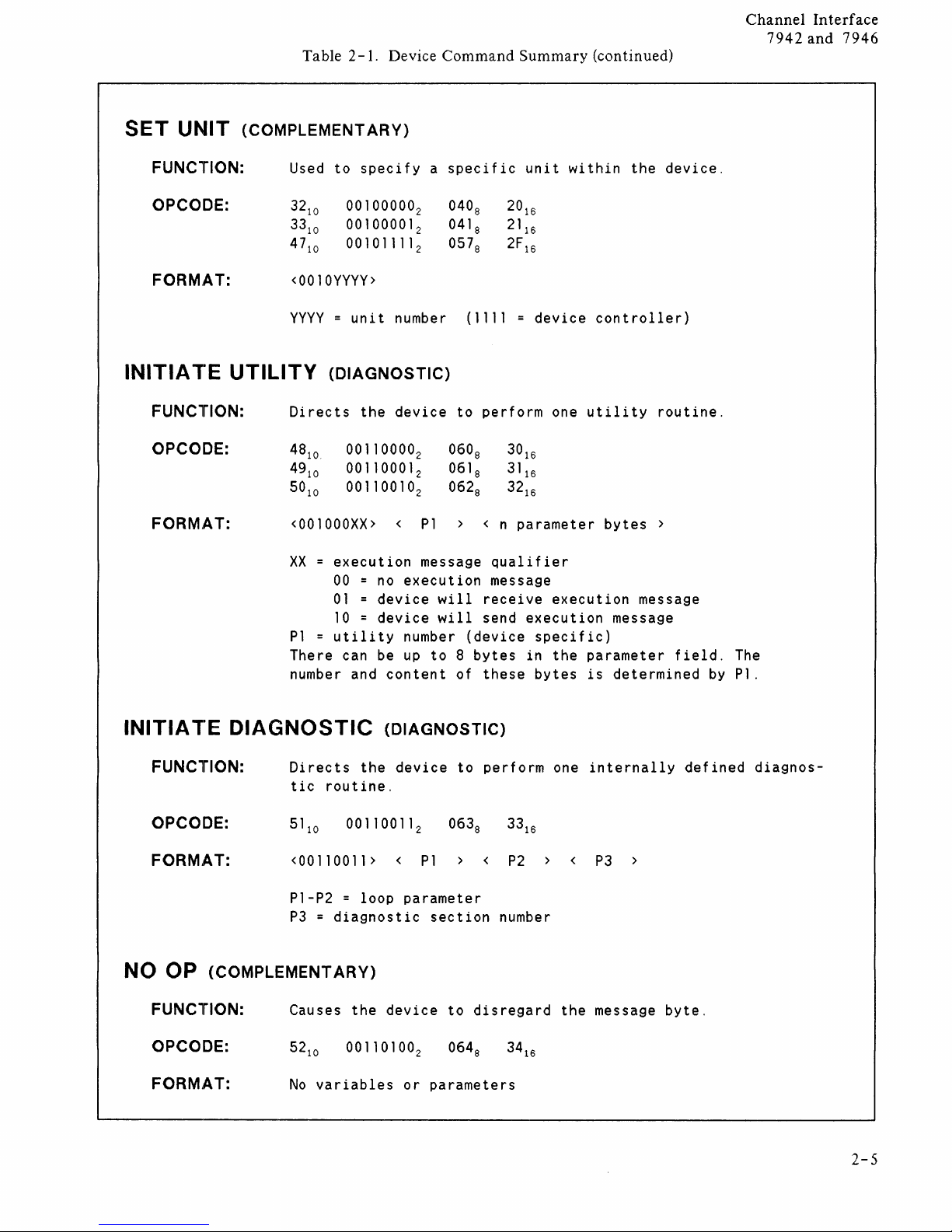

Table

2-1.

Device

Command

Summary

(continued)

Channel

7942

In

and

terf

7946

ace

SET

UNIT (COMPLEMENTARY)

FUNCTION:

OPCODE:

FORM,AT:

INITIA l"E

FUNCTION:

OPCODE:

FORMAT:

Used

32

10

33

10

47

10

<0010YYYY>

YYYY = unit

UTILITY

Directs

48

10

49

10

5010

<001000XX>

xx

Pl =

There can be

number and

to

specify a specific

00100000

00100001

00101111

2

2

2

number (1111

(DIAGNOSTIC)

the

device

00110000

00110001

00110010

2

2

2

<

=

execution

00 = no

execution

01 = device

10 = device

utility

number

up

content

040

8

041

8

057

8

to

perform

060

8

061

8

062

8

>

Pl

< n

message

will

receive

will

send

(device

to 8 bytes

of

these

unit

20

16

21

16

2F

16

device

30

16

31

16

32

16

parameter

qualifier

message

execution

specific)

in

bytes

within

controller)

one

utility

bytes

execution

message

the

parameter

is

determined

the

device.

routine.

>

message

field.

by

The

Pl.

INITIA l"E

FUNCTION:

DIAGNOSTIC

Directs

tic

the

routine.

OPCODE:

FORM,AT:

<00110011> < Pl <

Pl-P2

=

loop

P3 = diagnostic

NO OP (COMPLEMENTARY)

FUNCTION:

OPCODE:

FORM,AT:

Causes

No

the

variables

(DIAGNOSTIC)

device

to

perform

parameter

section

device

to

or

parameters

disregard

P2

number

one

<

the

internally

P3

>

message

defined

byte.

diagnos-

2-5

Page 24

Channel

7942

and

In

terf

7946

ace

Table

2-1.

DESCRIBE (GENERAL PURPOSE)

Device

Command

Summary

(continued)

FUNCTION:

OPCODE:

FORMAT:

INITIALIZE

FUNCTION:

OPCODE:

FORMAT:

Directs

No

the

variables

device

or

parameters

to

return

MEDIA (GENERAL PURPOSE)

Initializes

unit.

<00110111>

P1 = initialize

Options

CWZ

CWZ

CWZ

all

the

<OOOOOCWZ>Pl < P2

options

for

disc

media:

000

Retain

both

(secondary)

001

010

Retain

Retain

factory

no

data

byte

spares

information

fields

factory

spares

spares

(f

of

(primary)

only

0 r

CE

use

the

about

currently

and

only)

itself.

selected

field

SET

RPS (COMPLEMENTARY)

FUNCTION:

OPCODE:

FORMAT:

P2

= Block

Sets

data

is

time-to-target

transfers.

not implemented.

interleave

<00111001> <

TIME

TIME

time-to-target

1

2

window

The

TIME

size

byte

and

command

1>

in

window-size

is

accepted

<

TIME

2 >

in

hundreds of

hundreds of

time

intervals

but

the

microseconds

microseconds

RPS

for

RPS

function

2-6

Page 25

Table

2-1.

Device

Command

Summary

(continued)

Channel

7942

In

and

terf

7946

ace

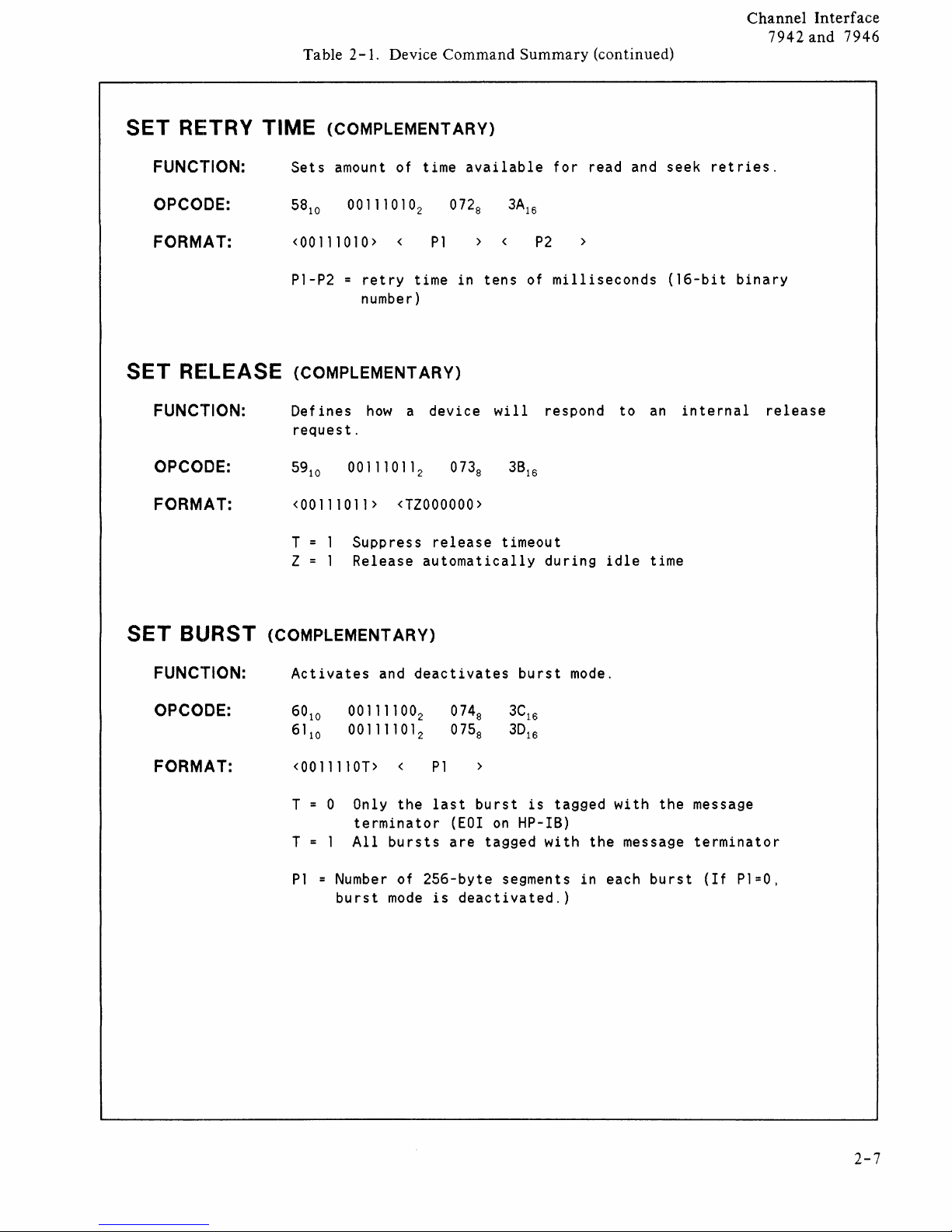

SET

SET

RETRY TIME

FUNCTION:

OPCODE:

FORMAT:

RE~LEASE

FUNCTION:

OPCODE:

FORMAT:

(COMPLEMENTARY)

Sets

amount of time

<00111010> <

P1-P2 =

retry

time

available

P1

in

number)

(COMPLEMENTARY)

Def

ines

how

a dev

ice

request.

<00111011> <T2000000>

T

2

Suppress

Release

release

automatically

tens

wi

11

timeout

for

read and

>

P2

of

milliseconds

respond

during

to

idle

seek

(16-bit

an

time

in

te

retries.

binary

rnal

release

SET

BlJRST

FUNCTION:

OPCODE:

FORMAT:

(COMPLEMENTARY)

Activates

60

10

61

10

and

00111100

00111101

deactivates

2

2

<0011110T> <

T 0 Only

the

terminator

T

P1 = Number

All

burst

bursts

of

mode

256-byte

074

8

075

8

>

P1

last

burst

(EOI

are

tagged

is

deactivated.)

burst

3C

16

3D

16

is

on

HP-IB)

segments

mode.

tagged

with

the

in

with

message

each

the

burst

message

terminator

(If

P1=0,

2-7

Page 26

Channel

7942

and

Interface

7946

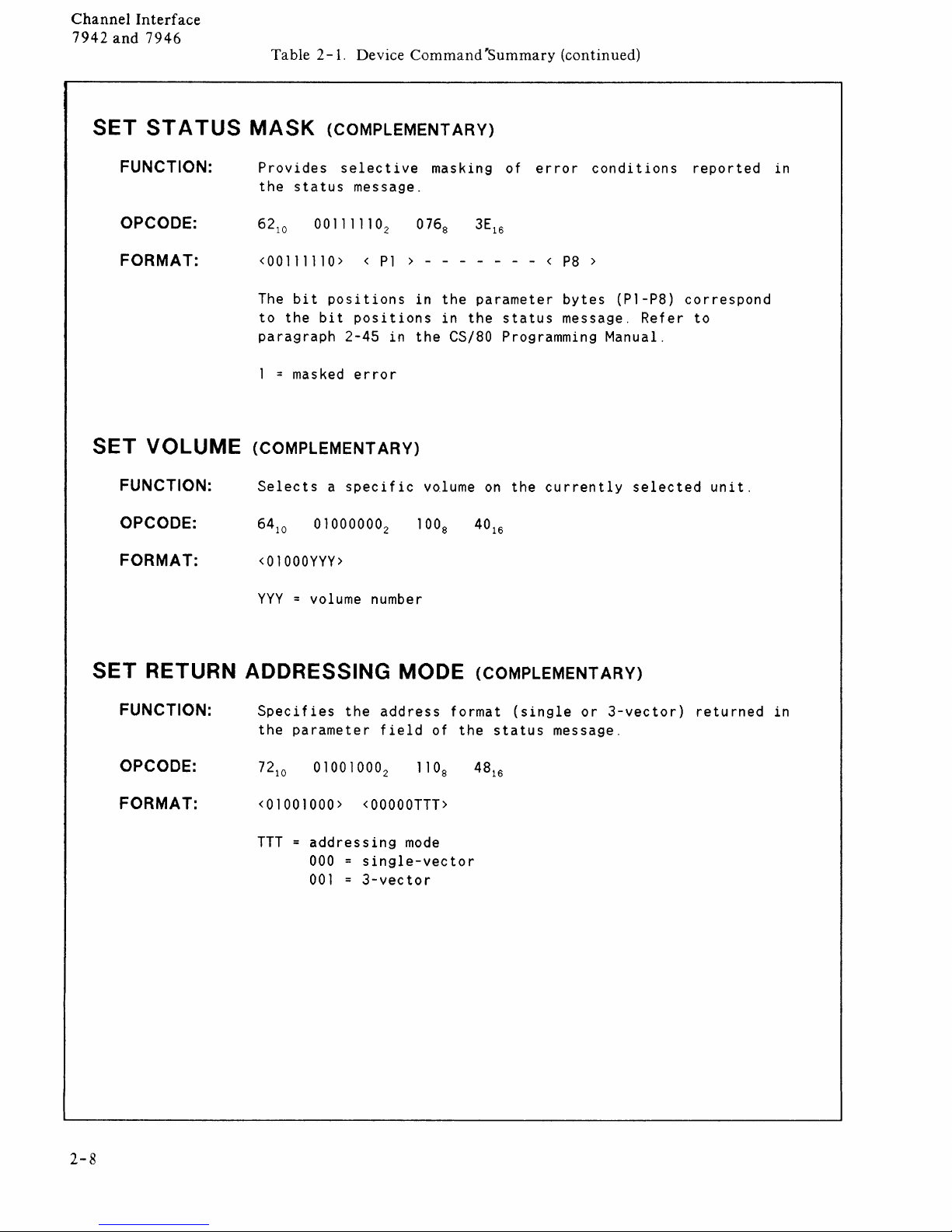

Table

2-1.

Device Command"Summary (continued)

SET

SET

ST A TUS

FUNCTION:

OPCODE:

FORMAT:

VOLUME

FUNCTION:

OPCODE:

FORMAT:

MASK

Provides

the

<00111110> <

The

to

paragraph

1

= masked

(COMPLEMENTARY)

(COMPLEMENTARY)

selective

status

message.

Pl

bit

positions

the

bit

positions

2-45

in

error

Selects a specific

64

10

01000000

2

<01000YYY>

masking of

> - - - - - - - <

in

the

parameter

in

the

the

CS/80 Programming Manual.

volume

on

error

status

the

P8

bytes

message.

currently

conditions

>

(Pl-P8)

Refer

selected

reported

correspond

to

unit.

in

SET

RETURN ADDRESSING MODE

FUNCTION:

OPCODE:

FORMAT:

YYY

= volume number

Specifies

the

parameter

72

10

<01001000>

the

01001000

<OOOOOTTT>

address

field

TTT = addressing

000

single-vector

001 = 3-vector

2

mode

(COMPLEMENTARY)

format

of

the

(single

status

or

3-vector)

message.

returned

in

2-8

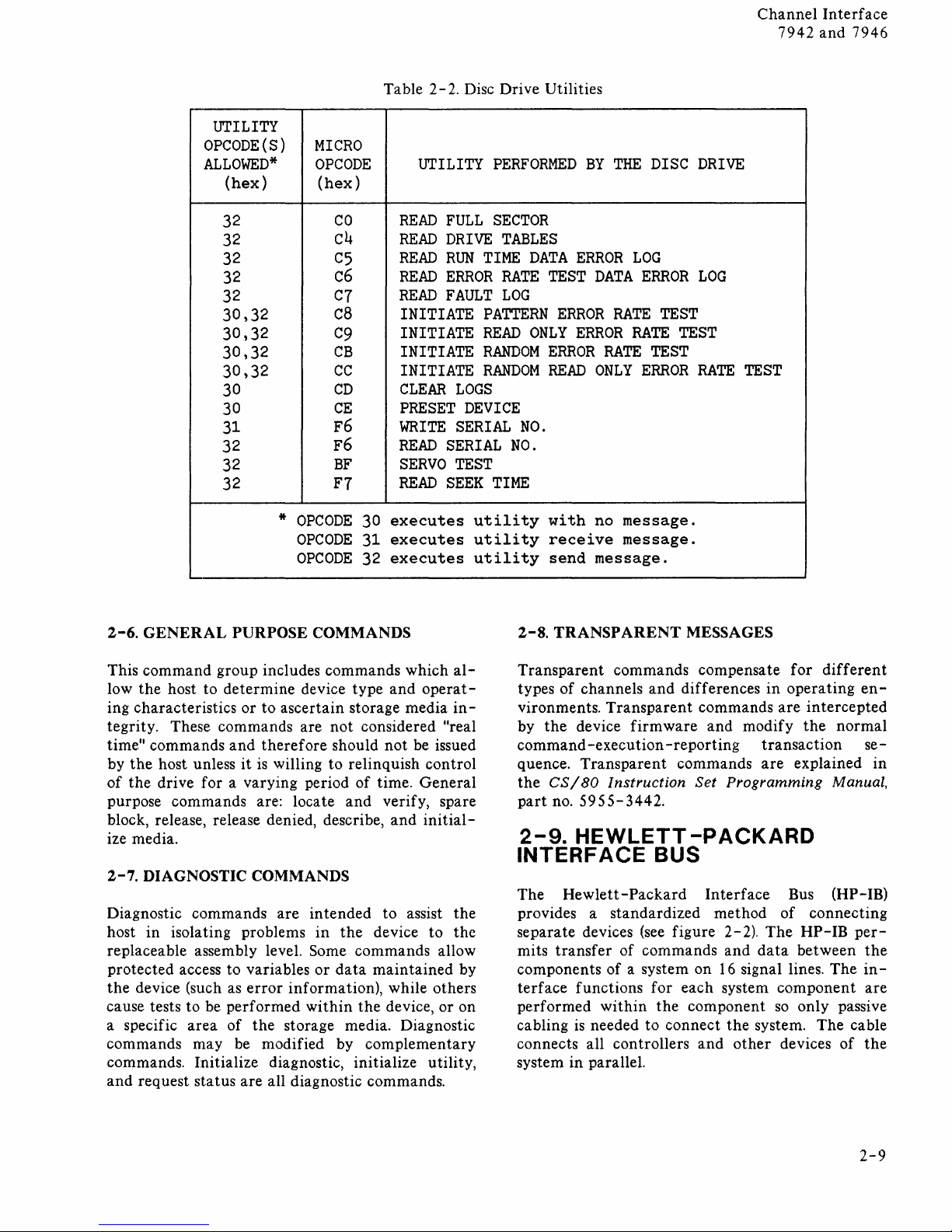

Page 27

UTILITY

OPCODE(S)

ALLOWED*

(hex)

32

32

32

32

32

30,32

30,32

30,32

30,32

30

30

31

32

32

32

MICRO

OPCODE

(hex)

CO

c4

C5

c6

C7

c8

C9

CB

CC

CD

CE

F6

F6

BF

F7

Table

2-2.

UTILITY

READ

READ

READ

READ

READ

INITIATE

INITIATE

INITIATE

INITIATE

CLEAR

PRESET

WRITE

READ

SERVO

READ

Disc Drive Utilities

PERFORMED

FULL

DRIVE

RUN

ERROR

FAULT

SECTOR

TABLES

TIME

DATA

RATE

LOG

TEST

PATTERN

READ

ONLY

RANDOM

RANDOM

ERROR

READ

LOGS

DEVICE

SERIAL

SERIAL

NO.

NO.

TEST

SEEK

TIME

BY

ERROR

DATA

ERROR

ERROR

RATE

ONLY

THE

LOG

ERROR

RATE

RATE

TEST

ERROR

DISC

TEST

TEST

DRIVE

LOG

RATE

Channel

7942

TEST

Interface

and

7946

*

OPCODE

OPCODE

OPCODE

2-6.

GENERAL

This

command

low

the

host to

ing characteristics

tegrity. These commands are

commands

time"

the

by

of

purpose commands are: locate

block, release, release denied, describe,

ize media.

2-7.

Diagnostic commands

host

replaceable assembly level. Some commands allow

protected access to variables

the

cause tests to be

a specific

commands

commands. Initialize diagnostic, initialize utility,

and

host unless

the

drive for a varying period

DIAGNOSTIC COMMANDS

in

isolating problems

device (such as

request status

PURPOSE COMMANDS

group includes commands

area

may

determine

or

and

it

error

performed

of

the

be modified by

are

device

to

ascertain storage media

not

therefore

is

willing

are

storage media. Diagnostic

all diagnostic commands.

should

to

in

tended

in

or

information), while others

within

the

data

executes

30

executes

31

executes

32

which

type

and

considered "real

not

relinquish control

of

time.

and

verify, spare

and

to assist

device to

maintained

the

device,

complementary

al-

operat-

in-

be issued

General

initial-

the

the

by

or

on

utility

utility

utility

with

receive

send

2-8.

TRANSPARENT

Transparent

types

of

channels

vironments.

by

the

device

command

quence.

the

part

2-9.

-execution

Transparent

CS/80

no.

5955-3442.

HEWLETT-PACKARD

INTERFACE

The

Hewlett-Packard

provides a

separate

mits

components

terface

performed

cabling

connects all controllers

system in parallel.

devices (see figure 2-2).

transfer

functions

is

needed to

no

message.

message.

message.

MESSAGES

commands compensate

and

differences

Transparent

firmware

Instruction

commands

and

-reporting

commands

Set

Programming

BUS

Interface

standardized

of commands

of

a system on

for

within

the

connect

method

and

16

each system

component

the

and

other

for

in

operating

are

intercepted

modify

signal lines.

system.

the

transaction

are

explained

Bus (HP-IB)

of

connecting

The

HP-IB

data

between

component

so

only passive

devices

different

en-

normal

se-

Manual,

per-

the

The

in-

are

The

cable

of

the

in

2-9

Page 28

Channel

7942

and 7946

Interface

TRANSACTION

PHASE

CO~MAND

Q

(0

EXECUTION

G

@

REPORTING

(1)

Logical Machine idle in command

(2)

Host sends command message.

@

CHANNEL

ACTIVITY

COMMAND

EXECUTION

REQUEST

(IF

APPLICABLE)

A

EXECUTION

MESSAGE

'I

(IF

APPLICABLE)

REPORTING

REQUEST

.A

REPORTING

MESSAGE

'It

MESSAGE

MESSAGE

MESSAGE

-ready

CD

COMMAND-READY

@

ACCEPT

AND

NOTE:

o

BEGIN

@

REQUEST

(1)

CO~PLETE

RECIEVE

G

COMPUTE

@

REQUEST

@

SEND

VALIDATE

LOGICAL

STATE

IF

HOST

EXECUTION

EXECUTION

EXECUTION

DATA.

TRANSACTION

REPORTING

ONE-BYTE

state.

UNIT

~HINE

12

IF

REQUESTS

OF

MESSAGE

OR

ACCOMPLISH

MESSAGE

REPORT

OPERATING

STATE

COMMAND

GOES

TO

COMMAND

REPORllNG

COMMAND

(IF

OF

COMMAND

STATUS

(QSTAT)

REPORTING

IS

INVALID.

MESSAGE.

APPLICABLE)

~SEND

COM

AND

ACTION)

OR

DATA.

(3)

Logical Machine accepts

to

execution state.

(4)

Unit

begins execution of command.

(5,6)

If

command involves

unit

completes execution

(7)

Execution message

(8)

Unit

completes execution

receives

data

If

through

and

verifies command. If command

not, Logical Machine moves

data

transfer,

(6).

is

established

if

of

command.

channel module. If not,

message.

(9)

Logical Machine computes completion status

QST AT, complete status set

(10,11) Logical Machine requests

(12) Reporting message

(1

3)

Logical Machine sends 1 - byte reporting message

is

action. Host must send request

into

reporting

established.

command

request status.

to

reporting state.

Logical Machine requests

command involves a

If

command involves

unit

of

data

completes action called for

transaction. Pass/Fail status IS set

message.

(QST A T)

for complete status

is

valid, Logical Machine moves

an

execution message.

transfer.

data

transfer,

unit

in

indicating Pass/Fail status

report

(20 bytes).

If

not,

sends

or

command

into

of

trans-

2-10

Figure 2

-1.

Transaction

Structure

Page 29

Channel

7942

In

and

terf

7946

ace

DATA

A (8

SIGNAL~NES)

<....,..

..

..-

---

..

..-

..

--

..

..-

..

..-.

..

..-.

.......

\/

TALK.LlSTEN

AND

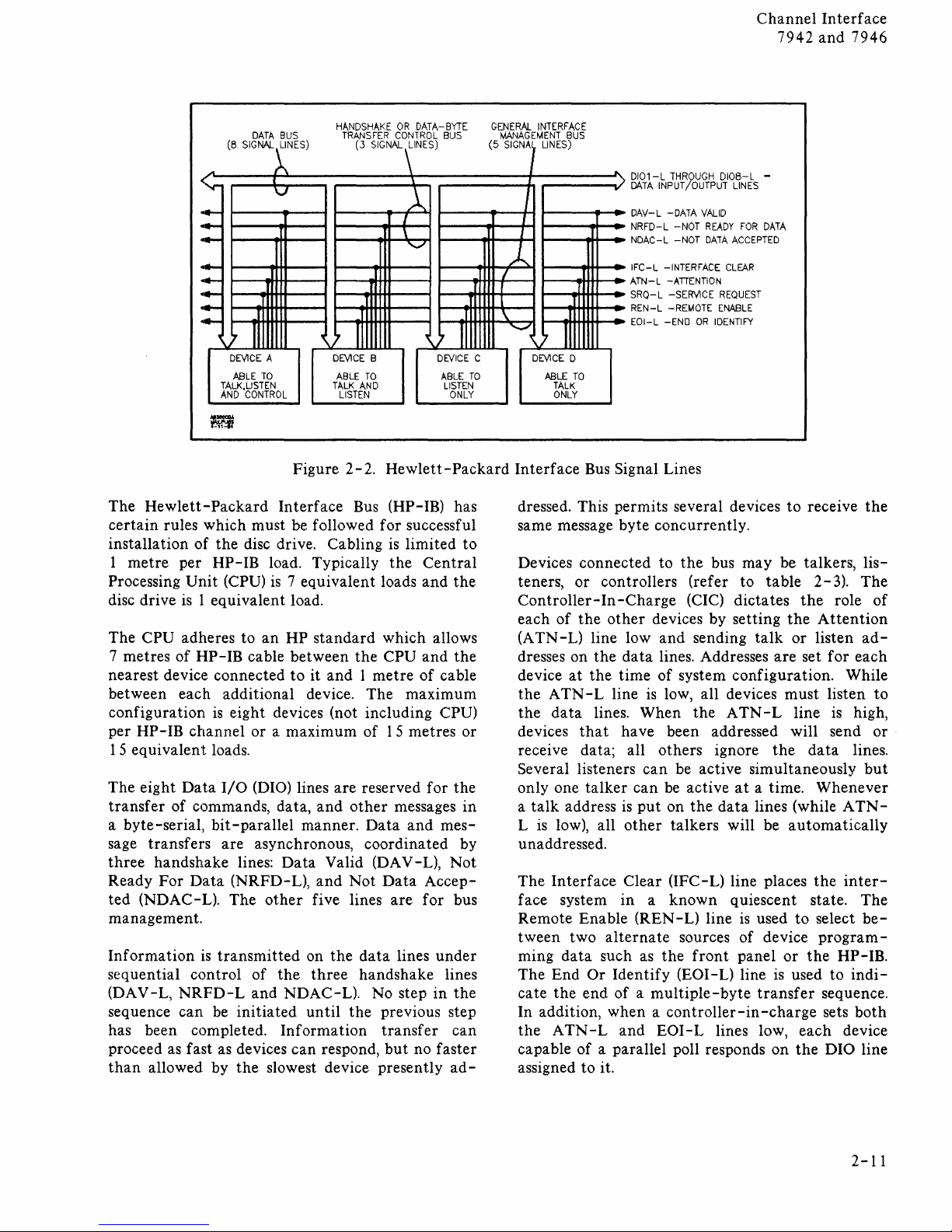

The

Hewlett-Packard

certain

installation of

1

Processing

disc drive

The

7 metres

rules which must be followed for successful

the

metre

per

HP-

Unit

(CPU)

is

1 equivalent load.

CPU adheres to an HP

of

HP-IB

I

V

J J J

II

DEViCE

A

ABLE

TO

CONTROL

disc drive. Cabling

IB

load. Typically

is

cable between

nearest device connected

BUS

HANDSHAKE

TRANSFER

~

>'

DEVICE

ABLE

TALK

LISTEN

Figure 2-2.

Interface

7 equivalent loads

standard

to

it

and 1 metre

OR

DATA-BYTE

CONTROL

(3

SIGNAL~INES)

fI

8

TO

AND

~

I

\

'-./

~

BUS

>'

II

DEVICE

ABLE

LISTEN

ONLY

Hewlett-Packard

Bus (HP-IB) has

is

limited to

the

Central

and

the

which allows

the

CPU

and

the

of

cable

between each additional device. The maximum

is

configuration

per

HP-IB

eight devices (not including CPU)

channel

or a maximum of 15 metres

or

15 equivalent loads.

The eight

transfer

a byte-serial,

sage transfers

three

Ready For

ted (NDAC-L). The

Data

I/O

(DIO) lines

of commands, data,

bit-parallel

are

asynchronous, coordinated by

handshake lines:

Data

(NRFD-L),

other

are

and

manner.

Data

Valid (DAV -L),

and

five lines

reserved for

other

messages

Data

and

Not

Data

are

the

in

mes-

Not

Accep-

for bus

management.

Information

sequential control

(DAV-L,

sequence can be

has been completed.

proceed as fast

than

allowed by

is

transmitted

NRFD-L

as

on

the

data

of

the

and

NDAC-L). No step

initiated

three

until

handshake lines

the

Information

devices can respond,

the

slowest device presently

lines

under

in

the

previous step

transfer

but

can

no faster

ad-

GENERAL

(5

.~

C

TO

INTERFACE

MANAGEMENT

SIGNA,

1

I

~

I

r

\ J

~

Interface

I

DEVICE

BUS

LINES)

'1

II

D

ABLE

TO

TALK

ONLY

Bus Signal Lines

...

DI01-L

THROUGH

DATA

INPUT

...

DAV-L -DATA

NRFD-L -NOT

NDAC-L -NOT

IFC-L

-INTERFACE

ATN-L

-ATIENTION

SRQ-L -SERViCE

REN-L

-REMOTE

EOI-L -END

jOUTPUT

VALID

READY

DATA

ENABLE

OR

IDENTIFY

DI08-L

LINES

ACCEPTED

CLEAR

REQUEST

dressed. This permits several devices

same message byte concurrently.

Devices connected to

teners,

Controllereach

(A

dresses on

device

the A TN

the

devices

of

TN -L)

at

data

or

controllers (refer to

In

-Charge

the

other

line low

the

data

the

time

-L line

lines. When

that

have been addressed will send

the

bus may be talkers,

(CIC) dictates

devices by setting

and

sending

lines. Addresses

of

system configuration. While

is

low, all devices

the A TN

receive data; all others ignore

can

Several listeners

only one

talk

a

is

L

talker

address

low), all

is

other

be active simultaneously

can

be active

pu t on

the

at

data

talkers will be

unaddressed.

Interface

The

face system

Remote Enable (REN tween two

ming

data

The End

cate

the

In addition,

the

ATN-L

capable

Clear (IFC-L) line places

in a known

alternate

such

as

the

Or

Identify

end

of a multiple-byte

sources of device

(EOI-L) line

quiescent state.

L)

line

front

when a controller-in-charge

and

EOI-L

of

a parallel poll responds on

lines low,

assigned to it.

-

FOR

DATA

to

receive

table 2-3).

the

role

the

Attention

talk

or

listen

are

set for each

must

listen

- L line

the

is

data

a time. Whenever

lines (while A

automatically

the

inter-

is

used

to

select

program-

panel

or

is

used to

transfer

the

HP-IB.

sequence.

sets

each

device

the

DIO line

the

lis-

The

of

ad-

to

high,

or

lines.

but

TN

The

be-

indi-

both

-

2-11

Page 30

Channel

7942

and

In

terf

7946

ace

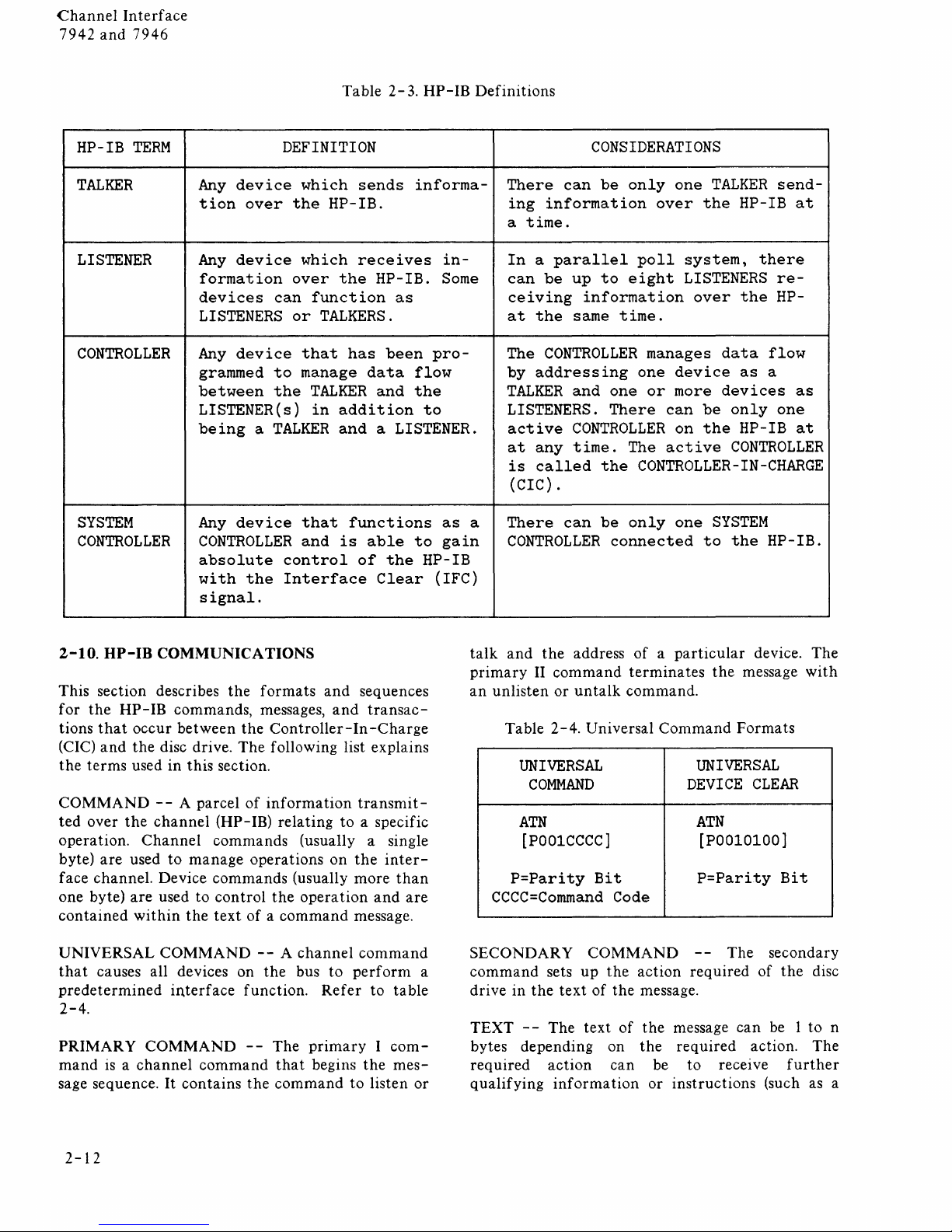

HP-IB

TERM

TALKER

LISTENER

CONTROLLER

SYSTEM

CONTROLLER

DEFINITION

Any

device

tion

Any

over

device

formation

devices

LISTENERS

Any

device

grammed

between

LISTENER(s)

the

over

can

or

to

the

which

which

function

TALKERS.

that

manage

TALKER

in

being a TALKER

Any

device

CONTROLLER

absolute

with

the

that

and

control

Interface

signal.

Table 2-3.

sends

HP-IB

informa-

HP-IB.

receives

the

HP-IB.

in-

Some

as

has

been

data

and

addition

proflow

the

to

and a LISTENER.

functions

is

able

of

the

Clear

as

to

gain

HP-IB

(IFC)

Definitions

There

ing

a

time.

In a parallel

can

ceiving

at

the

The

by

addressing

TALKER

LISTENERS.

active

at

any

is

called

(CIC) .

There

a

CONTROLLER

CONSIDERATIONS

can

be

only

information

poll

be

up

to

eight

information

same

time.

CONTROLLER

one

and

one

There

CONTROLLER

time.

can

The

the

CONTROLLER-IN-CHARGE

be

only

connected

one

over

the

system,

LISTENERS

over

manages

device

or

more

can

be

on