Page 1

HP 783Xx Series and HP 788Xx Series

Service Manual’- Volume 1

Patient Monitors and Neonatal Monitors

HEWLETT

Ea

HP Part No. 78354-90008

Printed in Germany

PACKARD

Edition 8

March 1993

Page 2

Notice

The information contained in this document is subject to change without notice.

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but

not limited to, the implied warranties of merchantability and fitness for a particular purpose.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or

consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on

equipment that is not furnished by Hewlett- Packard.

This document contains proprietary information, which is protected by copyright. All rights

are reserved. No part of this document may be photocopied, reproduced or translated to

another language without the prior written consent of Hewlett-Packard Company. The

information contained in this document is subject to change without notice.

Hewlett-Packard Company

Medical Products Group (Europe)

Schickardstrasse 4

7030 Boeblingen

Federal Republic

of Germany

@ Copyright Hewlett-Packard Company, 1991. All rights reserved.

Page 3

Printing History

New editions are complete revisions of the manual. Update packages, which are issued

between editions, contain additional and replacement pages to be merged into the manual by

the customer. The dates on the title page change only when a new edition or a new update is

published.

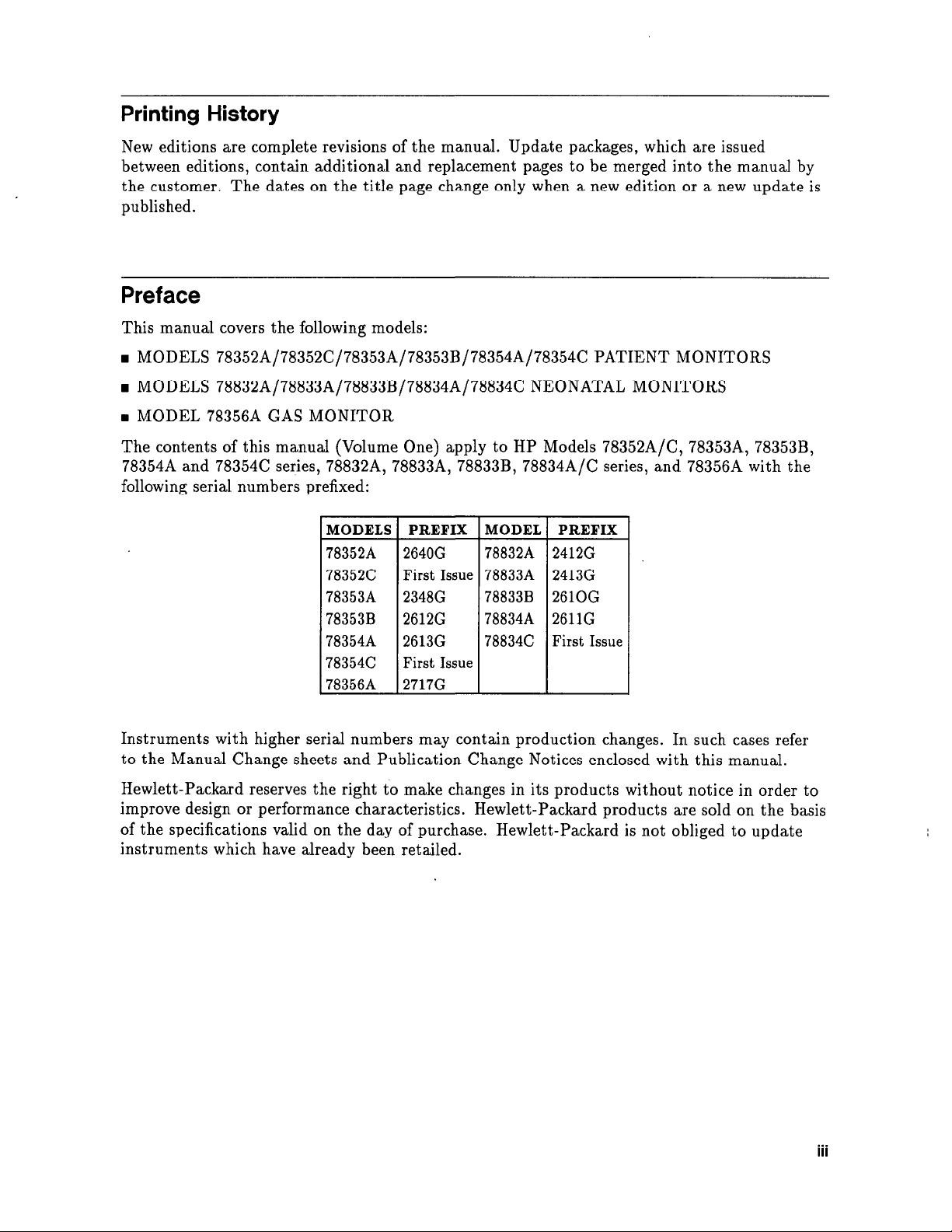

Preface

This manual covers the following models:

w MODELS 78352A/78352C/78353A/78353B/78354A/78354C PATIENT MONITORS

w MODELS 78832A/78833A/78833B/78834A/78834C NEONATAL MONITORS

w MODEL 78356A GAS MONITOR

The contents of this manual (Volume One) apply to HP Models 78352A/C, 78353A, 78353B,

78354A and 78354C series, 78832A, 78833A, 78833B, 78834A/C series, and 78356A with the

following serial numbers prefixed:

MODELS

78352A

78352C

78353A

78353B

78354A

78354C

78356A

PREFIX

2640G

First Issue

2348G

2612G

2613G

First Issue

2717G

MODEL

78832A

78833A

78833B

78834A

78834C

PREFIX

2412G

2413G

2610G

2611G

First Issue

Instruments with higher serial numbers may contain production changes. In such cases refer

to the Manual Change sheets and Publication Change Notices enclosed with this manual.

Hewlett-Packard reserves the right to make changes in its products without notice in order to

improve design or performance characteristics. Hewlett-Packard products are sold on the basis

of the specifications valid on the day of purchase. Hewlett-Packard is not obliged to update

instruments which have already been retailed.

. . .

III

Page 4

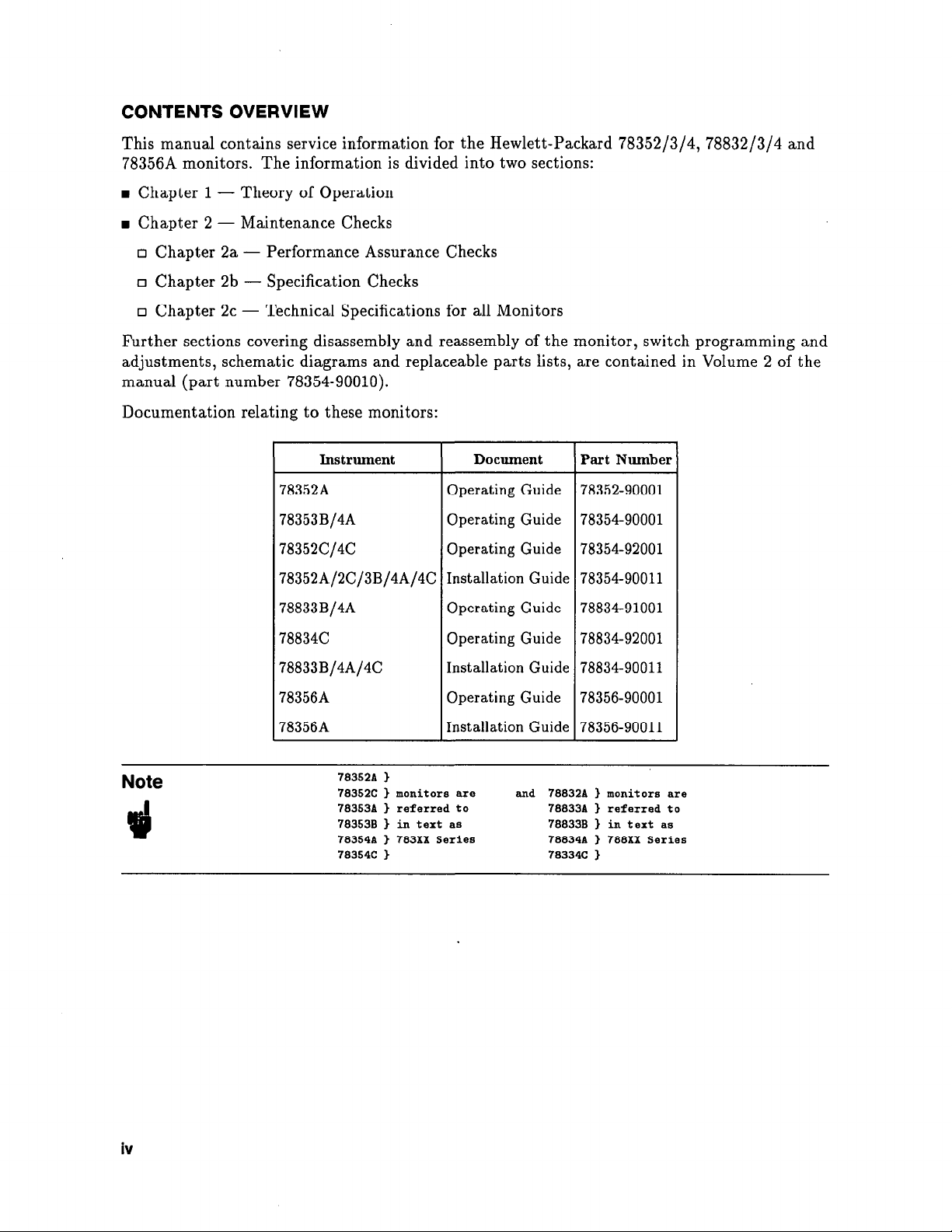

CONTENTS OVERVIEW

This manual contains service information for the Hewlett-Packard 78352/3/4, 78832/3/4 and

78356A monitors. The information is divided into two sections:

n

Chapter 1 - Theory of Operation

n

Chapter 2 - Maintenance Checks

q

Chapter 2a - Performance Assurance Checks

q

Chapter 2b - Specification Checks

q

Chapter 2c - Technical Specifications for all Monitors

Further sections covering disassembly and reassembly of the monitor, switch programming and

adjustments, schematic diagrams and replaceable parts lists, are contained in Volume 2 of the

manual (part number 78354-90010).

Documentation relating to these monitors:

Instrument Document Part Number

Note

78352A

78353B/4A

78352C/4C

78352A/2C/3B/4A/4C

78833B/4A

78834C

78833B/4A/4C

78356A

78356A

783528 )

78362C 3 monitors are

783638 ) referred to

783538 ) in text es

783548 3 783Xx Series

78354C

3

Operating Guide

Operating Guide

Operating Guide

Installation Guide

Operating Guide

Operating Guide

Installation Guide

Operating Guide

Installation Guide

end 788328 3 monitors are

78833A 1 referred to

708338 3 in text as

788348 3 788Xx Series

78334C

78352-90001

78354-90001

78354-92001

78354-90011

78834-91001

78834-92001

78834-90011

78356-90001

78356-90011

3

iv

Page 5

Special Notation

Notes, cautions, and/or warnings may accompany the

defined below:

Note

I

VI!

Caution

Warning

Notes provide emphasis to information or additional inforniation “off line”

from a procedure.

Cautions highlight procedures that must be followed to avoid damage to the

recorder.

Warnings highlight procedures that must be followed to avoid hazards to human

life or safety.

instructions in this manual. They are

Page 6

Contents

1. Theory Of Operation

Introduction

Functional description

Shared Memory and Data Transfer

General

Power Fail

Time Slices

Mother Board 78353-66501 and 78354-66501

Video Amplifier

Horizontal Deflection Circuit

Vertical Deflection Circuit

High Voltage Circuits

Power-On Reset

5 V Buffering.

Extender Board

Display UP Boards 78353-66502 (16K byte), 78354-66502 (40K byte)

78354-66602 and 78354-66702 (48K byte)

Character Generation

Slow/fast Sync. Signal Generation

Clock Generation

2 ms Interrupt Signal Generation

Alarm Trigger Generation

Power Fail Circuit

Display Software

Single Channel Interpolation Board 78352-66503

D-A Convertor and Sample and Hold Circuits

Shuffle Mux ............................

Video Pulse Generator

Ramp Generator

Raster Line Control

Erase Bar Latch

Wave Length Latch

Start-up Delay

Three-Channel Interpolation Board 78353-66503

Power Supply Board 78351-66506

+5 V DC Supply

f12 V DC Supplies

t17V DC Supply

Audio Board 78353-66512

Battery Board 78832-66519

Battery Charge Circuit

Alarm Lamp Drive Circuit

..............................

.............................

........................

.............................

...........................

......................

........................

..........................

...........................

..........................

........................

..........................

......................

.........................

..........................

........................

..........................

..........................

..........................

.........................

...........................

..........................

.........................

..........................

.......................

......................

.......................

......................

...................

..................

.....................

..................

...................

....................

...............

...............

.............

.............

.............

1-1

1-1

1-2

1-2

1-2

1-2

1-5

1-5

1-5

1-5

1-6

1-6

1-6

1-6

1-8

1-8

1-9

1-9

1-9

1-9

1-10

1-10

1-13

1-13

1-13

1-13

1-14

1-14

1-14

1-14

1-14

1-16

1-18

1-18

1-18

1-18

1-19

1-21

1-21

1-21

Contents-1

Page 7

ECG Board (Full Lead) 78354-66522(42) and 78354-66722(42)

Floating Input Circuit

Right-Leg Drive

INOP Detection Circuit

Lead Selector Circuit

Grounded Input Circuit

Digital Circuits

...........................

ECG Parameter Software

........................

..........................

.......................

........................

.......................

......................

ECG Board (3 Lead) 78832-66522 (50 Hz) and 78832-66542 (60 Hz)

Floating Input Circuit

Right-Leg Drive

INOP Detection Circuit

Lead Selector Circuit

Grounded Input Circuit

Digital Circuits

...........................

ECG Parameter Software

........................

..........................

.......................

........................

.......................

......................

........

.....

Pressure Board 78353-66532 (Single Channel) and 78353-66534 (Dual Channel)

Transducer Excitation Circuits

Transducer Signal Demodulation Circuits

Analog to Digital Conversion

Transducer Disconnected Detection

Zero, Calibration and Test Functions

Digital Circuits

...........................

Pressure Parameter Software

Non-Invasive Blood Pressure (NIBP) Board 78352-66535

General Principle of Operation

NIBP Parameter Board 78352-66535

Pressure Transducer

........................

Amplification and Filtering

Analog to Digital Conversion

Digital Circuit

..........................

Safety and Valve/Pump Control

NIBP Parameter Software

Non-Invasive Blood Pressure (NIBP) Board 78352-66358

Specifications

Patient Modes

Measurement Principle

............................

...........................

.......................

General Principle of Operation

NIBP Parameter Board 78352-66538

The Analog Board-Hardware Description

Pressure Transducers and Input Amplifier

Oscillation Channel

........................

Multiplexer and A/D Conversion

EEPROM and Latch

Hardware Description

Valve Drivers

Pump Motor

...........................

...........................

.......................

........................

The Digital Board-Hardware Description

Partial CO2 Pressure Board 78354-66540 and 78356-66540

General Principle of Operation

CO2 Parameter Board 78354-66540 and 78356-66540

....................

...............

.....................

..................

.................

.....................

..........

....................

.................

.....................

....................

..................

.....................

..........

....................

.................

...............

..............

..................

...............

.........

....................

..........

1-22

1-22

1-22

1-22

1-22

1-23

1-23

1-24

1-26

1-26

1-26

1-26

1-27

1-27

1-28

1-28

1-30

1-30

1-30

1-30

1-31

1-31

1-31

1-32

1-35

1-35

1-37

1-37

1-37

1-37

1-37

1-38

1-38

1-41

1-41

1-41

1-42

1-43

1-44

1-44

1-44

1-44

1-44

1-45

1-45

1-45

1-45

1-46

1-49

1-49

1-50

Contents-2

Page 8

Motor Circuit

Temperature Control Circuit

Preamplifier

Analog to Digital Conversion

Digital Circuits

Oxygen Board 78354-66541 and 78356-66541

General Principle of Operation

Preamplifier Circuit

Temp/Pleth/Aux Board 78353-66552 and 78354-66552

Pleth Floating Input Circuit

Test Function Generator

INOP Detection Circuit

Pleth Sensor Circuit

Temperature Floating Input Circuit

Temperature Grounded Circuit

Aux Input Circuit

Digital Circuits

Temp/Pleth/Aux Parameter Software

Temperature Board 78832-66552 and 78834-66552

Input Circuits

Signal Rectification and A/D Conversion

Digital Circuits

Temperature Parameter Software

..........................

....................

...........................

....................

..........................

...............

....................

.........................

...........

.....................

.......................

.......................

.........................

..................

....................

...................

...........................

.................

.............

...........................

................

...........................

...................

Dual Temperature Board 78353-66554 and 78354-66554

Input Circuits

Signal Rectification and A/D Conversion

Digital Circuits

Temperature Parameter Software

Respiration Board 78832-66562

Input Circuits

INOP Detection

Respiration Wave Signal Circuits

Feedback Loop Operation

A/D Conversion

A. Initial conditions

B. Patient impedence increases to 1.5 kohm + 10

C. Summing point again at zero volts

...........................

................

...........................

...................

.....................

...........................

..........................

...................

......................

..........................

........................

...........

................

Test Signals ............................

Digital Circuits

Respiration Parameter Software

...........................

....................

Transcutaneous Partial CO2 and O2 Board 78834-66572

Transducer Recognition

tcpCO2 Input

...........................

.......................

tcpO2 Input ............................

Polarization Voltage

Heater Circuit

Temperature Control

Analog Multiplexer

Analog to Pulse Width Conversion

Repolarization

Floating Power Supply

.........................

...........................

........................

.........................

..................

...........................

.......................

..........

..........

:

......

1-50

1-50

1-53

1-53

1-53

1-54

1-54

1-54

1-57

1-57

1-57

1-57

1-57

1-57

1-57

1-58

1-58

1-58

1-60

1-60

1-60

1-60

1-60

1-63

1-63

1-63

1-63

1-63

1-67

1-67

1-67

1-67

1-67

1-68

1-68

1-68

1-68

1-69

1-69

1-69

1-73

1-73

1-73

1-73

1-73

1-74

1-74

1-74

1-75

1-76

1-76

Contents-3

Page 9

Digital Circuits

Clock ..............................

Watchdog Circuit

EAROM

Barometer Board Information

Parameter Software

Barometer Board 78834-66573

Circuit Operation

Oxygen Saturation/Pleth (SPO2) Board 78354-66510/520

Floating Section

ESU Rejection ..........................

Ambient Light Rejection

Amplification

Compensation for Ambient Light ..................

The Transducer ..........................

Multiplexer ...........................

LEDs ..............................

Selftest .............................

Grounded Section

780 System Interface (Non-Annotating) 78353-66590

Input Circuits

Beat-to-beat Heart Rate

Average Heart Rate

System Control Signals

Status byte ...........................

ECG Wave.

Respiration Wave

780 Interface Board (Annotating) 78353-66592

Digital Circuits

Analog Circuits

System Board Software

SDN Board 78353-66595

Microprocessor Interface Circuit and I/O RAM

System Interface Controller (SIC)

Data Synchronization Circuit

Control Logic

Signature RAM

RS-232C Interface Board 78354-66598 ..................

General Principle of Operation

ROM/RAM

Counter-timer Circuit

Serial Interface ...........................

Watchdog Circuit

...........................

.........................

.............................

....................

.........................

.....................

..........................

..........................

......................

.................

..........................

...........

...........................

.......................

.........................

.......................

............................

..........................

..............

...........................

...........................

.......................

........................

.............

...................

.....................

............................

...........................

....................

............................

........................

..........................

.........

: .........

1-76

1-76

1-77

1-77

1-77

1-78

1-80

1-80

1-83

1-83

1-84

1-84

1-84

1-84

1-85

1-85

1-85

1-85

1-86

1-89

1-89

1-89

1-89

1-90

1-90

1-90

1-90

1-92

1-92

1-92

1-92

1-97

1-97

1-97

1-97

1-98

1-98

1-100

1-100

1-100

1-101

1-101

1-101

Contents-4

Page 10

2. Maintenance Checks

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2a. Performance Assurance Checks

Introduction

General ..............................

Test equipment

General checks

Monitor Service Test Mode

Display Intensity

Checks in ECG Setup Mode

Filter/Diagnostic Mode Check

Parameter Set-up Keys

Pressure Channel Check and Calibration

CO2 and O2 Calibration and Adjustments

Temperature Channel Checks

Plethysmograph Channel Checks

Barometer Board Checks

tcpCO2/tcpO2 Channel Checks and Transducer

HP 15210A Calibration Unit

Installation

Description

Unpacking the Instrument

Initial Inspection

Claims For Damage

Repacking for Shipment or Storage

Instrument Identification

Specification

Operating Environment

Operating Information

Fitting the Gas Cylinders

Storage of Gas Cylinders

Disposal of Used Gas Cylinders

Routine Maintenance

Changing the Gas Cylinders

Care and Cleaning

Theory of Operation

Gas Flow Performance Checks

Test Procedure

Disassembly

Parts List

Transducer Troubleshooting

SpO2 Channel Checks

.............................

............................

...........................

......................

..........................

.....................

...................

.......................

................

...............

.....................

...................

.......................

.............

......................

.............................

.............................

......................

.........................

........................

.................

.......................

............................

.......................

........................

......................

.......................

....................

.........................

.....................

.........................

.........................

.....................

...........................

.............................

..............................

......................

........................

2-1

2a-1

2a-1

2a-2

2a-2

2a-2

2a-4

2a-4

2a-5

2a-6

2a-7

2a-9

2a-10

2a-11

2a-11

2a-11

2a-15

2a-15

2a- 15

2a-15

2a-15

2a-15

2a-16

2a-16

2a-16

2a-17

2a-17

2a-17

2a-17

2a-17

2a-18

2a-18

2a-18

2a-19

2a-20

2a-20

2a-22

2a-25

2a-26

2a-30

Contents-5

Page 11

2b. Specification Checks

Introduction

Specification Checks Test Equipment

ECG Channel

Pressure Channel

Transformer Test Settings for Pressure Output Linearity

Plethysmograph channel

Respiration Channel

NIBP Calibration and Adjustments

NIBP Calibration and Adjustments (HP7xxxC Only)

RS 232C Interface Checks

Barometer Board Adjustment

TcpCO2 /tcpO2 Channel

SpO2 Board

2c. Technical Specifications for all Monitors

Introduction

Technical Specifications 78352A/C

General ..............................

Patient safety

Power requirements:

Environment:

Display

Superaster video display:

ECG Channel (Full lead)

ECG Amplifier

Patient Safety:

Cardiotach

Digital cardiotach

Analog output

ECG wave on phone-jack.

Alarms

Test/Calibration

ST Segment Monitoring (78354-66722)

Noninvasive Blood Pressure (NIBP)

General

Modes

Alarms .............................

Temperature Channel

Trend.. .............................

General .............................

ECG Channel

Pressure Channel

Dual Temperature Channel

System Interface

System outputs

SpO2 /Pleth

Alarms

Pleth Amplifier

Cardiotach

Graticule lines

.............................

...........................

..........................

.......................

.........................

......................

....................

.......................

............................

.............................

...................

..........................

........................

...........................

..............................

......................

......................

..........................

..........................

............................

.........................

..........................

.....................

.............................

.........................

.............................

..............................

........................

..........................

.........................

.....................

..........................

..........................

............................

.............................

..........................

............................

..........................

.................

..................

................

..................

........

..........

2b-1

2b-1

2b-1

2b-9

2b-11

2b-12

2b-12

2b-14

2b-17

2b-18

2b-20

2b-21

2b-21

2c-1

2c-1

2c-1

2c-1

2c- 1

2c-1

2c-2

2c-2

2c-2

2c-2

2c-2

2c-2

2c-2

2c-3

2c-3

2c-3

2c-3

2c-3

2c-4

2c-4

2c-5

2c-5

2c-5

2c-6

2c-6

2c-6

2c-6

2c-6

2c-6

2c-6

2c-7

2c-7

2c-7

2c-7

2c-8

Contents-6

Page 12

...............................

Test

Technical Specifications 78353A

General

Patient safety:

Power requirements:

Environmental:

Display

ECG Channel (3 lead)

ECG Amplifier

Cardiotach ............................

Analog Output

Alarms

Test

Plethysmograph Channel

Pleth. amplifier

Cardiotach. ............................

Graticule lines

Test

Alarms .............................

Pressure Channel

Pressure amplifier

Auto zero

Pressure wave display

Alarms .............................

Calibration/test signal

Rear panel output

Temperature Channel

Auxiliary Input Channel

General .............................

Auxiliary input -

Graticule line labelling and resolution

Auxiliary input - 47210 Capnometer

System 780 Annotating Interface

General .............................

ECG System Outputs

Pressure system outputs

Plethysmograph system outputs

Temperature system output

System 780 Non-Annotating Interface

ECG Wave.

Heart Rate

Control Signals

Alarm Relay (only loaded on request)

Technical Specifications - 78353B and 78354A/C

..............................

..........................

........................

..........................

..............................

........................

..........................

..........................

.............................

...............................

...........................

..........................

...............................

..........................

.........................

............................

........................

........................

78205D Pressure module

Auxiliary signals and parameters

Selectable channels for external recorder

Wave .............................

Wave (All the following voltages are f 50 mV.)

Wave .............................

DC output (HR)

DC output ...........................

...........................

............................

........................

..........................

.....................

......................

.......................

.......................

.......................

................

.................

...................

.................

.......................

......................

..................

....................

.................

................

..............

..............

...........

.............

2c-8

2c-9

2c-9

2c-9

2c-9

2c-9

2c-9

2c-10

2c-10

2c-10

2c-10

2c-11

2c-11

2c-11

2c-11

2c-11

2c-12

2c-12

2c-12

2c-12

2c-12

2c-12

2c-13

2c-13

2c-13

2c-13

2c-14

2c-14

2c-14

2c-14

2c-15

2c-15

2c-16

2c-16

2c-16

2c-16

2c-16

2c-16

2c-16

2c-16

2c-17

2c-17

2c-17

2c-17

2c-17

2c-18

2c-18

2c-18

2c-18

2c-18

2c-19

Contents-7

Page 13

General ..............................

Patient safety ..........................

Power requirements ........................

Enviromental ...........................

Display ..............................

ECG Channel (Full lead)

ECG Amplifier ..........................

Cardiotach

Analog output ..........................

Alarms

Test/Calibration .........................

ST Segment Monitoring (78354-66722)

Plethysmograph Channel

Pleth. amplifier ..........................

Cardiotach

Graticule lines ..........................

Autofix

Test ...............................

Alarms

Pressure Channel

Pressure amplifier .........................

Auto zero

Pressure wave display .......................

Graticule line labelling and resolution:

Pulse Rate

Alarms .............................

Test/calibration .........................

Noninvasive Blood Pressure (NIBP)

General

Modes ..............................

Alarms

Alarm Limit Adjustments (78354C):

Respiration Channel

Respiration amplifier .......................

Respiration trigger ........................

Alarms .............................

Fractional Inspired Oxygen

Alarms

Carbon Dioxide

General

Instantaneous CO2 Wave Display

End Tidal CO2 Numerical Display

Respiration Rate Numerical Display

Alarms .............................

Temperature Channel

Auxiliary Input Channel

General .............................

Auxiliary input - 78205D Pressure module

Graticule line labelling and resolution.

Auxiliary input - 47210 Capnometer

SpO2 / Pleth ............................

............................

..............................

............................

.............................

.............................

..........................

............................

............................

.............................

.............................

.........................

.............................

...........................

.............................

......................

......................

..................

......................

..................

........................

.......................

................

................

.................

.................

.................

..............

................

.................

2c-19

2c-19

2c-19

2c-19

2c-20

2c-20

2c-20

2c-20

2c-21

2c-21

2c-21

2c-21

2c-22

2c-22

2c-22

2c-23

2c-23

2c-23

2c-23

2c-23

2c-23

2c-23

2c-24

2c-24

2c-24

2c-24

2c-24

2c-25

2c-25

2c-25

2c-25

2c-25

2c-26

2c-26

2c-26

2c-26

2c-26

2c-27

2c-27

2c-27

2c-27

2c-27

2c-28

2c-28

2c-29

2c-29

2c-29

2c-29

2c-29

2c-30

2c-30

Contents-8

Page 14

Alarms

Pleth Amplifier

Cardiotach

Graticule lines

Test

.............................

........................... 2c-30

............................

..........................

...............................

Alarms .............................

System Interface

General (Opt. J11 only)

ECG system outputs

Pressure system outputs

..........................

......................

.......................

......................

Respiration system output

Plethysmograph system outputs

Temperature system output

Trend..

General

ECG Channel

Respiration Channel

Pressure Channel

Pleth Channel

AUX Channel

.............................

.............................

..........................

........................

.........................

..........................

..........................

Single Temperature Channel

Dual Temperature Channel

Oxygen Channel

Carbon Dioxide Channel

SpO2 Channel (78354C)

.........................

......................

......................

Technical Specifications - 78832A

General

Patient safety

Power Requirements

Environmental

Display

Superaster video display

ECG Channel

ECG Amplifier

Patient Safety:

Cardiotach

Analog Output

Alarms

Test/Calibration

Temperature Channel

Respiration Channel

Respiration amplifier

Respiration trigger

Respiration alarms

780 Annotating Interface

General

ECG System Outputs

.............................. 2c-36

........................... 2c-36

........................ 2c-36

..........................

.............................. 2c-36

...................... 2c-36

........................... 2c-37

.......................... 2c-37

.......................... 2c-37

............................ 2c-37

.......................... 2c-37

.............................

.........................

........................

.........................

.......................

........................

........................

.......................

.............................

.......................

Respiration-system output

Temperature - system output

Trend..

General

.............................

.............................

.....................

..................

....................

....................

.....................

....................

.....................

....................

2c-30

2c-31

2c-31

2c-31

2c-31

2c-31

2c-31

2c-31

2c-32

2c-32

2c-32

2c-32

2c-33

2c-33

2c-33

2c-33

2c-33

2c-33

2c-34

2c-34

2c-34

2c-34

2c-34

2c-35

2c-36

2c-36

2c-37

2c-38

2c-38

2c-38

2c-38

2c-39

2c-39

2c-39

2c-39

2c-39

2c-40

2c-40

2c-40

2c-40

Contents-9

Page 15

ECG Channel

Respiration Channel ........................

Technical Specifications - 78833A

General

Patient safety ..........................

Power Requirements ........................

Environmental ..........................

Display

Superaster video display ......................

ECG Channel ...........................

ECG Amplifier ..........................

Patient Safety: ..........................

Cardiotach ............................

Analog Output ..........................

Alarms .............................

Test/Calibration .........................

Respiration Channel

Respiration amplifier .......................

Respiration trigger ........................

Respiration alarms ........................

Pressure Channel

Pressure amplifier .........................

Auto zero ............................

Pressure wave display .......................

Pulse rate ............................

Graticule line labelling and resolution: ................

Alarms .............................

Test/calibration .........................

780 Annotating Interface

General .............................

ECG System Outputs .......................

Respiration-system output .....................

Pressure system output (P1 only) ..................

Trend..

General .............................

ECG Channel

Respiration Channel ........................

Pressure Channel .........................

Technical Specifications - 78833B and 78834A/C .............

General

Patient safety

Power requirements ........................

Environmental ..........................

Display

ECG Channel ...........................

ECG Amplifier ..........................

Cardiotach ............................

Analog output

Alarms

Test/Calibration

Temperature Channel

..............................

..............................

.............................

..............................

..............................

.............................

..........................

....................

.........................

..........................

.......................

..........................

..........................

..........................

.........................

........................

2c-40

2c-41

2c-42

2c-42

2c-42

2c-42

2c-42

2c-42

2c-42

2c-43

2c-43

2c-43

2c-43

2c-43

2c-43

2c-44

2c-44

2c-44

2c-44

2c-45

2c-45

2c-45

2c-45

2c-45

2c-45

2c-46

2c-46

2c-46

2c-47

2c-47

2c-47

2c-47

2c-47

2c-48

2c-48

2c-48

2c-48

2c-48

2c-49

2c-49

2c-49

2c-49

2c-49

2c-50

2c-50

2c-50

2c-51

2c-51

2c-51

2c-51

2c-52

Contents-10

Page 16

Respiration Channel

Respiration amplifier

Respiration trigger

Respiration alarms

Pressure Channel

Pressure amplifier

Auto zero

............................

Pressure wave display

Graticule line labelling and resolution:

Pulse Rate

Alarms

............................

.............................

.........................

.......................

........................

........................

..........................

.........................

.......................

................

Test/calibration

Transcutaneous O2 and CO2 Channel (tcpO2 and tcpCO2) : : : : : : : :

General

Transducer Heating

.............................

........................

Alarms .............................

Test Signal:

780 Annotating Interface

General

ECG system outputs

Respiration system output

Temperature system output

Pressure system output

tcpO2 and tcpCO2 system output

Plethysmograph system outputs (78834C)

Oxygen system output (78834C)

Carbon Dioxide system output (78834C)

Trend..

General

ECG Channel

Pressure Channel

Respiration Channel

Dual Temperature Channel

tcpO2 and tcpCO2 Channel

Pleth Channel (78834C)

Oxygen Channel (78834C)

Carbon Dioxide Channel (78834C)

SpO2 Channel (78834C)

SpO2 / Pleth (78834C)

Alarms

Pleth Amplifier

Cardiotach

Graticule lines

...........................

.......................

.............................

.......................

.....................

....................

......................

..................

..............

..................

...............

.............................

.............................

..........................

.........................

........................

.....................

....................

......................

.....................

.................

......................

......................

.............................

..........................

............................

..........................

Autofix .............................

...............................

Test

Pulse rate alarm limits

Noninvasive Blood Pressure (NIBP)

General

Modes

...................

..............................

......................

..................

. .........

Alarms .............................

Alarm Limit Adjustments:

.....................

2c-52

2c-52

2c-52

2c-52

2c-53

2c-53

2c-53

2c-53

2c-53

2c-54

2c-54

2c-54

2c-55

2c-55

2c-55

2c-55

2c-56

2c-56

2c-56

2c-56

2c-56

2c-56

2c-57

2c-57

2c-57

2c-57

2c-57

2c-58

2c-58

2c-58

2c-58

2c-58

2c-58

2c-59

2c-59

2c-59

2c-59

2c-59

2c-60

2c-60

2c-60

2c-60

2c-60

2c-60

2c-61

2c-61

2c-61

2c-61

2c-61

2c-62

2c-62

Contents-11

Page 17

Fractional Inspired Oxygen (78834C)

Alarms

Carbon Dioxide (78834C) : : : : : : : : : : : : : : :

General

Instantaneous CO2 Wave Display

End Tidal CO2 Numerical Display

Respiration Rate Numerical Display

Alarms

Graticule Line Labelling and Resolution:

Technical Specifications - 78356A

General

Patient safety

Power requirements

Environment ....................

Display

Inspired Oxygen

Carbon Dioxide

General

Instantaneous CO2 Wave Display

End Tidal and Inspired Minimum CO2 Numerical Display

Respiration Rate Numerical Display

Alarms

Trend

General ......................

Oxygen Channel

Carbon Dioxide Channel

System Interface

General (Opt. J11 only)

Instantaneous CO2

End Tidal CO2

Respiration Rate

02 ........................

......................

......................

.............

.......................

...................

.................

.......................

...................

....................

......................

......................

........................

..................

...............

...................

...............

.................

...................

..................

..........

...........

..........

..........

.......

...........

..........

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

.......

2c-62

2c-62

2c-62

2c-62

2c-63

2c-63

2c-63

2c-63

2c-64

2c-65

2c-65

2c-65

2c-65

2c-65

2c-65

2c-66

2c-66

2c-66

2c-67

2c-67

2c-67

2c-67

2c-68

2c-68

2c-68

2c-68

2c-68

2c-68

2c-69

2c-69

2c-69

2c-69

A. Ordering Information

Main Sales and Support Offices

United States of America

Other International Areas

Contents-12

..............

...............

...............

.......

.......

.......

A-1

A-1

A-2

Page 18

Figures

1-1. Allocation of Function Blocks to Time Slices

1-2. Shared Memory System

1-3. Mother Board Block Diagram

1-4. Address/Character Distribution on the screen

1-5. Display Microprocessor Board Block Diagram

1-6. Single Channel Interpolation Board Block Diagram

1-7. Interpolation Board Block Diagram

1-8. Voltage Sensing and Regulation

1-9. Audio Board Block Diagram

1-10. ECG Board Block Diagram (Full Lead)

1-11. ECG Board Block Diagram (3 Lead)

1-12. Pressure Board Block Diagram

1-13. Non-Invasive Blood Pressure Board Block Diagram (78352-66535)

1-14. Non-Invasive Blood Pressure Board Block Diagram (78352-66538)

1-15. 14360A Sensor, Mechanical Diagram

1-16. CO2/02 Board Block Diagram

1-17. Temp/Pleth/Aux Board Block Diagram

1-18. Temperature Board Block Diagram

1-19. Dual Temperature Board Block Diagram

1-20. Feedback Loop Operation - Stage 1

1-21. Feedback Loop Operation - Stage 2

1-22. Feedback Loop Operation - Stage 3

1-23. Respiration Board Block Diagram

1-24. TcpCOz/Oz Board Block Diagram

1-25. Barometer Board Block Diagram

1-26. SpOn Board Block Diagram

1-27. 780 System Board (Non-Annotating) Block Diagram

1-28. 780 System Board (Annotating) Block Diagram

1-29. SDN Board Block Diagram

1-30. RS232C Block Diagram

2a-1. Rigel Safety Tester

2a-2. Display Intensity

2a-3. Position of Photoresistor in A and B monitors

2a-4. Position of Photoresistor Monitor in “C” series monitors

2a-5. Initial Set-up Displays for Pressure, Pleth and Respiration

2a-6. Equipment for Pressure Calibration

2a-7. Mercury Calibration Set-up Display

2a-8. Pressure Display after successful Calibration

2a-9. Resistive Simulator for 0 and 200mmgh

2a-10. Block diagram - Internal Components

2a-11. Gas Flow Performance Check - Test 1

2a-12. Gas Flow Performance Check - Test 2/3

..........................

.......................

....................

..................

....................

.....................

.................

....................

.................

....................

..................

..................

..................

..................

...................

..................

...................

.....................

......................

.......................

.........................

..................

..................

.................

.................

..............

.............

.............

...........

................

................

................

..........

.............

.............

.........

........

..............

................

................

.....

.....

1-2

1-3

1-7

1-8

1-11

1-15

1-17

1-18

1-19

1-25

1-29

1-33

1-39

1-47

1-51

1-55

1-59

1-61

1-65

1-68

1-68

1-68

1-71

1-79

1-81

1-87

1-91

1-95

1-99

1-102

2a-1

2a-4

2a-4

2a-4

2a-6

2a-7

2a-7

2a-8

2a-8

2a-19

2a-20

2a-21

Contents-13

Page 19

2a-13. Cover Securing Screws (veiwed from underneath)

2a-14. Control Knob

2a-15. Regulator Control Block Securing Screws

2a-16. Regulator and Valve Control Blocks

2a-17. Tubing and Flow Regulator

2a-18. Replaceable Parts for 15210A

2b-1. ECG Amplifier Gain Frequency Response Test Set-up

2b-2. Trigger Sensitivity Check Set-up

2b-3. ECG Amplifier Noise Test Set-up

2b-4. ECG Noise with 50Hz Component

2b-5. 1 mV Calibration Test Set-up

2b-6. Common Mode Rejection Set-up

2b-7. Notch Filter Test Response Characteristic

2b-8. Equipment for Zero and Range Accuracy Check

2b-9. Plethysmograph Channel Test Circuit

2b-10. Test Circuit for INOP check

2b-11. Test Equipment for Respirotach Range Check

...........................

...............

..................

.....................

.....................

...................

...................

..................

....................

...................

...............

.................

.....................

.............

............

..........

............

2a-22

2a-22

2a-23

2a-23

2a-24

2a-25

2b-4

2b-5

2b-6

2b-6

2b-7

2b-8

2b-9

2b-10

2b-12

2b-13

2b-13

Contents-14

Page 20

Tables

1-1. Test Signals and Results

1-2. System Output Configurations

2b-1. Test Equipment Requirements for Specification Checks

2b-2. mmHg Test

............................

.......................

....................

1-69

1-93

......... 2b-3

2b-11

Contents-15

Page 21

1

Theory Of Operation

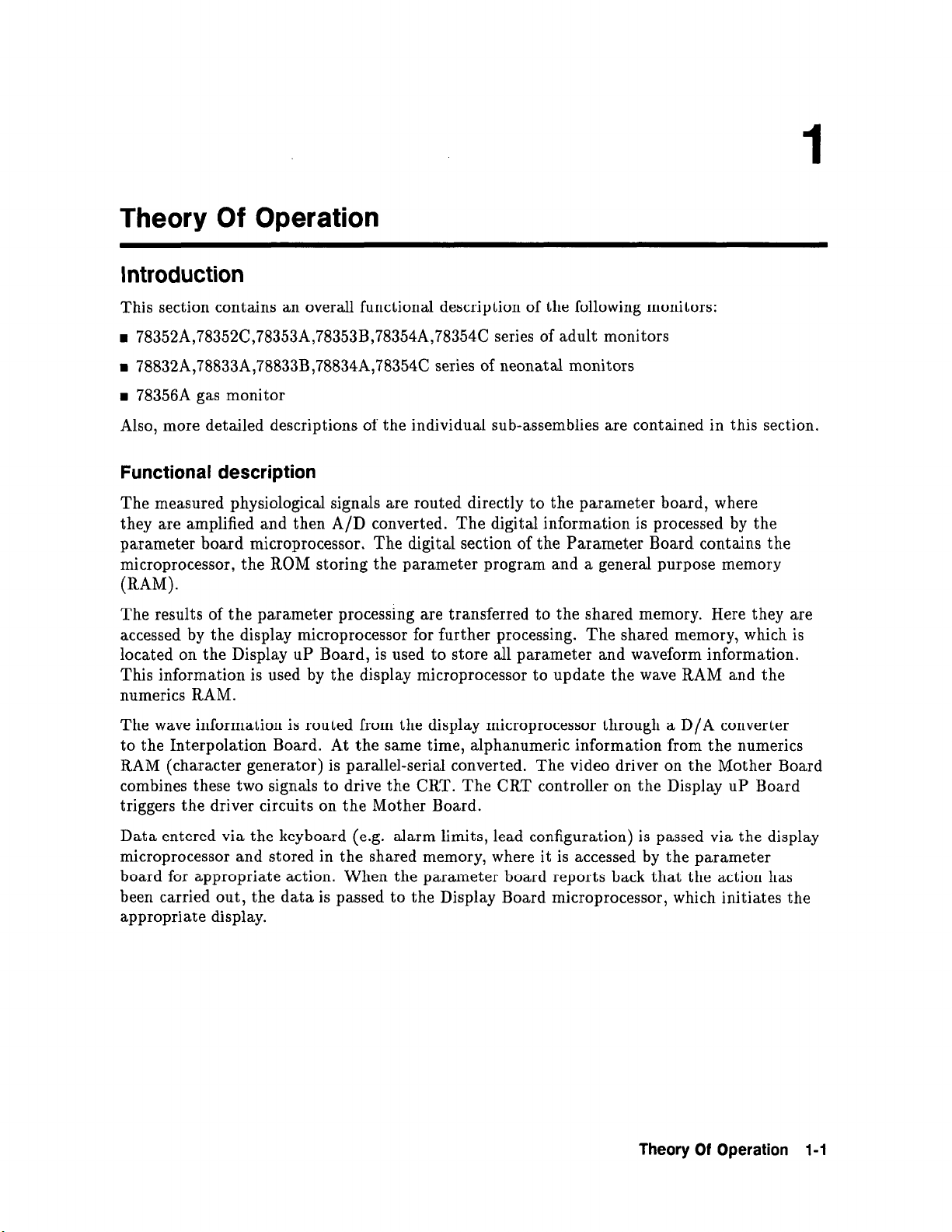

Introduction

This section contains an overall functional description of the following monitors:

n

78352A,78352C,78353A,78353B,78354A,78354C series of adult monitors

n

78832A,78833A,78833B,78834A,78354C series of neonatal monitors

n

78356A gas monitor

Also, more detailed descriptions of the individual sub-assemblies are contained in this section.

Functional description

The measured physiological signals are routed directly to the parameter board, where

they are amplified and then A/D converted. The digital information is processed by the

parameter board microprocessor. The digital section of the Parameter Board contains the

microprocessor, the ROM storing the parameter program and a general purpose memory

(RAM).

The results of the parameter processing are transferred to the shared memory. Here they are

accessed by the display microprocessor for further processing. The shared memory, which is

located on the Display UP Board, is used to store all parameter and waveform information.

This information is used by the display microprocessor to update the wave RAM and the

numerics RAM.

The wave information is routed from the display microprocessor through a D/A converter

to the Interpolation Board. At the same time, alphanumeric information from the numerics

RAM (character generator) is parallel-serial converted. The video driver on the Mother Board

combines these two signals to drive the CRT. The CRT controller on the Display UP Board

triggers the driver circuits on the Mother Board.

Data entered via the keyboard (e.g. alarm limits, lead configuration) is passed via the display

microprocessor and stored in the shared memory, where it is accessed by the parameter

board for appropriate action. When the parameter board reports back that the action has

been carried out, the data is passed to the Display Board microprocessor, which initiates the

appropriate display.

Theory Of Operation l-l

Page 22

Shared Memory and Data Transfer

General

Data transfer in the 783Xx series, the 788Xx series and the 78356A is carried out via a

common memory area, to which all function blocks have access. This common memory is the

Shared Memory chip U40 on A2 Display UP board. The local bus systems are separated from

the main shared memory bus by tri-state buffers.

Power Fail

In the event of power fail the configuration of the instrument at the time of power fail is held

in the shared memory for 15 seconds.

Time Slices

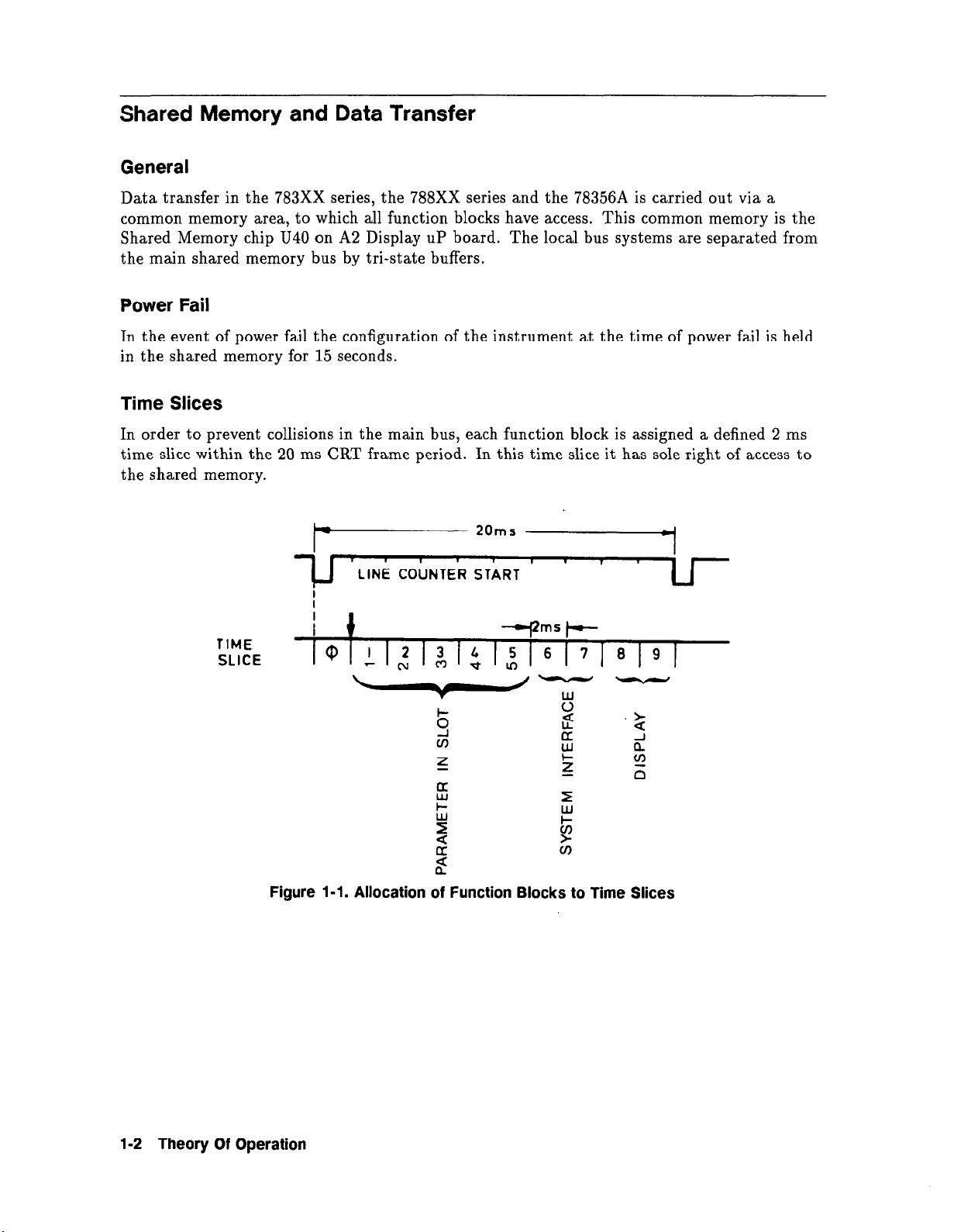

In order to prevent collisions in the main bus, each function block is assigned a defined 2 ms

time slice within the 20 ms CRT frame period. In this time slice it has sole right of access to

the shared memory.

/_ 20,ms

LINE COUNTER START

Figure l-l. Allocation of Function Blocks to Time Slices

1-2 Theory Of Operation

Page 23

Blatt von alte Seite l-3 hier horizontal einfiigen

Figure 1-2. Shared Memory System

Theory Of Operation 1-3

Page 24

. . . . . . . .

. . .

1-4 Theory Of Operation

Page 25

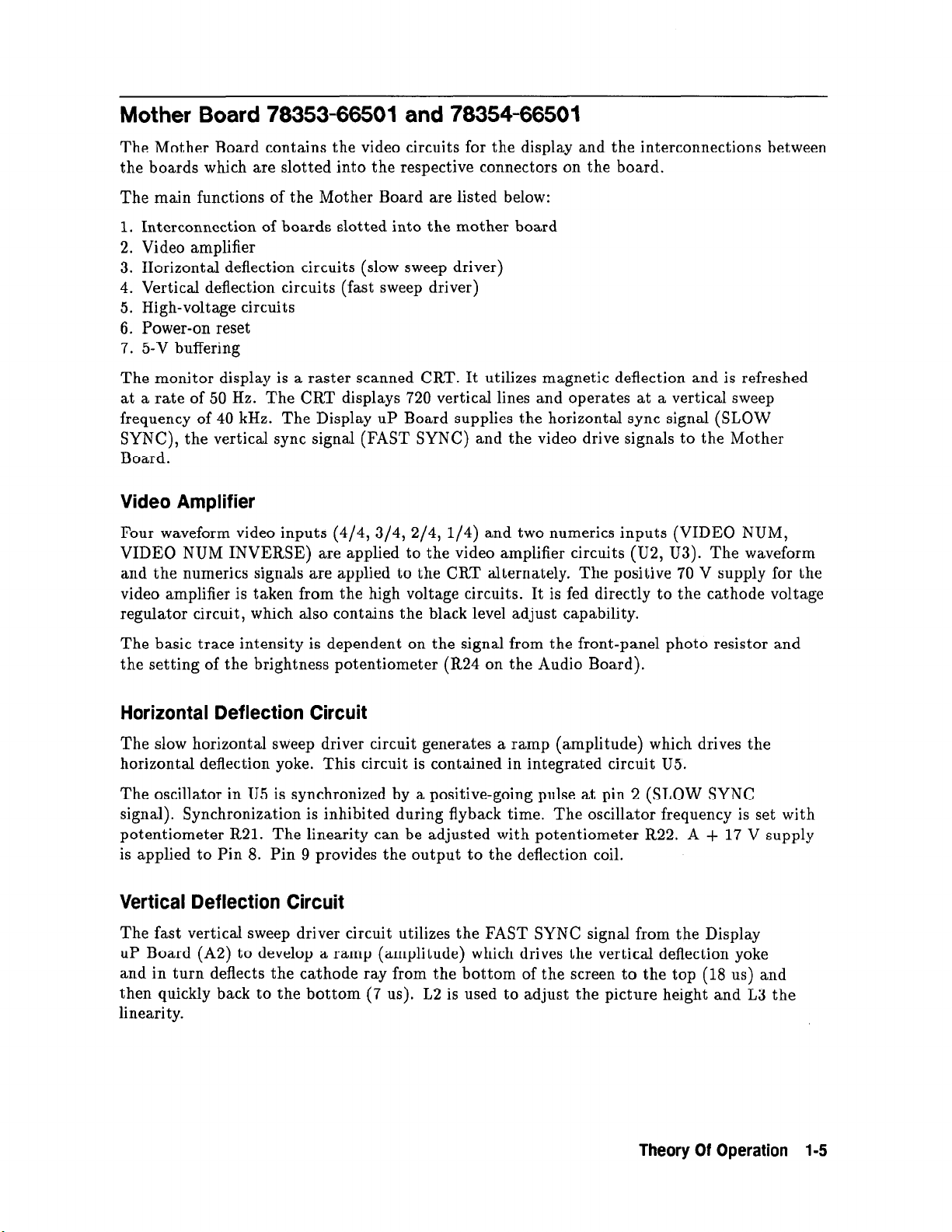

Mother Board 78353-66501 and 78354-66501

The Mother Board contains the video circuits for the display and the interconnections between

the boards which are slotted into the respective connectors on the board.

The main functions of the Mother Board are listed below:

1. Interconnection of boards slotted into the mother board

2. Video amplifier

3. Horizontal deflection circuits (slow sweep driver)

4. Vertical deflection circuits (fast sweep driver)

5. High-voltage circuits

6. Power-on reset

7. 5-V buffering

The monitor display is a raster scanned CRT. It utilizes magnetic deflection and is refreshed

at a rate of 50 Hz. The CRT displays 720 vertical lines and operates at a vertical sweep

frequency of 40 kHz. The Display UP Board supplies the horizontal sync signal (SLOW

SYNC), the vertical sync signal (FAST SYNC)

Board.

Video Amplifier

Four waveform video inputs (4/4, 3/4, 2/4, l/4) and two numerics inputs (VIDEO NUM,

VIDEO NUM INVERSE)

and the numerics signals are applied to the CRT alternately. The positive 70 V supply for the

video amplifier is taken from the high voltage circuits. It is fed directly to the cathode voltage

regulator circuit, which also contains the black level adjust capability.

are applied to the video amplifier circuits (U2, U3). The waveform

and the video drive signals to the Mother

The basic trace intensity is dependent on the signal from the front-panel photo resistor and

the setting of the brightness potentiometer (R24 on the Audio Board).

Horizontal Deflection Circuit

The slow horizontal sweep driver circuit generates a ramp (amplitude) which drives the

horizontal deflection yoke. This circuit is contained in integrated circuit U5.

The oscillator in U5 is synchronized by a positive-going pulse at pin 2 (SLOW SYNC

signal). Synchronization is inhibited during flyback time. The oscillator frequency is set with

potentiometer R21. The linearity can be adjusted with potentiometer R22. A + 17 V supply

is applied to Pin 8. Pin 9 provides the output to the deflection coil.

Vertical Deflection Circuit

The fast vertical sweep driver circuit utilizes the FAST SYNC signal from the Display

UP Board (A2) to develop a ramp (amplitude) which drives the vertical deflection yoke

and in turn deflects the cathode ray from the bottom of the screen to the top (18 us) and

then quickly back to the bottom (7 us). L2 is used to adjust the picture height and L3 the

linearity.

Theory Of Operation l-5

Page 26

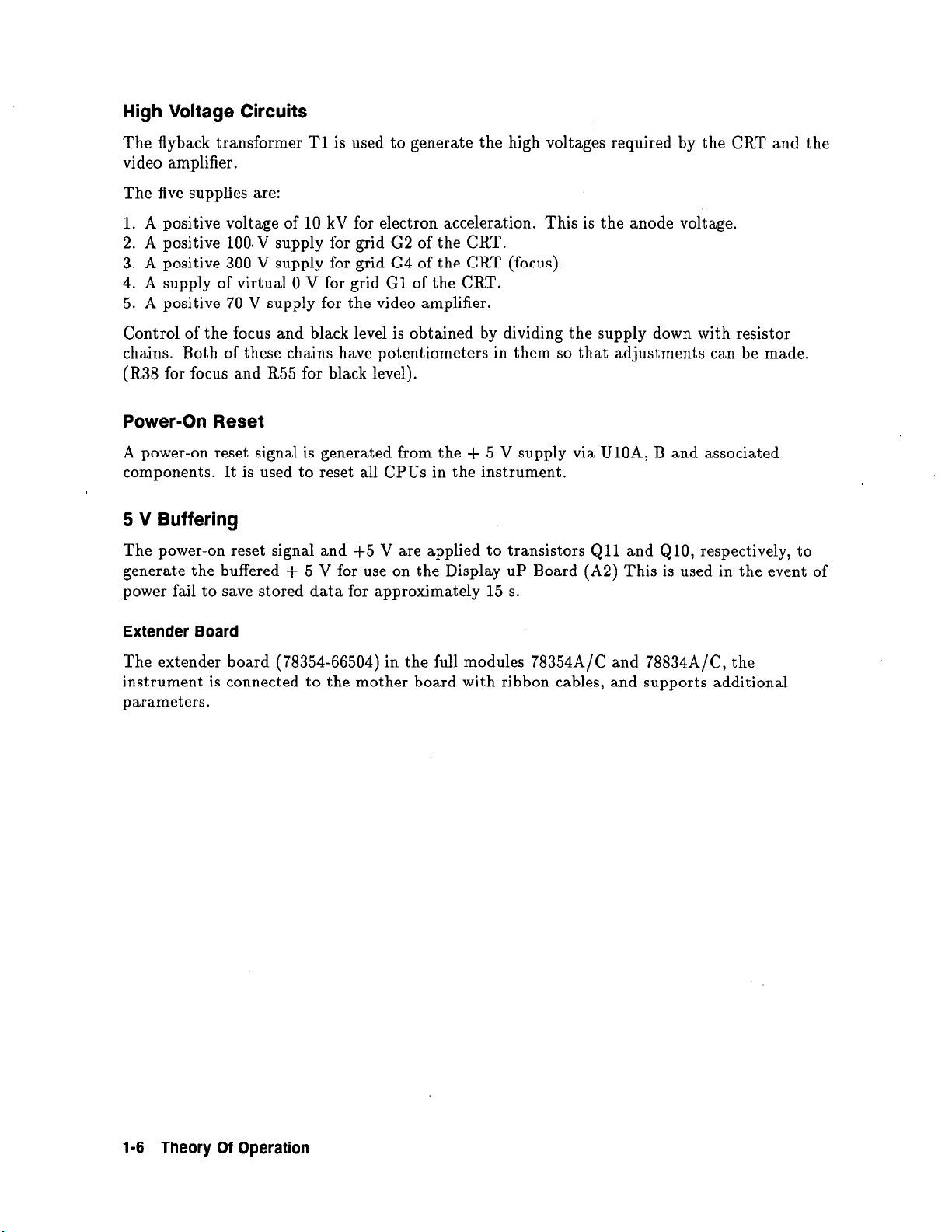

High Voltage Circuits

The flyback transformer Tl is used to generate the high voltages required by the CRT and the

video amplifier.

The five supplies are:

1. A positive voltage of 10 kV for electron acceleration. This is the anode voltage.

2. A positive 100, V supply for grid G2 of the CRT.

3. A positive 300 V supply for grid G4 of the CRT (focus).

4. A supply of virtual 0 V for grid Gl of the CRT.

5. A positive 70 V supply for the video amplifier.

Control of the focus and black level is obtained by dividing the supply down with resistor

chains. Both of these chains have potentiometers in them so that adjustments can be made.

(R38 for focus and R55 for black level).

Power-On Reset

A power-on reset signal is generated from the + 5 V supply via UlOA, B and associated

components. It is used to reset all CPUs in the instrument.

5 V Buffering

The power-on reset signal and +5 V are applied to transistors Qll and &lo, respectively, to

generate the buffered + 5 V for use on the Display UP Board (A2) This is used in the event of

power fail to save stored data for approximately 15 s.

Extender Board

The extender board (78354-66504)

instrument is connected to the mother board with ribbon cables, and supports additional

parameters.

in the full modules 78354A/C and 78834A/C, the

1-6 Theory Of Operation

Page 27

Blatt von alte Seite l-5 hier einfiigen

Figure 1-3. Mother Board Block Diagram

Theory Of Operation 1-7

Page 28

Display UP Boards 78353066502 (16K byte), 78354-66502 (40K byte)

78354-66602 and 78354966702 (48K byte)

The Display UP Board is the heart of the instrument. It contains the following functions:

1. Shared memory

2. Character generation (numerics)

3. Slow/fast sync. signal generation

4. Clock generation

5. 20 ms and 2 ms interrupt signal generation

6. Alarm trigger generation

7. Power fail circuit

8. Keyboard handling

The shared memory and data transfer are already described in “Shared Memory and Data

Transfer”.

Character Generation

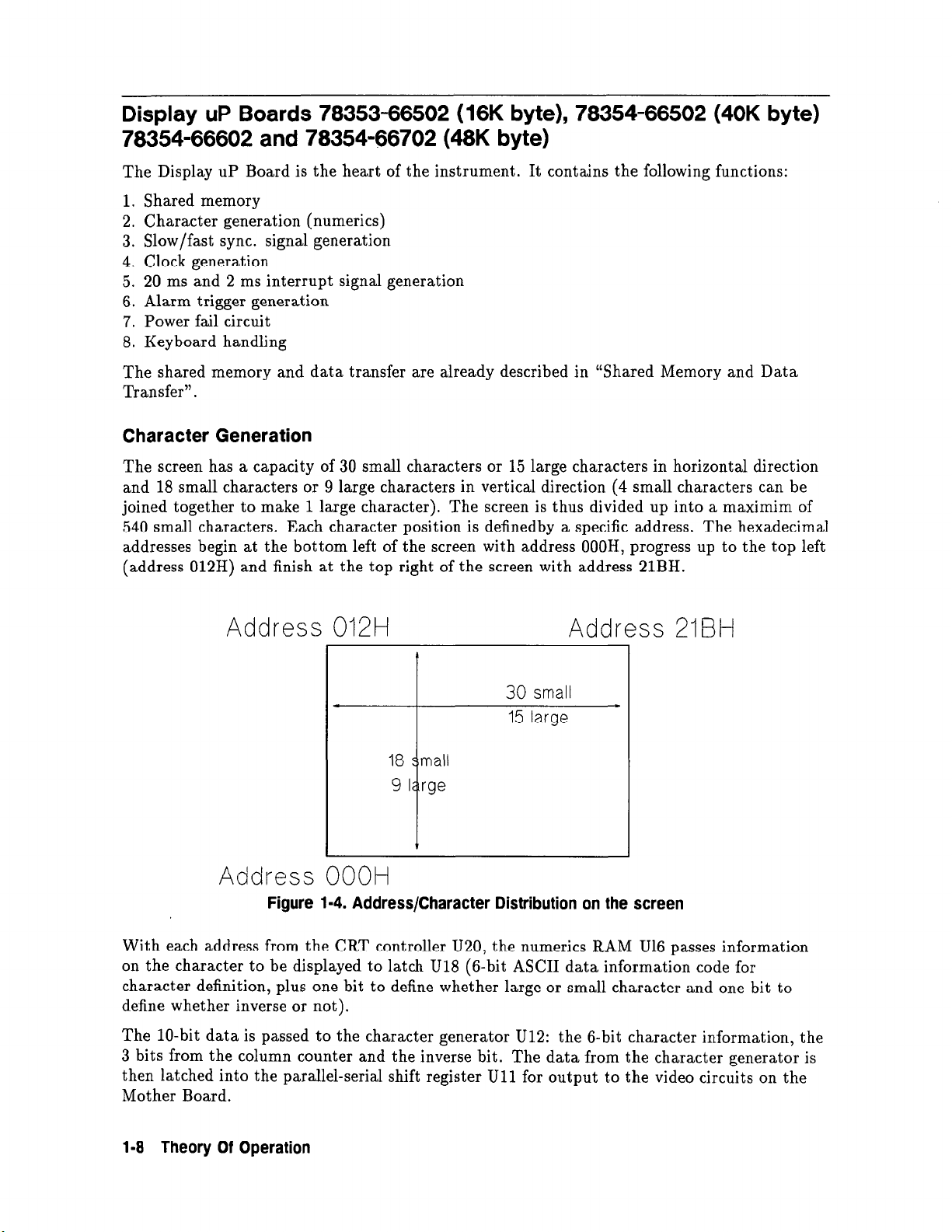

The screen has a capacity of 30 small characters or 15 large characters in horizontal direction

and 18 small characters or 9 large characters in vertical direction (4 small characters can be

joined together to make 1 large character). The screen is thus divided up into a maximim of

540 small characters. Each character position is definedby a specific address. The hexadecimal

addresses begin at the bottom left of the screen with address OOOH, progress up to the top left

(address 012H) and finish at the top right of the screen with address 21BH.

Address 012H

30

15 large

Address 21BH

small

Address OOOH

Figure 1-4. Address/Character Distribution on the screen

With each address from the CRT controller U20, the numerics RAM U16 passes information

on the character to be displayed to latch U18 (6-bit ASCII data information code for

character definition, plus one bit to define whether large or small character and one bit to

define whether inverse or not).

The lo-bit data is passed to the character generator U12: the 6-bit character information, the

3 bits from the column counter and the inverse bit. The data from the character generator is

then latched into the parallel-serial shift register Ull for output to the video circuits on the

Mother Board.

1-8 Theory Of Operation

Page 29

The sweep is delayed by two clock signals so that it does not start until the character

information has reached the parallel-serial shift register Ull; i.e. with one clock pulse, address

1 data is latched into the parallel-serial register, address 2 data is latched into U18 and

address 3 data presented to the numerics RAM from the CRT controller.

The CRT controller U20 is programmed to provide 24 fast sweeps per row of addresses. The

character size information is passed to column counter U14 to determine the number of fast

sweeps per column. With an 8x8 dot matrix per small character, this gives 3 fast sweeps for

every column for a small character, and 6 fast sweeps for every column for a large character.

The character size information is also passed to the load and clock multiplexer. The shift rate

for small characters is twice as high as the shift rate for the large characters. In the wave area

the characters are smaller than in the numeric area, 4x6 dot matrix instead of 5x7 dot matrix.

All characters in the wave area and the inverse characters in the numeric area are displayed

with half intensity.

Information from the CPU can only be written into the numerics RAM during the 2 ms

horizontal retrace time. For large characters the ASCII information is written into the

numerics RAM four times altogether.

Add X

I I

Small character

addressed once

Slow/fast Sync. Signal Generation

The CRT controller U20 also provides the slow sync. and the fast sync. signals for the video

circuits on the Mother Board and the display enable (DE) signal for the interpolation circuits

on A3.

Clock Generation

Clock chip Ul provides the clock signal for the clock divider U6. The clock signals generated

here are used in the entire instrument.

2 ms Interrupt Signal Generation

The 2 ms interrupt circuit U2, U3, U8 is used to generate the shared memory access timing

signals.

Alarm Trigger Generation

Add X Add X Large character

addressed

Add X Add x four times

4-l

The CPU generates the QRS, alarm and INOP trigger signals and latches these from the data

bus into U32 (alarm latch). U32 passes the trigger signals to the Audio Board for further

processing.

Theory Of Operation 1-9

Page 30

Power Fail Circuit

In the event of power fail, the shared memory, U40, is buffered for at least 15 s. If power

returns after these 15 s, the power fail signal is delayed (30 ms after the reset signal). This

creates a power-on reset, i.e. instrument set-up is reconfigured. If power returns before the

15 s are up, the instrument set-up is maintained.

Display Software

The Display software contains the following modules:

n

Initialisation of CRT controller

n

Self tests (ROM/RAMS/

n

Service tests (CRT adjust, wave interpolation check)

n

Keyboard handling

n

Soft key labeling

n

Display editing

n

Processing and issuing of alarms

H Wave handling (wave addressing, wave RAM loading, erase

n

bar control)

n

Communication with the parameter software via the common shared memory

The display software is contained in one 32K x 8 EPROM (U26), and in one 8K x 8 EPROM

(U50) on board 78354-66502, in one 16K EPROM (U50) on boards 78354-66602 and

78354-66702.

sounds test) and error handling

Note

I

lb

78353-66502 Board U26 is 16K x 8,

U47,U52,U54 and U55)

)

<ON RESET

) not included

l-10 Theory Of Operation

Page 31

Faltblatt von alte Seite l-9 hier einfiigen

Figure l-5. Display Microprocessor Board Block Diagram

Theory Of Operation

l-1 1

Page 32

. . . . . . . .

. . .

1-12 Theory Of Operation

Page 33

Single Channel Interpolation Board 78352-66503

The Interpolation Board contains most of the control circuit for generating the video pulses

for the waveform display.

The Monitor display uses a vertical raster format of 720 vertical lines with a vertical raster

frequently of 40 kHz and a frame frequency of 50 Hz. To eliminate the quantitization of

sampled data, the Interpolation Board utilizes a smoothing algorithm. The smoothing

algorithm interpolates four consecutive waveform samples.

of the four samples, the intensity of the CRT beam is modulated to produce a continuous

waveform with a constant line width.

The main functions of the Interpolation Board are listed below:

1. D-A converter

2. Sample and hold

3. Shuffle mux

4. Video pulse generator

5. Ramp generator

6. Raster line control

7. Erase bar latch

8. Wave length latch

9. Start-up delay

10. RAM for A2 display board (RAM 1)

Depending on the relative values

D-A Convertor and Sample and Hold Circuits

The waveform is stored in digital form in the wave RAM 1 (U35). It is converted in U5 into

an analog voltage in order to perform the smoothing algorithm. The smoothing algorithm

uses four waveform samples. Analog multiplexer A (U8) acts as a 4 PST switch rotating one

position in between every raster line. The sample and hold circuit (UlO), therefore, holds the

dc level of the present and previous 3 waveform samples.

Shuffle MUX

Analog multiplexer B (Ull, Ul2) makes alternately available to the video pulse generator the

four stored dc levels, in the correct time relationship.

Video Pulse Generator

The weighted comparators (U14, U15, U16, U17) generate a series of pulses in response to the

waveform samples. The video pulse generator circuit translates the pulses from the weighted

comparators into video pulses that are used by the video circuits on the Mother Board (Al).

Theory Of Operation 1-13

Page 34

Ramp Generator

The ramp generator (U28, Ql, Q2) g

ramp signals are used by the weighted comparators for each sample that is displayed. The

output combinational logic within the video pulse generator logically combines these pulses so

as to produce four digital outputs corresponding to four levels of CRT beam intensity.

enerates a ramp for each raster line (fast sweep). The

Raster Line Control

During data input to the DA converter U5, the raster line control (UlA, UlB) sends a WAIT

signal back to the Display UP Board, in order to synchronize the CPU, which operates as a

line counter. This status is reversed by the display enable signal.

Erase Bar Latch

The erase bar latch (U4A) provides waveform blanking (fading effect of erase bar) by using

Data DO information.

Wave Length Latch

The wave length latch (U3A)

have been displayed.

is used to blank the wave after a defined number of raster lines

Start-up Delay

The start-up delay (U7, U3B)

and ensures that the wave is blanked until all four samples are stored for the next frame.

d rives MUX A decoder (U9A, U32) and MUX B decoder (U2)

1-14 Theory Of Operation

Page 35

Faltblatt von alte Seite l-11 hier einfiigen

Figure 1-6. Single Channel Interpolation Board Block Diagram

Theory Of Operation 1-15

Page 36

Three-Channel Interpolation Board 78353-66503

The Interpolation Board (78353-66503)

pulses for the waveform display.

The main functions of the Interpolation Board are listed below:

1. D-A conversion

2. Waveform smoothing

3. Load Control

4. Load Timing

5. Video Pulse generation

6. Ramp generation

7. Ramp timing

8. Erase bar latch

The 783Xx and 788Xx monitor series use a vertical raster format of 720 vertical lines

with a vertical raster frequency of 40 kHz and a frame frequency of 50 Hz. To eliminate

the quantization of sampled data, the Interpolation Board uses a smoothing algorithm.

The smoothing algorithm interpolates four consecutive waveform samples, and is carried

out separately for each of the three channels. Depending on the relative values of the four

samples, the intensity of the CRT beam is modulated to produce a continuous waveform with

a constant line width.

The waveform is stored in digital form in the wave RAM

2 or 3 into an analog voltage, in order to perform the smoothing algorithm. The smoothing

algorithm uses four waveform samples.

contains the control circuit for generating the video

(U14).

It is converted in DAC

1,

In the Hybrid circuits the dc levels of the four waveform samples are compared with

the output signals of the ramp generators, resulting in a series of pulses. The output

combinational logic within the video intensity logic circuits logically combines these pulses

so as to produce four digital outputs corresponding to four levels of CRT beam intensity.

These video pulses are transferred to the video circuits on the mother board (to the 2 axis

amplifier).

Data input and output from the DAC stage is controlled by the load-control circuit which also

supplies a waveform-blanking signal for each channel, to the erase bar latch.

The load timing circuit controls the timing and sequence of signals into, and out of, the

Hybrid circuits. The load timing circuit also provides a wave-blanking signal, to blank all

waves, direct to the video intensity logic circuits.

The erase bar latch provides selective waveform blanking (fading effect of erase bar).

1-16 Theory Of Operation

Page 37

Blatt von alte Seite 1-13 verkleinern and horizontal hier einfiigen

Figure 1-7. Interpolation Board Block Diagram

Theory Of Operation 1-17

Page 38

Power Supply Board 78351-66506

+5 V DC Supply

In order to increase the efficiency of the analog dc power circuit (5 V), two unregulated dc

voltages (8.2 V and 6 V) are provided. The 6 V dc supply is connected to the sensing circuit;

if ever it falls below a threshold of 5.5 V, the 8.2 V dc is connected instead and remains

connected until the 6 V dc returns to a value higher than 5.5 V.

8.2 V

uMo. DC

m!,!: DC

5VDC

ov

1

I

I

I

I

I

I

!

I

- 5.5 v 7HRLSHOLD

Figure 1-6. Voltage Sensing and Regulation

The unregulated 8.2 V dc is applied to transistor Q4 and the unregulated 6 V dc to transistor

Q5. The unregulated 6 V is divided by R15/R16 and applied to sensing amplifier U6A. The

-4 V ref is applied to 1:l amplifier U6B, which alters the polarity of the signal to give a

constant +4 V at the base of transistor Q7.

If the unregulated 6 V is higher than the 5.5 V threshold, CR12 conducts, setting the output

of U6A to 3.4 V. Since the base potential of QS is now lower than that of Q7, Q7 is rendered

conductive. This causes driver transistor Q5 to conduct, letting the +6 V pass to provide the

+5 V. If the unregulated 6V is lower than the 5.5 V threshold, CR12 is reverse-biased and

CR11 conducts. the output of U6A is now at 4.6V which means that the base potential of QS

is higher than that of Q7. QS and Q4 are rendered conductive, letting the unregulated 8.2 V

pass.

U6D is the current-sensing circuit and U6C the voltage sensing circuit for the f5 V supply.

Qll is the switch for the battery mode. The -4 V ref is generated by U3 and associated

components. It is used as the reference power source for the +5 V and the i-40 V power

supplies.

f12 V DC Supplies

Ul and U2 are linear power regulators with internal current limiting. They provide the +12 V

and -12 V dc supplies, respectively.

+17V DC Supply

U5 is an adjustable power regulator with internal current limiting and overload protection. It

provides the i-17 V dc supply.

1-18 Theory Of Operation

Page 39

Audio Board 78353-665 12

r--- ----------- -----.----- .-----~

I

I

I

L ____ ---------~~----------~.~

ECG WAVE OUTPUT

OEFlERlLLATOR 1

INTERFACE

ClRculT

I

Figure 1-9. Audio Board Block Diagram

The Audio Board receives three signals (QRS, 1

a arm, INOP) from the Display UP Board.

Amplifier U3B creates the QRS tone, whereby appropriate jumpering (Sl on Al Mother

Board) can provide a differentiation between the standard and the Japanese QRS tones.

Divider Ul divides the 62.5 kHz signal to provide two signals (976 Hz and 488 Hz). These are

used in conjunction with the alarm signal and the INOP signal, respectively. Gates U2A, U2B

are used to select the signal to be amplified by U3A. Potentiometers are provided for QRS

volume adjustment (R22) and alarm volume adjustment (R23).

Theory Of Operation 1-19

Page 40

All three signals are applied to audio amplifier U3C where they are amplified and applied

directly to the loudspeaker. The Audio Board also contains the external brightness

potentiometer R24 and houses the input jack (auxiliary inputs 2 and

Defibrillator Interface circuit (78353-66511 only) - the defibrillator interface circuit is located

on the Audio Board. When the defibrillator senses an ECG wave from either the tip or the

ring of the phone jack, it sends back to the tip of the phone jack a marker pulse which is

detected by the Marker Detector Circuit. The marker is indicated as a vertical line on the

trace of the ECG wave.

21).

Note

3

The Audio board 78353-66509 does not include this circuit.

l-20 Theory Of Operation

,

Page 41

Battery Board 78832-66519

Battery Charge Circuit

When the unit is switched on, battery BTl is charged via U3C and U3D. In this situation the

j-5 V supply to the parameter boards is supplied via Q2. The power-on signal at the base of

Ql causes Ql, and hence Q2, to conduct. U3B is switched on and acts as a diode bringing the

base of U3A to +5 V. Hence U3A is reverse-biased and not conducting. So the i-5 V supply is

routed from the input connector via Q2 to the parameter boards.

When the power is switched off, Q2 is also switched off and the battery discharges power via

U3A to the parameter boards.

Alarm Lamp Drive Circuit

The alarm lamp signal and 20 ms SYNC signal are combined at gate UlA. When the alarm

lamp signal is low at the same time that the SYNC signal is low, the flip-flops (U2A, U2B) are

cleared and the lamps are off.

When there is one rising edge on the alarm lamp signal between SYNC pulses, the output of

U2B goes high and lamp Ll is switched on. When there are two rising edges the output of

U2A goes high and lamp L2 is switched on.

Theory Of Operation 1-21

Page 42

ECG Board (Full Lead) 78354-66522(42)and 78354-66722(42)

The ECG Board contains the entire circuit required for ECG signal processing. It consists of

an analog section containing:

1. Floating input circuit

2. Right leg drive

3. INOP detection circuit

4. Lead selector circuit

5. Grounded input circuity with bandpass and notch filters

6. A-D converter

and a digital section containing:

7. Microprocessor

8. ROM

9. RAM

Floating Input Circuit

The ECG input signals (C, LL, LA, RA)

to input amplifiers Ul, U2 which provide a gain of 1. The signals are then routed to lead

selector switch U4, U3. The amplified (U6) ECG ‘g 1

AC voltage is transferred to the grounded section by transformer T2.

are applied, via the overvoltage protection circuits,

sr na is fed to modulator U6. The resulting

Right-Leg Drive

The common-mode error signal that serves as input to the right leg drive circuit is derived

from the signals summed through R16 and R17. This common-mode error signal drives the

right-leg drive amplifier U9A. The output of the right-leg drive amplifier returns to the patient

through the patient cable, serving to prevent 50/60 Hz power line interference. Gates UlOA,

B, C switch this signal to the LL, LA or RA input (Ql, Q2, Q3, respectively) according to

which lead is selected (I, II, III) for the other lead positions, connection via RL is used.

INOP Detection Circuit

If any of the leads are disconnected, right-leg drive amplifier U5A generates an INOP signal

(logic high). This signal

U6. It is transferred to the grounded circuit and once again detected (U15). From latch U21,

it is transferred to the digital ECG circuits.

is p assed to INOP comparator U9B, and then switched to modulator

Lead Selector Circuit

U24 receives lead information from the microprocessor U27 via the data bus. The serial

output from U24 drives the opto-coupler U39 via Q13, to transmit information to the floating

circuit. U8 receives this incoming serial data and transmits parallel output to the lead

switches U4, U3 and to the gates U7 and UlO.

1-22 Theory Of Operation

Page 43

Grounded Input Circuit

Demodulator Ull provides the demodulated ECG signal. From here the signal is routed to

the bandpass filter U12, U14, which functions in conjunction with the FILTER/DIAGnostic

switching capability. When the FILTER (

filtered, giving a bandwidth of 0.5 Hz to 30 Hz.

Pace Pulse Rejection: the demodulated signal is directed to the pace pulse hybrid circuit

which detects pace pulses and transmits this information to UP via Latch U21. This signal is

then transferred to the instrument’s shared memory.

The notch filter removes AC line frequency artifacts and the results of AC line rectification

from the waveform display during electrosurgery. The notch filter is bypassed in the

DIAGnostic mode.

After these two filter stages, the ECG signal is A/D converted via DAC (lo-bit) U16 and

comparator U17 on the basis of successive approximation. In operation, the microprocessor

first guesses a number, then U16 converts this to an analog signal and U17 compares it with

the input voltage. The output of the comparator returns to the microprocessor for further

processing.

monitoring) mode is selected, the ECG signal is

Digital Circuits

The A/D converted ECG information is processed by the microprocessor U27 in the digital