HOLT HI-6010JT, HI-6010J, HI-6010CT, HI-6010CM-01, HI-6010C Datasheet

HI-6010

GENERALDESCRIPTION

TheHI-6010isaCMOSintegratedcircuitdesignedto

interfacetheavionicsdatabusstandardARINC429toan

8bitport.Itcontainsonereceiverandonetransmitter.

Theyoperateindependentlyexceptfortheselftestoption

andtheparityoption.Thereceiverdemandsthatthe

incomingdatameetthestandardprotocolandthe

transmitteroutputsastandardprotocolstream.

TheHI-6010providesflexibleoptionsforinterfacingtothe

usersystem.Thecontrollingprocessorcanoperateboth

thereceiverandtransmittereitherbyusinghardwired

flagsandgatesatthepinsorbyusingsoftwa rereadsand

writesoftheStatusRegisterandControlRegisterora

combinationthereof.

Thechipisprogrammabletooperatewithsingle8bit

bytesrequiring"ontheflytransmitterloadingandreceiver

downloading"ortooperatein32bit"extendedbuffer"

mode.Inadditionthereisanoptiontouseautomaticlabel

recognitionafterloading8possiblelabelsforcomparison.

Parityandselftestarealsosoftwareprogrammable.

MasterResetisactivatedonlybytakingtheMRpinhigh.

Twoclockinputsallowindependentselectionofthedata

ratesofthetransmitterandreceiver.Eachmustb e4Xthe

desiredARINC429frequency.

Errorflagsaregeneratedfortransmitterunderwritesand

forreceiverdataframingmiscues,parityerrors,andbuffer

overwrites.

TheHI-6010isa5voltchipthatwillrequiredatatranslationfromandtotheARINCbus.TheHI-8482andHI-8588

linereceiversareavailableforthereceiversideandthe

HI-318X,HI-838XandHI-858Xlinedriversareavailable

forthetransmitterside.TheHI-8590isalsoavailablewith

alinedriverandalinereceiverinasingle16-pinthermally

enhancedESOICpackage.

FEATURES

!

ARINC429protocolcontrollerwithinterfaceto

an8bitbus

!

Automaticlabelrecognitionoption

!

8bitor32bitbufferingoption

!

Selftestandparityoptions

!

CMOS/TTLlogicpins

!

Plasticandceramicpackageoptions-surface

mountorDIP

!

Militaryprocessingavailable

PINCONFIGURATION (TopView)

28

V1

SS

WEF2

3

CTS

TXC4

HFS5

MR6

TXE7

RXRDY8

TXRDY9

TXD010

TXD111

RXC12

FCR13

RXD014

PinnumbersapplyforplasticandceramicDIPand

forplasticPLCC.Consultfactoryforpinoutof48

leadceramicleadlesschipcarrier.

RE

27C/

D

26

CS

25

WE

24D7

23D6

22D5

21D4

20D3

19D2

18D1

17D0

16RXD1

15V

DD

!

AvionicsDataCommunication

!

SerialtoParallelConversion

!

ParalleltoSerialConversion

HOLTINTEGRATEDCIRCUITS

(DS6010Rev.A)01/014-3

!

VDD=5.0VOLTS±5%

!

VSS=0.0VOLTS

HI-6010

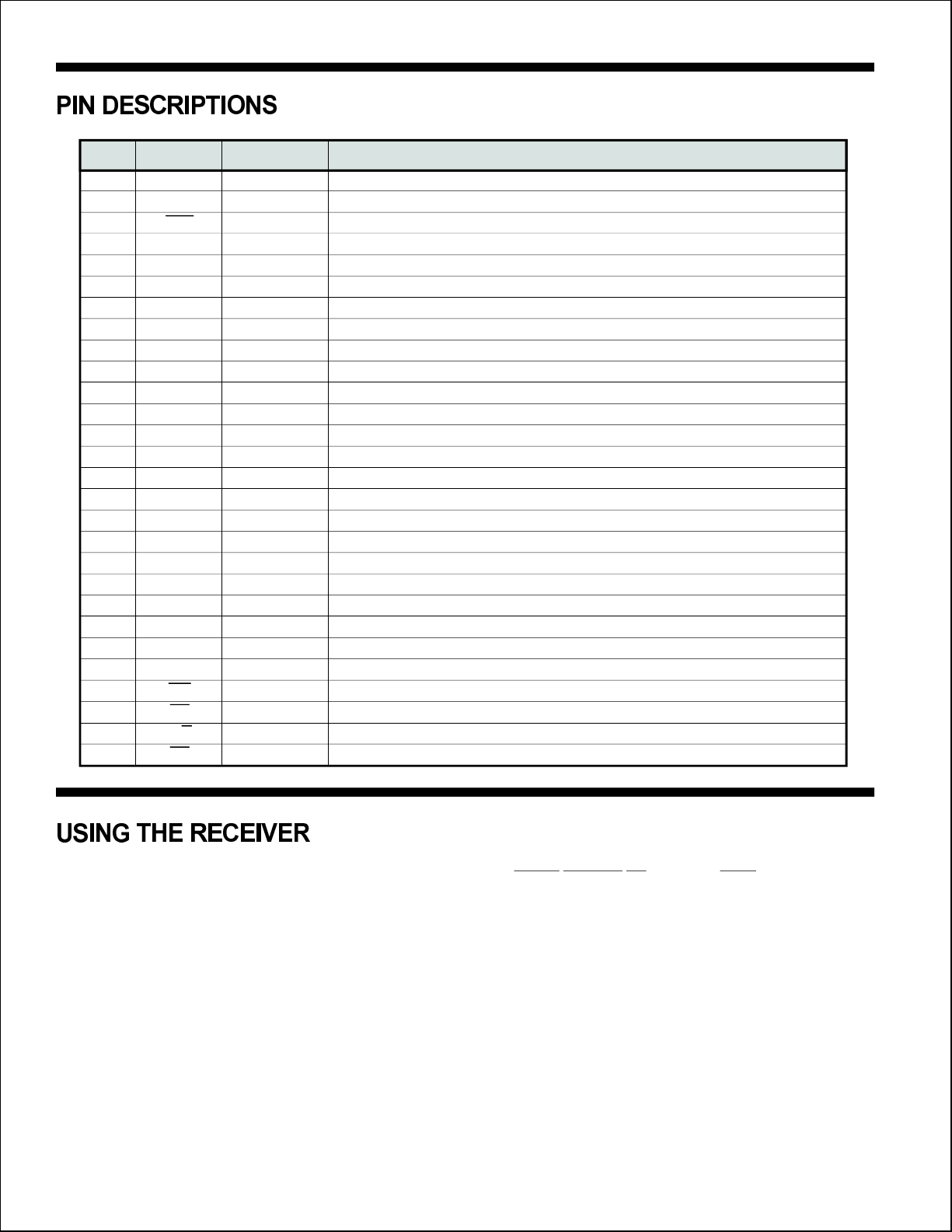

PINSYMBOLFUNCTIONDESCRIPTION

1VPOWER0.0Volts

2WEFOUTPUTErrorindicationifhigh.Statusregistermustbereadtodeterminespecificerror.

3INPUTEnablesdatatransmissionwhenlow.

4TXCINPUTSourceclockfordatatransmission.4timesbitrate.

5HFSINPUTHardwarefeatureselect.

6MRINPUTMasterreset,activehigh.

7TXEOUTPUTLowwhentransmissioninprogress.

8RXRDYOUTPUTHighwhendataofreceivedwordisavailable.

9TXRDYOUTPUTHighwhendataofatransmittedwordmaybeinput.

10TXD0OUTPUT"Zeroes"dataoutputoftransmitter.

11TXD1OUTPUT"Ones"dataoutputoftransmitter.

12RXCINPUTSourceclockf ordatareception.4timesbitrate.

13FCROUTPUTFirstcharacterreceivedflag.

14RXD0INPUT"Zeroes"datainputtoreceiver.

15VPOWER5Volts±5%

16RXD1INPUT"Ones"datainputtoreceiver.

17D0I/ODatabus

18D1I/ODatabus

19D2I/ODatabus

20D3I/ODatabus

21D4I/ODatabus

22D5I/ODatabus

23D6I/ODatabus

24D7I/ODatabus

25INPUT8bitdatabusinputcontrolactivelow.

26INPUTChipselect,activelow.

27C/INPUTHighforcontrolorstatusregisteroperations,lowfordata

28INPUT8bitdatabusoutputcontrol,activelow.

SS

CTS

DD

WE

CS

D

RE

Thereceiverlogicisindependentofthetransmitterexceptin

thefollowingways:

1.SelfTest

2.ParityOption

Inselftest,thetransmitteroutputsroutetothereceiverinputs

internallyignoringtheexternalinputs.Alsoinselftest,the

externalreceiverclockisreplacedwiththetransmitterclock.

Theparityoptionaffectsboththereceiverandtransmitter.

Eitherbothareoperationalorneither.

HARDWARECONTROLOFTHERECEIVER

PIN2-WEF

WEFisanerrorindicator.Itgoeshighforatransmitter

"underwrite"(failuretokeepupwithbyteloading)andpin2

HOLTINTEGRATEDCIRCUITS

goeshighforanyoneofthreereceivererrors.Thestatus

registerwillshowwhichofthethreeerrorsoccurred:

StatusRegisterBitError

SR3Receivedaparityerror

SR4DataOverwritten

SR5Receivingsequenceerror

ThepossibleReceiversequenceerrorsare:

1.RXD0andRXD1simultaneouslyaone.

2.Lessthan32bitsbefore3nulls.

3.Morethan32bits.

Therearenoerrorsflaggedforlabelsreceivedthatdon't

matchstoredlabelswheninthelabelrecognitionmode.

ErrorsareclearedbyMRorbyreadingtheStatusRegister.

PIN5-HFSandtheCONTROLREGISTER

Thispin,alongwiththecontrolregister,setsupthe

functioning(e.g.modes)ofthechip.IfH FSislow,the

4-4

HI-6010

PIN14-RXD0andPIN16-RXD1

receiverisnotprogrammabletothe32bit"extendedbuffer"

modenortothelabelrecognitionmode.Affectingthe

receiver:

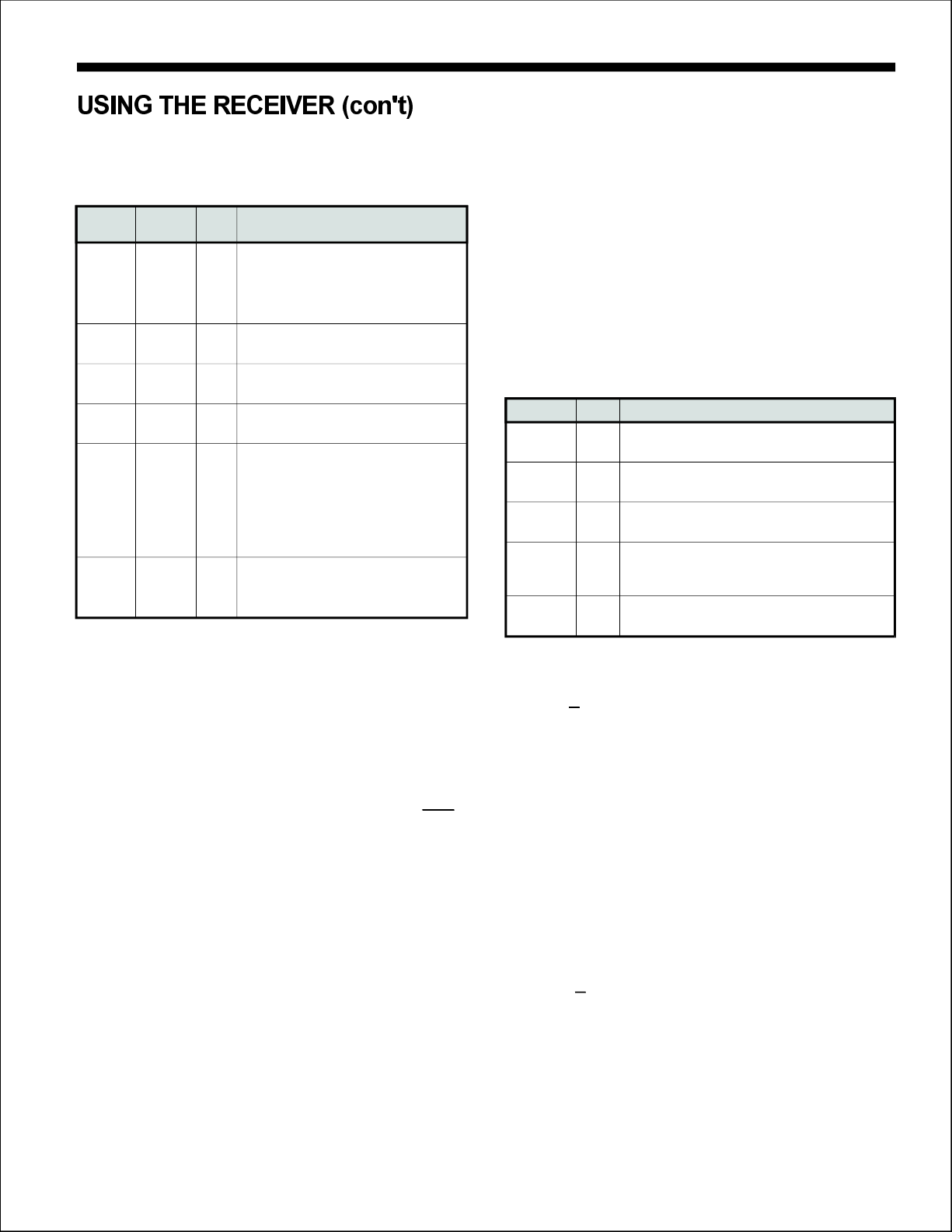

CONTROLPROGRAMPIN5

BITNAMEVALUEVALUE OPERATION

CR1X0Noaction

01Noaction

11Next8datareadcycleswillread

storedlabels.Onetimeonlysequence

oneachtransitonofCR1toa1.

CR20XReceiverisdisabled

1XReceiverisenabled

CR3*0XRXRDYgoeshighnormally

1XBlocksRXRDYforoneARINCword

CR40XSelftestdisabled

1XSelftestenabled

CR500Noparityerrorsenabledand32nd

bitisdata

10Parityerrorflagenabled

0132bit"extendedmode"enabledand

parityenabled.

118bit"onebyteatatime"modeand

parityenabled.

CR7X0Labelrecognitionnotprogrammable

01Labelrecognitiondisabled

11Labelrecognitionenabled

*CR3willbeautomaticallyresetto0afterbeingprogrammed

toa1atthecompletionofanARINCwordreception.This

allowsasoftwarelabelrecognitiondifferentfromtheautomatic

optionavailable.

Thesepinsmustbe5voltlogiclevels.Theremustbea

translatorbetweentheARINCbusandtheseinputs.

Typicallyareceiverchip,suchastheHI-8482orHI-8588

isinsertedbetweentheARINCbusandthelogicchips.

RXD0islookingforahighlevelforzeroinputsandRXD1is

lookingforahighlevelforoneinputs.Whenbothinputsare

lowthisisreferredtoastheNullstate.

SOFTWARECONTROLOFTHERECEIVER

BywritingtotheControlRegisterandreadingtheStatus

Registerthecontrollingprocessorcanoperatethereceiver

withouthardwareinterrupts.TheControlRegisterin

combinationwiththewiringofpin5wasexplained above.

TheStatusRegisterbitspertainingtothereceiverare

explainedbelow:

STATUSBITVALUEMEANING

SR10Noreceiverdata

1Receiverdataready

SR30Noparityerror

1Parityerror-Paritywaseven

SR40Receiverdatanotoverwritten

1Receiverdatawasoverwritten

SR50Receiverdatareceivedwithoutframingerror

1Framingerror-Didnotreceiveexactly32

goodbits

SR60Didnotreceivefirstbyte

1Receivedfirstbyte-Sameflagaspin13

COMMUNICATINGWITHTHECONTROLAND

STATUSREGISTERS

PIN6-MR

WhenMRisa1,thecontrolwordissetto0X100101(CR7CR0).Forthereceiverthissetsup8bitmodewiththe

receiverandparityenabled.MRalsoinitializestheregisters

andlogic.ThefirstARINCreceptionwillonlyoccura

after

wordgap.

PIN8-RXRDY

In8bitmode,thispingoeshighwhenever8bitsarereceived

withouterror.In32bitmodethispingoeshighafterall32bits

arereceivedwithnoerror.Thisflagmaybeinhibitedforone

ARINCwordifCR3isprogrammedto1.Thisflagisalso

inhibitedinlabelrecognitioniftheincomingARINClabeldoes

notmatchoneofthestored8labels.

PIN12-RXC

Thispinmusthaveaclocka ppliedthatis4Xthedesired

receivefrequency.

PIN13-FCR

In8bitmode,thispinflagsthefirstcharacter(byte)received.

In32bitmode,thispingoeshighforavalid32bitword.The

pinisnotaffectedbyCR3programming.

Pin27,C/,mustbehightoreadthestatusregisterorwrite

D

thecontrolregister.Readingthestatusregisterresets

errors.Thereisnoprovisiontoreadthecontrolregister.

LABELRECOGNITIONOPTION

Pin5mustbehighiflabelrecognitionisselectedineitherthe

8or32bitmodesandalleightlabelbuffersmustbewritten

usingredundantlabels,ifnecessary.

Thechipcomparestheincominglabeltothestoredlabels.If

amatchisfound,thedataisprocessed.Ifamatchisnot

found,noindicatorsofreceivingARINCdataarepresented.

LOADINGLABELS

AfterthewritethatchangesCR7from0to1,thenext8writes

ofdata(C/isazerofor data)willloadthelabelregisters.

D

Labelsmustbeloadedwheneverpin5goesfromlowto

high.

READINGLABELS

AfterthewritethatchangesCR1from0to1,thenext8data

readsarelabels.

HOLTINTEGRATEDCIRCUITS

4-5

HI-6010

PIN6-MR

Thetransmitterlogicisindependentofthereceiverexceptin

thefollowingways:

1.SelfTest

2.ParityOption

Inselftestthetransmitteroutputsroutetothereceiverinputs

internallyandtheTXD0andTXD1outputsareinhibited.

Whenparityisenabled,boththereceiverandtransmitterare

affected.Oddparityisautomaticallygeneratedinthe32nd

bitifthisoptionisselected.

HARDWARECONTROLOFTHETRANSMITTER

PIN2-WEF

Thisoutputgoeshighfor1transmittererrorand3receiver

errors.Todeterminewhicherrorisbeingflagged,readthe

StatusRegister.ReadingtheStatusRegisteralsoclearsthe

errorflag.Thetransmitte rwillnotfunctionuntiltheerroris

cleared.ItcanalsobeclearedbyMRgoinghigh.

Theonlypossibletransmittererrorisgeneratedwhenrunning

in8bitmode.Forthetransmitterthismeansloadingthelast3

byteswhilethetransmissionisinprogress.Failuretoloada

bytebeforethepreviousbyte's8thbitistransmittedwill

generatetheerror,indicatedbystatusbitSR7settoa1.

PIN3-

Thispinisahardwaregatefortransmissions.Ifthe

transmitterbufferisloadedandControlRegisterbitCR0isa

one,theonlyinhibitofthetransmitterwouldbefortobea

one.Whentakenlow,transmission ofanARINCwordis

enabled.Itmaybepulsedtoreleaseeachtransmittedword.

PIN4-TXC

Thedatarateoftransmissioniscontrolledbythispin.This

clockmustbe4Xthedesireddaterate.

PIN5-HFSandtheCONTROLREGISTER

CTS

CTS

Thechipisinitializedwheneverthispingoeshigh.The

ControlRegisterissetto0X100101(CR7-CR0).Forthe

transmitterthissetsup8bitmodewiththetransmitter

enabled.

PIN7-TXE

Wheneveratransmissionbegins,thispingoeslowand

returnshighafterthetransmissioniscomplete.

PIN9-TXRDY

WheneverTXRDYisaone,datamaybewrittenintothe

transmitterbuffer.In8bit"onebyteatatime"mode,thispin

maybemonitoredtoindicatewhentowritethenext8bits.

PIN10-TXD0andPIN11-TXD1

TXD0willgohighduringatransmissionifthedataiszero.

TXD1goeshighifdataisaone.Whenbothpinsarelowthis

isreferredtoastheNullstate .TypicallyanARINC

transmitterchip,suchastheHI-8382,HI-8383,HI-8585or

HI-8586isconnectedtothesepinstotranslatethe5volt

levelstotheproperARINCbuslevels.

SOFTWARECONTROLOFTHETRANSMITTER

BywritingintotheControlRegisterandreadingtheStatus

Register,thecontrollingprocessorcanoperatethe

transmitterindependentoftheflagsatthepins.

TransmissioncanbeinitiatedbychangingCR0froma0toa1

afterthetransmitterbufferhasbeenloaded.ThentheStatus

Registermaybemonitoredasfollows:

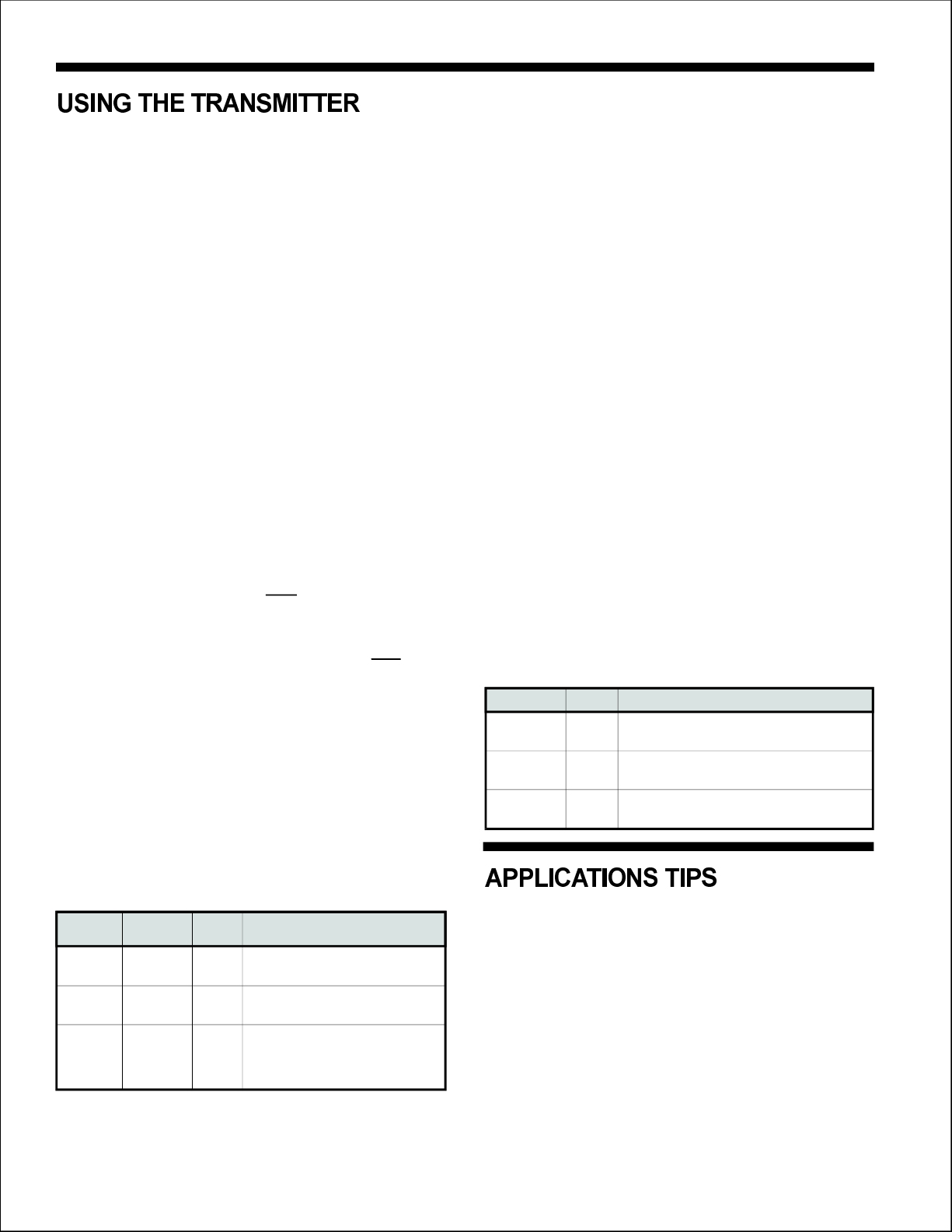

STATUSBITVALUEMEANING

SR00Donotloadthetransmitterbuffer

1Readytoloadthetransmitterbuffer

SR20Transmissioninprogress

1Transmitterisidle

SR70Notransmissionerror

18bitmodeonlyerrorforunderwritingdata

ThispinalongwiththeControlRegistersetsthefunctioningof

thechip.Forthetransmitter:

CONTROLPROGRAMPIN5

BITNAMEVALUEVALUE OPERATION

CR00XTransmitterisdisabled

1XTransmitterisenabled

CR40XNotinselftest

1XSelftestenabled

CR5008bitmode+datain32ndbit

108bitmode+parityenabled

0132bitmodewithparityenabled

118bitmodewithparityenabled

HOLTINTEGRATEDCIRCUITS

CablingNoise

thereforetheyaresusceptibletonoisenearground.Ifthedata

busispassedbyribboncableortheequivalenttothedevice

undertest,itispossibletogetsignificantglitchesontheMaster

Resetline.Theproblemwillappeartobeapatternsensitive

failure.OnecureissimplytoadequatelybypassMasterReset.

AnotheristobuffertheHI-6010inputsnearthechip.

ReceiverSeemsDead

receivermustseeawordgapbeforethefirstARINCdatabit.

ErrorflagsmustbeclearedbyeitheraStatusRegisterReador

byaMasterReset.Theoperati onofeitherthetransmitterorthe

receiverisinhibiteduponerror.

-TheHI-6010hasTTLcompatibleinputsand

-AfterMasterResettheHI-6010

4-6

Loading...

Loading...