HOLT HI-15530CDT, HI-15530CDM, HI-15530CDI, HI-15530PST, HI-15530PSI Datasheet

...

July2001

HI-15530

ManchesterEncoder/Decoder

GENERALDESCRIPTION

TheHI-15530isahighperformanceCMOSintegrated

circuitdesignedtomeettherequirementsofMil-Std-1553

andsimilarManchesterIIencoded,timedivision

multiplexedserialdataprotocols.TheHI-15530contains

bothanEncoderandDecoder,whichoperate

independently.

ThedevicegeneratesMil-Std-1553syncpulses,paritybits

aswellastheManchesterIIencodingofthedatabits.The

decoderrecognizesandidentifiessyncpulses,decodes

databits,andperformsparitychecking.

TheHI-15530supportsthe1Mbit/sdatarateofMil-Std1553overthefulltemperatureandvoltagerange.

Forapplicationsrequiringsmallfootprintsandlowcost,the

HI-15530isavailableina24-pinplasticSOICpackage.

CeramicDIPandLCCpackagesarealsoavailableto

achievethehighestlevelofreliabilityandtoprovidedrop-in

replacementforobsoletepartsfromothermanufacturers.

FEATURES

!

Mil-Std-1553compatible

!

InterfacestoHI-1567Transceiver

!

Smallfootprint24-pinplasticSOICpackage

option

!

Directreplacementfor:

HarrisHD15530

GECPlesseySemiconductorsMAS15530

AeroflexACT15530

!

1.25Mbit/sDataRate

!

ManchesterIIEncodeandDecode

!

SyncidentificationandLock-in

!

Clockrecovery

APPLICATIONS

!

Mil-Std-1553Interfaces

!

ARINC708AInterfaces

!

SmartMunitions

!

Storesmanagement

!

Sensorinterfaces

!

Instrumentation

PINCONFIGURATION (TopView)

VALIDWORD1

ENCODERSHIFTCLK2

TAKEDATA3

SERIALDATAOUT4

DECODERCLK5

BIPOLARZEROIN6

BIPOLARONEIN7

UNIPOLARDATAIN8

DECODERSHIFTCLK9

COMMAND/SYNC10

DATA

DECODERRESET11

GND12

HI-15530PSI

24PinSOICpackage

24VDD

23ENCODERCLK

22SENDCLKIN

21SENDDATA

20SYNCSELECT

19ENCODERENABLE

18SERIALDATAIN

17

BIPOLARONEOUT

16

OUTPUTINHIBIT

15

BIPOLARZEROOUT

146OUT

÷

13MASTERRESET

HOLTINTEGRATEDCIRCUITS

(DS15530Rev.A)07/01

HI-15530

PINDESCRIPTIONS

SIGNALFUNCTIONDESCRIPTION

VALIDWORDOUTPUTAhighoutputsignalsthereceiptofavalidword

ENCODERSHIFTCLOCKOUTPUTShiftsdataintotheencoderonalowtohightransition

TAKEDATAOUTPUTOutputishighduringreceiptofdataafteridentificationofaSync

PulseandtwovalidManchesterdatabits.

SERIALDATAOUTOUTPUTReceivedDataoutputinNRZformat

DECODERCLOCKINPUT12xthedatarate.Clockforthetransitionfinderandsynchronizer,

whichgeneratestheinternalclockfortheremainderofthedecoder

BIPOLARZEROININPUTAhighinputindicatesthe1553busisinitsnegativestate.

ThispinmustbeheldhighwhentheUnipolarinputisused

BIPOLARONEININPUTAhighinputindicatesthe1553busisinthepositivestate.

ThispinmustbeheldlowwhentheUnipolarinputisused

UNIPOLARDATAININPUTInputforunipolardatatothetransitionfinder.Mustbeheldlowwhen

notinuse

DECODERSHIFTCLOCKOUTPUTProvidestheDECODERCLOCKdividedby12,synchronizedbythe

recoveredserialdata

COMMAND/SYNCOUTPUTAhighonthispinoccursduringtheoutputofdecodeddatawhich

DECODERRESETINPUTAhighappliedtothispinduringaDECODERSHIFTCLOCKrising

GNDPOWER0Vsupply

MASTERRESETINPUTAhighonthispinclears2:1countersinbothEncoderandDecoder,

6OUTOUTPUTProvidesENCODERCLOCKdividedby6

÷

BIPOLARZEROOUT

OUTPUTINHIBITBIPOLARZEROOUTBIPOLARONEOUT

BIPOLARONEOUT

SERIALDATAININPUTReceiverserialdataattherateoftheENCODERSHIFTCLOCK

ENCODERENABLEINPUTAhighonthispininitiatestheencodecycle.(Subjecttothe

SYNCSELECTINPUTActuatesaCommandSyncforaninputhighandaDataSyncfora

SENDDATAOUTPUTAnactivehighoutputwhichenablestheexternalsourceofserial

SENDCLOCKININPUTClockinputat2timestheDatarate,usualydrivenby6OUT

ENCODERCLOCKINPUTInputtothedivideby6circuit.NormalfrequencyisDataratex12

VDDPOWER5V+/-10%

DATA

wasprecededbyaCommand(orStatus)synchronizingcharacter.A

lowoutputindicatesaDatasynchronizingcharacter

edgeresetsthebitcounter

andresetsthedivide-by-6circuit

OUTPUTAnactivelowoutputintendedtodrivethezeroornegativesenseofa

MIL-STD-1553LineDriver

INPUTAlowinhibitstheandby

forcingthemtoinactivehighstates

OUTPUTAnactivelowoutputintendedtodrivetheoneorpositivesenseona

MIL-STD-1553LineDriver

preceedingcyclebeingcomplete)

low

Data

÷

HOLTINTEGRATEDCIRCUITS

2

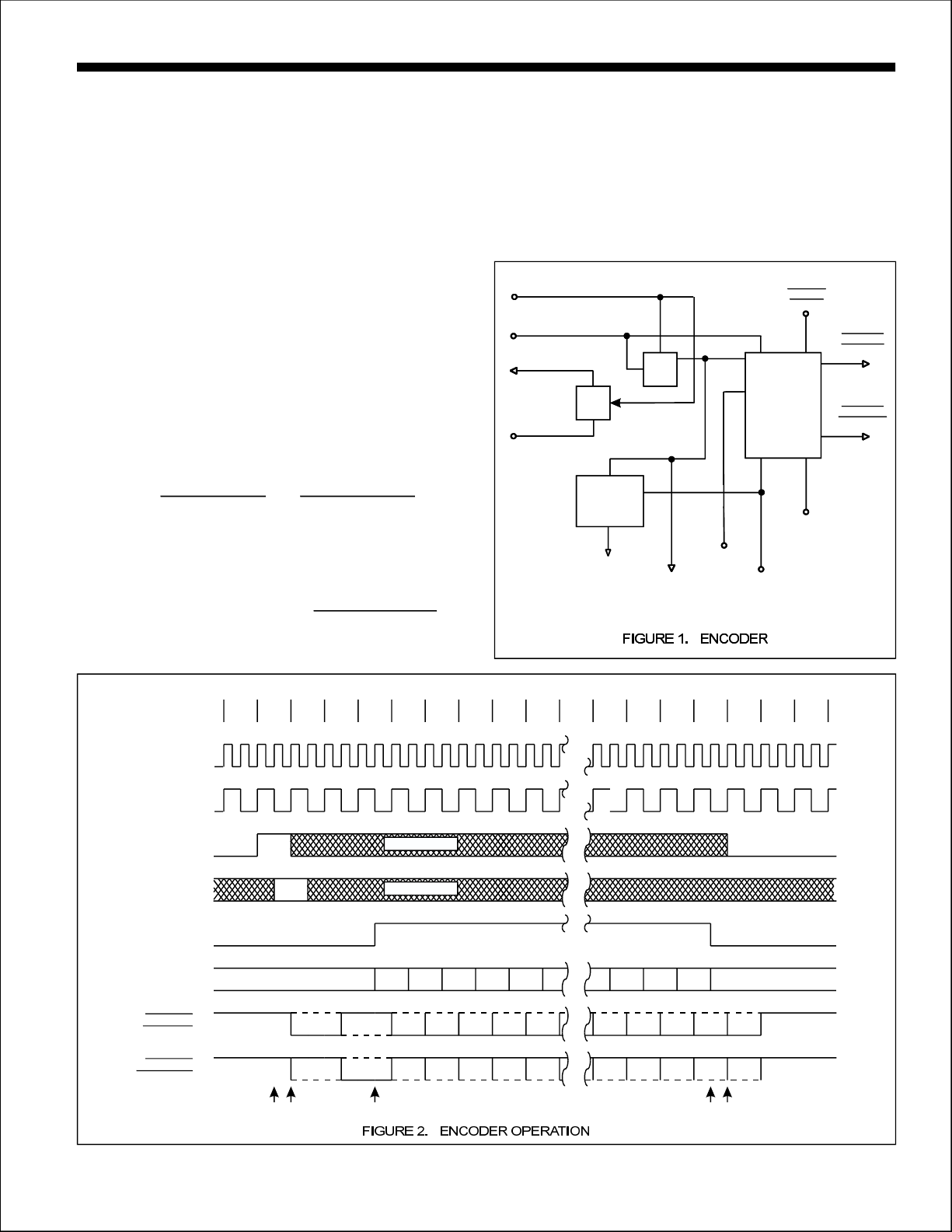

ENCODEROPERATION

HI-15530

Theencoderrequiresasingleclockwithafrequencyof

twicethedesiredrateappliedattheSENDCLOCKinput.

Anauxiliarydividebysixcounterisprovidedonchipwhich

canbeutilizedtoproducetheSENDCLOCKbydividing

theENCODERCLOCK.

TheEncoder'scyclebeginswhenENCODERENABLEis

highduringafallingedgeofENCODERSHIFTCLOCK(1).

ThiscyclelastsforonewordlengthortwentyENCODER

SHIFTCLOCKperiods.Atthenextlow-to-hightransitionof

theENCODERSHIFTCLOCK,ahighatSYNCSELECT

inputactuatesacommandsyncoralowwillproducea

datasyncforthatword(2).WhentheEncoderisreadyto

acceptdata,theSENDDATAoutputwillgohighand

remainhighforsixteenENCODERSHIFTCLOCKperiods

(3).Duringthesesixteenperiodsthedatashouldbe

clockedintotheSERIALDATAinputwitheverylow-to-high

transitionoftheENCODERSHIFTCLOCK(3)-(4).After

thesyncandtheManchesterIIcodeddataaretransmitted

throughtheandoutputs,

BIPOLARONEBIPOLARZERO

theEncoderaddsonanadditionalbitwhichistheparityfor

thatword(5).IfENCODERENABLEisheldhighcontinuously,consecutivewordswillbeencodedwithoutan

interframegap.ENCODERENABLEmustgolowbytime

(5)asshowntopreventaconsecutivewordfrombeing

encoded.Atanytimealowontheinput

OUTPUTINHIBIT

willforcebothbipolaroutputstoahighstatebutwillnot

affecttheEncoderinanyotherway.

ToaborttheEncodertransmissionapositivepulsemustbe

appliedatMASTERRESET.Anytimeafterorduringthis

pulse,alowtohightransitiononSENDCLOCKclearsthe

internalcountersandinitializestheEncoderforanew

word.

MASTERRESET

MASTERRESET

SENDCLKIN

SENDCLKIN

÷ 6OUT

÷ 6OUT

ENCODERCLK

ENCODERCLK

÷6÷2÷6

÷6÷2÷6

Bit

Bit

Counter

Counter

SEND

SEND

DATA

DATA

ENCODER

ENCODER

SHIFT

SHIFT

CLK

CLK

SERIAL

SERIAL

DATA

DATA

IN

IN

ENCODER

ENCODER

Character

Character

Former

Former

ENABLE

ENABLE

OUTPUT

OUTPUT

INHIBIT

INHIBIT

SYNC

SYNC

SELECT

SELECT

BIPOLAR

BIPOLAR

ONEOUT

ONEOUT

BIPOLAR

BIPOLAR

ZEROOUT

ZEROOUT

TIMING

SENDCLK

ENCODER

SHIFTCLK

ENCODER

ENABLE

SYNCSELECT

SENDDATA

SERIAL

DATAIN

BIPOLAR

ONEOUT

BIPLOAR

ZEROOUT

0 1 2 3 4 5 6 7 15 16 17 18 19

DON’TCARE

VALID

SYNC

(1) (2) (3) (4) (5)

DON’TCARE

15 14 13 12 11 3 2 1 010

SYNC

15 14 13 12 11 3 2 1 0 P

3 2 1 0 P15 14 13 12 11SYNC SYNC

HOLTINTEGRATEDCIRCUITS

3

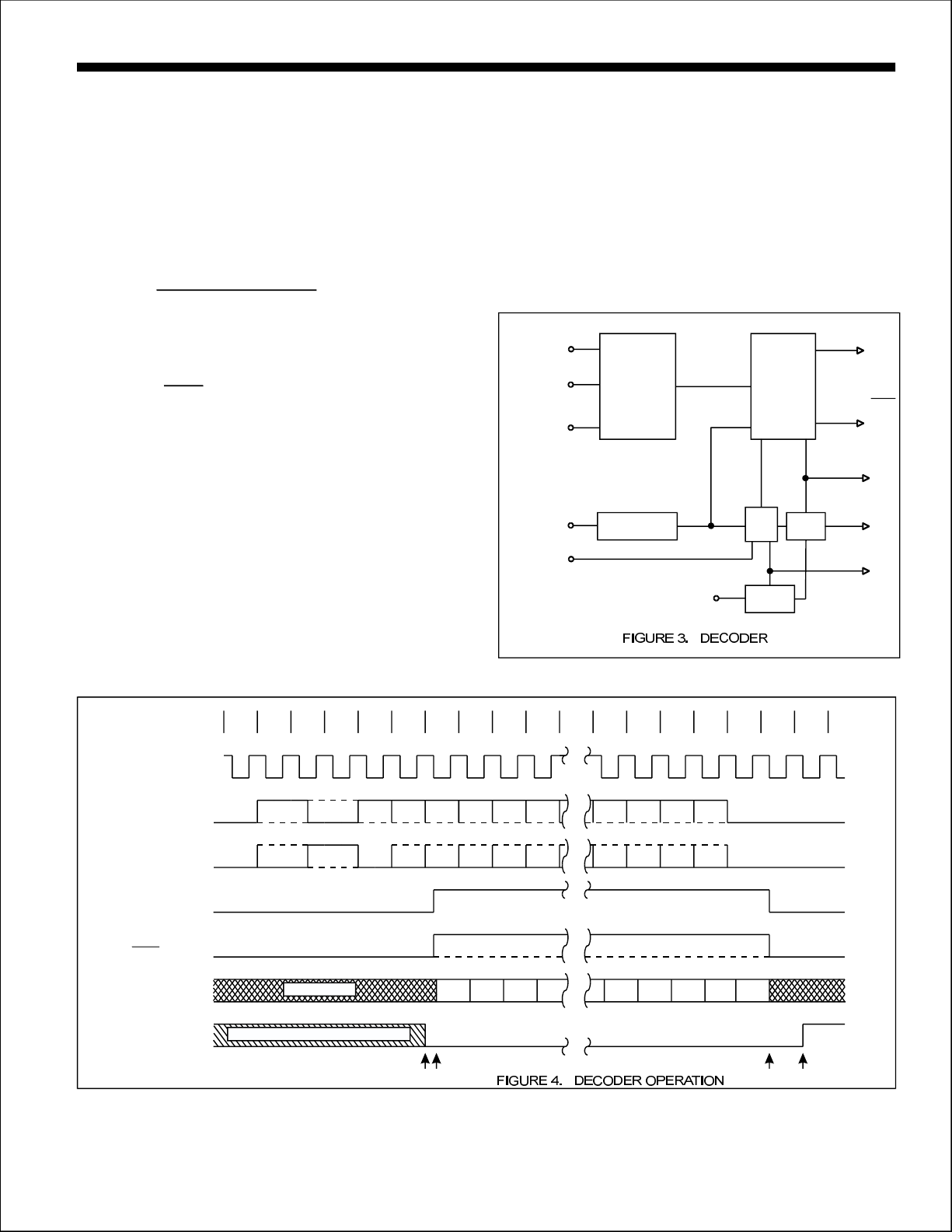

DECODEROPERATION

HI-15530

TheDecoderrequiresasingleclockwithafrequencyof12

timesthedesireddatarateappliedattheDECODER

CLOCKinput.TheManchesterIIcodeddatacanbe

presentedtotheDecoderinoneoftwoways.The

BIPOLARONEandBIPOLARZEROinputswillaccept

datafromacomparatorsensedtransformercoupledbusas

specifiedinMIL-STD-1553.TheUNIPOLARDATAinput

canonlyacceptnon-invertedManchesterIIcodeddata

(e.g.fromofanEncoder).The

BIPOLARZEROOUT

Decoderisfreerunningandcontinuouslymonitorsitsdata

inputlinesforavalidsynccharacterandtwovalid

Manchesterdatabitstostartanoutputcycle.Whenavalid

syncisrecognized(1),thetypeofsyncisindicatedon

COMMAND/SYNCoutput.Ifthesynccharacterwas

DATA

acommandsync,thisoutputwillgohigh(2)andremain

highforsixteenDECODERSHIFTCLOCKperiods(3),

otherwiseitwillremainlow.TheTAKEDATAoutputwillgo

highandremainhigh(2)-(3)whiletheDecoderis

transmittingthedecodeddatathroughSERIALDATAOUT.

ThedecodeddataavailableatSERIALDATAOUTisina

NRZformat.TheDECODERSHIFTCLOCKisprovidedso

thatthedecodedbitscanbeshiftedintoanexternalregister

oneverylow-to-hightransitionofthisclock(2)-(3).Afterall

sixteendecodedbitshavebeentransmitted(3)thedatais

checkedforoddparity.AhighonVALIDWORDoutput(4)

indicatesasuccessfulreceptionofawordwithoutany

Manchesterorparityerrors.AtthistimetheDecoderis

lookingforanewsynccharactertostartanotheroutput

sequence.VALIDWORDwillgolowapproximately20

DECODERSHIFTCLOCKperiodsafteritgoeshighifnot

resetlowsoonerbyavalidsyncandtwovalidManchester

bitsasshown(1).Atanytimeintheabovesequence,a

highinputonDECODERRESETduringalow-to-high

transitionofDECODERSHIFTCLOCKwillabort

transmissionandinitializetheDecodertostartlookingfora

newsynccharacter.

PARITY

CHECK

TAKEDATA

COMMAND/

SYNC

SERIALDATA

OUT

VALID

WORD

DECODER

SHIFTCLK

DATA

UNIPOLAR

DATAIN

BIPOLAR

ONEIN

BIPOLAR

ZEROIN

DECODER

CLK

MASTER

RESET

TRANSITION

FINDER

SYNCHRONIZER

DECODER

RESET

CHARACTER

IDENTIFIER

BIT

RATE

CLK

BIT

COUNTER

TIMING

DECODER

SHIFTCLK

BIPOLAR

ONEIN

BIPLOAR

ZEROIN

TAKEDATA

COMMAND/

SYNCDATA

SERIAL

DATAOUT

VALIDWORD

0 1 2 3 4 5 6 7 16 17 18 19

SYNC

Maybehighfrompreviousreception

SYNC

UNDEFINED

15 14 13 12 11 2 1 0 P

15 14 13 12 3 2 1 0

(1)(2) (3) (4)

8

10

10

2 1 0 P15 14 13 12 11SYNC SYNC

4

HOLTINTEGRATEDCIRCUITS

4

Loading...

Loading...