Page 1

HITACHI PERSONAL

COMPUTER

MB’6890 SERVICE

MANUAL

I

R

0.3012

98

Page 2

HITACHI

PERSONAL

COMPUTER

MB-6890

SERVICE

MANUAL

ev.

O,

30.1.2.1

Page 3

Index

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

a

0

a

o

0

Q

U

0

Q

u

o

0

0

0

0

»

9

General

.

2

Features

.

2

Specification

........

1

,

2

The

name

of

each

block

..

.

6

Function

of

I.C’s

used

........

»

»

3

10

Explanation

of

the circuit

..

..

Memory

map

..Q

....¢iii@;i==

..

31

Adjustment

.....

...

82

Service

points

.................

..

85

The

usage

of inbuilt

switches

..

...

87

Trouble

shootings

............

...

91

Operation

check

method

...

...102

Basic circuit

diagram

Basic

P.C.B.

layout

Waveform

of

each

block

Parts list

1

Page 4

(

Y 4

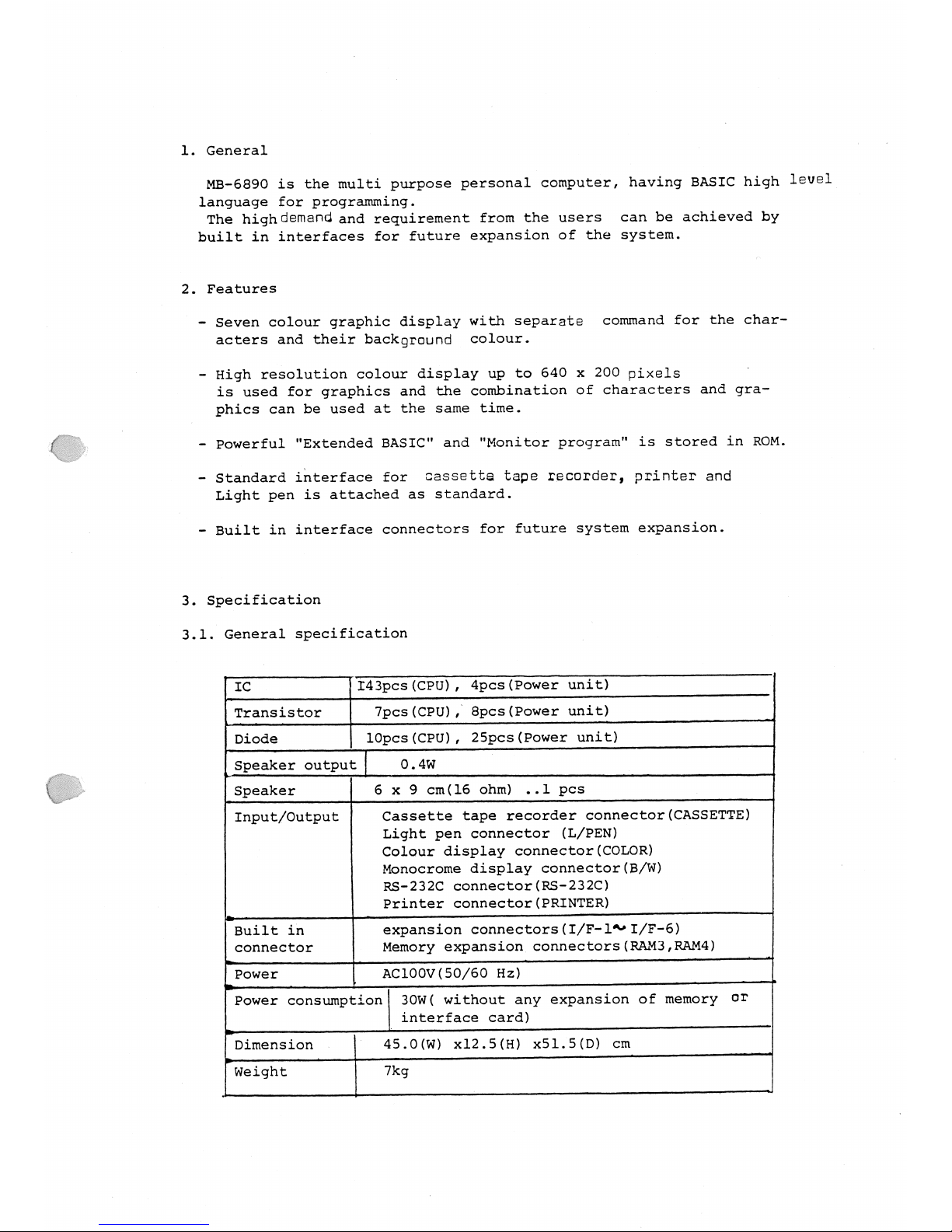

l. General

MB-6890

is the multi

purpose

personal

computer,

having

BASIC

high

language

for

programming.

The

h i g h d ‹ m ‹ H d

and

requirement

from

the users

can

be

achieved

by

built

in interfaces

for future

expansion

of the

system.

2.

Features

-

Seven

colour

graphic

display

with

separate

command

for

the

char

acters

and their

background

colour.

-

High

resolution

colour

display

up

to

640 x

200

pixels

is

used

for

graphics

and

the combination

of characters

and

gra-

phics

can

be

used

at the same

time.

-

Powerful

"Extended

BASIC"

and

"Monitor

program"

is stored

in ROM.

-

Standard

interface

for

cassette

tape

recorder, printer

and

Light

pen

is attached

as

standard.

-

Built

in

interface connectors

for

future

system

expansion.

3.

Specification

3.1.

General

specification

iIC

Wl43pcs(CPU),

4pcs(Power

unit)

Transistor

7pcs(CPU)[

8pcs(Power

unit)

p

Diode

lOpcs(CPU),

25pcs(Power

unit)

Speaker

output

O.4W

_Speaker

6 x 9

cm(l6

ohm)

_.l

pcs

I

Input/Output

Cassette

tape

recorder

connector(CASSETTE)

Light

pen

connector

(L/PEN)

Colour

display

connector(COLOR)

Monocrome

display

connector(B/W)

RS-232C

connector(RS-232C)

Printer

connector(PRINTER)

*

C

Built

in

expansion

connectors(I/F-l**I/F-6)

connector

Memory

expansion

connectors(RAM3,RAM4)

__

,

A

Power

AClOOV(5O/60

Hz)

.g

g_

.

C

,

r

Power

consumption

3OW(

without

any

expansion

of

memory

OT

interface

card)

_

_

Dimension

45.0(W)

x12.5(H)

x5l.5(D)

cm

W e i g h t

A

7kg

level

Page 5

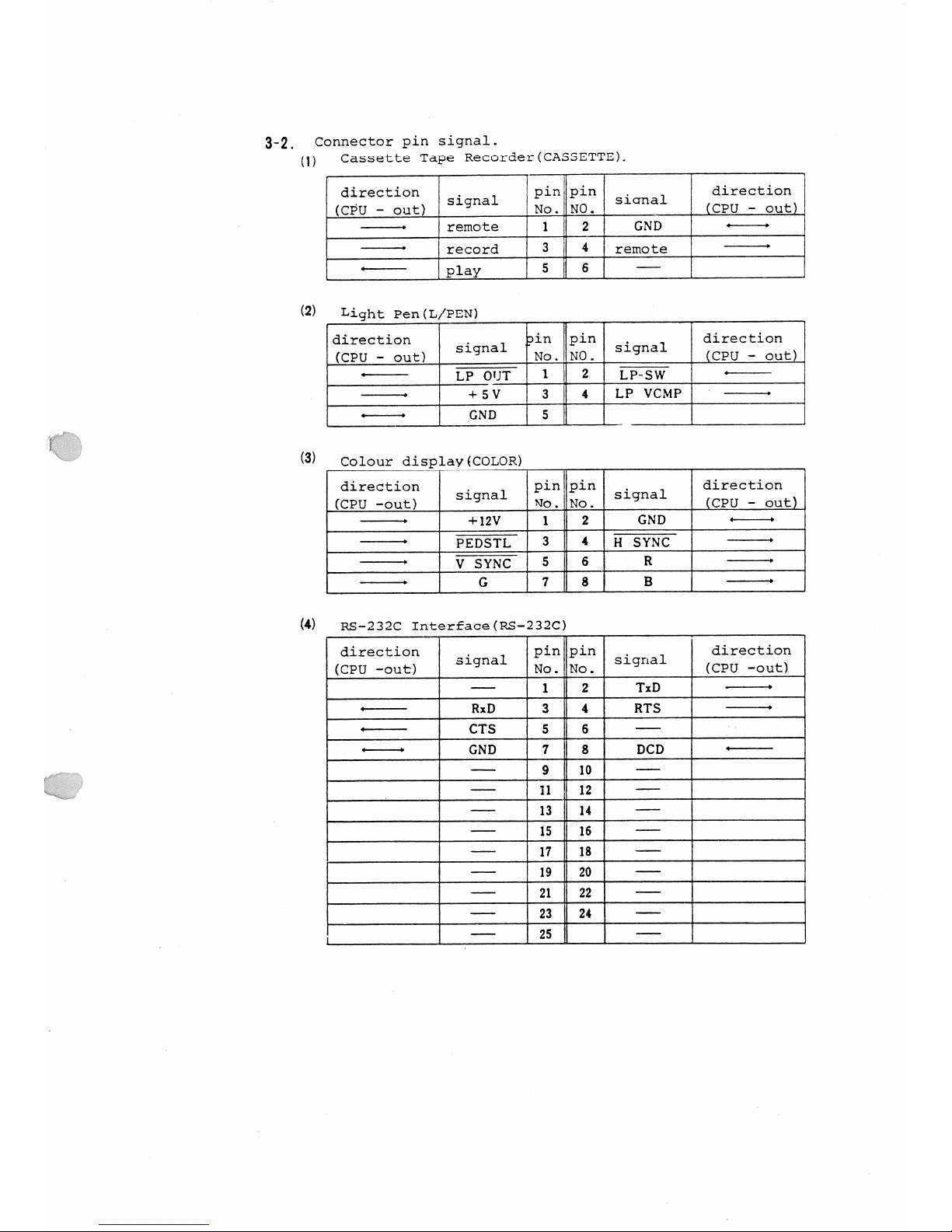

3-2_

Connector

pin

signal.

(1)

Cassette

Tape

Recorder(CASSETTEL

’W

|

direction

Signal

pin

pin

Signal

direction

(CPU

-

out)

No. NO.

(CPU

-

out

--~

remote

1

2

GUD

+--~

* - - *

record

3

4

l

remote

* - ’ *

1

* - ‘

|Play

5

6

1

_

(2)

Light

Penn./PEN)

direction

Signal

pin

pin

Signal

direction

(CPU

-

Out)

NO. NO.

(CPU

-

Out)

---

7675?

1

2

f137§vV

_ -

------

+5V

3

4

LP VCMP

‘

----

--1*

GND

5

(3)

Colour

displav(COLOR)

direction

.

pin pin

.

direction

(CPU

-out)

Slgnal

No.

No.

Signal

(CPU

-

out)

---»

+I2V

1

2

GND

#-~~»

--

T>‘§‘13§TT

3

4

QW

--

--

T565

5

’

6 R

---»

--

G

1 s B

--»

(4)

Rs-232C

Int

rfacems-232c)

direction _

pin pin

.

direction

(CPU

-out)

Signal

No. No.

Signal

(CPU

-out),

‘

*-

1

2

TxD

---*

*---

RxD 3 4 RTS

--~*

---

CTS s

e

-

i

r--

GND

7 8 DCD

- -

-

9 10

--

;

n 4 | 1

-

11

g

12

-

-~

13 14

--

’-

15 16

--

--

17

18

--

--

19 20

--

--

21 22

--

--

23 24

--

}

--

25

-

Page 6

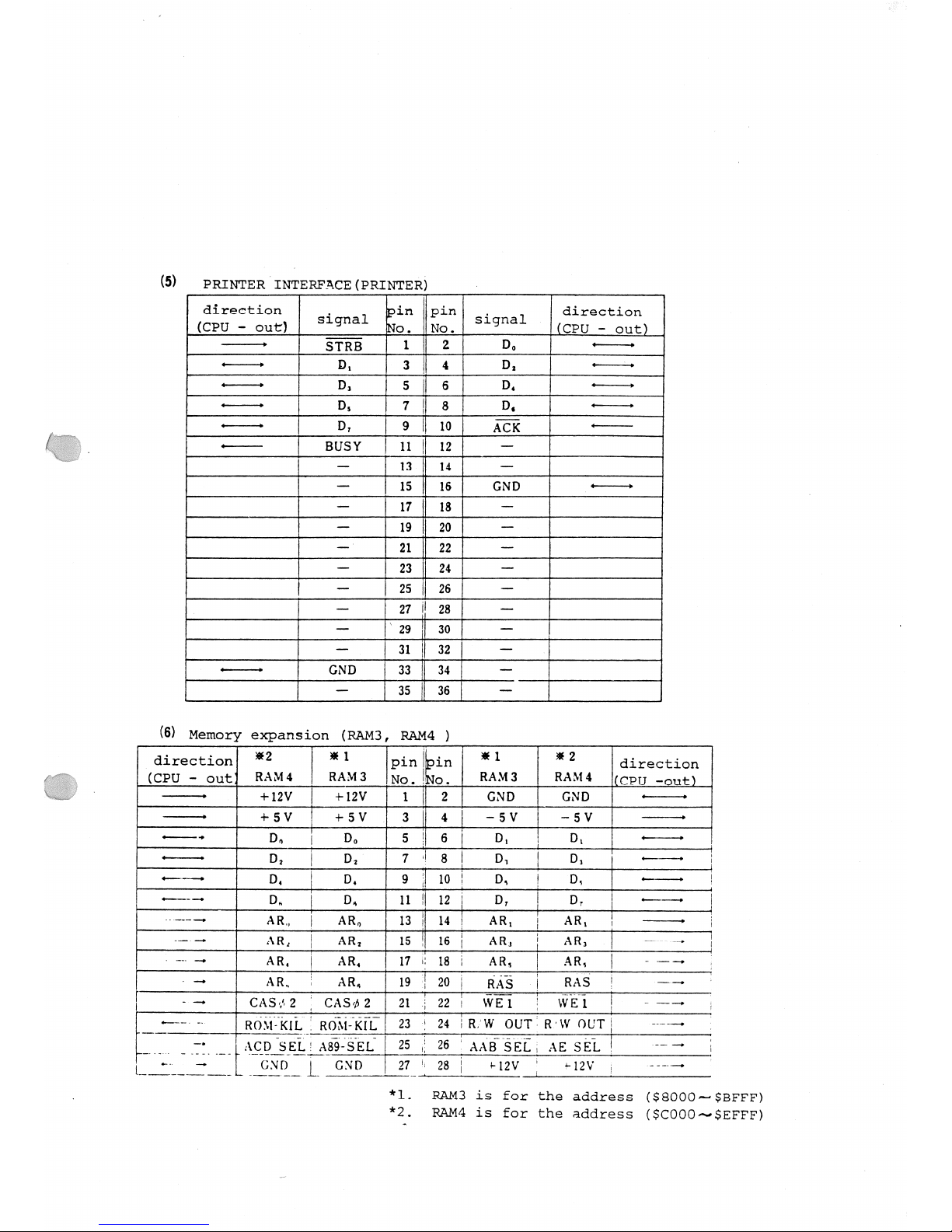

(5)

PRINTER

INTERFACE(PRINTER)

directien

.

min

Qpin

_

1

direction

V

(CPU-out)

S3151

filo.

No.

Signal

(CPU

-

out) 1

--~

STRB

1 2

D,,

-_-

--»

D,

3

_

4

D,

~_-~

---»

D,

Q

5

’_

5

D.

-_»

--~

D,

_

7

Q

s

D.

--»

--

D,

_

9

’

10

A i ; T <

--

---

BUSY

_

11

Q

12

-

Q

Q

-

,

13

Q

L4

,

-

I

I

-

_

15 15

GND

--»

-

17

0

18

-

Q

-

19 20

1

-

-

21 22

1

-

-

23 24

-

-

25

26

-

-

27

QI

28

-

-

\29

Q)

30

-

-

31Q32

-

»-_-

GND 33Q34

_

-

-

0

asQas

-

(5)

Memory expansion (RAM3,

RAM4

)

direction

*Z

*1

p i 1 1 Q

in

*I *Z

directicn

(CPU

_

QU_tI_

RAM4 RAM3

NO_

Q

O_

_

RAM3 RA114

_(CPU wut,

----»

+12v

Q

+12v 1

QQ

2

GND

Q

GND

»---

-_»

+sv

Q

+sv 3

‘

4‘

-sv

Q

-sv

---

--»

D0

Q

D0

5

Q

e

’

D,

DQ

Q

--

---

D,

Q

D,

7

3

Q

D1

D,

Q

---

--~

D.

Q

D.

9

10

Q

D, D,

--

---~»

D.

D.

11QQ12

Q

D,

D,

Q

---

»-----

A R

Q

ARD

13Q14

Q

AR, AR,

--

---»

AR,

Q

AR,

Q

15

16

Q

AR, AR,

--

--~

-

AR.

Q

AR.

_

I7

LE

18 1

AR,

AR,

_

»

--

V

-»

AR,

3

AR,

19’Q20

Q

mis

RAS

~-»

-

-»

CASQHZ

§

CAS’/52

21

22

Q

1?/E1 WEE

Q

2-

--»

*_-~~

-»

ROSFKIL

f R 0 1 1 - ‘ 1 ‹ i ’ E

23z24

QRuw

0UT§

ww

DUTQ

-s--~»

_

--

___

1 1 g D s E 1 ; e

A 8 5 - A S E I _ . _

25

.f

26

FA,11§"sE1I;

AE SEL

Q

’---

_i;N11;*Q_‘GND

0

2 7 Q _ _

28

Q

»12v

Q

»12v

~--~-»

*l,

£143 is

for

the

address

(58000

*2.

RAM4 is

for the

address

(SCOOO

SEFFF)

Page 7

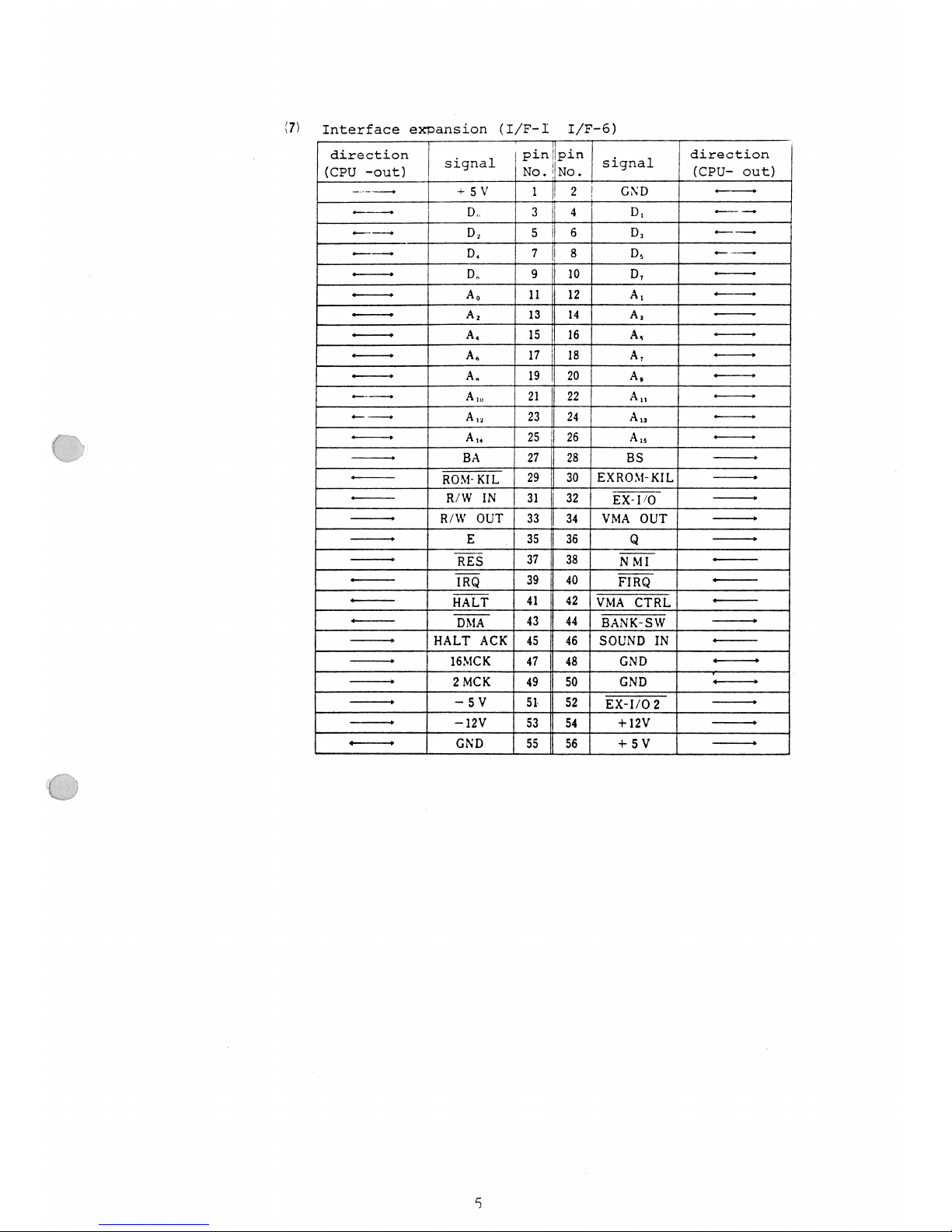

75

Ihterface

expansion

(I/F-I I/F-6)

i

direction

i

_

ipinppin

,

direction

(CPU

-out)

t

Signal

No.

Signal

(cPU-

out)

-4-_~

+5v

1

1

2 GND

---

-~-»

i

D..

3

4

D,

---»

--

D,

5

i

5

D,

--»

---»

D.

1

1

s

D5

---

--»

D1

9

’

10

D,

»--»

--~

A,,

11‘12

A,

----

1

---A

A

{

A,

Q

13

Q

14

A,

|

---

~

{

---»

A.

15 16

A.

--»

---

A.,

17

18

A,

--»

4--»

A.

19 20

A.

---

----

A .

21

A

22

A,,

---

---

A.,

23 24

A,,

--»

--»

A,.

25

26

A,,

--»

-_-

BA 27

’

28

BS

-~

---

‘

E555

‘

29"so

EXROM-KIL

--~

---

11/w IN 31‘32

E356

--~

---»

R/w OUT

33A34

VMA

our

--»

--»

1-:

as

as

Q

---»

1

---

‘1§‘§

37 38

FH

----

---

T55

as 40

mi

---

EXE4142WTTEE.---

EXE

41

42

WTTEE.

---

--

ETA’

43 44

§XN‘1FSW

---

--»

HALT ACK 45 46

SOUND

IN

---

---»

‘

ISMCK

47 48

GND

f--»

---

2Mc1< 49

so

GND

1--»

--~

-5V

51- 52

‘}§;‘§‘{ffR)"§"

--->

-1-

-12v

53 54

+12V

---»

----

GND 55 56

+5v

--

5

Page 8

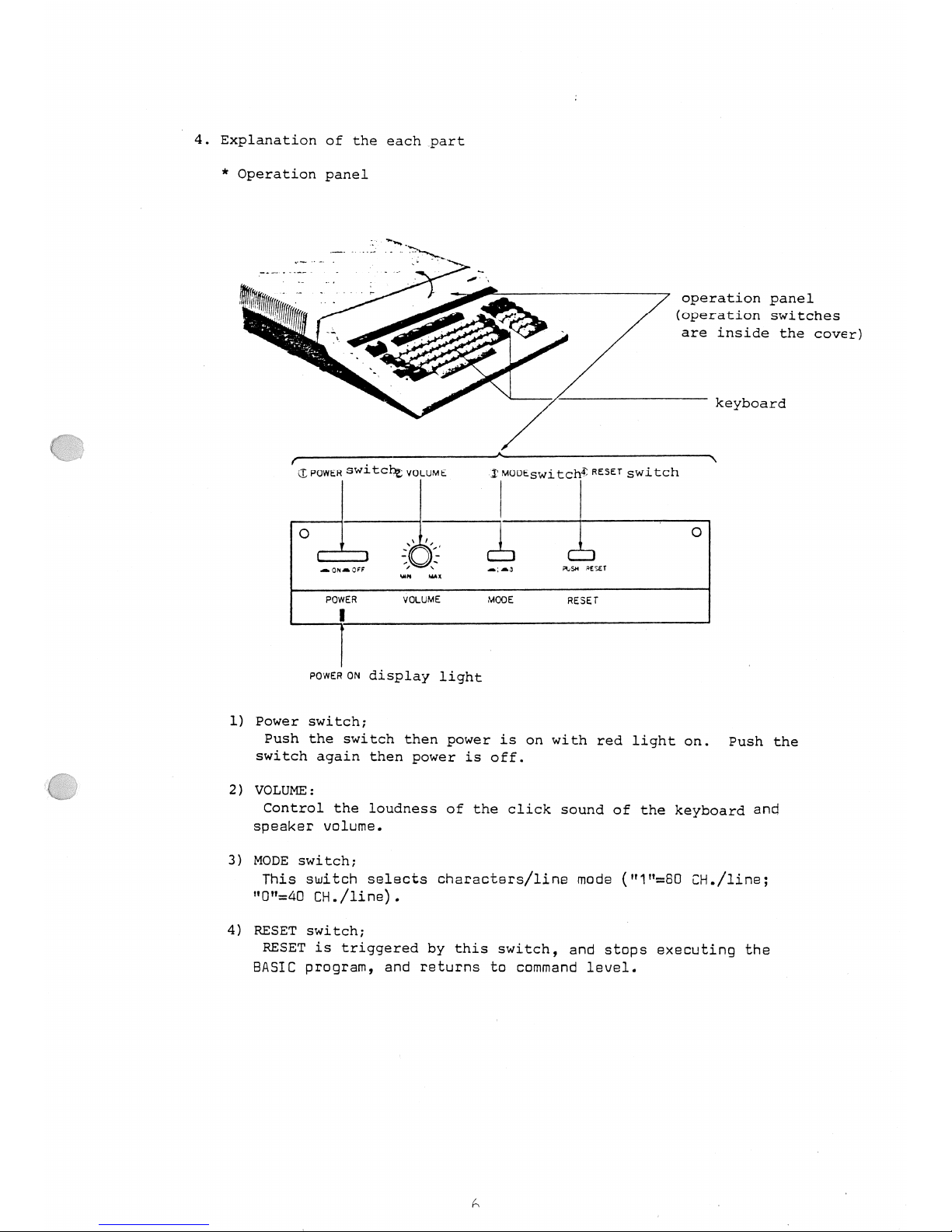

4.

Explanation

of the

each

part

*

Operation

panel

._

~»,‘

_.

.

,..,

:_

_ _

._

~"’"T

M

_

‘ _ -

»-=

’

V"

f_ _’

"

I

*

operation panel

~ W " C 5 G 5 ? ? 7 i W i ~

E

I

/

<@@fafi'H

switches

"fHfi@

~

__

_

~

are inside

the

cover)

.,’i’;i;@;_:_

N

_

-

_

’i

_

V

keyboard

*

\

(Q

eowsfz

S W 5 - C C h i

votufvia

j!MopE5wj_tC1q=?

RESET

Switch

0

}

O

_O,,,¢¢-

if \:

..;¢¢

msn

asssr

WN

MIX

POWER VOLUME MODE

RESET

Powaaon

display

light

l)

Power

switch;

Push the

switch

then

power

is

on with

red

light

on.

Push the

switch

again

then

power

is

off.

2

)

VOLUME :

Control the

loudness

of

the

Click sound

of the

keyboard

and

speaker

volume.

3)

MODE

switch;

This switch

selects

characters/line

mode

("1"=80 CH./line;

"o"=ao

CH./line).

4)

RESET

switch;

RESET

is

triggered by

this

switch,

and

stops executing

the

BASIC

program,

and returns to

command level.

A

Page 9

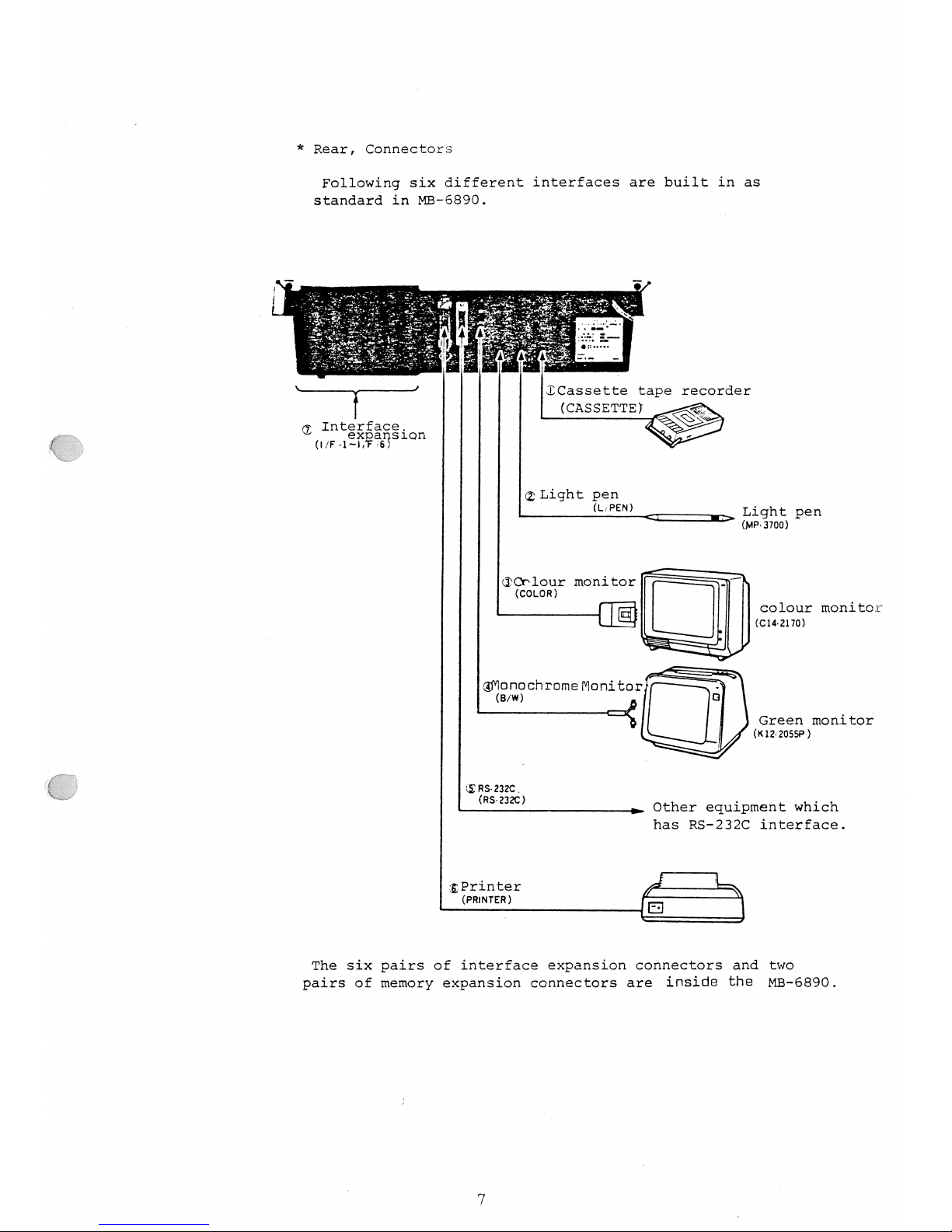

*

Rear,

Connectors

Following

six

different

interfaces are built in as

standard

in M -6890.

1

*

p.

mm

.H~mi»;_ __‘_

_,_

,

_

{

_

~

,

~ . ’ + = .

’ . ’ Q ~ ’ z ~ : ‹ :

’_

; ~ » ~ - =

_

f-

:""’

~

’;»

n " ¢ ’ 1 ~

‘

’»-

> ’ ~ 1 ; . " 1 ’ - : F i - k c ’ - ’ A

E§»:.-»;_

_V

T _ » " j ! , , 2 5 f " ‘

;-¢_

,_

. ,

‘?’

g’

gf

=

_ : i 2 , [ § » ; : i ; ’ § ’ + - ; § M ; i ? , ; @ 5 ’ , 2 f + l ; , 5 = i ! " 3 3 Z ’ § i : f 1 a a : H t l r f . " -

M;

i ? , ; @ 5 ’ , 2

f

+

l

; , 5 = i ! " 3 3 Z ’ § i : f 1 a a

:Htl

rf."-

, f

-if

» ¢ ~ f = t . = , \ 1 g f f , . ; - ~ - - , » f ’ ~ q ’ -

.V

’

~

~_ "F

~

’

$Cassette

tape

recorder

(CASSETTE)

,

@

Interface.

/W

ex a

sion

_

(I/F

-1~»,$-513

\/

Qlight

pen

(DPW)

__

Light pen

(BAP-3700)

fiCblour

monitor

"""i

-

(coLoR>

colour monitor

(c14-2170>

@MonochromeMonitor’

H

(ww)

B

Green

monitor

(KIZZDSSP)

5

ins-zazc.

Rs~z32c

. .

( )

Other

equipment

which

has RS-232C interface.

isprinter

(PMNTER)

The six

pairs

of interface

expansion

connectors and two

’

connectors are

inside

the

MB-6890.

pairs

of

memory

expansion

7

Page 10

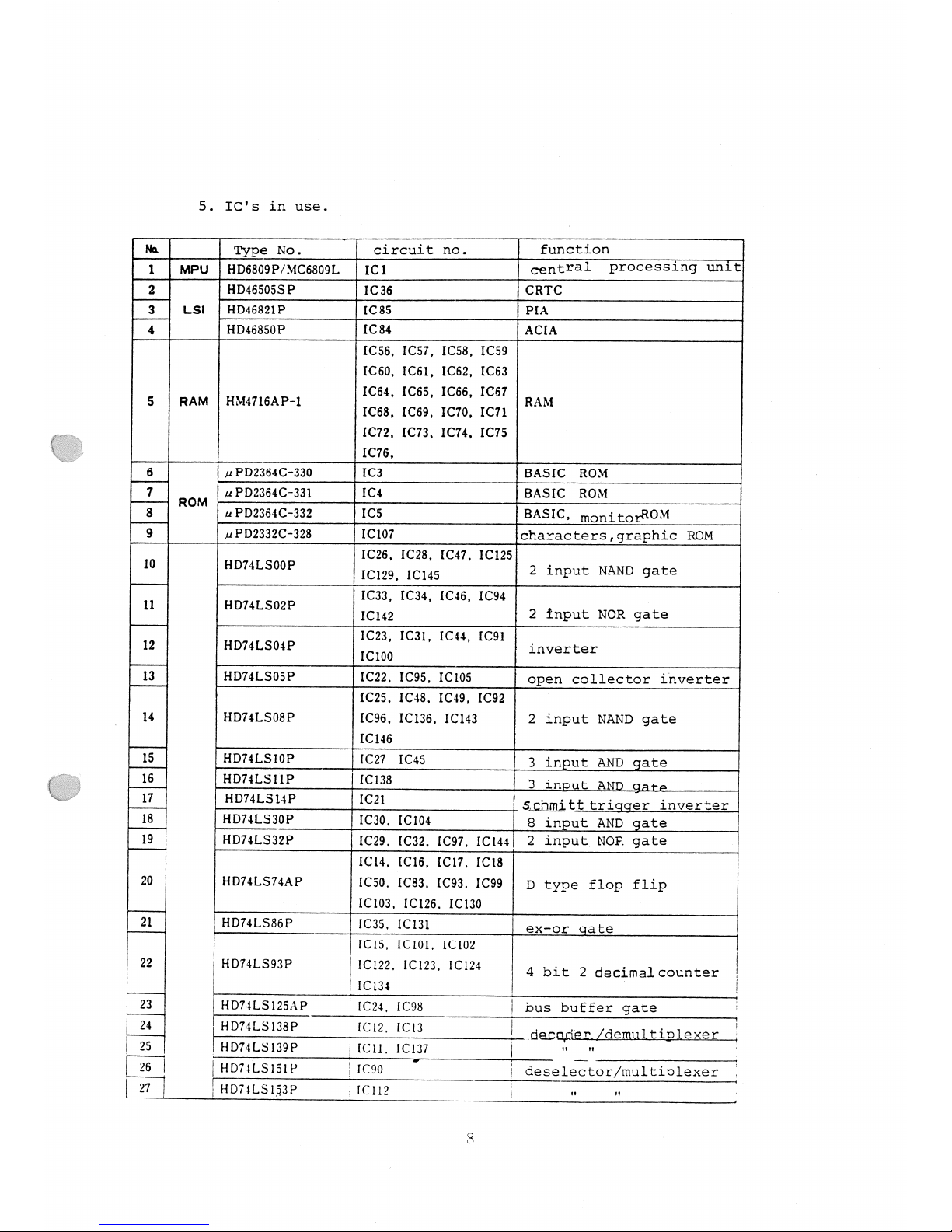

5. IC’s

in

use.

Type

No.

Q

circuit no.

function

Mpu

HDeso9P/MCeao9L

1C1 central

Pf C@SSif19

Unit

Hmssossp

rcse CRTC

L.Sl HD4ea21P

Q

LCSS

Q

PIA

Q

HD4sssoP

ICS4

ACIA

Icse,

1Cs1 Icss 1Cs9

1Cso,1Cs1

xcsz

[css

RAM HM4716AP-1

IC54’

IC65’

IC66

IC57

RAM

ICss,1Cs9

Icvo

IC71

IC12, IC73, IC14,

IC75

1C1s,

/mnzsasc-ssc

Qrcs

BASIC Rom

Q

ROM

uPD2364C-331

IC4

BASIC Rom

Q

uPD2364C-332

I C S

BASIC,

monitoraom

yPD2332C-328

IClO7

\characters,graphic

ROM

HDHLSODP

1C2s, rczs, IC47,

IC12s

2

_

IC129,

IC145

lnput

NAND

gate

Icaa,

IC34,

1C4e,

ICQ4

" D 7 L S " 2 P

[C142

2

input

NOR

gate

HDNLSMP

IC23,

IC31,

IC44,

1C91

inverter

IC100

HD74LS05P

IC22,

lC95,

ICIOS

open

collector inverter

xczs,

Icas,

xC49,

IC92

HD74LS08P

IC96, IC136,

IC143 2

input

NAND

gate

1C14s

HD74LS1OP

1C21

rC4s

3

input

AND

gate

HD74LS11P

Qrclss

3

input

AND

gm?

Q

H D 7 4 ~ 5 1 4 P

[Cm

Q

Stghmitt

trigger

inverter

V

HD74LS30P

rcso,

ICIO4

S

input

AND

gate

Q

HDm.S32P

1C29,

1C3z, IC97,

1Cl44]

2

input

NOP-

gate

IC14,

IC1s, ICI7,

IC1s

HD14Ls74AP

Icso,

xCs3, xC93,

IC99

D

type flop

flip

1C1o3

IC126.

ICl30

Q

HD14LSseP

Azcss,

[C131

eX_Or

qate

Q

1C1s, IC101.

rC1o2

Q

HD74LS93P

‘ICl22

1C123,

rC124

4 bit 2

decimalcounter

Q

IC\34

’

!

HD74LSI25AP

ICQ4,

me

bus buffer

gate

Q

HD14LS13sP

Q1C12.

IC13

_

d&m’dQr_Q/demltiplexer

HD14LS139P

ICU. IC137

-»

»~

Q

Hm4LS1sw

Q

xC9o

’

deselecwr/multiplexer

Q

HD74LS1_53P

Q 1C112

QQ

.» ~

1

3

Page 11

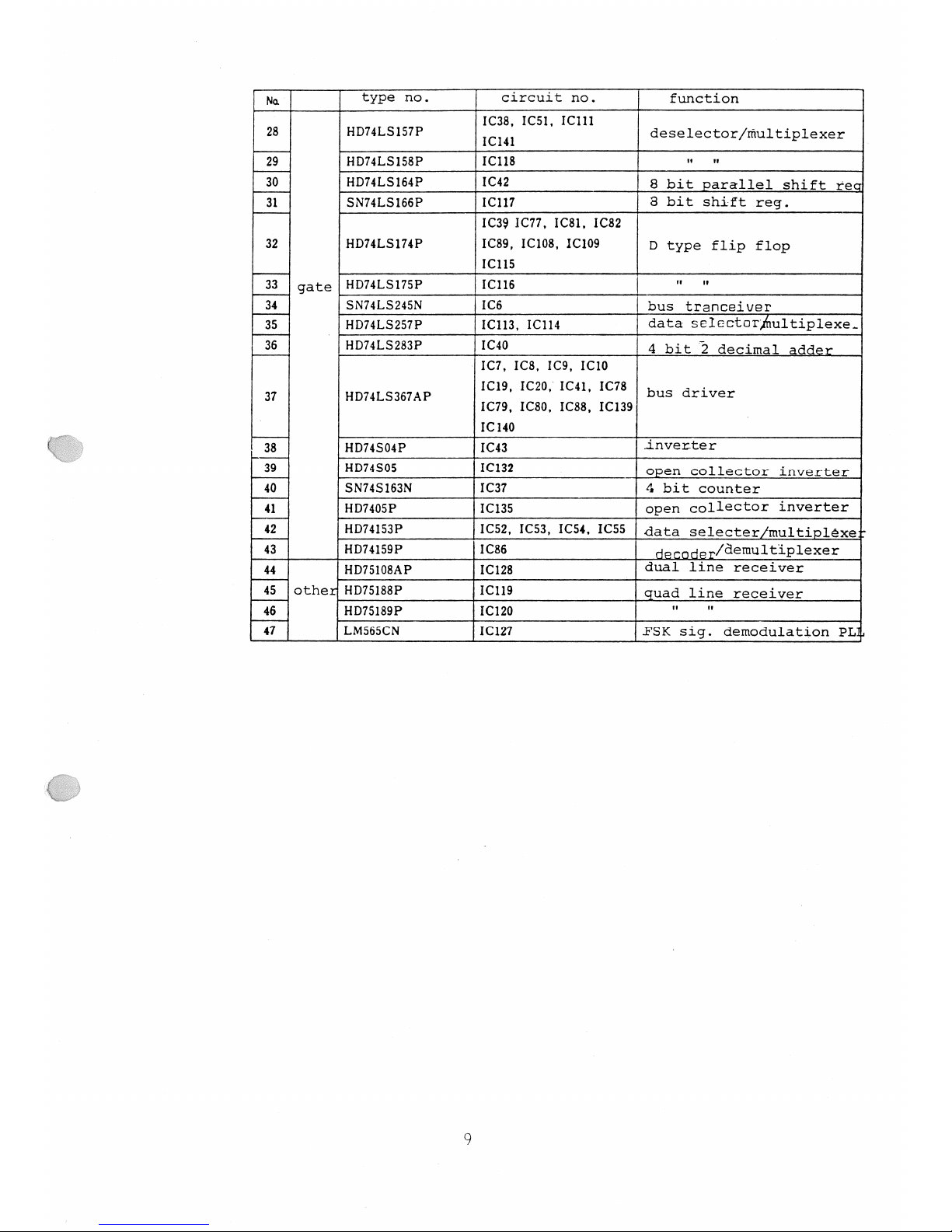

Na

type

no. circuit

no.

function

i

Icas,

IC51,

IC111

28 HD74LSl57P

ICI"

de-selector/rfzultiplexer

I

HD74LSI58P Icus

-- --

__§g_

HD14LS1e4P

IC42

8 bit

parallel

ahlft

req!

31

sN14Ls1seP

xcm

3

bit

shift

reg.

""

1ca91c11,

IC81,

xcsz

32

HD74LSl74P

rcse, ICIOS,

XC109

D

type

flip

flop

Icus

_:ET

gate

HD74LSl75P Icue

"

-’

T a sN741.s245N

arcs

bus

tranceiver

E

HD74LS257P

IC113,

IC114

data

Seleeterhultiplexe-

__§§_a

HD?"-5283? 1C4

4

bit Q

decimal

adder

1c1,

ics,

rcs,

Iclo

37 HD74LS367AP

xcle, Iczo, IC41,

lcvs

bus

driver

IC79,

Icso,

Icsa,

IC139

1c14o

Vi? HD74S04P IC43

inverter

E

H - 3 7 4 5 0 5

IIC132

J

open

collector

inverter

40

SN74S163N

IC37 4

bit

counter

’T Hrmosp IC135

open

collector

inverter

Z

Hm41s3P

1C52,

xcsa,

IC54,

IC55

data

Selecter/multiplØxe

43

HD74159P

IC86

decade):/demultiplexer

44 HD75l08AP IC128

duel

line

receiver

’Teena HD751saP IC119

quad

line

receiver

E;

HD75189P

IC120

" "

47 LMSGSCN

lC127

FSK

sig.

demodulation

PL

9

Page 12

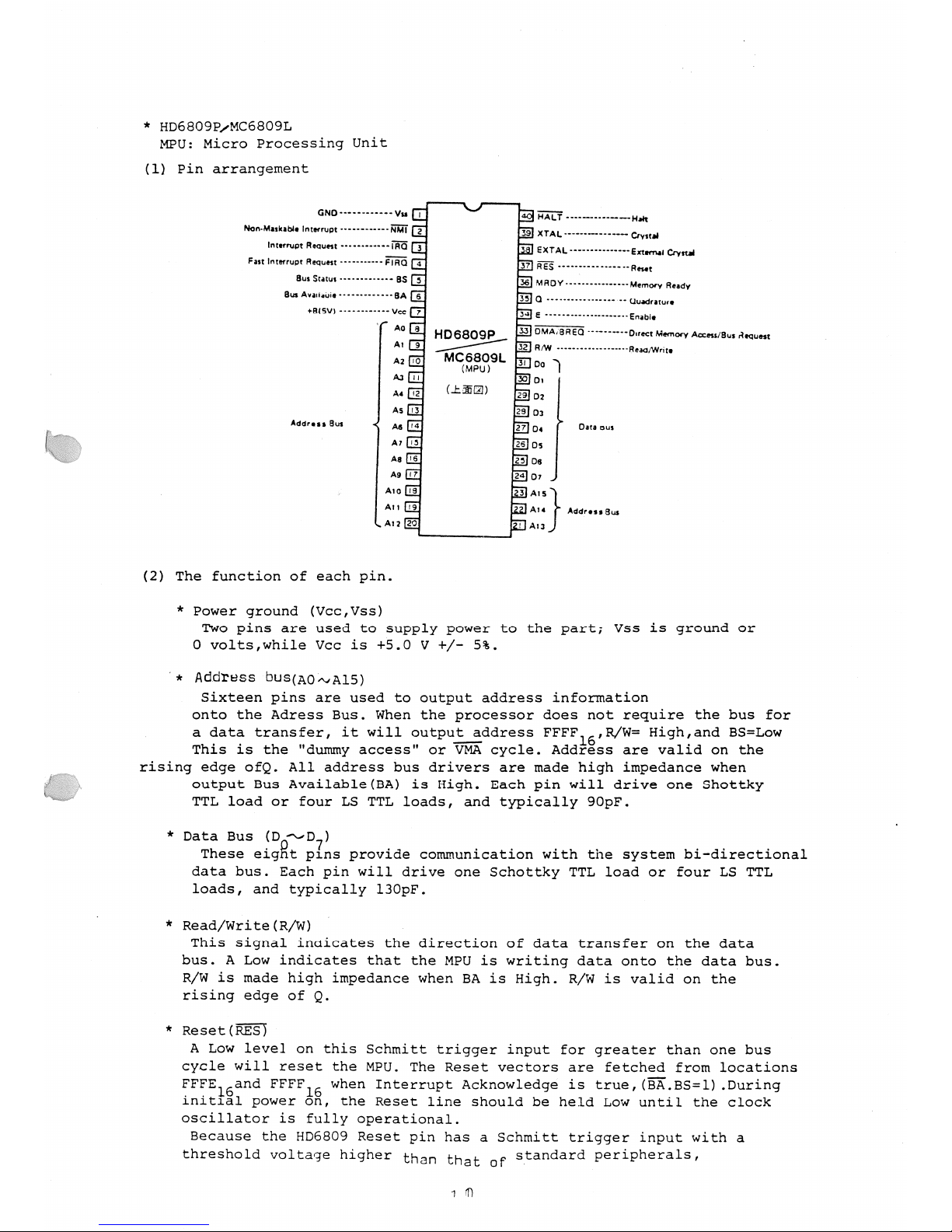

Address

DUS(AOA¢Al5)

*

HD6809P/MC6809L

MTU:

Micro

Processing

Unit

(1)

Pin

arrangement

GND------~-----V"

ll

E51HA|_r’-._--._

..-. __

H,"

Non-Mukabln

lnwrum

----- - ------

NMI

E

xYAL_

_____

___

_____ __

G y m

| \ ¢ " U 9 K

RMIUMI

~"’ - ’-"~~

I

RQ

B

gg]

SXTAL

_______

_____En

Icwnd

Pm

Immun:

Request

-~--~~~--~-

FIRQ

¢-|

gig

___ ____

_____R___t

=~=

B5

n

ss

Mm-,Y

........

-.-..M.m.,,

,.,,_,,

Bus

Avlxiauiq

-- --------

BA

B

Q

_ _ _ _ _ _ _ _ _ _ _

__

__

uu______w_

B15

---~--------

, .. ._

*

‘ V)

___

"’

’Z

"

""

" " " "

’

" "

E nabh

HD6809p

ommanso-

-~--DumMemoryAmer/au.Requen

~--Dum

Memory Amer/au.

Requen

A2

IE 3|

(MPU)

_

Do

W

A3

m

EE Dv

A4

D2

A5

D3

Addrusi

eu!

<

A.

m

D.

Dua nu,

A

’B

Ds

AU

E

E Ds

‘

A9"

E!o1)

AW

@

@ AIS

A"

m

m

A14

AddrnuEus

\A’1EE

n|Au

(2)

The

function of each

pin.

Two

pins

’

*

*

Power

ground

(Vcc,Vss)

are

used to

supply power

to the

part;

Vss is

ground

or

O

volts,while

Vcc is +5.0

V

+/-

5%.

d

to out ut

address

information

Sixteen

pins

are use

p

onto the Adress

Bus.

When the

processor

does not

require

the bus

for

t

t ddress

FFFF

R/W-

High,and

BS=Lowa data

transfer,

it

will ou

pu__a

16,

-

This is the

"dummy

access"

or

VMA

cycle.

Address are valid on the

rising edge

ofQ.

All address

bus drivers are

made

high

impedance

when

c * *

" = i l a b l e ( B A )

is

High.

Each

pin

will

drive

one

Shottky

\.J\.L\-bJ\4l¢

LJIJJ FXVQL

TTL load

or four LS TTL

loads,

and

typically 9OpF.

’d

nication

with

the

system

bi-directional

*

Data

Bus

(D-o/D7)

These

eiggt pins provi

e

commu

data

bus. Each

pin

will drive one

Schottky

TTL load or

four

LS TTL

loads,

and

typically l3OpF.

*

Read/Write(R/W)

This

signal

indicates

e

bus. A

Low indicates

that the MPU is

writing

data onto the data

bus.

R/W

is made

high impedance

when BA is

High.

R/W

is

valid on the

th

direction of data transfer on the data

rising edge

of

Q.

*

R ‹ S ‹ t ( R E S ;

A Low

level

on this

Schmitt

trigger

input

for

greater

than one bus

cycle

will

reset the

MPU. The Reset

vectors are fetched

from locations

‘

’_

-

Din

TFSEl6and

FFFFl6

when

Interrupt Acknowledge

is

true,(BA.BS-l).

ur

g

initial

power

on,

the

Reset

line should be

held Low

until the clock

oscillator is

fully

operational.

Because the HD6809

Reset

pin

has

a Schmitt

trigger input

with a

threshold

voltage

higher

than

that

of

standard

peripherals,

1 YD

Page 13

\

’k

a

simple

R/C

network

may

be

used

to reset

the entire

system.This

higher

threshold

voltage

ensures

that all

peripherals

are

out

of

the

reset

state before

the Processor.

*HALT

A Low level on

this

input pin

will cause

the MPU to

stop running

at

the

end of

the

present

instruction

and

remainhelted

indefinitely

without

loss

of data.

When

halted,

the

BA

output

is driven

High

indicat-

ing

the buses are

high impedance.

BS is also

High

which indicates

the

processor

is in the Halt

or

Bus Grant state.

*HALT

A

Low level on this

input

will cause the MPU

to

stop running

at the

end of the

present

instruction

and

remain

halted

indefinitelywithout

loss

of

data.

When

halted,

the BA

output

is driven

High indicating

the

buses

are

high

impedance.

BS

is

also

High

which indicates

the

processor

is in the

Halt

or

Bus Grant State,

Bus

Available,

Bus

Status(BA,BS)

The BA

output

is an

indication

of

an internal control

signal

which

makes

the MOS buses of the

MPU

high

impedance.

This

signal

does not

imply

that the bus will be

available for

more

than

one

cycle.

when BA

goes

Low,

an additional

dead

cycle

will

elapse

before

the MPU

acquires

the

bus.

The BS

output signal,

when decoded with

BA,

representing

the MPU

state(valid

with

leading edge

of

Q).

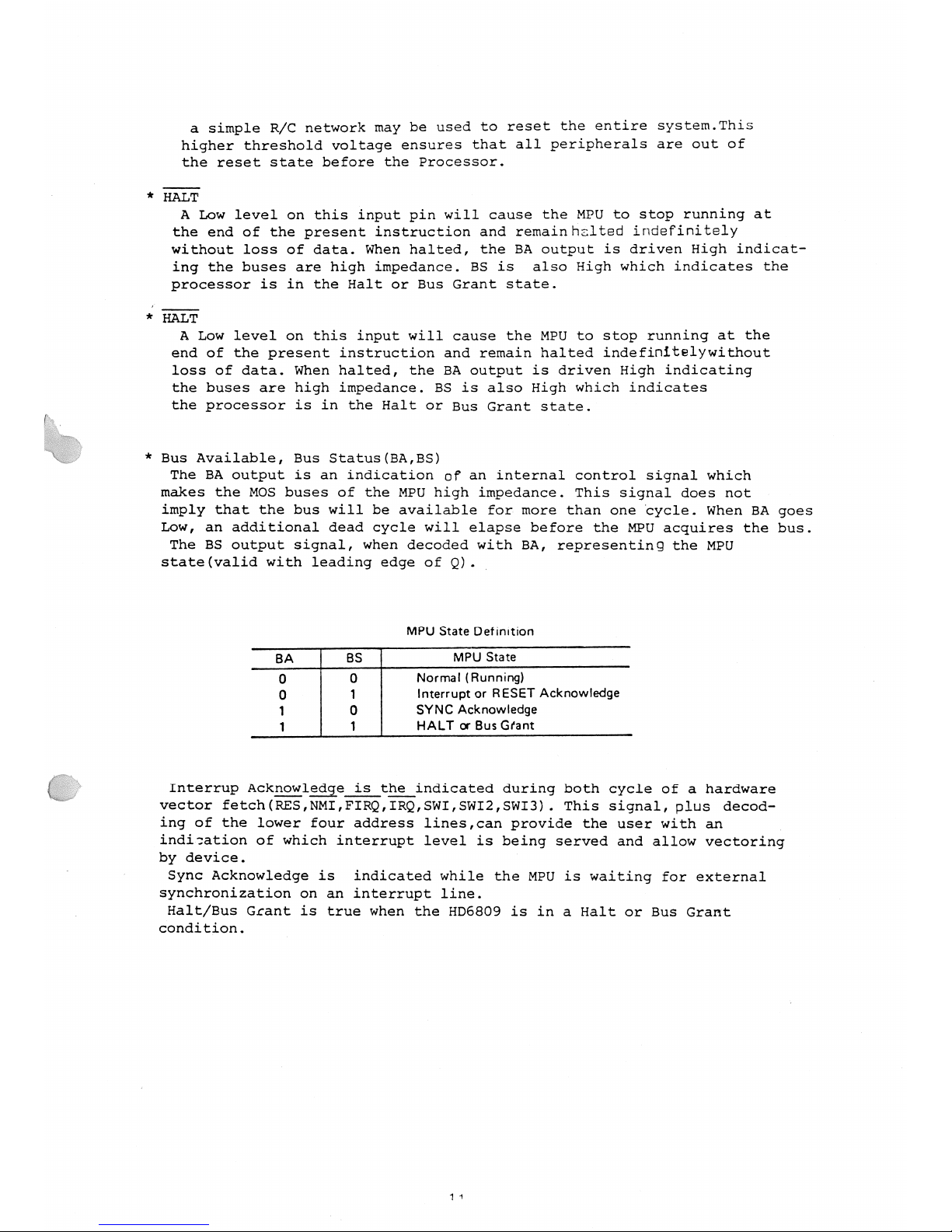

MPU State

Definition

BA

|

as

MPU

stare

0

0

Normal

(Running)

0

1

Interrupt

or RESET

Acknowledge

1

0

SYNC

Acknowledge

1

1

HALT

or Bus Grant

interrup

Acknowledge

is

th§_indicated

during

both

cycle

of a hardware

vector

fetch(RES,NMI,FIRQ,IRQ,SWI,SWI2,SWI3).

This

signal, plus

decod-

ing

of the

lower four address

lines,can

provide

the

user with an

indication

of which

interru

t

level

‘

b

by

device.

Sync

Acknowledge

is

indicated whi

synchronization

on an

interrupt

line.

Halt/Bus

Grant is

true

when the

HD6809 is in

a Halt or Bus

Grant

condition.

p

is

eing

served and

allow

vectoring

le

the MPU is

waiting

for

external

11

Page 14

*

Non Maskable

Interrupt

(NMI)

A

negative edge

on this

input

requests

that a nonmaskable

interrupt

sequence

be

generated.

Anon-maskeble

interrupt

cannot

be

inhibited

by

the

program,

and

also

has a

higher

priority

than

E I R Q , I R Q

or

software

interrupt.

*

Fast-Interrupt

Request(FIRQ)

A

Low

level on this

input pin

will initiate

provided

its

mask

bit(F)

in

the CC

is_§lear.

over

the standard

Interrupt

Request(IRQ),and

it stacks

only

the

contents of the condition

program

counter.

*

Interrupt

Request(I§Q)

A Low

level

input

on this

pin

will initiate

provided

the mask

bit(I)

in

the

CC

is

clear.

a

fast

interrupt sequence

This

sequence

has

priority

is fast in

the sense that

code

register

and the

an

interrupt Request sequence

Since

IRQ

stacks the

entire

machine state it

provides

a

slower

response

to

interrupt

than

FIRQ,IRQ

also has a

lower

priority

than

FIRQ.

*

E,

Q

E is

similar

to

theHD468OO bus

timing

signal

§Z52;Q

is

a

quadrature

clock

signal

which leads

E.Address

from the

MPU

will

be valid

with

the

leading

edge

of

Q.

Data is

latched on the

falling

edge

of

E.

*MRDY

This

input

control

signal

allows

stretching

of

E

and

Q

to extend data

access

time.

*

DMA/BREQ

_

The

DMA/BREQ

input provides

fa

method

of

suspending

execution and

acquiring

the MPU

bus for

another

use.

Typical

uses include

DMA and

dynamic

memory

refresh. When

BA

goes

Low,

the DMA

device

should be

taken

off the

bus.

~HD45821E

(PIA

3

Peripheral

Interface

Adapter)

*

PIA

INTERFACE SIGNALS FOR

MPU

(U

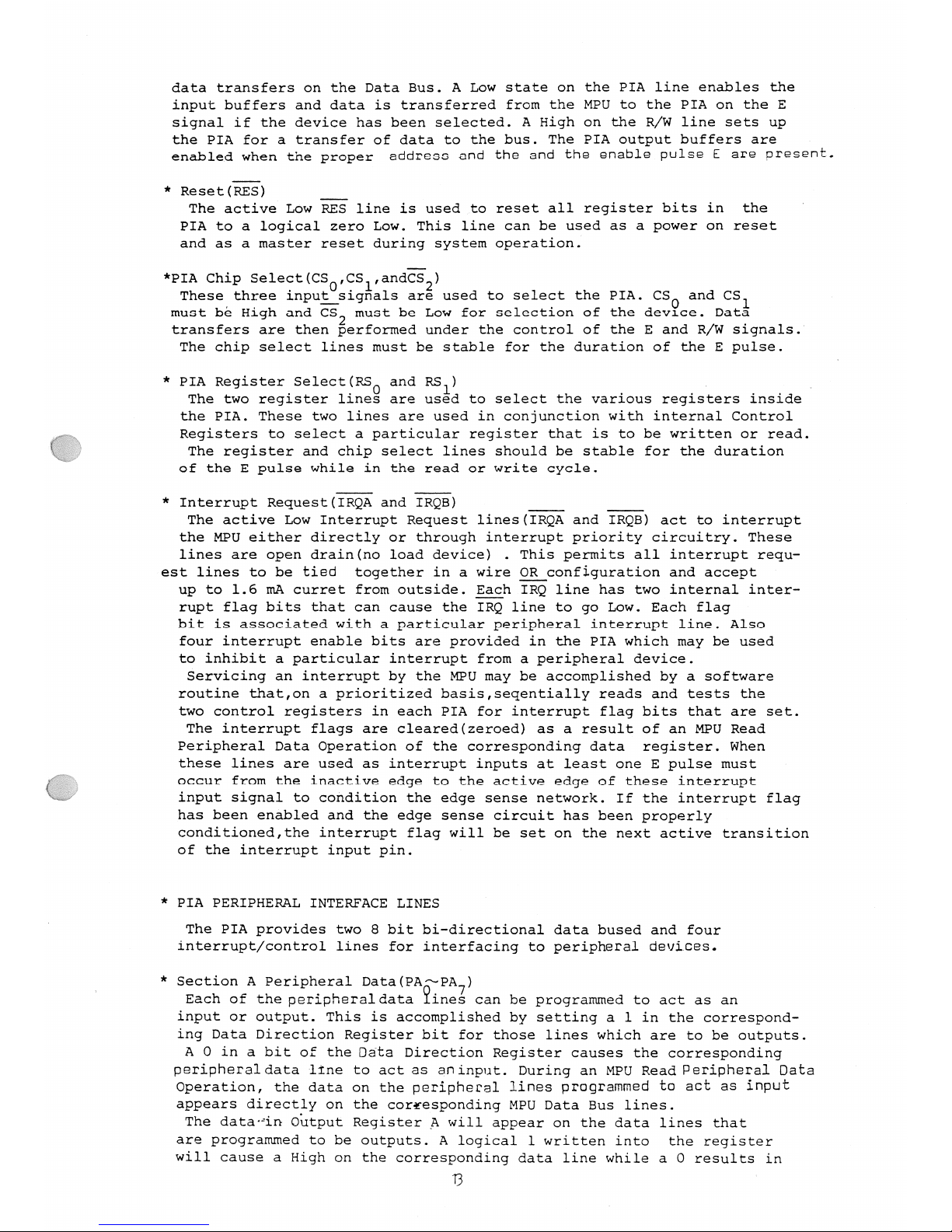

pin arrangement _ ,___ __ __. ._ _ _ _ ._ _ .

K

FLA

aleuirectional

uataLD»~jU7)

(GNDHM

CA’

The

bi-directional

data Qines

PM

CM

(D6’D7)allow

the

transfer

of

PM

WOT

data

between

the

MPU and the

PIA.

PM %§

The data

bus

output

drivers are

PM R50

three

state

devices

that remain

PM RS,

in the

high impedance(off)

state

,As m

exception

when the

MPU

performs

PM

0

a PIA

read

operation.

PA1

32

D1

no HD46821P

nz

*

PIA

Enable(E)

Pm

(Pm)

DJ

The

enable

pulse,E,

is the

only

N215

FED#

I

timing signal

that is

supplied

P91

05

to

the PIA.

Timing

of all

other

PB*

D6

signals

is

referenced

to the

leading

:Es

Z

and

trailing edges

of the E

pulse.

6

Q

*

PIA

Read/wri§;e

C82

CSD

This

signal

is

generated by

the

(5\/WEE:

: RM

MPU to

control the

direction

of

T2

Page 15

data transfers

on the Data Bus.

A Low state on

input

buffers and data is transferred

from

the

signal

if

the

device

has been selected.

A

High

the

PIA for

a

transfer of data to

the bus.

The

the PIA line enables the

MPU to the PIA

on

the E

on

the

R/W

line sets

up

PIA

output

buffers are

enabled when

the

proper

address

and

the and

the enable

pulse

E are

present

*

Reset(RES)

The

active Low RES line is used

to reset all

register

bits in the

PIA to a

logical

zero Low. This line

can be used as a

power

on

reset

and

as

a

master reset

during

system operation.

*PIA

Chip

se1e

These three

input

signals

are used to

select

the

PIA. CS

and

CS

rn1~|a{- kr: Uifvln an/4 PC m11c+- Ha Tr\v.1 Fnr cc1c>/

ma-- -t

nigh

and

e-2

mu-. be ao" lor -election

transfers are then

performed

under

the

control

of

the

devgce.

Dat;

of

the E and

R/W

signals.

The

chip

select lines must be stable for

the

duration

of the E

pulse.

*

PIA

Register

Select(RSO

and

RS1)

The two

register

lines are used to select

the

various

registers

inside

the PIA. These two lines are used

in

conjunction

with

internal Control

Registers

to select a

particular

register

that is to be written

or read.

The

register

and

chip

select lines should

be

stable for the duration

of

the E

pulse

while in the

read or write

cycle.

*

Interrupt Request(IRQA

and

IRQB)

The active Low

Interrupt Request lines(IRQA

and

IRQB)

act to

interrupt

the

MPU either

directly

or

through interrupt priority circuitry.

These

lines are

open

drain(no

load

device)

. This

permits

all

interrupt requ-

est lines to be tied

together

in a wire

QR_configuration

and

accept

up

to 1.6

mA

curret from outside.

gagh

IRQ

line has two

internal

inter-

rupt

flag

bits that can

cause the

IRQ

line to

go

Low.

Each

flag

bit is associated with

a

particular peripheral interrupt

line.

Also

four

interrupt

enable bits are

provided

in the PIA which

may

be

used

to inhibit a

particular interrupt

from a

peripheral

device.

Servicing

an

interrupt by

the MPU

may

be

accomplished

by

a software

routine

that,on

a

prioritized

basis,seqentially

reads and tests the

two control

registers

in

each PIA for

interrupt flag

bits that are set.

The

interrupt flags

are

cleared(zeroed)

as a

result of an MPU Read

Peripheral

Data

Operation

of the

corresponding

data

register.

When

these

lines are used as

interrupt inputs

at least one E

pulse

must

occur from the

inactive

edge

to the active

edge

of these

interrupt

input

signal

to

condition the

edge

sense network.

If

the

interrupt flag

has been

enabled

and

the

edge

sense circuit has

been

properly

conditioned,the

interrupt

flag

will be

set

on

the next active

transition

of the

interrupt input pin.

*

PIA

PERIPHERAL

INTERFACE LINES

The PIA

provides

two 8 bit

bi-directional data

bused and four

interrupt/control

lines

for

interfacing

to

peripheral

devices.

*

Section A

Peripheral

Data(PA’~PA7)

Each of the

peripheraldata

lines can be

programmed

to act as an

input

or

output.

This

is

accomplished

by setting

a l in

the

correspond-

ing

Data

Direction

Register

bit

for those lines which

are to be

outputs.

A O

in a

bit of the

Data

Direction

Register

causes the

corresponding

peripheraldata

line

Operation,

the data

appears

directly

on

The

d a t a i n

Output

to act as

aninput.

During

an MPU Read

Peripheral

Data

on

the

peripheral

lines

programmed

to

act

as

input

the

corresponding

MPU Data Bus lines.

Register A

will

appear

on the data lines that

are

programmed

to

be

outputs.

A

logical

l written into

the

register

will cause a

High

on

the

corresponding

data line while a O

results in

T3

Page 16

*

a Low.

Data in

Output

Register

A

may

be read

by

an M?U "Read

Peripheral

Data A"

operation

when the

corresponding

lines are

programmed

as

outputs.

This data will

be

read

properly

if

the

voltage

on

the

peripheral

data

lines is

greater

than

2.0 volts

for a

logic

l

output

and less

than

0.8 volt

for a

logic

0

output.

Loading

the

output

lines

such that the

voltage

on

these

lines

does

not reach

full

voltage

causes

the data

transferred

into the MPU on

a

Read

operation

to

differ from

that contained

in the

respective

bit of

Output Register

A.

Section

B

Peripheral

Data

(PBSPB7)

The

peripheral

data

lines on

the B Section

of the PIA can

be

programmed

to

act

as either

inputs

or

outputs

on a similar

manner to

P A P A 7 .

However,

the

output

buffers

driving

these lines differ from

Qhose

driving

lines

P A 5 P A 7 .

They

have

three state

capability,allowing

them to enter

a

high

impedance

state

when the

peripheral

data

line is used as

a

input.

In

addition,

data

on the

peripheral

data lines

PB6»PB7

will be

read

properly

from

those

lines

programmed

as

outputs.

As

outputs,

these

lines are

compatible

with

standard

TTL and

may

also

be

used as

a

source

of

up

to 2.5

milliampere(typ.)

at 1.5

volts to

directly

drive

the

base of a

transistor switch.

*

Interrupt

Input(CA1andCB1)

Peripheral Input

lines

CAl

and

CA2

are

input

only

lines that set the

interrupt flag

of

the control

registers,

The active transition

for these

signals

is also

programmed

by

the two control

registers.

*

Peripheral

Control

(te2)

TheD91‘iDh91‘controllineCAcanbeprogrammedtoactasan

control

line CA can

be

programmed

to act as

an

interrupt input

or

asa

D9fiDh9%5l

control

output.

As an

output,

this

line is

compatible

with standard TTL. The

function of this

signal

line

is

programmed

with Control

Register

A.

*

Peripheral

Control(CB2)

Peripheral

COntrol

line

CB2

may

also

be

programmed

to act as

an

inter-

rupt input

or

peripheral

control

output.

As an

input,this

line has

High

input impedance

and is

compatible

with standard TTL.

As an

output

it

is

compatible

with standard

TTL and

may

also be used of

up

to 2.5

mill-

iampere(typ.)

at 1.5 volts

to

directly

drive

the base of a transistor

switch. This

line is controlled

by

Control

Register

B.

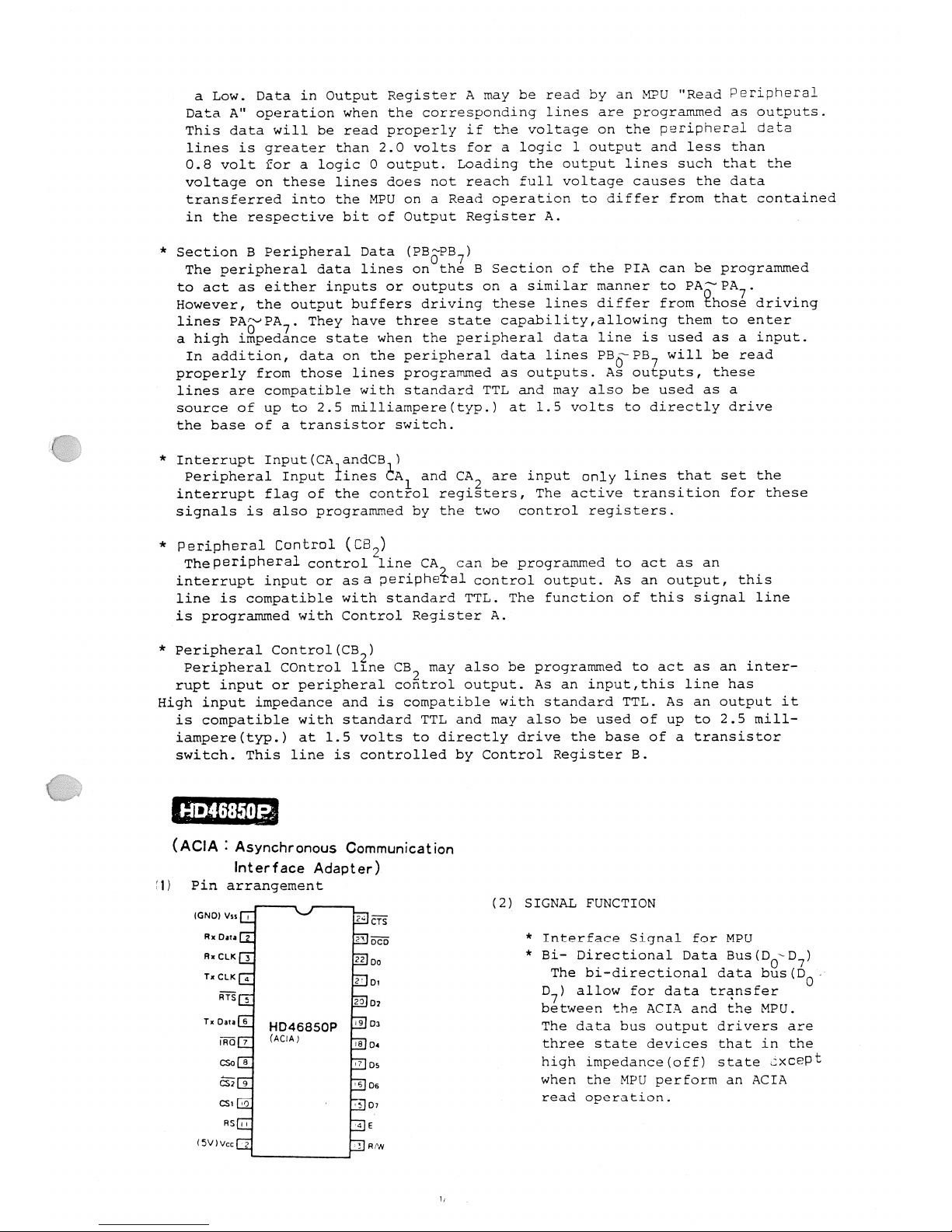

(ACIA

3

Asynchronous

Communication

Interface

Adapter)

W)

Pin

arrangement

(GND)

Vss

Rx

Dafa

RICLK

TxCLK

EE

Tx

Dau

EE

Gm

as

(31

M

(5V)V¢c

2

7

HD4685OP

MCM)

2;

23

E5

E5

Do

D1

D7

DJ

D4

Ds

D7

/W

||

||

ll

|$

EE

El

E5

||

I5

El

Ds

IE

@

~

E

R

SIGNAL FUNCTION

*

Interface

Signal

for MPU

*

Bi-

Directional Data

Bus(DO\D7)

The

bi-directional data

bus(DOf

D7)

allow

for data

transfer

between

the ACTA and the MPU.

The data bus

output

drivers are

three state

devices

that in the

high

impedance(off)

state

;xC9Dt

when

the MPU

perform

an ACIA

YDZA nnnrnØ-inn

..~..\..tA

vrf\.._\.r~.a.v|».

Page 17

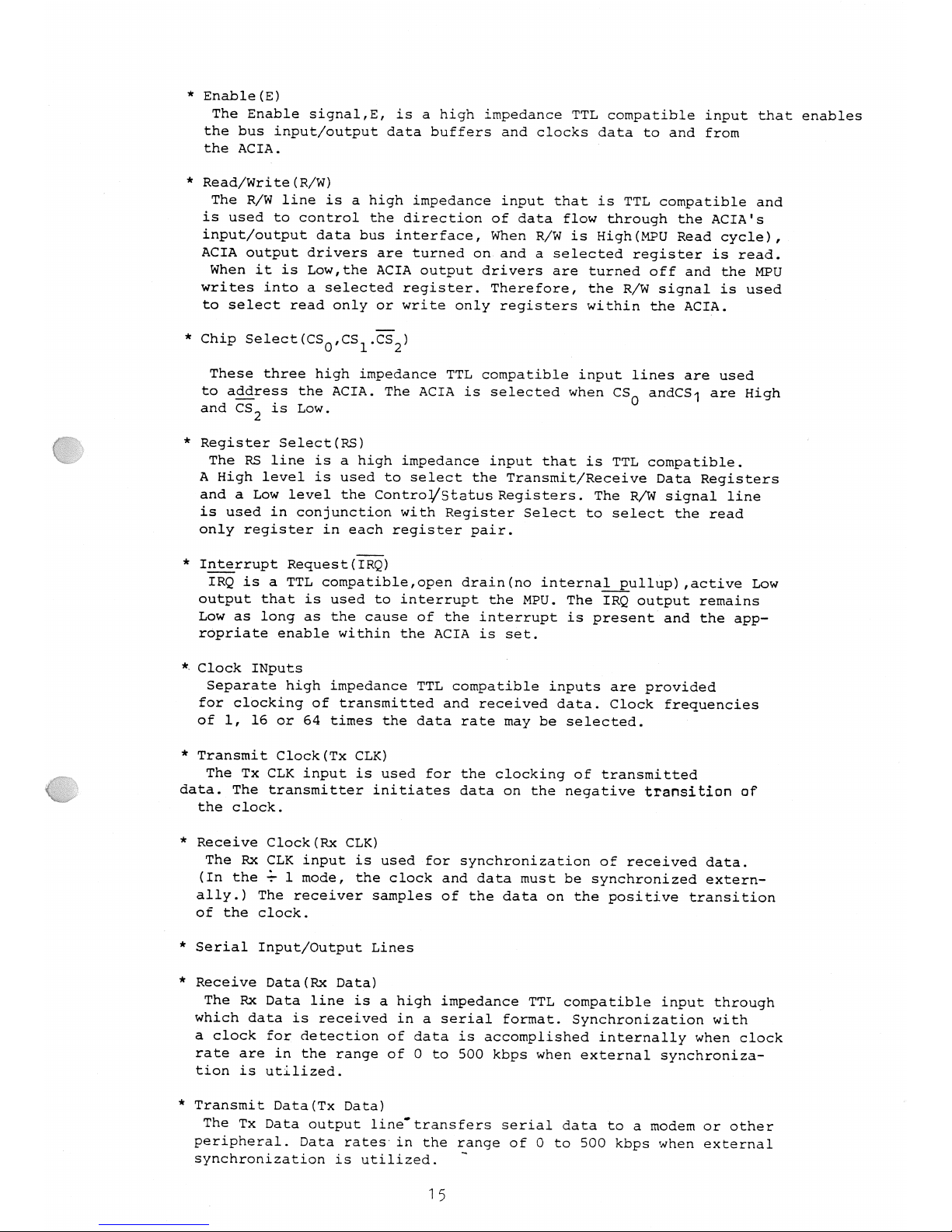

*

Enable(E)

The

Enable

signal,E,

is a

high impedance

TTL

compatible

input

that

the bus

input/output

data

buffers and

clocks data

to and

from

the

ACIA.

*

Read/Write(R/W)

The

R/W

line is

a

high

impedance

input

that is

TTL

compatible

and

is

used to

control the

direction of data

flow

through

the

ACIA’s

input/output

data bus

interface,

When

R/W

is

High(MPU

Read

cycle),

ACIA

output

drivers

are

turned on and

a

selected

register

is

read.

when it

is

Low,the

ACIA

output

drivers are turned

off

and

the MTU

writes into a

selected

register.

Therefore,

the

R/W

signal

is

used

to select

read

only

or write

only

registers

within the

ACIA.

*

chip

Select(CSO,CSl552)

These three

high impedance

TTL

compatible

input

lines

are

used

to

address

the

ACIA. The

ACIA is

selected when

CSO

andCS1

are

High

and

CS2

is

Low.

*

Register

Select(RS)

The RS line is

a

high impedance input

that is

TTL

compatible.

A

High

level is used to

select the

Transmit/Receive

Data

Registers

and a Low level the

ControVStatusRegisters.

The

R/W

signal

line

is used in

conjunction

with

Register

Select

to

select the

read

only

register

in

each

register pair.

*

Interrupt

Request(TR5)

IRQ

is a TTL

compatible,open

drain(no

internal_pullup),active

Low

output

that is

used to

interrupt

the

MPU. The

IRQ

output

remains

Low as

long

as

the cause

of the

interrupt

is

present

and the

app-

ropriate

enable within

the

ACIA is

set.

*

Clock

INputs

Separate

high impedance

TTL

compatible

inputs

are

provided

for

clocking

of

transmitted and

received

data.

Clock

frequencies

of

l,

16 or 64

times the

data

rate

may

be

selected.

*

Transmit

Clock(Tx CLK)

The

Tx CLK

input

is used

for the

clocking

of

transmitted

data.

The

transmitter

initiates data

on the

negative

transition

of

the

clock.

*

Receive

Clock(Rx CLK)

The Rx

CLK

input

is

used for

synchronization

of

received

data.

(In

the Ø l

mode,

the clock

and data

must be

synchronized

extern-

ally.)

The

receiver

samples

of

the data on

the

positive

transition

of the

clock.

*

Serial

Input/Output

Lines

*

Receive

Data(Rx

Data)

The

Rx

Data line is

a

high impedance

TTL

compatible

input

through

which

data is

received in

a serial

format.

Synchronization

with

a

clock

for

detection of

data is

accomplished

internally

when

clock

rate

are

in the

range

of

O

to SOO

kbps

when

external

synchroniza-

tion is

utilized.

*

Transmit

Data(Tx

Data)

The

Tx

Data

output

line’transfers

serial data

to

a modem

or other

peripheral.

Data

rates in

the

range

of O

to

500

kbps

when

external

synchronization

is

utilized.

N

T5

enables

Page 18

Modem

CC>ntrol

The

ACIA

includes

severa

a

peripheral

or

modem.

The

functions

included

are

CTS,RTS

andDCD.

l functions

that

permit

limited

control

of

Clear to

Send(CTS)

This

high

impedance

TTL

compatible

input

provides

automatic

control

of the

transmitting

end of

a communications

link via

the

modem CTS

active

Low

output by

inhibiting

the

Transmit

Data

Register

Empty(TDRE)

atatus

bit.

Request

to

Send(RTS)

The

RTS

output

enables

the

MPU to control

a

peripheral

or

modem via

the data

bus.

The

RTF;

output

corresponds

to the

state

of the

Control

Register

bits

CRS and CR6.

When CR6=O

or

both CR5

and

CR6=l,

the

RTS

output

is

Low(the

actiire

state).

This

output

can

also

be used

for

Data

Terminal

R e a d y ( D 1 R )

t

Data

Carrier

Detect(DCD)

This

high

impedance

TTL

compatible

input

provides

automatic

control,

such

as

in_the

receivingirld

of

a communications

link

by

means

of

a

modem

DCD

output.

The

DCD

input

inhibits

and

initializes

the

rec-

eiver

section

of

the ACIA

when

High.

A Low to

High

transition

of

the

DCD

initiates

an

interrupt

to the MPU

to indicate

the

occurrence

of

a

loss of carrier

when the Receiver

Interrupt

Enable

bit

is set.

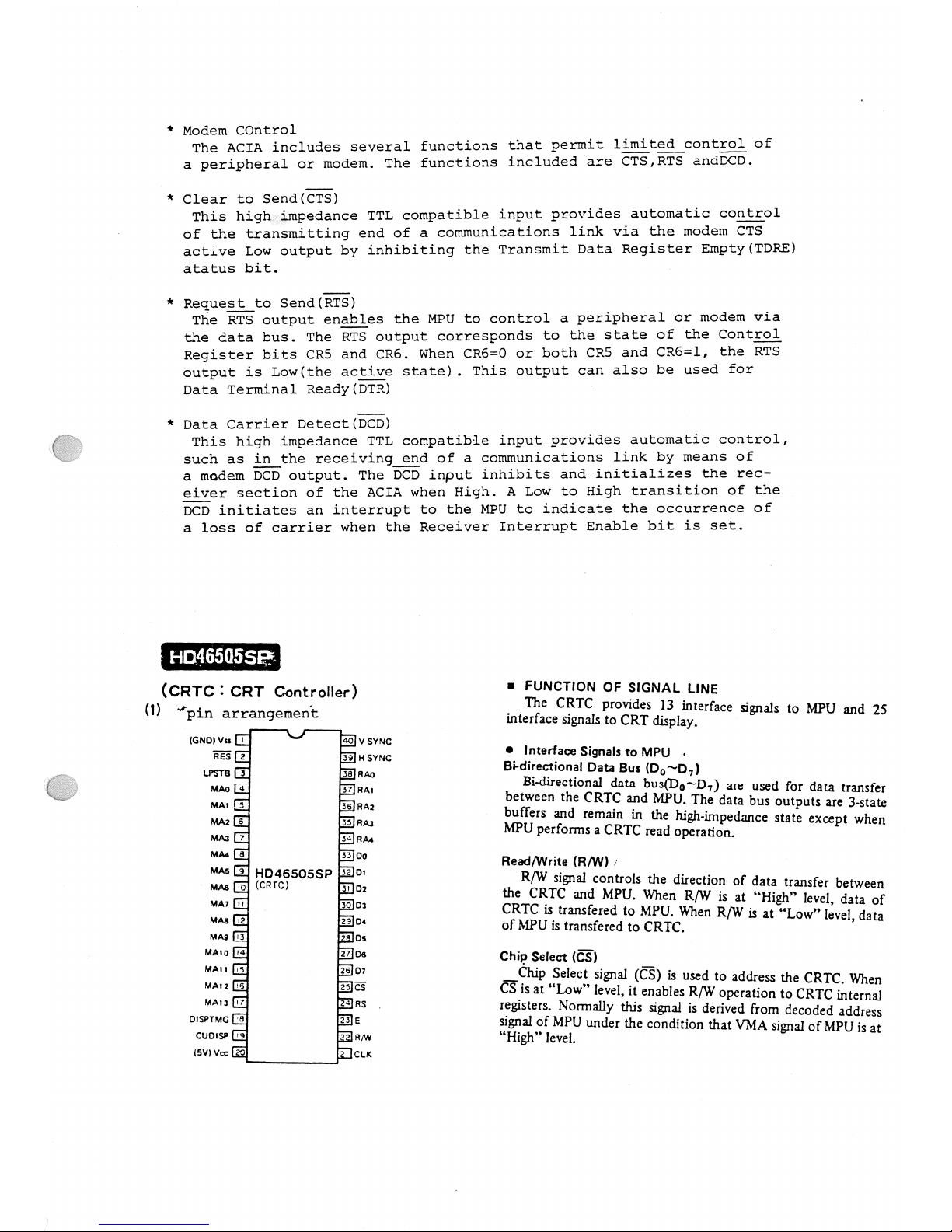

(U

p i n

arrangement

(GND)

Vss

RES

LPSTB

MAG

MAI

MA2

A4

MAS

As

MAT

MAB

A9

MA10

MAH

MAI

2

MAI]

DISPTMG

CUDISP

(5VI

Voc

_

E

E-E

HD46505SP

(CRTC)

EE

v

svnc

H

svmc

nm

nm

RA2

mu

cn

oz

I

I

l

I

Ds

I

Es‘

,

l

IEE mw

Ell CLK

(CRTC

3

CRT

Controller)

ll

4

5

B

EH

MAJ

RAA

M

El

Do

E]

EE

M

IE

gn

Ill so

D3

’2

29

D4

M

Il]

as os

IB

27

S

25

D1

E as

if

z

as

23

E

I

FUNCTION

OF

SIGNAL

LINE

The

CRTC

provides

13

int

f

’

al

interface

signals

to

CRT

d i s p l a y .

ace

sign

S

to MPU

and

25

0

Interface

Signals

to

MPU

.

Bi-directional

Data

Bus

(D0~D.,)

b

t B ! ‘ d ’ e C £ I n 3 l

data

b U 5 ( D o " D 1 )

are

used

for

data

transfer

br;/een

ide

CRTC and

Ub;1PU.

The

data

bus

outputs

are

3-state

ers an

remain

in

e

high-impedance

state

exce t

when

MPU

performs

a

CRTC

read

operation.

P

Read/Write

(R/W)

/

R/W

signal

controls the

direction

of

data

transfer

between

the

CRTC

and

MPU.

When

R/W

is

at

H i g h

level,

data

of

CRTC IS

transfered

to

MPU.

When

R/W

is

at

L o w

level

data

of MPU

is

transfered

to

CRTC.

’

Chip

Select

(C_§)

_Chip

Select

signal

(CS)

is

used

to

address

the

CRTC,

When

CSIIS

at

L o w

level,

it

enables

R/W

operation

to

CRTC

inremaj

ff¢5I5i¢f5-

N o f m a u l

this

Signal

is

derived

from

decoded

address

signal

of

MPU

under the

condition

that

VMA

sigial

ot‘MPU

is

at

H i g h

level.

Page 19

Register

Select (RS)

Register

Select

signal

(RS)

is

used

to

select

the

address’

register

and

18

control

registers

of

the

CRTC.

When

RS is

at

L o w

level,

the

address

register

is

selected

and

when

RS

is

at

H i g h

level,

control

registers

are

selected.

This

signal

is

normally

a

derivative

of

the

lowest

bit

(AO)

of

MPU

address bus.

Enable(El

Enable

signal

(E)

is

used

as

strobe

signal

in

MPU

Rfw

operation

with

the

CRTC

intemal

registers.

This

signal

is

normally

a

derivative

of the

HMCSSSOO

System

95;

clock.

Reset

(lil

___

Reset

siglal

(RES)

is

an

input

signal

used

to

reset

the

CRTC.

When

RES

is

at

L o w

level,

it

forces

the CRTC

into

the

following

status.

~

_ _ _ _ _

1)

All

the

counters

in

the

CRTC

are

cleared

and

the

device

stops

the

display

operation.

2)

All

the

outputs

go

down

to

L o w

level;

3)

Control

registers

in

the

CRTC

are

not

affected

and

remain

unchanged.

This

signal

is

different

from

other

HMCS6800

family

LSls

in the

following

functions

and

has

restrictions

for

usage.

1)

RES

signal

has

capability

of

reset

tiinction

only

when

LPSTB

is

at

L o w

level.

2)

The

CRTC

starts

the

display

operation

immediately

after

RTS

signal

goes

H i g h " .

0

lnterfage

Signals

to CRT

Display

Device

Character

Clock.

QCLK)

CLK

is

a standard

clock

input

signal

which

defines

character

timing

for

the CRTC

display

operation.

This

signal

is

normally

derived

from

the external

high-speed

dot

timing

logic.

Horizontal

Sync (HSYNC)

HSYNC

is

an active

H i g h

level

signal

which

provides

horizontal

synchronization

for

display

device.

Vertical

Sync

NSYNC)

VSYNC

is

an

active

H i g h

level

signal

which

provides

verti-

cal

synchronization

for

display

device.

Display

Timing

(DISPTMG)

DISPTMG

is

an active

H i g h

level

signal

which defines

the

display period

in

horizontal

and vertical

raster

scanning.

It is

necessary

to enable

video

signal

only

when

DISPTMG

is

at

l ’ l i g h "

level.

Refresh

Memory

Address

(MA0~MA13)

_

MA0~MA,,

are refresh

memory

address

signals

which are

used

to access

to refresh

memory

in order

to refresh

the CRT

screen

periodically.

These

outputs

enables 16k

words

max.

refresh

memory

access.

So,

for

instance,

these are

applicable

up

to

2000

characters/screen

and

8-page

system.

Raster

Address

(FlA0~RA4)

RA4,~RA.,

are

raster

address

signals

which

are used to

select

the

raster of

the character

generator

or

graphic

pattem

generator

etc.

Cursor

Display

(CUDISP)

CUDISP

is

an active

H i g h

level video

signal

which is

used

to

display

the

cursor

on the CRT screen.

’This

output

is in-

hibited

while DISPTMG

is

at l o w

level.

Normally

this

output

is mixed

with

video

signal

and

provided

to the

CRT

display

device.

Light_Pen

Strobe

(LPSTB)

LPSTB

is

an

active

H i g h

level

input

signal

which

accepts

strobe

pulse

detected

by

the

light pen

and control

circuit.

When

this

signal

is

activated,

the

refresh

memory

address

(MA,,~

MAH)

which

are shown

in

Fig.

2 are

stored

in

the

14-bit

light

pen

register.

The

stored

refresh

memory

address need

to be

corrected

in

software,

taking

the

delay

time

of

the

display

device,

light

pen,

and

light

pen

control

circuits

into account.

(16,384

BIT

DYNAMIC RAM)

’iff’ 255;

Dan

Ag

A,

A.

A,

H

*

Direct

access

of

l6l

memory by

7

E

El

E

lj

B

address

line(A6~A6)

can

not

be

done.

For

that

reason,

select

one

line

in

2

=l28

under

RAS

mode,

then

select

one

row

from

2 =l23 under

CAS

mode.

I

E] E1

E)

B

thus_select

one

from

l28xl28=l6,384

vu_o___

Dm

wg

nag

A0 A;

A

__\;o_c:

COlllblI’lB.l11Ol.’l..

U...

.....

galqrnw

*

The

corresponding

state

of

each

signal

Dom

-»-Dave OovWY

N>A6~

E"-Wf’9?11

El\UDl9’

FMS

--~~#

Fon Amress Seleul

U3--~Cc|um

Address

Selecn

pin

is as

follows;

RAS...

Low

level;

line

selection

mode

CAS...

Low

level;

row

selection

mode

’V~lE_..

Low

level;

write

mode,

the

data

from

D.

is written

in

RAM.

High

level..

read

mode,

the

data

from

l i l - I M

is read

through

D

out

Page 20

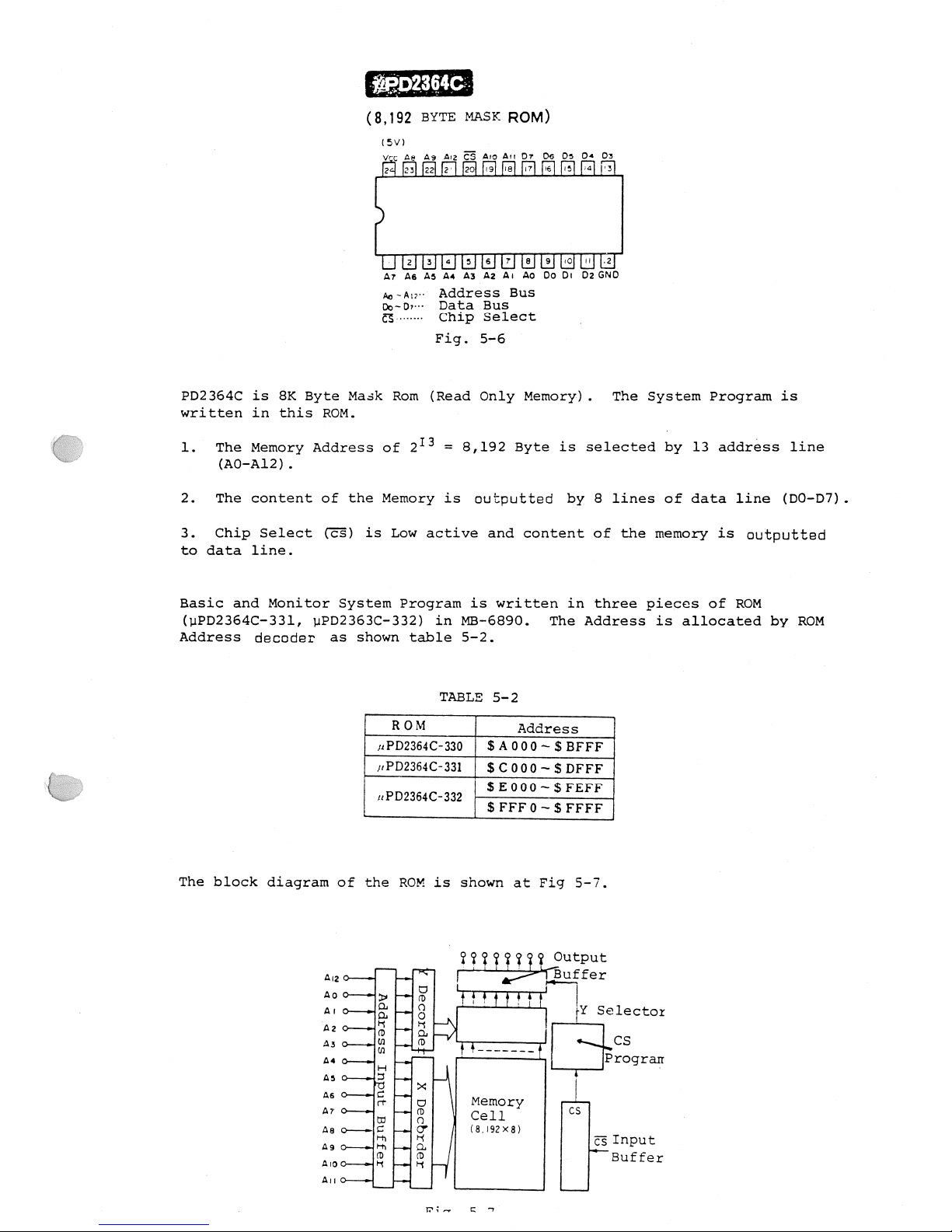

(8,\92

BYTE

MASK

Rom)

(5v)

V.-C

A9

A9 Aszgmo

Arr D1 D6 D5

D4 D3

& @BE B

BBEBB BEBN

I

Ar As A5

A4

A3 A2

An

Ao Do Du Oz

GND

A.»~Aw-»

Address

Bus

m~D~-

Data Bus _

----- ChipSelect

-----

Chip

Select

Fig.

5-6

PD2364C

is

SK

Byte

Mask Rom

(Read

Only Memory)

_ The

System Program

is

written in this

ROM.

I3

8 192 B te is selected

by

13

address

line

1. The

Memory

Address

of

2

=

,

y

(AO-Al2)

.

2. The content of the

Memory

is

outputted

by

8 lines of data line

(DO-D7)

3.

Chip

Select

(EE)

is Low

active and content of the

memory

is

outputted

to data line .

Basic and Monitor

System

Program

is

written

in

three

pieces

of ROM

(uPD2364C-331, pPD2363C-332)

in

MB-6890. The Address is

allocated

by

ROM

Address

decoder

as shown

table 5-2.

TABLE

5-2

R OM

I

Address

/1PD2se4c-aao

|

$

A

oo

o

~

s BFFF

,,PDz3e4c-331

1

s

c

ooo

~

s n1=z=1=

i »~ v- ~ - -

A

--Q-QQ

u P D 2 3 6 4 C 3 3 2

L"UU

5

bb"

s

FFF

o

~

s

FFFF

The block

diagram

of the ROM is shown

at

Fiq

5-7.

212

Output

M2

Buffer

A0

->

3

1

A»

o-Ag

_.Q

YY

Selector

A2

o-+3

-.

3.

A5

o-_~$

_.L_f1D_

_______

CS

M

Q_..H

_.r-’

PrOqra;r

A5

S33

_>

A6

fi

E;

Memory

A

AT

m 3

CS

Aao->C.’

_>O’

(8,l92>

A9

_.’S2

__

E1

5

P W C

.. O_.2

,Q

Buffer

\

A||;¢-L

i.._..¥

¥7§~

E

-1

Page 21

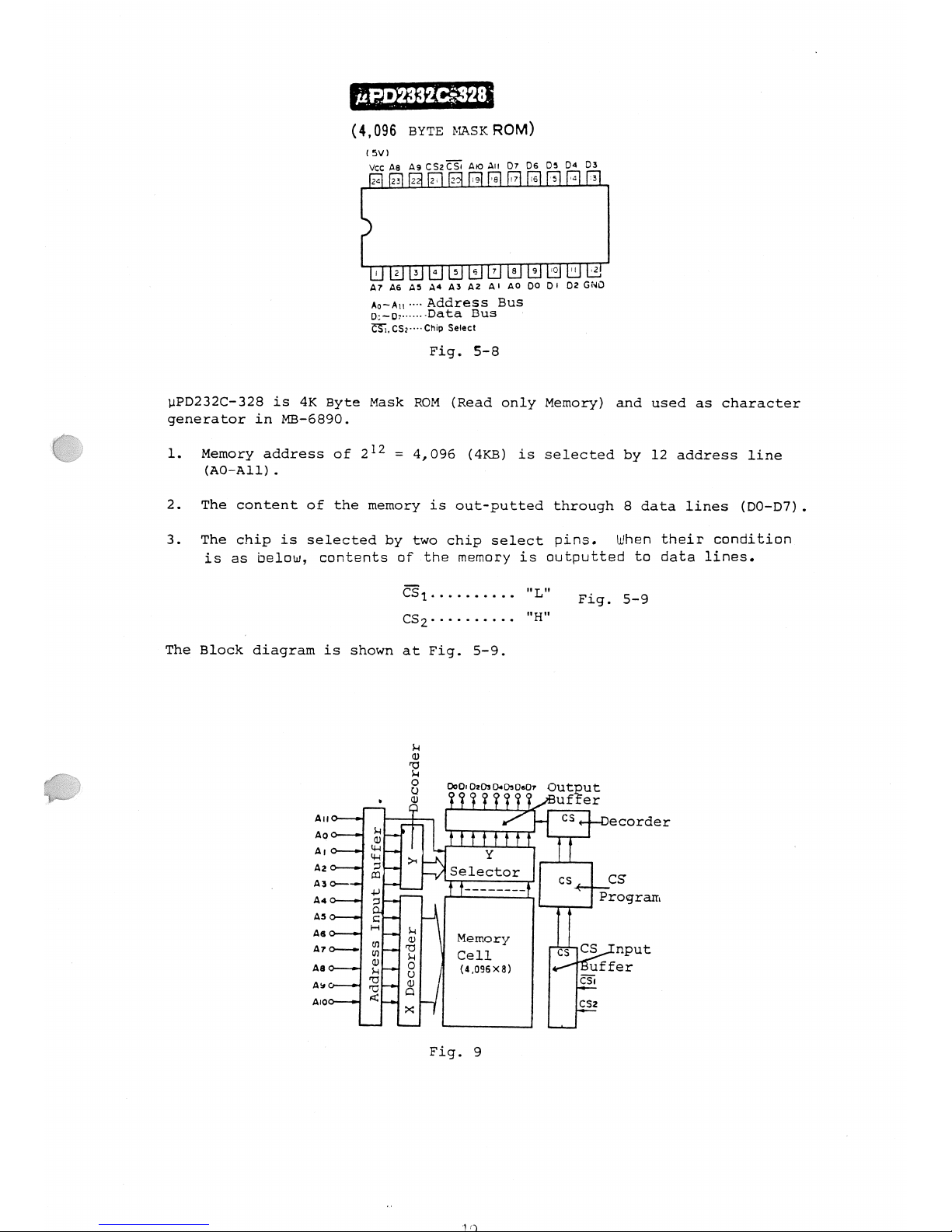

’igl?Q2332C»§328,§,

(4,096

BYTE

MASK

Rom)

:sw

v¢¢Ae

Ae

CSZEEE

Ao

Au

D1

os os

O4

os

EER E !

I B E EIEEU

A7

As

A5

A4 A5 AZ

Au

AO

D0

D’ DZGNU

M _ A

-~~-

Address

Bus

m_g,

......

.Data Bus

f5T.CSz

---~

Chip

Select

Fig.

5-8

uPD232C-328

is

4K

Byte

Mask

ROM

(Read

only

Memory)

and used

as character

generator

in M -6890.

1.

Memory

address of

212

=

4,096

(4KB)

is

selected

by

12

address

line

(A0=All}.

2.

The content of the

memory

is

out-putted

through

8

data lines

(DO-D7)

Fig.

9

1

1]

Page 22

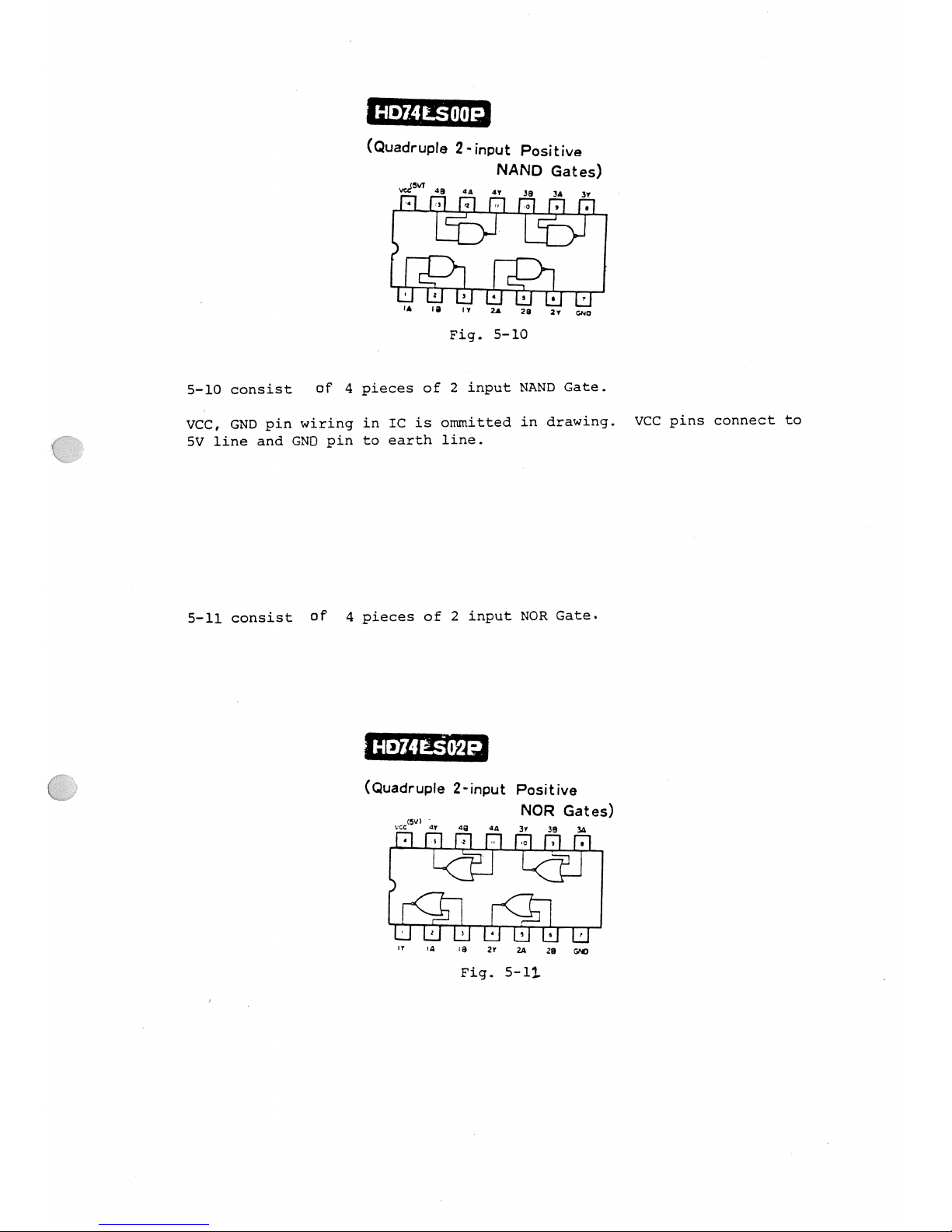

HDZQEQS

OUP

(Quadfllpfe

2‘i|’1DUt

Positive

NAND

Gates)

WØsw

B dA

Av

33

3,

3,

U

U

U

I

B

U

I

" "

’

E-1

*h

’

l’_

nnuunn

’lilvugeavgns

Fig.

5-10

5-10 consist

of 4

pieces

of

2

input

NAND

Gate.

VCC,

GND

pin

wiring

in IC

is omitted

in

drawing.

VCC

pins

connect

to

SV

line and GND

pin

to earth

line.

5-11

consist

of

4

pieces

of

2

input

NOR

Gate.

(Quadrupie

2-input

positive

)

_

NOR

Gates)

vcc(5V

av

ag 4,

3,

Ja M

.,‘, ,¢)_

QTQT

ii

u

»

v

PA

|g 21

25

Gm

Fig.

5-11

Page 23

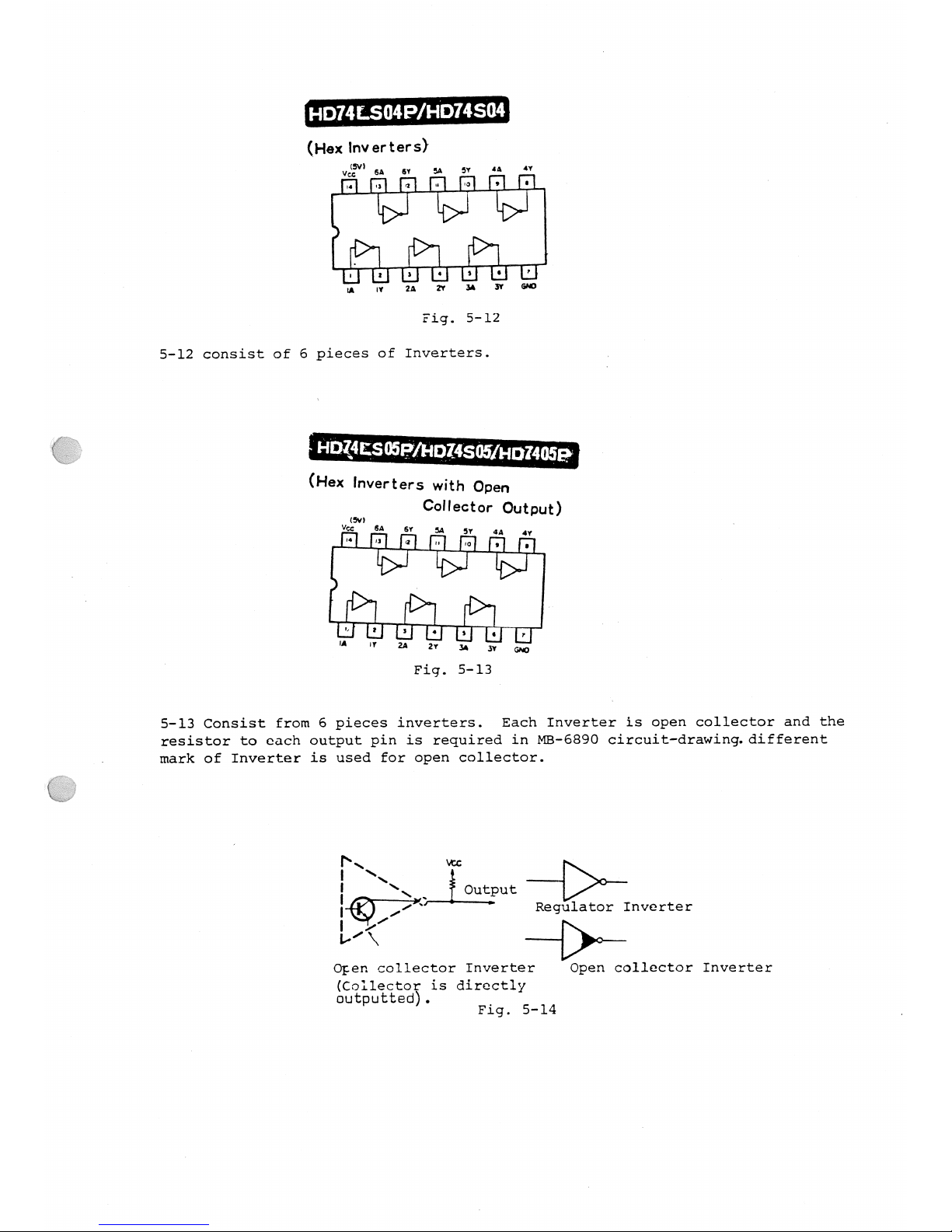

Hn74r.su4e/HD14su4

(Hex

Inv

er

ter

S)

s v

GA

sv

5A

5V

ll

V

I

ll

ll

li

ll

ll

P>

P*

I

Vcc

m

P’

P’

P’

ll

’H’

Fig.

5-12

5-12 consist

of

6

pieces

of

Inverters.

HDl4ES05E/HDZ4s05/Hnz4o5g

(Hex

Inverters

with

Open

CoHector

Output)

(sw

vc:

SA

51

54

5’

A

Y

5|

lF.’§l

II

IH

ll

ll

>

"

’F

li

li

u

II

II

I

IA

nv

Fig.

5-13

5-13 consist

from

6

pieces

inverters.

Each Inverter

is

open

collector and

the

resistor

to

each

output

pin

is

required

in MB-6890

circuit-drawing.different

mark

of Inverter

is

used for

open

collector.

"\

WDC

I

‘\\

:

\\

_

Output

|

/»"

Regulator

Inverter

|

//

v"\

Open

collector

Inverter

Open

collector

Inverter

(Collector

is

directly

outputted).

Fig.

5-14

Page 24

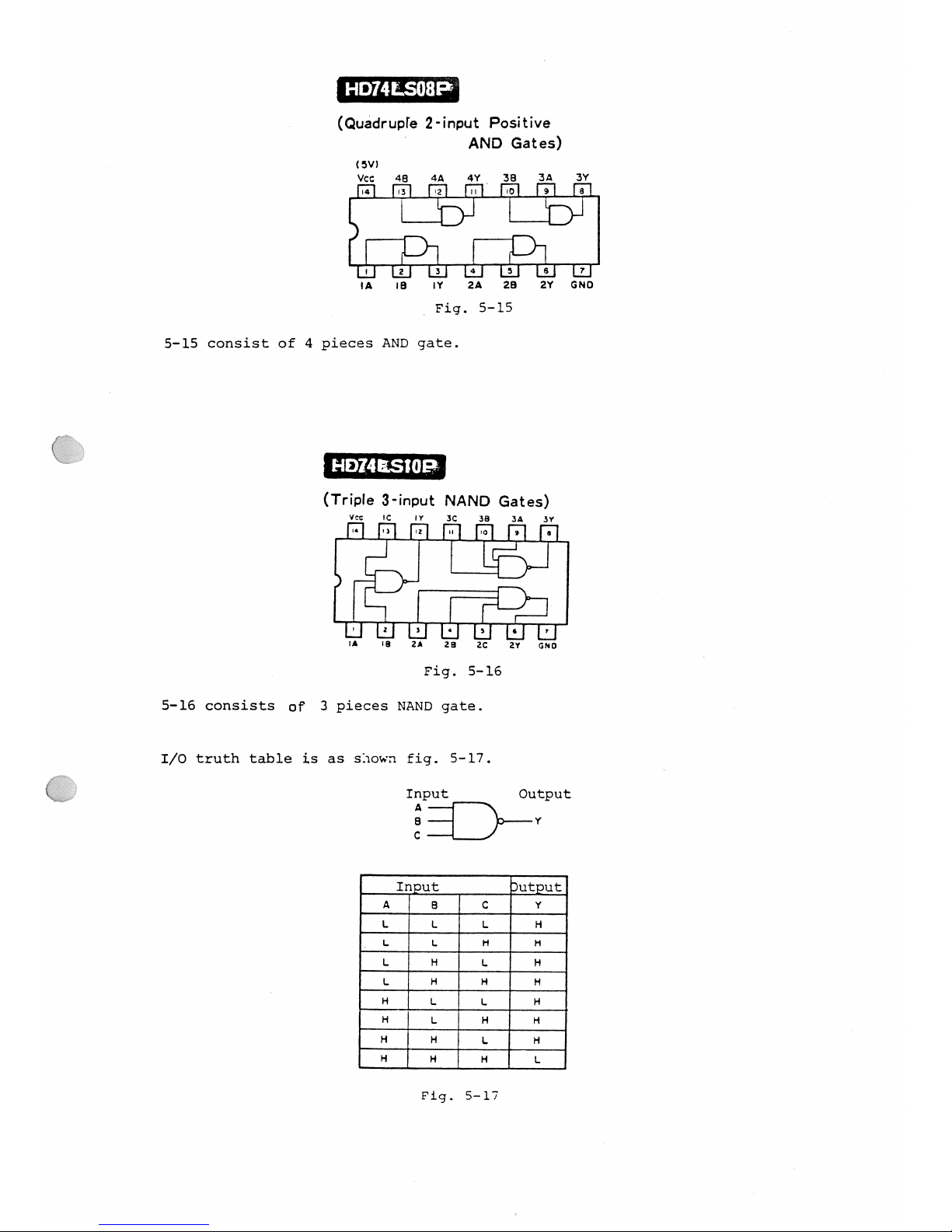

HD74l;S08F¥‘

(Quedrupfe

2-input

Positive

A

AND

Gates)

(svn

vc:

45

4A

avg

BB

BA sv

ml ’»3|

12

II

IO

9 a

§¢;

4

5

s

U:

IA IB

IY 2A

28 ZY GND

Fig.

5-15

5-15

consist of

4

pieces

AND

gate.

(Triple

3-input

NAND

Gates)

ve:

IC IY

_Sc

38

IA

5v

14|

I)

12 1|

ro

9

3

W’

I

l

1

S

V

C

I

7

ll

IB ZA

ZS

2C

ZY

GND

Fig.

S-16

5-16

consists

gf

3

pieces

NAND

gate.

I/O

truth table

is

as

shown

fig.

S-17.

Input

Output

Q

Y

c

In

ut

utput

V A p B l C

Y

L}L

L H

.LIL

H H

L|H|L

H

L H

\

H

H

HLIL

H

:HTL

H

H

HlH|L

H

HIHIH

L

Fin; 5-11

U

Page 25

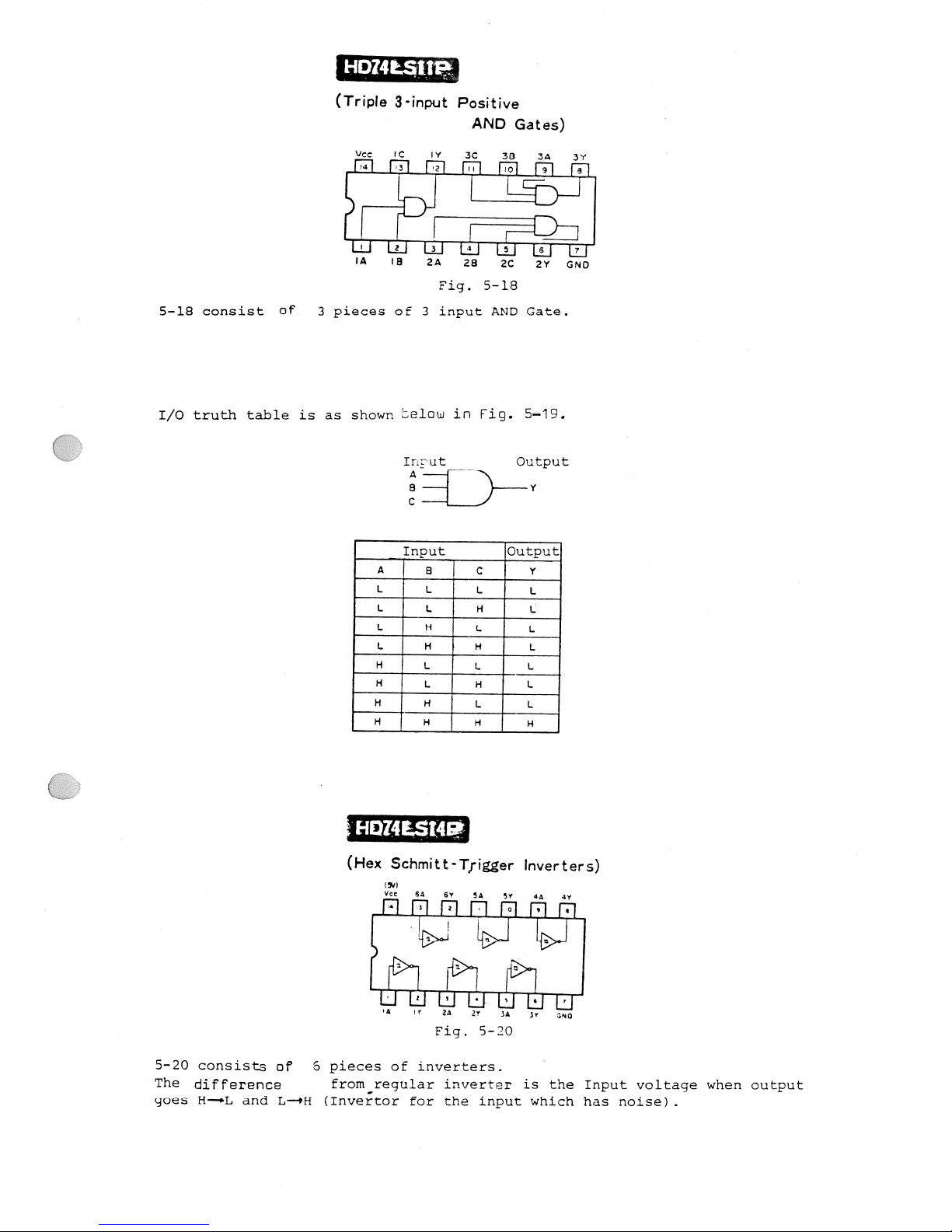

H’5?14¢$;l¥F§,.

(Triple

3

-input

Positive

g

H

L

L

L

AND

Gates)

Vcc IC IY

3C

38

V;/A

3Y

gal

II?

Ed

I

’

Lil

»

’I

2

~1

5

Is[’Ir

IA

IB

ZA

za

2C

2Y

GND

Fig.

5-18

5-18

consist

QF

3

pieces

of 3

input

AND

Gate.

I/O

truth table is

as shown

below

in

Fiq-

5-19-

Input Output

A

____

B Y

C

_

lnput

Output

I

A

I

a

c Y

L

I

L

I

L

L

L

L H

L

I

L H

L

L

L

I

H

H

L

H

H

l.

L

H

H

H

H

I

I

H

L

I

H L

I

I

(Hex

Schnutt-TjiggerInverters)

ISI)

Vcc

SA

SY

SA

5v

4,5

,gy

,I

,

Ii

I

I

I

I

I

I

I

I

’l

If

ZA

ZY

BA

Sv

Quo

Fig.

5-20

5-20

consists

of

5

pieces

of inverters.

The

diffgpengg

from

regular

inverter

is

the

Input

voltage

when

output

goes

H-#L

and

L-#H

(Inverter

for the

input

which has

noise).

Page 26

REQUl@f

Inverter

Trigger

Inverter

4

3

Regular

Inverter

2

Schmitt Trigger

Inverter

4

o

-r---

oas

u L5

5-2|

Input

(HD74LS|4P)

I

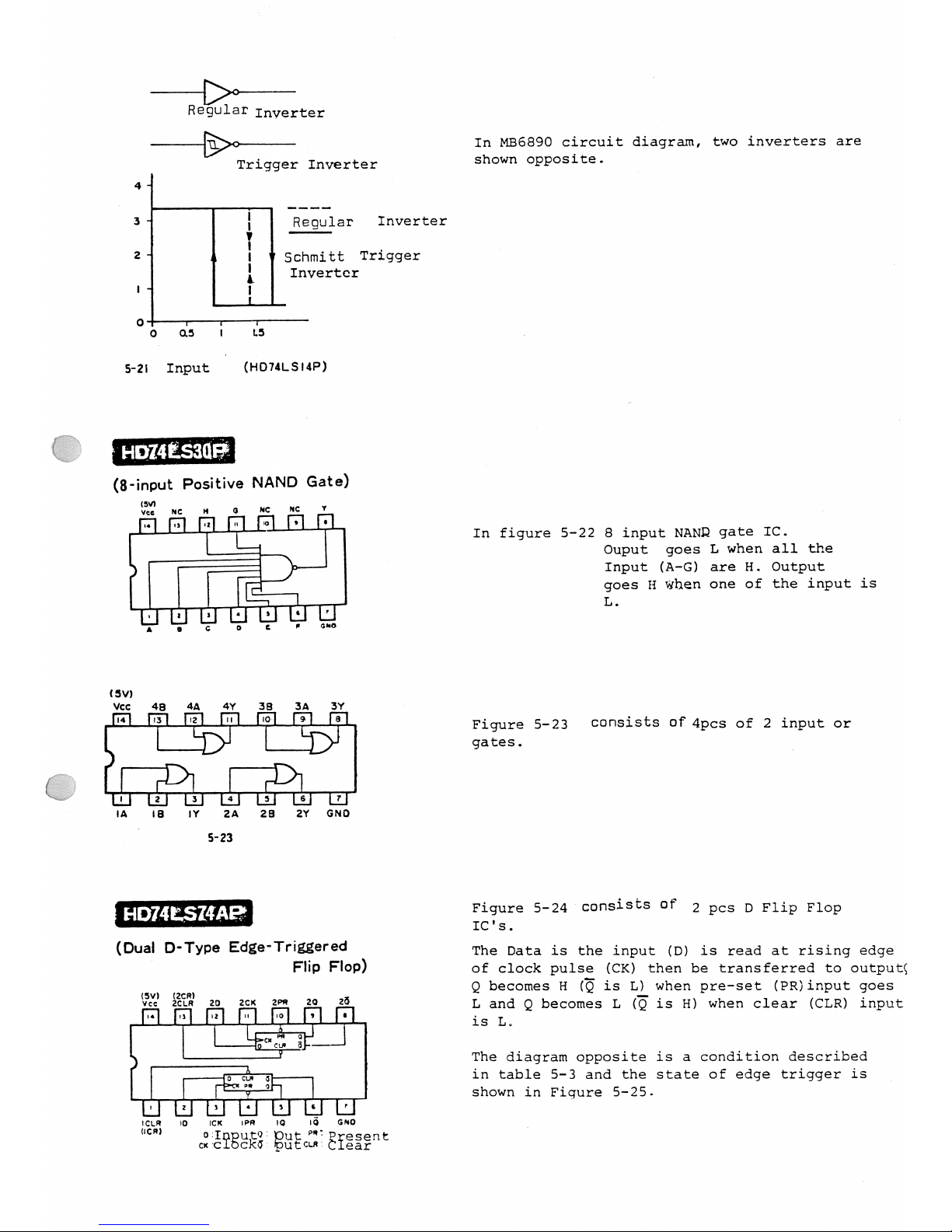

HDZ4ES3d§

(8-input

Positive

NAND Gate)

NC

pq

0

NC

NC

V

I

ll

D

I

I

ll

’il

K

GND

(SV)

VCC

4B

4A 4Y 38

3A 3Y

un

as nz

Il

IO

9 B

f ‘ i D 1 | i D 1

V!7\

Hn Hnnfr’

’TH V415|"f\

IA

ua

nv za aa av

cnc

’

s-23

E-lDT4|i$I4AE§

(Dual

D-Type

Edge-Triggered

Flip

Flop)

(SV) IZCR)

vee ZCLR

20

2c><

zvn

20

26

M’

.;

|;

ni

|o

9 |

cx ’f

cuvu

E I

li!

. ;

’.;J

*.;.’

’ . ; f ’ . ; i L ; . V

C33§T8E1%§:

$3527

EYSEEM

In

MB689O

circuit

diagram,

two inverters

are

shown

opposite.

In

figure

5-22 8

input

NAND

gate

IC.

Ouput goes

L

when all the

Input

(A-G)

are

H.

Output

goes

H when

one of the

input

is

L.

Figure

5-23

CUf"SiS’CS

of

4pcs

of 2

input

or

gates.

Figure

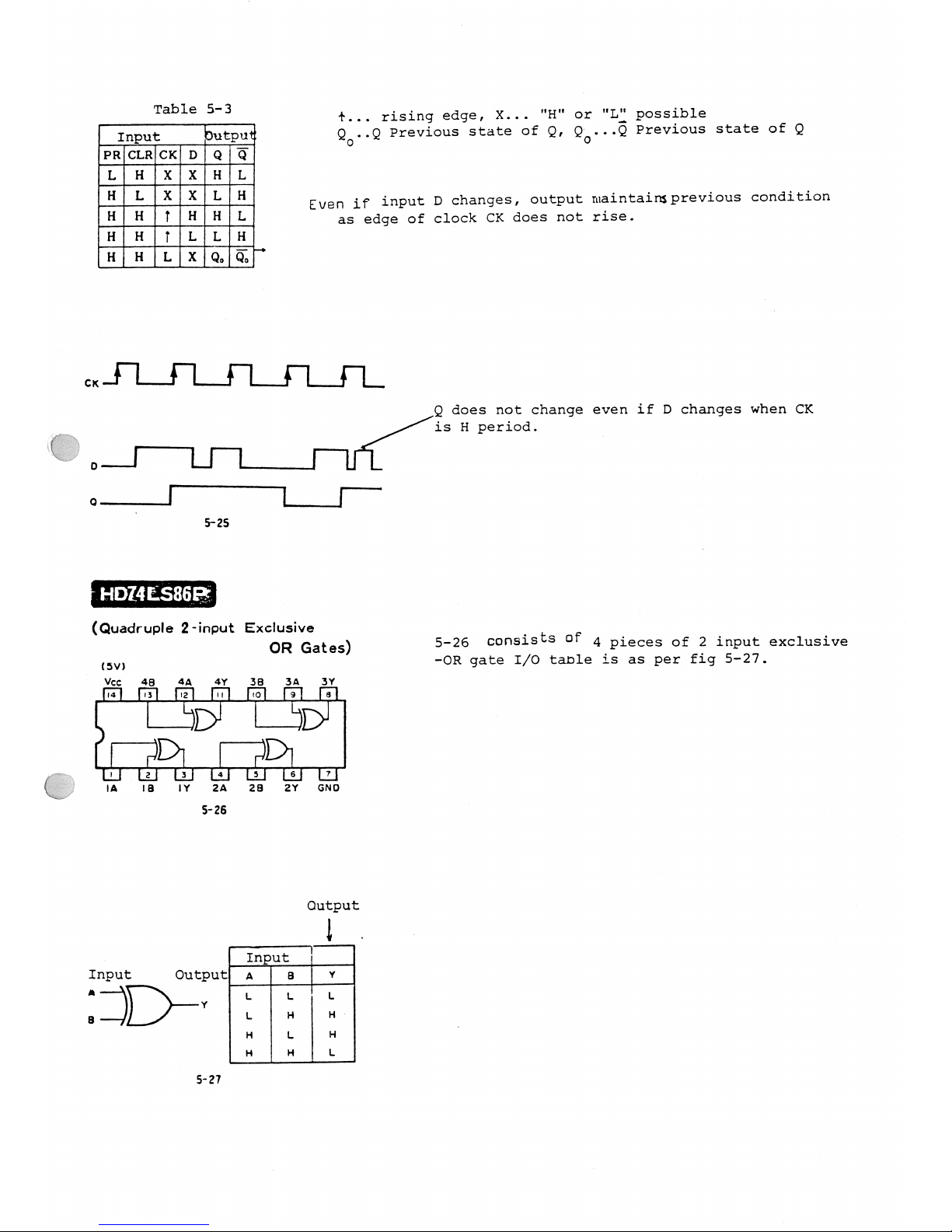

5-24

CDl’1Si5t5

of

2

pcs

D

Flip Flop

IC’s.

The Data

is

the

input

(D)

is

read

at

rising edge

then be

transferred

to

output;

when

pre-set

(PR)input goes

of

clock

pulse

(CK)

Q

becomes

H

(§

is

L)

L

and

Q

becomes

L

(5

is

H)

when

clear

(CLR)

input

is

L.

The

diagram

opposite

is a condition described

in

table

5-3

and

the state of

edge

trigger

is

shown in

Figure

5-25.

Page 27

Table

5-3

EB IEIEIEI

EI III

I I I

I

l=

L

IEIIEI

LL

IIIIII

l1llIl

IIIIEI-B

Q~»

E

H

+I

H

H

+L

rising

edge,

X...

"H" or

"L"

possible

+...

Q

..Q

Previous

state

of

Q,

Qo...Q

Previous

state

of

Q

o

Even

if

input

D

changes,

output

maintainsprevious

condition

as

edge

of

clock

CK

does

not rise.

D

0

5-25

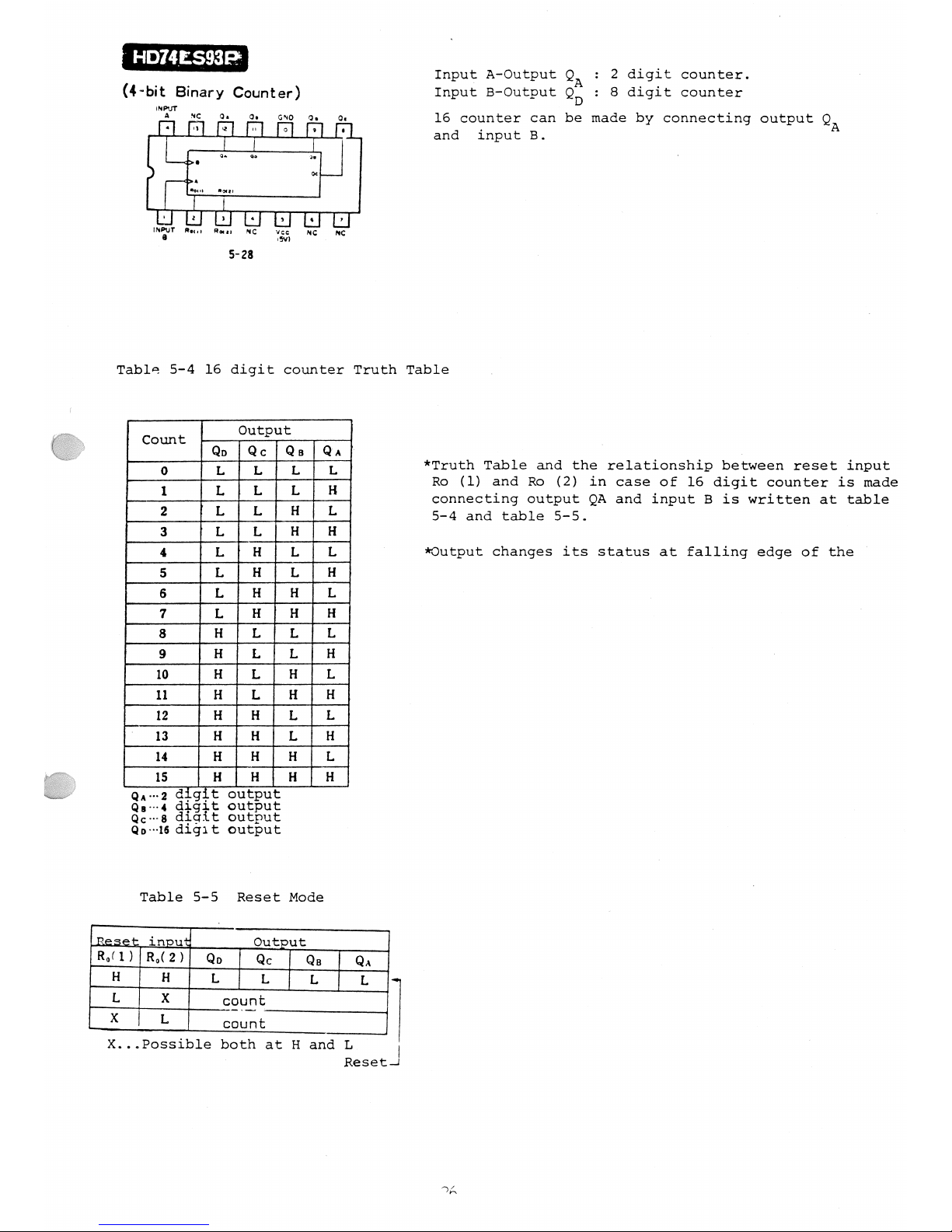

HDHESSSVEQ

(Quadruple

2-input

Exclusive

OR

Gates)

(SV)

Vcc

48

4A

4Y 38 3A

3Y

|4f

Lai

Ve;

?v|

Lo?is:

s

|

2

3

|4i

A5:

s

|1

IA

I8

IY 2A 2B ZY GND

S-25

Output

Input

Output

D D - Y

a

5-27

H

L

_

Input

|

L L

L

L

H

H~

H

L

H

H L

Q

does not

change

even if

D

changes

when CK

is H

period.

5-26

consiStS

OF

4

pieces

of 2

input

exclusive

-OR

gate

I/O

table

is as

per

fig

5-27.

Page 28

’

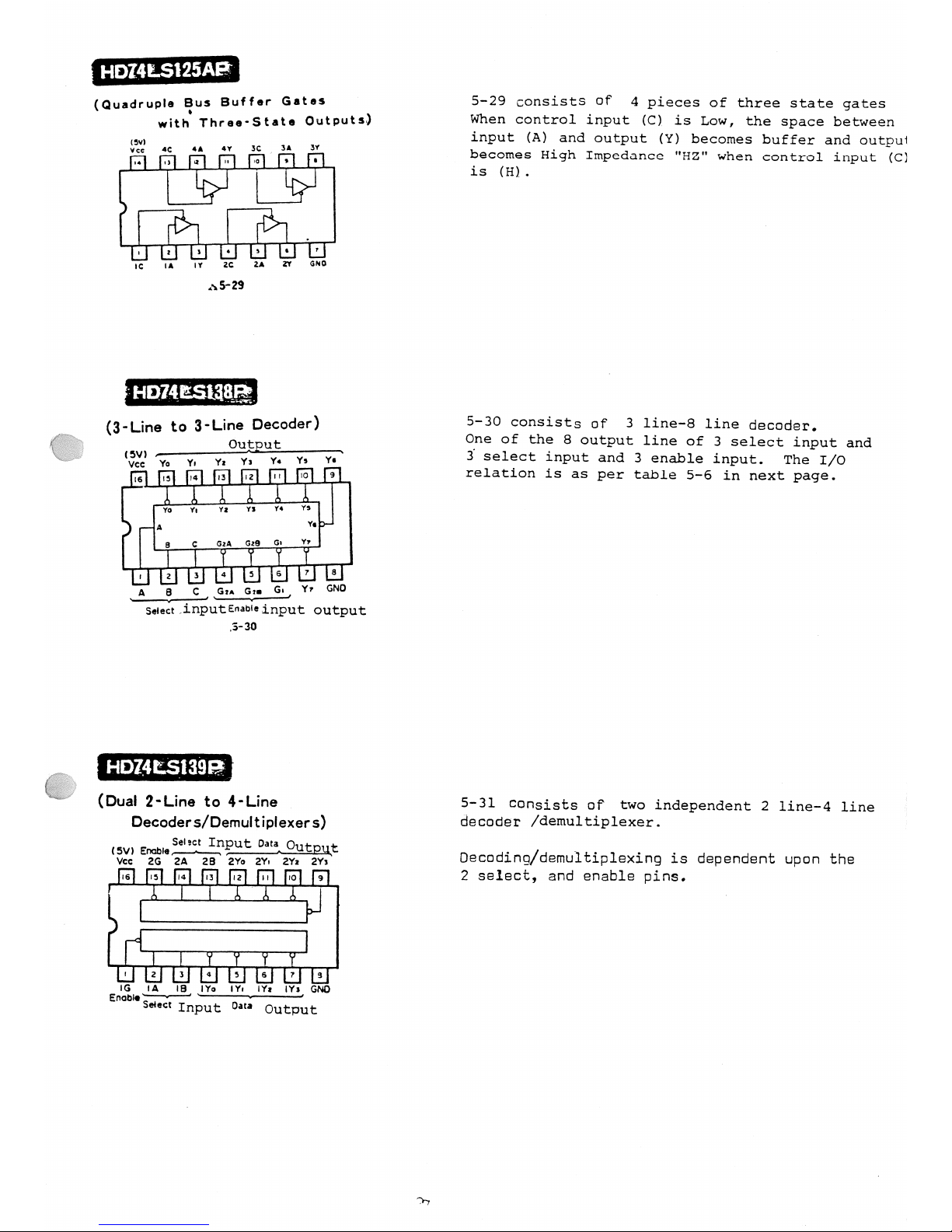

HD14IES93F!?

Input

A-Output

QA

: 2

digit

counter.

(4-mt

Bkmry

Counter)

Input

B-Output

QD

:

8

digit

counter

’NTT

0-

Gu

me

Q.

Q.

16

counter

can

be

made

by

connecting output

QA

I

n

I

B

H

and

input

B.

FQ

Q.

ua

Q.

EIIIIIIIIIIIIIIH

I

I

I

I

I

I

I

INPUT

Run

Run

NC

vcr:

NC

MQ

B

mv)

5-28

Table

5-4 16

digit

counter

Truth Table

O t

if

Cgunt

QD

Qc Qs QA

I

0

I

L

I

L

I

L

I

L

I

*Truth

Table

and

the

relationship

between

reset

input

l

1

|

L

I

L

L

H

’

Ro

(1)

and

Ro

(2)

in

case of 16

digit

counter is made

V

connecting

output

QA

and

input

B is

written at table

2

I

L L

_L

H L

5-4 and

table

5-5.

3

’

L

I

L

H H

4

1

L

I

H L

L

*Output

changes

its

status at

falling

edge

of

the

5

L

H

L

H

s L

H

H

L

L

7 L

H

I

H H

H

8

H L

H

L L

9

I

H L L

H

10

H

L

H L

H

I

H

L

H

H

I

N

12 H H L L

13

H

H L

H

14

H H H L

-

¢

H

»

H

¢

H

_

H

.

W

di it out ut

digit

outgut

Qc-_-5

digit

output

Qu~-~!5

digit output

Table 5-5 Reset

Mode

eseto

inpu

I

Out

ut

)QD’QCEIQBlQ,\

HHLILILIL

L

X

f=9vQt

count

R f1>IR

x

I

L

I

X...Possible both at H

and

I

Reset_1

’TQ

Page 29

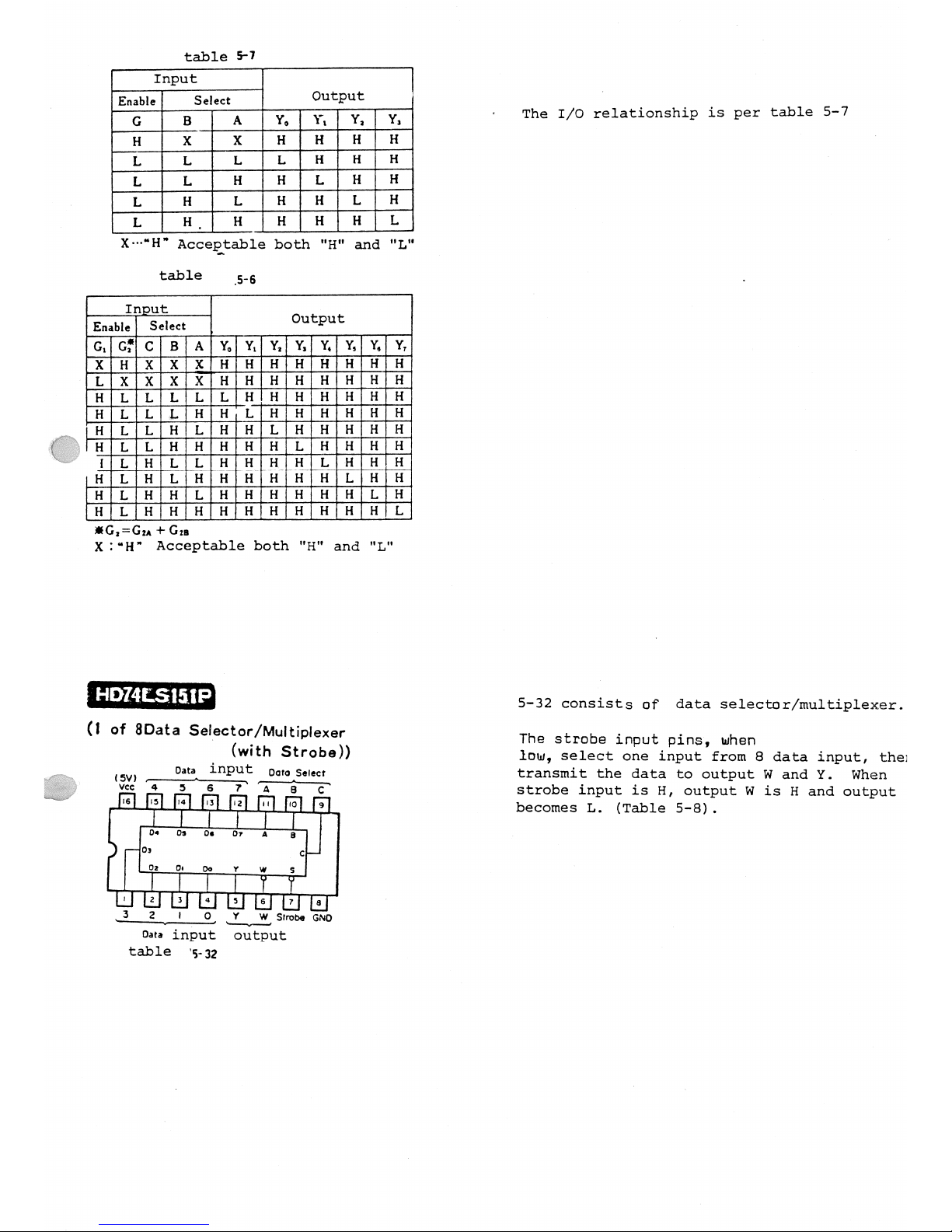

I-lDZ4E.S\

ZSAEP

(Quadruple

Bus

Buffer

Gates

5-29

Consists

Of

4

pieces

of

three

state

gates

with.

Three-State

Outputs()

When

control

input

(C)

is

Low,

the

space

between

(M

input

(A)

and

output

(Y)

becomes

buffer and

output

V"

" 3

" 3’

becomes

High

Impedance

"HZ"

when

control

input

(C)

U

U

EH’

U

’H

is

(H).

E

>

lik

lin

I

I

I

~

I

I

I

|¢

||

IV 2C

ZA

Z7

GNU

AS-29

=HD2=lE}Sl3§§_

(3_|__ine

tc,

3-Line

Decoder)

5-30

consists of

3

line-8

line

decoder,

Ougmt

One

of

the 8

output

line

of 3

select

input

and

(sv)

,

Y _

3

select

input

and

3

enable

input.

The

I/O

v

Y

,___ c. ._

_

t- e

i

~ - - -’ ’ ’ " "

relatlon

lS as

per

table

5-6

1n

next

page.

z

GB

Q YI

Yz

Yx

Ya

Ys

E

m

I3

|

Z

I ¢

O

9

vo

vu

YI

YI

Y*

Y

A

YI

5

Yr

3

C

G

A

.

1 2

B

B

6

8

A B

C

Gu

Gil

G*

Y’

GND

sem:

"input

Enabw

input

output

.3-30

Hnz-msiaseir

(Dual

2~Line to

4-Line

5-31

COF¢sists of

two

independent

2

line-4

line

Decoders/Demultiplexers)

GGCOUSP

/

Select

Input

D

t

Q

_

E ’ § § ’ ’ § ’ j § t

Decoding/demultiplexing

is

dependent

upon

the

,S

m

,4

,,

.2

,.

.O

9

2

select,

and

enable

pins.

IG IA

IB |Yu |Y| |Yz

lY|

GND

Enable?

ect

Input

Dan

Output

7"v

Page 30

table

5’7

Input

Enable

Select

Output

G

B

A

Y,

Y.I

Y,

I

Y,

H

x

x

H

H

H