Page 1

SERVICE MANUAL

MANUEL D'ENTRETIEN

WARTUNGSHANDBUCH

CAUTION:

Before servicing this chassis, it is important that the service technician read the “Safety

Precautions” and “Product Safety Notices” in this service manual.

No. 0153

HTDK170E

HTDK170EUK

Data contained within this Service

manual is subject to alteration for

improvement.

ATTENTION:

Avant d’effectuer l’entretien du châassis, le technicien doit lire les «Précautions de sécurité»

et les «Notices de sécurité du produit» présentés dans le présent manuel.

VORSICHT:

Vor Öffnen des Gehäuses hat der Service-Ingenieur die „Sicherheitshinweise“ und „Hinweise

zur Produktsicherheit“ in diesem Wartungshandbuch zu lesen.

Les données fournies dans le présent

manuel d’entretien peuvent faire l’objet

de modifications en vue de perfectionner

le produit.

Die in diesem Wartungshandbuch

enthaltenen Spezifikationen können sich

zwecks Verbesserungen ändern.

SPECIFICATIONS AND PARTS ARE SUBJECT TO CHANGE FOR IMPROVEMENT

DVD DIGITAL THEATRE SYSTEM

July 2003

Page 2

1. GENERAL DESCRIPTION

1.1 ES60X8

The ES6008/ES6018 Vibratto DVD processor is a single-chip MPEG video decoding chip

that integrates audio/video stream data processing, TV encoder, four video DACs with

Macrovision. copy protection, DVD system navigation, system control and housekeeping

functions.

The Vibratto DVD processor is built on the ESS proprietary dual CPU Programmable

Multimedia Processor (PMP) core consists of 32-bit RISC and 64-bit DSP processors and offers

the best DVD feature set.

These features can be listed as follows:

General Features:

• Single-chip DVD processor based on ESS proprietary dual CPU PMP core.

• Integrated NTSC/PAL encoder.

• Four integrated 10-bit video DACs.

• DVD-Video, VCD 1.1, 2.0, and SVCD

• Interface for ATAPI devices and A/V DVD loaders.

• Interface for Compact Flash, Memory Stick and SmartMedia cards.

• Direct interface of 8- or 16-bit SDRAM up to 128-Mb capacity.

• Direct interface for up to four banks of 8-/16-bit EPROM or Flash EPROM for up to 16-MB

capacity.

Video Related Features:

• Macrovision 7.1 for NTSC/PAL interlaced video.

• Simultaneous composite video and S-video outputs, or composite and YUV outputs, or

composite and RGB outputs.

• 8-bit CCIR 601 YUV 4:2:2 output.

• On-Screen Display (OSD) controller with 3-bit blending provides display with 256 colors in 8

degrees of transparency.

• Subpicture Unit (SPU) decoder supports karaoke lyric, subtitles, and EIA-608 compliant Line

21 Captioning.

Audio Related Features:

• Dolby Digital (AC-3) and Dolby Pro Logic.

2

Page 3

• High-Definition Compatible Digital. (HDCD) decoding.

• Dolby Digital Class A and HDCD certified.

• CD-DA.

• MP3.

1.2 MEMORY

1.2.1 System SRAM Interface

The system SRAM interface controls access to optional external SRAM, which can be

used for RISC code, stack, and data. The SRAM bus supports four independent address spaces,

each having programmable bus width and wait states. The interface can support not only SRAM,

ROM/EPROM and memory-mapped I/O ports for standalone applications are also supported.

1.2.2 DRAM Memory Interface

The Vibratto provides a glueless 16-bit interface to DRAM memory devices used as video

memory for a DVD player. The maximum amount of memory supported is 16 MB of Synchronous

DRAM (SDRAM). The memory interface is configurable in depth to support 128-Mb addressing.

The memory interface controls access to both external SDRAM or EDO memories, which can be

the sole unified external read/write memory acting as program and data memory as well as

various decoding and display buffers.

1.3 DRIVE INTERFACES

The Vibratto supports the AT Attachment Packet Interface (ATAPI), Integrated Drive

Electronics (IDE), and other parallel and serial port interfaces used by many types of DVD

loaders. These interfaces meet the specifications of many DVD loader manufacturers. An ATAPI

drive is connected via the standard 34 pin dual row PC style IDE header

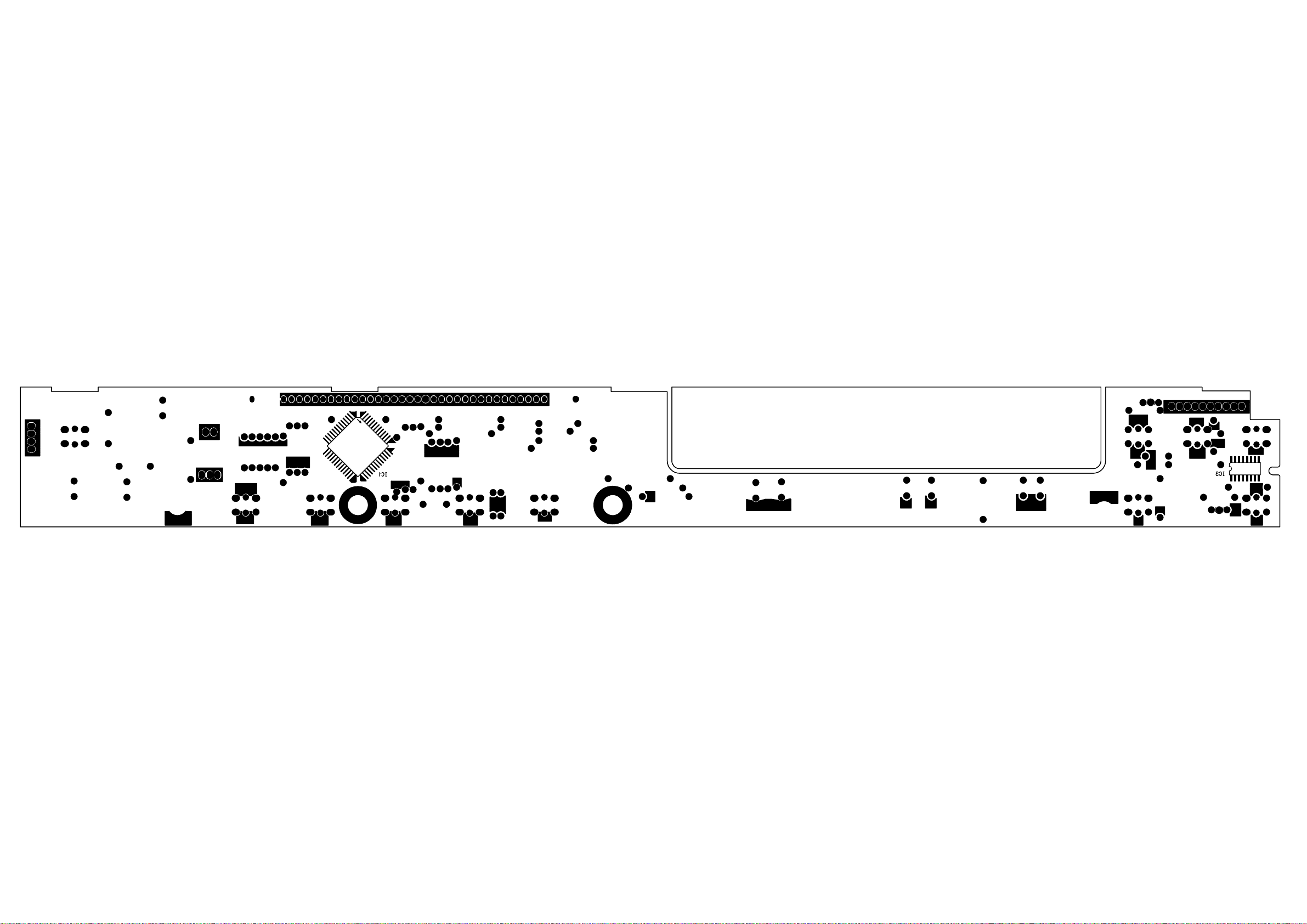

1.4 FRONT PANEL

The front panel is based around an Futaba VFD and a common NEC front panel

controller chip, (uPD16311). The ES6008/ES6018 controls the uPD16311 using several control

signals, (clock, data, chip select). The infrared remote control signal is passed directly to the

ES60X8 and 8051 for decoding.

1.5 REAR PANEL

Outputs and Inputs at the AV1000 rear panel:

- Left, Right and Subwoofer (active) audio outputs.

- Left, Right and CVBS input.

- Composite, S-Video, and SCART outputs.

- Input SCART

- 5x15W 8ohms (L,R,SL,SR,C) + 1x25W 4ohms Subwoofer outputs.

- AM / FM Tuner Antenna input

- 220-240 V 50Hz AC Power input

The six-video signals used to provide CVBS, S-Video, and RGB are generated by the ES60X8’s

internal video DAC. The video signals are buffered by external circuitry.

Six channel audio output by the ES6018 in the form of three I2S (or similar) data streams. The

S/PDIF serial stream is also generated by the ES60X8 output by the rear panel. A six channel

audio DAC (AK4356) are used for six channel audio output with ES6018, and similarly one

AK4362A Audio DAC is used for two channel audio output with ES6008 or ES6018.

3

Page 4

2. SYSTEM BLOCK DIAGRAM and ES6008/18 PIN DESCRIPTION

2.1 ES6008/18 PIN DESCRIPTION

4

Page 5

5

Page 6

678910

Page 7

Page 8

Page 9

Page 10

2.1 SYSTEM BLOCK DIAGRAM

System block diagram is shown in the following figure:

3. AUDIO OUTPUT

The ES6008 supports two-channel analog audio output while ES6018 supports six-channel

analog audio output. In a system configuration with six analog outputs, the front left and right

channels can be configured to provide the stereo (2 channel) outputs and Dolby Surround, or the

left and right front channels for a 5.1 channel surround system.

The ES6008 also provides digital output in S/PDIF format. The board supports both optical and

coaxial S/PDIF outputs.

AV1000 Has also 5.1 channel Class-D amplifier outputs to 8 ohms satelites and 4 ohms

subwoofer.

4 AUDIO DACS

The ES6008/18 supports several variations of an I2S type bus, varying the order of the data bits

(leading or no leading zero bit, left or right alignment within frame, and MSB or LSB first) is

possible using the ES6008/18 internal configuration registers. The I2S format uses four stereo

data lines and three clock lines. The I2S data and clock lines can be connected directly to one or

more audio DAC to generate analog audio output.

The two-channel DAC is an AKM AK4382A. The DACs support up to 192kHz sampling rate.

The outputs of the DACs are differential, not single ended so a buffering circuit is required. The

buffer circuits use National LM833 op-amps to perform the low-pass filtering and the buffering.

Page 11

5 VIDEO INTERFACE

5.1 Video Display Output

The video output section controls the transfer of video frames stored in memory to the internal TV

encoder of the Vibratto. The output section consists of a programmable CRT controller capable of

operating either in Master or Slave mode.

The video output section features internal line buffers which allow the outgoing luminance and

chrominance data to match the internal clock rates with external pixel clock rates, easily

facilitating YUV4: 2:2 to YUV4: 2:0 component and sample conversion. A polyphase filter

achieves arbitrary horizontal decimation and interpolation.

Video Bus

The video bus has 8 YUV data pins that transfer luminance and chrominance (YUV) pixels in

CCIR601 pixel format (4:2:2). In this format, there are half as many chrominance (U or V) pixels

per line as luminance (Y) pixels; there are as many chrominance lines as luminance.

Video Post-Processing

The Vibratto video post-processing circuitry provides support for the color conversion, scaling,

and filtering functions through a combination of special hardware and software. Horizontal upsampling and filtering is done with a programmable, 7-tap polyphase filter bank for accurate

non-integer interpolations. Vertical scaling is achieved by repeating and dropping lines in

accordance with the applicable scaling ratio.

Video Timing

The video bus can be clocked either by double pixel clock and clock qualifier or by a single pixel

clock. The double clock typically is used for TV displays, the single for computer displays.

Video Interface Registers

VID_SCN_HSTART

The write-only Video Screen Horizontal Start Address register contains the 13-bit horizontal pixel

starting address of the active video display.

VID_SCN_HEND

The write-only Video Screen Horizontal End Address register contains the 13-bit horizontal pixel

ending address of the active video display.

VID_SCN_VSTART

The write-only Video Screen Vertical Start Address register contains the 13-bit vertical scan line

starting address of the active video display.

VID_SCN_VEND

The write-only Video Screen Vertical End Address register contains the 13-bit vertical scan line

ending address of the active video display.

VID_SCN_VERTIRQ

The write-only Video Screen Vertical Line Interrupt register is selectable by software and contains

the line in which a vertical interrupt will occur. Line 0 is the top of the screen, as defined by the

leading edge of the VSYNC pin. Typically, an interrupt is set either just before or just after the

active video display.

VID_SCN_HBLANK_START

The write-only Video Screen Horizontal Blanking Interval Start Address register contains the 13bit starting address of the horizontal blanking interval for the active video display.

11

Page 12

VID_SCN_HBLANK_STOP

The write-only Video Screen Horizontal Blanking Interval End Address register contains the 13-bit

ending address of the horizontal blanking stop interval for the active video display.

VID_SCN_VBLANK_START

The Video Screen Vertical Blanking Interval Start Address register contains the 13-bit starting

address of the vertical blanking interval for the active video display.

VID_SCN_VBLANK_STOP

The write-only Video Screen Vertical Blanking Interval Stop Address register contains the 13-bit

ending address of the vertical blanking stop interval for the active video display.

VID_SCN_HSYNCWIDTH

The write-only Video Screen Horizontal Sync Width Pulse register contains the 13-bit value of the

horizontal sync pulse width for the active video display. This register is needed only if sync

direction is output

VID_SCN_HSYNCPERIOD

The write-only Video Screen Horizontal Sync Period register contains the 13-bit value for the

period of the horizontal sync pulse used by the active video display. It is needed only if sync

direction is output.

VID_SCN_VSYNCPERIOD

The write-only Video Screen Video Sync Period register contains the 13-bit value for the period of

the vertical sync pulse used by the active video display. This register is needed only if sync

direction is output.

VID_SCN_VSYNCPIXEL

The write-only Video Screen Vertical Sync Pixel register defines which pixel VSYNC will change

on for the active video display. The number of pixels delayed from HSYNC that VSYNC will

change on either the rising or falling edge of VSYNC. This register is needed only if sync direction

is output

VID_SCN_VSYNCWIDTH

The write-only Video Screen Vertical Sync Pulse Width register defines the width of the 6-bit

vertical sync pulse. It is needed only if sync direction is output

VID_SCN_VERTCOUNT

The read-only Video Screen Verital Counter register contains the current line of the vertical

counter, and starts its counting at VSYNC line 0. This register is typically used for testing only.

VID_SCN_HORIZCOUNT

The read-only Video Screen Horizontal Counter register contains the current pixel of the

horizontal counter, and starts its counting at HSYNC pixel 0. This register is typically used for

testing only.

VID_SCN_COUNTER_CTL

The write-only Video Screen Counter Control register contains counter control bits for the inverted

blank sync, inverted horizontal sync, and inverted vertical sync functions. This register initializes

to 0x00 after reset.

VID_SCN_OUTPUTCNTL

The Video Screen Output Control register contains the control logic used to control the clamping

and filtering characteristics of the signal being output to the video display.

12

Page 13

VID_SCN_ITERFACECNTL

The Video Screen Interface Control register contains the control logic used to determine the

signal output characteristics to the video display.

VID_SCN_RESETS

The Video Screen Reset register contains the control logic for reset events, including the reset

pan and scan, horizontal filtering and DMA enabling functions. This register is set to 1 on reset.

VID_SCN_STATUS

The Video Screen Status register contains the status bits for the video section.

VID_SCN_OSD_HSTART

The OSD Video Screen Horizontal Start Address register contains the horizontal starting address

value for the OSD, as referenced from the active display window.

VID_SCN_OSD_HEND

The OSD Video Screen Horizontal End Address register contains the 13-bit horizontal ending

address value for the OSD, as referenced from the active video display.

VID_SCN_OSD_VSTART

The OSD Video Screen Vertical Start Address register contains the 13-bit vertical starting

address value for the OSD, as referenced from the active video display.

VID_SCN_OSD_VEND

The OSD Video Screen Vertical End Address register contains the 13-bit vertical ending address

value for the OSD, as referenced from the active video display.

VID_SCN_OSD_MISC

The OSD Video Screen Miscellaneous register contains the control logic and status bits for the

OSD controller.

VID_SCN_OSD_PALETTE

These 16 registers contain the OSD palette.

6 SDRAM MEMORY

The memory bus interface generates all the control signals to interface with external memory.

The Vibratto supports different configurations using the memory configuration bits SDCFG[1:0]

(bits 12:11), the SD8BIT bit (bit 14), and SD64M bit (bit 15) in the BUSCON_DRAM_CONTROL

register. Configurations can be implemented in many ways. The following table lists the typical

SDRAM configurations used by the Vibratto.

13

Page 14

Typical SDRAM Configurations:

The memory interface controls access to both external SDRAM or EDO memories, which can be

the sole unified external read/write memory acting as program and data memory as well as

various decoding and display buffers. At high clock speeds, the Vibratto memory bus interface

has sufficient bandwidth to support the decoding and displaying of CCIR601 resolution images at

full frame rate.

7 FLASH MEMORY

The decoder board supports AMD class Flash memories. Currently 4 configurations are

supported:

FLASH_512K_8b

FLASH_1024K_8b

FLASH_512Kx2_8b

FLASH_512Kx2_16b

The Vibratto permits both 8- and 16-bit common memory I/O accesses with a removable storage

card via the host interface.

8 SERIAL EEPROM MEMORY

An I2C serial EEPROM is used to store user configuration (i.e. language preferences,

speaker setup, etc.) and software configuration.. Industry standard EEPROM range in size from

1kbit to 256kbit and share the same IC footprint and pinout. The default device is 2kbit, 256kx 8,

SOIC8 SGS Thomson ST24C02M1 or equivalent.

14

Page 15

9 ATA/IDE LOADER INTERFACE

The host interface can directly support ATAPI devices such as DVD drives or I/O

controllers. PIO modes 0 through 4 are supported. The ATA/IDE interface can directly control two

devices through the use of the HCS1FX# and HCS3FX# signals. The ATA/IDE interface of the

Vibratto uses a command execution protocol that allows the operation of audio-CD and DVD

loaders to coexist on the same type of interface cable that most computers use for CD loaders

and hard disk drives.

Note: The decoder board supports the standard ATAPI electrical connections, but the

software protocol within the drive is not always supported according to ATAPI specifications.

Custom software may need to be developed and tested to support ATAPI drives from different

manufacturers.

10 AUDIO INTERFACE AUDIO SAMPLING RATE AND PLL COMPONENT

CONFIGURATION

The ES6008/18 Vibratto audio mode configuration is selectable, allowing it to interface

directly with low-cost audio DACs and ADCs. The audio port provides a standard I2S interface

input and output and S/PDIF (IEC958) audio output. Stereo mode is in I2S format while six

channels Dolby Digital (5.1 channel) audio output can be channeled through the S/PDIF. The

S/PDIF interface consists of a bi-phase mark encoder, which has low skew. The transmit I2S

interface supports the 128, 192, 256, 384, and 512 sampling frequency formats, where sampling

frequency Fs is usually 32 kHz, 44.1 kHz, 48 kHz, 96 kHz, or 192 kHz. The audio samples for the

I2S transmit interface can be 16, 18, 20, 24, and 32-bit samples.

For Linear PCM audio stream format, the Vibratto supports 48 kHz and 96 kHz. Dolby

Digital audio only supports 48 kHz. The ES6008/18 Vibratto incorporates a built-in programmable

analog PLL in the device architecture in order to generate a master audio clock. The MCLK pin is

for the audio DAC clock and can either be an output from or an input to the ES6008/18 Vibratto.

Audio data out (TSD) and audio frame sync (TWS) are clocked out of the Vibratto based on the

audio transmit bit clock (TBCK). Audio receive bit clock (RBCK) is used to clock in audio data in

(RSD) and audio receive frame sync (RWS).

11 FRONT PANEL

11.1 VFD CONTROLLER

The VFD controller is a NEC uPD16311. This controller is not a processor, but does

include a simple state machine which scans the VFD and reads the front panel button matrix. The

16311 also includes RAM so it can store the current state of all the VFD icons and segments.

Therefore, the 16311 need only be accessed when the VFD status changes and when the button

status is read. The ES6008/ES6018 can control this chip directly using PIO pins or can allow the

front panel PIC to control the VFD.

12 MISCELLANEOUS FUNCTIONS

12.1 RESET CIRCUITRY

Two different chips are supported to provide the power-on-reset DS1811 or AAT3520.

12.2 VOLTAGE REGULATORS

15

Page 16

There are 7812, 7805 and LM317 linear regulator ICs on the power supply to generate

+5V, -5V, +12V, -12V and +3.3V for the device. On the standby mode just +12Vst and +5V

supplies are generating for standby power consumption.

The ES6008/18 requires 2.5V to operate. This voltage is generated from +5V.

13 CONNECTORS

13.1 ATAPI DRIVE STANDARD CONNECTOR

The I/O connector is a 40-pin connector as shown in figure A.1, with pin assignments as shown in table

A.1. The connector shall be keyed to prevent the possibility of installing it upside down. A key is provided

by the removal of pin 20. The corresponding pin on the cable connector shall be plugged.

The cable plug, not the receptacle, governs the pin locations. The way in which the receptacle is mounted

on the printed circuit board affects the pin positions, and pin 1 shall remain in the same relative position.

This means the pin numbers of the receptacle may not reflect the conductor number of the plug. The

header receptacle is not polarized, and all the signals are relative to pin 20, which is keyed.

By using the plug positions as primary, a straight cable can connect devices. As shown in figure A.1,

conductor 1 on pin 1 of the plug shall be in the same relative position no matter what the receptacle

numbering looks like. If receptacle numbering was followed, the cable would have to twist 180 degrees

between a device with top-mounted receptacles, and a device with bottom-mounted receptacles.

1

40 20 2

Circuit board Circuit board

40 20 2

1

Figure A.1 - 40-pin connector mounting

16

Page 17

Table A.1 - 40-pin connector interface signals

Signal name Connector

contact

RESET- 1 1 2 2 Ground

DD7 3 3 4 4 DD8

DD6 5 5 6 6 DD9

DD5 7 7 8 8 DD10

DD4 9 9 10 10 DD11

DD3 11 11 12 12 DD12

DD2 13 13 14 14 DD13

DD1 15 15 16 16 DD14

DD0 17 17 18 18 DD15

Ground 19 19 20 20 (keypin)

DMARQ 21 21 22 22 Ground

DIOW- 23 23 24 24 Ground

DIOR- 25 25 26 26 Ground

IORDY 27 27 28 28 CSEL

DMACK- 29 29 30 30 Ground

INTRQ 31 31 32 32 reserved

DA1 33 33 34 34 PDIAGDA0 35 35 36 36 DA2

CS0- 37 37 38 38 CS1-

DASP- 39 39 40 40 Ground

Conductor Connector

contact

Signal name

Recommended part numbers for the mating connector and cable are shown below, but equivalent parts may

be used.

Connector (40 pin) 3M 3417-7000 or equivalent

Strain relief 3M 3448-2040 or equivalent

Flat cable (stranded 28 AWG) 3M 3365-40 or equivalent

Flat cable (stranded 28 AWG) 3M 3517-40 (shielded) or equivalent

13.2 SCART CONNECTORS

Pinout of the scart connector:

1 à Audio Right Out

2 à Audio Right In

3 à Audio Left / Monu Out

4 à Audio Gnd

5 à Blue Gnd

6 à Audio Left / Mono In

7 à Blue

8 à Control Voltage

9 à Green Gnd

10 à Comms Data 2

17

Page 18

11 à Green

12 à Comms Data 1

13 à Red Gnd

14 à Comms Data Gnd

15 à Red

16 à Fast Blanking

17 à Video Gnd

18 à Fast Blanking Gnd

19 à Composite Video In

20 à Composite Video Out

21 à Shield

Some cheaper SCART cables use unshielded wires, which is just about acceptable for

short cable lengths. For longer lengths, shielded co-ax cable become essential.

Scart Signals:

Audio signals

0.5V RMS, <1K output impedance, >10K input impedance.

Red, Green, Blue

0.7Vpp ±2dB, 75R input and output impedance. Note that the Red connection (pin 20) can

alternatively carry the S-VHS Chrominance signal, which is 0.3V.

Composite Video / CSync

1Vpp including sync, ±2dB, 75R input and output impedance.Bandwidth = 25Hz to 4.8MHz for

normal TV Video de-emphasis to CCIR 405.1 (625-line TV)

Fast Blanking

75R input and output impedance. This control voltage allows devices to over-ride the composite

video input with RGB inputs, for example when inserting closed caption text. It is called fast

because this can be done at the same speeds as other video signals, which is why it requires the

same 75R impedances.

0 to 0.4V: TV is driven by the composite video input signal (pin 19).

Left unconnected, it is pulled to 0V by its 75R termination.

1V to 3V: the TV is driven by the signals Red, Green, Blue and composite sync. The

latter is sent to the TV on pin 19. This signal is useful when using a TV to display the

RGB output of devices such as home computers with TV-compatible frame rates. Tying

the signal to 5V via 100R forms a potential divider with the 75R termination, holding the

signal at around 2V. Alternatively, if a TTL level (0 to 5V) negative sync pulse is

available, this will be high during the display periods, so this can drive the blanking signal

via a suitable resistor.

Control Voltage

0 to 2V = TV, Normal.

5 to 8V = TV wide screen

9.5 to 12V = AV mode

18

Page 19

IC500 8051 Micro Controller's Main Functions:

There are 2 main functions of the IC500 8051 micro controller; signal switching and

standby controlls. IC500 communicates with ES80X6 microcontroller by using I2C bus. (AUX0,

AUX1 signals)

Multiplexer (MUX) control signals for signal switching supplied by IC500. These MUX

signals are using the select signal sources and input-output signals.

MUX Control Signal list is shown in the following figure:

14. CIRCUIT DESCRIPTION

14.1 POWER SUPPLY:

• Socket PL800 is the 220VAC input.

• 3.5A fuse F800 is used to protect the device against short circuit and

unexpected overloads.

• Line filter and capacitors L800, C800 and C803 are used to block the parasitic

coming from the mains. They also prevent the noise, produced in the circuit,

from being injected to the line.

• Voltage is rectified by using diodes D805 diode bridge. Using capacitor C815

(220µf) a DC voltage is produced. (310- 320VDC).

• The current in the primary side of the transformer TR800 comes to the SMPS

IC (IC800 MC44608). The SMPS IC has a eight-pin DIP-8 package and an

external MOSFET with a cooler is mounted on it. It has a built-in oscillator,

overcurrent and overvoltage protection circuitry and runs at 100kHz. It starts

with the current from the primary side of the transformer and follows the

current from the feedback winding.

• Feedback current is deteceted by optocoupler IC803. Depending on the

control current coming from the secondary side, SMPS IC keeps the output

voltage constant by controlling the duty cycle of the ~30kHz signal (PWM) at

the primary side of the transformer.

19

Page 20

• Voltages on the secondary side are as follows: +20 Volts at D811, +10 Volts

at D808, +14V at D810, -22 Volts at D812, +12Vst at Q804.

• Using the output of the D808, a photo diode inside of the IC803 generates

feedback signal bu using optocoupler's photo transistor. This photo transistor

adjusts the control voltage at the IC800 pin3. The voltage at this pin effects

the pwm output frequency on the IC800 pin5. And finally output voltages

reach their correct values by this way.

• Voltage regulator IC805 (LM7805) supplies +5 Volts,

IC807 supplies +5V (off on standby mode),

IC809 supplies +3.3V (by using output of the IC807, off on standby mode),

Q804 supplies +12Vst,

IC806 supplies +12V (off on standby mode),

Q808 supplies -5V,

D812 supplies -22V.

Standby mode controlled by standby control transistors Q805, Q806, Q807.

Standby control signal comes from PL805 connector and generated by 8051

micro controllers.

• –22 Volts is used to feed the VFD (Vacuum Fluorescent Display) driver IC on

the front panel. Using diode R844, –22V is decreased and connected to the

filament winding to produce the DC offset for the filaments.

14.2 FRONT PANEL:

• All the functions on the front panel are controlled by IC1 (ES6008/18) on the

mainboard. Key scanning and IR checking operations on the standby mode

are controlled by IC500.

• ES60X8 IC sends the commands to IC1 uPD16311 via socket PL1 (pins 2,3

and 4).

• There are 16 keys scanning function, 2 LED outputs, 1 Stand-by output and

VFD drivers on IC2.

• Pin 52 is the oscillator pin and is connected via R5 56K.

• LED D5 is bright red in stand-by mode and soft red when the device is on.

• Vacuum fluorescent display MD1 is specially designed for AV1000.

• The scanned keys are transmitted via IC3 to IC1 on the mainboard.

• IR remote control receiver module IC2 (TSOP1836) sends the commands

from the remote control directly to IC1 and IC500.

• Socket PL2 carries the VFD filament voltage and –22 Volts.

14.3 I/Os and Back Panel:

• PL303 connector on the main board carries digital audio and command

signals to Class-D amplifier board (DDX Board). Command signals are

carried by an I2C bus and digital audio signals are carried by I2S bus

interface. After processing and amplification of audio signals amplificated

audio signals comes to back panel with this order(left to right): Front Left,

Front Right, Rear Right, Center, Rear Left and Subwoofer.

20

Page 21

• There are 1 DOUBLE SCART connector PL300 (Scart1 is for input on Scart

mode and Scart2 is for TV output), 3 pieces RCA audio jacks (L,R, Active

Subwoofer) for audio output, 3 pieces RCA A/V jacks for CVBS,L,R inputs on

AV mode, 1 RCA connector for CVBS out, 1 Connector for SVHS output.

• There are two op-amp ICs IC109 and IC110 for L,R and Active Subwoofer

output after DAC ICs (IC107 or IC108). IC109 generates L and R audio

outputs; IC110 generates Active Subwoofer output. JK302 is the output

connector for L,R and Active SW signals.

• JK306 is the CVBS, L and R input connector on the AV mode.

• Radio L,R, RCA Connector L,R, Scart connector input L,R, TV scart L,R

input (TV mode, for future use) are selected as analog audio source of the

system by IC402 MUX IC. This selected analog audio source comes to the

IC412 (LM833 op-amp IC) for amplification. By using ADC IC407 (CS5333) L

and R signals becomes digital audio signal and comes to ES60X8 for audio

proccessing operations.

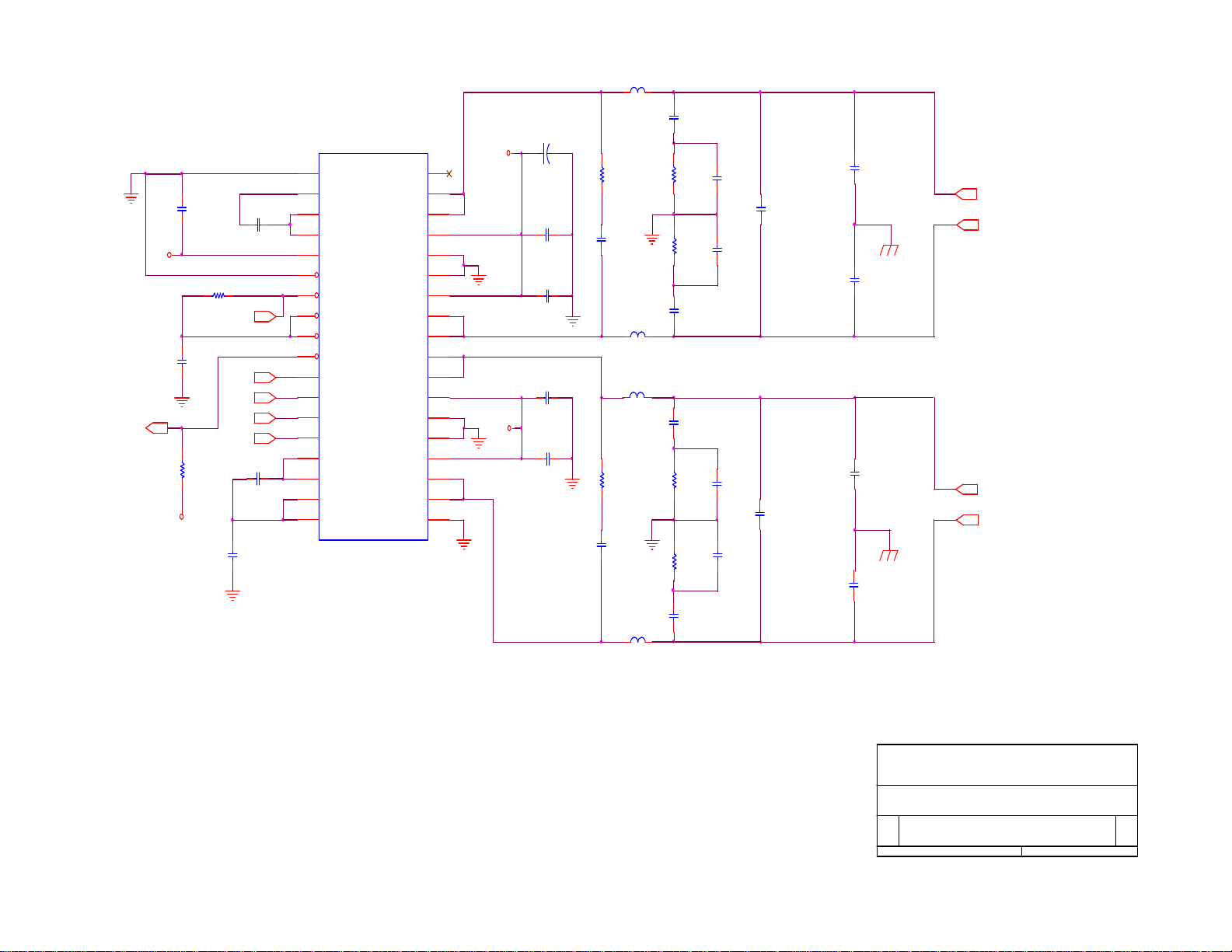

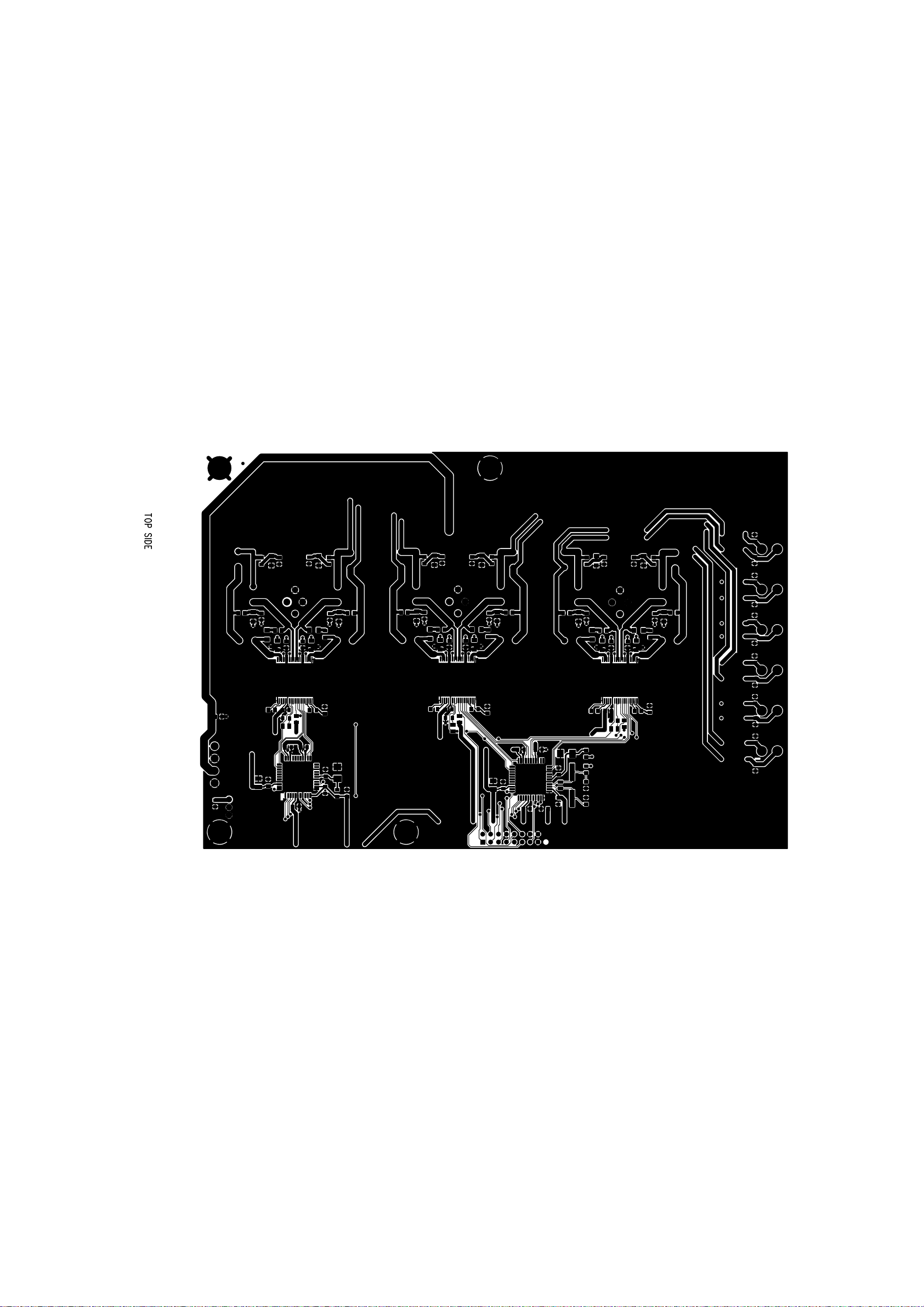

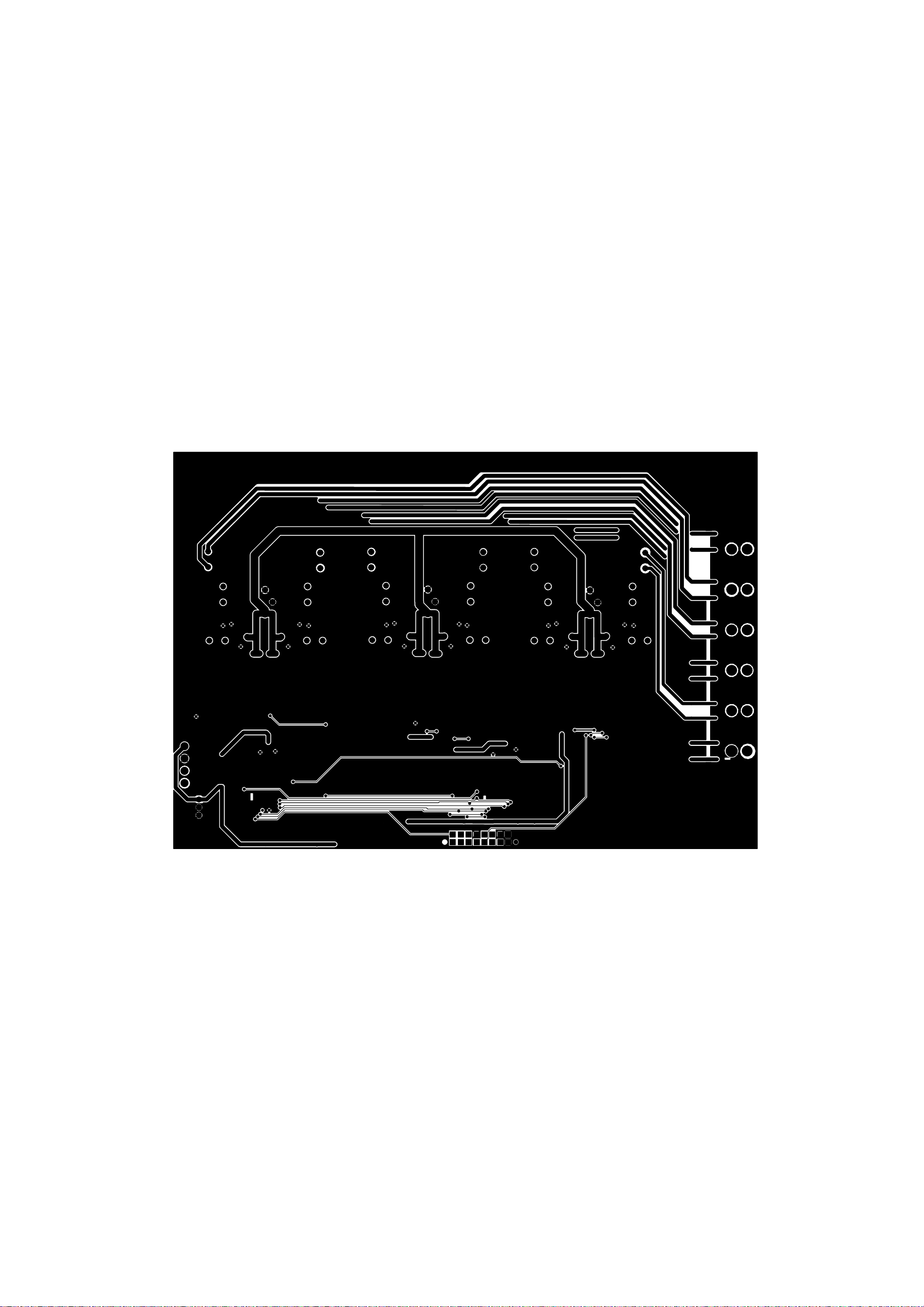

14.4 DDX Board (Class-D Amplifier):

• Chipset : 2xDDX-4100 + 3x DDX-2060

• Architecture : Full-Bridge x 6

• Power Supply : + 20V unipolar supply @ 6A max., + 3.3V @ 0.1A typ.

• Audio Input Interface: Serial I2S

• Control Interface: I2C

• Power Interface: + 20V @ 6A Max., + 3.3V@ 0.1A Typ

• Output Interface: Speaker Level

• Speakers: 8 Ohm Satellites + 4 Ohm Subwoofer

• Output Power: 5 x 15 W + 25 W

• DDX Audio proccess ICs are U1 and U2 (DDX-4100A).

• U1 and U2 ICs on the DDX board have digital audio input with I2S bus.

• I2S signals are SDI_1, SDI_2, SDI_3 serial data lines U1,U2 pin1,pin2,

LRCK Left-Right clock signal U1,U2 pin3,

SCK serial clock signal U1, U2 pin4.

• For mute function U1 and U2 ICs uses EAPD (pin35, External Amplifier

Powerdown) signal. This signal comes to the power output ICs U3, U4 and

U5 (DDX-2060 ICs Pin25) as power down signal.

21

Page 22

Page 23

Page 24

Page 25

Page 26

Page 27

Page 28

Page 29

Page 30

Page 31

Page 32

Page 33

Page 34

Page 35

Sch_A_Input

SD0

SD1

SD2

LRCK

BICK

SDA

SCL

PWRDWN

POWER_ON_RST

TWARN1

TWARN2

TWARN3

SD0

SD1

SD2

LRCK

BICK

SDA

SCL

PWRDWN

POWER_ON_RST

TWARN1

TWARN2

TWARN3

SD0

SD2

LRCK

BICK

SDA

SCL

PWRDWN

POWER_ON_RST

XTO

XTO

Sch_B_Frnt_Cntr_Sub_Processing

SD1

LRCK

BICK

SDA

SCL

PWDN

POWER_ON_RST

XTI

RIGHTA

RIGHTB

LFE_A

LFE_B

EAPD1

LEFTA

LEFTB

CENTERA

CENTERB

SLEFTA

SLEFTB

SRIGHTA

SRIGHTB

EAPD2

RIGHTA

RIGHTB

LFE_A

LFE_B

EAPD1

LEFTA

LEFTB

CENTERA

CENTERB

SLEFTA

SLEFTB

SRIGHTA

SRIGHTB

EAPD2

RIGHTA

RIGHTB

LFE_A

LFE_B

EAPD1

Sch_RightCh_Sub_Out

EAPD1

LEFTA

LEFTB

CENTERA

CENTERB

CENTER+

CENTER-

Sch_LeftCh_CNTR_Out

SLEFTA

SLEFTB

SRIGHTA

SRIGHTB

SRIGHT+

EAPD2

Sch_LR_Rear Out

RIGHT+

RIGHT-

LFE +

LFE -

TWARN1

LEFT+

LEFT-

TWARN3

SLEFT+

SLEFT-

SRIGHT-

TWARN2

RIGHT+

RIGHT-

LFE+

LFE-

TWARN1

LEFT+

LEFT-

CENTER+

CENTER-

TWARN3

SLEFT+

SLEFT-

SRIGHT+

SRIGHT-

TWARN2

SPEAKER OUTPUT

RIGHT+

RIGHT-

LFE +

LFE -

LEFT+

LEFT-

CENTER+

CENTER-

SLEFT+

SLEFT-

SRIGHT+

SRIGHT-

Sch_B_Rear Processing

Title

5.1 CHANNEL AMPLIFIER SCHEMATICS

Size Document Number Rev

150-0000-001 A

B

Date: Sheet

1 8Sunday, March 03, 2002

of

Page 36

SD2

BICK

SCL

TWARN1

TWARN3

POWER_ON_RST

INPUTCONNECTOR

J1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

87256-1611

SD1SD0

LRCK

SDA

TWARN2

PWRDWN

+3.3V +20V

+

C101

100UF

6.3V

C2

100NF

Y5V

C1

100NF

X7R

JP1

1

2

3

4

JS-1120-04

POWER

Title

5.1 CHANNEL SCHEMATIC INPUT CONNECTOR

Size Document Number Rev

A

150-0000-001 A

Date: Sheet

2 8Thursday, February 14, 2002

of

Page 37

+3.3V

C3

+

2.2UF

6.3VDC

C4 100NF

Y5V

R1

0000-0805

Y1

24.576 MHz

C12

18PF

NPO

1M

+3.3V

C6

100NF

Y5V

C13

18PF

NPO

SDI0 = L, R

SDI1 = LS, RS

SDI2 = C, SUB

PWRD WN

SD0

SD2

LRCK

BICK

POWER_ON_RST

SDA

SCL

+3.3V

L15 600 ohm@100mhz

1

2

EIA0805

XTO

1

SDI_1/SDATA_OUT

2

SDI_2/SDATA_IN

3

LRCKI/SYNC

4

BCKI/BIT_CLK

5

VDD_1

6

GND_1

7

RESET

8

AC97_MODE

9

SDA

10

SCL

11

SA

+3.3V

C9

100NF

Y5V

EAPD1

CENTERA

34

35

36

37

38

39

40

41

42

43

44

SCKO

PW DN

CKOUT

TEST_MODE

VDD_2

12

13

14

SDO_1

SDO_2

SDO_3

VDD_5

GN D _5

LRCKO

XTI

XTO

GN D _2

VCC

RXP

RXN

VSS

15

16

17

18

19

20

21

EAPD

LFE_B

22

+

SLEF T_A

SLEFT_B

VDD_4

GND_4

LEFT_A

LEFT_B

RIGH T_A

RIGH T_B

VDD_3

GND_3

SRIGH T_A

SRIGH T_B

LFE_A

DDX4100A

C8

22UF

6.3VDC

U1

33

32

31

30

29

28

27

26

25

24

23

L1 100NH

1

EIA0805

C10

100NF

Y5V

CENTERB

LEFTA

LEFTB

RIGHTA

RIGHTB

C7

100NF

Y5V

LFE_A

LFE_B

2

+3.3V

C11

100NF

Y5V

+3.3V

+3.3V

C5

100NF

Y5V

Title

5.1CHANN EL SCHEMATIC FRONT, CENTER, SUB PROCESSING

Size Document Number Rev

150-0000-001 A

B

Date: Sheet

3 8Friday, February 15, 2002

of

Page 38

+3.3V

C14

+

2.2UF

6.3VDC

C15 100NF

Y5V

+3.3V

C17

100NF

Y5V

SDI0 = L, R

SDI1 = LS, RS

SDI2 = C, SUB

SD1

LRCK

BICK

POWER_ON_RST

SDA

SCL

PWDN

XTI

1

SDI_1/SDATA_OUT

2

SDI_2/SDATA_IN

3

LRCKI/SYNC

4

BCKI/BIT_CLK

5

VDD_1

6

GND_1

7

RESET

8

AC97_MODE

9

SDA

10

SCL

11

SA

+3.3V

C20

100NF

Y5V

EAPD2

SLEFTA

SLEFTB

34

35

36

37

38

39

40

41

42

43

44

SCKO

PWDN

CKOUT

TEST_MODE

VDD_2

12

13

14

SDO_1

SDO_2

SDO_3

VDD_5

GND_5

XTI

XTO

15

LRCKO

GND_2

VCC

RXP

RXN

VSS

16

17

18

19

20

EAPD

LFE_B

21

22

+

SLEFT_A

SLEFT_B

VDD_4

GND_4

LEFT_A

LEFT_B

RIGHT_A

RIGHT_B

VDD_3

GND_3

SRIGHT_A

SRIGHT_B

LFE_A

DDX4100A

C19

22UF

6.3VDC

U2

33

32

31

30

29

28

27

26

25

24

23

L2 100NH

1

EIA0805

C21

100NF

Y5V

SRIGHTA

SRIGHTB

2

+3.3V

C18

100NF

Y5V

+3.3V

C22

100NF

Y5V

C16

100NF

Y5V

+3.3V

Title

5.1 CHANNEL SCHEMATIC REAR CHANNEL PROCESSING

Size Document Number Rev

150-0000-001 A

B

Date: Sheet

4 8Thursday, February 14, 2002

of

Page 39

TWARN3

+3.3V

+3.3V

C26

100NF

X7R

R5 10K

0000-0805

C34

100NF

Y5V

R6

10K

0000-0805

EAPD1

CENTERA

CENTERB

LEFTA

LEFTB

C28 100NF

C38 100NF

X7R

C42

100NF

X7R

X7R

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

U3

GNDR1

VREG1

VREG1

VL

CONFIG

PWRDN

TRI-STATE

FAULT

TWARN

INLA

INLB

INRA

INRB

VREG2

VREG2

VSIG

VSIG

DDX2060

OUTPL

OUTPL

VCC1P

PGND1P

PGND1N

VCC1N

OUTNL

OUTNL

OUTPR

OUTPR

VCC2P

PGND2P

PGND2N

VCC2N

OUTNR

OUTNR

GNDS

L3 22uh

1

2

IND-22UH-CT622LY

C24

18

NCGNDREF

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+20V

+20V

+

1000UF

25VDC

C29 1UF

X7R

C32 100NF

X7R

C35 1UF

X7R

C37 100NF

X7R

R2

20

0000-1206

5%

C30

330PF

X7R

L4 22uh

1

IND-22UH-CT622LY

L5 22uh

1

IND-22UH-CT622LY

R7

20

0000-1206

5%

C41

330PF

X7R

L6 22uh

1

IND-22UH-CT622LY

C23

100NF

X7R

R3

C25

6.2

100NF

0000-1206

X7R

5%

C31

R4

100NF

6.2

5%

C33

100NF

X7R

C36

100NF

X7R

R8

6.2

0000-1206

5%

R9

6.2

0000-1206

5%

X7R

C39

100NF

X7R

C43

100NF

X7R

0000-1206

2

2

C44

100NF

X7R

2

CENTER+

C27

470NF

FILM

CENTER-

LEFT+

C40

470NF

FILM

LEFT-

R26

150

0000-1206

5%

C89

1000PF

NPO

C90

1000PF

NPO

C91

1000PF

NPO

C92

1000PF

NPO

CENTER+

8 OHM

CENTER-

LEFT+

8 OHM

LEFT-

Title

5.1CHANNELSCHEMATICCENTER,LFCHANNELSAMPLIFIER

Size DocumentNumber Rev

150-0000-001 A

B

Date: Sheet

5 8Monday,February18, 2002

of

Page 40

TWARN2

+3.3V

+3.3V

C70

100NF

X7R

R21 10K

0000-0805

C78

100NF

Y5V

R22

10K

0000-0805

EAPD2

SLEFTA

SLEFTB

SRIGHTA

SRIGHTB

C72 100NF

C82 100NF

C86

100NF

X7R

L11 22uh

2

1

IND-22UH-CT622LY

+20V

C68

+

1000UF

25VDC

C73 1UF

X7R

C76 100NF

X7R

C79 1UF

X7R

C81 100NF

X7R

R18

20

0000-1206

5%

C74

330PF

X7R

L12 22uh

1

IND-22UH-CT622LY

L13 22uh

1

IND-22UH-CT622LY

R23

20

0000-1206

5%

C85

330PF

X7R

L14 22uh

1

IND-22UH-CT622LY

U5

19

20

GNDR1

21

VREG1

22

X7R

X7R

23

24

25

26

27

28

29

30

31

32

33

34

35

36

VREG1

VL

CONFIG

PWRDN

TRI-STATE

FAULT

TWARN

INLA

INLB

INRA

INRB

VREG2

VREG2

VSIG

VSIG

OUTPL

OUTPL

VCC1P

PGND1P

PGND1N

VCC1N

OUTNL

OUTNL

OUTPR

OUTPR

VCC2P

PGND2P

PGND2N

VCC2N

OUTNR

OUTNR

GNDS

18

NCGNDREF

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+20V

DDX2060

C67

100NF

X7R

R19

C69

6.2

100NF

0000-1206

X7R

5%

C75

R20

100NF

6.2

X7R

0000-1206

5%

C77

100NF

X7R

2

2

C80

100NF

X7R

C83

R24

100NF

6.2

X7R

0000-1206

5%

C87

R25

100NF

6.2

X7R

0000-1206

5%

C88

100NF

X7R

2

C71

470NF

FILM

C84

470NF

FILM

SLEFT+

SLEFT-

SRIGHT+

SRIGHT-

C93

1000PF

NPO

C94

1000PF

NPO

C95

1000PF

NPO

C96

1000PF

NPO

SLEFT+

8 OHM

SLEFT-

SRIGHT+

8 OHM

SRIGHT-

Title

5.1CHANNELSCHEMATICREARCHANNELAMPLIFIERS

Size Document Number Rev

150-0000-001 A

B

Date: Sheet

6 8Thursday,February14,2002

of

Page 41

TWARN1

+3.3V

+3.3V

C48

100NF

X7R

R13 10K

0000-0805

C56

100NF

Y5V

R14

10K

0000-0805

EAPD1

LFE_A

LFE_B

RIGHTA

RIGHTB

C64

100NF

X7R

C50100NF

X7R

C60100NF

X7R

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

U4

GNDR1

VREG1

VREG1

VL

CONFIG

PWRDN

TRI-STATE

FAULT

TWARN

INLA

INLB

INRA

INRB

VREG2

VREG2

VSIG

VSIG

DDX2060

NCGNDREF

OUTPL

OUTPL

VCC1P

PGND1P

PGND1N

VCC1N

OUTNL

OUTNL

OUTPR

OUTPR

VCC2P

PGND2P

PGND2N

VCC2N

OUTNR

OUTNR

GNDS

L7 10uH

1

2

IND-10UH-CT622LY

C46

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+20V

+20V

+

1000UF

25VDC

C511UF

X7R

C54100NF

X7R

C571UF

X7R

C59100NF

X7R

R10

20

0000-1206

5%

C52

330PF

X7R

L8 10uH

1

IND-10UH-CT622LY

L9 22uh

1

IND-22UH-CT622LY

R15

20

0000-1206

5%

C63

330PF

X7R

L10 22uh

1

IND-22UH-CT622LY

C45

100NF

X7R

C47

R11

100NF

6.2

X7R

0000-1206

5%

C53

R12

100NF

6.2

X7R

0000-1206

5%

C55

100NF

X7R

2

2

C58

100NF

X7R

C61

R16

100NF

6.2

X7R

0000-1206

5%

C65

R17

100NF

6.2

X7R

0000-1206

5%

C66

100NF

X7R

2

LFE +

C49

470NF

FILM

LFE -

RIGHT+

C62

470NF

FILM

RIGHT-

R27

150

0000-1206

5%

C97

1000PF

NPO

C98

1000PF

NPO

C99

1000PF

NPO

C100

1000PF

NPO

LFE +

4 OHM

LFE -

RIGHT+

8 OHM

RIGHT-

Title

5.1 CHANNEL SCHEMATIC RIGHT, LFE CHANNEL AMPLIFIERS

Size Document Number Rev

150-0000-001 A

B

Date: Sheet

7 8Monday , F ebruary 18, 2002

of

Page 42

LEFT+

3

1

..

..

SLEFT+

SRIGHT+

5

..

LFE +

11

9

7

..

..

..

J2

PT1201

CENTER+

RIGHT+

SPEAKER

12

10

8

6

4

2

LEFT-

RIGHT-

SRIGHT-

LFE -

SLEFT-

CENTER-

Title

5.1 CHANN EL SCH EMATIC OUTPUT CON N EC TOR

Size Doc um ent Num ber Rev

150-0000-001 A

A

of

Date: Sheet

8 8Friday , February 15, 2002

Page 43

Page 44

Page 45

Page 46

Page 47

Page 48

Page 49

Page 50

Page 51

Page 52

Page 53

THE UPDATED PARTS LIST

FOR THIS MODEL IS

AVAILABLE ON ESTA

Page 54

Hitachi, Ltd. Tokyo, Japan

International Sales Division

THE HITACHI ATAGO BUILDING,

No. 15 –12 Nishi Shinbashi, 2 – Chome,

Minato – Ku, Tokyo 105-8430, Japan.

Tel: 03 35022111

HITACHI EUROPE LTD,

Whitebrook Park

Lower Cookham Road

Maidenhead

Berkshire

SL6 8YA

UNITED KINGDOM

Tel: 01628 643000

Fax: 01628 643400

Email: consumer-service@hitachi-eu.com

HITACHI EUROPE GmbH

Munich Office

Dornacher Strasse 3

D-85622 Feldkirchen bei München

GERMANY

Tel: +49-89-991 80-0

Fax: +49-89-991 80-224

Hotline: +49-180-551 25 51 (12ct/min)

Email: HSE-DUS.service@hitachi-eu.com

HITACHI EUROPE srl

Via Tommaso Gulli N.39, 20147

Milano, Italia

ITALY

Tel: +39 02 487861

Tel: +39 02 38073415 Servizio Clienti

Fax: +39 02 48786381/2

Email: customerservice.italy@hitachi-eu.com

HITACHI EUROPE S.A.S

Lyon Office

B.P. 45, 69671 BRON CEDEX

FRANCE

Tel: 04 72 14 29 70

Fax: 04 72 14 29 99

Email: france.consommateur@hitachi-eu.com

HITACH EUROPE AB

Egebækgård

Egebækvej 98

DK-2850 Nærum

DENMARK

Tel: +45 43 43 6050

Fax: +45 43 60 51

Email: csgnor@hitachi-eu.com

Hitachi Europe Ltd

Bergensesteenweg 421

1600 Sint- Pieters-Leeuw

BELGIUM

Tel: +32 2 363 99 01

Fax: +32 2 363 99 00

Email: sofie.van.bom@hitachi-eu.com

www.hitachidigitalmedia.com

HITACHI EUROPE S.A.

364 Kifissias Ave. & 1, Delfon Str.

152 33 Chalandri

Athens

GREECE

Tel: 1-6837200

Fax: 1-6835964

Email: service.hellas@hitachi-eu.com

HITACHI EUROPE S.A.

Gran Via Carlos III, 101- 1

08028 Barcelona

SPAIN

Tel: 93 409 2550

Fax: 93 491 3513

Email: atencion.cliente@hitachi-eu.com

HITACHI HOME ELECTRONICS (NORDIC) AB

Box 77 S-164 94 Kista

SWEDEN

Tel: +46 (0) 8 562 711 00

Fax: +46 (0) 8 562 711 13

Email: csgswe@hitachi-eu.com

HITACHI EUROPE LTD (Norway) AB

STRANDVEIEN 18

1366 Lysaker

NORWAY

Tel: 67 5190 30

Fax: 67 5190 32

Email: csgnor@hitachi-eu.com

HITACHI EUROPE AB

Neopoli / Niemenkatu 73

FIN-15140 Lahti

FINLAND

Tel : +358 3 8858 271

Fax: +358 3 8858 272

Email: csgnor@hitachi-eu.com

HITACHI EUROPE LTD

Na Sychrove 975/8

101 27 Praha 10 – Bohdalec

CZECH REPUBLIC

Tel: +420 267 212 383

Fax: +420 267 212 385

Email: csgnor@hitachi-eu.com

Loading...

Loading...