Page 1

Windows® CE Intelligent Peripheral Controller

HD64465

User’s Manual

ADE-602-168B

Rev. 3.0

03/08/01

Hitachi Ltd.

Page 2

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party’s

rights, including intellectual property rights, in connection with use of the information

contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you

have received the latest product standards or specifications before final design, purchase or

use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability.

However, contact Hitachi’s sales office before using the product in an application that

demands especially high quality and reliability or where its failure or malfunction may directly

threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear

power, combustion control, transportation, traffic, safety equipment or medical equipment for

life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi

particularly for maximum rating, operating supply voltage range, heat radiation characteristics,

installation conditions and other characteristics. Hitachi bears no respon sibility for failure or

damage when used beyond the guaranteed ranges. Even within the guaranteed ranges,

consider normally foreseeable failure rates or failure modes in semiconductor devices and

employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi

product does not cause bodily injury, fire or other consequential damage due to operation of

the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi

semiconductor products.

Page 3

Revisions and Additions in this Edition

Page Item Description

- Description of register address <Former Edition> 0x……… / ………h

<This Edition> H’………

- Description of HD64465BQ Add the description of new product “HD64465BQ”

- HD64465BP Specifications

Changed

16 Add the description of M12 to M15 pins

17

26 Table 4.4 Pin Descriptions of

39

52 6.3 Register Dexcription

Table 4.1 HD64465BP Signal

Names (by pin numbers in

alphabetical order)

CPU Interface

Table 4. 24 Pin Descr iptions of

No Connected Pins

Table 4. 25 Pin Descr iptions of

Power/Ground

Table 6.1 The Register List Of

Power Management and System

Configuration

<Former Edition>

PLL used in bypass mode and 48 MHz clock input into

UCK terminal

<This Edition>

PLL used in bypass mode

Add the description of N12 to N15, P12 to P15, R12 to

R15 pins

Signal name of R1 pin

<Former Edition>

RESET#

<This Edition>

RESETPI#

Correct the table name

<Former Edition>

Pin Descriptions of LCD Interface

<This Edition>

Pin Descriptions of No Connected Pins

Pin description of AVSS3

<Former Edition>

Ground for analog circuit (can not connected)

<This Edition>

NC (No Connected Pin)

<Former Edition>

Register Size = 2

Access Size = 2

<This Edition>

Register Size = 16

Access Size = 16

Page 4

Page Item Description

54 6.3.2 System Configuration

Register (SCONFR)

Description of Bits 11 - 8

58 6.3.4 System Peripheral Clock

Control Register (SPCCR)

59 Figure 6.1 AFECK & LCK

Related Clock Diagram

71 7.3.1 Port Data Register <Former Edition>

Add the following description

Note that the relationship between HW[3:0] and CPU

programmed inserted wait states (IWS) is 2 ≤ 1 WS ≤

1+HW[3:0]. Hence, the CPU default inserted wait

states should be 2.

<Former Edition>

Note: The parameter, Twkst, please refer the AC

timing specification.

<This Edition>

Note: The parameter, Twkst = 15 ms

Add the description ofACCLK pin

GPCDR -- Address: 100004018h

<This Edition>

GPEDR -- Address: H’100004018

91 Table 9.1 The Register List of

Timer Module

93 9.2.3 TRVR1:Timer 1 Read Vlue

Register

94 9.2.4 TRVR0:Timer 0 Read

Value Register

99 9.2.9 PWM1CS: PWM1 Clock

Scale Register

Bits 5 - 0

102 9.2.12 PWM0CS: PWM0 Clock

Scale Register

Bits 5 - 0

121 10.4.8 PCC1 General Control

Register (PCC1GCR)

<Former Edition>

Register Size = 2

Access Size = 2

<This Edition>

Register Size = 16

Access Size = 16

<Former Edition> R/W value = R/O

<This Edition> R/W value = R

Delete the default value

Description of bit 7

<Former Edition> PCC0

<This Edition> PCC1

Description of bit 4

<Former Edition> VCC0SEL1

<This Edition> VCC1SEL0

Page 5

Page Item Description

152 (26) Timing control Register

(ITMCR)

Bits 5 - 0

176

227 Table 14.3 AC97 Timing <Former Edition> Unit : Us

336 19.2.1 A/D Data Registers A to D

341 19.3.2 Acan Mode (SCAN = 1) Add the ADCSR table

352, 353 Table 20.13 AFECK clock input

363, 364 Figure 20.26 AFECK Clock Input

(2) ECP Address FIFO Register

(ECPAFifo)

(4) Device Control Register (der)

(Address H’1000A004, Mode All)

(ADDRA to ADDRD, ADCAL)

AC Timing Spec. (PLL1:bypass)

(unit : ns)

Table 20.14 AFECK clock input

AC Timing Spec.

(PLL1:operatings) (unit : ns)

Table 20.15 AFECK clock input

AC Timing Spec. (PLL2:bypass)

(unit : ns)

Table 20.16 AFECK clock input

AC Timing Spec.

(PLL2:operating) (unit : ns)

Timing

Figure 20.27 UCK Clock Input

Timing

Delete the default value

Default value of bits 2 - 0

<Former Edition> 111b

<This Edition> 111

Default value of bits 2 - 0

<Former Edition> 11b

<This Edition> 11

Ns

<This Edition> Unit : µs

ns

<Former Edition> Bit 9 : AD8

Bit 8 : AD9

<This Edition> Bit 9 : AD9

Bit 8 : AD8

New tables added

New figures added

Page 6

HD64465BP Specifications Changed

1. Change in Specifications

Item changed Guaranteed value before change Guaranteed value after change

PLL stabilization time 5ms Not guaranteed

2. Major Influences Due to Above Change in Specifications

Preconditions Problems in usage

PLL used in bypass mode No problem (no standby time added)

Reset signal input after turning power on No problem (no standby time added)

PLL standby not used although oscillation stop used No problem (no standby time added)

Certain interval allowed between PLL standby and

wakeup

3. Countermeasures

Use the system in a state without any problem by referring to "2." above.

•

Create your program in a way to prohibit access other than to the HD64465BP system

•

configuration register (offset address: H'00000000 to H'00000ff0) for a certain period of time

after returning from PLL standby.

4. Debugged Version

The cause of this problem has already been clarified, which can be solved by correcting the

wiring layer. The new mask product (HD64465EBP) is available as the debugged version.

Several seconds may be required for access

by HD64465BP from CPU.

Page 7

Contents

Section 1 Features............................................................................................1

1.1 CPU Interface....................................................................................................................1

1.2 PCMCIA Controller..........................................................................................................1

1.3 AFE Interface....................................................................................................................1

1.4 GPIO Function(Port Interrupt)..........................................................................................1

1.5 Interrupt Controller ...........................................................................................................2

1.6 Power Management...........................................................................................................2

1.7 Timer.................................................................................................................................2

1.8 Keyboard Controller Interface...........................................................................................2

1.9 UART................................................................................................................................ 2

1.10 Printer interface.................................................................................................................3

1.11 Audio CODEC Interface...................................................................................................3

1.12 IrDA ..................................................................................................................................3

1.13 Clock Generator and PLL..................................................................................................3

1.14 USB Host Controller.........................................................................................................4

1.15 10-bit ADC........................................................................................................................4

1.16 Package .............................................................................................................................4

Section 2 General Description.........................................................................5

Section 3 System Block Diagram....................................................................7

3.1 Application Circuit............................................................................................................7

3.2 System Block Diagram......................................................................................................8

3.3 Physical Address Space.....................................................................................................9

3.4 HD64465 Memory Address .............................................................................................. 10

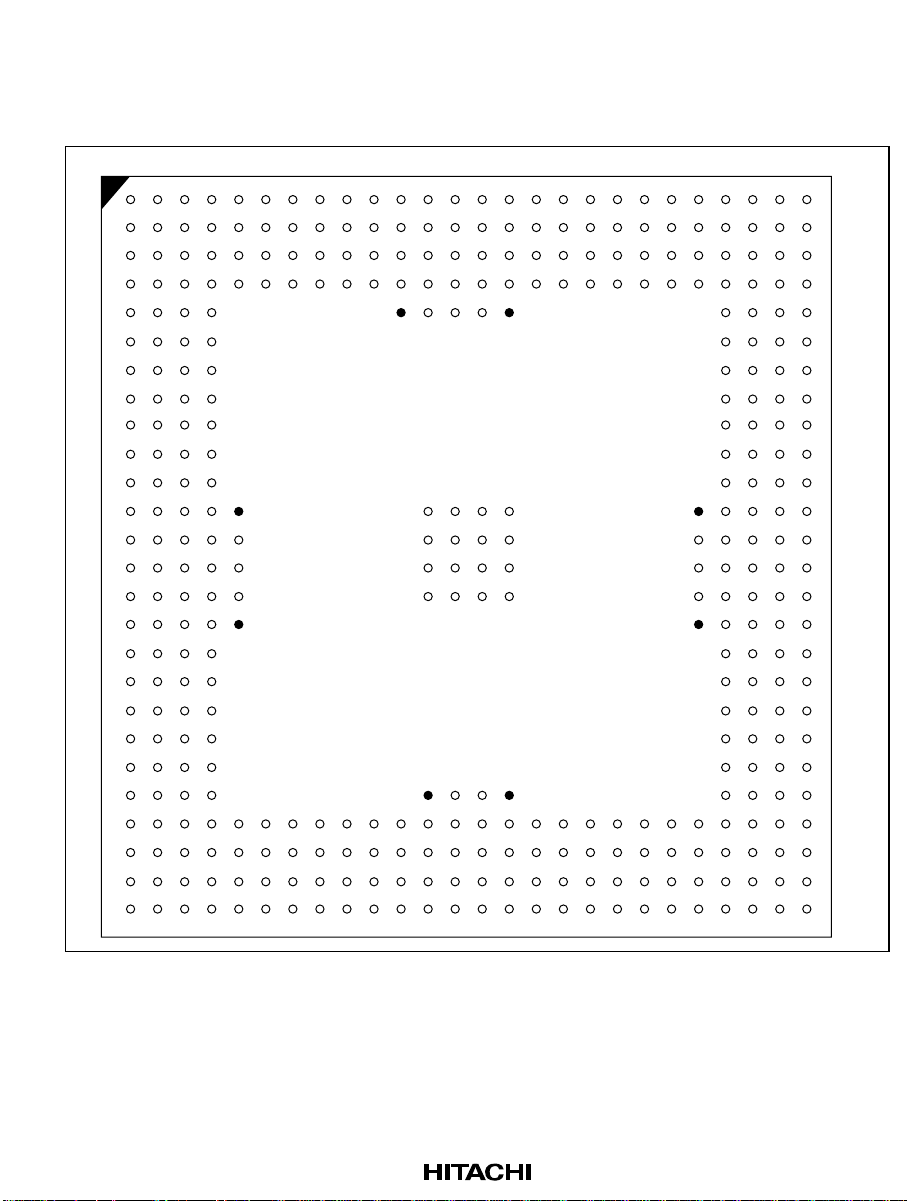

3.5 Pin Configuration..............................................................................................................11

3.5.1 HD64465BP Top View........................................................................................11

3.5.2 HD64465BP Bottom View...................................................................................12

3.5.3 HD64465BQ Top View .......................................................................................13

3.5.4 HD64465BQ Bottom View..................................................................................14

Section 4 Pin Description................................................................................15

Section 5 Internal CPU Interface.....................................................................41

5.1 Introduction.......................................................................................................................41

5.2 CPU Interface Signal Description.....................................................................................42

5.2.1 System Bus Interface Signals...............................................................................42

5.2.2 Internal Bus Interface Signals..............................................................................43

5.3 Function Description.........................................................................................................44

Rev. 3.0, 03/01, page i of xiii

Page 8

5.4 Signal Timing Description ................................................................................................45

5.4.1 Low Speed Timing...............................................................................................45

5.4.2 High Speed Timing..............................................................................................47

5.5 Internal Bus Data Swap Rules...........................................................................................49

5.6 Internal Peripheral Bus AC Timing Specification.............................................................50

Section 6 Power Management and System Configuration..............................51

6.1 Overview...........................................................................................................................51

6.2 Features.............................................................................................................................51

6.3 Register Description..........................................................................................................52

6.3.1 System Module Standby Control Register (SMSCR)..........................................52

6.3.2 System Configuration Register (SCONFR).........................................................54

6.3.3 System Bus Control Register (SBCR)..................................................................55

6.3.4 System Peripheral Clock Control Register (SPCCR)...........................................57

6.3.5 System Peripheral S/W Reset Control Register (SPSRCR).................................61

6.3.6 System PLL Control Register (SPLLCR)............................................................63

6.3.7 System Revision Register (SRR)..........................................................................64

6.3.8 System Device ID Register (SDID) ..................................................................... 64

6.4 System Hardware Reset Timing........................................................................................65

6.4.1 Power-On Reset Output .......................................................................................65

6.4.2 Manual Reset Output............................................................................................66

Section 7 General Purpose I/O Port ................................................................67

7.1 Overview...........................................................................................................................67

7.1.1 Features................................................................................................................67

7.2 Register Configuration......................................................................................................69

7.3 Register Descriptions ........................................................................................................70

7.3.1 Port Data Register................................................................................................70

7.3.2 Port Control Register............................................................................................72

7.3.3 Port Interrupt Control Register.............................................................................74

7.3.4 Port Interrupt Status Register...............................................................................76

Section 8 Interrupt Controller (INTC) ............................................................ 79

8.1 Overview...........................................................................................................................79

8.1.1 Features................................................................................................................79

8.1.2 Block Diagram.....................................................................................................80

8.1.3 Pin Configuration.................................................................................................80

8.1.4 Register Configuration.........................................................................................80

8.2 Interrupt Sources...............................................................................................................81

8.2.1 On-Chip Module Interrupt ...................................................................................81

8.2.2 Interrupt Exception Processing and Priority.........................................................81

8.3 NIRR: Interrupt Request Register.....................................................................................82

8.4 NIMR: Interrupt Mask Register ........................................................................................84

Rev. 3.0, 03/01, page ii of xiii

Page 9

8.5 NITR: Interrupt Trigger Mode Register............................................................................86

Section 9 Timer ...............................................................................................89

9.1 Overview...........................................................................................................................89

9.1.1 Features................................................................................................................89

9.1.2 Block Diagram.....................................................................................................90

9.1.3 Pin Configuration.................................................................................................91

9.1.4 Register Configuration.........................................................................................91

9.2 Timer Register ...................................................................................................................92

9.2.1 TCVR1: Timer 1 Constant Value Register...........................................................92

9.2.2 TCVR0: Timer 0 Constant Value Register...........................................................93

9.2.3 TRVR1: Timer 1 Read Value Register ................................................................93

9.2.4 TRVR0: Timer 0 Read Value Register ................................................................94

9.2.5 TCR1: Timer 1 Control Register..........................................................................95

9.2.6 TCR0: Timer 0 Control Register..........................................................................96

9.2.7 TIRR: Timer Interrupt Request Register..............................................................97

9.2.8 TIDR*: Timer Interrupt Disable Register............................................................98

9.2.9 PWM1CS: PWM 1 Clock Scale Register.............................................................99

9.2.10 PWM1LPC: PWM 1 Low Pulse Width Counter Register....................................100

9.2.11 PWM1HPC: PWM 1 High Pulse Width Counter Register ..................................101

9.2.12 PWM0CS: PWM 0 Clock Scale Register.............................................................102

9.2.13 PWM0LPC: PWM 0 Low Pulse Width Counter Register....................................103

9.2.14 PWM0HPC: PWM 0 High Pulse Width Counter Register ..................................104

9.3 Special Register Programming Sequence..........................................................................104

9.4 Interrupt Timing................................................................................................................104

9.5 A/D Trigger Signal ADTRIG#..........................................................................................106

9.6 DMA Request Enable Function.........................................................................................108

9.7 PWM Operation ................................................................................................................108

Section 10 PC Card Controller (PCC)...............................................................109

10.1 Overview...........................................................................................................................109

10.2 Features.............................................................................................................................109

10.3 Register Configuration......................................................................................................109

10.4 Register Description..........................................................................................................110

10.4.1 PCC0 Interface Status Register (PCC0ISR) .........................................................110

10.4.2 PCC0 General Control Register (PCC0GCR)......................................................112

10.4.3 PCC0 Card Status Change Register (PCC0CSCR)..............................................114

10.4.4 PCC0 Card Status Change Interrupt Enable Register (PCC0CSCIER)................116

10.4.5 PCC0 Software Control Register (PCC0SCR).....................................................118

10.4.6 PCC Serial Power Switch Control Register (PCCPSR).......................................119

10.4.7 PCC1 Interface Status Register (PCC1ISR) .........................................................119

10.4.8 PCC1 General Control Register (PCC1GCR)......................................................121

10.4.9 PCC1 Card Status Change Register (PCC1CSCR)..............................................123

Rev. 3.0, 03/01, page iii of xiii

Page 10

10.4.10 PCC1 Card Status Change Interrupt Enable Register (PCC1CSCIER)................125

10.4.11 PCC1 Software Control Register (PCC1SCR).....................................................127

Section 11 FIR Module.....................................................................................129

11.1 Overview...........................................................................................................................129

11.1.1 Features................................................................................................................129

11.1.2 Functional Block Diagram of FIR........................................................................130

11.2 FIR Controller Register Description..................................................................................132

11.2.1 UART Register of FIR Portion ............................................................................132

11.2.2 FIR Controller Register........................................................................................133

11.2.3 Register Description.............................................................................................134

11.3 FIR Transmit Operation ....................................................................................................1 53

11.4 FIR Receive Operation......................................................................................................154

11.5 Example of Initialization and Programming Procedure for HP-SIR.................................156

Section 12 UART.............................................................................................. 157

12.1 Overview...........................................................................................................................157

12.2 Features.............................................................................................................................157

12.3 Serial Channel Register Description..................................................................................158

12.3.1 Data Register........................................................................................................ 158

12.3.2 Control Registers: UIER, UIIR, UFCR, UDLL, UDLM, ULCR, UMCR ...........159

12.3.3 Status Register ULSR and UMSR........................................................................164

12.4 Reset..................................................................................................................................167

12.5 Programming.....................................................................................................................168

12.5.1 Programming Sequence........................................................................................168

12.6 Software Reset...................................................................................................................168

12.7 Clock Input Operation.......................................................................................................168

12.8 FIFO Interrupt Mode Operation........................................................................................169

12.9 CAUTION.........................................................................................................................170

Section 13 Parallel Port..................................................................................... 171

13.1 Overview...........................................................................................................................171

13.2 Features.............................................................................................................................171

13.3 Parallel Port Register Description.....................................................................................171

13.3.1 SPP and EPP Modes.............................................................................................173

13.3.2 ECP Mode............................................................................................................174

Section 14 Serial CODEC Interface.................................................................. 181

14.1 Overview...........................................................................................................................181

14.1.1 Features................................................................................................................181

14.1.2 Block Diagram.....................................................................................................182

14.2 Register Description..........................................................................................................183

14.2.1 Transmit Data Register (TDR).............................................................................184

Rev. 3.0, 03/01, page iv of xiii

Page 11

14.2.2 Receive Data Register (RDR) ..............................................................................185

14.2.3 Control Register (CR) ..........................................................................................186

14.2.4 Status Register (SR).............................................................................................187

14.2.5 Frequency Select Register....................................................................................189

14.2.6 Command/Status Address Register (CSAR)........................................................190

14.2.7 Command/Status Data Register (CSDR)..............................................................191

14.2.8 PCM Playback/Record Left Channel (PCML).....................................................192

14.2.9 PCM Playback/Record Right Channel (PCMR) ..................................................193

14.2.10 Line 1 Data Register (LINE1)..............................................................................194

14.2.11 PCM Center Playback/MIC ADC Channel (PCMC) ...........................................195

14.2.12 PCM Left Surround Channel Data Register (PCMLS)........................................196

14.2.13 PCM Right Surround Channel Data Register (PCMRS)......................................197

14.2.14 PCMLFE Data Register (PCMLFE) ....................................................................198

14.2.15 Line 2 Channel Data Register (LINE2)................................................................199

14.2.16 HSET Data Register (HSET) ...............................................................................200

14.2.17 IO Control/Status Data Register (IOCS)..............................................................201

14.2.18 AC97 Transmit Interrupt Enable Register (ATIER) ............................................202

14.2.19 AC97 TX FIFO Status Register ...........................................................................205

14.2.20 AC97 RX FIFO Interrupt Enable Register (ARIER) ...........................................208

14.2.21 AC97 RX Status Register (ARSR) .......................................................................211

14.2.22 AC97 Control Register (ACR).............................................................................213

14.2.23 AC97 TAG Register (ATAGR)............................................................................215

14.2.24 Slot Request Active Register (SRAR)..................................................................216

14.3 Function Description.........................................................................................................217

14.3.1 Internal Bus Interface...........................................................................................217

14.3.2 Clock Generator...................................................................................................217

14.3.3 CS4218 or CS4271 TX Controller.......................................................................218

14.3.4 CS4218 or CS4271 RX Controller....................................................................... 218

14.3.5 AC97 TX Controller.............................................................................................218

14.3.6 AC97 RX Controller ............................................................................................219

14.3.7 Miscellaneous Function Block.............................................................................219

14.3.8 Data Structure of Memory in DMA Mode...........................................................219

14.4 Program Flow....................................................................................................................220

Section 15 AFE Interface ..................................................................................229

15.1 Overview...........................................................................................................................229

15.1.1 Features................................................................................................................229

15.1.2 Block Diagram.....................................................................................................230

15.2 Register Description..........................................................................................................231

15.2.1 Control Register (CTR)........................................................................................232

15.2.2 Status Register (STR)...........................................................................................233

15.2.3 Transmit Data Register (TXDR)..........................................................................236

15.2.4 Receive Data Register (RXDR)............................................................................236

Rev. 3.0, 03/01, page v of xiii

Page 12

15.2.5 Transmit Data Buffers (TXDB0,1) ......................................................................236

15.2.6 Transmit Shift Register (TSFTR).........................................................................236

15.2.7 Receive Data Buffers (RXDB0,1)........................................................................237

15.2.8 Receive Shift Register (RSFTR)..........................................................................237

15.3 Data Transfer.....................................................................................................................237

15.3.1 Data Transmit.......................................................................................................237

15.3.2 Data Receive........................................................................................................238

15.4 Divider...............................................................................................................................239

15.5 External Chip Control Signal............................................................................................240

15.6 Interrupt.............................................................................................................................241

15.7 How to Use the Special Pin (RLYCNT, RING)................................................................ 242

15.7.1 How to use the RLYCNT pin...............................................................................242

15.7.2 How to Use the RING pin....................................................................................242

Section 16 Keyboard Controller Interface ........................................................ 243

16.1 Overview...........................................................................................................................243

16.1.1 Features................................................................................................................243

16.1.2 Block Diagram.....................................................................................................244

16.2 Register Description..........................................................................................................245

16.2.1 Control Register (CR) ..........................................................................................245

16.2.2 Status Register (SR).............................................................................................246

16.2.3 H8 Control 1 Register (H8C1R)...........................................................................247

16.2.4 H8 Control 2 Register (H8C2R)...........................................................................247

16.3 Function Description.........................................................................................................247

16.4 Timing Diagram................................................................................................................247

Section 17 PS/2 Interface.................................................................................. 249

17.1 Overview...........................................................................................................................249

17.2 Pin Configuration..............................................................................................................249

17.3 Registers Description ........................................................................................................249

17.3.1 Keyboard Control/Status Register (KBCSR).......................................................250

17.3.2 Keyboard Interrupt Status Register (KBISR).......................................................251

17.3.3 Mouse Control/Status Register (MSCSR)............................................................252

17.3.4 Mouse Interrupt Status Register (MSISR)............................................................253

17.4 Block Diagram ..................................................................................................................254

17.5 Operation...........................................................................................................................255

17.5.1 Serial Data Format...............................................................................................255

17.5.2 Software Operational Sequence...........................................................................255

17.5.3 Communication Protocol......................................................................................256

17.6 CAUTION.........................................................................................................................258

Section 18 USB Host Controller....................................................................... 259

18.1 Introduction.......................................................................................................................259

Rev. 3.0, 03/01, page vi of xiii

Page 13

18.1.1 Device Description / Purpose...............................................................................259

18.1.2 Reference Information..........................................................................................259

18.2 Function Description.........................................................................................................260

18.2.1 System Architecture.............................................................................................260

18.2.2 USB Host Controller............................................................................................261

18.2.3 USB Interface.......................................................................................................293

18.2.4 Power Management..............................................................................................315

18.2.5 Register/Address Summary..................................................................................316

Section 19 A/D Converter.................................................................................333

19.1 Overview...........................................................................................................................333

19.1.1 Features................................................................................................................333

19.1.2 Block Diagram.....................................................................................................334

19.1.3 Input Pins.............................................................................................................334

19.1.4 Register Configuration.........................................................................................335

19.2 Register Descriptions ........................................................................................................336

19.2.1 A/D Data Registers A to D (ADDRA to ADDRD, ADCAL)..............................336

19.2.2 A/D Control/Status Register (ADCSR)................................................................337

19.2.3 A/D Calibration Sample Control Register (ADCALCR).....................................338

19.3 Operation...........................................................................................................................339

19.3.1 Single Mode (SCAN = 0).....................................................................................339

19.3.2 Scan Mode (SCAN = 1).......................................................................................341

19.3.3 Input Sampling and A/D Conversion Time..........................................................343

19.3.4 A/D External Trigger Input Timing .....................................................................344

19.4 Interrupts...........................................................................................................................344

19.5 Usage Notes.......................................................................................................................345

19.6 A/D Conversion Characteristics........................................................................................345

19.7 Analog Input Pin Characteristics....................................................................................... 346

Section 20 Electrical Characteristics (VCC =3.3V±0.3V, VCCA, VCCB,

VCC5=5.0V±0.5V, Ta=0°C to 70°C, unit : ns) ...............................347

20.1 DC Electrical Characteristics ............................................................................................347

20.2 AC Characteristics.............................................................................................................349

Section 21 Recommended Reflow Condition ...................................................365

Section 22 Package Information........................................................................367

Section 23 Ordering Information.......................................................................369

Appendix .........................................................................................................371

Rev. 3.0, 03/01, page vii of xiii

Page 14

Tables

Table 4-1. HD64465BP Signal Names (by pin numbers in alphabetical order) ..........................15

Table 4-2. HD64465BQ Signal Names (by pin numbers in alphabetical order)..........................20

Table 4-3. Pin Descriptions of Test Mode Select.........................................................................25

Table 4-4. Pin Descriptions of CPU Interface..............................................................................25

Table 4-5. Pin Descriptions of PCMCIA 0 Interface................................................................... 27

Table 4-6. Pin Descriptions of PCMCIA 1 Interface................................................................... 29

Table 4-7. Pin Descriptions of UART 0.......................................................................................31

Table 4-8. Pin Description of IrDA..............................................................................................31

Table 4-9. Pin Descriptions of Printer Port Interface...................................................................32

Table 4-10. Pin Descriptions of AFE Interface............................................................................33

Table 4-11. Pin Descriptions of CODEC Interface......................................................................34

Table 4-12. Pin Descriptions of USB Interface............................................................................34

Table 4-13. Pin Descriptions of Keyboard Interface....................................................................35

Table 4-14. Pin Descriptions of IO Port A...................................................................................35

Table 4-15. Pin Description of IO Port B.....................................................................................36

Table 4-16. Pin Descriptions of IO Port C...................................................................................36

Table 4-17. Pin Descriptions of IO Port D...................................................................................37

Table 4-18. Pin Descriptions of IO Port E...................................................................................37

Table 4-19. Pin Descriptions of 10-bit ADC Interface.................................................................37

Table 4-20. Pin Descriptions of PS/2 Interface............................................................................38

Table 4-21. Pin Descriptions of System Reset Interface..............................................................38

Table 4-22. Pin Descriptions of Crystal Interface........................................................................38

Table 4-23. Pin Description of Miscellaneous Interface..............................................................38

Table 4-24. Pin Descriptions of LCD Interface ...........................................................................39

Table 4-25. Pin Descriptions of Power/Ground...........................................................................39

Table 6-1. The Register List of Power Management and System Configuration.........................52

Table 7-1. The List of I/O Port Pin Function Configurations......................................................67

Table 7-2. The List of Register Configurations...........................................................................69

Table 7-3. Control Bits Definition of the Port x Control Register

and Its Relevant READ/WRITE Operation of Port Data Register.........................73

Table 9-1. The Register List of Timer Module............................................................................91

Table 10-1. PC Card Controller Registers....................................................................................109

Table 11-1. Summary of FIR Controller Registers......................................................................133

Table 12-1. Serial Channel Registers...........................................................................................158

Table 12-2. Interrupt Identification Register................................................................................160

Table 12-3. Baud Rates Using (9.216MHz/5) Clock...................................................................162

Table 12-4. Modem Control Register Bits...................................................................................163

Table 12-5. Line Status Register Bits...........................................................................................165

Table 12-6. Modem Status Register Bits......................................................................................166

Table 12-7. Reset Control of Register and Pinout Signals...........................................................167

Table 13-1. The Register List of Parallel Port..............................................................................172

Table 13-2. Bit Map of the EPP Registers...................................................................................172

Rev. 3.0, 03/01, page viii of xiii

Page 15

Table 13-3. Status Port Register Description...............................................................................173

Table 13-4. Control Port Register Description.............................................................................173

Table 13-5. Bit Map of the ECP Mode Register..........................................................................174

Table 13-6. ECP Register Definition ...........................................................................................175

Table 13-7. ECP Mode Description.............................................................................................17 5

Table 14-1. Pin Function of Serial CODEC Interface Module....................................................183

Table 14-2. Registers of SCDI.....................................................................................................183

Table 14-3. AC97 Timing............................................................................................................227

Table 15-1. Pin Function of AFE Interface Module....................................................................231

Table 15-2. Registers of AFE Interface .......................................................................................231

Table 16-1. Pin Function of Keyboard Controller Interface Module...........................................235

Table 16-2. Keyboard Controller Interface Read Cycle AC Timing...........................................248

Table 16-3. Keyboard Controller Interface Write Cycle AC Timing...........................................248

Table 17-1. PS/2 Interface Control Registers...............................................................................249

Table 17-2. Data Receive Timing Parameters..............................................................................257

Table 17-3. Data Send Timing Parameters ..................................................................................258

Table 18-1. Example Calculation of R and Host Controller Action............................................275

Table 18-2. ITD Packet Offset Location......................................................................................276

Table 18-3. Completion Codes ....................................................................................................279

Table 18-4. Dword0 GTD Fields.................................................................................................282

Table 18-5. Dword0 ITD Fields...................................................................................................282

Table 18-6. Dword1 GTD Fields.................................................................................................282

Table 18-7. Dword1 ITD Fields...................................................................................................283

Table 18-8. Dword2 Fields ..........................................................................................................283

Table 18-9. Dword3 GTD Fields.................................................................................................283

Table 18-10. Dword3 ITD Fields.................................................................................................283

Table 18-11. Offset0 Field Description........................................................................................284

Table 18-12. List Processor Control Signals................................................................................285

Table 18-13. Transaction Control Information............................................................................294

Table 18-14. PID Encoding..........................................................................................................295

Table 18-15. Bus Time-out Periods.............................................................................................305

Table 18-16. SIE EOF Timing Requirements..............................................................................306

Table 18-17. SIE Completion Status............................................................................................308

Table 18-18. IN Transaction Error Response...............................................................................309

Table 18-19. OUT Transaction Error Response...........................................................................309

Table 18-20. Hub / Port Commands.............................................................................................310

Table 18-21. Power Switching Configurations............................................................................311

Table 18-22. HC Operational Register Summary........................................................................316

Table 18-23. HcRevision Register...............................................................................................317

Table 18-24. HcControl Register.................................................................................................318

Table 18-25. HcCommandStatus Register...................................................................................319

Table 18-26. HcInterruptStatus Register......................................................................................320

Table 18-27. HcInterrutpEnable Register....................................................................................321

Rev. 3.0, 03/01, page ix of xiii

Page 16

Table 18-28. HcInterruptDisable Register...................................................................................322

Table 18-29. HcHCCA Register..................................................................................................323

Table 18-30. HcPeriodCurrentED Register..................................................................................323

Table 18-31. HcControlHeadED..................................................................................................323

Table 18-32. HcControlCurrentED Register................................................................................324

Table 18-33. HcBulkHeadED Register........................................................................................324

Table 18-34. HcBulkCurrentED Register....................................................................................324

Table 18-35. HcDoneHead Register............................................................................................325

Table 18-36. HcFmInterval Register............................................................................................325

Table 18-37. HcFrameRemaining Register..................................................................................326

Table 18-38. HcFmNumberb Register.........................................................................................326

Table 18-39. HcPeriodicStart Register.........................................................................................326

Table 18-40. HcLSThreshold Register.........................................................................................327

Table 18-41. HcRhDescriptorA Register.....................................................................................328

Table 18-42. HcRhDescriptorB Register.....................................................................................329

Table 18-43. HcRhStatus Register...............................................................................................330

Table 18-44. HcRhPortStatus Register........................................................................................331

Table 19-1. A/D Converter Pins...................................................................................................334

Table 19-2. A/D Converter Registers...........................................................................................335

Table 19-3. Analog Input Channels and A/D Data Registers.......................................................336

Table 19-4. A/D Conversion Time (Single Mode).......................................................................344

Table 19-5. A/D Conversion Characteristics ...............................................................................345

Table 19-6. Analog Input Pin Characteristics..............................................................................346

Table 20-1. DC Electrical Characteristics (Ta=0°C to 70°C) ......................................................347

Table 20-2. CPU Interface AC Timing Spec. .............................................................................349

Table 20-3. Crystal/Oscillator and PLL Settle AC Timing Spec. ...............................................349

Table 20-4. GPIO AC Timing Spec. ...........................................................................................349

Table 20-5. I/O Port Interrupt AC Timing Spec. ........................................................................350

Table 20-6. PCMCIA AC Timing Spec. .....................................................................................350

Table 20-7. UART AC Timing Spec. .........................................................................................350

Table 20-8. Parallel Port AC Timing Spec. ................................................................................351

Table 20-9. SCDI AC Timing Spec. ...........................................................................................351

Table 20-10. AFE Interface AC Timing Spec. ............................................................................352

Table 20-11. KBC AC Timing Spec. ..........................................................................................352

Table 20-12. USB Host AC Timing Spec. ..................................................................................352

Table 20-13. AFECK Clock Input AC Timing Spec. (PLL1 : bypass) .......................................352

Table 20-14. AFECK Clock Input AC Timing Spec. (PLL1 : operating) ...................................353

Table 20-15. UCK Clock Input AC Timing Spec. (PLL2 : bypass) ...........................................353

Table 20-16. UCK Clock Input AC Timing Spec. (PLL2 : operating) .......................................353

Figures

Figure 5-1. CPU Interface Module Interconnection Diagram......................................................44

Figure 5-2. Low-Speed Basic Internal Peripheral Bus Access Timing........................................45

Rev. 3.0, 03/01, page x of xiii

Page 17

Figure 5-3. Low-Speed Internal Peripheral Bus Access Timing With TWe Phase...................... 46

Figure 5-4. High-Speed Basic Internal Peripheral Bus Access Timing.......................................47

Figure 5-5. High-Speed Internal Peripheral Bus Access Timing With TWe Phase.....................48

Figure 6-1. AFECK Related Clock Diagram...............................................................................59

Figure 6-2. UCK Related Clock Diagram....................................................................................60

Figure 6-3. System Hardware Reset Related Pins........................................................................65

Figure 6-4. Power-On Reset Diagram, tPORST=10ms................................................................65

Figure 6-5. SH4 Manual Reset Diagram, tM2PS=tM2PH=80ns, tMARST=10ms......................66

Figure 6-6. SH3 Manual Reset Diagram, tMARST=10ms..........................................................66

Figure 7-1. Pin Configuration of All Ports...................................................................................70

Figure 8-1. Block Diagram of the Interrupt Controller................................................................80

Figure 9-1. Block Diagram of Timer ...........................................................................................90

Figure 9-2. Interrupt Request Timer1/0r Timing Diagram in Case Prescale *1,

Timer1/0_clk=CKIO ..............................................................................................105

Figure 9-3. Interrupt Request Timer1/0r Timing Diagram in Case Prescale*1/4,

Timer1/0_clk = CKIO/4 .........................................................................................105

Figure 9-4. Interrupt Request Timer1/0r Timing Diagram in Case Prescale*1/8,

Timer1/0_clk = CKIO/8 .........................................................................................106

Figure 9-5. Interrupt Request Timer1/0r Timing Diagram in Case Prescale*1/16,

Timer1/0_clk = CKIO/16 .......................................................................................106

Figure 9-6. A/D Trigger Signal ADTRIG# Timing Diagram in Case Prescale 1,

Timer0_clk=CKIO..................................................................................................107

Figure 9-7. A/D Trigger Signal ADTRIG# Timing Diagram in Case Prescale 1/4,

Timer0_clk=CKIO/4 ..............................................................................................107

Figure 9-8. A/D Trigger Signal ADTRIG# Timing Diagram in Case Prescale 1/8,

Timer0_clk=CKIO/8 ..............................................................................................107

Figure 9-9. A/D Trigger Signal ADTRIG# Timing Diagram in Case Prescale 1/16,

Timer0_clk=CKIO/16 ............................................................................................107

Figure 9-10. PWM Signals...........................................................................................................108

Figure 11-1. Functional Block Diagram of FIR...........................................................................130

Figure 14-1. The Block Diagram of Serial CODEC Interface.....................................................182

Figure 14-2. Data Transfer Scheme in DMA TX Mode ..............................................................219

Figure 14-3. CS4218 or CS4271 TX Controller ..........................................................................220

Figure 14-4. CS4218 or CS4271 RX Controller..........................................................................220

Figure 14-5. AC97 TX Controller................................................................................................221

Figure 14-6. AC97 RX Controller ...............................................................................................222

Figure 14-7. TX Flow in PIO Mode for CS4218 or CS4271.......................................................223

Figure 14-8. RX Flow in PIO Mode for CS4218 or CS4271.......................................................224

Figure 14-9. AC97 DMA Program Flow.....................................................................................225

Figure 14-10. Warm/Cold Reset Timing......................................................................................226

Figure 14-11. Serial Data Setup, Hold and Output Delay Timing...............................................226

Figure 15-1. AFE Interface Block Diagram.................................................................................230

Figure 15-2. Divider Configuration.............................................................................................239

Rev. 3.0, 03/01, page xi of xiii

Page 18

Figure 15-3. HC1 Pin and Control Data Outputs.........................................................................240

Figure 15-4. TDEI Output Timing...............................................................................................241

Figure 15-5. RDFI Output Timing...............................................................................................242

Figure 16-1. H8 Keyboard Controller Interface Block Diagram..................................................244

Figure 16-2. Keyboard Controller Interface Read Timing...........................................................247

Figure 16-3. Keyboard Controller Interface Write Timing..........................................................247

Figure 17-1. PS/2 Keyboard/Mouse Interface Block Diagram....................................................254

Figure 17-2. Keyboard Serial Data Format..................................................................................255

Figure 17-3. Data Receive Timing...............................................................................................257

Figure 17-4. Data Send Timing....................................................................................................258

Figure 18-1. USB States...............................................................................................................261

Figure 18-2. List Priority within a USB Frame............................................................................264

Figure 18-3. Example of Control/Bulk Service Ratio of 4:1........................................................265

Figure 18-4. List Service Flow.....................................................................................................268

Figure 18-5. Endpoint Descriptor Service Flow ..........................................................................271

Figure 18-6. Endpoint Descriptor ................................................................................................273

Figure 18-7. Transfer Description Service Flow..........................................................................274

Figure 18-8. Standard Token Packet Format................................................................................296

Figure 18-9. SOF Token Packet Format......................................................................................296

Figure 18-10. Data Packet Format...............................................................................................297

Figure 18-11. Handshake Packet Format.....................................................................................297

Figure 18-12. Preamble Packet Format........................................................................................298

Figure 18-13. Serializer................................................................................................................299

Figure 18-14. CRC Logic.............................................................................................................300

Figure 18-15. Non-Isochronous Bus Transaction........................................................................304

Figure 18-16. Isochronous Bus Transaction.................................................................................305

Figure 19-1. A/D Converter Block Diagram................................................................................334

Figure 19-2. Example of A/D Converter Operation (Single Mode, Channel 1 Selected)............340

Figure 19-3. Example of A/D Converter Operation

(Scan Mode, Channels An0 to AN2 Selected)........................................................342

Figure 19-4. A/D Conversion Timing..........................................................................................343

Figure 19-5. External Trigger Input Timing ................................................................................344

Figure 19-6. Analog Input Pin RC Equivalent Circuit.................................................................346

Figure 20-1. CPU Write Cycle Timing Diagram.........................................................................354

Figure 20-2. CPU Read Cycle Timing Diagram..........................................................................354

Figure 20-3. Crystal/Oscillator and PLL Settle Timing Diagrams...............................................355

Figure 20-4. I/O Port Interrupt Timing (Falling Edge Trigger)...................................................355

Figure 20-5. I/O Port Interrupt Timing (Rising Edge Trigger) ....................................................356

Figure 20-6. IRQ0#/TMO0# Timing For Timer..........................................................................356

Figure 20-7. IRQ0#/TMO1# Timing For Timer..........................................................................356

Figure 20-8. DREQ0# / DREQ1# Timing ...................................................................................356

Figure 20-9. PCMCIA I/O Bus Cycle (NO Wait)........................................................................357

Figure 20-10. PCMCIA Memory Bus Cycle (No Wait)..............................................................358

Rev. 3.0, 03/01, page xii of xiii

Page 19

Figure 20-11. UART DTR, RTS Timing.....................................................................................358

Figure 20-12. UART Rx Timing..................................................................................................359

Figure 20-13. Control Signal Delay Time of Parallel Port Timing..............................................359

Figure 20-14. EPP Address or Data Write Timing ......................................................................359

Figure 20-15. EPP Address or Data Read Timing.......................................................................360

Figure 20-16. ECP Parallel Port Forward Timing........................................................................360

Figure 20-17. ECP Parallel Port Backward Timing.....................................................................360

Figure 20-18. SCDI DMA Request Timing.................................................................................361

Figure 20-19. Cold Reset Timing.................................................................................................361

Figure 20-20. Warm Reset Timing ..............................................................................................361

Figure 20-21. SCDI Sync and Data Timing .................................................................................362

Figure 20-22. AFE Interface Access Timing...............................................................................362

Figure 20-23. Keyboard Controller Interface Read Timing.........................................................363

Figure 20-24. Keyboard Controller Interface Write Timing........................................................363

Figure 20-25. USB Over-Current Detect to Power Down Timing...............................................363

Figure 20-26. AFECK Clock Input Timing.................................................................................363

Figure 20-27. UCK Clock Input Timing......................................................................................364

Figure 22-1. HD64465BP Package Dimensions..........................................................................367

Figure 22-2. HD64465BQ Package Dimensions.........................................................................368

Rev. 3.0, 03/01, page xiii of xiii

Page 20

Section 1 Features

1.1 CPU Interface

Supports Hitachi SH-4/SH7709/SH3-DSP family of CPUs with bus speeds from 15 MHz up to

•

66 MHz.

Supports STANDBY mode when CKIO is stopped.

•

Memory mapped on area 4 of SH4/SH7709/SH3DSP for internal registers

•

3.3 V-CMOS interface

•

32 - bit data interface

•

1.2 PCMCIA Controller

PCMCIA PC card standard v2.1 compliant

•

Supports dual PCMCIA memory or IO cards at SH4/SH7709/SH3-DSP area 5 and area 6

•

8- or 16-bit PCMCIA interface support

•

Mixed voltage (3.3V or 5V) operation is fully supported for PCMCIA address, data and control

•

signals.

Supports TI TPS2206 serial interface

•

Supports STANDBY mode

•

1.3 AFE Interface

Supports SGS-THOMSON STLC7546 and STLC7550 interface

•

Read buffer and write buffer are provided for performance enhancement

•

Supports STANDBY mode

•

1.4 GPIO Function(Port Interrupt)

GPIO pins can be programmed as input, output ports, or as interrupt inputs.

•

Internal pull-up resistor ON/OFF control

•

Interrupt events can be independently generated or masked on each I/O pin.

•

Interrupt can be independently programmed to rising edge or falling edge trigger

•

Power down control by software (input gated and output floating)

•

Maximum 40 bits for I/O port functions

•

Rev. 3.0, 03/01, page 1 of 390

Page 21

1.5 Interrupt Controller

Provides an interrupt to SH-4/SH7709/SH3-DSP, which is generated by an internal module

•

interrupt request

Module interrupts can be masked on/off by setting the registers.

•

1.6 Power Management

Supports STANDBY mode to stop clock for each module

•

All clock inputs can be stopped

•

All built-in PLLs can be set to STANDBY mode

•

The CPU input signals can be gated

•

1.7 Timer

2-channel 16-bit auto-reloaded timer with pre-scale (1, 1/4, 1/8, 1/16) for dividing CKIO

•

Supports generating DMA or Interrupt request whenever timer’s count reaches zero

•

Supports generating ADC external trigger whenever timer’s count reaches zero

•

Provides two-channel Pulse Width Modulation (PWM) for VR control of LCD.

•

Supports STANDBY mode

•

1.8 Keyboard Controller Interface

Supports ISA-bus-like interface to pair with the external keyboard controller

•

Supports 2 channels of PS/2 interface to connect PS/2 device like keyboard and mouse.

•

Supports STANDBY mode

•

1.9 UART

Standard 16550 compatible full spec UART

•

Supports one channel of serial port

•

Supports STANDBY mode

•

Rev. 3.0, 03/01, page 2 of 390

Page 22

1.10 Printer interface

Supports three access modes, SPP, EPP and ECP(ECP mode only supports PIO mode)

•

5V interface to printer

•

Supports STANDBY mode

•

1.11 Audio CODEC Interface

Directly interfaced to CS4271/CS4218/AC97 Codec for controlling voice data to the speaker,

•

or from the mic.

Dual TX/RX FIFO ( 8 × 32 -bit) are supported for CS4271/CS4218 interface

•

12-channel TX FIFO (4 × 20-bit) and 9-channel RX FIFO ( 4 × 20 -bit) are supported for AC97

•

Codec interface

Voice captures and playbacks can be supported by PIO or DMA mode access.

•

The Codec Interface is able to provide SM3 Slave Mode for communication with CS4218 and

•

CS4271, and SM3 Master Mode for CS4218.

Supports AC97 version 1.03 and version 2.0 serial-link interface

•

Supports STANDBY mode

•

1.12 IrDA

Supports HP SIR or ASKIR infrared interface

•

Supports FIR and MIR

•

Provides DMA channel mode for FIR

•

Supports STANDBY mode

•

1.13 Clock Generator and PLL

Provides a × 4 PLL from 12 MHz to 48 MHz for USB, IrDA, and Parallel Port

•

Provides a × 3 PLL from 12.288 MHz to 36.864 MHz for AFE, CS4218/CS4271/AC97 codec

•

interface

12.288 MHz clock input for AFE interface, CODEC interface, USB, IrDA and Parallel Port

•

Each clock generator and PLL supports STANDBY mode

•

Rev. 3.0, 03/01, page 3 of 390

Page 23

1.14 USB Host Controller

Supports direct interfaces of 2 USB ports

•

Supports device bandwidth of 12Mbps or 1.5Mbps

•

Supports power management mode to protect USB Bus power; and over-current detector to

•

protect USB Bus from abnormal over-current load

Fully compatible with the USB specification version 1.0 and register compatible with Open

•

Host Controller Interface (OHCI) specification version v1.0 issued by Microsoft, Compaq and

NS

4 K-byte SRAM provided for USB Open Host Controller driver to store frame lists, transaction

•

descriptors for USB host controller’s schedule control and this local memory is also used as

data buffer for host controller to send/receive data to/from USB devices

1.15 10-bit ADC

10-bit resolution

•

Provides four input channels

•

High-speed conversion, conversion time is maximum 10 µs per channel

•

Two conversion modes

•

Single mode: one channel A/D conversions are supported.

Scan mode: continuous conversions are operated in cycles from one to four channels.

A/D conversion can be triggered by timer or software

•

Supports STANDBY mode

•

1.16 Package

387-pin BGA (35 mm × 35 mm: HD64465BP)

•

387-pin BGA (27 mm × 27 mm: HD64465BQ)

•

Rev. 3.0, 03/01, page 4 of 390

Page 24

Section 2 General Description

The HD64465 is directly connected to SH-4/SH7709/SH3-DSP, and consists of PCMCIA

controller, analog front end (AFE) interface, I/O port controller, timer, UART, parallel port

interface controller, keyboard interface, CS4218/CS4271/AC97 Codec interface, IrDA controller,

USB Host controller, AC97 Codec, 10-bit ADC and power management unit. This chip pairs with

SH-4/SH7709/SH3-DSP processors, and features all the key peripheral functions required by the

sub sub-notebooks designed for Windows

Windows

®

CE Mini NoteBook (SubsubNoteBook) PC system.

®

CE v2.0 and above, providing a total solution for

Rev. 3.0, 03/01, page 5 of 390

Page 25

Rev. 3.0, 03/01, page 6 of 390

Page 26

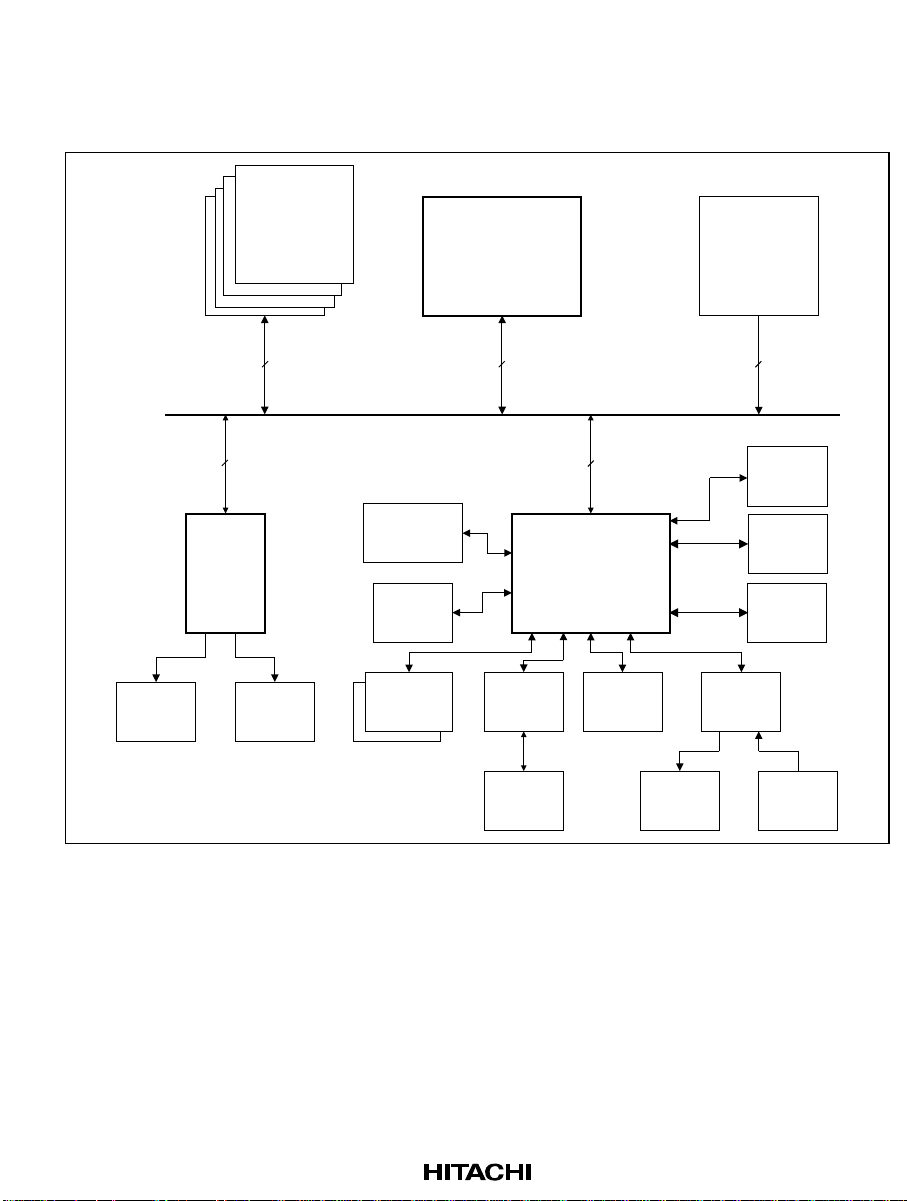

Section 3 System Block Diagram

3.1 Application Circuit

DRAM

SH-4/SH7709

ROM

KEYBOARD

8

Keyboard

Controller

32

TOUCH

PAD

UART

PRINTER

PCMCIA 0

32 32

32

HD64465

STLC7546

DAA

USB

Devices

SPEAKER

CS4218/

CS4271/

AC97

Touch

Panel

IrDA

PS/2

Keyboard

MIC

Rev. 3.0, 03/01, page 7 of 390

Page 27

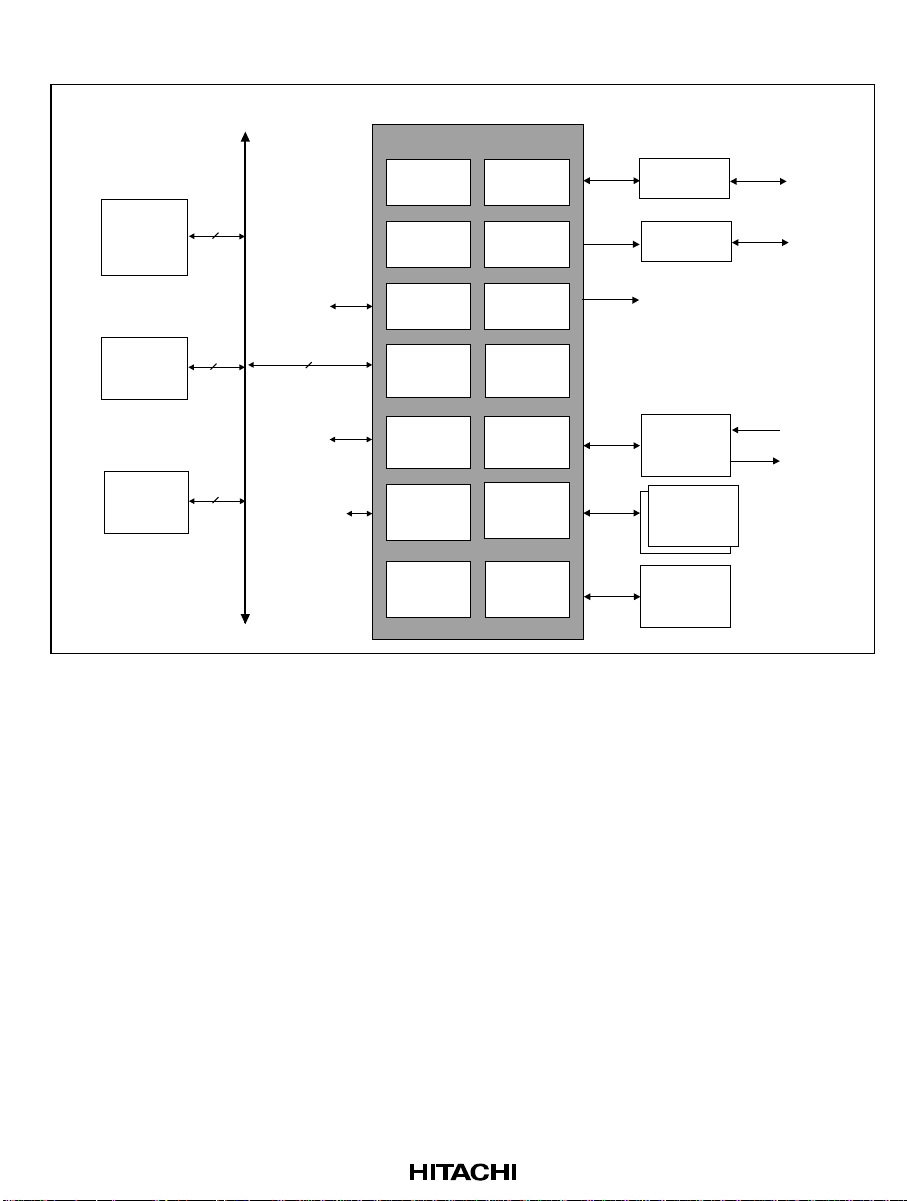

3.2 System Block Diagram

HD64465

Timer & PMU

AFE I/F

STLC7546/7550

AFE

To Public Line

SH-4/SH7709/

SH3-DSP

DRAM

ROM

32

32

32

To Host PC

32

To Host PC

To USB Devices

INTC KBC I/F

UART

Clock Gen &

PLL

IrDA CODEC I/F

USB Host

controller

GPIO(40)

PCMCIA +

Printer I/F

PS/2

Buffers