Page 1

查询H8/3640供应商查询H8/3640供应商

H8/3644 Series

H8/3644

HD6473644, HD6433644

H8/3643

HD6433643

H8/3642

HD6433642

H8/3641

HD6433641

H8/3640

HD6433640

ADE-602-087C

Rev. 4.0

08/08/98

Hitachi, Ltd.

MC-Setsu

H8/3644F-ZTAT™

HD64F3644

H8/3643F-ZTAT™

HD64F3643

H8/3642AF-ZTAT™

HD64F3642A

Hardware Manual

Page 2

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party’s

rights, including intellectual property rights, in connection with use of the information

contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you

have received the latest product standards or specifications before final design, purchase or

use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability.

However, contact Hitachi’s sales office before using the product in an application that

demands especially high quality and reliability or where its failure or malfunction may directly

threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear

power, combustion control, transportation, traffic, safety equipment or medical equipment for

life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi

particularly for maximum rating, operating supply voltage range, heat radiation characteristics,

installation conditions and other characteristics. Hitachi bears no responsibility for failure or

damage when used beyond the guaranteed ranges. Even within the guaranteed ranges,

consider normally foreseeable failure rates or failure modes in semiconductor devices and

employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi

product does not cause bodily injury, fire or other consequential damage due to operation of

the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi

semiconductor products.

Page 3

Preface

The H8/300L Series of single-chip microcomputers has the high-speed H8/300L CPU at its core,

with many necessary peripheral functions on-chip. The H8/300L CPU instruction set is compatible

with the H8/300 CPU.

The H8/3644 Series has a system-on-a-chip architecture that includes such peripheral functions as

a D/A converter, five timers, a 14-bit PWM, a two-channel serial communication interface, and an

A/D converter. This makes it ideal for use in advanced control systems.

This manual describes the hardware of the H8/3644 Series. For details on the H8/3644 Series

instruction set, refer to the H8/300L Series Programming Manual.

Page 4

Contents

Section 1 Overview........................................................................................................... 1

1.1 Overview............................................................................................................................ 1

1.2 Internal Block Diagram ..................................................................................................... 5

1.3 Pin Arrangement and Functions........................................................................................ 6

1.3.1 Pin Arrangement .................................................................................................. 6

1.3.2 Pin Functions........................................................................................................ 9

Section 2 CPU..................................................................................................................... 15

2.1 Overview............................................................................................................................ 15

2.1.1 Features ................................................................................................................ 15

2.1.2 Address Space ...................................................................................................... 16

2.1.3 Register Configuration ......................................................................................... 16

2.2 Register Descriptions......................................................................................................... 17

2.2.1 General Registers.................................................................................................. 17

2.2.2 Control Registers.................................................................................................. 17

2.2.3 Initial Register Values.......................................................................................... 19

2.3 Data Formats...................................................................................................................... 19

2.3.1 Data Formats in General Registers....................................................................... 20

2.3.2 Memory Data Formats.......................................................................................... 21

2.4 Addressing Modes............................................................................................................. 22

2.4.1 Addressing Modes................................................................................................ 22

2.4.2 Effective Address Calculation.............................................................................. 24

2.5 Instruction Set.................................................................................................................... 28

2.5.1 Data Transfer Instructions.................................................................................... 30

2.5.2 Arithmetic Operations.......................................................................................... 32

2.5.3 Logic Operations.................................................................................................. 33

2.5.4 Shift Operations.................................................................................................... 33

2.5.5 Bit Manipulations................................................................................................. 35

2.5.6 Branching Instructions.......................................................................................... 39

2.5.7 System Control Instructions ................................................................................. 41

2.5.8 Block Data Transfer Instruction ........................................................................... 42

2.6 Basic Operational Timing.................................................................................................. 44

2.6.1 Access to On-Chip Memory (RAM, ROM)......................................................... 44

2.6.2 Access to On-Chip Peripheral Modules ............................................................... 45

2.7 CPU States......................................................................................................................... 46

2.7.1 Overview.............................................................................................................. 46

2.7.2 Program Execution State...................................................................................... 48

2.7.3 Program Halt State ............................................................................................... 48

2.7.4 Exception-Handling State .................................................................................... 48

i

Page 5

2.8 Memory Map..................................................................................................................... 49

2.9 Application Notes.............................................................................................................. 50

2.9.1 Notes on Data Access........................................................................................... 50

2.9.2 Notes on Bit Manipulation ................................................................................... 52

2.9.3 Notes on Use of the EEPMOV Instruction .......................................................... 58

Section 3 Exception Handling........................................................................................ 59

3.1 Overview............................................................................................................................ 59

3.2 Reset.................................................................................................................................. 59

3.2.1 Overview.............................................................................................................. 59

3.2.2 Reset Sequence..................................................................................................... 59

3.2.3 Interrupt Immediately after Reset ........................................................................ 61

3.3 Interrupts............................................................................................................................ 61

3.3.1 Overview.............................................................................................................. 61

3.3.2 Interrupt Control Registers................................................................................... 63

3.3.3 External Interrupts................................................................................................ 72

3.3.4 Internal Interrupts................................................................................................. 72

3.3.5 Interrupt Operations.............................................................................................. 73

3.3.6 Interrupt Response Time ...................................................................................... 78

3.4 Application Notes.............................................................................................................. 79

3.4.1 Notes on Stack Area Use...................................................................................... 79

3.4.2 Notes on Rewriting Port Mode Registers............................................................. 80

Section 4 Clock Pulse Generators................................................................................. 83

4.1 Overview............................................................................................................................ 83

4.1.1 Block Diagram...................................................................................................... 83

4.1.2 System Clock and Subclock ................................................................................. 83

4.2 System Clock Generator.................................................................................................... 84

4.3 Subclock Generator ........................................................................................................... 87

4.4 Prescalers........................................................................................................................... 88

4.5 Note on Oscillators............................................................................................................ 88

Section 5 Power-Down Modes...................................................................................... 89

5.1 Overview............................................................................................................................ 89

5.1.1 System Control Registers ..................................................................................... 92

5.2 Sleep Mode........................................................................................................................ 96

5.2.1 Transition to Sleep Mode ..................................................................................... 96

5.2.2 Clearing Sleep Mode............................................................................................ 96

5.2.3 Clock Frequency in Sleep (Medium-Speed) Mode.............................................. 96

5.3 Standby Mode.................................................................................................................... 97

5.3.1 Transition to Standby Mode ................................................................................. 97

5.3.2 Clearing Standby Mode........................................................................................ 97

5.3.3 Oscillator Settling Time after Standby Mode is Cleared...................................... 98

ii

Page 6

5.4 Watch Mode ...................................................................................................................... 99

5.4.1 Transition to Watch Mode.................................................................................... 99

5.4.2 Clearing Watch Mode .......................................................................................... 99

5.4.3 Oscillator Settling Time after Watch Mode is Cleared........................................ 99

5.5 Subsleep Mode .................................................................................................................. 100

5.5.1 Transition to Subsleep Mode................................................................................ 100

5.5.2 Clearing Subsleep Mode ...................................................................................... 100

5.6 Subactive Mode................................................................................................................. 101

5.6.1 Transition to Subactive Mode .............................................................................. 101

5.6.2 Clearing Subactive Mode ..................................................................................... 101

5.6.3 Operating Frequency in Subactive Mode............................................................. 101

5.7 Active (Medium-Speed) Mode.......................................................................................... 102

5.7.1 Transition to Active (Medium-Speed) Mode ....................................................... 102

5.7.2 Clearing Active (Medium-Speed) Mode.............................................................. 102

5.7.3 Operating Frequency in Active (Medium-Speed) Mode...................................... 102

5.8 Direct Transfer................................................................................................................... 103

Section 6 ROM................................................................................................................... 105

6.1 Overview............................................................................................................................ 105

6.1.1 Block Diagram...................................................................................................... 105

6.2 PROM Mode...................................................................................................................... 106

6.2.1 Setting to PROM Mode........................................................................................ 106

6.2.2 Socket Adapter Pin Arrangement and Memory Map........................................... 106

6.3 Programming ..................................................................................................................... 108

6.3.1 Writing and Verifying .......................................................................................... 109

6.3.2 Programming Precautions .................................................................................... 112

6.3.3 Reliability of Programmed Data .......................................................................... 113

6.4 Flash Memory Overview................................................................................................... 113

6.4.1 Principle of Flash Memory Operation.................................................................. 113

6.4.2 Mode Pin Settings and ROM Space ..................................................................... 114

6.4.3 Features ................................................................................................................ 115

6.4.4 Block Diagram...................................................................................................... 116

6.4.5 Pin Configuration ................................................................................................. 117

6.4.6 Register Configuration ......................................................................................... 117

6.5 Flash Memory Register Descriptions................................................................................ 118

6.5.1 Flash Memory Control Register (FLMCR).......................................................... 118

6.5.2 Erase Block Register 1 (EBR1)............................................................................ 120

6.5.3 Erase Block Register 2 (EBR2)............................................................................ 121

6.6 On-Board Programming Modes........................................................................................ 123

6.6.1 Boot Mode............................................................................................................ 123

6.6.2 User Program Mode ............................................................................................. 128

6.7 Programming and Erasing Flash Memory......................................................................... 130

6.7.1 Program Mode...................................................................................................... 130

iii

Page 7

6.7.2 Program-Verify Mode.......................................................................................... 131

6.7.3 Programming Flowchart and Sample Program .................................................... 132

6.7.4 Erase Mode........................................................................................................... 135

6.7.5 Erase-Verify Mode............................................................................................... 135

6.7.6 Erase Flowcharts and Sample Programs .............................................................. 136

6.7.7 Prewrite-Verify Mode .......................................................................................... 149

6.7.8 Protect Modes....................................................................................................... 149

6.7.9 Interrupt Handling during Flash Memory Programming/Erasing........................ 150

6.8 Flash Memory PROM Mode (H8/3644F, H8/3643F, and H8/3642AF)........................... 151

6.8.1 PROM Mode Setting............................................................................................ 151

6.8.2 Socket Adapter and Memory Map ....................................................................... 151

6.8.3 Operation in PROM Mode ................................................................................... 154

6.9 Flash Memory Programming and Erasing Precautions..................................................... 163

Section 7 RAM................................................................................................................... 169

7.1 Overview............................................................................................................................ 169

7.1.1 Block Diagram...................................................................................................... 169

Section 8 I/O Ports ............................................................................................................ 171

8.1 Overview............................................................................................................................ 171

8.2 Port 1.................................................................................................................................. 173

8.2.1 Overview.............................................................................................................. 173

8.2.2 Register Configuration and Description............................................................... 173

8.2.3 Pin Functions........................................................................................................ 177

8.2.4 Pin States.............................................................................................................. 178

8.2.5 MOS Input Pull-Up .............................................................................................. 178

8.3 Port 2.................................................................................................................................. 179

8.3.1 Overview.............................................................................................................. 179

8.3.2 Register Configuration and Description............................................................... 179

8.3.3 Pin Functions........................................................................................................ 181

8.3.4 Pin States.............................................................................................................. 181

8.4 Port 3.................................................................................................................................. 182

8.4.1 Overview.............................................................................................................. 182

8.4.2 Register Configuration and Description............................................................... 182

8.4.3 Pin Functions........................................................................................................ 186

8.4.4 Pin States.............................................................................................................. 187

8.4.5 MOS Input Pull-Up .............................................................................................. 187

8.5 Port 5.................................................................................................................................. 188

8.5.1 Overview.............................................................................................................. 188

8.5.2 Register Configuration and Description............................................................... 188

8.5.3 Pin Functions........................................................................................................ 190

8.5.4 Pin States.............................................................................................................. 191

8.5.5 MOS Input Pull-Up .............................................................................................. 191

iv

Page 8

8.6 Port 6.................................................................................................................................. 192

8.6.1 Overview.............................................................................................................. 192

8.6.2 Register Configuration and Description............................................................... 192

8.6.3 Pin Functions........................................................................................................ 193

8.6.4 Pin States.............................................................................................................. 194

8.7 Port 7.................................................................................................................................. 195

8.7.1 Overview.............................................................................................................. 195

8.7.2 Register Configuration and Description............................................................... 195

8.7.3 Pin Functions........................................................................................................ 197

8.7.4 Pin States.............................................................................................................. 197

8.8 Port 8.................................................................................................................................. 198

8.8.1 Overview.............................................................................................................. 198

8.8.2 Register Configuration and Description............................................................... 198

8.8.3 Pin Functions........................................................................................................ 200

8.8.4 Pin States.............................................................................................................. 201

8.9 Port 9.................................................................................................................................. 202

8.9.1 Overview.............................................................................................................. 202

8.9.2 Register Configuration and Description............................................................... 202

8.9.3 Pin Functions........................................................................................................ 204

8.9.4 Pin States.............................................................................................................. 204

8.10 Port B................................................................................................................................. 205

8.10.1 Overview.............................................................................................................. 205

8.10.2 Register Configuration and Description............................................................... 205

8.10.3 Pin Functions........................................................................................................ 206

8.10.4 Pin States.............................................................................................................. 206

Section 9 Timers................................................................................................................ 207

9.1 Overview............................................................................................................................ 207

9.2 Timer A.............................................................................................................................. 208

9.2.1 Overview.............................................................................................................. 208

9.2.2 Register Descriptions............................................................................................ 210

9.2.3 Timer Operation ................................................................................................... 212

9.2.4 Timer A Operation States..................................................................................... 213

9.3 Timer B1............................................................................................................................ 214

9.3.1 Overview.............................................................................................................. 214

9.3.2 Register Descriptions............................................................................................ 215

9.3.3 Timer Operation ................................................................................................... 217

9.3.4 Timer B1 Operation States ................................................................................... 218

9.4 Timer V.............................................................................................................................. 219

9.4.1 Overview.............................................................................................................. 219

9.4.2 Register Descriptions............................................................................................ 222

9.4.3 Timer Operation ................................................................................................... 228

9.4.4 Timer V Operation Modes.................................................................................... 233

v

Page 9

9.4.5 Interrupt Sources .................................................................................................. 233

9.4.6 Application Examples .......................................................................................... 234

9.4.7 Application Notes................................................................................................. 236

9.5 Timer X.............................................................................................................................. 242

9.5.1 Overview.............................................................................................................. 242

9.5.2 Register Descriptions............................................................................................ 246

9.5.3 CPU Interface....................................................................................................... 257

9.5.4 Timer Operation ................................................................................................... 260

9.5.5 Timer X Operation Modes.................................................................................... 267

9.5.6 Interrupt Sources .................................................................................................. 267

9.5.7 Timer X Application Example ............................................................................. 268

9.5.8 Application Notes................................................................................................. 269

9.6 Watchdog Timer................................................................................................................ 274

9.6.1 Overview.............................................................................................................. 274

9.6.2 Register Descriptions............................................................................................ 275

9.6.3 Timer Operation ................................................................................................... 278

9.6.4 Watchdog Timer Operation States ....................................................................... 279

Section 10 Serial Communication Interface................................................................ 281

10.1 Overview............................................................................................................................ 281

10.2 SCI1................................................................................................................................... 281

10.2.1 Overview.............................................................................................................. 281

10.2.2 Register Descriptions............................................................................................ 284

10.2.3 Operation in Synchronous Mode.......................................................................... 288

10.2.4 Operation in SSB Mode........................................................................................ 291

10.2.5 Interrupts .............................................................................................................. 293

10.3 SCI3................................................................................................................................... 293

10.3.1 Overview.............................................................................................................. 293

10.3.2 Register Descriptions............................................................................................ 296

10.3.3 Operation.............................................................................................................. 314

10.3.4 Operation in Asynchronous Mode........................................................................ 318

10.3.5 Operation in Synchronous Mode.......................................................................... 327

10.3.6 Multiprocessor Communication Function............................................................ 334

10.3.7 Interrupts .............................................................................................................. 341

10.3.8 Application Notes................................................................................................. 342

Section 11 14-Bit PWM..................................................................................................... 347

11.1 Overview............................................................................................................................ 347

11.1.1 Features ................................................................................................................ 347

11.1.2 Block Diagram...................................................................................................... 347

11.1.3 Pin Configuration ................................................................................................. 348

11.1.4 Register Configuration........................................................................................ 348

11.2 Register Descriptions......................................................................................................... 348

vi

Page 10

11.2.1 PWM Control Register (PWCR).......................................................................... 348

11.2.2 PWM Data Registers U and L (PWDRU, PWDRL)............................................ 349

11.3 Operation ........................................................................................................................... 350

Section 12 A/D Converter ................................................................................................. 351

12.1 Overview............................................................................................................................ 351

12.1.1 Features ................................................................................................................ 351

12.1.2 Block Diagram...................................................................................................... 352

12.1.3 Pin Configuration ................................................................................................. 353

12.1.4 Register Configuration ......................................................................................... 353

12.2 Register Descriptions......................................................................................................... 354

12.2.1 A/D Result Register (ADRR)............................................................................... 354

12.2.2 A/D Mode Register (AMR).................................................................................. 354

12.2.3 A/D Start Register (ADSR).................................................................................. 356

12.3 Operation ........................................................................................................................... 357

12.3.1 A/D Conversion Operation................................................................................... 357

12.3.2 Start of A/D Conversion by External Trigger Input............................................. 357

12.4 Interrupts............................................................................................................................ 358

12.5 Typical Use........................................................................................................................ 358

12.6 Application Notes.............................................................................................................. 361

Section 13 Electrical Characteristics.............................................................................. 363

13.1 Absolute Maximum Ratings.............................................................................................. 363

13.2 Electrical Characteristics (ZTAT™, Mask ROM Version)............................................... 364

13.2.1 Power Supply Voltage and Operating Range....................................................... 364

13.2.2 DC Characteristics (HD6473644)........................................................................ 367

13.2.3 AC Characteristics (HD6473644)........................................................................ 373

13.2.4 DC Characteristics (HD6433644, HD6433643, HD6433642, HD6433641,

HD6433640)......................................................................................................... 376

13.2.5 AC Characteristics (HD6433644, HD6433643, HD6433642, HD6433641,

HD6433640)......................................................................................................... 381

13.2.6 A/D Converter Characteristics ............................................................................. 385

13.3 Electrical Characteristics (F-ZTAT™ Version)................................................................ 386

13.3.1 Power Supply Voltage and Operating Range....................................................... 386

13.3.2 DC Characteristics (HD64F3644, HD64F3643, HD64F3642A) ......................... 389

13.3.3 AC Characteristics (HD64F3644, HD64F3643, HD64F3642A) ......................... 395

13.3.4 A/D Converter Characteristics ............................................................................. 398

13.4 Operation Timing .............................................................................................................. 399

13.5 Output Load Circuit........................................................................................................... 402

Appendix A CPU Instruction Set.................................................................................... 403

A.1 Instructions........................................................................................................................ 403

A.2 Operation Code Map.......................................................................................................... 411

vii

Page 11

A.3 Number of Execution States.............................................................................................. 413

Appendix B Internal I/O Registers................................................................................. 420

B.1 Addresses........................................................................................................................... 420

B.2 Functions............................................................................................................................ 424

Appendix C I/O Port Block Diagrams.......................................................................... 471

C.1 Block Diagrams of Port 1.................................................................................................. 471

C.2 Block Diagrams of Port 2.................................................................................................. 475

C.3 Block Diagrams of Port 3.................................................................................................. 478

C.4 Block Diagrams of Port 5.................................................................................................. 481

C.5 Block Diagram of Port 6.................................................................................................... 484

C.6 Block Diagrams of Port 7.................................................................................................. 485

C.7 Block Diagrams of Port 8.................................................................................................. 489

C.8 Block Diagram of Port 9.................................................................................................... 497

C.9 Block Diagram of Port B................................................................................................... 498

Appendix D Port States in the Different Processing States.................................... 499

Appendix E Product Code Lineup................................................................................. 500

Appendix F Package Dimensions.................................................................................. 501

viii

Page 12

Section 1 Overview

1.1 Overview

The H8/300L Series is a series of single-chip microcomputers (MCU: microcomputer unit), built

around the high-speed H8/300L CPU and equipped with peripheral system functions on-chip.

Within the H8/300L Series, the H8/3644 Series of microcomputers are equipped with a UART

(Universal Asynchronous Receiver/Transmitter). Other on-chip peripheral functions include five

timers, a 14-bit pulse width modulator (PWM), two serial communication interface channels, and

an A/D converter, providing an ideal configuration as a microcomputer for embedding in highlevel control systems. In addition to the mask ROM version, the H8/3644 is also available in a

ZTAT™*1 version with on-chip user-programmable PROM, and an F-ZTAT™*2 version with onchip flash memory that can be programmed on-board. Table 1 summarizes the features of the

H8/3644 Series.

Notes: 1. ZTAT is a trademark of Hitachi, Ltd.

2. F-ZTAT is a registered trademark of Hitachi, Ltd.

1

Page 13

Table 1.1 Features

Item Description

CPU High-speed H8/300L CPU

• General-register architecture

General registers: Sixteen 8-bit registers (can be used as eight 16-bit

registers)

• Operating speed

Max. operation speed: 5 MHz (mask ROM and ZTAT versions)

8 MHz (F-ZTAT version)

Add/subtract: 0.4 µs (operating at ø = 5 MHz)

0.25 µs (operating at ø = 8 MHz)

Multiply/divide: 2.8 µs (operating at ø = 5 MHz)

1.75 µs (operating at ø = 8 MHz)

Can run on 32.768 kHz subclock

• Instruction set compatible with H8/300 CPU

Instruction length of 2 bytes or 4 bytes

Basic arithmetic operations between registers

MOV instruction for data transfer between memory and registers

• Typical instructions

Multiply (8 bits × 8 bits)

Divide (16 bits ÷ 8 bits)

Bit accumulator

Register-indirect designation of bit position

Interrupts 33 interrupt sources

• 12 external interrupt sources (IRQ

• 21 internal interrupt sources

Clock pulse

generators

Power-down

modes

Note: *Values in parentheses are for the F-ZTAT version.

Two on-chip clock pulse generators

• System clock pulse generator: 1 to 10 MHz (1 to 16 MHz)*

• Crystal or ceramic resonator: 2 to 10 MHz (2 to 16 MHz)*

• External clock input: 1 to 10 MHz (1 to 16 MHz)*

Seven power-down modes

• Sleep (high-speed) mode

• Sleep (medium-speed) mode

• Standby mode

• Watch mode

• Subsleep mode

• Subactive mode

• Active (medium-speed) mode

to IRQ0, INT7 to INT0)

3

2

Page 14

Table 1.1 Features (cont)

Item Description

Memory Large on-chip memory

• H8/3644: 32-kbyte ROM, 1-kbyte RAM

• H8/3643: 24-kbyte ROM, 1-kbyte RAM

• H8/3642: 16-kbyte ROM, 512 byte RAM (1-kbyte RAM F-ZTAT version)

• H8/3641: 12-kbyte ROM, 512 byte RAM

• H8/3640: 8-kbyte ROM, 512 byte RAM

I/O ports 53 pins

• 45 I/O pins

• 8 input pins

Timers Five on-chip timers

• Timer A: 8-bit timer

Count-up timer with selection of eight internal clock signals divided from the

system clock (ø)* and four clock signals divided from the watch clock (ø

• Timer B1: 8-bit timer

Count-up timer with selection of seven internal clock signals or event

input from external pin

Auto-reloading

• Timer V: 8-bit timer

Count-up timer with selection of six internal clock signals or event input

from external pin

Compare-match waveform output

Externally triggerable

• Timer X: 16-bit timer

Count-up timer with selection of three internal clock signals or event

input from external pin

Output compare (2 output pins)

Input capture (4 input pins)

• Watchdog timer

Reset signal generated by 8-bit counter overflow

)*

w

Note: *ø and ø

are defined in section 4, Clock Pulse Generators.

W

3

Page 15

Table 1.1 Features (cont)

Item Description

Serial

communication

interface

14-bit PWM Pulse-division PWM output for reduced ripple

A/D converter Successive approximations using a resistance ladder

Product lineup Product Code

Two on-chip serial communication interface channels

• SCI1: synchronous serial interface

Choice of 8-bit or 16-bit data transfer

• SCI3: 8-bit synchronous/asynchronous serial interface

Incorporates multiprocessor communication function

• Can be used as a 14-bit D/A converter by connecting to an external low-pass

filter.

• 8-channel analog input pins

• Conversion time: 31/ø or 62/ø per channel

Mask ROM

Version

HD6433644H HD6473644H HD64F3644H 64-pin QFP (FP-64A) ROM: 32 kbytes

HD6433644P HD6473644P HD64F3644P 64-pin SDIP (DP-64S)

HD6433644W HD6473644W HD64F3644W 80-pin TQFP (TFP-80C)

HD6433643H — HD64F3643H 64-pin QFP (FP-64A) ROM: 24 kbytes

HD6433643P — HD64F3643P 64-pin SDIP (DP-64S)

HD6433643W — HD64F3643W 80-pin TQFP (TFP-80C)

HD6433642H — HD64F3642AH 64-pin QFP (FP-64A) ROM: 16 kbytes

HD6433642P — HD64F3642AP 64-pin SDIP (DP-64S) RAM: 512 kbytes

HD6433642W — HD64F3642AW 80-pin TQFP (TFP-80C) RAM: 1 kbyte

HD6433641H — — 64-pin QFP (FP-64A) ROM: 12 kbytes

HD6433641P — — 64-pin SDIP (DP-64S)

HD6433641W — — 80-pin TQFP (TFP-80C)

HD6433640H — — 64-pin QFP (FP-64A) ROM: 8 kbytes

HD6433640P — — 64-pin SDIP (DP-64S)

HD6433640W — — 80-pin TQFP (TFP-80C)

ZTAT™

Version

F-ZTAT™

Version Package ROM/RAM Size

RAM: 1 kbyte

RAM: 1 kbyte

(F-ZTAT version)

RAM: 512 bytes

RAM: 512 bytes

4

Page 16

1.2 Internal Block Diagram

Figure 1.1 shows a block diagram of the H8/3644 Series.

P10/TMOW

P1

/PWM

4

P1

/IRQ

5

P16/IRQ

P17/IRQ3/TRGV

P20/SCK3

P2

/RXD

1

P2

/TXD

2

P30/SCK

P31/SI

P32/SO

2

OSC1OSC2X1X

Subclock

generator

generator

System clock

1

Port 1

2

Port 2

1

1

Port 3

1

VSSVCCRES

IRQ0TEST

CPU

H8/300L

Data bus (lower)

ROM

RAM

Timer A SCI1

Timer B1

SCI3

Timer X

Timer V

Address bus

Data bus (upper)

Port 8

Port 7

Port 6

P8

7

P86/FTID

P8

/FTIC

5

P8

/FTIB

4

P8

/FTIA

3

P8

/FTOB

2

P8

/FTOA

1

P8

/FTCI

0

P7

7

P76/TMOV

P7

/TMCIV

5

P7

/TMRIV

4

P7

3

P6

7

P6

6

CMOS large-

P6

5

current port

P6

4

I

P6

OL

3

@V

P6

2

P6

1

P6

0

= 10 mA

= 1V

OL

*

P90/FV

PP

P9

1

P9

2

Port 9

P9

3

P9

4

Watchdog

timer

14-bit PWM

A/D converter

Port B

SS

CC

0

1

2

3

4

5

6

AV

AV

/AN

/AN

/AN

/AN

0

1

2

PB

PB

PB

PB

7

/AN

/AN

/AN

/AN

3

4

5

6

7

PB

PB

PB

PB

Note: * There is no P90 function in the flash memory version.

Figure 1.1 Block Diagram

P57/INT

P56/INT6/TMIB

P5

P5

P53/INT

Port 5

P52/INT

P51/INT

P50/INT

7

/INT5/ADTRG

5

/INT

4

4

3

2

1

0

5

Page 17

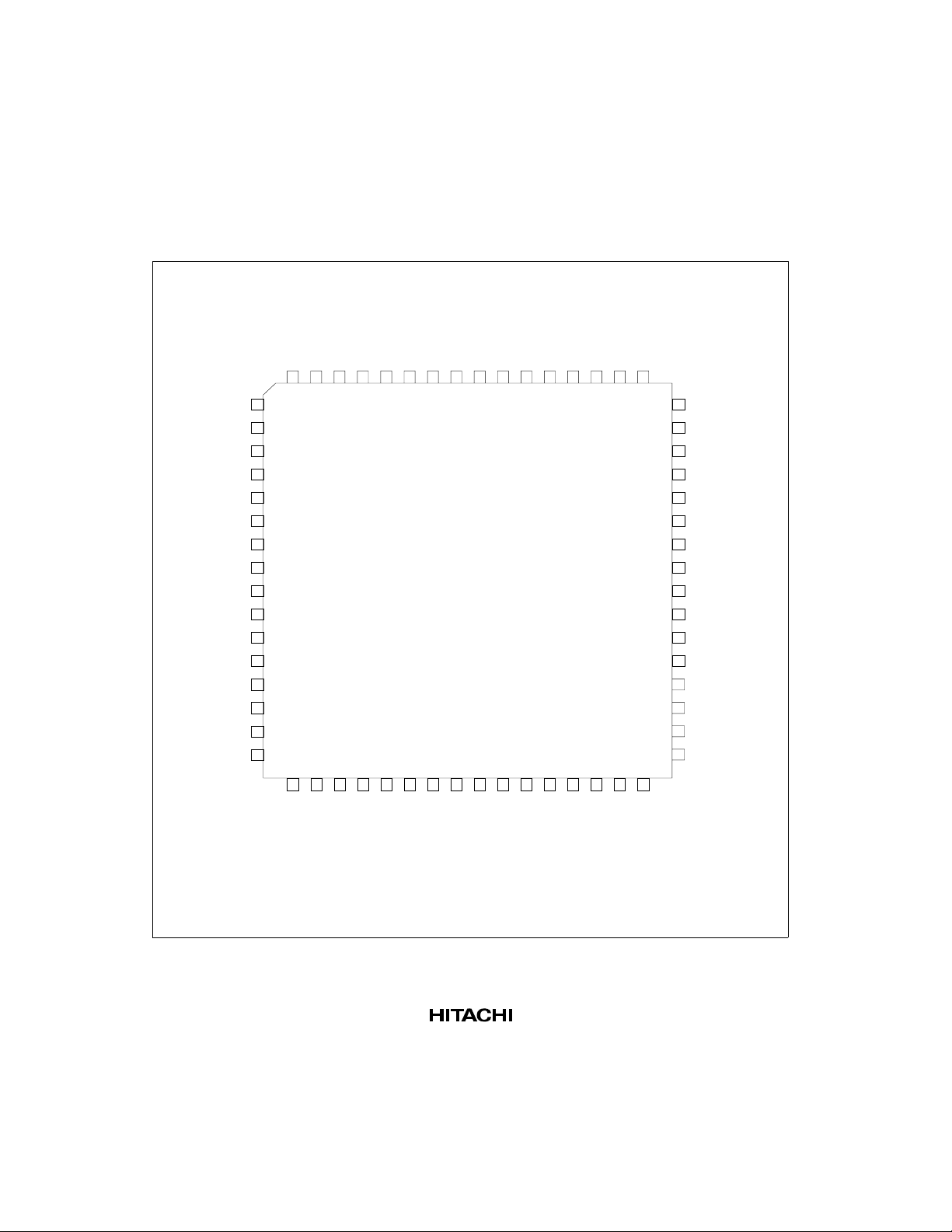

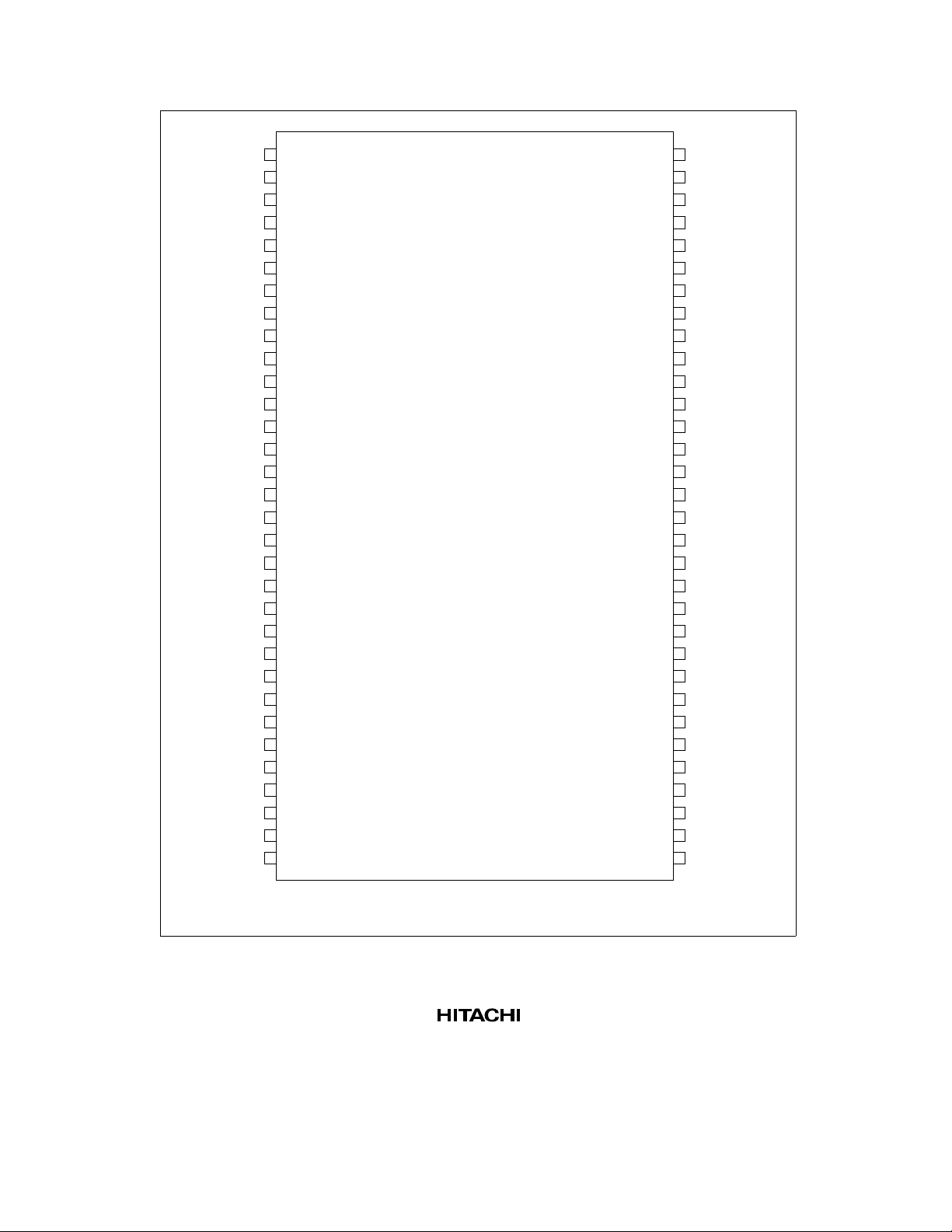

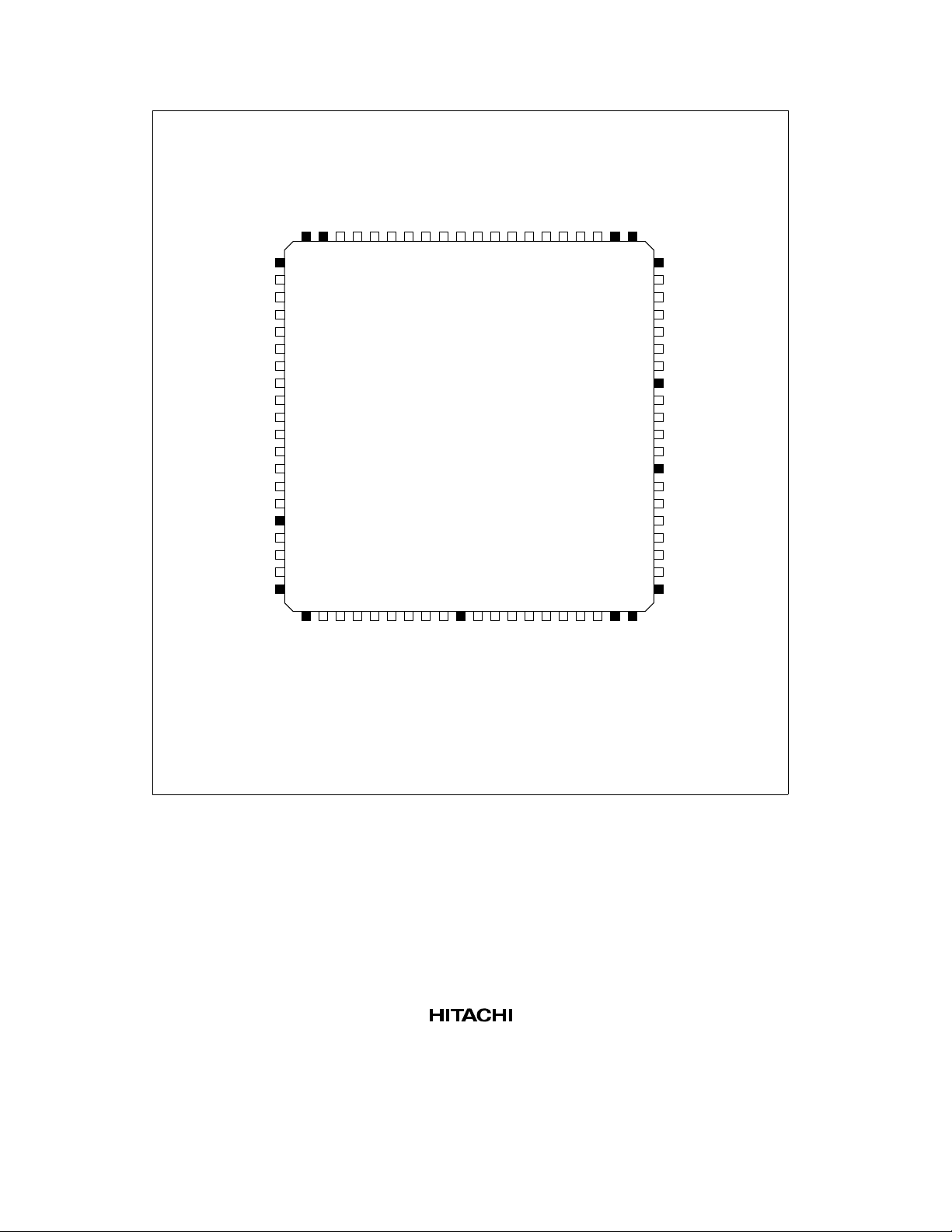

1.3 Pin Arrangement and Functions

1.3.1 Pin Arrangement

The H8/3644 Series pin arrangement is shown in figures 1.2 (FP-64A), 1.3 (DP-64S), and 1.4

(TFP-80C).

PB1/AN

PB0/AN

P9

0

AV

TEST

OSC

OSC

/FV

V

RES

PP

P9

P9

P9

P9

IRQ

SS

X

X

SS

/TRGV

3

2

/IRQ

6

P1

56

1

/IRQ

5

P1

55

/PWM

4

P1

54

2

3

4

5

6

7

/AN

/AN

/AN

/AN

/AN

/AN

2

3

4

5

6

PB

PB

PB

PB

PB

64

64

62

61

1

1

2

0

60

7

PB

59

/IRQ

7

AVCCP1

58

57

3

4

5

2

6

1

7

8

1

9

2

10

*

11

12

1

13

2

14

3

15

4

16

0

17

18

19

20

21

22

23

24

25

26

27

1

/TMOW

/SCK

0

0

P1

P3

53

52

28

29

/SI

P3

51

30

1

1

/SO

/TXD

1

2

2

P3

P2

50

49

48

P21/RXD

47

P2

/SCK

0

3

46

P8

7

45

P86/FTID

44

P8

/FTIC

5

43

P8

/FTIB

4

42

P8

/FTIA

3

41

P8

/FTOB

2

40

P8

/FTOA

1

39

P8

/FTCI

0

38

P7

7

37

P76/TMOV

36

P7

/TMCIV

5

35

P7

/TMRIV

4

34

P7

3

33

V

31

32

CC

0

/INT

0

P5

1

/INT

1

P5

P60P61P62P63P64P65P66P6

7

Note: * There is no P90 function in the flash memory version.

Figure 1.2 Pin Arrangement (FP-64A: Top View)

6

2

/INT

2

P5

3

/INT

3

P5

4

/INT

4

P5

/TMIB

6

/ADTRG

5

/INT

6

/INT

5

P5

P5

7

/INT

7

P5

Page 18

P17/IRQ3/TRGV

AV

CC

PB7/AN

PB6/AN

PB5/AN

PB4/AN

PB3/AN

PB2/AN

PB1/AN

PB0/AN

AV

SS

TEST

X

X

V

SS

OSC

OSC

RES

/FV

P9

0

PP

P9

P9

P9

P9

IRQ

P6

P6

P6

P6

P6

P6

P6

P6

1

2

3

7

4

6

5

5

6

4

7

3

8

2

9

1

10

0

11

12

13

2

14

1

15

16

1

17

2

18

*

19

20

1

21

2

22

3

23

4

24

0

25

0

26

1

27

2

28

3

29

4

30

5

31

6

32

7

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

/IRQ

P1

6

2

P15/IRQ

1

P14/PWM

/TMOW

P1

0

/SCK

P3

0

1

P31/SI

1

P32/SO

1

P22/TXD

/RXD

P2

1

/SCK

P2

0

3

P8

7

P86/FTID

/FTIC

P8

5

/FTIB

P8

4

/FTIA

P8

3

/FTOB

P8

2

/FTOA

P8

1

/FTCI

P8

0

P7

7

P76/TMOV

/TMCIV

P7

5

/TMRIV

P7

4

P7

3

V

CC

P57/INT

7

P56/INT6/TMIB

/INT5/ADTRG

P5

5

/INT

P5

4

4

P53/INT

3

P52/INT

2

P51/INT

1

P50/INT

0

Note: * There is no P90 function in the flash memory version.

Figure 1.3 Pin Arrangement (DP-64S: Top View)

7

Page 19

2

/AN

2

NCNCPB

3

/AN

3

PB

4

/AN

4

PB

5

/AN

5

PB

6

/AN

6

PB

7

/AN

7

PB

/TRGV

3

/IRQ

7

AVCCP1

2

/IRQ

6

P1

1

/IRQ

5

P1

/PWM

/TMOW

4

0

P1

P1

1

/SCK

/SI

0

P3

P3

1

1

/SO

/TXD

1

2

2

NC

P2

NC

P3

PB

PB0/AN

P9

0

NC

/AN

1

AV

SS

TEST

X

X

V

SS1

OSC

OSC

V

SS2

RES

/FVPP*

P9

P9

NC

P9

P9

IRQ

NC

80797877767574737271706968676665646362

1

2

1

3

0

4

5

6

2

7

1

8

9

1

10

2

11

12

13

14

1

15

2

16

17

3

18

4

19

0

20

21222324252627282930313233343536373839

0

1

2

3

/INT

2

P5

/INT

3

P5

4

/INT

4

/ADTRG

P5

/INT

5

5

/TMIB

6

/INT

6

P5

0P61P62P63P64P65P66P67

NC

P6

NC

/INT

0

P5

/INT

1

P5

7

/INT

7

P5

NC

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

NC

NC

P2

/RXD

1

P2

/SCK

0

P8

3

7

P86/FTID

P8

/FTIC

5

P8

/FTIB

4

NC

P8

/FTIA

3

P8

/FTOB

2

P8

/FTOA

1

P8

/FTCI

0

NC

P7

7

P76/TMOV

P7

/TMCIV

5

P7

/TMRIV

4

P7

3

V

CC

NC

P5

Note: * There is no P90 function in the flash memory version.

Figure 1.4 Pin Arrangement (TFP-80C: Top View)

8

Page 20

1.3.2 Pin Functions

Table 1.2 outlines the pin functions of the H8/3644 Series.

Table 1.2 Pin Functions

Pin No.

Type Symbol FP-64A DP-64S TFP-80C I/O Name and Functions

Power

source pins

Clock pins OSC

V

CC

V

SS

AV

CC

AV

SS

OSC

33 41 42 Input Power supply: All VCC pins

should be connected to the user

system V

.

CC

7 15 8, 11 Input Ground: All VSS pins should be

connected to the user system

GND.

58 2 72 Input Analog power supply: This is

the power supply pin for the A/D

converter. When the A/D

converter is not used, connect

this pin to the user system V

3 11 4 Input Analog ground: This is the A/D

converter ground pin. It should be

connected to the user system

GND.

8 16 9 Input System clock: These pins

1

connect to a crystal or ceramic

oscillator, or can be used to input

an external clock.

9 17 10 Output

2

See section 4, Clock Pulse

Generators, for a typical

connection diagram.

.

CC

System

control

X

1

6 14 7 Input Subclock: These pins connect to

a 32.768-kHz crystal oscillator.

X

2

5 13 6 Output

See section 4, Clock Pulse

Generators, for a typical

connection diagram.

RES 10 18 12 Input Reset: When this pin is driven

low, the chip is reset

TEST 4 12 5 Input Test: This is a test pin, not for

use in application systems. It

should be connected to V

.

SS

9

Page 21

Table 1.2 Pin Functions (cont)

Pin No.

Type Symbol FP-64A DP-64S TFP-80C I/O Name and Functions

Interrupt

pins

IRQ

IRQ

IRQ

IRQ

INT

INT

16

0

55

1

56

2

57

3

to

7

0

32 to 25 40 to 33 38 to 31 Input INT interrupt request 0 to 7:

24

63

64

1

19

69

70

71

Timer pins TMOW 53 61 67 Output Clock output: This is an output

TMIB 31 39 37 Input Timer B1 event counter input:

TMOV 37 45 46 Output Timer V output: This is an output

TMCIV 36 44 45 Input Timer V event input: This is an

TMRIV 35 43 44 Input Timer V counter reset: This is a

TRGV 57 1 71 Input Timer V counter trigger input:

FTCI 39 47 49 Input Timer X clock input: This is an

FTOA 40 48 50 Output Timer X output compare A

FTOB 41 49 51 Output Timer X output compare B

Input IRQ interrupt request 0 to 3:

These are input pins for edgesensitive external interrupts, with

a selection of rising or falling

edge

These are input pins for edgesensitive external interrupts, with

a selection of rising or falling

edge

pin for waveforms generated by

the timer A output circuit

This is an event input pin for input

to the timer B1 counter

pin for waveforms generated by

the timer V output compare

function

event input pin for input to the

timer V counter

counter reset input pin for timer V

This is a trigger input pin for the

timer V counter and realtime

output port

external clock input pin for input

to the timer X counter

output: This is an output pin for

timer X output compare A

output: This is an output pin for

timer X output compare B

10

Page 22

Table 1.2 Pin Functions (cont)

Pin No.

Type Symbol FP-64A DP-64S TFP-80C I/O Name and Functions

Timer pins FTIA 42 50 52 Input Timer X input capture A input:

This is an input pin for timer X

input capture A

FTIB 43 51 54 Input Timer X input capture B input:

This is an input pin for timer X

input capture B

FTIC 44 52 55 Input Timer X input capture C input:

This is an input pin for timer X

input capture C

FTID 45 53 56 Input Timer X input capture D input:

This is an input pin for timer X

input capture D

14-bit

PWM pin

I/O ports PB7 to

PWM 54 62 68 Output 14-bit PWM output: This is an

output pin for waveforms

generated by the 14-bit PWM

PB

0

P17 to

P1

,

4

P1

0

59 to 64,

1 to 2

57 to 53 1,

3 to 10 73 to 78

2, 3

71 to 67 I/O Port 1: This is a 5-bit I/O port.

64 to 61

Input Port B: This is an 8-bit input port

Input or output can be designated

for each bit by means of port

control register 1 (PCR1)

P22 to

P2

0

49 to 47 57 to 55 63, 5958I/O Port 2: This is a 3-bit I/O port.

Input or output can be designated

for each bit by means of port

control register 2 (PCR2)

P32 to

P3

0

50 to 52 58 to 60 64 to 66 I/O Port 3: This is a 3-bit I/O port.

Input or output can be designated

for each bit by means of port

control register 3 (PCR3)

P57 to

P5

0

32 to 25 40 to 33 38 to 31 I/O Port 5: This is an 8-bit I/O port.

Input or output can be designated

for each bit by means of port

control register 5 (PCR5)

P67 to

P6

0

24 to 17 32 to 25 29 to 22 I/O Port 6: This is an 8-bit I/O port.

Input or output can be designated

for each bit by means of port

control register 6 (PCR6)

11

Page 23

Table 1.2 Pin Functions (cont)

Pin No.

Type Symbol FP-64A DP-64S TFP-80C I/O Name and Functions

I/O ports P77 to

P7

3

P87 to

P8

0

P94 to

P9

0

Serial com-

SI

1

munication

interface

(SCI)

SO

1

SCK

RXD 48 56 59 Input SCI3 receive data input:

TXD 49 57 63 Output SCI3 transmit data output:

SCK

A/D

converter

AN7 to

AN

0

ADTRG 30 38 36 Input A/D converter trigger input:

38 to 34 46 to 42 47 to 43 I/O Port 7: This is a 5-bit I/O port.

Input or output can be designated

for each bit by means of port

control register 7 (PCR7)

46 to 39 54 to 47 57 to 54,

52 to 49

I/O Port 8: This is an 8-bit I/O port.

Input or output can be designated

for each bit by means of port

control register 8 (PCR8)

15 to 11 23 to 19 18, 17

15 to 13

I/O Port 9: This is a 5-bit I/O port.

Input or output can be designated

for each bit by means of port

control register 9 (PCR9)

Note: There is no P9

the flash memory version

since P9

FV

pin.

PP

51 59 65 Input SCI1 receive data input:

This is the SCI1 data input pin

50 58 64 Output SCI1 transmit data output:

This is the SCI1 data output pin

52 60 66 I/O SCI1 clock I/O:

1

This is the SCI1 clock I/O pin

This is the SCI3 data input pin

This is the SCI3 data output pin

47 55 58 I/O SCI3 clock I/O:

3

This is the SCI3 clock I/O pin

59 to 64,

1 to 2

3 to 10 73 to 78

2, 3

Input Analog input channels 11 to 0:

These are analog data input

channels to the A/D converter

This is the external trigger input

pin to the A/D converter

is used as the

0

function in

0

12

Page 24

Table 1.2 Pin Functions (cont)

Pin No.

Type Symbol FP-64A DP-64S TFP-80C I/O Name and Functions

Flash

memory

Other NC — — 1, 16,

FV

PP

11 19 13 Input On-board-programmable flash

memory power supply:

Connected to the flash memory

programming power supply

(+12 V). When the flash memory

is not being programmed,

connect to the user system V

In versions other than the on-chip

flash memory version, this pin is

P9

0

— Non-connected pins: These

20, 21,

pins must be left unconnected

30, 39,

40, 41,

48, 53,

60 to 62,

79, 80

.

CC

13

Page 25

Section 2 CPU

2.1 Overview

The H8/300L CPU has sixteen 8-bit general registers, which can also be paired as eight 16-bit

registers. Its concise instruction set is designed for high-speed operation.

2.1.1 Features

Features of the H8/300L CPU are listed below.

• General-register architecture

Sixteen 8-bit general registers, also usable as eight 16-bit general registers

• Instruction set with 55 basic instructions, including:

Multiply and divide instructions

Powerful bit-manipulation instructions

• Eight addressing modes

Register direct

Register indirect

Register indirect with displacement

Register indirect with post-increment or pre-decrement

Absolute address

Immediate

Program-counter relative

Memory indirect

• 64-kbyte address space

• High-speed operation

All frequently used instructions are executed in two to four states

High-speed arithmetic and logic operations

8- or 16-bit register-register add or subtract: 0.4 µs (operating at ø = 5 MHz)

0.25 µs (operating at ø = 8 MHz)*

8 × 8-bit multiply: 2.8 µs (operating at ø = 5 MHz)

1.75 µs (operating at ø = 8 MHz)*

16 ÷ 8-bit divide: 2.8 µs (operating at ø = 5 MHz)

1.75 µs (operating at ø = 8 MHz)*

Note: * F-ZTAT version only.

• Low-power operation modes

SLEEP instruction for transfer to low-power operation

Note: * These values are at ø = 5 MHz.

15

Page 26

2.1.2 Address Space

The H8/300L CPU supports an address space of up to 64 kbytes for storing program code and

data.

See 2.8, Memory Map, for details of the memory map.

2.1.3 Register Configuration

Figure 2.1 shows the register structure of the H8/300L CPU. There are two groups of registers: the

general registers and control registers.

General registers (Rn)

7070

R0H

R1H

R2H

R3H

R4H

R5H

R6H

R7H

(SP)

R0L

R1L

R2L

R3L

R4L

R5L

R6L

R7L

SP: Stack pointer

16

Control registers (CR)

15 0

PC

75321064

CCR I U H U N Z V C

Figure 2.1 CPU Registers

PC: Program counter

CCR: Condition code register

Carry flag

Overflow flag

Zero flag

Negative flag

Half-carry flag

Interrupt mask bit

User bit

User bit

Page 27

2.2 Register Descriptions

2.2.1 General Registers

All the general registers can be used as both data registers and address registers.

When used as data registers, they can be accessed as 16-bit registers (R0 to R7), or the high bytes

(R0H to R7H) and low bytes (R0L to R7L) can be accessed separately as 8-bit registers.

When used as address registers, the general registers are accessed as 16-bit registers (R0 to R7).

R7 also functions as the stack pointer (SP), used implicitly by hardware in exception processing

and subroutine calls. When it functions as the stack pointer, as indicated in figure 2.2, SP (R7)

points to the top of the stack.

Lower address side [H'0000]

Unused area

SP (R7)

Stack area

Upper address side [H'FFFF]

Figure 2.2 Stack Pointer

2.2.2 Control Registers

The CPU control registers include a 16-bit program counter (PC) and an 8-bit condition code

register (CCR).

Program Counter (PC): This 16-bit register indicates the address of the next instruction the CPU

will execute. All instructions are fetched 16 bits (1 word) at a time, so the least significant bit of

the PC is ignored (always regarded as 0).

17

Page 28

Condition Code Register (CCR): This 8-bit register contains internal status information,

including the interrupt mask bit (I) and half-carry (H), negative (N), zero (Z), overflow (V), and

carry (C) flags. These bits can be read and written by software (using the LDC, STC, ANDC,

ORC, and XORC instructions). The N, Z, V, and C flags are used as branching conditions for

conditional branching (Bcc) instructions.

Bit 7—Interrupt Mask Bit (I): When this bit is set to 1, interrupts are masked. This bit is set to 1

automatically at the start of exception handling. The interrupt mask bit may be read and written by

software. For further details, see section 3.3, Interrupts.

Bit 6—User Bit (U): Can be used freely by the user.

Bit 5—Half-Carry Flag (H): When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B

instruction is executed, this flag is set to 1 if there is a carry or borrow at bit 3, and is cleared to 0

otherwise.

The H flag is used implicitly by the DAA and DAS instructions.

When the ADD.W, SUB.W, or CMP.W instruction is executed, the H flag is set to 1 if there is a

carry or borrow at bit 11, and is cleared to 0 otherwise.

Bit 4—User Bit (U): Can be used freely by the user.

Bit 3—Negative Flag (N): Indicates the most significant bit (sign bit) of the result of an

instruction.

Bit 2—Zero Flag (Z): Set to 1 to indicate a zero result, and cleared to 0 to indicate a non-zero

result.

Bit 1—Overflow Flag (V): Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other

times.

Bit 0—Carry Flag (C): Set to 1 when a carry occurs, and cleared to 0 otherwise. Used by:

• Add instructions, to indicate a carry

• Subtract instructions, to indicate a borrow

• Shift/rotate carry

The carry flag is also used as a bit accumulator by bit manipulation instructions.

Some instructions leave some or all of the flag bits unchanged.

Refer to the H8/300L Series Programming Manual for the action of each instruction on the flag

bits.

18

Page 29

2.2.3 Initial Register Values

In reset exception handling, the program counter (PC) is initialized by a vector address (H'0000)

load, and the I bit in the CCR is set to 1. The other CCR bits and the general registers are not

initialized. In particular, the stack pointer (R7) is not initialized. The stack pointer should be

initialized by software, by the first instruction executed after a reset.

2.3 Data Formats

The H8/300L CPU can process 1-bit data, 4-bit (BCD) data, 8-bit (byte) data, and 16-bit (word)

data.

The H8/300L CPU can process 1-bit, 4-bit BCD, 8-bit (byte), and 16-bit (word) data. 1-bit data is

handled by bit manipulation instructions, and is accessed by being specified as bit n (n = 0, 1, 2, ...

7) in the operand data (byte).

Byte data is handled by all arithmetic and logic instructions except ADDS and SUBS. Word data

is handled by the MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU ( b bits × 8 bits),

and DIVXU (16 bits ÷ 8 bits) instructions.

With the DAA and DAS decimal adjustment instructions, byte data is handled as two 4-bit BCD

data units.

19

Page 30

2.3.1 Data Formats in General Registers

Data of all the sizes above can be stored in general registers as shown in figure 2.3.

Data Type Register No. Data Format

70

1-bit data RnH

1-bit data RnL

Byte data RnH

Byte data RnL

Word data Rn

76543210 don’t care

70

76543210don’t care

70

MSB LSB

70

don’t care

15 0

MSB LSB

MSB LSB

don’t care

4-bit BCD data RnH

4-bit BCD data RnL

Legend:

Upper byte of general register

RnH:

Lower byte of general register

RnL:

Most significant bit

MSB:

Least significant bit

LSB:

20

7034

Upper digit Lower digit

70

don’t care

Upper digit Lower digit

Figure 2.3 General Register Data Formats

don’t care

34

Page 31

2.3.2 Memory Data Formats

Figure 2.4 indicates the data formats in memory. For access by the H8/300L CPU, word data

stored in memory must always begin at an even address. When word data beginning at an odd

address is accessed, the least significant bit is regarded as 0, and the word data beginning at the

preceding address is accessed. The same applies to instruction codes.

1-bit data

Byte data

Word data

Byte data (CCR) on stack

Word data on stack

CCR: Condition code register

Note: Ignored on return*

AddressData Type

Address n

Address n

Even address

Odd address

Even address

Odd address

Even address

Odd address

Data Format

70

76543210

MSB LSB

MSB

MSB LSBCCR

MSB LSB

MSB

Upper 8 bits

Lower 8 bits

*

CCR

LSB

LSB

Figure 2.4 Memory Data Formats

When the stack is accessed using R7 as an address register, word access should always be

performed. The CCR is stored as word data with the same value in the upper 8 bits and the lower 8

bits. On return, the lower 8 bits are ignored.

21

Page 32

2.4 Addressing Modes

2.4.1 Addressing Modes

The H8/300L CPU supports the eight addressing modes listed in table 2.1. Each instruction uses a

subset of these addressing modes.

Table 2.1 Addressing Modes

No. Address Modes Symbol

1 Register direct Rn

2 Register indirect @Rn

3 Register indirect with displacement @(d:16, Rn)

4 Register indirect with post-increment

Register indirect with pre-decrement

5 Absolute address @aa:8 or @aa:16

6 Immediate #xx:8 or #xx:16

7 Program-counter relative @(d:8, PC)

8 Memory indirect @@aa:8

1. Register Direct—Rn: The register field of the instruction specifies an 8- or 16-bit general

register containing the operand.

@Rn+

@–Rn

Only the MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits × 8 bits), and

DIVXU (16 bits ÷ 8 bits) instructions have 16-bit operands.

2. Register Indirect—@Rn: The register field of the instruction specifies a 16-bit general

register containing the address of the operand in memory.

3. Register Indirect with Displacement—@(d:16, Rn): The instruction has a second word

(bytes 3 and 4) containing a displacement which is added to the contents of the specified

general register to obtain the operand address in memory.

This mode is used only in MOV instructions. For the MOV.W instruction, the resulting address

must be even.

22

Page 33

4. Register Indirect with Post-Increment or Pre-Decrement—@Rn+ or @–Rn:

• Register indirect with post-increment—@Rn+

The @Rn+ mode is used with MOV instructions that load registers from memory.

The register field of the instruction specifies a 16-bit general register containing the address

of the operand. After the operand is accessed, the register is incremented by 1 for MOV.B

or 2 for MOV.W, and the result of the addition is stored in the register. For MOV.W, the

original contents of the 16-bit general register must be even.

• Register indirect with pre-decrement—@–Rn

The @–Rn mode is used with MOV instructions that store register contents to memory.

The register field of the instruction specifies a 16-bit general register which is decremented

by 1 or 2 to obtain the address of the operand in memory. The register retains the

decremented value. The size of the decrement is 1 for MOV.B or 2 for MOV.W. For

MOV.W, the original contents of the register must be even.

5. Absolute Address—@aa:8 or @aa:16: The instruction specifies the absolute address of the

operand in memory.

The absolute address may be 8 bits long (@aa:8) or 16 bits long (@aa:16). The MOV.B and bit

manipulation instructions can use 8-bit absolute addresses. The MOV.B, MOV.W, JMP, and

JSR instructions can use 16-bit absolute addresses.

For an 8-bit absolute address, the upper 8 bits are assumed to be 1 (H'FF). The address range is

H'FF00 to H'FFFF (65280 to 65535).

6. Immediate—#xx:8 or #xx:16: The second byte (#xx:8) or the third and fourth bytes (#xx:16)

of the instruction code are used directly as the operand. Only MOV.W instructions can be used

with #xx:16.

The ADDS and SUBS instructions implicitly contain the value 1 or 2 as immediate data. Some

bit manipulation instructions contain 3-bit immediate data in the second or fourth byte of the

instruction, specifying a bit number.

7. Program-Counter Relative—@(d:8, PC): This mode is used in the Bcc and BSR

instructions. An 8-bit displacement in byte 2 of the instruction code is sign-extended to 16 bits