Page 1

6(59,&(0$18$/

J

0$18(/'·(175(7,(1

:$5781*6+$1'%8&+

&$87,21

%HIRUH VHUYLFLQJ WKLV FKDVVLV LW LV LPSRUWDQW WKDW WKH VHUYLFH WHFKQLFLDQ UHDG

WKH ´6DIHW\ 3UHFDXWLRQVµ DQG ´3URGXFW 6DIHW\ 1RWLFHVµ LQ WKLV VHUYLFH PDQXDO

$77(17,21

$YDQW G·HIIHFWXHU O·HQWUHWLHQ GX FKkDVVLV OH WHFKQLFLHQ GRLW OLUH OHV

©3UpFDXWLRQV GH VpFXULWpª HW OHV ©1RWLFHV GH VpFXULWp GX SURGXLWª SUpVHQWpV

GDQV OH SUpVHQW PDQXHO

1R

&/:7$1

&/:7$1

&/:7$1

&/:7$1

&:71

&:71

'DWD FRQWDLQHG ZLWKLQ WKLV 6HUYLFH

PDQXDO LV VXEMHFW WR DOWHUDWLRQ IRU

LPSURYHPHQW

/HV GRQQpHV IRXUQLHV GDQV OH

SUpVHQW PDQXHO G·HQWUHWLHQ

SHXYHQW IDLUH O·REMHW GH

PRGLILFDWLRQV HQ YXH GH

SHUIHFWLRQQHU OH SURGXLW

9256,&+7

9RU gIIQHQ GHV *HKlXVHV KDW GHU 6HUYLFH,QJHQLHXU GLH Å6LFKHUKHLWVKLQZHLVH´

XQG Å+LQZHLVH ]XU 3URGXNWVLFKHUKHLW´ LQ GLHVHP :DUWXQJVKDQGEXFK ]X OHVHQ

'LH LQ GLHVHP :DUWXQJVKDQGEXFK

HQWKDOWHQHQ 6SH]LILNDWLRQHQ

N|QQHQ VLFK ]ZHFNV

9HUEHVVHUXQ

HQ lQGHUQ

7(&+1,&$/ 63(&,),&$7,216 63e&,),&$7,216 7(&+1,48(6 63(&,),&$7,216 7(&+1,48(6

79 6WDQGDUG

&KDQQHO FRYHUDJH

$HULDO LQSXW LPSHGDQFH

3URJUDPPH 6HOHFWRUV

3RZHU &RQVXPSWLRQ 3LFWXUH 7XEH &RQVRPPDWLRQ

:

:

:

:

:

:

6WDQGE\ 3RZHU &RQVXPSWLRQ :

0DLQV 9ROWDJH99 +]

)XVH 7$ 7\SH

)RFXVLQJ(OHFWUR VWDWLF

8+)9+) +\SHU EDQG ([SRUW

EXWWRQV ZLWK SURJUDPPH

)UHTXHQF\ GLUHFW LQSXW

7%$

:

:

7%$

:

:

%*+ // ([SRUW

8+) &KDQQHOV 8.

&KDQQHO 83'2:1

OLQHV

67$1'$5' , 8.

RKP

8QEDODQFHG

UHPRWH FRQWURO

&+ GLUHFW LQSXW

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

6WDQGDUG 79 OLJQHV

&RXYHUWXUH GH FDQDX[ &DQDX[ 8+) 58

,PSpGDQFH GHQWUpH GDQWHQQH RKPV

6pOHFWHXUV GH SURJUDPPHV 7RXFKHV GH

pOHFWULTXH

:

:

:

:

:

:

&RQVRPPDWLRQ HQ PRGH YHLOOH :

7HQWLRQ VHFWHXU99 +]

)XVLEOH 7\SH 7 $

0LVH DX SRLQW(OHFWURVWDWLTXH

67$1'$5' 58

%*+ // ([SRUW

8+)9+) %DQG K\SHU ([SRUW

1RQ pTXLOLEUpH

6pOHFWLRQ GH FDQDX[ +$87%$6

$YHF SURJUDPPHV

(QWUpH GLUHFWH FDQDO &+

7%$

:

:

7%$

:

:

7pOpFRPPDQGH

(QWUpH GLUHFWH IUpTXHQFH

7XEHVLPDJHV /HLVWXQJVDXIQDKPH %LOGU|KUH

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

)HUQVHKQRUP =HLOHQ

.DQlOH 8+)%HUHLFK *%

8+)9+)+\SHUEDQG%HUHLFK ([SRUW

$QWHQQHQHLQJDQJVLPSHGDQ] RKQ

6HQGHUZDKO$8)$%7DVWH

:

:

:

:

:

:

/HLVWXQJVDXIQDKPH LP 6WDQGE\0RGXV :

1HW]VSDQQXQJ 9 9 +]

6LFKHUXQJ 7$

)RNXVLHUXQJ(OHNWURVWDWLVFK

DXI )HUQEHGLHQXQJ IU 6HQGHU

)HUQVHKQRUP , QXU *%

)HUQVHKQRUP %*+ //

8QV\PPHWULVFK

6HQGHUGLUHNWHLQJDEH

)UHTXHQ]GLUHNWLQJDEH

7%$

:

:

7%$

:

:

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

FP 7\SH

0D\

Page 2

ENGLISH .............................................................................................................................................3

SAFETY ............................................................................................................................................3

SAFETY PRECAUTIONS ..............................................................................................................................3

CIRCUIT DESCRIPTION...................................................................................................................4

D8/A8 CHASSIS ALIGNMENT PROCEDURE ................................................................................................4

DIGITAL COMB FILTER – TOSHIBA TC9090AF..........................................................................................13

SCAN VELOCITY MODULATION. ...............................................................................................................13

DIGITAL DOUBLE SCAN CONVERSION UNIT (FEATURE BOX).................................................................13

INPUT PROCESSOR - PHILIPS TDA 9320..................................................................................................14

PICTURE IMPROVEMENT - PHILIPS TDA 9178..........................................................................................15

TUNER........................................................................................................................................................15

RGB PROCESSOR - TDA 9330...................................................................................................................15

SIGNAL PATH DESCRIPTION.....................................................................................................................16

AUDIO CIRCUIT..........................................................................................................................................16

AUDIO OUTPUT..........................................................................................................................................17

DOLBY DECODER. .....................................................................................................................................17

DEFLECTION..............................................................................................................................................17

HIGH END FEATURE BOX..........................................................................................................................18

LOW END FEATURE BOX ..........................................................................................................................18

MICROCONTROLLER SECTION ON THE A8/D8 CHASSIS ........................................................................19

POWERED CONSOLE................................................................................................................................26

DIGITAL SECTION...................................................................................................................................... 27

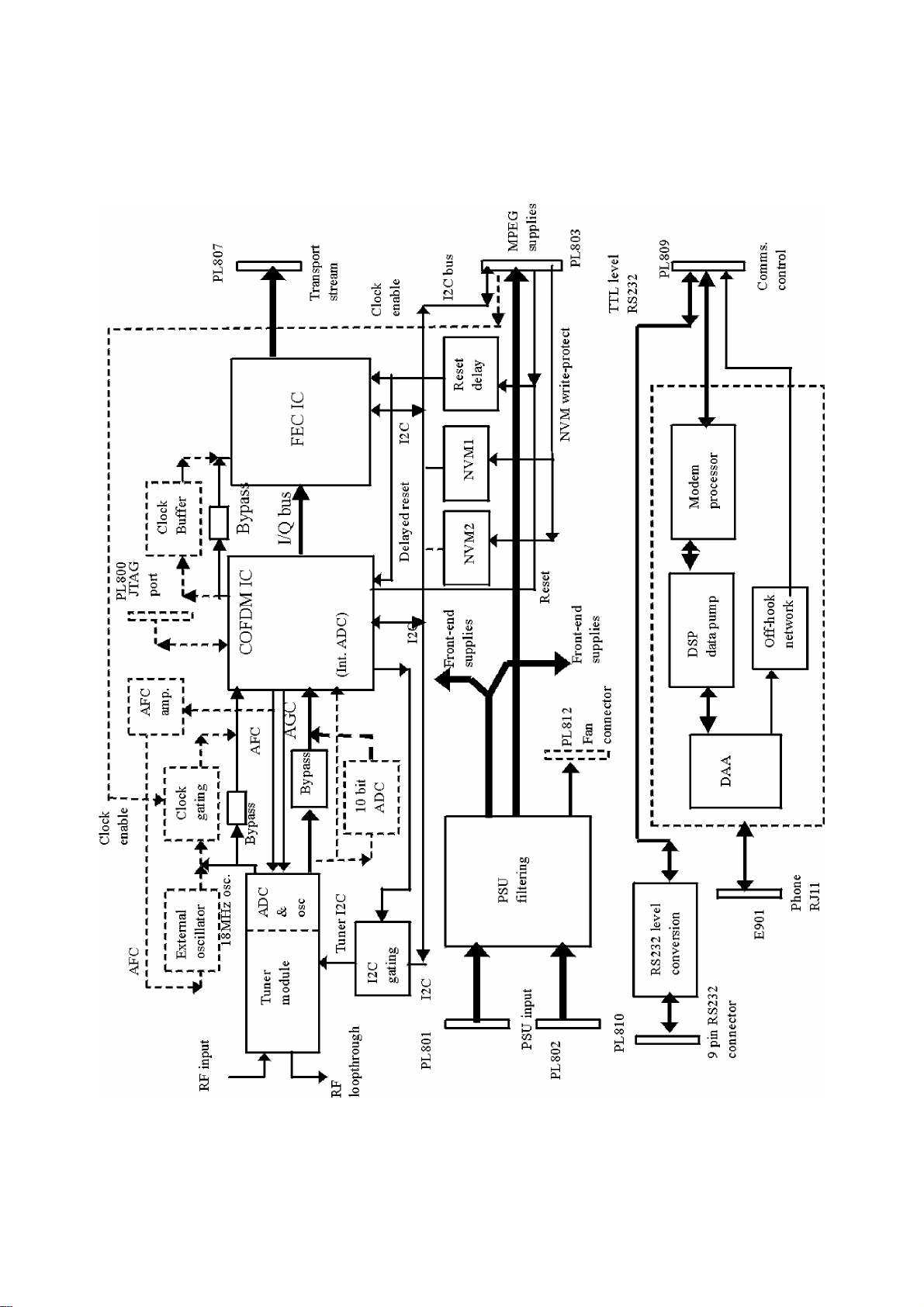

GENERAL BLOCK DIAGRAM......................................................................................................................28

COFDM FRONT-END PCB ..........................................................................................................................29

MPEG DECODER AND AV/GRAPHICS PCB............................................................................................... 37

CONNECTOR SPECIFICATION..................................................................................................................60

A8/D8 PSU ..................................................................................................................................................66

DTI PSU ......................................................................................................................................................67

SERVICING..................................................................................................................................... 69

SERVICE. ...................................................................................................................................................69

SELF DIAGNOSTICS ..................................................................................................................................71

DIAGNOSTIC INTERFACE..........................................................................................................................73

FRANÇAIS.........................................................................................................................................74

SÉCURITÉ......................................................................................................................................74

CONSIGNES DE SECURITE.......................................................................................................................74

DESCRIPTION DU CIRCUIT...........................................................................................................75

PROCEDURE D'ALIGNEMANT DU COFFRET D8/A8.................................................................................. 75

FILTRE-PEIGNE NUMÉRIQUE....................................................................................................................84

MODULATION DE LA VITESSE DE BALAYAGE..........................................................................................84

GROUPE DE CONVERSION NUMÉRIQUE À DOUBLE VISIONNEMENT (COFFRET DES FONCTIONS).... 84

PROCESSEUR D'ENTRÉE – PHILIPS TDA 9320 ........................................................................................85

AMÉLIORATION DE L'IMAGE - PHILIPS TDA 9178.....................................................................................86

TUNER........................................................................................................................................................86

PROCESSEUR RGB - TDA 9330.................................................................................................................86

DESCRIPTION DE LA TRAJECTOIRE DES SIGNAUX ................................................................................87

CIRCUIT AUDIO..........................................................................................................................................87

SORTIE AUDIO ...........................................................................................................................................88

DÉCODEUR DOLBY...................................................................................................................................88

DEFLEXION................................................................................................................................................89

CASE DE FONCTIONS EXTRÉMITÉ HAUTE ..............................................................................................90

CASE FONCTIONS EXTRÉMITÉ BASSE....................................................................................................90

SECTION DU MICROCONTRÔLEUR DU CHÂSSIS A8/D8.......................................................................... 91

CONSOLE D'ALIMENTATION .....................................................................................................................99

DESCRIPTION GÉNÉRALE ......................................................................................................................100

SCHÉMA SYNOPTIQUE ...........................................................................................................................101

CIRCUIT IMPRIMÉ FRONTAL COFDM......................................................................................................102

CIRCUIT IMPRIMÉ DE DÉCODEUR MPEG ET AV/GRAPHIQUES ............................................................110

SPÉCIFICATION DES CONNECTEURS....................................................................................................132

ALIMENTATION A8/D8..............................................................................................................................139

ALIMENTATION DTI..................................................................................................................................140

ENTRETIEN COURANT................................................................................................................142

SERVICE. .................................................................................................................................................142

AUTO-DIAGNOSTIC..................................................................................................................................146

1

Page 3

INTERFACE DE DIAGNOSTIC..................................................................................................................148

DEUTSCH........................................................................................................................................149

SICHERHEIT.................................................................................................................................149

SICHERHEITSVORKEHRUNGEN.............................................................................................................149

SCHALTUNGSBESCHREIBUNG .................................................................................................. 150

D8/A8 VERFAHREN ZUM GRUNDPLATTENABGLEICH ...........................................................................150

DIGITALER KAMMFILTER – TOSHIBA TC9090AF....................................................................................159

MODULATION DER ABTAST-GESCHWINDIGKEIT...................................................................................159

DIGITALES DOPPELABTASTUNGS-UMWANDLUNGS-AGGREGAT (ZUSATZ-KASTEN). ........................159

EINGABE-PROZESSOR - PHILIPS TDA 9320...........................................................................................160

BILDVERBESSERUNG - PHILIPS TDA 9178.............................................................................................161

TUNER......................................................................................................................................................161

RGB PROZESSOR - TDA 9330.................................................................................................................161

BESCHREIBUNG DES SIGNALWEGS......................................................................................................162

AUDIO-SCHALTKREIS..............................................................................................................................162

AUDIO-AUSGABE.....................................................................................................................................163

DOLBY DECODER. ...................................................................................................................................163

ABLENKUNG............................................................................................................................................163

„HÖHERE“ FEATURE BOX .......................................................................................................................165

„NIEDRIGE“ FEATURE BOX......................................................................................................................165

MIKROCONTROLLER-ABSCHNITT AUF DER A8/D8 GRUNDPLATTE......................................................166

MIT STROM VERSORGTE KONSOLE ......................................................................................................175

DIGITALER TEIL.......................................................................................................................................175

BLOCKSCHALTBILD.................................................................................................................................177

COFDM EINGANGS-FLACHBAUGRUPPE................................................................................................178

MPEG DECODER UND AV/GRAFIK FLACHBAUGRUPPE........................................................................187

STECKER-SPEZIFIKATION ......................................................................................................................210

A8/D8 NETZTEIL.......................................................................................................................................217

DTI-NETZTEIL...........................................................................................................................................218

WARTUNG....................................................................................................................................220

WARTUNG................................................................................................................................................220

SELBST-DIAGNOSE.................................................................................................................................223

DIAGNOSE-SCHNITTSTELLE...................................................................................................................224

WAVEFORMS............................................................................................................................... 225

IC DATA........................................................................................................................................ 230

I200...........................................................................................................................................................230

IE02..........................................................................................................................................................235

MECHANICAL............................................................................................................................... 238

2

Page 4

ENGLISHENGLISH

SAFETY

SAFETY PRECAUTIONS

WARNING: The following precautions must be observed.

ALL PRODUCTS

1. Before any service is performed on the chassis an isolation transformer should be inserted between the power line and

the product.

2. When replacing the chassis in the cabinet, ensure all the protective devices are put back in place.

3. When service is required, observe the original lead dressing. Extra precaution should be taken to ensure correct lead

dressing in any high voltage circuitry area.

4. Many electrical and mechanical parts in HITACHI products have special safety related characteristics. These

characteristics are often not evident from visual inspection, nor can the protection afforded by them necessarily be

obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these

special safety characteristics are identified by marking with a ! on the schematics and the replacement parts list.

The use of a substitute replacement component that does not have the same safety characteristics as the HITACHI

recommended replacement one, shown in the parts list, may create electrical shock, fire, X-radiation, or other hazards.

5. Always replace original spacers and maintain lead lengths. Furthermore, where a short circuit has occurred, replace those

components that indicate evidence of overheating.

6. Insulation resistance should not be less than 2M ohms at 500V DC between the main poles and any accessible metal

parts.

7. No flashover or breakdown should occur during the dielectric strength test, applying 3kV AC or 4.25kV DC for two

seconds between the main poles and accessible metal parts.

8. Before returning a serviced product to the customer, the service technician must thoroughly test the unit to be certain that

it is completely safe to operate without danger of electrical shock. The service technician must make sure that no

protective device built into the instrument by the manufacturer has become defective, or inadvertently damaged during

servicing.

CE MARK

1. HITACHI products may contain the CE mark on the rating plate indicating that the product contains parts that have been

specifically approved to provide electromagnetic compatibility to designated levels.

2. When replacing any part in this product, please use only the correct part itemised in the parts list to ensure this standard

is maintained, and take care to replace lead dressing to its original state, as this can have a bearing on the

electromagnetic radiation/immunity.

PICTURE TUBE

1. The line output stage can develop voltages in excess of 25kV; if the E.H.T. cap is required to be removed, discharge the

anode to chassis via a high value resistor, prior to its removal from the picture tube.

2. High voltage should always be kept at the rated value of the chassis and no higher. Operating at higher voltages may

cause a failure of the picture tube or high voltage supply, and also, under certain circumstances could produce X-radiation

levels moderately in excess of design levels. The high voltage must not, under any circumstances, exceed 29kV on the

chassis (except for projection Televisions).

3. The primary source of X-radiation in the product is the picture tube. The picture tube utilised for the above mentioned

function in this chassis is specially constructed to limit X-radiation. For continued X-radiation protection, replace tube with

the same type as the original HITACHI approved type

4. Keep the picture tube away from the body while handling. Do not install, remove, or handle the picture tube in any manner

unless shatterproof goggles are worn. People not so equipped should be kept away while picture tubes are handled

LASERS

If the product contains a laser avoid direct exposure to the beam when the cover is open or when interlocks are defeated or have

failed.CIRCUIT DESCRIPTIONCIRCUIT DESCRIPTION

3

Page 5

CIRCUIT DESCRIPTION

D8/A8 CHASSIS ALIGNMENT PROCEDURE

APPLICATIONS

THIS SPEC. SHOULD BE APPLIED TO ALL UK AND EXPORT, A8 RECEIVERS

P.W.B ASSEMBLY ADJUSTMENT

FOR SIGNAL

PREPARATION ADJUSTMENT

• +B adj. VR982..........Centre

• Screen VR (FBT).......Counter-clockwise fully

• Turn on set. Adjust +B to approximately 152V. (Pre adjustment only - final adjustment in +B VOLTAGE ADJUSTMENT

section)

• If flaring is observed adjust L501 until a clean video signal is seen on the oscilloscope video out port.

For models which have a flash device fitted, ensure that the service information reads FLASH: x.x instead of Code: x.x for the

software version.

STANDARD AFC ALIGNMENT

To reduce the influence of circuit temperature drift, let the television warm up by leaving it operating normally for more than two

minutes.

• Receive a 'PAL I' signal by selecting program 3 via the remote control handset.

• Receive a signal level of +60 dBuV at 623,25MHz (CH40) by direct frequency entry under the CH option.

• Set AFC offset (in service - options) to the centre position.

• In the tuner menu select standard I.F AFC and press either '<' or '>' on the remote control to activate the automatic AFC

setting procedure.

• If the indicator bar goes either end, then returns to the centre, adjust L201 one turn and then return to step 3, continue this

until the indicator bar no longer jumps back to the centre.

L' AFC ALIGNMENT (FOR EXPORT MODELS ONLY).

• To reduce the influence of circuit temperature drift, let the television warm up by leaving it operating normally for more

than two minutes.

• Receive an L' signal by selecting program 14 via the remote control hand-set.

• Receive a signal level of +60 dBuV at 63,75MHz (CH4) by direct frequency entry under the CH option.

• In the tuner menu select L' I.F AFC and press '<' or '>' on the remote control.

• If the bar goes to either end then returns to centre, adjust L201 one turn and then return to step 3, continue this until the

Because the set up procedures are interactive it is necessary to repeat all procedures from STANDARD AFC ALIGNMENT until no

adjustment of L201 is required.

AGC ALIGNMENT

indicator bar no longer jumps back to the centre.

• To reduce the influence of circuit temperature drift, let the television warm up by leaving it operating normally for more

than two minutes.

• Connect a voltmeter of at least 100K internal resistance to the A.G.C. terminal of the tuner.

• Receive channel 40 (623.25mhz) at +60dBuV.

• Adjust the A.G.C. using the A.G.C take-over option in the tuner sub menu until the A.G.C. voltage is 2.8V +/- 0.1V.

4

Page 6

POWER AND DEFLECTION ADJUSTMENT

+B VOLTAGE ADJUSTMENT

• AC input voltage = 230V ± 5V/50Hz

• Turn +B voltage (R982) to mid-point (if pre-adjustment not done).

• Receive Philips circuit pattern. Switch on chassis and set the brightness and contrast to maximum.

• After applying heat run for 1 MIN. or more, turn R982 gradually and adjust +B (re-check after 30 secs)

Measuring point : +B voltage C958 + side

Gnd C958 - side

• Set the value of +B voltage to the value shown in the table below.

MODEL +B VOLTAGE (V)

All D8 151V ± 0.2V

All A8 148V ± 0.2V

Min Load Max Load

+8V = 8V ± 5%

+5V = 5V ± 5%

+16V = 16V ,+3V – 0.5V 0A 1.6A

+16V(Phono) = +16V, (+ 3V, - 1V) 0A 200mA

+B 0.2A 0.8A

• Check + B voltage in standby > 145V and < 160V.

Short circuit test (all rails). PSU should go into standby/reset/lockup (supply may have to be removed to restart). Audio rail should be

tested , Q921 source to 0V.

0.3A 0.8A

0.3A 0.8A

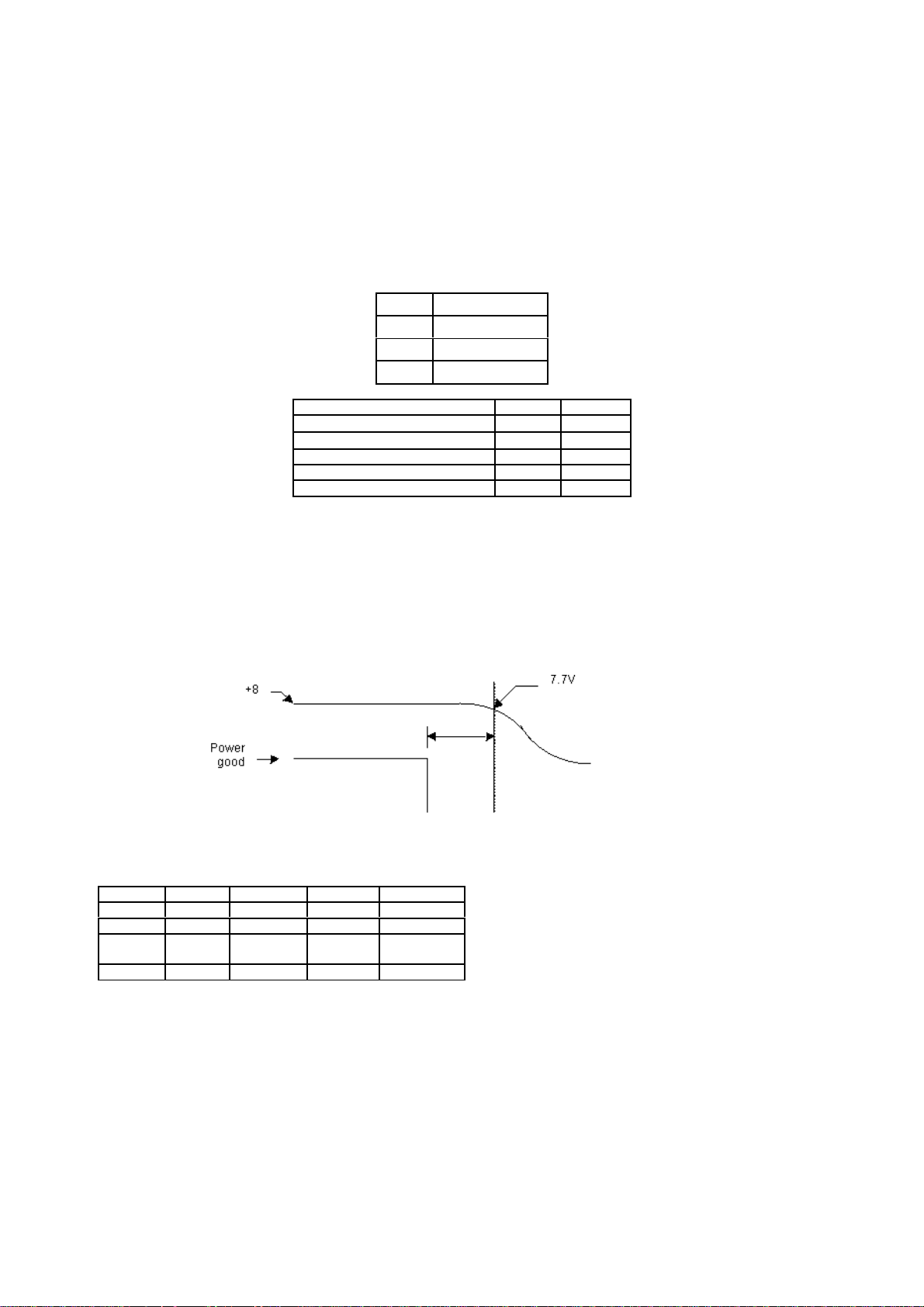

POWER AND DEFLECTION ADJUSTMENT

POWER GOOD LINE

PRIMARY CURRENT LIMIT

(Pre-set R980 to mid point)

Rail Trip Load Check Load Trip Power Check Power

+B 1.2ADC 1.1A 180W 165W

+16V 2.24ADC 1.65A 36W 26W

+11V

(+5, +8)

TOTAL W 234W 209W

• In standby apply full load +40%, to the +B & audio/+11V rails (dynamic load) as table above.

• Adjust R980 until set trips out .

• In standby apply check load. PSU should not trip.

• Set picture to same conditions as above.

• Measure pin 2 I903. Should be HI, if LOW then cut R962 (if fitted). If HI but no power down timing (see below)

then cut R955 (if fitted).

• Check power down logic timing ( >40mS, < 300mS )

• After setting power good , check operation at 200V AC mains

1.60A 1.60A 18W 18W

STANDBY OPERATION CHECK

• Check all rails (except +B and standby +5V) go to 0V.

• Check +B does not rise above 160V

5

Page 7

GENERAL SAFETY CHECKS

• High voltage BEAB test to confirm components across barrier (including sub board).

• Deg relay insertion orientation test (relay can be fitted inverted on main and sub PSU console stand). + Job instruction to

show orientation of relay.

SUB BOARD PSU CHECK (DTT/BASS/CONSOLE PSU)

• Short circuit test (all rails)

• Output voltage test (all rails), see table.

• Standby operation. All rails should be off. +10V remains to supply, sub PSU & opto.

• Full load operation check.

RAIL DTT BASS CONSOLE

38V / 0.62A 0.62A

32V / / 0.92A

9V 400mA / /

5.1V 1.5A Used for mute Used for mute

3V3 2.7A / /

30V 10mA / /

12V 10mA / /

DTT +5V SETTING

• Set VR1 to approx. centre position (10kΩ).

• Turn power on applying external load, see table.

• Adjust VR1 making sure +5.2V rail is within ± 0.05V.

SUB-BOARD MUST BE BEAB TESTED IN A SET OR CONSOLE STAND.

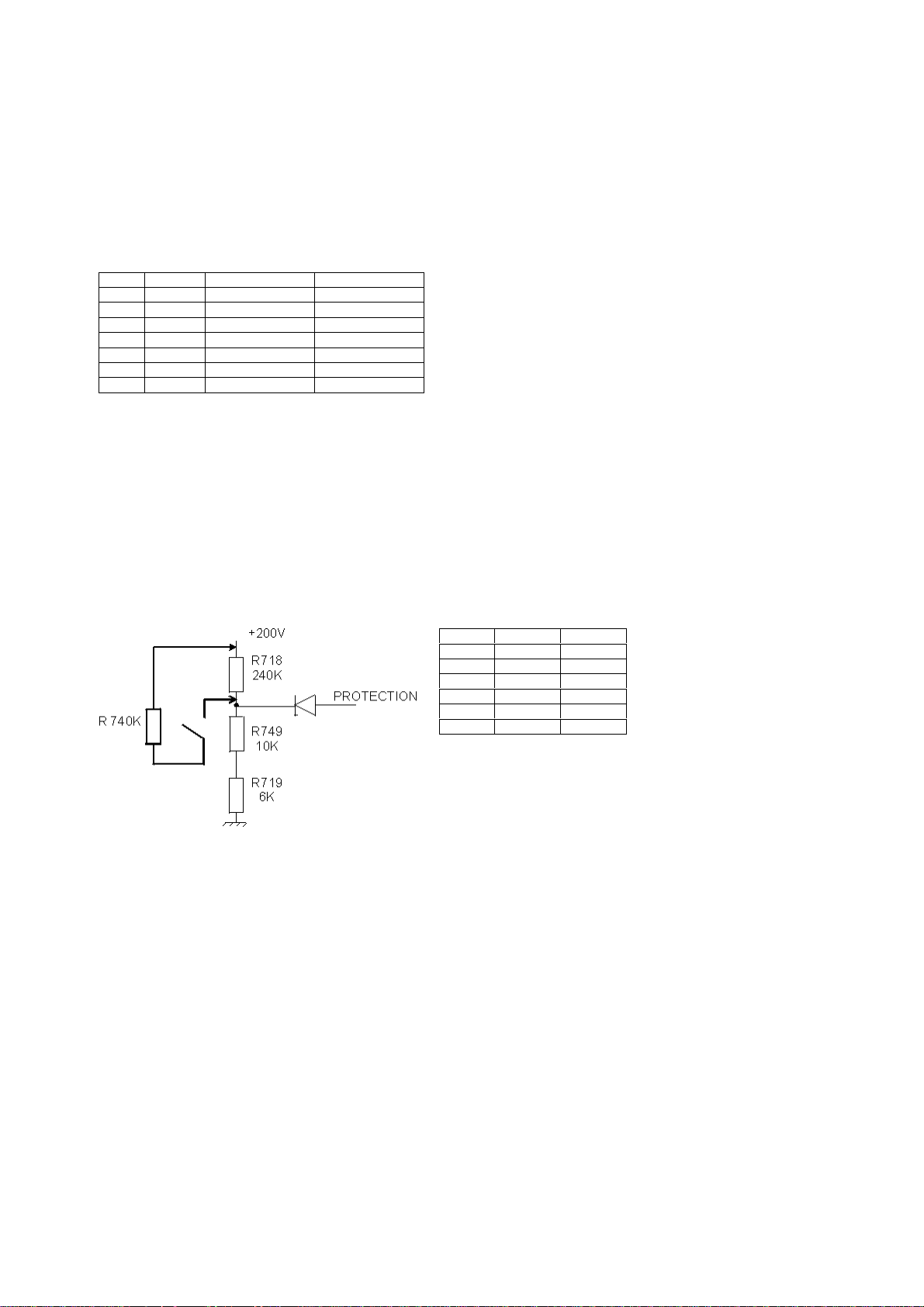

HIGH VOLTAGE LIMITER CIRCUIT CHECK

• Mount the PW board to the set and adjust normally.

• Receive the circle pattern signal.

• Set the contrast and brightness to maximum.

• Add R=470K in parallel with R718 and R718A.

• Check that picture and sound disappear when R is added.

NOTE:

High voltage limiter circuit jig:

2

25",28" 47K 4K7

28" 16/9 47K 4K7

32" 16/9 47K 4K7

ANODE/FOCUS SHORT-CIRCUIT TEST PROTECTION CIRCUIT CHECK

• Add a dc voltage to R760 until set trips ( The dc level should be equivalent to 1.7 x (+B current peak value )

0.6 VDC R760 SET SHOULD NOT TRIP

1.6 VDC R760 SET SHOULD TRIP

FINAL ANODE VOLTAGE LEVEL CHECK.

Please check on all A8 models that the final anode voltage does not exceed the voltages stated.

28" widescreen 31kV

32" widescreen 32kV

This test should be carried out with the brightness and the contrast set to minimum.

R719 R749

6

Page 8

FOR FEATURE BOX (A8 ONLY)

5V & 8V SHORT CIRCUIT CHECK USING FEATURE BOX BOARD

• Measure the resistance between 5V (EU11, pin1) and GND (EU11, pin3) by multi-meter. If the meter shows 62.5 ± 4Ω,

The FEATURE BOX is OK.

• Measure the resistance between 8V (EU11, pin6) and GND (EU11, pin3) by multi-meter. If the meter shows 1.29 ± 0.1kΩ,

If these resistance are not correct, Please check solder bridge or solder losing around IU03 (SDA9272).

FEATURE BOX OPERATION CHECK

The FEATURE BOX is OK.

• Fit FEATURE BOX onto main board.

• Receiving circle pattern (PAL), checking the picture quality. Check: Horizontal line is stable (see horizontal line). <-----

Only for 2897,W35 models Colour bar part is correct (see colour bar). White part of picture is pure white(see greyscale).

• Check the progressive scan/100Hz operation by handset (scan-key) <----Only for 2897,W35 models.

• Change sharpness , CTI , compression (14:9, 4:3 & zoom), noise reduction (low, mid & high) by handset. Check the total

Receive an NTSC signal , check same items as PAL.

performance. Whenever digital noise is appears on the picture, or miss operation occurs, reject the feature box.

7

Page 9

PICTURE POSITION/SHAPE

HORIZONTAL PHASE

VERTICAL CENTRE

VERTICAL AMPLITUDE

• Wait 5 minutes minimum after switching on the mains before adjustment.

• Receive the Philips circle pattern.

• Set brightness and contrast to maximum.

• The set should face North or South.

• AC input should be 230V ± 5V 50Hz.

• Adjust software control (using PC / HAND SET)

• Adjust control so that the centre of the picture is as in the diagram below.

Note:

The picture should be exaggerated as to create a barrel type picture at the vertical edges. The compensation to achieve this barrel

picture should be 3 steps passed the normal vertical edge position. This is to compensate for the pin cushion effect noticeable on

the OSDs.

TILT

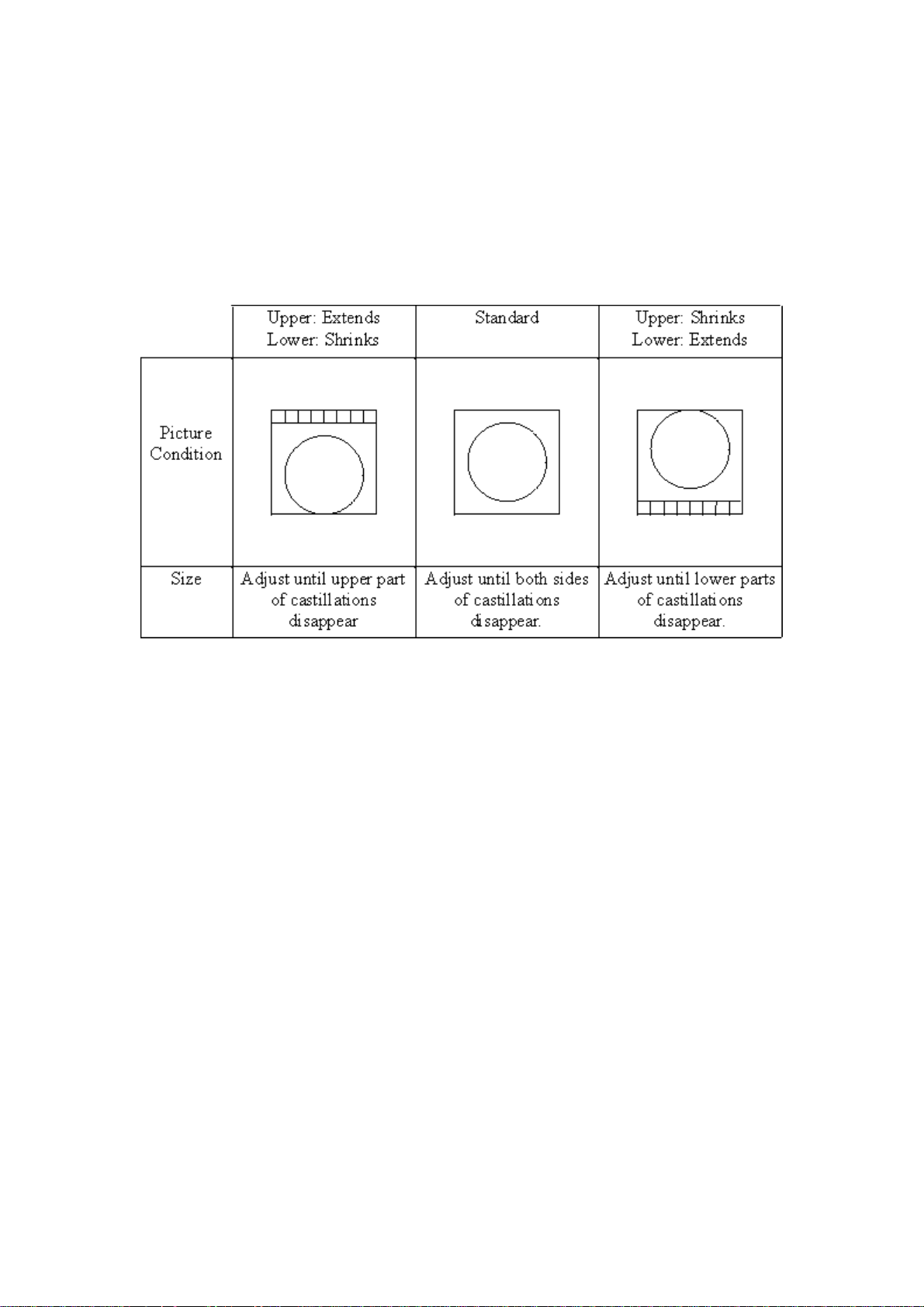

PARABOLA

WIDTH

• Allow 5 minutes warm up time before adjustment.

• Receive Philips circle pattern.

• Set brightness and contrast to nominal.

• The set should face North or South.

• AC input should be 230V ± 5V 50Hz.

• Adjust software so that the vertical lines at the outside edges of the screen are adjusted to be roughly vertical.

• Adjust the software so that the (approximately) vertical lines at the sides of the screen are adjusted as vertical as the

centre of the screen.

• Adjust the software so that the castillations at the sides of the picture are not quite visible. Reduce the brightness and

contrast to make sure that the picture width has not reduced so that you can see beyond the castillations. You may have

NOTE. For all 16:9 receivers the picture should be first set up in 16:9 mode, then final adjustment for parabola and corner correction

only to be carried out in 4:3 mode.

to repeat stages 6 and 7 again.

8

Page 10

FOCUS ADJUSTMENT

• Receive the Philips circle pattern.

• Adjust after horizontal/vertical has been adjusted.

• Switch the received signal to the cross hatch signal.

• Turn the focus VR gradually clockwise from the full counter clockwise position so that the focus of the vertical line in the

centre part, furthest to the right is adjusted for best result (contrast - maximum, brightness - normal).

WHITE BALANCE ADJUSTMENT

• Receive 100% white signal. (Do not use factory signals, use generator through RF, for improved signal)

• Set Colour Saturation to centre

• Adjust Red and Blue bars using the 'white point' menu Measurement to be made at 10cd

CL Model 7400oK

W30 Models 8700oK

C Model 9300oK

All new models from August 1999 (including the W30), the colour temperature should be set to 8700K

TEXT BRIGHTNESS

• Set text pattern to white box test pattern

• Adjust brightness to 90Cd/m

2

CUT-OFF ADJUSTMENT

• Rough Adjustment.

• Set video mode with no signal.

• Turn screen pot of FBT until lines disappear.

• Fine Adjustment.

• Select A.V mode without any signal applied.

• Service »» white point »» more on bottom line. You can see

This is an indication of the black current status (cut-off). Adjust it to 'i-' with screen pot of FBT.

0+ or i- or 0-

PICTURE SOFTWARE SETTINGS.

SEE SHIPPING SPEC. TABLES AT THE END OF THIS DOCUMENT.

RGB SHIFT

• Receive RGB signal from scart, and SERVICE»» HORIZONTAL»» RGB SHIFT by handset.

• Adjust the horizontal picture position by changing RGB SHIFT.

9

Page 11

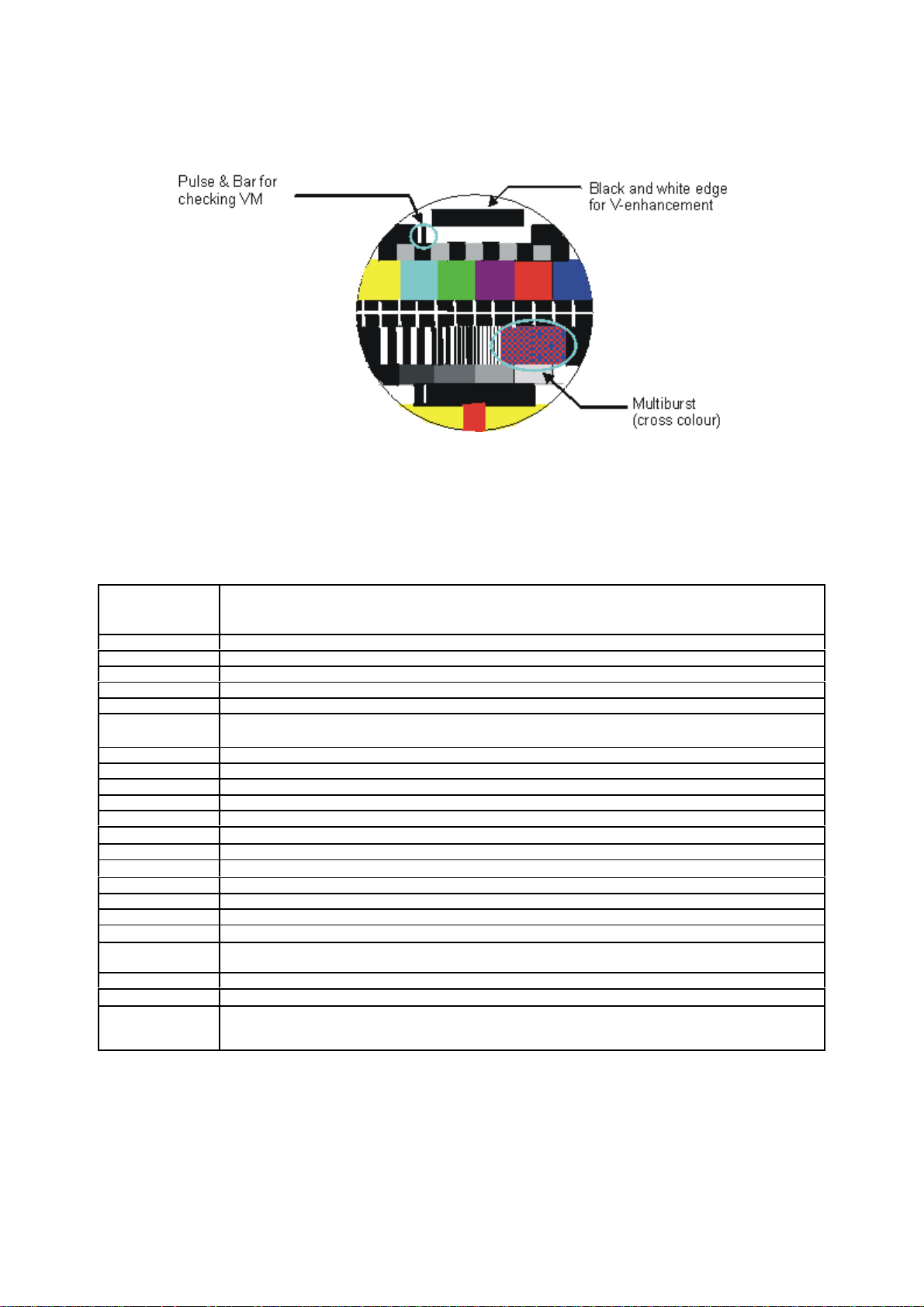

COMBFILTER OPERATION CHECK

• Receive Philips circle test pattern. PICTURE»» MORE»»COMBFILTER by handset

• Ensure the combfilter is ON using handset and watch the multiburst making sure there is no 'Cross Colour'.

• Check "VERTICAL ENHANCEMENT" by watching horizontal edge of black and white.

• Check the total picture quality.

VM OPERATION CHECK

• Receive Philips circle pattern.

PICTURE»» MORE»» VM by handset

Check the bar width changes wider (see above ) when VM is switched ON by handset.

DTT MODULE FUNCTION CHECK LIST.

FUNCTION

Reception Lower

Channel (ch.21)

Video Output No error

RGB Output No error, right colour

Audio Output L/R out, No error

BER* under 7.00E-003

Reception Centre

Channel (ch.41)

Video Output No error

RGB Output No error, right colour

Audio Output L/R out, No error

BER* under 7.00E-003

Modem

RS232

Output from Module Indicate running software status correctly

Input to Module Possible to input command

PCMCIA

Software Upgrade

from PC Card

RF Output

OK STATUS

Possible to upgrade

Check the function of the RF output terminal for a gain of +2dB/-3dB.

Reduce the level of the digital test signal to -65dBm, there should be no blocking on screen. This test must

be performed with the +5V supply adjusted so that its voltage is set to the minimum, inside the tolerance i.e.

5.1V - 1% = 5.05 V.

OVER-LOAD PROTECTION CHECK.

• To check for tripping during maximum load for picture, set a signal generator to Black to White bounce signal.

10

Page 12

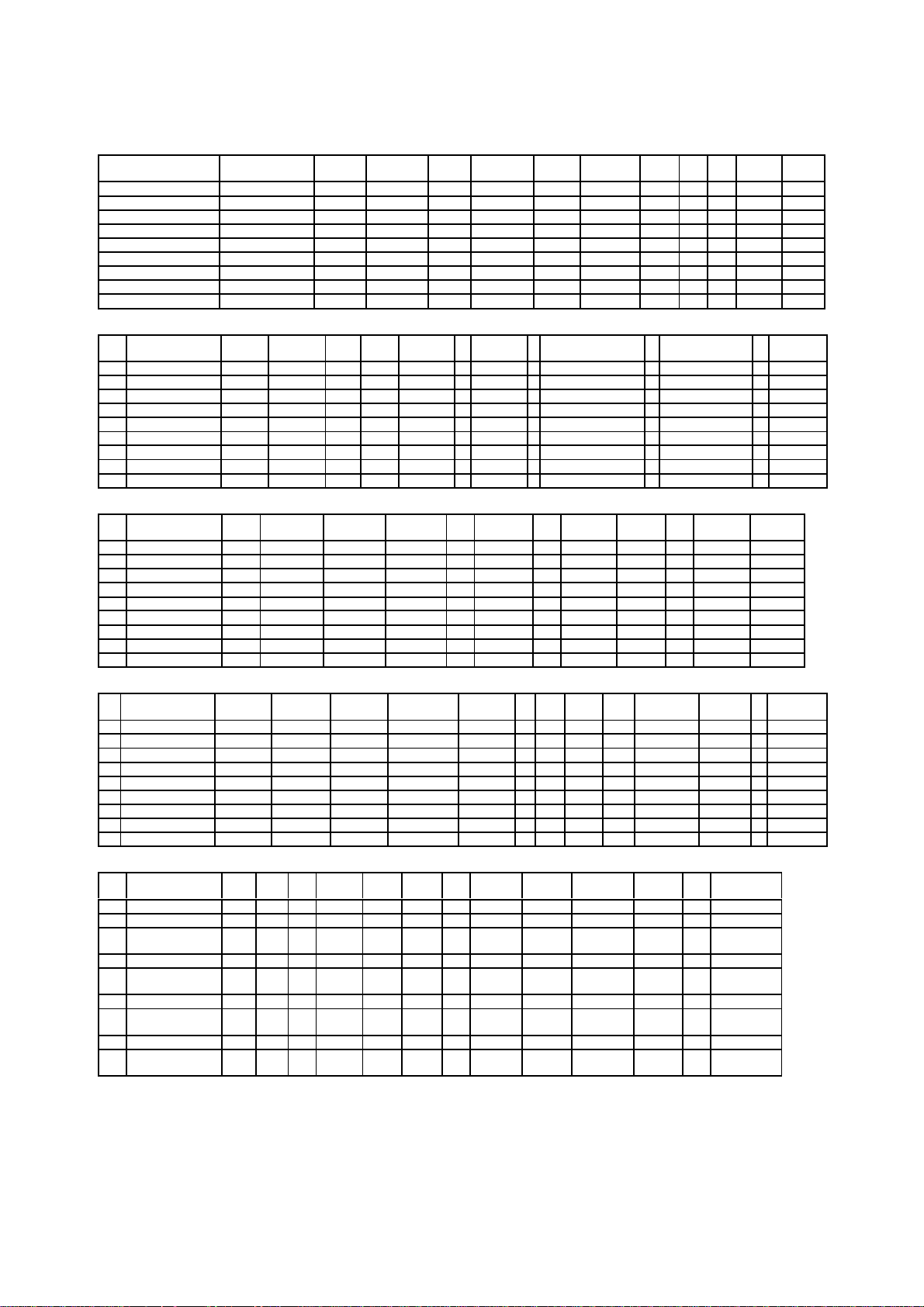

SHIPPING SPEC. TABLES

SERVICE DATA SETTINGS. This is the data set in SERVICE mode for various models.

Model No. Contrast Brightness Colour Sharpness More… Noise

1 C28W40TN(A) 100% 50% 50% 50% Off N/A Off On Normal Off

2 C32W30TN(A) 100% 50% 50% 50% Low N/A Off N/A Normal On

3 C32W35TN(A) 100% 50% 50% 50% Off Off Off Off Normal On

4 C32W40TN(A) 100% 50% 50% 50% Off N/A Off On Normal Off

5 C32W2000N 100% 50% 50% 50% Off Off Off Off Normal On

6 CL28W30TAN(A) 100% 50% 50% 50% Low N/A Off N/A Normal On

7 CL28W35TAN(A) 100% 50% 50% 50% Low Off Off Off Normal On

8 CL32W30TAN(A) 100% 50% 50% 50% Low N/A Off N/A Normal On

9 CL32W35TAN(A) 100% 50% 50% 50% Low Off Off Off Normal On

SERVICE DATA SETTINGS. This is the data set in SERVICE mode for various models.

Model No. Volume Loudness more Mode Graphic

1 C28W40TN(A) 10% Off 1 50% Pro Logic N/A Digital Auto

2 C32W30TN(A) 10% Off 1 50% N/A 100Hz Analogue Auto

3 C32W35TN(A) 10% Off 1 50% Pro Logic Progressive Analogue Auto

4 C32W40TN(A) 10% Off 1 50% Pro Logic N/A Digital Auto

5 C32W2000N 10% Off 1 50% Pro Logic Progressive Analogue Auto

6 CL28W30TAN(A) 10% Off 1 50% N/A 100Hz Analogue Auto

7 CL28W35TAN(A) 10% Off 1 50% Pro Logic Progressive Analogue Auto

8 CL32W30TAN(A) 10% Off 1 50% N/A 100Hz Analogue Auto

9 CL32W35TAN(A) 10% Off 1 50% Pro Logic Progressive Analogue Auto

SERVICE DATA SETTINGS. This is the data set in SERVICE mode for various models.

Model No. Sleep

Timer

1 C28W40TN(A) Off Panoramic Panoramic On English 100% Mid On Normal

2 C32W30TN(A) Off Panoramic Panoramic On English N/A N/A On N/A

3 C32W35TN(A) Off Panoramic Panoramic On English 100% Mid On Normal

4 C32W40TN(A) Off Panoramic Panoramic On English 100% Mid On Normal

5 C32W2000N Off Panoramic Panoramic On English 100% N/A On Phantom

6 CL28W30TAN(A) Off Panoramic Panoramic On English N/A N/A On N/A

7 CL28W35TAN(A) Off Panoramic Panoramic On English 100% Mid On Phantom

8 CL32W30TAN(A) Off Panoramic Panoramic On English N/A N/A On N/A

9 CL32W35TAN(A) Off Panoramic Panoramic On English 100% Mid On Phantom

Default

Zoom

Default

4:3

Equaliser

Auto Wide

Detection

Sound

Language Surround

100Hz/ Progressive

Mode

Reduction

Scan

Set-up

Comb

Filter

Digital/ Analogue

Seating

Internal

Position

CTI VM White

Mode

Speakers

Point

16:9 Mode

Channel

Centre

Black

Stretch

SERVICE DATA SETTINGS. This is the data set in SERVICE mode for various models.

Model No. AV1 VCR

1 C28W40TN(A) On Auto On RF Off Off I Off 11 76 Off

2 C32W30TN(A) On Auto Off RF Off Off I On 11 76 N/A

3 C32W35TN(A) On Auto Off RF Off Off I Off 11 76 Off

4 C32W40TN(A) On Auto On RF Off Off I Off 11 76 Off

5 C32W2000N On Auto On RF Off Off I Off 11 76 On

6 CL28W30TAN(A) On Auto Off RF Off On L/L’ On 11 76 N/A

7 CL28W35TAN(A) On Auto Off RF Off On L/L’ On 11 76 On

8 CL32W30TAN(A) On Auto Off RF Off On L/L’ On 11 76 N/A

9 CL32W35TAN(A) On Auto Off RF Off On L/L’ On 11 76 On

SERVICE DATA SETTINGS. This is the data set in SERVICE mode for various models.

Model No. RGB

1 C28W40TN(A) 35 31 32 4 4 83V 3 31 N/A Single

2 C32W30TN(A) 35 31 32 4 4 71V 3 31 N/A Single

* C32W35TN(A)

(Old FB/New FB)

4 C32W40TN(A) 35 31 32 4 4 83V 3 31 N/A Single

5 C32W2000N

(Old FB/New FB)

6 CL28W30TAN(A) 35 31 32 4 4 71V 3 31 16 Single

7* CL28W35TAN(A)

(Old FB/New FB)

8 CL32W30TAN(A) 35 31 32 4 4 71V 3 31 16 Single

9* CL32W35TAN(A)

(Old FB/New FB)

Mode

Shift

AV1 SAV

Mode

Text

Shift

35 31 32 4 4 62V/71V 3 31 N/A Single

35 31 32 4 4 62V/71V 3 31 N/A Single

35 31 32 4 4 62V/71V 3 31 6/16 Single

35 31 32 4 4 62V/71V 3 31 6/16 Single

AV2 VCR

Mode

R, G, B Cool

Offset

*AV2 Output

Mode

Warm

Offset

AV3 VCR

Mode

Cathode

Level

B/G Other VHF AFC Offset L’ Offset 3DS Mode

C Delay Text

Brightness

SECAM

Offset

Current Text

Mode

11

Page 13

SERVICE DATA SETTINGS. This is the data set in SERVICE mode for various models.

Model No. Top

1 C28W40TN(A) Off SGL JBL Off Off Off 1 50% 1 1

2 C32W30TN(A) Off SGL JBL Off Off Off 1 50% N/A 1

3 C32W35TN(A) Off SDS JBL Off Off On 1 50% N/A 1

4 C32W40TN(A) Off SGL JBL Off Off Off 1 50% 1 1

5 C32W2000N Off SDS JBL Off Off Off 1 50% N/A 1

6 CL28W30TAN(A) On SGL JBL Off Off On 1 50% N/A 1

7 CL28W35TAN(A) On SDS JBL Off Off On 1 50% N/A 1

8 CL32W30TAN(A) On SGL JBL Off Off On 1 50% N/A 1

9 CL32W35TAN(A) On SDS JBL Off Off On 1 50% N/A 1

Text

Text

Modes

Processor Tube

Type

M Gating Hotel

ModeNoStandby

Prog. Max.

Volume

DTT

Prog.

Unit

ID

12

Page 14

DIGITAL COMB FILTER – TOSHIBA TC9090AF.

The operation of a comb filter is to separate the composite video into luminance and reconstruct the chrominance colour sub carrier

signal using digital signal processing techniques. The comb filter IC, IN01 has an additional vertical edge enhancement feature.

Composite video input (Pin 6 of connector E500) and colour sub-carrier (pin 8 of E500) are converted via an 8 bit analogue to digital

converter where the vertical enhancement and digital comb filtering takes place. Separated luminance and chrominance output

components are available via a digital to analogue 8 bit converter at pins 1 & 4 respectively.

SCAN VELOCITY MODULATION.

During transmission the signal sufferers from degradation and also due to the frequency characteristics of the television circuitry.

This normally results in a gently rise or fall in the luminance change areas when black-to-white-to-black patterns are received.

The picture sharpness quality can be assessed by how steep the leading and trailing edges are. The scan velocity modulation circuit

has been designed to improve picture quality, i.e. make the video signal edges steeper, by controlling the horizontal scanning

velocity of the electron beam in the CRT.

The velocity modulation circuit produces a compensation signal by adding the RGB components then differentiating. The

compensation signal is given some current gain, applied to the auxiliary coil (connector E806) on the neck of the cathode ray tube

(CRT).

The VM circuit is located on the CRT base along with the final RGB amplifiers. The RGB signals derive from PL803 pins 4-6 and

into emitter of Q861, through the differentiator C863, R891 arriving at the base of Q862 for voltage amplification and latter stages,

power gain.

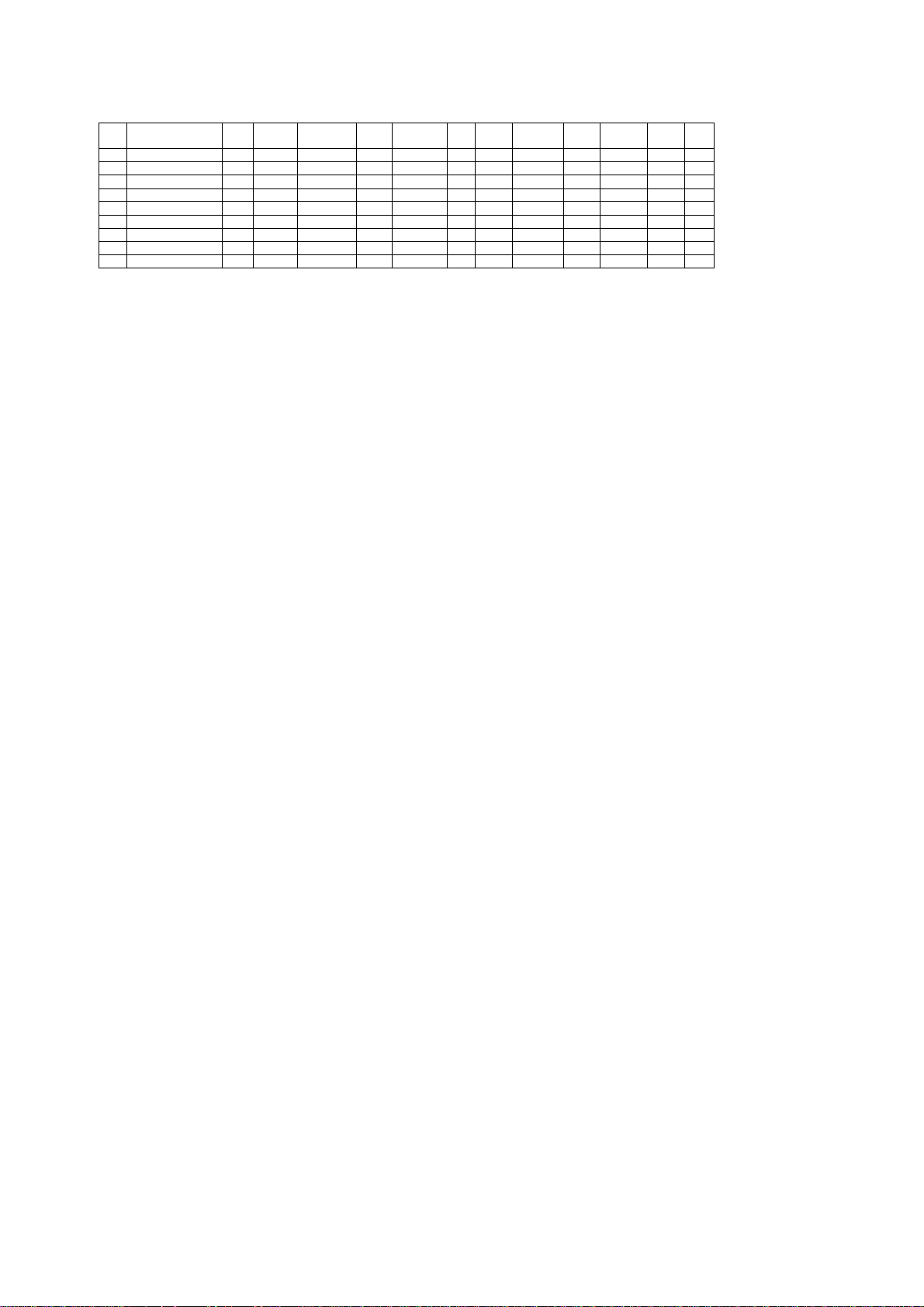

DIGITAL DOUBLE SCAN CONVERSION UNIT (FEATURE BOX).

The main feature of this unit is double scan frequency conversion, 100/120Hz interlaced and 50/60Hz progressive scan. Other

features of this unit are CTI (Colour Transient Improvement), horizontal compression, noise reduction, sharpness and vertical zoom.

These functions are controlled by I2C bus and are provided elsewhere by the picture improvement IC, TDA 9178 (IE01) for digital

models without 100Hz/progressive scan.

Scan rate conversion mode for display

13

Page 15

As the diagram shows, A/B are the Odd/Even original 50Hz signal fields which are used to create extra picture information, while

A*/B* are the predicted/manipulated extra picture information, created by the feature box. Fig.1 shows the differences between

100/120Hz interlaced and 50/60Hz progressive scan. The biggest advantage of progressive scan is "non-interlaced" scanning;

keeping the field frequency at 50/60Hz. This means the line construction is double per field, compared with 100/120Hz interlaced. It

will make very fine pitch scan lines and will eliminate line flicker. The advantage of selecting 100Hz operation will be the reduction of

large area flicker and will reduce the line flicker (except for A8 W30 100Hz models).

This unit is powered from +5V and +8V supplies, feeding into pins 21, 22 and 26 of E10 respectively. The three input 50Hz video

signals Y, U, V are sent to this unit at pins 8, 10 and 12 of E11. The Y, U, V video output signals (double frequency video) are taken

from pins 5, 3 and 1 of E11. The horizontal and vertical sync signals are input to this unit as a composite sync signal at 24 of E10,

the double frequency horizontal and vertical sync signals outputs are from pins 30 and 31of E10.

INPUT PROCESSOR - PHILIPS TDA 9320.

The TDA9320 is a multistandard input processor. Features include:

VIDEO OUTPUTS/EXTERNAL INPUTS.

The input processor has provision for three CVBS inputs (1 internal & 2 external) and 2 Y/C inputs. The external CVBS inputs are

used for the Scart sockets. The Y/C inputs are used for S-VHS and a third CVBS input. The circuit can detect whether CVBS or a

Y/C signal is presented to AV3 input. The I.C. has 2 RGB inputs with fast switching. The switching of the various sources is

controlled by I2C and detection of a Comb filter can be made.

SYNCHRONISATION.

The sync separator is preceded by a controlled amplifier which adjusts the sync pulse amplitude to a fixed level. These pulses are

fed to the slicing stage which is operating at 50% of the amplitude. The sync pulses are fed to the phase detector and to the

coincidence detector. This coincidence detector is used to detect whether the line oscillator is synchronised and can also be used

for transmitter identification. The PLL has a very high statical steepness so that the phase of the picture is independent of the line

frequency.

For the horizontal output pulse, two conditions are possible:

An HA pulse which has a phase and width which is identical to the incoming horizontal sync pulse.

A clamp pulse CLP which has a phase and width which is identical to the clamp pulse in the sandcastle pulse.

The HA/CLP signal is generated by means of an oscillator which is running at a frequency of 440 x FH. Its frequency is divided by

440 to lock the first loop to the incoming signal. The free running frequency of the oscillator is determined by a digital control circuit

which is locked to the reference signal of the colour decoder. When the coincidence detector indicates an out of lock situation the

calibration procedure is repeated.

The vertical pulse is obtained via a vertical count down circuit. The countdown circuit has various windows depending on the

incoming signal (50/60Hz).

VISION I.F. AMPLIFIER.

The video signal is demodulated by means of a PLL carrier regenerator. This circuit contains a frequency detector and a phase

detector. During acquisition the frequency detector will tune the VCO to the right frequency. After lock-in, the phase detector controls

the VCO so that a stable phase relation between VCO and the input signal is achieved. The VCO is running at double the I.F.

frequency with the reference signal for the demodulator obtained by means of a frequency divider circuit.

The AFC output is obtained by using the VCO control voltage of the PLL and can be read via the I2C bus. The AGC detector

operates on top sync and top white level. The time constant on the AGC system during positive modulation is long to avoid visible

variations of the signal amplitude. To improve the speed of the AGC system a circuit has been included which detects whether the

AGC detector is activated every frame period. When during 3 field periods no action is detected the speed of the system is

increased. For signals without peak white information the system switches automatically to a gated black level AGC. Because a

black level clamp pulse is required for this way of operation the circuit will only switch to black level AGC in the internal mode.

The circuit contains a video identification circuit which is independent of the synchronisation circuit. Therefore search tuning is

possible when the display section of the receiver is used as a monitor.

CHROMA & LUMA PROCESSING.

The I.C. contains a chrominance bandpass filter , the SECAM cloche and chrominance traps. The filters are calibrated using the

tuning frequency and the crystal frequency of the colour decoder. The luminance output signal which is derived from the incoming

CVBS or Y/C signal can be varied in amplitude by means of a separate gain control.

COLOUR DECODING.

The colour decoder can decode PAL, NTSC and SECAM signals. The PAL / NTSC decoder contains an alignment free crystal

oscillator with 4 separate pins, a killer circuit and two colour difference demodulators. The 90o phase shift for the reference signal is

made internally. Because it is possible to connect 4 different crystals to the colour decoder, all colour standards can be decoded

without external switching circuits. Crystals not used must be left open. The horizontal oscillator is calibrated by means of the crystal

frequency of the PLL.

The I.C. contains an automatic colour limiting circuit which is switchable which prevents over saturation when signals with a high

chroma-to-burst ratio are received. The acl circuit is designed such that it only reduces the chroma signal and not the burst. This has

the advantage that the colour sensitivity is not affected by this function.

The SECAM decoder contains an auto-calibrating PLL demodulator which has two references, the 4.43MHz sub-carrier frequency

which is obtained from the crystal oscillator which is used to tune the PLL to the desired free running frequency and the bandgap

reference to obtain the correct absolute value of the output signal. The VCO of the PLL is calibrated during each vertical blanking

period, when the I.C. is in search or SECAM mode. The base-band delay line is integrated into the package.

14

Page 16

PICTURE IMPROVEMENT - PHILIPS TDA 9178.

The picture improvement IC is an analogue video processor offering three main processing functions; luminance vector, colour

vector and spectral processing. Features presently being implemented are; luminance transient improvement (LTI), colour transient

improvement (CTI), variable gamma control and picture dependant non-linear Y and U, V processing by luminance histogram

analysis.

The spectral processor provides luminance transient improvement, luminance detail enhancement by smart peaking and colour step

improvement (CTI). The linewidth control may be user defined. The luminance vector processor, the transfer function is controlled in

a non-linear manor by histogram analysis of measured luminance values measured in a picture. As a result the contrast ratio of the

most important parts of the scene will be improved. A variable gamma function after the conversion offers the possibility of

alternative brightness control or factory adjustment of the picture tube.

The following functions sharpness, noise reduction and colour transient improvement (CTI) are provided by the picture improvement

IC for digital models, while 100Hz/progressive scan models provide these functions within the double scan module. All functions

described are switchable/adjustable via I2C control using the options in the service menu.

Y, U and V signals are taken from I200 pins 49, 50 & 51 and go straight into Yin Uin and Vin (pins 6, 8 and 9 of IE01). The enhanced

Y, U & V outputs originate from IE01 (pins 19, 17 & 16 respectively) and are directed to IE02 (pins 28, 27 & 26 respectively).

TUNER.

The tuner U100, is a frequency synthesis type with an unbalanced input, powered from the +5V rail while the tuning voltage is

supplied by the +33V rail, supplied from the horizontal deflection circuit. Direct frequency access, channel selection, AGC and AFC

functions are controlled via the I2C bus. AGC, AFC and Offset controls may be selected by entering the service menu and selecting

the ‘tuner’ option.

Pin 1, AGC is taken from pin 62 of TDA 9320. The balanced I.F. output is taken from pins 10 & 11, which are then arrive at both the

inputs of the vision and sound SAW filters (pins 1 & 2). The outputs from X200 and X202 (pins 4 & 5 respectively) pass through to

pins 2 & 3 and pins 63 & 64 of I200, where they are demodulated.

RGB PROCESSOR - TDA 9330.

VERTICAL DEFLECTION & GEOMETRY CONTROLS.

The drive circuit for the vertical and E-W deflection circuits are generated by means of a vertical divider which gets its clock from the

line oscillator. The divider is synchronised by the incoming vertical pulse, generated by the input processor or the feature box.

The vertical drive is realised by means of a differential output current. The outputs must be DC coupled to the vertical output stage.

The vertical geometry can be adjusted by I2C control via the service menu.

HORIZONTAL SYNCHRONISATION & DRIVE CIRCUIT.

The horizontal drive signal is obtained from an internal VCO which is running at a frequency of 13.75MHz. This oscillator is

stabilised to this frequency by means of a resonant oscillator 12 MHz. The internal VCO is synchronised to the incoming horizontal

Hd pulse by means of a PLL with an internal time constant. The horizontal drive signal generated by means of a second control loop

which compares the phase of the reference signal from the internal VCO with the flyblack pulse. The time constant loop is internal.

The I.C. has a dynamic horizontal phase correction input which can be used to compensate phase shifts which are caused by beam

current variations. Additional settings of the horizontal deflection which are realised via the second loop are the horizontal shift and

the parallelogram correction.

The horizontal drive signal is switched on and off via the so called soft-start/soft-stop procedure. This function is realised by means

of a variation to the Ton of the horizontal drive pulse. For EHT generators without bleeder the I.C. can be set in a fixed beam current

mode. In that case the picture tube capacitance is discharged with a current of about 1mA which is determined by the black current

feedback loop. With the fixed beam current option activated it is still possible to have a black screen during switch-off. This can be

realised by placing the vertical deflection in an overscan position.

An additional function of the I.C. is the low-power start-up feature. This mode is activated when a supply voltage of 5V is supplied to

the start-up pin. The required current for this function is 3mA typical. In this condition the horizontal drive signal has the normal T

and Ton grows gradually from zero to about 30% of the normal value. This results in a line frequency of about 50kHz or 25kHz. The

output signal remains unchanged until the mains voltage is switched-on. Then the horizontal drive signal will gradually change to the

normal frequency and duty cycle via the soft-start procedure.

The I.C. has a general purpose bus controlled DAC output with a resolution of 6 bits and with an output voltage range between 0.2

to 4V.

off

INPUT SIGNALS.

The RGB control circuit of the TDA 9330 contains three sets of input signals.

Y, U, V, input signals which are supplied by the input processor or feature box. The nominal input signals for u and V are 1.33 V

and 1.05V

to-Peak

Two RGB sources are intended for use by the Scart, while the second is used for the OSD and teletext. The required input signal

has an amplitude of 0.7V

. this input is only controlled by brightness.

Switching between various sources can be realised via the I2C bus and by fast insertion switches. The circuit contains switchable

matrix circuits for the colour difference signal so that the colour reproduction can be adapted for PAL/SCAM and NTSC.

Peak-to-Peak

respectively. These input signals are controlled by brightness, contrast and saturation.

Peak-to-Peak

. The switching between the internal signal and the OSD signal can be realised via a fast blanking

Peak-

OUTPUT AMPLIFIER.

The output signal has an amplitude of around 2V black-to-white at nominal settings. The required white point setting of the picture

tube is implemented by 3 separate gain settings for the RGB channels.

15

Page 17

To obtain an accurate biasing of the tube, a continuous cathode calibration circuit is implemented by means of a two point black

level stabilisation circuit. By inserting 2 test levels for each gun and comparing the resulting cathode currents with two different

reference currents the influence of the picture tube parameters like the spread in cut-off voltage can be eliminated.

SIGNAL PATH DESCRIPTION.

The I.F. signal is obtained from SAW filters X200 (vision) and X202 (Sound ) pins 4 & 5 and are fed into pins 2 & 3 vision and 63 &

64 sound of I200. A composite video signal is available at pin 10 from the vision demodulator. I.F. sound out from pin 6. The video is

taken from pin 10 via C304 into pin 12 and out at pin 13. This is the selectable Group Delay via software input output. The

composite video gets taken through buffer and filtering stages where the desired video returns to I200 at pin 14.

The AV switching matrix supports two Scart sockets, phono CVBS and S-VHS inputs. Scart CVBS inputs are at pins 20 (AV1 E301)

and 16 (AV2 E302), CVBS outputs to Scart pins 19 from emitter of Q301 (AV1) and emitter of Q303 (AV2). The RGB input (Digital

models) to I200 from the Digital Terrestrial Tuner (DTT) comes to pins 36-38, from P301 pins 9, 7 and 5, respectively. S-VHS input

is via E300 to pin 23 & 24 of IE02, detection of CVBS input is detected within IE02. For models with progressive scan feature

detection for a Comb filter has been fitted via Y/C input pins 28 & 29. Colour sub-carrier output for the Comb filter is form pin 30.

Y, U and V signals are taken from I200 pins 49, 50 & 51 and go straight into Yin Uin and Vin (pins 6, 8 and 9 of IE01) for 50Hz

operation, while 100Hz operation, Y, U, V signals are directed to pins 9, 10 & 12 of the double scan module (UQ01).

Other miscellaneous pins such as the sandcastle pin 59 is independent of the sandcastle pulse generated by IE02, they do not drive

each other. The Vertical and Horizontal output pulses generated by I200 drive the double scan module, pins 18 & 19 respectively

(100Hz operation) or the IE02 (50Hz operation) pins 23 & 24. I2C control lines are pins 46 & 47, and tuner AGC control voltage is

present at pin 62.

As already previously described Y, U, V signals in either 50Hz/100Hz/Progressive scan mode are sent to pins 26-28 of the TDA

9330 (IE02). Once inside the RGB processor, geometry and synchronisation functions can be implemented before being sent to the

CRT base (pins 40-42 of IE02 & 3-5 of P302) for final video amplification and to the velocity modulation circuit.

The vertical drive output is provided by pin 1 & 2 of IE02 directly to I601 Vertical Output I.C. (pins 11 & 12). Horizontal output is from

pin 8 of IE02 and feeds the base of Q701 Bipolar (50Hz), Q701B MOSFET (100Hz). East-West drive output can be obtained at pin 3

and is driving the gate of the East-West MOSFET Q700.

I2C is present at pins 10 & 11 (IE02) and +8V supply rails at pins 7 & 17. Two sets of RGB inputs are available, only one set is used

for the OSD, pins 35-37, the other is for a VGA board which is not fitted.

AUDIO CIRCUIT

The output from the Tuner T1 is fed via a gain and buffer stage formed by Q200 and Q201 to the Saw Filter X202. The saw filter has

two separate characteristics depending on which of the two inputs (on pin 1 and 2 of the Saw Filter) the signal is applied to.

Selection is achieved by the combination of Q204 and Q203. For most standards, pin 1 is selected. However, when an L’ Signal has

been selected , the micro ( I001) instructs I200 via an I2C command to take pin 19 high. When this happens Q204 conducts taking

pin 1low and switching Q203 and D203 off. This means that the collector of Q203 goes high allowing D202 to conduct and hence

the signal to be applied to pin 2. To return to other broadcast standards, pin 19 of I200 is obviously returned to the low condition.

The output of the Saw is applied to pins 63 and 64 of I200. Here the Signal is transformed from the 1st IF (30 – 40 MHz depending

on transmission standard) to the sound IF (5.5 to 6.5 MHz depending on the transmission standard ).

I200 also provides AM demodulation for the L’ and L standards. The demodulated signal appears superimposed on the Sound IF on

pin 5 of I200.

This signal then takes two paths. The first takes it through a Low pass filter formed by R426 and C427 and coupling capacitor C426.

This is then applied to pin 55 of I400 and forms the AM sound Input. The second path takes the signal through a amplifier and buffer

stage formed by Q400 and Q401.

After these stages some high pass filtering is applied by C464 and R477 before the sound IF is applied to pin 60 of I400 via C431.

I400 is The MSP3410D. This IC provides Nicam , FM Mono and FM Stereo Demodulation as well as matrixing of the scart / digital

receiver signals (If Fitted).

The AV1 input is applied on pins 52 and 53, the AV2 input on pins 49 and 50, the AV3 input on pins 46 and 47. The Digital input

(DTT) is applied to pins 43 and 44 (when fitted). In Each case a 100R resistor and 330n capacitor is used.

The Scart outputs on I400 use the following protocol.

Scart Output

AV1 RF Digital

AV2 Selectable or Auto* Selectable or Auto*

*If auto is selected in the on screen menu’s, AV2 follows the audio of what is being watched the device is I2C Controlled via pins 10

and 11 and receives a reset from the micro at power up on pin 24.The clock is provided by X406 on pins 62 and 63. The device has

three supply rails, 5V Digital (Pin 18), 5v Analogue (Pin 57), and 8v Analogue (Pin 39).

Non Digital Models Digital Models

Output Signal

16

Page 18

AUDIO OUTPUT

The left, right, centre and surround signals are output from pins 29, 28 26 and 25 of the MSP3410D (I400) and are then applied to

an operational amplifier (IF03) at pins 5, 10, 12 and 3 respectively. This adds 3dB of gain.

The outputs from IF03 for the left and right (pins 7 and 8) are supplied to both the audio amplifier (I401) via the attenuation networks

R443 / R439 & R446 / R447 and the phono outputs via buffer transistors QF02 and QF01.

The centre and surround outputs from IF03 (pins 14 and 1) are only supplied to the phono outputs via buffer transistors QF22 and

QF21.

The left and right output stage consists of one TDA7297 (I401) which is a dual bridge amplifier which in this case is driven to give

12W per channel @ 10% thd. The power output is limited by the Vcc supply to pins 3 & 13.

The left and right signals are input to pins 4 & 6 and the outputs obtained from pins 1& 2 and 14 & 15.

Warning. Neither output for either channel is connected to the chassis ground so caution must be taken if an oscilloscope and

other mains operated equipment with a common earth is to be used simultaneously when checking the audio outputs.

The TDA7297 has two control lines on pins 6 & 7. These control inputs are high when the outputs are active and low when muted.

The outputs from pins 2 and 14 of I401 are connected directly to pins 2 and 3 of P400. The outputs from pins 1 and 15 are

connected to pins 1 and 4 of P400 via the headphone socket J400. When a set of headphones is inserted the connections between

I401 and P400 are broken. The left and right outputs from pins 1 and 15 of I401are connected to ground via C438 / R438 & the left

headphone coil and C437 / R437 & the right headphone coil respectively. This method was used to limit the power dissipated in the

headphones.

J400 also contains a switch for the 16V supply that appears at the rear single phono socket. When a suitable plug is inserted into

the headphone socket the connection between pins 8 and 9 of J400 is broken removing the 16V from pin 8. This is sensed by pin 19

of I001 (the micro processor) via the potential divider R473 and R474, this tells I001 to change the audio menu’s to the headphone

versions (Dolby models only).

The 16V is also removed from the rear phono socket, this turns off the infra red surround sound speaker transmitter or the power

console (if connected - not supplied with all models).

For non Dolby models the speaker leads are connected directly to P400. For Dolby models the internal speakers are connected

from P400 via a sub panel screwed to the rear of the chassis frame. This houses two din type speaker sockets with internal

switches. The switches disconnect the internal left and right speakers when a plug is inserted, thus allowing external left and right

speakers to be fitted.

DOLBY DECODER.

The Dolby decoding is provided by IF01 (YSS241) The signals which are sent to this device from I400 in the I2S format, and are:SD0 (Pin Of I400) - the Left and Right channel data (before Dolby decoding)

SCK (Pin Of I400) - the system or bit clock

WS (Pin Of I400) - the word select line, provides selection between the Left and Right samples on the SDO Line.

IFO1 is provided with an 18.432 MHz clock via pin 1 of I400 (SYSCLK),a reset line from pin 4, and is I2C controlled. The Pro-logic

signals that the device decodes are provided in I2S form at pins 40 and 41 (DACS1 and DALR) These signals are in a 32bit per

channel format ( The MSP4310D uses 16 bit) and must therefore pass through a conversion IC IF02. This IC also takes a Bit clock,

DABC from pin 36 of IF01. IF02 then provides the 16 bit pro-logic I2S channels as SDI1 and SDI2 on pins 14 and 20 of I400.

I400 then passes these signals through DAC’s so that the Left, Right, Centre and Surround signals appear at pins 29, 28,26 and 25

as Pre-L, Pre-R, Pre-C and Pre-S respectively. Theses are then amplified by 3dB by op-amp IF03 to become AmpL, AmpR, Centre

and Surround. These then pass through a buffer and filter network to the four way phono plug JF01. The AmpL and AmpR signals

split off before the buffers to the amplifier I401 via dividing resistors R443/R439 and R446/R447 and are decoupled by C443 and

C445. The operation of the amplifier is explained elsewhere in this manual.

DEFLECTION

100HZ HORIZONTAL DEFLECTION STAGE (A8)

The 2H output from UQ01 (the feature box) from pin 30 is fed via K66 and RH03 to pin 24 of IE02 TDA9330 the "HOP".

The horizontal drive is then output from pin 8 is passed through an emitter follower stage (Q705) to the gate of Q701B. A mosfet is

used to sharpen the switching edges and reduce the temperature of the power transistor Q751. The drain of Q701B is fed from the

+B via R701 and the primary of the drive transformer T702. The secondary of the transformer drives the base of the power transistor

Q751, the collector of which is supplied from the +B via R751, L700 and the primary of the FBT T701. The emitter is connected to

ground via R760 a 1 Ohm 10W resistor ( R760 should be kept away from Q751 heatsink to reduce heat transfer) which is a sense

resistor for the protection circuit.

The capacitive divider network C717 and C708 produce a line pulse which is sampled by Z704 and clamped by D713 and D714 this

is then returned to pin 13 of IE02.

50HZ HORIZONTAL DEFLECTION STAGE (D8)

The HA OUT from pin 60 of I200 TDA9320 the "HIP" is fed via K66 and RH03 to pin 24 of IE02 TDA9330 the "HOP".

The horizontal drive is then output from pin 8 is fed to the base of Q701. The collector of Q701 is supplied from the +B via R701 and

the primary of the drive transformer T702. The secondary of T702 drives the base of the power transistor Q751. The collector of

Q751 is supplied from the +B via R751, L700 and the primary of the FBT T701. The emitter is connected to ground via R760 which

is a sense resistor for the protection circuit.

The capacitive divider network C717 and C708 produce a line pulse which is sampled by Z704 and clamped by D713 and D714 this

is then returned to pin 13 of IE02.

17

Page 19

VERTICAL DEFLECTION

On the 50Hz D8 the vertical drive pulse come from pin 61 (VA OUT) of I200 and on the 100Hz A8 it comes from pin 31 of UQ01.

This is fed via K65 and RV02 to pin 23 of IE02. The vertical sawtooth waveforms are output from pins 1 and 2 of IE02 and fed to

pins 11 and 12 of I601 via RV04 and RV03. I601 (TDA8354) is the vertical output amplifier, it requires 2 supply voltages,

approximately 14V to pins 4 and 10 to operate the IC and approximately 48V to pin 7 for the flyback pulse generator. The outputs

are from pins 2 and 9 with the gain setting feedback resistors R602 and R603 connected to pin 5.

Pin 1 is the vertical guard which is connected to pin 9 of IE02 if a vertical failure is detected the vertical part of the sandcastle pulse

is removed and IE02 blanks the picture to prevent damage to the tube. Z615 samples the flyback pulse which is then clamped by

Z606 this generates the frame pulse used by the micro I001.

EAST WEST CORRECTION

The east west parabola is output from pin 3 of IE02 and fed to the gate of Q700 via RH04. The drain of Q700 is connected to the

centre of the diode modulator D706 and D707 via the east west injection coil L751.

HIGH END FEATURE BOX

LOW END FEATURE BOX

18

Page 20

MICROCONTROLLER SECTION ON THE A8/D8 CHASSIS

INTRODUCTION:

The main microcontroller on the A8/D8 chassis is located at I001 (ST92R195B). This is an 80-pin QFP (quad-flat package) that is

surface mounted for compactness. This highly complex device controls many of the other integrated circuits via dedicated

input/output lines or the I2C bus. This device also generates the RGB signals for the on-screen display (OSD) menus and the

teletext. The device can acquire, decode and display the teletext without the need for a separate IC. This microcontroller is ROMless which results in the need of a separate memory device to store the program code necessary for operating the television. This

memory device is located at I002 and is multi-time programmable (MTP). This allows the device to be re-programmed and in the

future can even be re-programmed in the board without having to remove the back cabinet of the TV. The television stores all the

necessary customer preferences and operating settings in an on-board EEPROM (E2). This device can hold 2Kb of information for

storing the programme information (frequency, name, AV setting, etc.), factory alignment settings (geometry, white balance, tuner

AFC/AGC, etc.), service diagnostic errors and customer control settings (volume, brightness, contrast, etc.). This device

communicates with the main microcontroller via the I2C bus, even in the standby mode.

MAIN MICROCONTROLLER (I001)

INTRODUCTION

The ST92R195B is an enhanced microcontroller based on the ST9+ instruction set from STMicroelectronics. It is capable of

displaying menus and teletext for 50Hz and 100Hz televisions. This device can acquire/decode and display pages of teletext

information in FLOF (FastText) and TOP (only in Germany/Switzerland/Austria) modes. The device operates from a single 4MHz

crystal and a +5V supply. Dedicated address/data lines enable it to access 4Mbytes of address space, even though in this television

it is accessing 128Kbytes (1Mbit). These address/data lines are connected to the EPROM/MTP device which holds the instructions

necessary for controlling the television.

DESCRIPTION

EXTERNAL MEMORY INTERFACE MMU ADDRESS LINES

• Pins 1 (MMU0), 15 (MMU1) and 16 (MMU2) are used to access addresses above 64Kbytes. Normally pins 15 and 16 are

not used when using a 128Kbyte EPROM/MTP device (MX26C1000APC) in position I002.

• Pin 2 (MMU3) is used to select between either the EPROM/MTP in position I002, or a future device that can be fitted in

position I003. When this line is low, the MX26C1000APC device in position I002 is enabled (chip enable).

• Pin 17 (MMU4) is used as an output port to derive a clock signal needed for shifting the data into the 74HC595 shift

register (I006).

• Pin 18 (MMU5) is not used.

EXTERNAL MEMORY INTERFACE CONTROL LINES

• Pin 4 is the Data strobe line which is connected to the output enable input of the EPROM/MTP (I002). When data is read

from the EPROM/MTP, this line is temporarily low.

• Pin 8 is the Read/Write line for I003. Normally, this line is not used (HIGH) but if an SRAM were to be fitted into this

position, the line could be low when writing data to the SRAM.

EXTERNAL MEMORY INTERFACE ADDRESS LINES

• Pins 3, 5, 6, 7, 13, 14 and 71 to 80 are the address lines needed to specify which location in a 64Kbyte page is needed to

be accessed from the EPROM/MTP (I002). These lines are also connected to I003 if an SRAM is to be fitted in future.

Normally these lines will be changing state (0V to approx. +5V). By placing an oscilloscope on pin 12 of the EPROM/MTP

(I002) it can be confirmed that the microcontroller is operating successfully. In this case, this line should be changing state

very frequently.

EXTERNAL MEMORY INTERFACE DATA LINES

• Pins 63 to 70 are the 8 data lines needed for receiving data from the EPROM/MTP (I002). If an SRAM were to be fitted in

position I003, then these lines would be used to transfer data from the microcontroller to the SRAM. Under normal

circumstances these lines change from LOW (0V) to HIGH (approx. +5V).

GROUND CONNECTIONS

• Pin 9 (GNDM) is the ground connection (0V) for the external memory interface. This should be free of noise to enable

successful communications between the microcontroller and the EPROM/MTP (or SRAM).

• Pin 35 (GND) is the digital ground connection (0V) for normal operation of the device.

• Pin 62 (GNDA) is the analogue ground connection for the DAC and phase lock loops (PLL’s).

SUPPLY CONNECTIONS

• Pin 10 (VDDM) is the +5V supply for the external memory interface. Without this supply, the microcontroller cannot

communicate with the EPROM/MTP (or SRAM).

• Pin 34 (VDD) is the main digital supply voltage to the IC (5V 10% tolerance).

• Pin 52 (VDDA) is the analogue supply voltage for the DAC’s and PLL’s (+5V). These connections are all joined together

to the +5V standby rail of the television, ensuring that the microcontroller operates even in the standby state.

19

Page 21

CRYSTAL OSCILLATOR CONNECTIONS

• Pin 11 is the 4MHz crystal oscillator input (OSCIN).

• Pin 12 is the 4MHz crystal oscillator output (OSCOUT). By connecting a x100 scope probe to pin 11, it can be seen if a

4MHz sine wave is present at the oscillator input to the microcontroller.

RESET CONNECTION

• Pin 54 is the active low RESET input of the microcontroller. This input is normally high (approx. +5V) under operating

conditions, but changes state when the standby +5V power supply is typically below +4.5V. In this circumstance, the reset

IC (I021) pulls pin 54 low until the input of it is above +4.5V. The diode (D001) ensures that the capacitor (C015)

discharges quickly when the standby supply falls, so that the reset operates quickly. The capacitor (C015) charges up

slowly when the standby +5V supply is restored, ensuring that there is some hysteresis.

INFRA-RED (IR) RECEIVER INPUT

• Pin 25 is the IR receiver’s filtered output. This input from the IR receiver consists of PWM pulses between 0V and +5V

which are decoded by the microcontroller into useful commands from the handset. When a valid command has been

decoded, the Red LED on the front of the TV will briefly flash.

HORIZONTAL AND VERTICAL SYNCHRONISATION CONNECTIONS

• Pin 48 is the vertical synchronisation input from the deflection stage. This input is used to ensure that the OSD is

displayed in a stable vertical position. When the TV is in the standby state, this input is normally low. The vertical input is

triggered on the rising edge (positive polarity).

• Pin 9 is the horizontal synchronisation input from the deflection stage. This input ensures that the OSD is displayed in

stable horizontal position. When the TV is in the standby state, this input is normally low. This input is rising edge

triggered (positive polarity).

GENERAL INPUT CONNECTIONS

HEADPHONE INPUT

• Pin 19 is used to detect if the headphone has been inserted into its socket. This input is normally HIGH (+5V) unless the

headphone has been inserted, in which case it is near 0V. When the headphone is inserted, the headphone mode option

is then available in the "Sound Mode" Menu and the loudspeakers (and internal sub-woofer if available) in the television

are muted.

PROTECTION INPUT

• Pin 26 is used to determine if a protection fault has occurred on the chassis. This line is connected to the comparator

outputs 1, 13 and 14 of I903 in the power supply. This line is normally high (approx. +5V) unless a fault has occurred, in

which case it is near ground potential (0V).

• Comparator output 1 monitors the +16V audio supply rail for over-current. If this rail is shorted, or draws too much current,

then the comparator output (pin 1 of I903) will change state to 0V.

• Comparator output 13 monitors the EHT voltage generated by the FBT in the deflection circuit. If this voltage is too high,

then this output will be low to indicate that there is a problem with the deflection.

• Comparator output 14 is connected to the secondary side of the deflection’s line input transformer. It is primarily used to

indicate whether too much current is being drawn from the line-input transformer and FBT.

POWER-GOOD INPUT

• Pin 27 is used to indicate if the power has been removed from the TV or whether a static discharge has occurred. This

input is interrupt driven to react instantaneously to a falling edge (+5V -> 0V). Under this circumstance, the audio power

amplifiers are muted and the television begins to power-down into standby. This input is derived from the comparator

output (pin 2 of I903) in the power supply. This comparator provides an "early warning" indication that the primary supply