HIT HN58X24128FPI, HN58X24128TI, HN58X24256FPI Datasheet

HN58X24128I/HN58X24256I

Two-wire serial interface

128k EEPROM (16-kword × 8-bit)

256k EEPROM (32-kword × 8-bit)

ADE-203-1029B (Z)

Rev. 2.0

Nov. 26, 1999

Description

HN58X24xxx series are two-wire serial interface EEPROM (Electrically Erasable and Programmable

ROM). They realize high speed, low power consumption and a high level of reliability by employing

advanced MNOS memory technology and CMOS process and low voltage circuitry technology. They also

have a 64-byte page programming function to make their write operation faster.

Note: Hitachi’s serial EEPROM are authorized for using consumer applications such as cellular phone,

camcorders, audio equipment. Therefore, please contact Hitachi’s sales office before using

industrial applications such as automotive systems, embedded controllers, and meters.

Features

• Single supply: 1.8 V to 5.5 V

• Two-wire serial interface (I2CTM serial bus*1)

• Clock frequency: 400 kHz

• Power dissipation:

Standby: 3 µA (max)

Active (Read): 1 mA (max)

Active (Write): 5 mA (max)

• Automatic page write: 64-byte/page

• Write cycle time: 10 ms (2.7 V to 5.5 V)/15 ms (1.8 V to 2.7 V)

• Endurance: 105 Cycles (Page write mode)

• Data retention: 10 Years

HN58X24128I/HN58X24256I

• Small size packages: SOP-8pin, TSSOP-14pin

• Shipping tape and reel

TSSOP 14-pin: 2,000 IC/reel

SOP 8-pin: 2,500 IC/reel

• Temperature range: –40 to +85°C

Note: 1. I2C is a trademark of Philips Corporation.

Ordering Information

Type No. Internal organization Operating voltage Frequency Package

HN58X24128FPI 128k bit

(16384 × 8-bit)

HN58X24256FPI 256k bit

(32768 × 8-bit)

HN58X24128TI 128k bit

(16384 × 8-bit)

HN58X24256TI 256k bit

(32768 × 8-bit)

1.8 V to 5.5 V 400 kHz 150 mil 8-pin plastic SOP

(FP-8DB)

1.8 V to 5.5 V 400 kHz 14-pin plastic TSSOP

(TTP-14D)

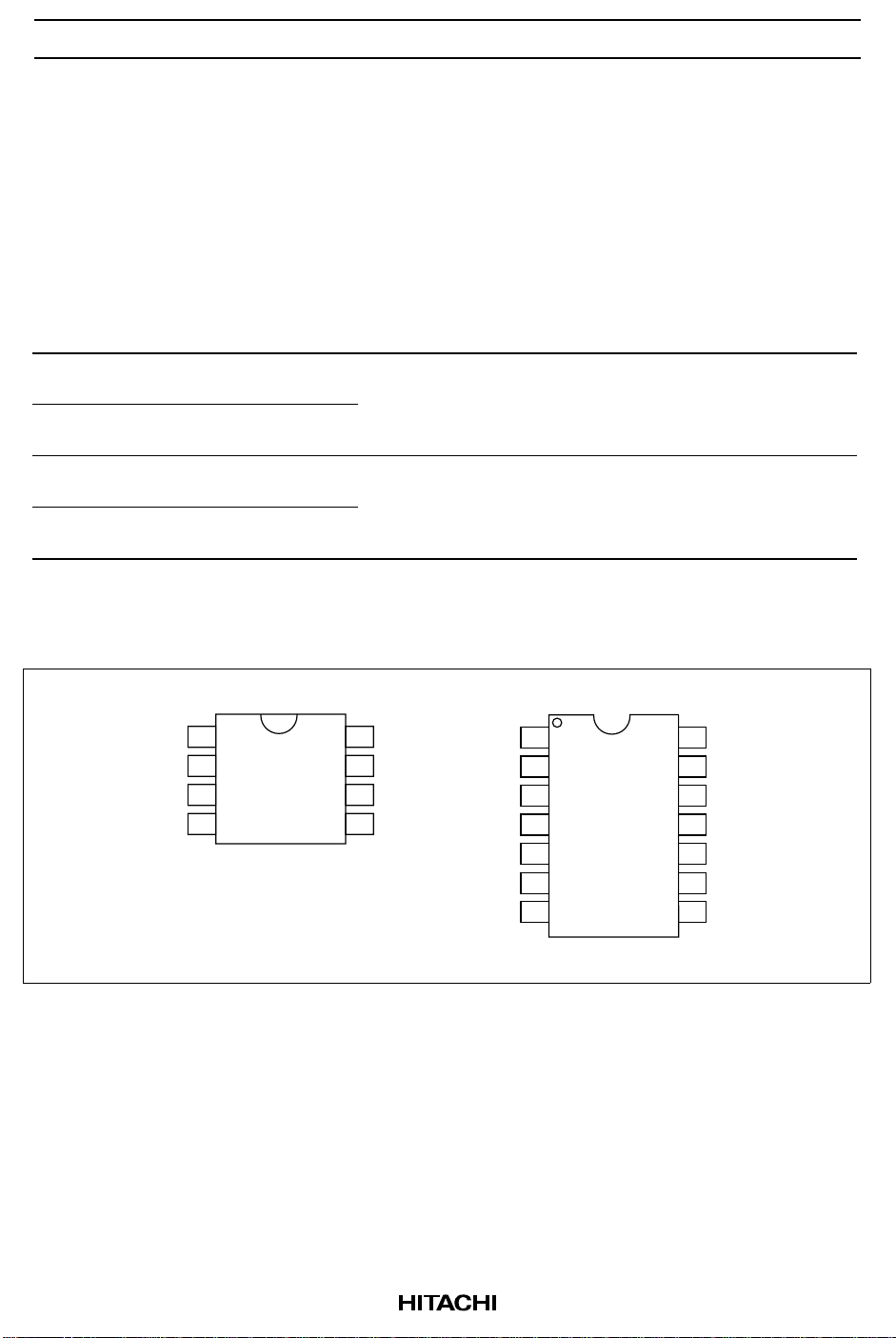

Pin Arrangement

A0

A1

A2

V

SS

8-pin SOP

1

2

3

4

(Top view)

14-pin TSSOP

1

2

3

4

5

6

7

(Top view)

14

13

12

11

10

9

8

V

CC

WP

NC

NC

NC

SCL

SDA

NC

NC

NC

V

A0

A1

A2

SS

8

7

6

5

V

CC

WP

SCL

SDA

2

Pin Description

Pin name Function

A0 to A2 Device address

SCL Serial clock input

SDA Serial data input/output

WP Write protect

V

CC

V

SS

Power supply

Ground

NC No connection

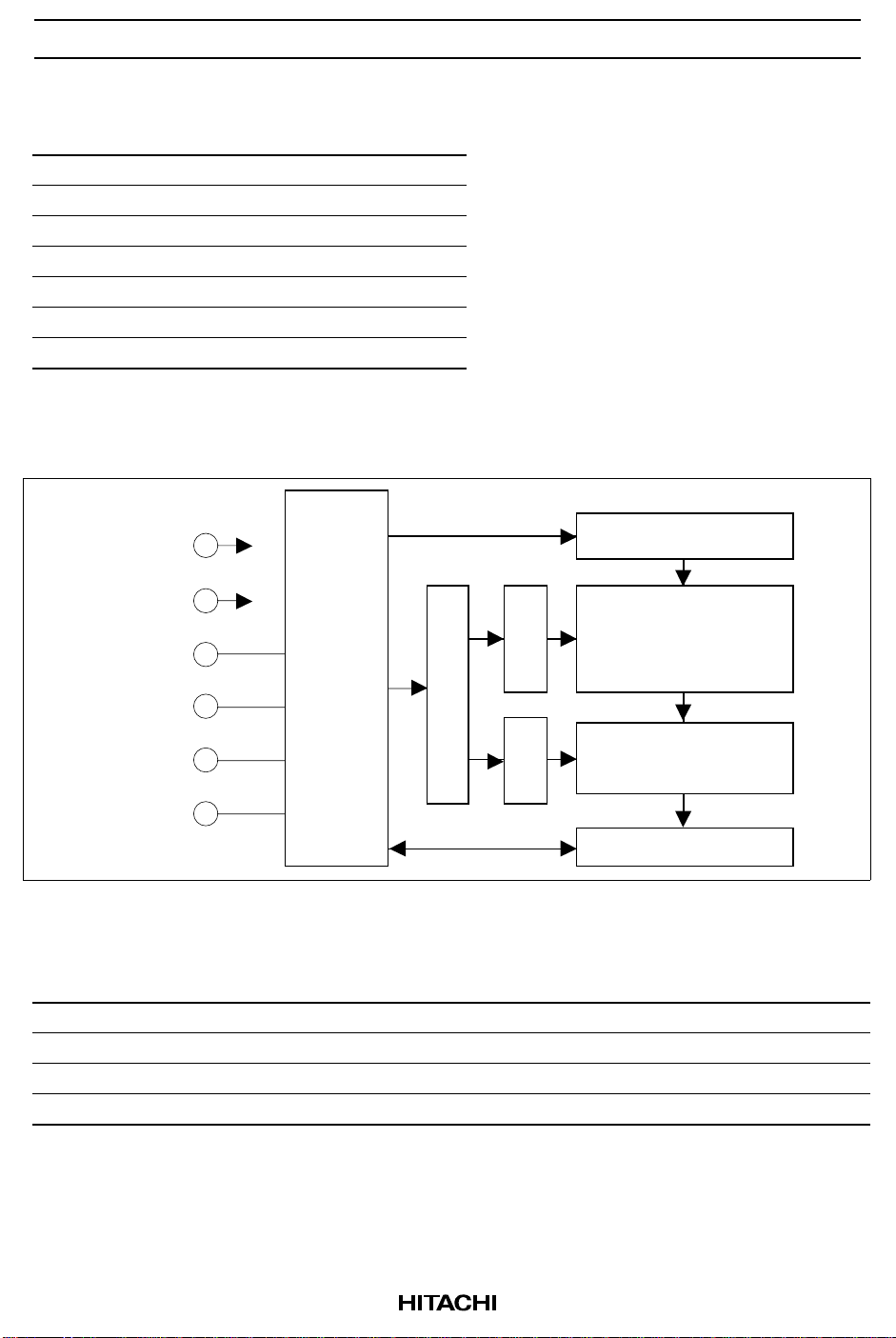

Block Diagram

HN58X24128I/HN58X24256I

V

CC

V

SS

High voltage generator

Memory array

WP

Control

logic

X decoderY decoder

A0, A1, A2

SCL

Address generator

Y-select & Sense amp.

SDA

Serial-parallel converter

Absolute Maximum Ratings

Parameter Symbol Value Unit

Supply voltage relative to V

Input voltage relative to V

SS

SS

Operating temperature range*

1

V

CC

Vin –0.5*2 to +7.0*

Topr –40 to +85 ˚C

Storage temperature range Tstg –65 to +125 ˚C

Notes: 1. Including electrical characteristics and data retention.

2. Vin (min): –3.0 V for pulse width ≤ 50 ns.

3. Should not exceed V

+ 1.0 V.

CC

–0.6 to +7.0 V

3

V

3

HN58X24128I/HN58X24256I

DC Operating Conditions

Parameter Symbol Min Typ Max Unit

Supply voltage V

Input high voltage V

Input low voltage V

CC

V

SS

IH

IL

Operating temperature Topr –40 — 85 ˚C

Notes: 1. VIL (min): –1.0 V for pulse width ≤ 50 ns.

DC Characteristics (Ta = –40 to +85˚C, VCC = 1.8 V to 5.5 V)

Parameter Symbol Min Typ Max Unit Test conditions

Input leakage current I

Output leakage current I

Standby VCC current I

Read VCC current I

Write VCC current I

Output low voltage V

LI

LO

SB

CC1

CC2

OL2

V

OL1

— — 2.0 µAVCC = 5.5 V, Vin = 0 to 5.5 V

— — 2.0 µAVCC = 5.5 V, Vout = 0 to 5.5 V

— 1.0 3.0 µA Vin = VSS or V

— — 1.0 mA VCC = 5.5 V, Read at 400 kHz

— — 5.0 mA VCC = 5.5 V, Write at 400 kHz

— — 0.4 V VCC = 4.5 to 5.5 V, IOL = 1.6 mA

— — 0.2 V VCC = 1.8 to 2.7 V, IOL = 0.2 mA

1.8 — 5.5 V

000V

VCC × 0.7 — VCC + 1.0 V

1

–0.3*

—V

V

= 2.7 to 4.5 V, IOL = 0.8 mA

CC

V

= 1.8 to 2.7 V, IOL = 0.4 mA

CC

× 0.3 V

CC

CC

Capacitance (Ta = 25˚C, f = 1 MHz)

Parameter Symbol Min Typ Max Unit

1

Input capacitance (A0 to A2, SCL, WP) Cin*

Output capacitance (SDA) C

I/O

Note: 1. This parameter is sampled and not 100% tested.

4

— — 6.0 pF Vin = 0 V

1

*

— — 6.0 pF Vout = 0 V

Test

conditions

HN58X24128I/HN58X24256I

AC Characteristics (Ta = –40 to +85˚C, VCC = 1.8 to 5.5 V)

Test Conditions

• Input pules levels:

VIL = 0.2 × V

VIH = 0.8 × V

• Input rise and fall time: ≤ 20 ns

• Input and output timing reference levels: 0.5 × V

• Output load: TTL Gate + 100 pF

Parameter Symbol Min Typ Max Unit Notes

Clock frequency f

Clock pulse width low t

Clock pulse width high t

Noise suppression time t

Access time t

Bus free time for next mode t

Start hold time t

Start setup time t

Data in hold time t

Data in setup time t

Input rise time t

Input fall time t

Stop setup time t

Data out hold time t

Write cycle time VCC = 2.7 V to 5.5 V t

Notes: 1. This parameter is sampled and not 100% tested.

2. t

WC

CC

CC

CC

— — 400 kHz

1200 — — ns

600 — — ns

— — 50 ns 1

100 — 900 ns

1200 — — ns

600 — — ns

600 — — ns

0——ns

100 — — ns

— — 300 ns 1

— — 300 ns 1

600 — — ns

50 — — ns

— — 10 ms 2

— — 15 ms 2

VCC = 1.8 V to 2.7 V t

SCL

LOW

HIGH

I

AA

BUF

HD.STA

SU.STA

HD.DAT

SU.DAT

R

F

SU.STO

DH

WC

WC

is the time from a stop condition to the end of internally controlled write cycle.

5

HN58X24128I/HN58X24256I

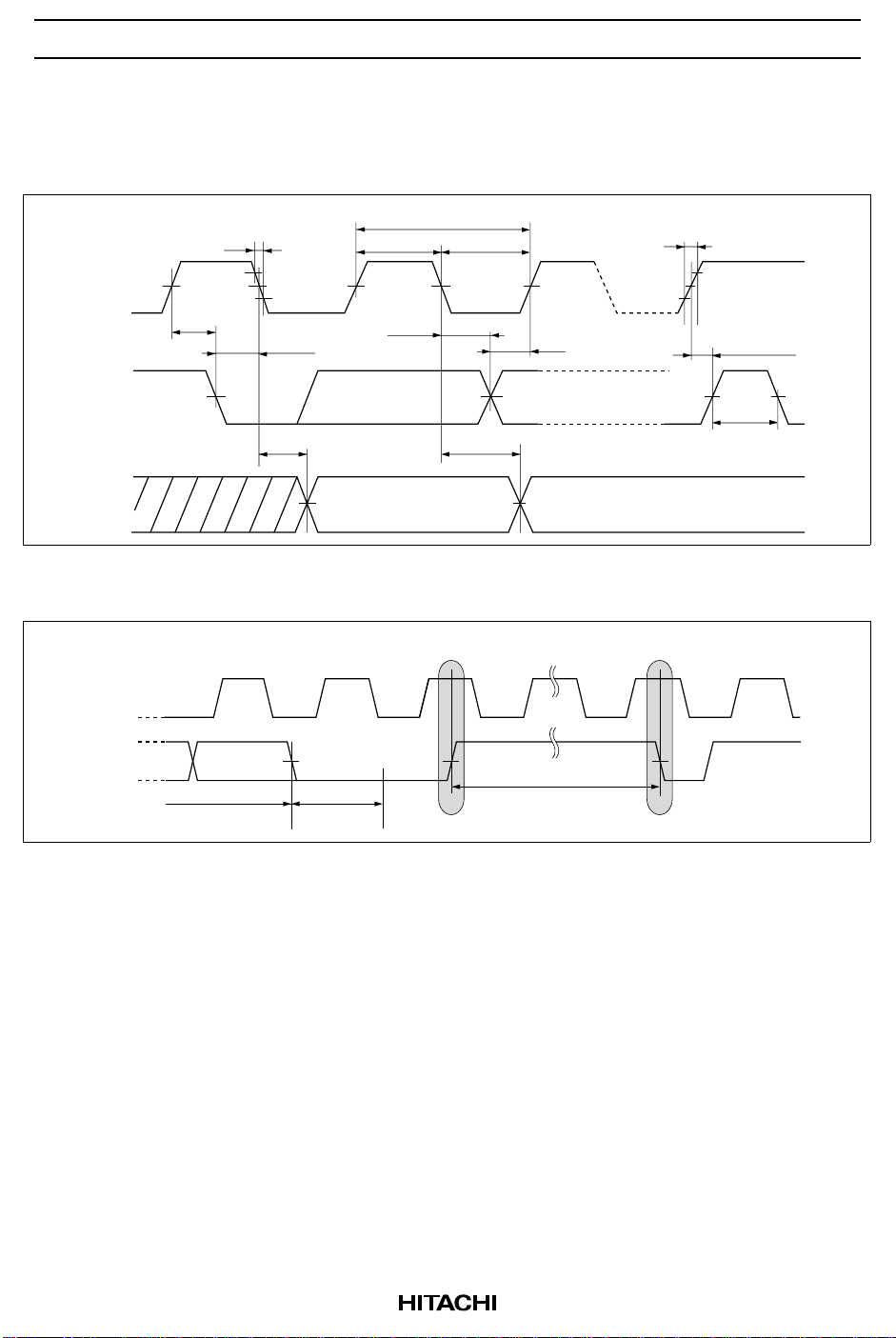

Timing Waveforms

Bus Timing

t

F

SCL

t

SU.STA

t

HD.STA

t

HIGH

t

HD.DAT

1/f

SCL

t

LOW

t

SU.DAT

t

R

t

SU.STO

SDA

(in)

SDA

(out)

Write Cycle Timing

SCL

SDA

(Address (n))

t

AA

D0 in

Write data ACK

t

DH

Stop condition Start condition

t

WC

(Internally controlled)

t

BUF

6

HN58X24128I/HN58X24256I

Pin Function

Serial Clock (SCL)

The SCL pin is used to control serial input/output data timing. The SCL input is used to positive edge

clock data into EEPROM device and negative edge clock data out of each device. Maximum clock rate is

400 kHz.

Serial Input/Output Data (SDA)

The SDA pin is bidirectional for serial data transfer. The SDA pin needs to be pulled up by resistor as that

pin is open-drain driven structure. Use proper resistor value for your system by considering VOL, IOL and

the SDA pin capacitance. Except for a start condition and a stop condition which will be discussed later,

the SDA transition needs to be completed during SCL low period.

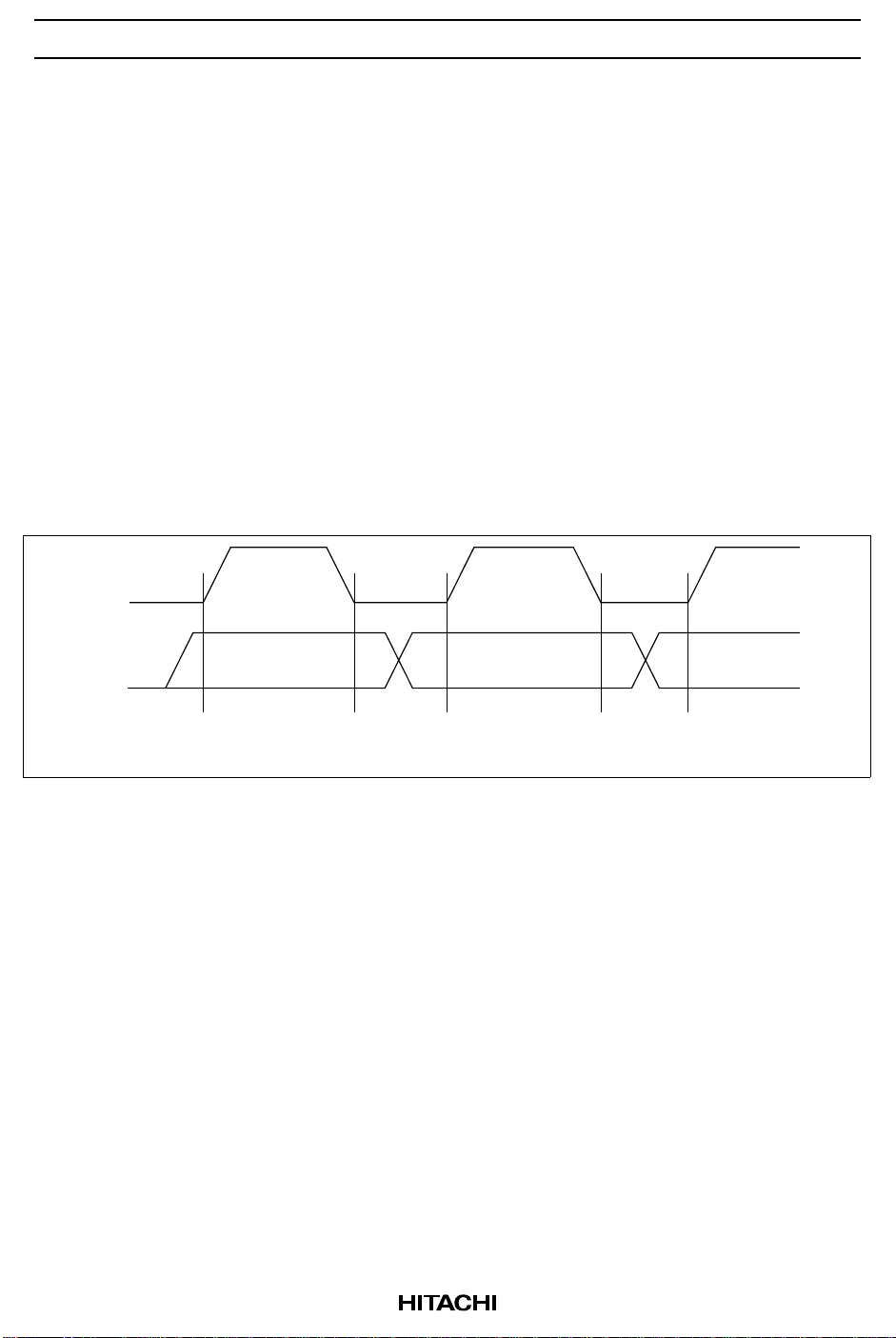

Data Validity (SDA data change timing waveform)

SCL

SDA

Data

change

Note: High-to-low and low-to-high change of SDA should be done during SCL low periods.

Data

change

7

Loading...

Loading...