Page 1

- GDVX580

- GDVX580

GDVX580

Service Manual

Service Manual

Page 2

CONTENTS :

1.INFORMATIONS……………………………………………………………………………….3

Vibratto-II DVD Processor (ESS 66x8)

2. OPERATING INSTRUCTIONS……………………………………………………………..14

3. PRODUCT SPECIFICATIONS……………………………………………………………...24

4. TROUBLESHOOTING……………………………………………………………………….25

5. MAINTENANCE INSTRUCTIONS……………………………………………………..…..26

6. ELECTRICAL PART LIST…………………………………………………………………..35

7. DISASSEMBLY AND REASSEMBLY……………………………………………………..43

8. CIRCUIT DIAGRAMS………………………………………………………………………..44

9. WIRING DIAGRAM…………………………………………………………………………..49

2

Page 3

1. INFORMATIONS

Vibratto-II DVD Processor (ESS 66x8)

Vibratto-II DVD Processor

FEATURES:

Single-chip DVD processoe incorporating all front-end and back-end functions

Unified memory architecture

Proven focusing, sledding, tracking, and CLV/CAV spindke servo control

Proven ESS, EFM,?EFM+ demodulation, and EDC circuit

Built-in ADCs and DACs for servo control signals

Direct interface to ES6603 servo AFE chip

Integrated NTSC/PAL encode with pixel-adaptive de-interlacer and five 10-bit 54MHz video DACs

DVD-video, DVD-VR, VCD1.1 and 2.0, and SVCD

DivX and MPEG-4 Advanced Simple profile at full screen(D1)

Full DVD-audio support including MLP and LPCM decode, CPPM decryption, and watermark

detection

Media playback with CD-ROM, CD-R/RW, DVD-R/RW, and DVD+R/RW

Up to 7.1 channel audio outputs

Direct interface of 16 bit DRAM up to 128Mb capacity

Direct interface for up to 4 banks of 8-bit EPROM or FLASH EPROM for up to 4MB per bank

Macrovision 7.1 for NTSC/PAL (480p/576p) progressie scan video

Simultaneous composite,S-video and YUV output

CCIR656/601 yuv 4:2:2 output

OSD controller supports 256 colors in 8 degrees of transparency

Subpicture Unit(SPU) decoder supports karaoke iyric,subtitles,and EIA-608 compliant Line 21

Captioning.

SmartBrght™ for clear and bright movie presentation.

SmartColor™ for vivid flesh-tone image display.

SmartLogo™ for custom JPEG wallpaper.

JPEG digital photo CD support (Kodak Picture CD™ and Fujifilm FujiColor CD™.

ESS Music Slideshor™.

Bass management.

Dolby Digital(AC-3),Dolby ProLogic™,and ProLogicll.

DTS™surround(ES6698D only).

S/PDIF digital audio input and output.

MPEG AAC and Multichannel.

SRS TruSurround

Professional karaoke with full scoring scheme.

3

Page 4

Functional Description:

The internal block digram for ESS 6698

4

Page 5

Pinout Diagram

5

Page 6

ES6698 PIN DEXCRIPTION

Names Pin Numbers I/P Definitions

VD33

1.10.19.35.44.53.6

2.79.96.126.185.

P I/O power supply.

VID_XI 2 I Crystal input.

VID_XO 3 O Crystal output.

VID_XO 3 O Crystal output.

CLK 4 I System clock.

DMA[11:0] 5:8 11:17 20 O DRAM address bus.

9.18.34.43.52.61.7

VX33

95.119.127.186.20

8.

G Ground for I/O power supply.

8

DCAS# 21 O DRAM column address strobe (active-low).

DCS[1:0]# 22.23 O DRAM chip select (active-low).

DRAS[2:0]# 24.25.28 O DRAM row address strobe (active-low).

VSS 26.70.86.137.197 G Ground for core power supply.

VDD 27.71.87.138.198 P Core power supply.

DSCK_EN O DRAM clock enable output .

DOE#

29

O DRAM output enable(active-low).

DWE# 30 O DRAM write enable(active-low).

DB[15:0] 31:33,36:42,45:50 I/O DRAM data bus.

DSCK 51 O Output clock to DRAM.

DQM 54 O Data input/output mask.

LA[21:0]

55:60,63:69,72:77

80:82

O RISC port address bus .

LCS[3:0]# 83:85 88 O RISC port chip select (active-low).

LWRLL# 89 O RISC port low-byte write enable(active-low).

LOE# 90 O RISC port output enable (active-low).

LD[7:0] 91:94,97:100 I/O RISC port data bus; (5V tolerant input).

RSD 101 I Audio receive serial data; (5V tolerant input ).

RBCK 102 I Audio receive bit clock; (5V tolerant input ).

RWS 103 I Audio receive frame sync; (5V tolerant input ).

VD33_PL 104 P Power for PLL blocks.

VS33_PL 105 G Ground for PLL blocks.

VREF I Internal voltage reference to video DAC.

YUV1

COMP I Compensation input .

YUV3

RSET I DAC current adjustment resistor input .

YUV4

FDAC

106

107

108

109

O YUV pixel 1 output data .

O YUV pixel 3 output data .

O YUV pixel 4 output data.

Video DAC output. Refer to description and matrix for

O

UDAC pin 115.

6

Page 7

YUV7 O YUV pixel 7 output data .

VDAC

110

YUV6

Video DAC output . Refer to description and matrix for

O

UDAC pin 115.

O YUV pixel 6 output data.

Names Pin Numbers I/P Definitions

VD33_DA 111 P Power for I/O power supply for VDAC.

VS33-DA 112 G Ground for I/O power supply for VDAC.

YDAC

113

YUV5

CDAC

114

YUV2

Video DAC output. Refer to description and matrix for

O

UDAC pin 115.

O YUV pixel 5 output data.

Video DAC output. Refer to description and matrix for

O

UDAC pin 115.

O YUV pixel 2 output data .

Video DAC output.

Pin 109 110 113 114 115

Valu

e

0

1

2

3

4

5

UDAC O

6

7 N/A

8

9 CVBS

10 CVBS

11 N/A

12

13

FDAC VDAC YDAC CDAC UDAC

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS/Chrom

a

CVBS

1

CVBS

1

Y C N/A

Y C

N/A Y C N/A

CVBS

1

CVBS

1

CVBS

1

N/A N/A

N/A N/A N/A

Y Pb Pr

N/A Y Pb Pr

SYNC

Chrom

a

CVBS

1

CVBS

1

SYNC

G B R

Y Pb Pr

G B R

G R B

G R B

N/A Y Pr Pb

CVBS

1

Y Pr Pb

14 Chroma Y G R B

F: VCBS/chroma signal for simultaneous mode.

Y: Luma component for YUV and Y/C processing.

CVBS2

CVBS2

7

Page 8

C: Chrominance signal for Y/C processing.

U: Chrominance component signal for YUV mode.

V: Chrominance component signal for YUV mode.

TWS 116 O Audio transmit frame sync output.

8

Page 9

Names Pin Numbers I/P Definitions

System and DSCK output clock frequency selection is

made at the rising edge of RESET#. The matrix below

lists the available clock frequencies and their respective

PLL bit settings. Strapped to VCC or ground via 4.7-KΩ

resistor; read only during reset.

SEL_PLL2 SEL_PLL1 SEL_PLL0 Clock

0 0 0 CLK*4.5

SEL_PLL2 I

0 0 1 CLK*5.0

0 1 0 Bypass

0 1 1 CLK*4.0

1 0 0 CLK*4.25

1 0 1 CLK*4.75

1 1 0 CLK*5.5

1 1 1 CLK*6.0

Type(MHz)

TSD0 O Audio transmit serial data port 0.

SEL_PLL0

117

I Refer to the description and matrix for SEL_Pll2 pin 116.

TSD1 O Audio transmit serial data port 1.

SEL_PLL1

118

Refer to the description and matrix for SEL_PLL2 pin

I

116.

TSD[2:3] 120.121 O Audio transmit serial data ports 2 and 3.

MCLK 122 I/O Audio master clock for audio DAC.

TBCK 123 O Audio transmit bit clock.

SPD_DOBM O S/PDIF output .

SEL_PLL3

124

Clock source select. Strapped to VCC or ground via 4.7K

read only during reset .

Ω

I

SEL_PLL3 Clock Source

0 Crystal oscillator

1 CLK input

SPDIF_IN 125 I S/PDIF input; (5V tolerant input).

WBLCLK

128 O

DVD-RAM wobble detector circuit clock source to

preamp.

WBL 129 O DVD-RAM wobble output.

LG 130 O DVD-RAM land/groove flag.

IP2 131 I DVD-RAM header position index 2.

IP1 132 I DVD-RAM header position index 1.

FLAG[3:0] 133:136 O To monitor servo status .

TEXI 139 I High-speed tracking error input .

TESTAD 140 I Test AD input .

SBAD 141 I Sub-beam addition input signal .

FEI 142 I Focus input error signal.

AVSS_AD 143 G Analog ground for ADC block .

9

Page 10

CEI 144 I Center error input signal .

TEI 145 I Tracking error input signal .

RFRP 146 I RF ripple/envelope input signal.

AVDD3_AD 147 P Analog power supply for ADC block.

VREF21 148 O 2.1V reference voltage.

VREF09 149 O 0.9Vreference voltage.

VREF15 150 O 1.5V reference voltage.

Names Pin Numbers I/P Definitions

IREF

151 I

Servo data PLL interface reference current generator

connect a resistor between this pin and ground to set

reference current .

AVDD3_DS 152 P Analog power supply for data slicer .block.

IPIN 153 I Inverting input of data slicer .

RFIN

RFIP

154 I

155 I

Analog RF signal input after passing through

equalizer(minus)

Analog RF signal input after passing through

equalizer(plus).

DSSLV 156 O Data slicer level output.

AVSS_DS 157 G Analog ground for data slicer block.

AVSS_PL 158 G Analog ground for data PLL block.

PDOFTR1 159 O Servo data PLL phase detector filter pin number 1.

FDO

160 O

Servo data PLL output node of frequency detector

charge pump.

FTROPI 161 I Servo data PLL input node of loop filter OP circuit .

AVDD3_OL 162 P Analog power supply for data PLL block .

PLLFTR1 163 I Servo data PLL loop filter pin number1.

PLLFTR2 164 I Servo data PLL loop filter pin number2.

VREF0 165 O Servo data PLL reference voltage output.

AWRC 166 I/O Auto wide range control VCO signal from/to AWRC DAC.

AVSS_DA 167 G Analog ground for DAC part.

RFRPCTR 168 I/O Central level of RFRP.

TRAY 169 O Output voltage level for tray buffer IC.

AVDD3_DA 170 P Analog power supply for DAC part .

SPINDLE 171 O Output voltage level for spindle buffer IC.

FOCUS 172 O Output voltage level for focus buffer IC.

SLEGP 173 O Output voltage level for Sledge buffer IC(plus).

SLEGN 174 O Output voltage level for Sledge buffer IC(minus).

TRACK 175 O Output voltage level for tracking buffer IC.

TESTDA 176 O Test DA output .

FGIN 177 I Spindle hall sensor input .

PHOI 178 I Sledge photo interrupt signal input.

SCSJ 179 O Chip selection signal to RF chip (serial data enable).

SDATA 180 I/O Data signal from/to RF chip.

SCLK 181 O Serial clock source to RF chip.

DFCT 182 I Defect flag input signal.

10

Page 11

LDC 183 O Laser diode on/off control output.

SPDON 184 O Spindle power driver on/off control output.

GPIO[9:4]

187:192 I/O

General-purpose input/output used for servo control;

(5V tolerant input.)

EAUX[3:0] 193:196 I/O Extended auxiliary ports;(5V tolerant input).

I²CDATA

AUX0

I²C_CLK

AUX1

199

200

I/O

I/O Auxiliary port (open collector);(5V tolerant input).

I/O

I/O Auxiliary port (open collector);(5V tolerant input).

I²C data I/O;(5V tolerant input).

I²C clock I/O;(5V tolerant input).

IOW# O I/O Write strobe(LCS1)(active-low).

HSYNC# I/O Horizontal sync (active low);(5V tolerant input).

AUX2

201

I/O

Auxiliary port ;(5V tolerant input).

Names Pin Numbers I/P Definitions

IOR# O I/O Read strobe (LCS1)(active –low).

VSYNC# I/O Vertical sync (active-low);(5V tolerant input ).

AUX3

C2PO I Error correction flag from CD;(5V tolerant input).

AUX4

202

203

I/O Auxiliary port;(5V tolerant input).

I/O Auxiliary port;(5V tolerant input).

AUX[5:6] 204:205 I/O Auxiliary ports ;(5V tolerant input).

IR I Infrared remote control input;(5V tolerant input).

AUX7

206

I/O Auxiliary port;(5V tolerant input ).

RESET# 207 I Reset input (active –low );(5V tolerant input).

101 I Audio receive serial data input[RSD];(5V tolerant input).

102 I Audio receive bit clock input [RBCK]:(5V tolerant input ).

103 I Audio receive frame sync input[RWS];(5V tolerant input).

116 O Audio transmit frame sync output[TWS].

Audio Port

Interface

117.118.120.121 O Audio transmit serial data outputs [TSD[3:0]].

122 I/O Audio DAC master clock[MCLK].

123 O Audio transmit bit clock output[TBCK].

124 O Sony/Philips Digital Interface audio output [SPD_DOBM].

125 I

Sony/Philips Digital Interface audio Input [SPDIF_IN];(5V tolerant input).

Auxiliary Port

Interface

Clock Inetface

and Reset

Interface

193:196 I/O Extended auxiliary ports [EAUX[3:0]];(5V tolerant input).

199.200 I/O Open collectors [AUX[1:0]],(5V tolerant input).

201:206 I/O Primary auxiliary port I/Os [AUX[7:2]];(5V tolerant input).

2 I 27-MHz crystal clock input [VID_XI].

3 O 27-MHz crystal clock output[VID_XO].

4 I System clock [CLK].

29 O DRAM clock enable output [DSCK_EN].

51 O Output clock [DSCK] to video memory (DRAM).

116:118 I Clock frequency select PLL outputs [SEL_PLL[2:0]].

207 I Reset input (active-low)[RESET#];(5V tolerant input).

106:110.113:115 O Pixel data outputs [YUV[7:0]]. Display

201 I/O Horizontal sync[HSYNC#];(%V tolerant input).

11

Page 12

202 I/O Vertical sync [VSYNC#];(5V tolerant input ).

EPROM/Flas

h ROM and

RISC Port

Intetface

55:60.63:69.72:77.

80:82

83:85 O

89 O

90 O

91:94.97:100 I/O

RISC port address bus [LA[21:0]]to EPROM or Flash

O

memory.

RISC port chip select outputs [LCS[2:0]#]to EPROM or

Flash memory.

RISC port low-byte write enable output[LWRLL#]to

EPROM or Flash memory.

RISC port output enable[LOE#]to EPROM and Flash

memory.

RISC port data bus [LD[7:0]]to EPROM or Flash memory

(5V tolerant input ).

106 I Video DAC reference voltage input[VREF]. Filter and

Reference

voltang

107 I Compensation input[COMP].

Interface

Front Panel

Display

206 I Infrared remote control input [IR];(5V tolerant input).

Interface

Names Pin Numbers I/P Definitions

General-Purp

ose

I²C Bus

Interface

187:192 I/O

199 I/O

200 I/O

1.10.19.35.44.53.6

2.79.96.126.185

9.18.34.43.52.61.7

8.95.119.127.186.

General –purpose I/O[GPIO[9:4]];(5V tolerant input).

I²C data I/O[12C_DATA];(5V tolerant input).

I²C clock I/O[12C_CLK];(5V tolerant input).

I/O power supply [VD33].

P

I/O ground [VS33].

G

208

26.70.86.137.197 G Ground for core power [VSS].

27.71.87.138.198 P Core power supply [VDD].

104 P Power supply for PLL block .[VD33_PL].

Power and

Ground

105 G Ground for PLL block [VS33_PL].

111 P Power supply for video DAC[VD33_DA].

112 G Ground for video DAC[VS33_DA].

143 G Analog ground for ADC[AVSS_AD].

147 P Analog power supply for ADC[AVDD3_AD].

152 P Analog power supply for data slicer [AVDD3_DS].

157 G Analog ground for data slicer[AVSS_DS].

158 G Analog ground for data PLL [AVSS_PL].

162 P Analog power supply for data PLL[AVDD3_PL].

167 G Analog ground for DAC[AVSS_DA].

170 P Analog power supply for DAC[AVDD3_DA].

Serial Port

Interface 203 I

C2PO error correction flag from CD[C2PO];(5V tolerant

input).

12

Page 13

Servo Data

Slicer

Interface

153 I

154

Inverting input of data slicer [IPIN].

Analog RF signal input after passing through

I

equalizer(minus) [RFIN].

Analog RF signal input after passing through

155 I

equalizer(plus) [RFIP].

156 O

Data slicer level output[DSSLV].

13

Page 14

2.OPERATING INSTRUCTIONS

.

A

A

A

V

1. GENERAL SETUP

Pressing the SETUP button on remote control during STOP or PLAY mode to SETUP MENU.

sing Cursor to select GENERAL SETUP. Press ENTER to enter GENERAL SETUP page.

SETUP MENU - MAIN PAGE

GENERAL SETUP

SPEAKER SETUP

AUDIO SETUP

PREFERENCE

EXIT SETUP

a.TV DISPLAY

-- GENERAL PAGE --

TV DISPLAY NORMAL P/S

PIC MODE NORMAL L/B

ANGLE MARK W IDE

OSD LANG

CAPTIONS

SCR SAVER

MA IN P A G E

b. PIC MODE (PICTURE MODE)

( FOR PROGRESSIVE-SCAN MODEL )

-- GENERAL PAGE --

TV DISPLAY

PIC MODE AUTO

ANGLE MARK HI-RES

OSD LANG NON-FLICKER

CAPTIONS

SCR SAVER

MA IN P A G E

-- GENERAL PAGE --

TV DISPLAY

PIC MODE

NGLE MARK

OSD LANG

CAPTIONS

SCR SAVER

MA IN P A G E

Using cursor to move to desired setting and

press ENTER to confirm.

NORMAL/PS – 4 x 3 Pan Scan

Full screen of picture on TV. Normally, left and

right edges cannot be shown.

NORMAL/LB – 4 x 3 Letter Box

Orginal ratio of aspect.

WIDE – 16 : 9 Widescreen

-- GENERAL PAGE --

TV DISPLAY

PIC MODE

NGLE MARK FILM

OSD LANG

CAPTIONS SMART

SCR SAVER SUPER SMART

MA IN P A G E

UTO

IDE O

14

Page 15

c.ANGLE MARK

-- GENERAL PAGE --

TV DISPLY

PIC MODE

ANGLE MAR K ON

OSD LANG OFF

CAPTIONS

SCR SAVER

MA IN P A G E

This feature is functioned only for the disc,

which has ANGLE function:

When the ANGLE MARK is set ON, the screen displays the mark.

When the ANGLE MARK is set OFF, the mark is not displayed.

d. OSD LANG (ON SCREEN DISPLAY LANGUAGE)

-- GENERAL PAGE --

TV DISPLAY

PIC MODE

ANGLE M ARK

OSD LANG ENGLISH

CA P T ION S IT A L IA N

SCR SAVER

MA IN P A G E

e. CAPTIONS

-- GENERAL PAGE --

TV DISPLAY

PIC MODE

ANGLE M ARK

OSD LANG

CAPTIONS ON

SCR SAVER OFF

MA IN P A G E

f. SCR SAVER

-- GENERAL PAGE --

When the unit is stopped, no operation, no function button is

TV DISPLAY

PIC MODE

ANGLE M ARK

OSD LANG

CAPTIONS ON

SCR SAVER OFF

MA IN P A G E

pressed in 1 minute,screen saver appears for the purpose to

protect the TV screen if SCR SAVER is set ON.

15

Page 16

2.SPEAKER SETUP

SETUP MENU - MAIN PAGE

GENERAL SETUP

SPEAKER SETUP

AUDIO SETUP

PREFERENCE

EXIT SETUP

a. DOWNMIX

-- SPEAKER SETUP PAGE --

DOWNMIX LT/RT

CENTER STEREO

REAR OFF

OFF : Turn off the Downmix mode. 5.1 channels can be preformed only if

SUBWOOFER

CNTR DELAY

REAR DELAY

TEST TONE

LT/RT : Left and Right output mode

STEREO : Stereo output mode

Downmix is set OFF and the rest of other setup can be activated.

MA IN P A G E

b. CENTER c. REAR

-- SPEAKER SETUP PAGE --

DOWNMIX

CENTER ON

REAR OFF

SUBWOOFER

CNTR DELAY

REAR DELAY

TEST TONE

-- SPEAKER SETUP PAGE --

DOWNMIX

CENTER

REAR ON

SUBWOOFER OFF

CNTR DELAY

REAR DELAY

TEST TONE

MA IN P A GE

MAIN PAGE

d. SUBWOOFER

-- SPEAKER SETUP PAGE --

DOWNM IX

CENTER

REAR

SUBWOOFER ON

CNTR DELAY OFF

REAR DELAY

TEST TONE

M A IN P A G E

16

Page 17

e. CNTR DELAY f. REAR DELAY

Adjust the audio delay from center Adjust the audio delay from center

channel from 0 to 5MS. channel rom 0 to 15MS.

-- SPEAKER SETUP PAGE --

DOWNM IX

CENTER

REAR

SUB W O OFE R 5 MS

CNTR DELAY

REA R DE LA Y 3MS

TEST TONE

M A IN P A G E OFF

1MS

-- SPEAKER SETUP PAGE --

DOWNM IX

CENTER

REAR

SUB W O OFE R 15MS

CNTR DELAY

REAR DELAY 9MS

TEST TONE

M A IN P A G E OFF

3MS

g. TEST TONE

-- SPEAKER SETUP PAGE --

DOWNMIX

CENTER

REAR

SUBWOOFER

CNTR DELAY

REAR DELAY ON

TEST TONE OFF

MA IN P A GE

ON : open the 5.1 channel test function.

OFF : turn off the 5.1 channel test function.

17

Page 18

3.AUDIO SETUP

SETUP MENU - MAIN PAGE

GENERAL SETUP

SPEAKER SETUP

AUDIO SETUP

PREFERENCE

EXIT SETUP

a. SPDIF OUTPUT

OFF: Audio signal is out from AUDIO OUT (RCA)

-- AUDIO S ETU P PA GE --

jacks.

SPDIF OUTPUT OFF

SPDIF/RAW: The player is connected to a Dolby Digital

OP MODE SPDIF/RAW

amplifier through DIGITAL OUT Coaxial or

DUAL MONO SPDIF/PCM

COMPRESSION

Optical jack.

PRO LOGIC

SPDIF/PCM: The player is connected to a 2-channel digital

LPCM OUTPUT

mode or stereo amplifier through Coaxial or

M A IN PAG E

Optical jack.

b. OP MODE

-- AUDIO SETUP --

SPDIF OUTPUT

OP MODE LINE OUT

DUAL MONO RF REM OD

COMPRESSION

PRO LOGIC

LPCM OUTPUT

MA IN P A G E

LINE OUT : Line out mode with digital dialog normalization,

compress input linear signal.

RF REMOD : RF remodulation mode with heavy compression

and digital dialog normalization.

c. DUAL MONO

-- AUDIO S ET UP --

SPDIF O UTPUT

OP MODE

DUAL MON O STEREO

COMPR ESSION L-MONO

PRO LOGIC R-M ONO

LPCM OUTPUT MIX-M ONO

MAIN PAGE

Output mode of the L/R signals. Mix-mono can be functioned

only if the DVD is playing in 5.1 channel.

d. COMPRESSION

-- AUDIO SETUP --

SP D IF O U T PU T - - FUL L

OP MOD E - -

DU A L MON O - - 6/8

COMPRESSION - -

PR O L O GIC - - 4/8

LP C M OU T P U T - -

- - 2/8

M A IN P A G E - - OF F

To adjust linear compression rate to obtain the different

compression results of the signals only if the OP MODE is

set to LINE OUT.

18

Page 19

e. PRO LOGIC(optional)

-- AUDIO SETUP --

To select Dolby Prologic Surround mode.

SPDIF OUTPUT

OP MODE

DUAL MONO

COMPRESSION

PRO LOGIC OFF

LPCM OUTPUT ON

MA IN P A G E

AUTO

f. LPCM OUTPUT

-- AUDIO SETUP --

SPDIF OUTPUT

OP MODE

DUAL MONO

COMPRESSION

PRO LOGIC

LPCM OUTPUT LPCM 48K

LPCM 96K

MA IN P A G E

To select LPCM output at 48K or 96K.

19

Page 20

4. PREFERENCE

V

V

A

V

V

A

SETUP MENU - MAIN PAGE

GENERAL SETUP

SPEAKER SETUP

AUDIO SETUP

PREFERENCE

EXIT SETUP

a. TV TYPE b. VIDEO OUTPUT

-- PREFERENCE PAGE --

-- PREFERENCE PAGE --

TV TYPE MULTI

IDEO OUTPUT NTSC

AUDIO PAL

SUBTITLE

DISC MENU

LOCALE

PARENTAL

TV TYPE S-VIDEO

IDE O O U T PU T YPbPr

UDIO RGB

SUBTITLE

DISC M ENU

LOCALE

PARENTAL

c. AUDIO d. SUBTITLE

-- PREFERENCE PAGE --

-- PREFERENCE PAGE --

TV TYPE

VIDEO OUTPUT ENGLISH

AUDIO FRENCH

SUBTITLE SPANISH

DISC MENU CHINESE

LOCALE JAPANESE

PARENTAL ITALIAN

TV TYPE ENGLISH

VIDEO OUTPUT FRENCH

AUDIO SPANISH

SUBTITLE CHINESE

DISC MENU JAPANESE

LOCALE ITALIAN

PARENTAL O FF

e. DISC MEUN f. LOCALE

-- PREFERENCE PAGE --

-- PREFERENCE PAGE --

TV TYPE

IDE O OU T PU T ENGLISH

AUDIO FRENCH

SUBTITLE SPANISH

DISC MENU ITALIA N

LOCALE CHINESE

PARENTAL JAPANESE

TV TYPE CHINA

IDEO OUTPUT FRANCE

UDIO

SUBTITLE JAPAN

DISC MENU TAIW AN

LOCALE GBR

PARENTAL USA

HONG KONG

20

Page 21

g. PARENTAL

V

V

V

A

-- PREFERENCE PAGE --

TV TYPE 1 G

IDE O OU T PU T 2

AUDIO 3 PG

SUBTITLE 4 PG 13

DISC MENU 5

LOCALE 6 PG-R

PARENTAL 7 NC-17

PASSWORD 8 ADULT

To select an age control grade according to the grade of

the disc and your desired. The disc cannot be played for

the rate higher than the grade set.

Go to the PASSWORD VERIFY PAGE to input password

after selection of Parental grade.

h. PASSWORD i. DEFLAUTS

-- PREFERENCE PAGE --

-- PREFERENCE PAGE --

TV TYPE

IDE O OU T PU T

AUDIO

SUBTITLE

DISC MENU

LOCALE

PARENTAL

PASSWORD CHANGE

IDE O O U T PU T

UDIO

SUBTITLE

DISC M ENU

LOCALE

PARENTAL

PASSWORD

DEFLAUTS RESET

The default setting of password is 3308 To reset the settings to factory setting

j. SMART NAVI

-- PREFERENCE PAGE --

AUDIO

SUBTITLE

DISC MENU

LOCALE

PARENTAL

PASSWORD

DEFLAUTS NO MENU

SMART NAVI WITH MENU

To select the display with MENU for playing MP3 and

PHOTO CD (JPEG).

21

Page 22

5. JPEG, MP3 & MPEG4 Format

(Playback of MP3, WMA, CD-R and CD-RW may depend on recording condition)

ROOT JPEG 1

SMART NAVI

ROOT MP3 1

JPEG 2

JPEG 3

JPEG 4

JPEG 5

JPEG 6

JPEG 7

JPEG 8

SMART NAVI

MP3 2

MP3 3

MP3 4

MP3 5

MP3 6

MP3 7

MP3 8

Press to select the „ROOT“ on the left columns & the „FILE“ on the right side, press

ENTER“/“PLAY“ to view the JPEG PHOTOS or to play MP3 files. Then press “STOP” to go back to the menu

of SMART NAVI”.

FUNCTION KEYS

Zoom Press the “ZOOM” Button, then the screen will show “ZOOM ON”,

and press Icons to “zoom in” or “zoom out”.

Rotate Press to rotate the picture

Next/ Press to the next or previous pictures/songs.

Previous

Forward/ Press the icons to playing fast forward ans fast backward.

Backward

Menu Press “Menu” to preview the photos.

Mute Press “MUTE” button to turn the audio off. Press it again to resume.

Pause Press to pause playin & press again to resume.

22

Page 23

MPEG4 FORMAT

ROOT MP4 1

SMART NAVI

MP4 3

MP4 3

MP4 4

MP4 5

MP4 6

MP4 7

MP4 8

FUNCTION KEYS

Forward/ Press the icons to playing fast forward and fast backward.

Backward Continuously pressing and back to normal.

Next/ Press to the next or previous chapter or files.

Previous

Mute Press “MUTE” button to turn the audio off. Press it again to resume.

Pause Press ___ to pause playing & press again to resume.

Slow Press “SLOW” and playback of slow motion. Please “Play” to resume it.

Step Keeping press “STEP” repeatedly button to playing frames by frames.

GoTo Search the chapter and time you want. Functions please refer to “Function Buttons” on instruction

book.

Subtitle

In order to use the function of Subtitle (For the MPEG4 file with subtitle function):

Insert disc and choose the file in “?” icon, then press ‘ANGLE’ button in remote control,

the screen will shown subtitle is being selected. Then get back to the appropriate .avi file

and press ‘ENTER’ to playback, then the subtitle function is activate.

23

Page 24

3.PRODUCT SPECIFICATIONS

A. Playback System

DVD Video

Video CD (1.1, 2.0, 3.0)

SVCD

CD and CDDA

CD-R/RW

PICTURE CD

B. Television Signal System

NTSC/PAL

C. Video Performance

Video Out 1V

S-Video Out Y: 1VPP into 75ohm

D/A Converter 27MHz/10 bit

D. Audio Performance

Frequency Response DVD: fs48//96KHz, 4Hz-22/44KHz

Output Level Analog: 2V

D/A Converter 96KHz/24bit

S/N Ratio With LPF 95dB

E. Connections

Coxial digital out X1

into 75ohm

PP

C: 0.286V

into 75ohm

PP

Video CD: fs 44.1KHz, 4Hz-20KHz

Audio CD: fs44.1KHZ, 4Hz-20KHz

(1KHZ)

RMS

Digital: 1.15V

PP

Without LPF 90dB

Digital out X1

Audio Analog out (5.1ch) X1

S-Video out X1

F. Power Supply

Power Source AC 90-250V 50/60Hz

Power Consumption <25 Watt

24

Page 25

4.TROUBLESHOOTING

Symptom Check and Action

No Power

Do not play

No Picture

Picture noise /

distorted

Picture not full

screen

Cannot SKIP or

SEARCH

No sound or

Sound output not

complete

1. Check the power cord has been properly connected to the wall outlet

2. Check the main power has been switched on

1. No disc, load a disc

2. Disc has been loaded upside down. Place the disc with the label side up

Disc’s region code is not matching to the unit

3.

Disc is not correct type to be played

4.

Disc is damaged or dirty, clean the disc or try another disc

5.

Moisture may be condensed inside the unit. Remove the disc and leave the unit

6.

power on for one or two hours

1. Check the TV set has been power on, and setting at the correct AV mode

2. Check the system connection is secure

3. Check if the connection cables are damaged

4. Clean the disc

1. Disc is dirty or damaged. Clean the disc or try another disc

2. Reset the color system of the DVD unit or the TV set

3. Try to direct the DVD unit to the TV set instead of via the components like VCR.

1. Select the screen format. Enter SETUP MENU (TV DISPLAY)

2. Select the screen format from DVD disc menu

1. Some disc are programmed that do not allow users to SKIP or SEARCH forward

at some sections, especially at the beginning WARNING section

2. Single Chapter disc cannot apply SKIP function

1. Check the TV and amplifier has been power on and correctly setting

2. Check the TV and amplifier system connections are secure

3. Press AUDIO button select other audio tracks output of disc

4. Check if the MUTE function of the DVD, TV or amplifier has be activated

5. There will be no sound output during REVERSE PLAY / PAUSE / STEP / SLOW /

SEARCH

25

Page 26

5.MAINTENANCE INSTRUCTIONS

INDEX:

a. No power

Please see Fiugure 1

b. No VFD display

Please see Fiugure 2

c. No Video output

Please see Fiugure 3

d. Cannot read disc

Please see Fiugure 4

e. No ear phone output

Please see Fiugure 5

f. Remote control no function

Please see Fiugure 6

g. No 5.1ch output

Please see Fiugure 7

h. Disc door cannot open

Please see Fiugure 8

26

Page 27

i Figure 1

t

N

START

Power on

The unit cannot switch

on

Does the connecti on

between power board and

the power cord/rear switch

is correc

?

o

Change/reinset the

cables or wires

Yes

Does the fuse on power

board is burned?

Yes

Change

fuse

Change power board

Change MPEG board

END

27

Page 28

ii Figure 2

N

START

Power on

No VFD display

Does the output level at

power board "con6"

correct?

F1, F2:+3.3V(+2.6~3.5V)

+5V: +4.5V~5.4V

-24V: -18V~-26V

Yes

Change MPEG board

Change

front penal

END

o

Change

power board

28

Page 29

iii Figure 3

START

Power on

Scart no output?

Change

MPEG board

Change

scart board

Change

MPEG board

END

29

Page 30

iv Figure 4

START

Power on

Insert VCD DVD CD-R/RW DVD-R/RW

DVD+R/RW PHOTO CD

VFD Display "NO DISC" or the unit DEAD

Change the 24PIN cable

(from loader to mpeg board )

Change loader

Change MPEG board

END

30

Page 31

v Figure 5

N

START

Power on

Ear phone no output

Does ear phone board and

power board have correct

connection?

Yes

Change MPEG board

Change front panel

END

o

Change

the cable

31

Page 32

vi Figure 6

N

START

Power on

Remote control does

not work

Does the remote control

have batteries?

Yes

Does other remote control

work?

Change MPEG board

Change front panel

END

o

Yes

Insert new batteries

Change

remote control

32

Page 33

vii Figure 7

N

N

N

START

Power on

5.1ch no output

Does the disc support

5.1ch output?

Yes

Does the unit audio

setting is at 5.1ch?

Yes

Does the power board

"con4"outpnt level

correct?

+12v (+9~15V)

-

-

~

Yes

Change MPEG board

END

O

O

o

Use other disc to

check

Reset the unit at setup

menu

Change the power

board

33

Page 34

viii Figure 8

START

Power on

The disc door cannot open

Change

5PIN cable

(from loader to MPEG board)

Change

loader

Change

MPEG board

END

34

Page 35

6.ELECTRICAL PART LIST

A. MPEG board

Item Name of Components Specification

1

2 IC 8MFLASH 29F800BA--70PFTN 1 U2

3 IC ES6688 1 U1

4 IC ES6603 1 UU2

5 IC SDRAM 4Mx16--6T, 1 U5

6 IC 24C02 1 U3

7 IC 74HC04 1 U13

8 IC V6300 1 U8

9 IC BA6287F 1 UU5

10 IC BA5954FP 1 UU3

11 IC WM8746 /DA1196 1 U9

PCB板

ESS-66X8 PCB REV:1.3 1

Qty

Location

12 IC RC4558 3

13 IC TL3472 1 UU4

14 IC AMS1117/LM1117 3 Q4,Q3,QQ4

15 Jack TJC3-7(7pin x2.54mm ) 1 J4

16 Jack TJC3-3 (3pin x 2.54mm ) 1 J1

17 Jack

18 Jack PH2.0 ( 5pin x 2.0mm ) 2 JJ5, J2

19 Jack PH2.0 (6pin x 2.0mm ) 1 J12

20 Jack PH2.0 ( 11pin x 2.0mm ) 1 J6

21 Jack TOTX179 1 J8

22 Jack AV1-8.4-1S 1 J9

FPC Jack(24Pin Pitch0.5mm)

U12,U14,U15

1JJ3

35

Page 36

23 Jack 4PIN,AV4---8.4---13P 1 J13

24 Jack 6PIN,AV6---8.4---13P 1 J10

25

26

27

28

29

30

31

32

33

34 Chip diode 4.3V 1/2W 1 D14

35 Chip diode 1N6263 10 D1,D2,D3,D4,D5,D6,D7,D8,D9,D10

36 Chip diode 1N4148 7 D15,D16,D17,DD1,DD2,DD3,D13

37

Crystal

Transistor

Transistor

Transistor

Transistor

Transistor

Chip Bead

Chip Bead

chip Inductor

chip Resistor

27M-30ppm HC-49S 1 Y1

PMBT3904,NPN type

2SC3327 6 Q7,Q12,Q17,Q18,Q19,Q22

8550 2 Q6,Q8

8050 1 Q2

2SB1132 2 QQ1,QQ2

FB0805-0.2A-26@100MHz 9 LL1,LL2,LL4,LL5,LL6,FB1,FB2,FB4,LL3

FB1206-0.2A-26@100MHz 6 L11,L12,L13,L14,L15,L16

LG0805-0.2A-1.8uH±10% 5 L1,L2,L3,L4,L5

R0603-0Ω ±5% 18

1Q9

RL3,R5,R14,R17,R19,R20,R40,R43

R61,R157,RR10,RR11,RR19,RR41

RR58,RR72,RR75,RR87

38

39

40

41

42

43

44

45

46

47

48

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

R0805-1 Ω±5% 4 RR66,RR67,RR68,RR69

R0805-3.3Ω±5% 1 RR83

R0603-10Ω ±5% 8

R0603-33Ω ±5% 23

R0603-47Ω±5% 1 R33

R0603-68Ω±5% 1 R113

R0603-75Ω±5% 5 R6,R11,R12,R15,R16

R0603-91Ω±5% 1 R105

R0603-100Ω±5% 2 RR35,RR36

R0603-150Ω±5% 1 R76

R0603-240Ω±1% 1 R80

36

R82,R98,R115,R127

R133,R145,RR45,RR46

R23,R24,R25,R26,R28,R29,R30,R31

R44,R48,R49,R50,R52,R58,R60,R63

R65,R66,R68,RR27,RR28,RR29,RR52

Page 37

49

chip Resistor

R0603-330Ω±1% 1 R75

50

51

52

53

54

55

56

57

58

59

60

61

62

63

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

R0603-330Ω±5% 2 R102,R125

R0603-360Ω±5% 1 R13

R0603-412Ω±1% 2 R74,RR85

R0603-470Ω±5% 1 R95

R0603-681Ω±1% 2 R79,RR86

R0603-1KΩ±5% 6 R21,R22,R89,R90,RR43,RR56

R0603-1.2KΩ±5% 3 RR16,RR37,RR39

R0603-1.5KΩ±5% 2 RR71,RR79

R0603-2KΩ±5% 6 R88,R108,R131,R124,R140,R152

R0603-2.2KΩ±5% 1 R85

R0603-3.3KΩ±5% 11

R0603-4.7KΩ±5% 7 R7,R8,R9,R10,R27,R73,RR76

R0603-5.1KΩ±5% 3

R0603-6.8KΩ±5% 6 R83,RR20,RR21,RR22,RR25,RR26

R87,R107,R123,R130,R139,R151

RR3,RR4,RR5,RR6,RR55

RR18,RR24,RR50

64

65

66

67

68

69

70

71

72

73

74

75

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

chip Resistor

R0603-10KΩ±5% 5 RR7,RR17,RR44,RR70,RR77

R0603-11kΩ±5% 6 R86,R106,R122,R129,R138,R150

R0603-12kΩ±1% 1 RR34

R0603-12kΩ±5% 1 RR53

R0603-18kΩ±5% 6 R94,R111,R126,R132,R141,R153

R0603-20kΩ±5% 1 RR9

R0603-22kΩ±5% 3 RR48,RR74,RR82

R0603-33kΩ±5% 3 RR15,RR47,RR51

R0603-47kΩ±5% 2 RR49,RR54

R0603-68kΩ±5% 1 RR8

R0603-100kΩ±5% 8

R0603-1MΩ±5% 2 R96,RR73

R42,R84,R100,R93,

R117,R128,R136,R148

37

Page 38

76

chip Resistor

R0603-10MΩ±5% 1 R91

77

78

79

80

81

82

83

84

85

86

87

88

89

chip Resistor

chip Resistor

chip Resistor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

0603 ,10Ωx4 3 RN1,RN2,RN3

0603 ,33Ωx4 2 RN9,RN10

0603 ,4.7kΩx4 1 RN4

C0603-22P±5% 6 C37,C47,C56,C60,C67,C81

C0603-27P±5% 2 C13,C14

C0603-33P±5% 3 CC35,CC36,CC37

C0603-47P±5% 1 CC25

C0603-100P±5% 2 CC70,CC72

C0603-120P±5% 1 CC57

C0603-150P±5% 6 C40,C50,C57,C63,C69,C83

C0603-160P±5% 1 CC65

C0603-330P±20% 10

C0603-470P±20% 3 CC41,CC43,CC86

C1,C2,C3,C4,C5,C6,C9,C10,C11,C12

90

91

92

93

94

95

96

97

98

99

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

chip capacitor

C0603-560P±20% 3 CC23,CC30,CC33

C0603-820P±20% 1 CC48

C0603-1000P±20% 12

C0603-2200P±20% 4 CC51,CC52,CC53,CC56

C0603-4700P±20% 3 CC6,CC11,CC73

C0603-6800P±20% 1 CC17

C0603-0.01U±20% 4 CC40,CC42,CC45,CC67

C0603-0.015U±20% 3 CC28,CC31,CC32

C0603-0.033U±20% 1 CC66

C0603-0.047U±20% 2 CC21,CC54

C43,C52,C58,C64,C70,C90,CC1

CC2,CC3,CC4,CC64,CC71

38

Page 39

100

chip capacitor

C0603-0.1U±20% 65

B9,B10,B11,B12,B15,B18,B23,B24,B25

B26,B27,B28,B29,B30,B31,B32,B33,B36

B37,B38,B39,B40,B41,B42,B44,B45,B46

B47,B48,B49,B50,C7,C8,C30,C42,C48

C72,C73,C74,C75,C84,C85,C86,CC5,CC13

CC14,CC15,CC22,CC24,CC26,CC27

CC34,CC38,CC39,CC44,CC47,CC49

CC50,CC60,CC62,CC75,CC77,CC80,CC81

,CC94

101

102

103

104

105

106

107

108

chip capacitor

chip capacitor

Electrolytic capacitor

Electrolytic capacitor

Electrolytic capacitor

Electrolytic capacitor

Electrolytic capacitor

Electrolytic capacitor

C0603-0.22U±20% 1 CC63

C0603-1U±20% 6

CD-11,4.7U/25V±20% 1 CC8

CD-11,10U/25V±20% size:Φ4x5 18

CD-11,10U/25V±20% 10

CC10,CC12,CC20,CC83

CC88,CC92

B1,B60,C16,C17,C18,C20,C22,C26, C31

C35,C45,C55,C59,C65,C79,C87,C88,C89

B13,B19,B34,B43,B51,B61,C71,C76,C77,C

78

CD-11,100U/16V ±20% 12

CD-11,220U/16V±20% 5 B5,B7,C38,CC93,B14

CD-11,470U/25V±20% 2 C36,CC84

B2,B3,B4,B20,B22,CC68,CC69

CC78,CC85,CC87,CC89,CC91

39

Page 40

B. Power board

Item Name of Components Specification

Carbon Film Resistor

1

Carbon Film Resistor

2

Carbon Film Resistor

3

Carbon Film Resistor

4

Carbon Film Resistor

5

Carbon Film Resistor

6

Carbon Film Resistor

7

Carbon Film Resistor

8

Metal Film Resistor

9

Electrolytic capacitor

10

Electrolytic capacitor

11

Electrolytic capacitor

12

Electrolytic capacitor

13

RT14-1/4W-10-±5% 4 R7,R8,R16,R17

RT14-1/4W-270-±5%

RT14-1/4W-1K-±5%

RT14-1/4W-2K2-±5% 1 R13

RT14-1/4W-4K7-±5% 1 R19

RT14-1/4W-100K-±5%

RT14-1/4W-470K-±5% 4 R1,R2,R3,R4

RT13-1/2W-22-±5% 3 L5,L3,L4

RJ14-1/4W-1K-±1%

CD11-470u-16V--20%+80% 1 EC7

CD11-47u-25V--20%+80% 1 EC9

CD11-220u-25V--20%+80% 1

CD11-22u-50V--20%+80%

Qty

2 R15,R10

4 R9,R14,R18,R21

2 R5,R6

2 R11,R12

Location

EC5

EC2,EC11,EC13

3

Electrolytic capacitor

14

Electrolytic capacitor( high frequency)

15

Electrolytic capacitor( high frequency)

16

Electrolytic capacitor( high frequency)

17

Electrolytic capacitor( high frequency)

18

Electrolytic capacitor( high frequency)

19

Ceramic capacitor

20

Ceramic capacitor

21

Ceramic capacitor

22

23

High Voltage Ceramic Capacitors

24

High Voltage Ceramic Capacitors

25

CC1-100V-220n--20%+80% 1 C6

CD293-47u-400V--20%+80% 1

CD288-1000u/16V--20%+80% 1 EC6

CD288-100u/16V--20%+80%

CD288-100u/25V--20%+80% 1

CD288-470u/25V--20%+80% 1 EC4

CD288-100u/50V--20%+80%

CC1-50V-0.1u--20%+80% 1 C19

CC1-50V-470P--20%+80%

CC1-50V-10n--±20%

CC81-1KVDC-10nF-±20% 1 C4

CC81-1KVDC-0.1nF-±20%

EC1 (6.5mm)

EC12

1

EC8

1 EC10

2 C7,C9

1 C5

1 C3

40

Page 41

Safety Regulation capacitor

26

CT7-400VAC-1n-±20% 3

C16,C17,C18

27 Capacitor CBB230-275VAC-100n-M 1 C1

28 ferrite core Inductor 22uH-±10%-9X12mm-5mm

Bead

29

30

31

Diode

Diode

LB-3.5*9mm-5A-90

1N4007

SR360

Diode

32

33

34

Diode

Diode

HER102

HER103

HER107

Diode

35

36

IC

37

IC

38

IC

39

Fuse

40

HER153

3.9V-5mA-1/2W-(DO-35)

305T817

KA5L0380R

TL431

RTH-30-630mA-250VAC

2 L1,L2

1 L6

4 D1,D2,D3,D4

1 D7

1 D11

D5,D9,D10

3

1 D6

1 D8

1 ZD1

1 U2

1 U1

1 U3

1 (F1)

Fuse Jack

41

FC-21 2 F1

42

43

44

Jack

Jack

Jack

VH-3(7.92mm,2pins

TJC3-5A(2.54mm,5pins)

TJC3-7(2.54mm,7pins)

)

2 CON1,CON2

CON6

1

1 CON4

45 Transformer

Filter

46

47

BCK28C929A

LT16U137 68mH 1 LF1

2

1 T1

48 Heatsink 16x10x26mm 1 U1

Screw

49

50

51

Jumper

Jumper

PM3X8

φ0.6--9mm

φ0.6--4mm

1 U1

3 R31,J3,J8

1 J5

41

Page 42

52

53

Jumper

Jumper

φ0.6--6.5mm

0.6--15mm

φ

1 J7

2 J1,J2

54

PCB board

153mmX57mm 1

DVD-POWER-03 VER2.0

42

Page 43

7.DISASSEMBLY AND REASSEMBLY

43

Page 44

8.CIRCUIT DIAGRAMS

A. Index

44

Page 45

B. Vibratto-II ES66x8

45

Page 46

C. Motor Drives

46

Page 47

D. Audio and Power

47

Page 48

E. Audio Filter and output

48

Page 49

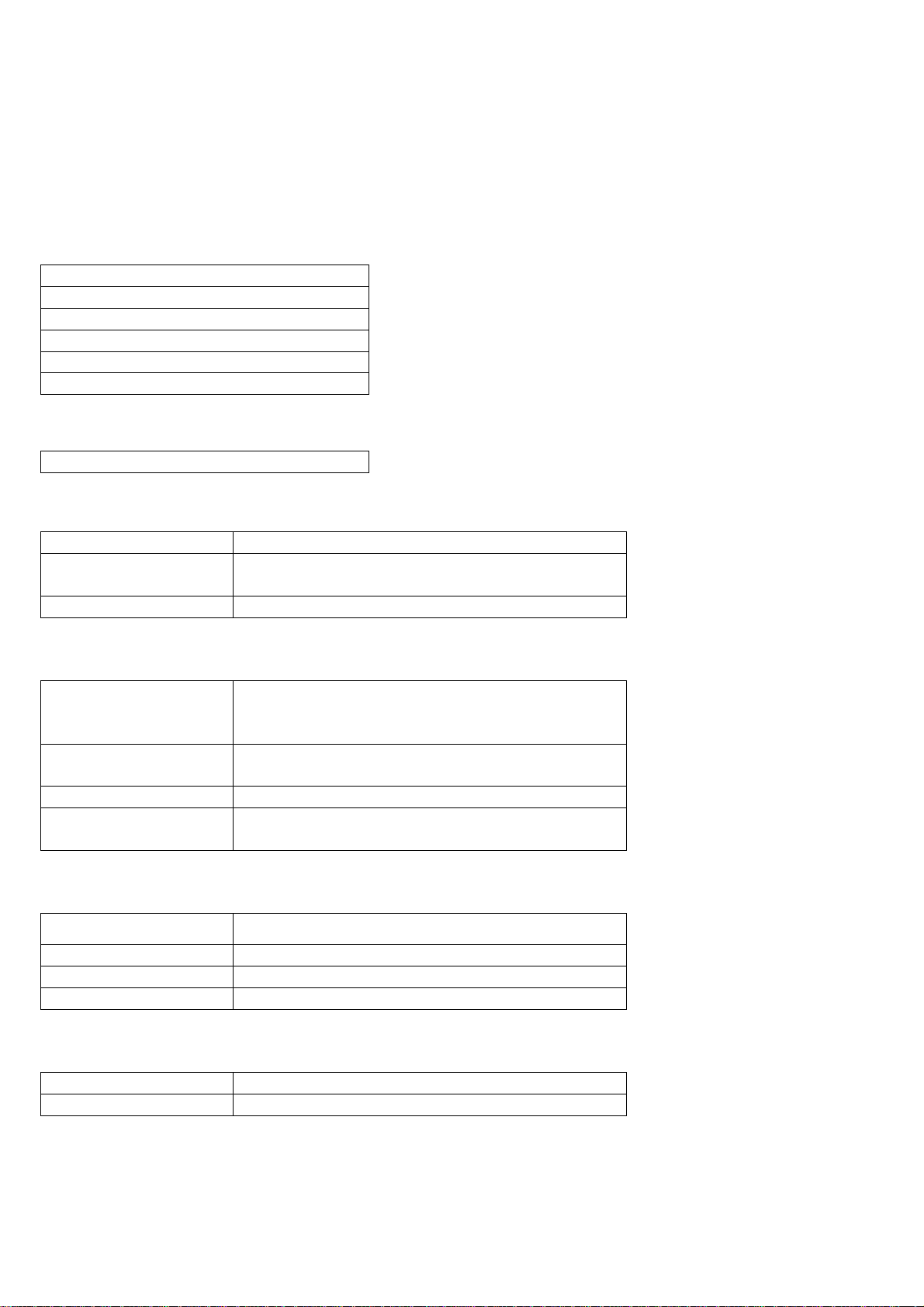

9.WIRING DIAGRAM

p

Ear Phone

CON4

Power

supply

Scart

J13

24PIN

J4 J1

Front

anel

MPEG

J2

J12 JJ5

24PIN

Loader

49

Loading...

Loading...