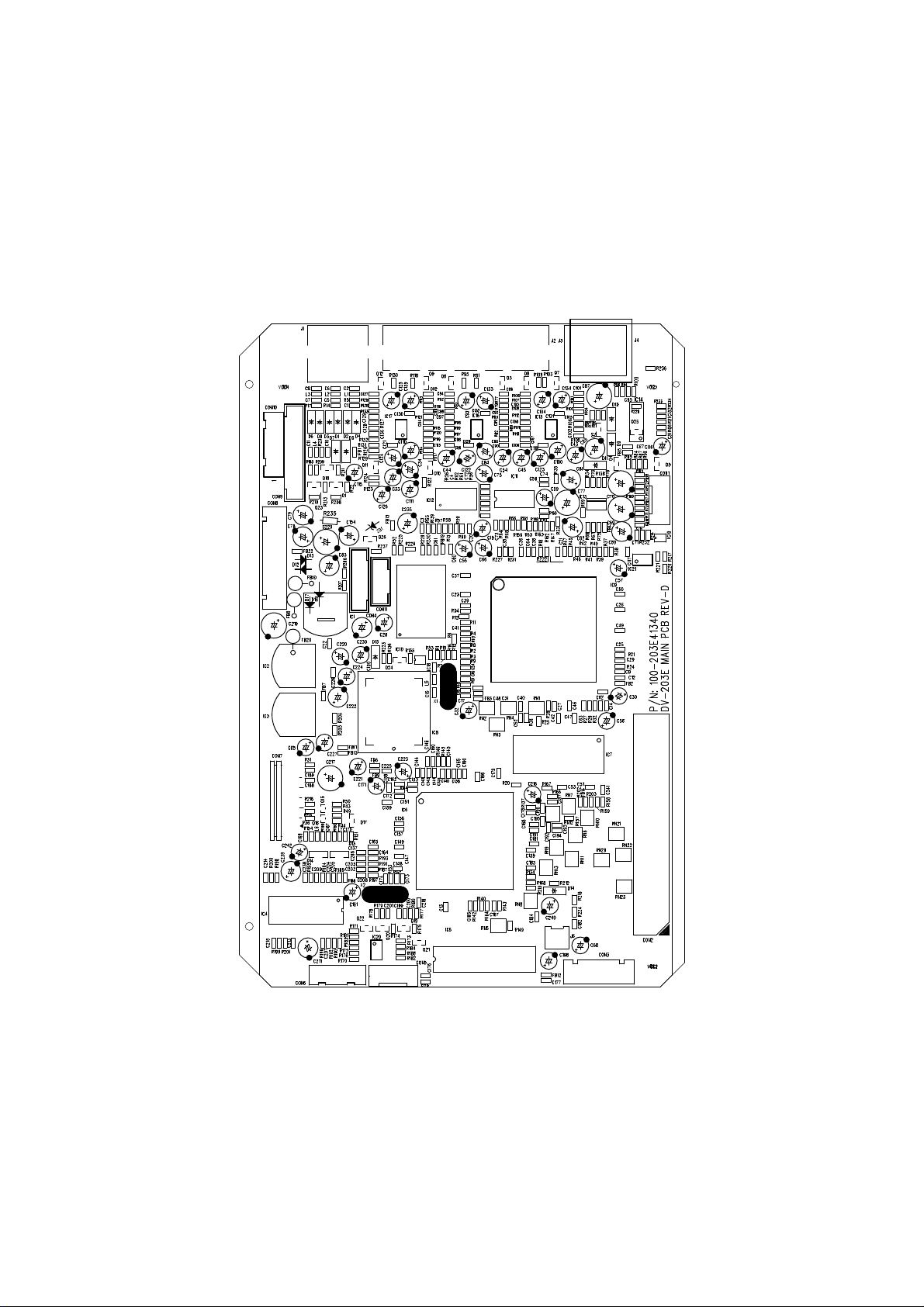

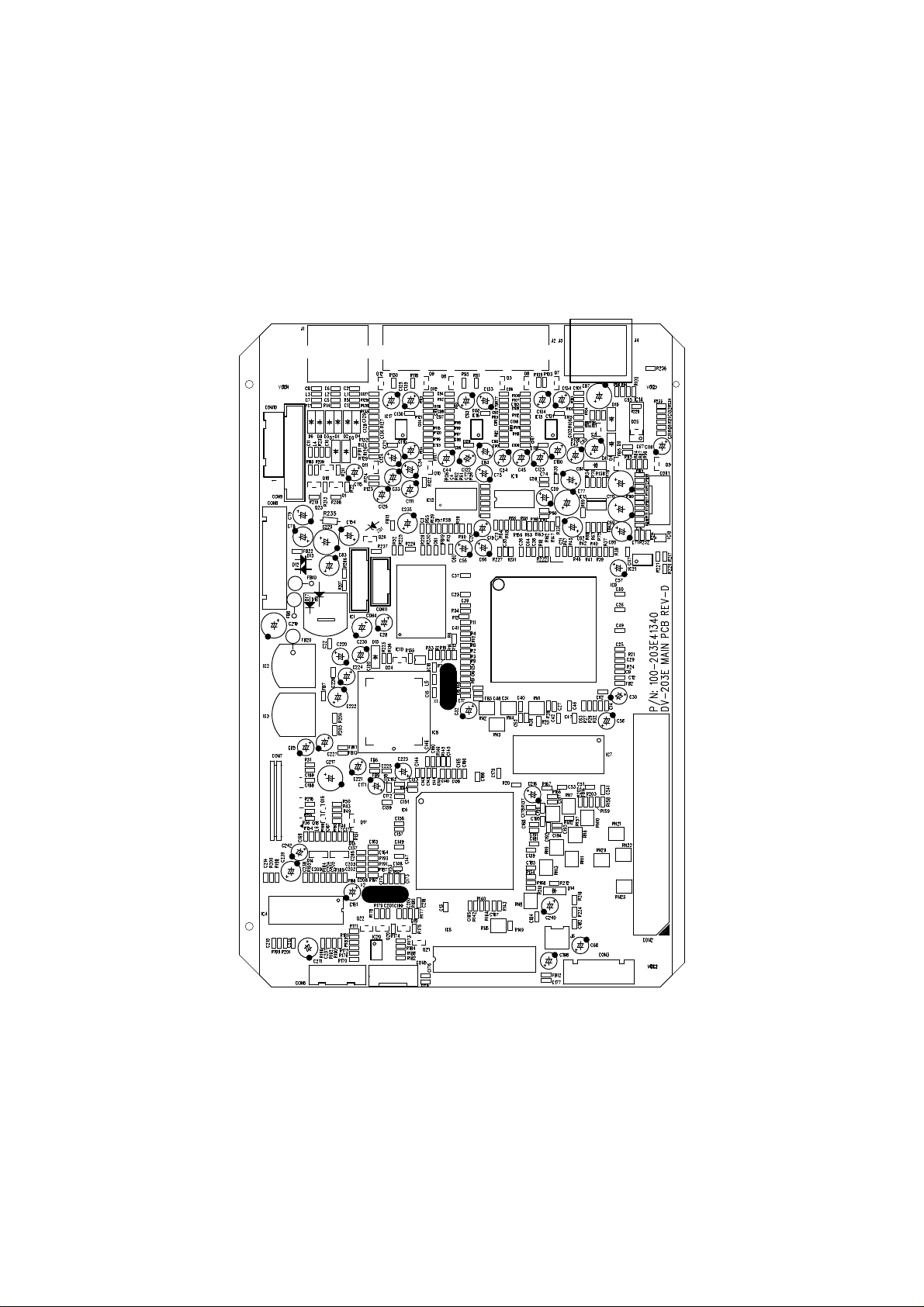

Page 1

- GDVD516S

- GDVD516S

GDVD516S

Service Manual

Service Manual

Page 2

Page 3

Page 4

Page 5

Page 6

Page 7

Page 8

A

4 4

MANUFACTURE

INTEL

INTEL

TI

TI

SHARP

AMD

ATMEL

SST

SST

SST

SST

ST RESET

ST

LA0

LD15

VCC

VCC33

3 3

2 2

1 1

IC10

LA16

LA15

LA14

LA13

LA12

LA11

LA10

LA9

10

11

-RST

12

13

14

15

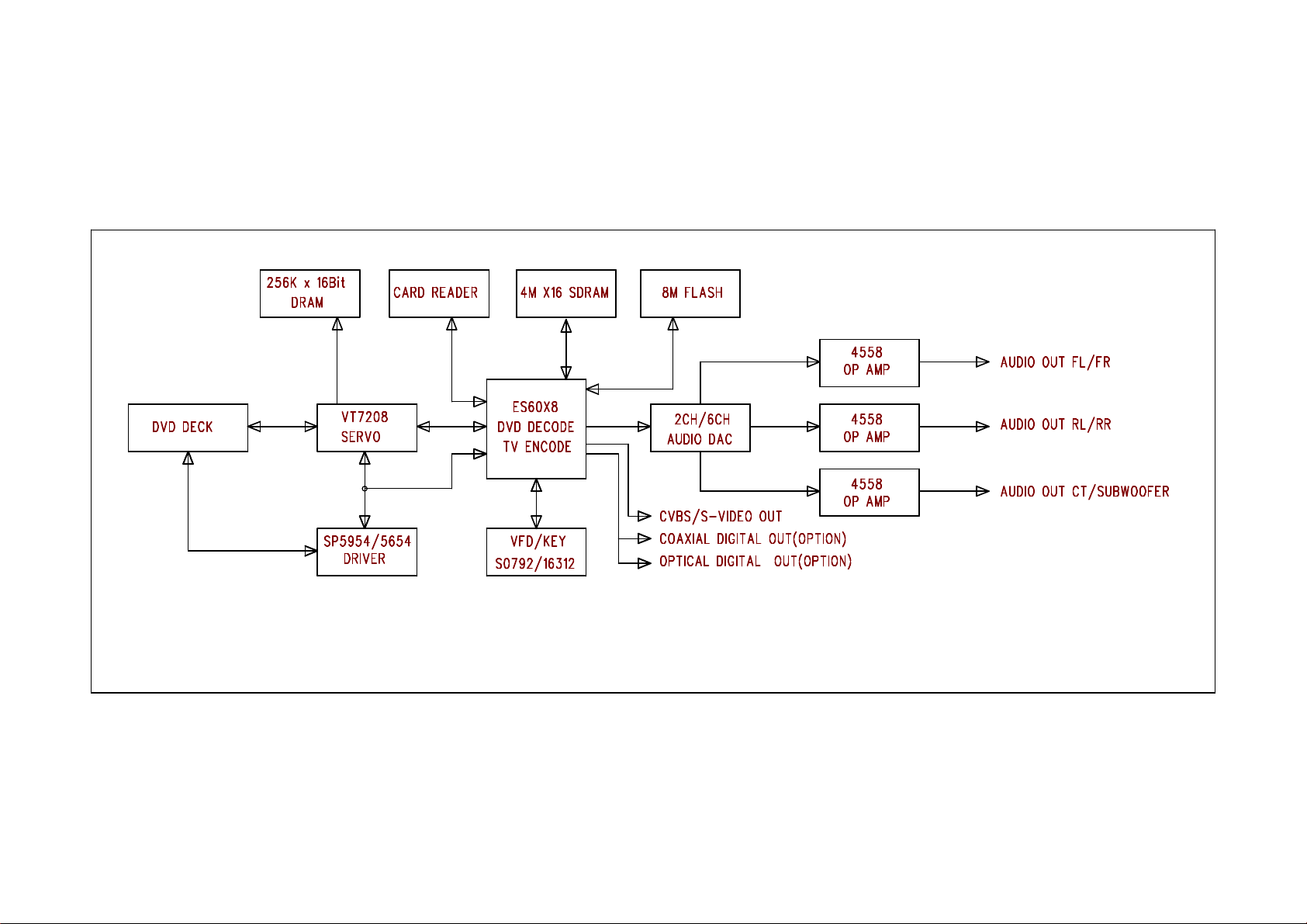

LA19

16

LA18

17

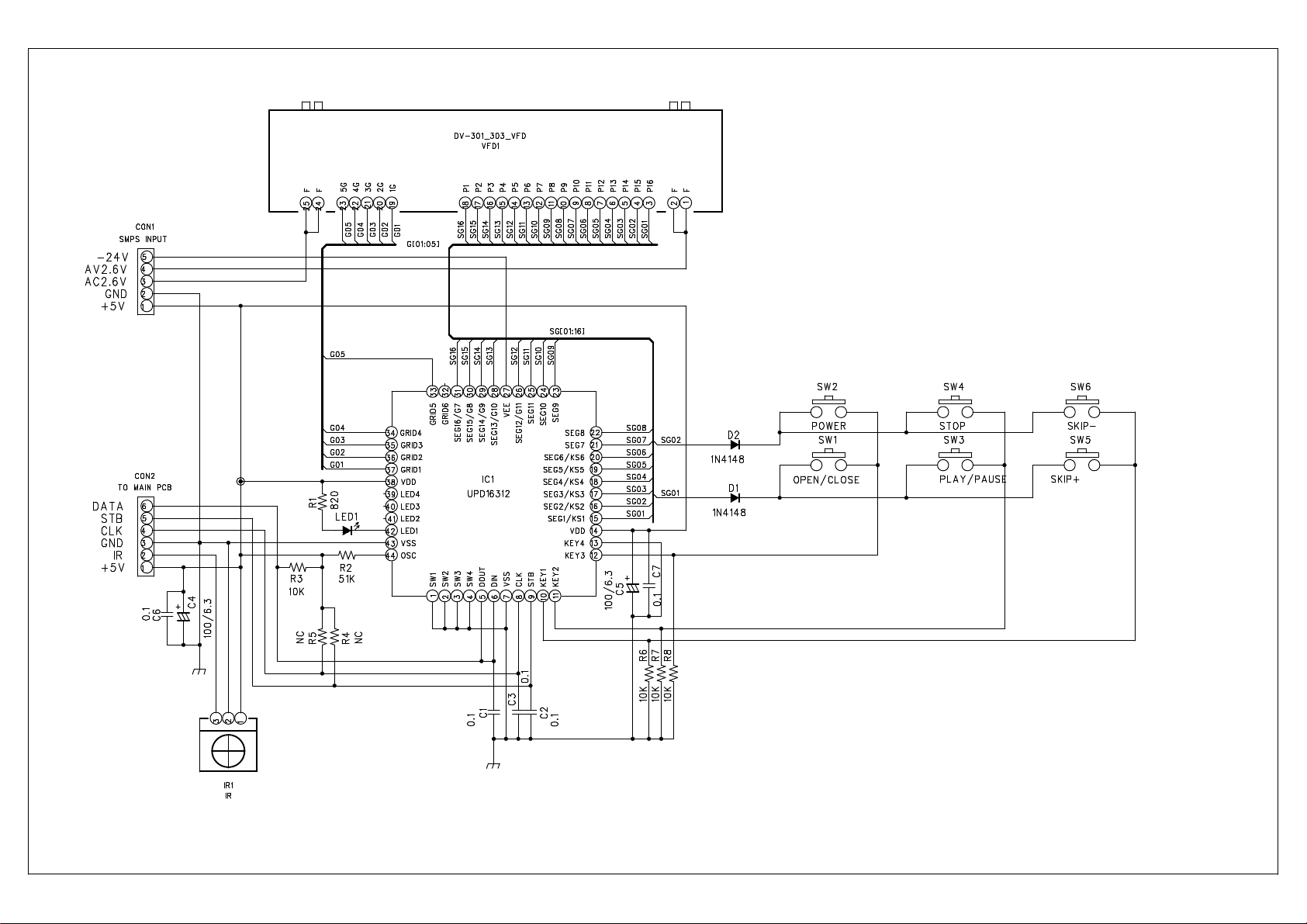

LA8

18

LA7

19

LA6

20

LA5

21

LA4

22

LA3

23

LA2

24 25

-WRHL

-SWRLL

-LCS2

-LCS3

EM-MARIN

RESET IC

IC18

NC

GND

NC

RES

VDD

V6300,SOT-23 5L

Package: SOT-23 5L

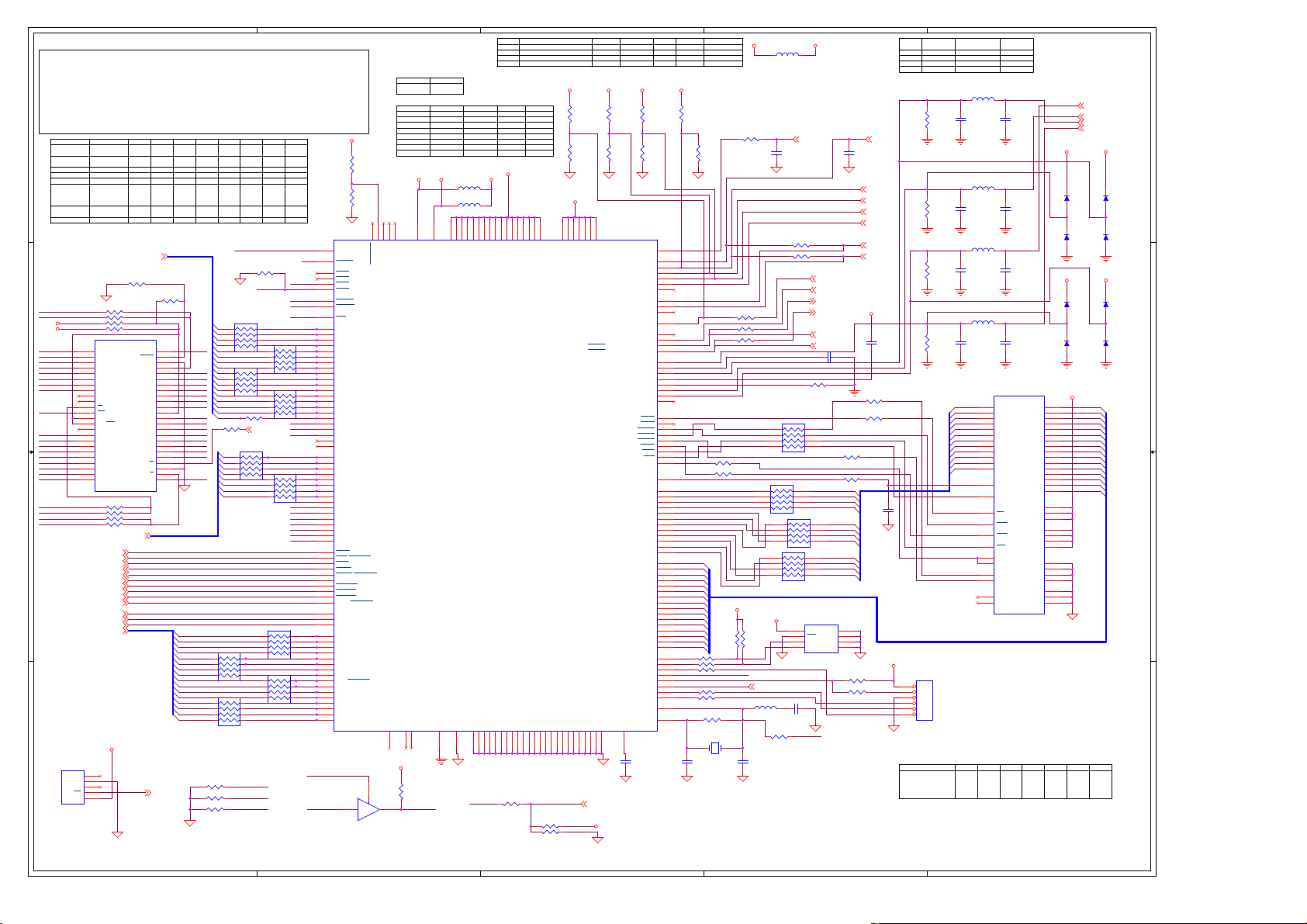

The information has been checked and is believed to be reliable. However, no responsibility is assumed for inaccuracies. Circuit diagrams are provided as a means of illustrating typical applications; consequently complete information for construction purposes is not necessarily given. ESS reserves the right to make changes at any time in order to improve the design.

28F800B5

TMS28F400AXY

TMS28F800AXY

LHF80V11

AM29F800B

AT49F8192A(T)

SST39VF400

SST39VF800

ST39VF800Q

M29F800AT

M29F800AB

MX29F800T/B

R2270,0603

R228(DEL)0,0603 UM

R2290,0603

R2300,0603 UM

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

9

NC

NC

W

RP

VPP

DU/WP

NC

NC

A17

A7

A6

A5

A4

A3

A2

A1 A0

-HRST7

-HRD7

-HWR7

EAUX402

EARPHONE2

HIORDY7

-HIOCS167

-HCS17

-HCS37

HIRQ7

HA07

HA17

HA27

HD[0..15]7

VCC

1

2

3

4

5

PIN 9

PIN10

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC RESET

NC

SA[0..16]

SA[0..16]4

BYTE

R2250,0603

R226

0,0603 UM

48

A16

47

BYTE

46

GND

45

DQ15/A_1

44

DQ7

43

DQ14

42

DQ6

41

DQ13

40

DQ5

39

DQ12

38

DQ4

37

VCC

36

DQ11

35

DQ3

34

DQ10

33

DQ2

32

DQ9

31

DQ1

30

DQ8

29

TMS28F400Axy

DQ0

28

G

27

GND

26

E

R2310,0603 UM

R2320,0603

R223(DEL)0,0603 UM

R2220,0603

SD[0..7]

SD[0..7]4

-HRST

HD[0..15]

-RST

-REST

A

2

PIN 12

RP

RP

RP

RP

RP

RESET

RESET

NC

NC

NC

NC

RESET

LA17

LD7

LD14

LD6

LD13

LD5

LD12

LD4

LD11

LD3

LD10

LD2

LD9

LD1

LD8

LD0

-LOE

LA1

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

PIN14

PIN13

VPP

WP#

WP#

VPP

DU/WP

VPP

DU/WP

VPP

WP#NC

VPP

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

RN14 NC

SA0

1

SA1

3

SA2

5

SA3

7 8

SA4

SA5

SA6

SA7

RN16 NC

SA8

1

SA9

3

SA10

5

SA11

7 8

SA12

SA13

SA14

SA15

SA16

R135(DEL)

0,0603 UM(DEL)

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

RN21 33x4

1

3

5

7 8

RN23 33x4

1

3

5

7 8

R52 10K,0603

R53 10K,0603

R54 10K,0603

PIN15PART #

NC

NC

NC

NC

RY/BY#

RY/BY#

NC

NC

NC

NC

NC

RY/BY#

RY/BY#

RY/BY#MXIC

R18 100,0603

R136(DEL)

0,0603 UM(DEL)

LOE 4

RN18 NC

1

3

5

7 8

2

4

6

2

4

6

LA17

LA18

LA19

PIN47

PIN16

BYTE

NC28F400B5

A18

BYTE

BYTE

NC

BYTE

A18

BYTE

A18

BYTE

A18

BYTE

A18

NC

NC

A18

NC

VDDQSST39VF400Q

NC

VDDQ

A18

A18

BYTE

A18

BYTE

A18

BYTE

27/33M

-LCS3

2

4

6

RN15 NC

1

3

5

7 8

2

4

6

RN17 NC

1

3

5

7 8

2

4

6

RN19 NC

1

3

5

7 8

-HRD

-HWR

HIORDY

-HIOCS16

-HCS1

-HCS3

HIRQ

RN20 33x4

1

3

5

7 8

RN22 33x4

1

3

5

7 8

105

-RST

173

174

-LCS2

175

176

-WRLL

198

-WRHL

199

-LOE

170

LA0

204

LA1

205

LA2

206

LA3

207

LA4

2

LA5

4

LA6

6

LA7 VREF

LA8

LA9

LA10

LA11

LA12

2

LA13

4

LA14

6

LA15

LA16

LA17

LA18

LA19

LD0

178

LD1

179

LD2

180

LD3

181

LD4

182

2

LD5

185

4

LD6

186

6

LD7

187

LD8

188

LD9

189

LD10

190

LD11

191

LD12

194

LD13

195

LD14

196

LD15

197

145

150

149

143

142

146

151

152

153

144

HA0

154

HA1

155

HA2

158

122

2

123

4

124

6

125

126

127

128

131

2

132

4

133

6

134

135

136

137

140

141

AUX3

-WRLL -SWRLL

B

VCC

R11

4.7K,0603

R12

4.7K,0603 UM

CLK

24

RESET

LCS0

LCS1

LCS2

LCS3

LWRLL

LWRHL

LOE

LA0

LA1

LA2

LA3

2

LA4

3

LA5

4

LA6

5

LA7

6

LA8

7

LA9

10

LA10

11

LA11

12

LA12

13

LA13

14

LA14

15

LA15

16

LA16

19

LA17

20

LA18

21

LA19

22

LA20

23

LA21

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

LD8

LD9

LD10

LD11

LD12

LD13

LD14

LD15

HRST/EAUX3[5]

HRD/DCI_ACK/EAUX4[6]

HWR/DCI_CLK/EAUX4[5]

HRDQ/EAUX4[0]

HWRQ/DCI_REQ/EAUX4[1]

HIORDY/EAUX3[3]

HIOCS16/CAMPCLK/EAUX3[4]

HCS1FX/EAUX3[7]

HCS3FX/EAUX3[6]

HIRQ/DCI_ERR/EAUX4[7]

HA0/EAUX4[2]

HA1/EAUX4[3]

HA2/EAUX4[4]

HD0/DCI[0]/EAUX1[0]

HD1/DCI[1]/EAUX1[1]

HD2/DCI[2]/EAUX1[2]

HD3/DCI[3]/EAUX1[3]

HD4/DCI[4]/EAUX1[4]

HD5/DCI[5]/EAUX1[5]

HD6/DCI[6]/EAUX1[6]

HD7/DCI[7]/EAUX1[7]

HD8/DCI_FDS/EAUX2[0]

HD9/EAUX2[1]

HD10/EAUX2[2]

HD11/EAUX2[3]

HD12/EAUX2[4]

HD13/EAUX2[5]

HD14/EAUX2[6]

HD15/EAUX2[7]

214

IC19

NC7SZ125

B

CHIP

VCC33

VC33

VC33

VC33

ES6008

ES6018

ES6028

ES6038

VC33

FREQ SOURCE

DCLKINPUT OR CRYSTALOSC

DCLKINPUT OR CRYSTALOSC

DCLKINPUT OR CRYSTALOSC

DCLKINPUT AND CRYSTALOSC

MULTIPLL0(pin33)

4.250

reserved

bypass

3.75

4.5

reserved

3.50

VCC33

130

148

157

159

164

VC33

VC33

VC33

VC33

VC33

Pull high TDMDX

to select 8-bit

ROM boot, pull

low to select

16-bit ROM boot

2526282930

31

TDMFS

TDMDR

TDMCLK

TDMTSC

TDMDX/RSEL

Pull high ES60x8 pin 41 to use

DCLK for clock source, no need

for XIN/XOUT crystal circuitry

PLL3(pin41)

CLK SOURCE

DCLK INPUT1

CRSTAL OSC

0

PLL1(pin36)

PLL2(pin32)

0

0

0

0

1

1

0

01

1

11

1

1

VCC33P

VCC33E

111

AVCC(PLL)

AVCC(VDAC)

0

1 NA

0

0

1

104

FB2 FB

FB3 FB

1

18

596875929951104

VC33

VC33

VC33

VC33

VC33

ES60x8

VSS

VSS

VSS

NC/CAMVS

42

VCC

CAMYUV0

CAMYUV1

202

203

R214

4.7K,0603

AVSS(VDAC)

112

AVSS(PLL)

52

8

17

VSS

VSS

VSS

34

43

60

67

R221 0,0603

VSS

VSS

VSS

VSS

76

84

91

Frequency

114.75

27

101.251

121.5

NA

94.5

108

9

183

193

201

VC33

VC33

VC33

VSS

VSS

VSS

VSS

VSS

VSS

129

98

103

120

138

147

156

PRST#AUX3

R220 4.7K,0603 UM

R217 4.7K,0603 UM

C

R44

INSTALL

INSTALL

INSTALL

REMOVE

VCC

VCC

R1

OPEN

(4.7K)

R7

4.7K,0603

VCC25

35

83

121

13927172

44

VC25

VC25

VC25

VC25

VC25

VC25

VC25

PCLK2XSCN/CAMYUV4

PCLKQSCN/CAMYUV5/AUX3[2]

HSSCN/CAMYUV7/EAUX3[0]

VSSCN/CAMYUV6/EAUX3[1]

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

163

171

177

184

192

200

208

PRST# 4

VCC33

C

MULTI

DCLKINPUT

NA

X4

X4

NA

X4

NA 108.0MHz

X3.5

33.3MHz

VCC

R2

R3

4.7K,0603

4.7K,0603

R8

R9

NC

NC

(4.7K)

(4.7K)

IC9

ES60x8

39

MCLK

40

TBCK

32

TWS/SEL_PLL2

33

TSD0/SEL_PLL0

36

TSD1/SEL_PLL1

37

TSD2

38

TSD3

47

RBCK

46

RWS

45

RSD

YUV0/CAMYUV2

YUV1/VREF

YUV2/CDAC

YUV3/COMP

YUV4/RSET

YUV5/YDAC

YUV6/VDAC

YUV7CAMYUV3

DCS0

DCS1

DRAS0

DBANK0/DRAS1

DBANK1/DRAS2

DCAS

DSCK/DOE

DSCK

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

DMA9

DMA10

DMA11

DB10

DB11

DB12

DB13

DB14

DB15

AUX0

AUX1

AUX2

AUX3

AUX4

AUX5

AUX6

AUX7

XOUT

NC/APLL

48

C16

OPEN,0603

SCAP2-06

DWE

DQM

41

116

117

119

118

106

107

108

109

110

113

114

115

100

97

72

73

74

69

71

70

101

102

53

54

55

56

57

58

61

62

63

64

65

66

77

DB0

78

DB1

79

DB2

80

DB3

81

DB4

82

DB5

85

DB6

86

DB7

87

DB8

88

DB9

89

90

93

94

95

96

160

161

162

165

166

167

168

169

49

XIN

50

SPDIF/SEL_PLL3

FREQ

108.0MHz

108.0MHz

116.7MHz

VCC

R4

4.7K,0603

SPDIF

DSCLK

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

DMA9

DMA10

DMA11

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

R39 33,0603

R40 33,0603

R41 33,0603

R45 33,0603

R47 33,0603

XOUT

27pF,0603

CRYSTALOSC

VCCV

27MHZ

27MHZ

27MHZ

27MHZ

R6

R10

33,0603

NC

(4.7K)

R19 33,0603

R21 33,0603 UM

R22 33,0603 UM

R29 33,0603

R30 33,0603

VCC

R37

R38

1K,0603

1K,0603

AUX0

AUX1

AUX2

AUX3

AUX5 2

XIN

L5

R48 1M,0603

X1 27M

C17

3.3uH

R51 33,0603

C18

27pF,0603

Option to use 27MHz crystal at XIN/XOUT for clock

generation, need to pull low ES60x8 pin 41, no need

for DCLK portion OSC circuitry

FB1 FB

MCLK 2

C3

OPEN,0603

SCAP2-06

R15 OPEN,0603

R16 OPEN,0603

MICMUTE

EAUX30

EAUX31

R24 270,0603

RN1 33x4

1 2

3 4

5 6

7 8

RN2 10x4

7 8

5 6

3 4

1 2

RN3 10x4

1 2

3 4

5 6

7 8

RN4 10x4

1 2

3 4

5 6

7 8

SERIAL EEPROM

VCC

IC21

8

7

6

24C01A

C15

10pF,0603

27/33M

FB4 3.3UH

C250 1000PF

D

VCC

SPDIF1 3

MICMUTE 3

HSYN

VSYN

EAUX30 2

EAUX31 2

C12 0.1uF,0603

MA0

MA1

MA2

MA3

DB[0..15]

VCC

WC

SCL

GNDSDA

D

C4

OPEN,0603

SCAP2-06

TWS 2

TSD0 2

TSD1 2

TSD2 2

RBCK 2

RWS 2

VCC33E

R25 0,0603

R27 33,0603

R28 0,0603

R32 68,0603

MA[0..11]

15pF,0603

MA7

MA6

MA5

MA4

MA11

MA10

MA9

MA8

1

S0

2

S1

3

S2

45

R42 4.7K,0603

R46 33,0603

VFD+REMOTE INTERFACE

TBCK 2

C9

0.1uF,0603

C14

VCC

CVBS and

S-VIDEO

VDAC

CV

Y

YDAC

C

CDAC

UDAC

R5

75,0603

R14

75,0603

R17

75,0603

R23

75,0603

CON3

+5V

1

IR

2

GND

3

VFD-CLK

4

VFD-CS

5

VFD-DATA

6

HDR1x 6 (2.54mm)

64M SDRAM

32M SDRAM BA0=0

32M SDRAM BA0=1

32M SDRAM BA1=0

32M SDRAM BA1=1

CVBS and COLOR

DIFFERENCE

DCLK

CKE

-CS0

-RAS0

-CAS

-WE

BANK0

BANK1

R,G,B

CV

Y

PB

PR

L1 2.4UH

C1

470pF,0603

L2 2.4UH

C5

470pF,0603

L3 2.4UH

C7

470pF,0603

L4 2.4UH

C10

470pF,0603

IC7

MA0

23

A0

MA1

24

A1

MA2

25

A2

MA3

26

A3

MA4

29

A4

MA5

30

A5

MA6

31

A6

MA7

32

A7

MA8

33

A8

MA9

34

A9

MA10

22

A10

MA11

35

A11

38

CLK

37

CKE

19

CS

18

RAS

17

CAS

16

WE

DQMX

15

DQML

39

DQMH

20

BA0

21

BA1

36

NC

40

NC

4Mx16 SDRAM (9ns)

32/64MBIT SDRAM

R310

R312

R313

CLOSE

CLOSE

OPEN OPEN

CLOSE OPEN

OPEN

OPEN

OPEN

CLOSE

OPEN

OPEN

CLOSE

CLOSE

OPEN

OPEN

G

R

B

C2

470pF,0603

C6

470pF,0603

C8

470pF,0603

C11

470pF,0603

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VCC

VCC

VCC

VCCQ

VCCQ

VCCQ

VCCQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

OPEN

OPEN

OPEN

OPEN

CLOSE

E

E

VIDEO OUT

VDAC

YDAC

CDAC

UDAC

VCCV

D1

1N4148,LL-34

D3

1N4148,LL-34

D5

1N4148,LL-34

D7

1N4148,LL-34

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

1

14

27

3

9

43

49

6

12

46

52

28

41

54

R308R311

OPEN

OPEN

OPEN

CLOSE

OPEN

VCC33

R306

CLOSE

OPEN

OPEN

CVBS 3

LUMA 3

CHROMA 3

U 3

VCCV

D2

1N4148,LL-34

D4

1N4148,LL-34

VCCVVCCV

D6

1N4148,LL-34

D8

1N4148,LL-34

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

R307

OPEN

CLOSE

OPEN

OPENOPEN

OPEN

Page 9

A

B

C

D

E

2.5V

VCC

FB

FB20

IC1

AME1117-ADJ,SOT-223

FB21

FB

3

D12

D13

NC

NC

C83

4 4

DECOUPLING CAPACITORS

3 3

47uF/16V

VCC25

VIN

ADJ/GND

1

No need to install

ATC117 circuitry

if JS4provide

2.5V

VOUT

ATC1117

2

R206

150,0603 1%

1%

(OPEN OHM)

R207

91,0603 1%

1%

(0 OHM)

VCC25

C230

100uF/16V

(100UF)

47uF/16V

C79

+12V -12V

47uF/16V

VCCAVCC

VCC

-12V

+12V

C78

C234

220uF/16V

VCC33PVCC33E

5V5V

C229

220uF/16V

VCC25

VCC25

R235

56 4/1W

R237

470

C154

100UF/16V

NC

FB15

FOR S/N

VCC

CON6

NC

9

2.5V

8

FB

+5V

TP11

FB22

GND

7

6

5

4

3

2

1

2.54MM 9PIN

GND

GND

GND

-12V

+12V

+5V

+5V

R55 33 OHM

MCLK1

-REST1

TBCK

TBCK1

TWS

TWS1

R56 33 OHM

TSD01

ML

EAUX311

AUX51

EAUX401

R57 33 OHM

MC

R58 33 OHM

MD

R59 33 OHM

ZERO

R60 NC

R61 0

MCLK-

R13NC

R62NC

R139NC

U6

2CH DAC

2

SCKI

7

RSTB

14

BCKIN

16

LRCIN

15

DIN

4

ML/I2S

5

MC/IWL

6

MD/DM

8

ZERO

3

NC

1

NC

17

MUTE

18

MODE

AVCC

VOUTL

VOUTR

AGND

DGND

VCC_DAC

C235

10UF

19

VDD

11

L

12

R

9

AVCM

13

CAP

C19

10UF

10

20

(ZENER DIODE)

C20

0.1UF,0603

5V6 2/1W

8050,SOT-23

Q26

1 3

2

ZD1

C21

C22

0.1uF,0603

0.1uF,0603

VCC33

C35

0.1uF,0603

C46

0.1uF,0603

C55

10uF/16V

2 2

1 1

VCC33 VCC

C61

C60

0.1uF,0603

0.1uF,0603

C24

C23

0.1uF,0603

0.1uF,0603

ES60x8

C36

0.1uF,0603

C47

0.1uF,0603

C56

10uF/16V

SDRAM EPROM

C62

0.1uF,0603

C25

0.1uF,0603

C37

0.1uF,0603

C48

0.1uF,0603

C57

10uF/16V

C63

0.1uF,0603

VCC

24C01

C71

0.1uF,0603

C26

0.1uF,0603

C38

0.1uF,0603

C49

0.1uF,0603

C64

0.1uF,0603

C27

0.1uF,0603

C39

0.1uF,0603

C50

0.1uF,0603

C65

10uF/16V

C28

10uF/16V

C40

0.1uF,0603

C51

0.1uF,0603

C66

10uF/16V

VCCA

0.1uF,0603

0.1uF,0603

0.1uF,0603

C72

0.1uF,0603

C29

C30

10uF/16V

C41

C42

0.1uF,0603

C52

C53

0.1uF,0603

C67

0.1uF,0603

WM8746

C73

0.1uF,0603

0.1uF,0603

C68

10uF/16V

C74

0.1uF,0603

C32

C31

10uF/16V

C75

10uF/16V

ML

R148 33,0603

MC

R147 33,0603

MD

R141 33,0603

ZERO

ZERO3

R160

R156 0

MCLKTBCK

TWS

TSD0

R65 33,0603

TSD11

R66 33,0603

TSD21

NC

R26

NC

VCC_DAC

NC

NC

R163

R162

R63 OPEN,0603

R64 0,0603

6-CHANNEL

AUDIO OUT

WOLFSON 6-CHANNEL AUDIODAC

NC

IC11

1

DVDD

R161

11

DGND

12

LATCH/12S

13

SCLK/IWL

14

SDIN/DM0

9

MUTE

8

MODE

10

LRCLK2

2

MCLK

3

BCLK

4

LRCLK

5

DIN0

6

DIN1

7

DIN2

WM8746,SSOP

AVDD1

AVDD2

AGND1

AGND2

OUT0L

OUT0R

OUT1L

OUT1R

OUT2L

OUT2R

GR0

GR1

GR2

CAP

15

28

20

24

26

22

18

25

27

21

23

17

19

16

0.1uF,0603

VCC_DAC

C75

10uF/16V

AOUT0L 3

C33 10uF/16V

L

R

C58

C59

10uF/16V

C34 10uF/16V

C43 10uF/16V

C44 10uF/16V

C45 10uF/16V

C54 10uF/16V

AOUT0R 3

AOUT1L 3

AOUT1R 3

AOUT2L 3

AOUT2R 3

ESS CONFIDENTIAL

The information has been checked and is believed to be reliable. However, no responsibility is assumed for inaccuracies. Circuit diagrams are provided as a means of illustrating typical applications; consequently complete information for construction purposes is not necessarily given. ESS reserves the right to make changes at any time in order to improve the design.

A

B

C

D

E

Page 10

A

R82

10K,0603

R97

10K,0603

R104

10K,0603

R110

10K,0603

C92

1000pF,0603

C99

1000pF,0603

C103

1000pF,0603

C109

1000pF,0603

R83

3.3K,0603

R89

18K,0603

R98

3.3K,0603

R99

18K,0603

R105

3.3K,0603

R106

18K,0603

R111

3.3K,0603

R112

18K,0603

C88

AOUT2R2

4 4

AOUT1R2

68nF +/-10%,0603

C90

68nF +/-10%,0603

C96

68nF +/-10%,0603

C98

68nF +/-10%,0603

3 3

AOUT1L2

C106

68nF +/-10%,0603

AOUT2L2

C107

68nF +/-10%,0603

2 2

R114

C111

10,0603

10uF/16V

KARR

R117

100K,0603

R119

AOUT0R2

1 1

11K,0603

C118

1000pF,0603

R122

470,0603

VCC

R123

MICMUTE1

AOUT0L2

1K,0603

R124

470,0603

C126

R126

10uF/16V

R131

10K,0603

C136

1000pF,0603

10,0603

R129

100K,0603

KARL

C113

22pF,0603

2

2

C128

22pF,0603

R115

10K,0603

R120

3.3K,0603

R121

18K,0603

Q10

9014,TO-92

1 3

13

Q11

9014,TO-92

R127

10K,0603

R132

3.3K,0603

R133

18K,0603

3

2

5

6

3

2

5

6

+12V

-12V

C89

150pF,0603

+12V

-12V

C97

150pF,0603

+12V

-12V

C102

150pF,0603

+12V

-12V

C108

150pF,0603

84

V+

V-

84

V+

V-

84

V+

V-

84

V+

V-

3

2

IC16-1

KA4558,SOP-8

1

IC16-2

KA4558,SOP-8

7

IC15-1

KA4558,SOP-8

1

IC15-2

KA4558,SOP-8

7

+12V

-12V

C114

150pF,0603

5

6

C129

150pF,0603

84

V+

V-

+12V

-12V

IC17-1

KA4558,SOP-8

1

84

V+

V-

Rs_OUT

Ls_OUT

LFE_OUT

C_OUT

IC17-2

KA4558,SOP-8

7

C84

10uF/16V

C93

10uF/16V

C100

10uF/16V

C104

10uF/16V

C110

10uF/16V

C125

10uF/16V

B

R77

QUIET

QUIET

QUIET

QUIET

QUIET

QUIET

10,0603

R79

100K,0603

R92

10,0603

R93

100K,0603

R101

10,0603

R102

100K,0603

R107

10,0603

R108

100K,0603

R113

10,0603

R116

100K,0603

R125

10,0603

R128

100K,0603

R81

470,0603

R95

470,0603

R103

470,0603

R109

470,0603

R118

470,0603

R130

470,0603

C86

22pF,0603

C94

22pF,0603

C101

22pF,0603

C105

22pF,0603

C112

22pF,0603

C127

22pF,0603

RS

Q3

2

2N3904,TO-92

1 3

LS

Q6

2

2N3904,TO-92

1 3

CVBS1

LUMA1

CHROMA1

SUB

Q7

2

2N3904,TO-92

1 3

CC

Q8

2

2N3904,TO-92

1 3

KARL

KARR

FR

Q9

2

2N3904,TO-92

1 3

+12V

FL

Q12

2

2N3904,TO-92

1 3

-12V

CVBS

ON/OFF

0.1uF,0603

0.1uF,0603

+5VA

ZERO2

TP10

TP9

EARPHONE

CON1

GND

1

2

GND

3

LOUT

4

ROUT

5

5 PIN

R169

OPEN

R165

OPEN

C120

C119

0.1uF,0603

C130

C131

0.1uF,0603

1

VCC

TP7

C121

0.1uF,0603

C132

0.1uF,0603

1N4148,LL-34

R84

1K,0603

R87

1K,0603 UM

R90

470,0603

T8

+12V

C87

220uF/16V

C122

10uF/16V

C133

10uF/16V

D10

1

1

FB16 FB

C76

0.1UF

1

6

5

4

3

FB17 FB

C

2

J1

6

5

4

3

FB18 FB

C123

10uF/16V

10uF/16V

D

1

13

Q4

8550,TO-92

D11

1N4148,LL-34

R73

4.7R

R74

4.7R

1

10uF/16V

+5VA

1

C85

100uF/16V

13

Q2

2

8550,TO-92

QUIET

1

-12V

R88

100K,0603

J2C

FL

FR

RCA CONN 6

R68 3.6K

FB4

8.2UH

R75 1K

C69

220UF/10V

C80

100UF/10V

GNDA

C70

220UF/10V

R76

68K

VCC

C116

C117

0.1uF,0603

VCC

FB5

1

FB

C115

10uF/16V

R67 68K

234

R138 3.6K

R69 51K

6781

5

C77

IC13PT2308L

220UF/10V

GNDA

R70

51K

VCC

C82

R33

FL

10K

10UF

R34

1K

C81

R35

FR

10K

10UF

SPDIF11

J3

1

1

2

2

3

3

4

4

OPT

VSYN

HSYN

D9

R78

1N4148,LL-34

R80

6.8K,0603

1

2.2K,0603

+5VA

R85

1K,0603

1

2

Q5

2N3904,TO-92

MUTE CIRCUIT

1 3

78

78

9

9

2 1

2 1

R71

1K

R72

1K

C124

10uF/16V

C134

C135

10uF/16V

VCC

1

R86

10M,0603

IC14B

3 4

C91

0.1uF,0603

74F04

1

R91

1M,0603

65

65

8

8

10

10

7

7

J4

RCA CONN

123

14

J2A

LS

LS

RS

RS

RCA CONN 6

HSYN

VSYN

VCC33

R213 1K

+12V

R211

2.2K

R210 1K

R209 1K

1

EAUX401

IC14C

5 6

74F04

coaxial

R96

91,0603

optic

coaxial

VDAC

CDAC

YDAC

UDAC

HSYN

VSYN

GNDV

R208

2.2K

Q1

23

3906

1

0V------CVBS

3V------RGB

RGB/VCBS#

SCART_TV

0V--TV

6V--AV 16:9

R185

12V--AV 4:3

2.2K

Q23

Q18

1

3904

3904

2 3

2 3

GND

1

CC

SUB

1

FR

R100

68,0603

R94

330,0603

CC

TP4

IC14D

9 8

74F04

SUB

TP6

FL

UDAC

SCART_TV_SEL

YDAC

CDAC

RGB/CVBS#

VDAC

SCART_TV

E

TP5

Y

V

C95

0.1uF,0603

J2B

RCA CONN 6

TP3

TP2

TP1

GNDV

1 2

11 10

13 12

CON8

7

6

5

4

3

2

1

2.0MM 7PIN

2.0MM 11PIN

IC14A

74F04

IC14E

74F04

IC14F

74F04

CVBS

GND

R/V

G/Y

B/U

HSYNC

VSYNC

CON7

FR

1

GND

2

FL

3

GND

4

B/U

5

ASPECT1

6

G/Y

7

R/V

8

RGB/CVBS

9

CVBS

10

SCART/TV

11

A

B

C

D

E

Page 11

5

R20 NC

D5V

IC8

5

6

7

8

9

10

11

12

13

C137

0.1uF,0603

SA12

4

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

14151617181920

SD1

A12

DQ1

DGND

SA16

-ROMWE

SA15

P35_S

123

303132

A16

A15

A17

NC1

VDD

WE_

SA14

29

A14

SA13

28

A13

SA8

27

A8

SA9

26

A9

SA11

25

A11

LOE

24

23

22

21

SA10

SD7

120pF,0603

47pF,0603

200pF,0603

10uF/16V

DGND

LOE 1

SA[0..16]1

SD[0..7]1

AGND

AGND

RFDSLV

A5V

+

R145

2K,0603

R146

2K,0603

0.1uF,0603

AGND

RFDSLV

SCO

SCO

C169

C145

C146

C160

C242

OE_

A10

CE_

DQ7

DQ2

GND

DQ3

DQ4

DQ5

DQ6

SD5

SD3

SD6

SD4

SD2

AGND

D D

SST39SF020-PLCC

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

SD0

C C

B B

A A

4.7uF,0805

4.7uF,0805

VRD

C162

C161

0.1uF,0603

AGND

VRA

C172

C171

0.1uF,0603

AGND

R137 0,0603

DGND

SA16

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA12

SA15

SA14

SA13

SA8

SA9

SA11

SA10

C138 1nF,0603

C140 10nF,0603

C141 3300pF,0603

C142 3300pF,0603

C143 0.1uF,0603

RFOP

RFON

LDO1

LDO15

LDO2

LDO25

4

27nF,0603

AGND

VCC3

-ROMWE

P35_S

VDD

LOE

SD7

SD6

SD5

SD4

SD3

SD2

SD1

SD0

JITFO

LPFO

C144

3.3VA

R144

6.2K,0603,1%

VCC3

VDD

RFDSLV

SCO

RFOP

RFON

L7

10uH

3

DA17

DA07

DA27

CS1FX#7

CS3FX#7

INTRQ

DMAACK#

RXD

TXD

P30

P31

VCC3

DGND

163

INT1#

164

P34

165

RD#

166

P10

167

P11

168

P12

169

P13

170

VCC2

171

P14

172

P15

173

P16

174

P17

175

AH12

176

AH15

177

ROMWE#

178

P35

179

VSS1

180

AH14

181

AH13

182

VDD1

183

AH8

184

GND1

185

AH9

186

AH11

187

PSEN#

188

AH10

189

ADL7

190

VCC1

191

ADL6

192

ADL5

193

ADL4

194

ADL3

195

ADL2

196

ADL1

197

ADL0

198

PLLVSS

199

PLLVCC

200

AVSS1

201

JITFO

202

LPFO

203

AVCC1

204

RFDSLV

205

SCO

206

AGFU

207

AGFI

208

AGFR

209

AVSS2

210

OSP

211

OSN

212

AVCC2

213

RFOP

214

RFON

215

AVSS3

216

IREF

AGND

AGND

3.3VA

R150

27,0603

ec

Q13

2SB1132R

R154

27,0603

ec

L6

10uH

Q14

2SB1132R

b

b

162

INT0#

VRD

123

C158

1uF,0603

161

VSS2

VRA

VRAVRD

C170

1uF,0603

C187

1uF,0603

156

155

157

158

159

160

P30

P31

ALE

WR#

CSEL

AVCC3

DVDRFIN

DVDRFIP

DVDINA

DVDINB

43756789

A

C

B

A 5C 5

B 5

C159

1uF,0603

RF

RF 5

AGND

R151

2.7K,0603

R155

2.7K,0603

VDD

DA1

DA2

DA0

CS1FX#

CS3FX#

154

153

152

151

150

149

148

147

145

144

143

146

DA2

DA0

DA1

VCC3

VDD2

GND2

DASP#

DVDINC

LDOCD

LDODVD

INTRQ

PDIAG#

CS3FX#

CS1FX#

DVDIND

CDC/SC

101112131415161719182224232021282526273229313435394038414244454347484950515246

D

D 5

HFE

H 5F 5E 5G 5

DMAACK#

CDD/SD

CDA/SA

CDB/SB

PEAK

RFRPSLV

RFRPDC/BD

RFRPAC/BD

IDSUBO

IDSUBI

PEAK

RFRP

C157

C156

1nF,0603

3.9nF,0603

G

1 2 3

B C E

2SB1132R(SOT89)

INTRQ 7

DMAACK# 7

IORDY 7

DIORD# 7

DIOWR# 7

IORDY

DD0

DIORD#

DD15

DD1

DIOWR#

DD14

DD13

135

142

140

139

138

133

137

141

136

134

DD0

DD1

DD14

DD15

IORDY

DIORD#

DMARQ

DIOWR#

VCC4

DD13

VSS3

VT7208

216-PIN LQFP

LDO2

TNI

FLVL

FEO

AVSS4

TPI

MDI1

CSO

CEC

MDI2

LDO1

30

FEO

MDI1

MDI2

FLVL

CSO

C163

3300pF,0603

MDI 5

VRD

DD2

132

DD2

AVCC4

TEZILP

131

TEO

DD12

130

GND3

TEZILP

33

DPD1

DPD2

DD3

128

129

DD3

DD12

VDD3

TEO

AVSS5

DPD2

VRD

DD11

127

126

VSS4

DPD1

36

DD4

DD11

AVCC5

C164

0.1uF,0603

DD6

DD9

DD10

DD5

123

125

124

122

121

DD5

DD4

DD9

DD10

DPDVCC

AVSS6

DPDVSS

FMO

TRO

FMO

FOO 6

TRO 6

FMO 6

DGND

VCC3

R134

10K,0603

PRST#

DD7

DD8

DRST#

TRAYOUT#

117

119

120

118

116

115

DD8

DD7

DD6

VCC5

PRST#

HRST#

TRO

DMO

ADBG1

FOO

AVCC6

ADBG2

DGND

DMO

FOO

ADBG2

ADBG1

ADBG2

ADBG1

DMO 6

C173

15pF,0603

C174

15pF,0603

114

113

IEC

DACVCC

TRAYOUT#

XTALVSS

XTALO

XTALI

XTALI

XTALO

VCC3

FGIN

HRFZC

X2

33.8688MHz

DRST# 7

PRST# 1

112

109

110

111

LO

RO

DACVREF

GIO7/IOCS16#

XTALVCC

FGIN

HRFZC

53

54

DMOEN

DMOEN 6

R153

0,0603

DD[0..15]

DACVSS

TRAYIN#

OUTTRAY

DMOEN

DGND

VSS5

LIMIT#

EJECT#

PLAY#

INTRAY

GIO3

VCC6

GIO2/EA

VDD4

GIO5

GND4

GIO4

GIO6

GIO1

GIO0

VSS6

MA3

MA4

MA2

MA5

MA1

MA6

VCC7

MA0

MA7

MA8

RAS#

WE#

VSS7

CASH#

CASL#

MD7

MD8

MD6

MD9

VCC8

MD5

MD10

MD4

MD11

MD3

MD12

VSS8

MD2

MD13

MD1

MD14

MD0

MD15

R152

1M,0603 UM

LED

OE#

XTALI

XTALO

IC6

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

CASL#

CASH#

WE#

OE#

RAS#

DD[0..15] 7

DGND

TRAYIN#

OUTTRAY

VCC3

LIMIT#

INTRAY

VCC3

R219

10K,0603

VCC3

OUTTRAY 6

INTRAY 6

LED

GIO2/EA

VDD

GIO5

GIO5 6

GIO7

GIO1

GIO0

SMA3

SMA4

SMA2

SMA5

SMA1

SMA6

SMA0

SMA7

SMA8

RAS#

OE#

WE#

CASH#

CASL#

SMD7

SMD8

SMD6

SMD9

SMD5

SMD10

SMD4

SMD11

SMD3

SMD12

SMD2

SMD13

SMD1

SMD14

SMD0

SMD15

RN5

33x4

R149 33,0603

D5V

FB12

2

123456

LED

GIO6 5

12

34

56

78

FB

0.1uF,0603

78

RN8

33x4

VCC3

LCAS

UCAS

WE

OE

RAS

C175

0.1uF,0603

TRAYOUT# 6

C240

10uF/16V

TRAYIN# 6

LIMIT# 6

R224

10K,0603

GIO7 7

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

C177

C176

0.1uF,0603

2.7K,0603

R212

D14

1N4148

+

IC5

29

LCAS

28

UCAS

13

WE

27

OE

14

RAS

SOJ40

16

A428316S-25

A0

17

A1

18

A2

19

A3

I/O10

22

A4

I/O11

23

A5

I/O12

24

A6

I/O13

25

A7

I/O14

26

A8

I/O15

1 21

VCC GND

GND2VCC2

20

GND3

VCC3

A428316S

D5V

VCC3

GIO1

GIO0

DGND DGND

SMD0

2

I/O0

SMD1

3

I/O1

SMD2

4

I/O2

SMD3

5

I/O3

SMD4

7

I/O4

SMD5

8

I/O5

SMD6

9

I/O6

SMD7

10

I/O7

SMD8

31

I/O8

SMD9

32

I/O9

SMD10

33

SMD11

34

SMD12

36

SMD13

37

SMD14

38

SMD15

39

356

40

DGND

1

DRST# 7

R210(DEL)

0,0603 UM(DEL)

PRST#

PRST# 1

R258(DEL)

4.7K,0603(NC)

DGND

R140

10K,0603

EXT.

GIO2/EA

C148

0.1uF,0603 UM

0.1uF,0603 UM

0.1uF,0603

C179

0.1uF,0603 UM

0.1uF,0603

C149

C165

0.1uF,0603

C180

INT.

R143

10K,0603

0.1uF,0603 UM

C166

0.1uF,0603

C181

0.1uF,0603

C151

VDD VDDVDDVDD VDD

0.1uF,0603

R142

10K,0603

3.3VA

C147

0.1uF,0603

VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3

C178

0.1uF,0603 UM

C167

0.1uF,0603

C182

0.1uF,0603 UM

C153

0.1uF,0603 UM

C168

DGND

C183

0.1uF,0603

3.3VA3.3VA3.3VA3.3VA3.3VA

C139

0.1uF,0603

C184

0.1uF,0603 UM

C155

0.1uF,0603

C185

3.3VA

AGND

C13

0.1uF,0603

DGND

5

4

3

2

1

Page 12

VRAA5V

C188

0.1uF,0603

AGND AGND

C189

0.1uF,0603

For PCB View

P1

P26

A5V

R49

47K,0603

8050,TO-92

GIO64

R50

10K,0603

Q17

2

AGND

R44

0,0603

1 3

R43

100K,0603

Q16

2SK3018

Q15

2SK3018

For PUH View

28

31

2

AGND

VR_DVD

31

2

AGND

VR_CD

27

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

For PUH View

R215

0,0603

R216

100,0603

VRA

R31

1k,0603

AGND

A5VVRA

VR_DVD

A5V

VR_CD

A5V

R36

NC

H C B

F

F- TR+CON7

F+

LD01

E

DG

TR-

TR-

TR- 6

TR+

TR+ 6

F-

F- 6

F+

F+ 6

LDO1

LDO1 4

MDI

MDI

A

LD02

LDO2

RF

B

E

D

C

H

G

A

F

RF

MDI 4

LDO2 4

B 4

E 4

D 4

C 4

H 4

G 4

A 4

F 4

RF 4

Page 13

C198

33uF/16V

OUTTRAY4

D5V

D5V

+

C199

0.1uF,0603

PGND

OUTTRAY INTRAY

R177

100,0603

560,0603

R180

R175

220,0603

2

8550,TO-92

8050,TO-92

2

C200

390pF,0603

13

Q19

Q21

1 3

PGND

13

2

Q20

8550,TO-92

R174

220,0603

LOADLOAD+

8050,TO-92

Q22

2

1 3

R179

560,0603

Replace

the

BA6208

FOO

FOO4

FMO

FMO4

F-5

F+5

C211

33uF/16V

D5V

C238

0.1uF,0603 UM

D5V

+

PGND

C239

100uF/16V

PGND

C213

0.1uF,0603 UM

SPIN+

R170

10K,0603

R172

1.5K,0603

R176

22K,0603

R178

100,0603

C201

390pF,0603

R187

2.2K,0603

R193

2.2K,0603

SLEDSLED+

F+ TR+

VRD

VRD

INTRAY 4

C202

470pF,0603

C206

47000pF,0603

FMSO

C214

10nF,0603

FOSO

R194

8.2k,0603

VRD

PGND

C204

0.1uF,0603 UM

R195

8.2K,0603

PGND

SPIN-

R181

10K,0603

R183

1.5K,0603

R186

22K,0603

PGND PGND

R188

0,0603

VRD

C209

680pF,0603

R198 1,0805

R200 1,0805

R171

1M,0603

D5V

3

+

2

-

PGND

R182

1M,0603

D5V

5

+

6

-

R189 47K,0603

C205 100pF,0603

D5V

D5V

PGND

IC20A

84

1

LM393,SOP-8

IC20B

84

7

LM393,SOP-8

IC4

BA5954FP,Rohm(HSOP-28)

1

VINFC

2

CFCERR1

3

CFCERR2

4

VINSL+

5

VINSL-

6

VOSL

7

VNFFC

8

VCC

9

PVCC1

10

PGND

11

VOSL-

12

VOSL+

13

VOFC-

14

VOFC+

29

PGND

D5V

D5V

GND

GND

30

R173

4.7K,0603

GIO5

R184

4.7K,0603

STBY

BIAS

VINTK

CTKERR1

CTKERR2

VINLD

PREGND

PVCC2

VNFTK

PGND

VOLDVOLD+

VOTKVOTK+

GIO5 4

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PGND

DMOEN

R190 0,0603

R192

47K,0603

R196

0,0603

D5V

R199 1,0805

R201 1,0805

CON4

1

2

3

4

5

5 PIN

CON6

1

1

2

2

3

3

4

4

5

5

6

6

CONN RECT 6

DMOEN 4

VRD

C207 100pF,0603

PGND

TOSO

DMO

L-

PGND

LOADLOAD+

L+

TRAYOUT#

TRAYIN#

SP+

SP-

PGND

VRD

C203

470pF,0603

VRD

SL+

C208

100nF,0603

C215

10nF,0603

TRN

R191

2.2K,0603

R197

5.1K,0603

TRO

SL-

SPINSPIN+

TR-F-

LIM

TRAYOUT# 4

TRAYIN# 4

SPIN+

SPINSLED+

SLEDLIMIT#

TRO

DMO

LIMIT# 4

TRO 4

DMO 4

TR- 5

TR+ 5

Page 14

D5V

642

R15710K,0603

R158

R15910K,0603

135

7 8

RN10 33x4

1

INTRQ4

IORDY4

DIORD#4

DIOWR#4

DA14

DA04

DA24

DMAACK#4

C191 10pF,0603

C193 10pF,0603

C195 10pF,0603

C197 10pF,0603

3

5

7 8

RN12 47x4

7

5

3

1 2

2

4

6

8

6

4

C192 10pF,0603 UM

C194 10pF,0603

C196 10pF,0603

10K,0603

(FOR C-CUBE ONLY)

C65 : 0.47U

DGND

RN7

10Kx4

HIRQ

HIORDY

-HRD

-HWR

HA1

HA0

HA2

C241

0.1uF,0603

DGND

HIRQ 1

HIORDY 1

-HRD 1

-HWR 1

HA1 1

HA0 1

HA2 1

HD[0..15]1 DD[0..15] 4

HD[0..15]

HD7

HD8

HD6

HD9

HD5

HD10

HD4

HD11

HD3

HD12

HD2

HD13

HD1

HD14

HD0

HD15

RN6 33x4

7 8

5

3

1

RN9 33x4

7 8

5

3

1

RN11 33x4

7 8

5

3

1

RN13 33x4

7 8

5

3

1

DD15

DD0

6

DD14

4

DD1

2

DD13

DD2

6

DD12

4

DD3

2

DD11

DD4

6

DD10

4

DD5

2

DD9

DD6

6

DD8

4

DD7

2

DD[0..15]

HD[0..15]

-HRST

-HWR

-HRD

HIORDY

HIRQ

HA1

HA0

-HCS1

-HCS3

HA2

-HIOCS16

HD[0..15]

DRST

DWR#

DRD#

DIORDY

DIRQ

DACS1#

DACS3#

DIOCS16#

R202

4.7K

CON2

1 2

HD15

R203

4.7K

HD13

HD12

HD11

HD10

HD9

HD8

VCCVCC

RESET GND

3 4

D7 D8

5 6

D6 D9

7 8

D5 D10

9 10

D4 D11

11 12

D3 D12

13 14

D2 D13

15 16

D1 D14

17 18

D0 D15

19 20

GND KEY

21 22

DRQ GND

23 24

IOW GND

25 26

IOR GND

27 28

IOCHRDY BALE

29 30

DACK GND

31 32

IRQ14 IOCS16

33 34

A1 RESERVED

35 36

A0 A2

37 38

CS0 CS1

39 40

ACTIVITY GND

IDE

HD0

HD1HD14

HD2

HD3

HD4

HD5

HD6

HD7

FB14 FERB

VCC

DRST#

-IOCS16

R164

DGND

R166 33,0603

R167 33,0603

R168 0,0603

R218 47,0603

10K,0603

CS3FX#4

CS1FX#4

DRST#4

GIO74 -HIOCS16 1

-HCS3

-HCS1

-HIOCS16

-HCS3 1

-HCS1 1

-HRST 1

Page 15

VDD=2.0V FOR CORE

VDD

FB13 FB

C221

+

10uF/16V

DGND

IC3

AME1117-ADJ,SOT-223

2

R204

1K,0603

C227

10uF/16V

VOUT

+

DGND

ADJ/GND

1

VIN

DGND

3

C222

47uF/16V

R205

560,0603

+

DGND

VCCA

VCC

FB7

FB

D5V FOR Spindle

Driver, uP and

EEPROM

A5V FOR PUH and ALPC BJT

FB11 FB

D5V

FB

FB10

FB8

+

FB

DGND DGND

+

C219

C220

220uF/16V

22uF/16V

DGND DGND

A5V

C217

+

220uF/16V

IC2

AME1117-3.3V,SOT-223

3

VIN

VOUT

ADJ/GND

1

2

C226

0.1uF,0603

+

DGND

C224

10uF/16V

FB6

FB

FB9

FB

FB19

FB

C216

10uF/16V

C223

10uF/16V

VCC3

VCC=3.3V FOR PAD

+

C218

0.1uF,0603

DGNDAGND

DGND

3.3VA

3.3VA=3.3V FOR Aanalog CKT

+

C225

0.1uF,0603

DGNDDGND

VCC33

Page 16

A

VCC

J1

LD8

LD10

LD12

LD14

LCS1#

4 4

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

LD9

LD11

LD13

LD15

LCS2#

R3

OPEN

R8

OPEN

SD_CMD

MS_SDIO

FEMALE SOCKET CONN 2X10

JS2

DRST#

DD15 DD0

DD14

DD13

DD12

DD11

DD10

DD9

DD8

3 3

DWR#

DRD#

DIORDY

DACK#

DIRQ

DA1

DA0

DACS1#

1 2

RESET GND

3 4

D7 D8

5 6

D6 D9

7 8

D5 D10

9 10

D4 D11

11 12

D3 D12

13 14

D2 D13

15 16

D1 D14

17 18

D0 D15

19 20

GND KEY

21 22

DRQ GND

23 24

IOW GND

25 26

IOR GND

27 28

IOCHRDY BALE

29 30

DACK GND

31 32

IRQ14 IOCS16

33 34

A1 RESERVED

35 36

A0 A2

37 38

CS0 CS1

39 40

ACTIVITY GND

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DIOCS16#

DA2

DACS3#

HEADER-2X20 (2.54mm)

HEADER FROM MPEG BOARD

VCC

2 2

DRST#

DD15

DD14

DD13

DD12

DD11

DD10

DD9

DD8

DWR#

DRD#

DIORDY

DACK#

DIRQ

DA1

DA0

DACS1#

DASP

1 1

JS3

1 2

RESET GND

3 4

D7 D8

5 6

D6 D9

7 8

D5 D10

9 10

D4 D11

11 12

D3 D12

13 14

D2 D13

15 16

D1 D14

17 18

D0 D15

19 20

GND KEY

21 22

DRQ GND

23 24

IOW GND

25 26

IOR GND

27 28

IOCHRDY BALE

29 30

DACK GND

31 32

IRQ14 IOCS16

33 34

A1 RESERVED

35 36

A0 A2

37 38

CS0 CS1

39 40

ACTIVITY GND

HEADER-2X20 (2.54mm)

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DIOCS16#

PDIAG

DA2

IDE_CS3#

HEADER TO HDD/DVD LOADER

B

LD8

LD9

LD10

LD11

LD12

LD13

LD14

LD15

LCS2#

CF_CD#

SD_CD#

SD_WP#

SM_RB#

SM_WPD#

SM_CD#

MS_INS

LCS1#

11

13

15

17

19

SM_MUX

DACS3#

SM_MUX

R15

12 11

2.2K

VCC

JP2

1 2

JUMPER

(default close)

JP3

JUMPER

ext. 5V

(default not supplied)

VCC33

U1

3

D0

4

D1

7

D2

8

D3

13

D4

14

D5

17

D6

18

D7

1

OC

11

CLK

74F374

U3

2

1A1

4

1A2

6

1A3

8

1A4

2A1

2A2

2A3

2A4

1

1G

2G

74LS244

10

9 8

U2C

IDTQS3125-S1

13

U2D

IDTQS3125-S1

1

2

Q3

FDN360P

PWR_CTL2

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q2

FDN360P

DS

2

5

6

9

12

15

16

19

18

1Y1

16

1Y2

14

1Y3

12

1Y4

9

2Y1

7

2Y2

5

2Y3

3

2Y4

VCC

IDE_CS3#

(SOIC-14)

SM_CE#

DS

PWR_CTL1

CARD_VCC

R1 10 OHM

R2 10 OHM

MS_EN#

SM_MUX

SD_EN#

R4 10 OHM

PWR_CTL1

PWR_CTL2

LD8

LD9

LD10

LD11

LD12

LD13

LD14

LD15

VCC

R10

10K

R14

5.1K

CF_VCC

C

MS_BS

MS_SCLK

VCC

C1

0.1UF

VCC

VCC

C11

10UF

C5

0.1UF

SD_CLK

R5 10K

R6 10K

CARD_VCC

RP1

1 8

2 7

3 6

4 5

OPEN

(51Kx4)

CARD_VCC

RP2

1 8

2 7

3 6

4 5

10Kx4

VCC VCC33

U4

3

Vin

C10

10UF

AMS1117-33

VCC

C4

0.1UF

VCC33

CARD_VCC

DD0

DD1

DD2

DD3

SM_RB#

SM_WPD#

SD_WP#

VCC33

VCC33

Vout

GND/Vadj

R11 10K

R13 10K

R17 10K

R18 10K

2

1

DD4

DD5

10UF

C9

SD_EN#

MS_EN#

SD_CD#

SD_WP#

DD1

DD0

SD_CLK

SD_CMD

DD3

DD2

DD12

DD11

DD13

DD10

DD14

DD9

DD15

DD8

DA2

DWR#

SM_RB#

DA1

DRD#

DA0

SM_CE#

SM_WPD#

SM_CD#

MS_BS

MS_SDIO

MS_INS

MS_SCLK

D

1

2 3

U2A

IDTQS3125-S1

4

5 6

U2B

IDTQS3125-S1

CARD_VCC

C6

0.1UF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

4-IN-1 SOCKET

(SD/MMC + SM + MS)

R7

0 OHM

R9

0 OHM

C7

0.1UF

CN1

GND_SM_SD

SD_CD#

SD_WP#

SD_DAT1

SD_DAT0

SD_CLK

SD_CMD

SD_DAT3

SD_DAT2

VCC_SM_SD

GND_SM

SM_D4

SM_D3

SM_D5

SM_D2

SM_D6

SM_D1

SM_D7

SM_D0

VCC_SM

SM_WP#

SM_WE#

SM_RB#

SM_ALE

SM_RE#

SM_CLE

SM_CE#

SM_WP_SW

SM_CD#

VCC_SM_MS

MS_BS

MS_SDIO

MS_PIN5

MS_INS

MS_PIN7

MS_SCLK

GND2_ALL

SD_CMD

MS_SDIO

C8

0.1UF

COMPACT FLASH HEADER

JS1

1

GND

26

CD1

2

D03

27

D11

3

D04

28

D12

4

D05

29

D13

5

D06

30

D14

6

D07

31

D15

7

CS0

32

CS1

8

A10

33

VS1

9

ATASEL

34

IORD

10

A09

35

IOWR

11

A08

36

WE

12

A07

37

INTRQ

13

VCC

38

VCC

14

A06

39

CSEL

15

A05

40

VS2

16

A04

41

RESET

17

A03

42

IORDY

18

A02

43

INPACK

19

A01

44

REG

20

A00

45

DASP

21

D00

46

PDIAG

22

D01

47

D08

23

D02

48

D09

24

ICOCS16

49

D10

25

CD2

50

GND

CON50

JP1

1

2

JUMPER

OPEN = SLAVE

CLOSE = MASTER

E

CF_VCC

DD11

DD3

DD12

DD4

DD13

DD5

DD14

DD6

DD15

DD7

DACS1#

IDE_CS3#

DRD#

DWR#

DIRQ

DRST#

DIORDY

DA2

DA1

DA0

DASP

DD8

PDIAG

DD9

DD0

DD10

DD1

DIOCS16#

DD2

CF_CD#

C2

0.1UF

C3

0.1UF

VCC33

R16

10K

A

B

C

D

E

Page 17

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

1 196-547150100 SCART CONNECTION WIRE WITH PCS

POLYBAG (12" X 5" X 0.04)

W/PRINTING PUNCH HOLE

2 201-003033760 POWER CORD VDE APP. 76" PCS

W/BUSHING TO 2 PIN HOUSING

PITCH=8.0mm BLACK COLOUR

3 213-201280020 DVD MECHANISM (KHM-280AAA)SONY PCS

4 214-821010200 DVD PLASTIC LOADER ASSEMBLY PCS

(WXD-8210) W/MOTOR FOR SONY

KHM280 PICK-UP

5 303-000004020 CABLE TIE 4" PCS

6 310-700000002 HEAT-SHRINKABLE UL APP. TUBE M

DIA 25mm LENGH 35mm

7 500-030803000 SCREW M3.0 X 8BT SELF-TAPPING PCS

NICHEL PLATE

8 500-031010000 SCREW T3 X 10WT SELF-TAPPING PCS

WASHER HEAD ?0.0mm

9 501-030502000 SCREW M3 X 5B/M MACHINE NICKEL PCS

PLATE

10 501-030603010 SCREW 3 X 6 K/M (BLACK) PCS

11 501-030802000 SCREW M3 X 8B/M MACHINE NICKEL PCS

PLATE

12 501-031002000 SCREW 3 X 10 BM MACHINE NICKEL PCS

13 501-031502000 SCREW 3 X 15 B/M MACHINE PCS

NICKEL

14 602-020010015 PAD CORD 20 X 10 X 1.5mmTHK PCS

15 605-144000030 RUBBER FOOT DIA 14.4mm X 3mm PCS

SILICON WHITE COLOUR

16 720-022300000 DOOR LEFT SPRING WIRE DIA PCS

0.3mm

17 720-022301000 DOOR RIGHT SPRING WIRE DIA PCS

0.3mm

18 731-120301030 BACK PANEL 0.7mm THK. EG PLATE PCS

5.1CH W/SCART W/O OPTICAL OUT

W/BLACK S.S. W/O LICENCE

19 732-120300020 TOP COVER 0.6mm THK. EG PLATE PCS

SPRAY SILVER

20 733-120300003 BOTTOM TRAY 0.7mm THK. PCS

EG PLATE FOR DV-XXXF W/BRACKET

21 800-022301010 FRONT CABINET WITH CF CARD PCS

BRIGHT SILVER (A78-030) SPRAY

W/D.GREY (PMS 432C) S.S

22 807-022300010 CD DOOR BRIGHT SILVER(A78-030) PCS

Page 18

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

SPRAY

23 824-022300010 POWER KNOB W/CHROME PCS

24 825-022300011 FUNCTION KNOB W/CHROME PCS

25 835-022302030 DISPLAY LENS (DV-223E) L.GREY PCS

LENS (921543L) W/SILVER

(PMS 877C) ROADSTARD DESIGN

26 836-022301030 DOOR LENS(L.GREY LENS 921543L) PCS

W/SILVER (PMS 877C) S.S

27 844-020300000 MPEG PCB HOLDER ABS MOLD GREY PCS

28 844-020301000 POWER PCB HOLDER ABS MOLD GREY PCS

29 886-020300010 PLASTIC FOOT W/BRIGHT SILVER PCS

(A78-030) SPRAY

30 887-022300010 CD DOOR DECO W/CHROME PCS

31 888-022300010 LEFT DECO W/CHROME PCS

32 888-022301010 RIGHT DECO W/CHROME PCS

33 901-022320120 GIFT BOX ROADSTAR DESIGN PCS

(DVD-2053S) "7621800023292"

34 902-022300060 INSTRUCTION MANUAL ROADSTAR PCS

DESIGN(DVD-2053S)5.1CH W/SCART

(ENG/GER/FR/IT/SP/PORT)

35 903-030300110 WARRANTY CARD ROADSTAR DESIGN PCS

(MULTI-LANG) 2003 YR

36 906-468284003 CARTON SHEET 468 X 284 X 3mm PCS

37 919-022301020 SERIAL NO. LABEL ROADSTAR PCS

DESIGN (DVD-2053S)

"MRR00096700001"

38 919-030102010 LASER BEAM LABEL YELLOW B/G PCS

W/BLACK TEXT STD W/COATING

39 919-022303010 LASER CAUTION LABEL YELLOW PCS

B/G W/BLACK TEXT W/COATING

HARVARD DESIGN (2004YR)

40 919-030399130 AC INPUT LABEL ROADSTAR DESIGN PCS

"AC 230V" 50HZ

41 919-030104010 CLASS 1 LABEL B/G W/BLACK TEXT PCS

W/COATING MULTI LANGUAGE STD

42 919-030303020 CAUTION LABEL ROADSTAR PCS

DESIGN

43 919-030314010 DATE CODE LABEL STANDARD "MMY" PCS

44 920-022300030 RATING LABEL ROADSTAR DESIGN PCS

(DVD-2053S)

45 930-022301000 POLYFOAM (FRONT) PCS

46 930-022302000 POLYFOAM(LEFT) PCS

47 930-022303000 POLYFOAM(RIGHT) PCS

Page 19

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

48 960-100504010 POLYBAG(10"x5") PCS

49 960-120504010 POLYBAG (12" X 5" X 0.04) PCS

W/PRINTING PUNCH HOLE

50 960-151004010 POLYBAG 15" X 10" OPEN PCS

W/HOLES W/RECYCLE MARK

51 960-172004010 POLYBAG (17" X 20" OPEN) PCS

W/HOLES W/PRINTING

52 D01-020301023 MPEG BOARD ASS'Y 5.1CH PCS

VT7208 (SERVO) + ES6018 (MPEG)

W/SCART FOR DV-203/213/223E

0,1 100-203E41340 MAIN PCB VT7208+ES6018 PCS

DV-203E

0,2 101-082241224 I.C. T224162B (SOJ-40) PCS

256Kx16 DRAM (TM)

0,3 101-082402096 I.C. AT24C02N-10SI-2.7 PCS

0,4 101-082880096 I.C. AT49F8192AT-70TC 8M PCS

0,5 101-082911217 I.C. A290011TL-70(PLCC-32) PCS

AMIC 1M FLASH

0,6 101-083472073 I.C. TL3472 (SOP-8) OP. AMP. PCS

(TI)

0,7 101-084162229 I.C. 4MX16T2-7 SDRAM PCS

0,8 101-084558022 I.C. C4558D DUAL POERATON AMP PCS

S0-8

0,9 101-085654202 I.C. AT5654H (SMD) PCS

0,1 101-086018068 **I.C. ES6018 (SMD) PCS

0,11 101-087208079 I.C. VT7208S (LQFP-216) PCS

0,12 101-087404031 I.C. 74HCU04D PCS

0,13 101-088746221 I.C. WM8746 6CH AUDIO DAC PCS

0,14 101-098860226 I.C. FS8860-CJ (SOT-223) PCS

0,15 102-003904001 TRANSISTOR 3904 (SOT-23) SMD PCS

0,16 102-003906001 TRANSISTOR 3906 PNP (SOT-23) PCS

SMD

0,17 102-008050001 TRANSISTOR IMTX8050 NPN PCS

(SOT-23) SMD

0,18 102-008550001 TRANSISTOR 8550 PNP (SOT-23) PCS

SMD

0,19 102-009014001 TRANSISTOR 9014C SOT23 PCS

0,2 102-021132001 TRANSISTOR 2SB1132 SOT-346 PCS

SMD

0,21 102-063018000 TRANSISTOR 2SK3018 PCS

0,22 104-134001010 DIODE 1N4001 PCS

0,23 104-144148080 DIODE IN4148 SMD LL-34 PCS

0,24 104-410056010 ZENER DIODE 5.6V 1/2W PCS

Page 20

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

0,25 113-000274200 27MHz CRYSTAL HC-49/US FUND PCS

LP-3.5-27-000F-20

0,26 113-338005000 CRYSTALS 33.8688 MHz HC-49US PCS

LC=16PF

0,27 117-101302300 **COIL 10uH (SMD 0603) PCS

0,28 117-124102300

0,29 130-015603100

0,3 130-100003840

0,31 130-100103840

0,32 130-100113840

0,33 130-100123840

0,34 130-100133840

0,35 130-100143840

0,36 130-100153840

0,37 130-100163840

0,38 130-100173840

0,39 130-100233840

0,4 130-101523840

0,41 130-101833840

0,42 130-102213840

0,43 130-102223840

0,44 130-102233840

0,45 130-102703840

0,46 130-102713840

0,47 130-102723840

COIL 2.4UH ±5% (SMD 0603)

RESISTOR CF 56 OHM 1/4W ±5%

RESISTOR 0 1/16W ±5%

(SMD 0603)

RESISTOR 1 1/16W ±5%

(SMD 0603)

RESISTOR 10 1/16W ±5%

(SMD 0603)

RESISTOR 100 1/16W ±5%

(SMD 0603)

RESISTOR 1K 1/16W ±5%

(SMD 0603)

RESISTOR 10K OHM 1/16W ±5%

(SMD 0603)

RESISTOR 100K 1/16W ±5%

(SMD 0603)

RESISTOR 1M 1/16W ±5%

(SMD 0603)

RESISTOR 10M 1/16W ±5%

(SMD 0603)

RESISTOR 2K 1/16W ±5%

(SMD 0603)

RESISTOR 1.5K 1/16W ±5%

(SMD 0603)

RESISTOR 18K 1/16W ±5%

(SMD 0603)

RESISTOR 220 1/16W ±5%

(SMD 0603)

RESISTOR 2.2K 1/16W ±5%

(SMD 0603)

RESISTOR 22K 1/16W ±5%

(SMD 0603)

RESISTOR 27 OHM 1/16W ±5%

(SMD 0603)

RESISTOR 270 1/16W ±5%

(SMD 0603)

RESISTOR 2.7K 1/16W ±5%

(SMD 0603)

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

Page 21

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

0,48 130-103303840

0,49 130-103313840

0,5 130-103323840

0,51 130-104703840

0,52 130-104713840

0,53 130-104723840

0,54 130-104733840

0,55 130-105123840

0,56 130-105613840

0,57 130-106223840

0,58 130-106803840

0,59 130-106823840

0,6 130-107503840

0,61 130-108223840

0,62 130-109103840

0,63 130-130113840 RESISTOR 10 OHM X4 SMT Network PCS

0,64 130-130143840

0,65 130-133303840

0,66 130-134703840

0,67 140-401102323

0,68 140-401202323

0,69 140-401302283

RESISTOR 33 1/16W ±5%

(SMD 0603)

RESISTOR 330 1/16W ±5%

(SMD 0603)

RESISTOR 3.3K 1/16W ±5%

(SMD 0603)

RESISTOR 47 1/16W ±5%

(SMD 0603)

RESISTOR 470 1/16W ±5%

(SMD 0603)

RESISTOR 4.7K 1/16W ±5%

(SMD 0603)

RESISTOR 47K 1/16W ±5%

(SMD 0603)

RESISTOR 5.1K 1/16W ±5%

(SMD 0603)

RESISTOR 560 1/16W ±5%

(SMD 0603)

RESISTOR 6.2K 1/16W ±5%

(SMD 0603)

RESISTOR 68 1/16W ±5%

(SMD 0603)

RESISTOR 6.8K 1/16W ±5%

(SMD 0603)

RESISTOR 75 OHM 1/16W ±5%

(SMD 0603)

RESISTOR 8.2K 1/16W ±5%

(SMD 0603)

RESISTOR 91 1/16W ±5%

(SMD 0603)

Tesistors (MNR14) 1/16W

RESISTOR 10K OHM X 4 1/16W ±5%

(SMD 0603)

RESISTOR 33 OHM X 4 1/16W ±5%

(SMD 0603)

RESISTOR 47 X 4 1/16W ±5%

(SMD 0603)

CERAMIC CAP 10P 50V ±5%

(SMD 0603)

CERAMIC CAP 100P 50V ±5%

(SMD 0603)

CERAMIC CAP 1000P 50V ±10%

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

Page 22

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

(SMD 0603) X7R

0,7 140-401402043 CERAMIC CAP 0.1u 50V +80-20% PCS

(SMD 0603) Y5V

0,71 140-401502283 CERAMIC CAP 10n 50V X7R +10% PCS

(SMD 0603)

0,72 140-401610183

0,73 140-402202283

0,74 140-412102283

0,75 140-415002323

0,76 140-415102283

0,77 140-422002323

0,78 140-427002323

0,79 140-427302143

0,8 140-433202283

0,81 140-439102283

0,82 140-439202283

0,83 140-447002323

0,84 140-447102283

0,85 140-447302143

0,86 140-468102283

0,87 140-468302143

0,88 141-002204430 ELECT CAP 220uF 16V +80-20% PCS

0,89 141-080104520

0,9 141-110105420

0,91 141-112204320

0,92 141-113304320

0,93 141-114707220

CERAMIC CAP 1uF 16V ±10%

(SMD 0603)

CERAMIC CAP 200p 50V X7R ±10%

(SMD 0603)

CERAMIC CAP 120P 50V ±10%

(SMD 0603)

CERAMIC CAP 15P 50V ±5%

(SMD 0603)

CERAMIC CAP 150P 50V X7R ±10%

(SMD 0603)

CERAMIC CAP 22p 50V NPO ±5%

(SMD 0603)

CERAMIC CAP 27pF 50V NPO ±5%

(SMD 0603)

CERAMIC CAP 0.027UF 50V ±10%

(SMD 0603)

CERAMIC CAP 3300p 50V X7R ±10%

(SMD 0603)

CERAMIC CAP 390P 50V NPO ±10%

(SMD 0603) X7R

CERAMIC CAP 3900P 50V ±10%

(SMD 0603)

CERAMIC CAP 47P 50V ±5%

(SMD 0603)

CERAMIC CAP 470P 50V ±10%

(SMD 0603) X7R

CERAMIC CAP 0.047uF 50V ±10%

(SMD 0603)

CERAMIC CAP 680P 50V ±10%

(SMD 0603)

CERAMIC CAP0.068UF 50V ±10%

(SMD 0603)

ELECT CAP 100uF 16V ±20% (6X7)

ELECT CAP 10uF 25V ±20%(4 X 7)

ELECT CAP 22UF 16V ±20% (4x7)

ELECT CAP 33UF 16V ±20% (4X7)

ELECT CAP 4.7UF 50V ±20% (4X7)

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

PCS

Page 23

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

0,94 141-144704320

ELECT CAP 47UF 16V ±20% (5X7)

PCS

0,95 182-352063B00 FERRITE BEAD(TB36-869568) PCS

0,96 183-020601001 MBW1608-601 2.5A (0603) PCS

FERRITE BEAD

0,97 190-606538000 RCA JACK (RS-653A8-01) PCS

(RCA X 6)

0,98 190-630102000 VIDEO PORT+S-VIDEO(MDW-102/Y) PCS

0,99 190-95AVGQ000 COAXIAL RCA SOCKET (AV+GQ-02) PCS

FOR DV-203

0,1 193-205020000 WAFER 5 PIN, 2mm PITCH PCS

(TRAY IN / OUT)

STRAIGHT TYPE

0,101 193-206020000 WAFER 6P PITCH 2mm PITCH(CON6) PCS

0,102 193-206025000 WAFER 6PIN 2.5MM PITCH (VFD) PCS

STRAIGHT TYPE

0,103 193-207020000 WAFER 7P PITCH 2.0mm PCS

0,104 193-208025000 WAFER 8P 2.5mm PITCH PCS

(CON9) STRAIGHT TYPE

0,105 193-211020000 WAFER 11 PIN 2MM PITCH (SCART) PCS

STRAIGHT TYPE

0,106 193-226050900 FFC SOCKET PITCH=0.5mm 26P PCS

0,107 193-240254000 WAFER 40P PITCH 2.54mm PCS

53 D01-020307003 POWER SUPPLY ASS'Y PCS

EP35G-3.3 (NO EMI PARTS AND

NO POWER SW) STD

54 D01-020309001 MEMORY CARD BOARD ASS'Y PCS

0,1 100-203E42340 MEMORY CARD PCB PCS

0,2 101-080374031 I.C. 74F374D PCS

0,3 101-083125243 I.C. IDTQS3125-S1 QUICK PCS

SWITCH

0,4 101-087424073 I.C. 74LS244 (SO-20) PCS

0,5 101-088860226 I.C. FS8860-3.3CJ (SOT-223) PCS

0,6 102-520338164 P-CHANNEL MOSFET FDN338P PCS

(SOT-23)

0,7 130-100003840

RESISTOR 0 1/16W ±5%

PCS

(SMD 0603)

0,8 130-100113840

RESISTOR 10 1/16W ±5%

PCS

(SMD 0603)

0,9 130-100143840

RESISTOR 10K OHM 1/16W ±5%

PCS

(SMD 0603)

0,1 130-102223840

RESISTOR 2.2K 1/16W ±5%

PCS

(SMD 0603)

0,11 130-105123840

RESISTOR 5.1K 1/16W ±5%

PCS

Page 24

-------------- -- Component -----------------

Leve l No. Name UM

---- ------------------------------------------------ ----- --------------

5.1CH W/SCART W/O OPTICAL SIL.

W/CARD SLOT VDE 230V

(SMD 0603)

0,12 130-130143840

RESISTOR 10K OHM X 4 1/16W ±5%

PCS

(SMD 0603)

0,13 140-401402043 CERAMIC CAP 0.1u 50V +80-20% PCS

(SMD 0603) Y5V

0,14 141-110105420

ELECT CAP 10uF 25V ±20%(4 X 7)

PCS

0,15 190-970001000 CF CONNECTOR TOP H=3.95mm PCS

(148-1111000-01)

0,16 190-970002000 4 IN 1 MEMORY CONNECTOR SMT PCS

/BOTTOM MOUNT (P5S2E930)

0,17 193-213020000 WAFER 13PIN 2.0mm PITCH (DIP) PCS

0,18 193-240254000 WAFER 40P PITCH 2.54mm PCS

55 D01-021304002 SCART PCB ASS'Y (DV-213B) PCS

0,1 100-020305060 DV-203 SCART PCB (NEW) PCS

0,2 190-300109000 SCART SOCKET 21P (CS-109) PCS

0,3 193-211020000 WAFER 11 PIN 2MM PITCH (SCART) PCS

STRAIGHT TYPE

56 D01-022302007 DISPLAY PCB ASS'Y FOR DV-203E PCS

W/O POWER SW

0,1 100-203E01000 DV-203E DISPLAY PCB PCS

0,2 101-080792220 I.C. S0792 (SGNEC) QFP-44 VFD PCS

DRIVERIC

0,3 104-134148010 DIODE SILICON IN4148 PCS

0,4 104-5300004A0 LED 2x5mm RED PCS

0,5 105-010496080 DETECT SENSOR IRM 496V-S PCS

0,6 130-010143000

0,7 130-012233000

0,8 130-018213000

RESISTOR CF 10K 1/8W ±5%

RESISTOR CF 22K 1/8W ±5%

RESISTOR CF 820 1/8W ±5%

PCS

PCS

PCS

0,9 140-001402000 CERAMIC CAP 0.1uF 50V +80-20% PCS

0,1 140-003102200

0,11 141-000103520

CERAMIC CAP 30P 50V ±10%

ELECT CAP 100U 10V ±20%

PCS

PCS

0,12 161-09E050902 VFD (VFD20-0509A) PCS

0,13 175-800005090 TACT SWITCH H=5mm (BLACK) PCS

0,14 198-000003000 BARE WIRE LBS

(1 LBS=273M=4550 LBS PCS)

1PCS=60mm=0.00022 LBS DIA0.6mm

0,15 720-030300000 SPRING DIA 0.4mm PCS

0,16 843-022300000 DISPLAY BRACKET-ABS MOLD. PCS

57 D01-022303107 REMOTE PCB ASS'Y FOR DV-223E PCS

ROADSTAR

0,1 100-030013460 REMOTE PCB (FOR PT2222) PCS

0,2 101-082222092 I.C. PT2222-001 (SMD) PCS

0,3 102-008050002 NPN TRANSISTOR 8050 SORT BY PCS

Page 25