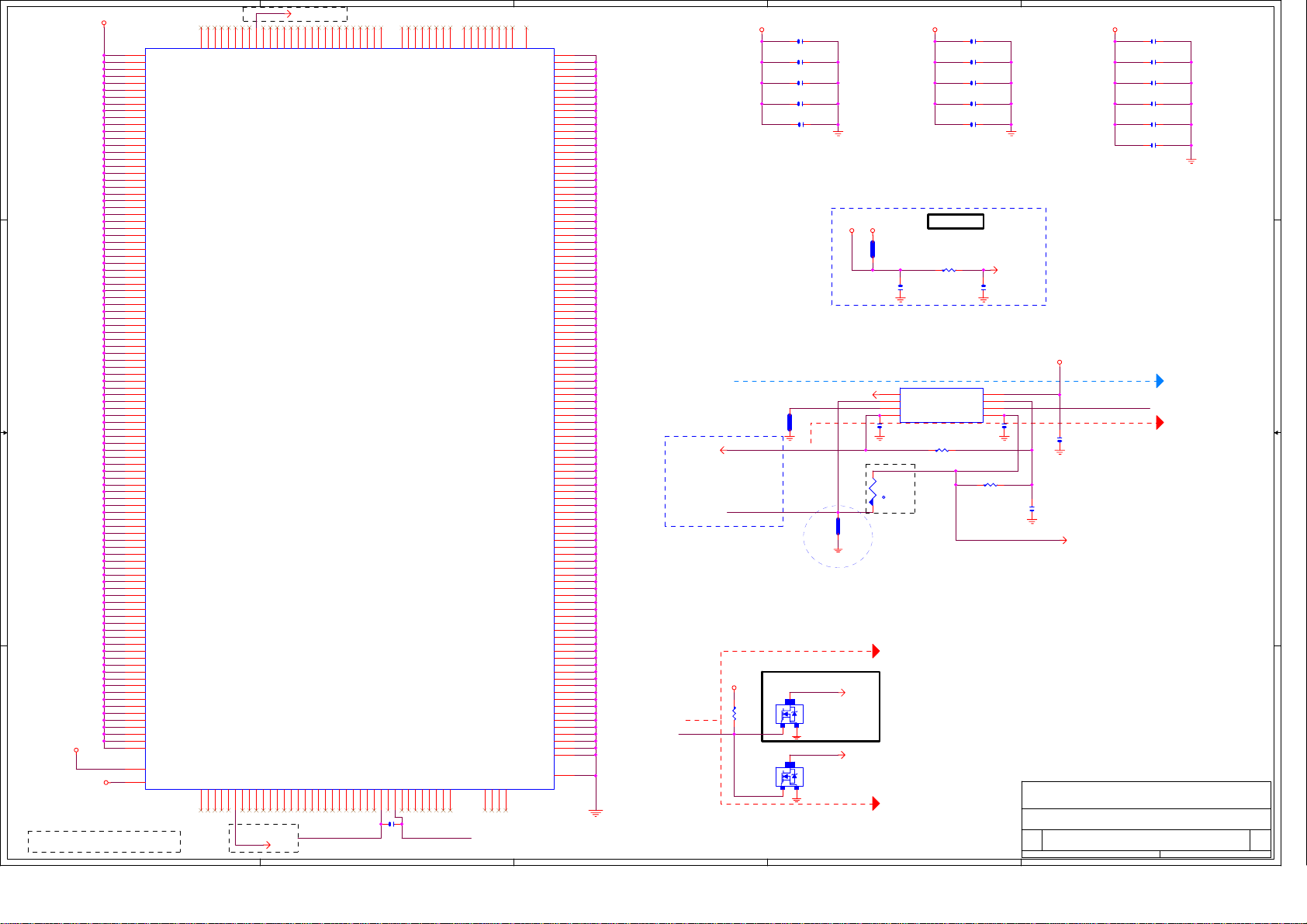

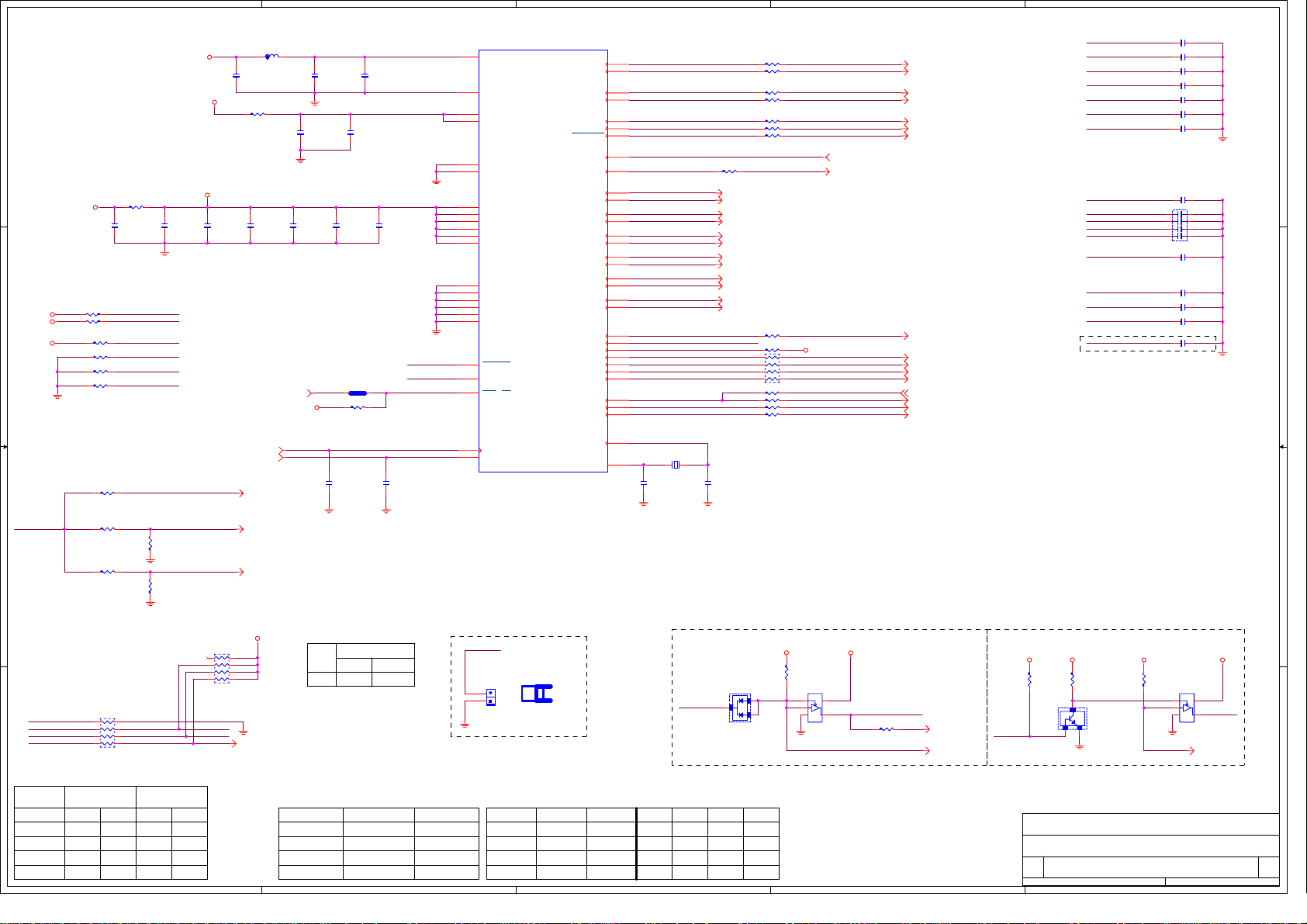

Gigabyte XP-K7VM333 REV.1.0 Schematic

5

4

3

2

1

Model Name: XP-K7VM333

Revision 1.0

D D

SHEET

1

2

3

4,5

6,7,8

9

10,11,12

C C

13,14

15

16

17

18

19

20

B B

21

BOM & PCB MODIFY HISTORY

COVER SHEET

BLOCK DIAGRAM

AMD CPU SOCKET A

KM266 PRO HOST; DDR; AGP,VLINK,POWER/GROUND

CLOCK GENERATOR (RTM360-520)

VT8235/CE (SOUTH BIRDGE)

DDR SDRAM DIMMS 1,2 DDR TERMINATION

AGP SLOT

PCI SLOT 1,2,3

IDE,USB

LPCIO_IT8705

BIOS

COM,PRT,FDD,KB/MS,IR

AC 97 VT1617 CODEC

TITLE

22

23

24

25

26

27

A A

5

28

4

AUDIO JACK,GAME PORT

VT6103L & USB CONNECTOR

PANEL,FANS

DDR POWER

ATX CONN,3VDUAL,VDDQ DC POWER

VCORE PHASE PWM FAIRCHILD FAN5091M

VID,FID CONTROL

3

COMPONENT SIDE

(1 oz. Copper)

GND SIDE

(1 oz. Copper)

VCC SIDE

(1 oz. Copper)

SOLDER SIDE

(1 oz. Copper)

Title

Size Document Number Rev

Custom

星期四, 六月

2

Date: Sheet of

GIGABYTE

COVER SHEET

XP-K7VM333

24, 2004

128

1

1.0

5

4

3

2

1

Model Name: XP-K7VM333

Circuit or PCB layout change for next version

Version:1.0

D D

Date Change Item Reason

2004.05.13 VER: 1.0 PCB GERBER OUT XP-K7VM333

Component value change history

2004.01.13

Date Change Item Reason

Modify from 7VM333RZ 1.0A.0.1 BOM ISSUED.2004.03.22

2004.04.12 1.0A BOM ISSUED.

XP-K7VM333 1.0A NEW BOM AGP 11AC1-05R124-51 Short wire:11NH2-010005-002004.05.20

C C

B B

A A

Title

Size Document Number Rev

Custom

Date: Sheet

5

4

3

2

星期四, 六月

GIGABYTE

BOM & PCB MODIFY HISTORY

XP-K7VM333

24, 2004

1

of

228

1.0

5

4

3

2

1

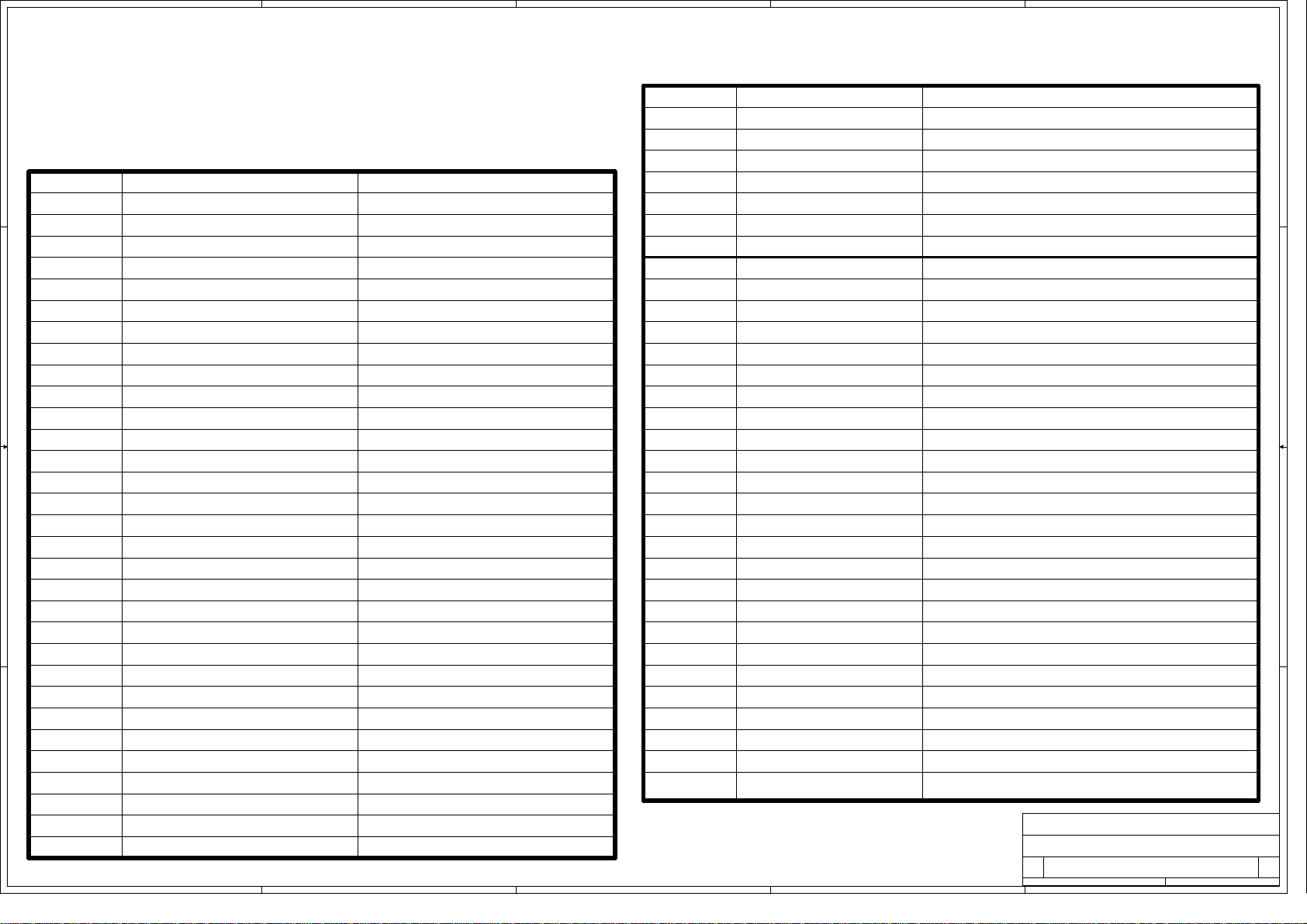

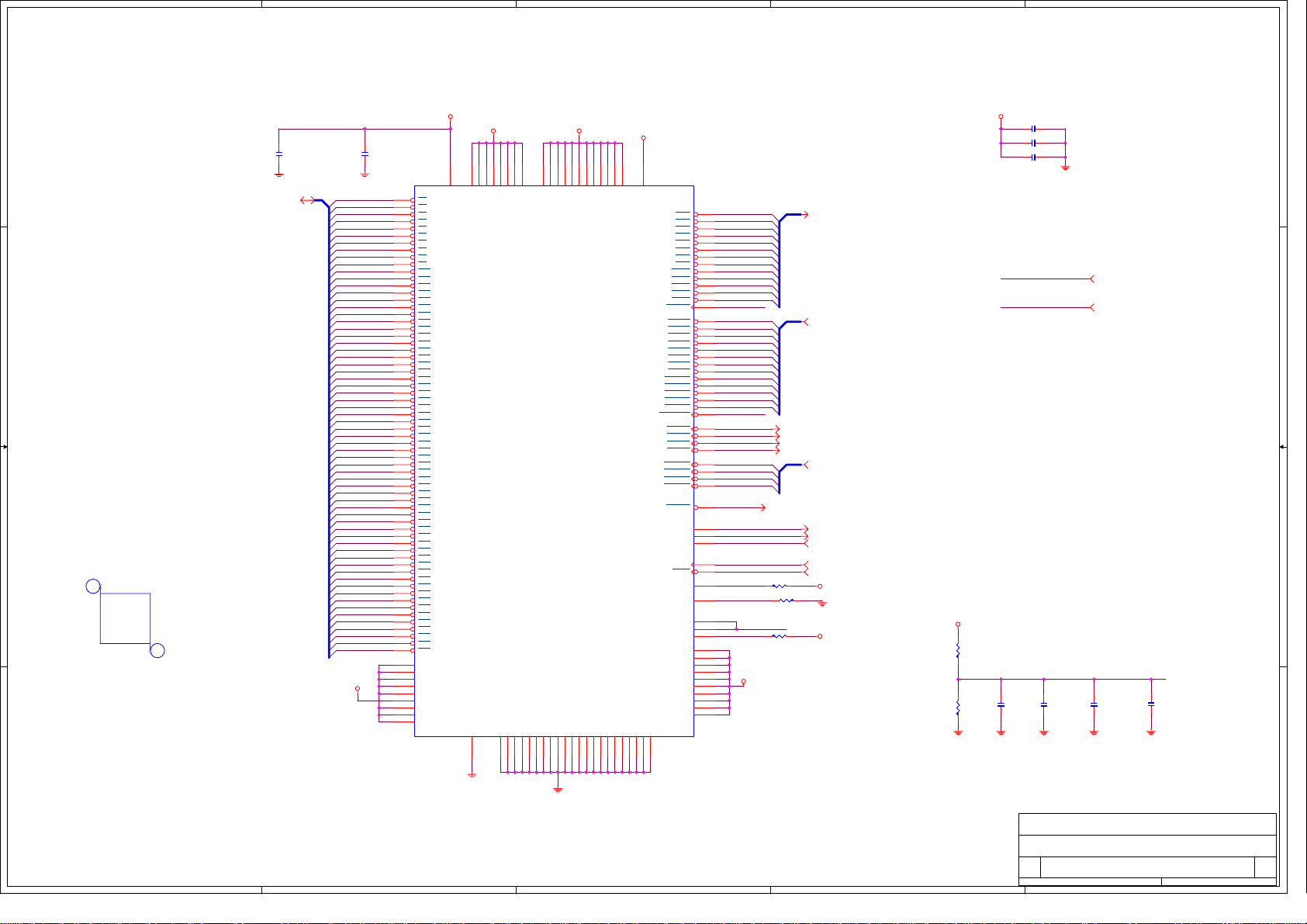

XP-K7VM333 BLOCK DIAGRAM

CLOCK GENERATOR

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

VCC3 = 3.3V

D D

C C

AC97 CODEC VT1617

+12V = 12V

VCC3 = 3.3V

VCC = 5V

B B

AVDD = 5V

AUDIO PORTS :

LIN_ OUT

CD_IN

PAGE 09

AGP SLOT 4X

VDDQ = 1.5V (AGP POWER 4X)

VCC3 = 3.3V

+12V = 12V

3VDUAL = 3.3V

VCC = 5V

USB PORTS 0~3

VCC = 5V

5VSB = 5V

5VUSB = 5V

FRONT AUDIO

LINE_IN

GAME PORT

MIC

PAGE 15

PAGE 19

PAGE 21

PAGE 22

GAD0~31

AD_STB0,-AD_STB0

AD_STB1,-AD_STB1

SBA0~7

SB_STB,-SB_STB

-GBE0~3

ST0~2

AGP BUS

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

VCCA = 2.5V ; 2_5V = 2.5V

PAGE 4, 5

VIA KM266 PRO NORTH BRIDGE

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

DDR25V = 2.5V(SUSPEND POWER)

VDDQ = 1.5V (AGP POWER 4X)

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

VLAD0~7

CONTROL BUS

V LINK

PAGE 6,7,8

VIA VT8235/CE SOUTH BRIDGE

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

3VDUAL = 3.3V(SUSPEND POWER)

VCC3 = 3.3V

RTCVDD = 3.3V

PAGE 10,11,12

PCI BUS

PCI SLOT 1,2,3

+12 = 12V

-12 = -12V

VCC = 5V

VCC3 = 3V

3VDUAL = 3V

PAGE 16

VID0~4

MAA0~15

MDD0~63

-DQSD0~7

MII LAN

PWM/OTHER POWER

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

5VSB,-12V,+12V,VCC,VCC3,3VDUAL

DDRVTT,DDR25V,3VSTR,VCC25

PAGE 25,26,27

DDR SDRAM DIMM X 2

DDR25V = 2.5V(SUSPEND POWER)

DDRVTT = 1.25V

PAGE 13,14

DQM0~7

VT6103L & USB CONN

PAGE 23

IDE Primary and Secondary

VCC = 5V

PAGE 17

BIOS

VCC = 5V

VCC3 = 3V

PAGE 19

LPC BUS

LPC I/O IT8705

AMD K7

VCC = 5V

5VSB = 5V

VBAT = 3V

A A

5

4

FRONT PANEL/FANS

VCC = 5V

5VSB = 5V

+12 = 12V

PVCC = 5V

PAGE 24

3

I/O PORTS :

COMA

LPT

PS2

2

FDD

PAGE 18

PAGE 20

Title

Size Document Number Rev

Custom

星期四, 六月

Date: Sheet of

GIGABYTE

BLOCK DIAGRAM

XP-K7VM333

24, 2004

1

328

1.0

5

4

3

2

1

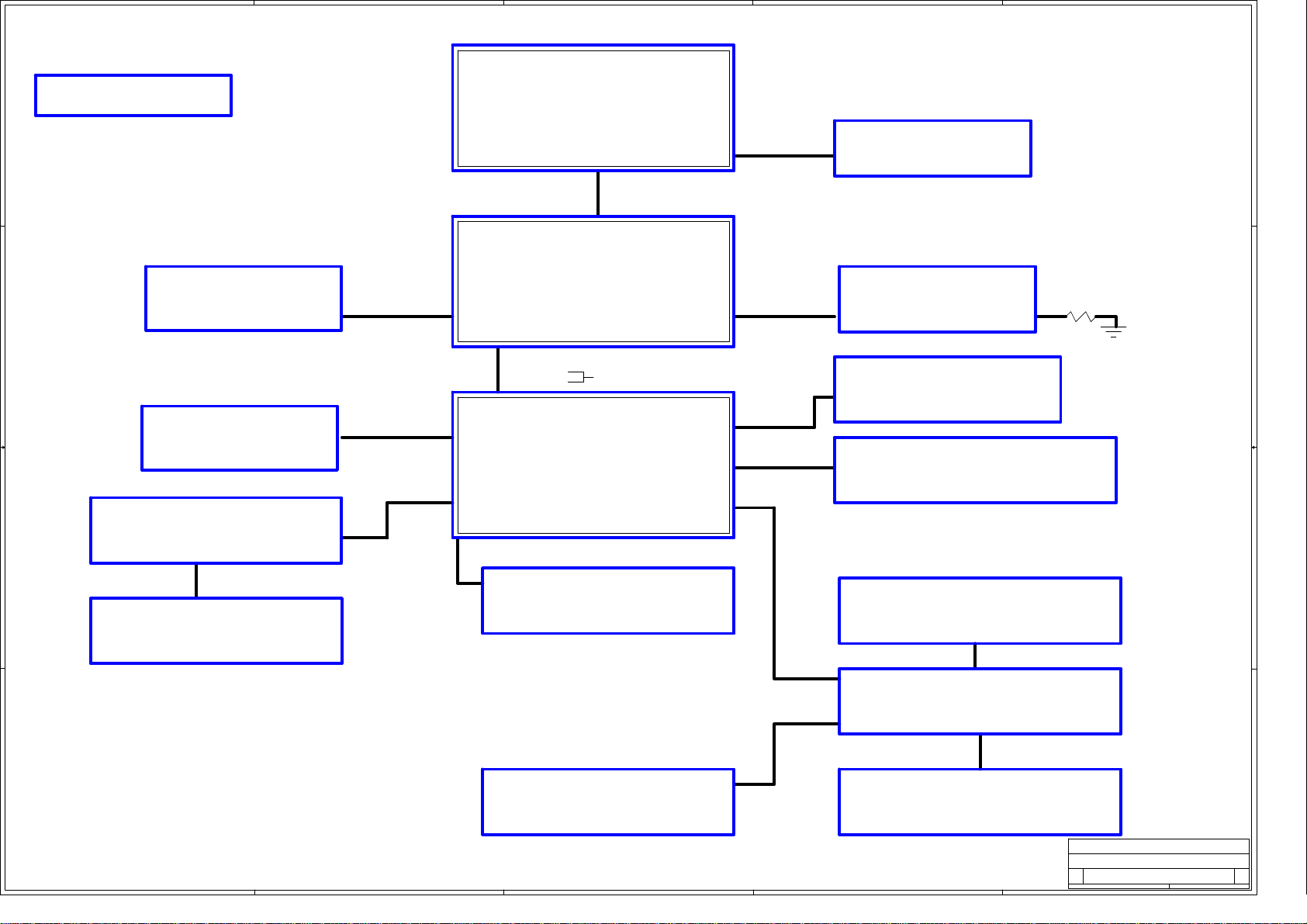

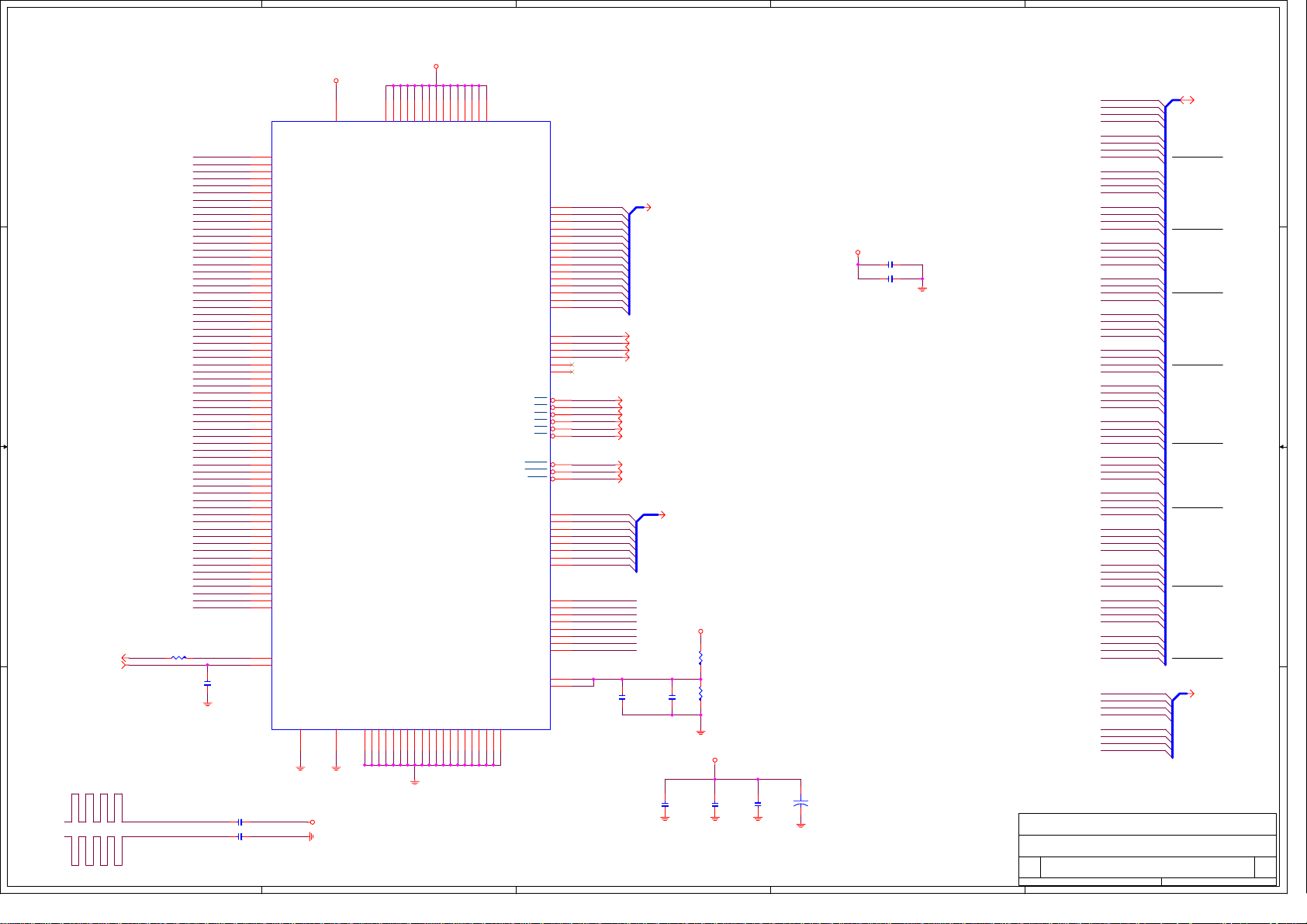

-CPURST

AA35

W37

W35

AA33

AE37

AC33

AC37

AA37

AC35

Q37

Q35

G33

G37

G35

Q33

W33

AN33

AE35

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

Y35

U35

U33

S37

S33

Y37

S35

N37

J33

E37

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

J35

E27

E15

C37

A33

C11

SOCKET_AA

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

0

1

2

3

SOCKETA

4

A20M

FERR

INTR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFBCOREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

Socket_A/White

INIT

NMI

SMI

TCK

-A20M

AE1

FERR

AG1

-CPUINIT

AJ3

INTR

AL1

-IGNNE

AJ1

NMI_SB

AN3

-CPURST

AG3

-SMI

AN5

-STPCLK

AC1

PWK

AE3

PICCLK0

N1

-PICD0

N3

-PICD1

N5

-COREFB

AG13

COREFB

AG11

AN17

AL17

AN19

AL19

K7CLKOUT

AL21

-K7CLKOUT

AN21

AJ13

SYSVREFMODE

AA5

VREFSYS

W5

ZN

AC5

ZN

ZP

TDI

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

ZP

-PLLBYPASS

PLLBYPASSCLK

-PLLBYPASSCLK

PLLMON1

PLLMON2

-PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

-DBREQ

-FLUSH

P_TCK

P_TDI

P_TMS

-P_TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

-AO2

-AO3

-AO4

-AO5

-AO6

-AO7

-AO8

-AO9

-AO10

-AO11

-AO12

-AO13

-AO14

-A20M <10>

-CPUINIT <10>

INTR <10>

-IGNNE <10>

NMI_SB <10>

-CPURST <26>

-SMI <10>

-STPCLK <10>

PWK <26>

PICCLK0 <9>

-PICD0 <10>

-PICD1 <10>

C1 680P/4/X/50V

C2 680P/4/X/50V

VID[4..0]

R20 1K/6/X

R22 1K/6/X

VID[4..0] <28>

-AO[2..14]

-AOCLK

CPUCLK

-CPUCLK

-CDICLK0

-CDICLK1

-CDICLK2

-CDICLK3

-CAICLK

-AO[2..14] <6>

-AOCLK <6>

3

VCORE

R3

60.4/6/1

301/6/1

L17

10nH/6/10

L1

10nH/6/10

L38

10nH/6/10

L5

10nH/6/10

L19

10nH/6/10

FID[0..3]

R6

R4

60.4/6/1

DIC0

C147

5P/4/N/50V

DIC1

C4

5P/4/N/50V

DIC2

C356

5P/4/N/50V

DIC3

C6

5P/4/N/50V

AIC

C148

5P/4/N/50V

FID[0..3] <28>

CPUCLK <9>

-CPUCLK <9>

L18

10nH/6/10

L2

10nH/6/10

L39

10nH/6/10

L6

10nH/6/10

L20

10nH/6/10

-DICLK0 <6>

-DICLK1 <6>

-DICLK2 <6>

close to cpu socket.

-DICLK3 <6>

-AICLK <6>

Put them inside socket462

-P_TRST

P_TDI

P_TMS

P_TCK

-PLLTEST

R19 470/6

-DBREQ

R21 470/6

SCANINTEVAL

SCANCLK1

SCANCLK2

SCANSHIFTEN

PWK

To CPU

AIN0

AIN1

-SDATA0

-SDATA1

-SDATA2

-SDATA3

-SDATA4

-SDATA5

-SDATA6

-SDATA7

-SDATA8

-SDATA9

-SDATA10

-SDATA11

-SDATA12

-SDATA13

-SDATA14

-SDATA15

-SDATA16

-SDATA17

-SDATA18

-SDATA19

-SDATA20

-SDATA21

-SDATA22

-SDATA23

-SDATA24

-SDATA25

-SDATA26

-SDATA27

-SDATA28

-SDATA29

-SDATA30

-SDATA31

-SDATA32

-SDATA33

-SDATA34

-SDATA35

-SDATA36

-SDATA37

-SDATA38

-SDATA39

-SDATA40

-SDATA41

-SDATA42

-SDATA43

-SDATA44

-SDATA45

-SDATA46

-SDATA47

-SDATA48

-SDATA49

-SDATA50

-SDATA51

-SDATA52

-SDATA53

-SDATA54

-SDATA55

-SDATA56

-SDATA57

-SDATA58

-SDATA59

-SDATA60

-SDATA61

-SDATA62

-SDATA63

-CDICLK0

-CDICLK1

-CDICLK2

-CDICLK3

-DIVAL

-DOCLK0

-DOCLK1

-DOCLK2

-DOCLK3

-DOVAL

-AI2

-AI3

-AI4

-AI5

-AI6

-AI7

-AI8

-AI9

-AI10

-AI11

-AI12

-AI13

-AI14

-FILVAL

-SDATA[0..63]<6>

D D

C C

B B

A A

VCORE

-DIVAL<6>

-DOCLK[0:3]<6>

-AI[2:14]<6>

CLKFWDRST<6>

CONNECT<6>

PROCRDY<6>

-SDATA[0..63]

R13 330/6

R16 680/6

R18 680/6

-AI[2:14]

-CAICLK

CLKFWDRST

CONNECT

PROCRDY

R28 330/6

5

RN3

470/8P4R

RN6

330/8P4R

C3

10P/4/X

VCORE

R5

C146

10P/4/X

VCORE

78

56

34

12

78

56

34

12

Title

Size Document Number Rev

2

Date: Sheet

FERR

PLLBYPASSCLK

-PLLBYPASSCLK

K7CLKOUT

-K7CLKOUT

至少

10 mil.

-PICD0

-PICD1

PLLMON1

PLLMON2

-PLLBYPASS

ZN

-CPUINIT

INTR

-FLUSH

NMI_SB

-IGNNE

-A20M

-STPCLK

-SMI

COREFB

-COREFB

ZP

SYSVREFMODE

Custom

星期四, 六月

680/6

R7 1K/6

VREFSYS

24, 2004

100/6/1

R10 330/6

R11 330/6

RN4 680/8P4R

RN5 680/8P4R

VCC3

C

BE

FERR+

2

RN1

1 2

3 4

5 6

7 8

100/8P4R

RN2

1 2

3 4

5 6

7 8

100/8P4R

VCORE

R8

100/6/1

R9

BC1

1U/6/Y/10V

VCC25

R12 56/6

R14 56/6

R15 680/6

R17 40.2/6/1

12

34

56

78

12

34

56

78

R24 8.2K/6

R25 8.2K/6

R26 56/6/1

R27 330/6

GIGABYTE

SOCKETA-1

XP-K7VM333

1

R2

330/6

-FERR <10>

3

Q2

MMBT2222A/SOT23

1

VCORE

VCORE

VCORE

VCORE

VCORE

428

1.0

of

5

VCORE

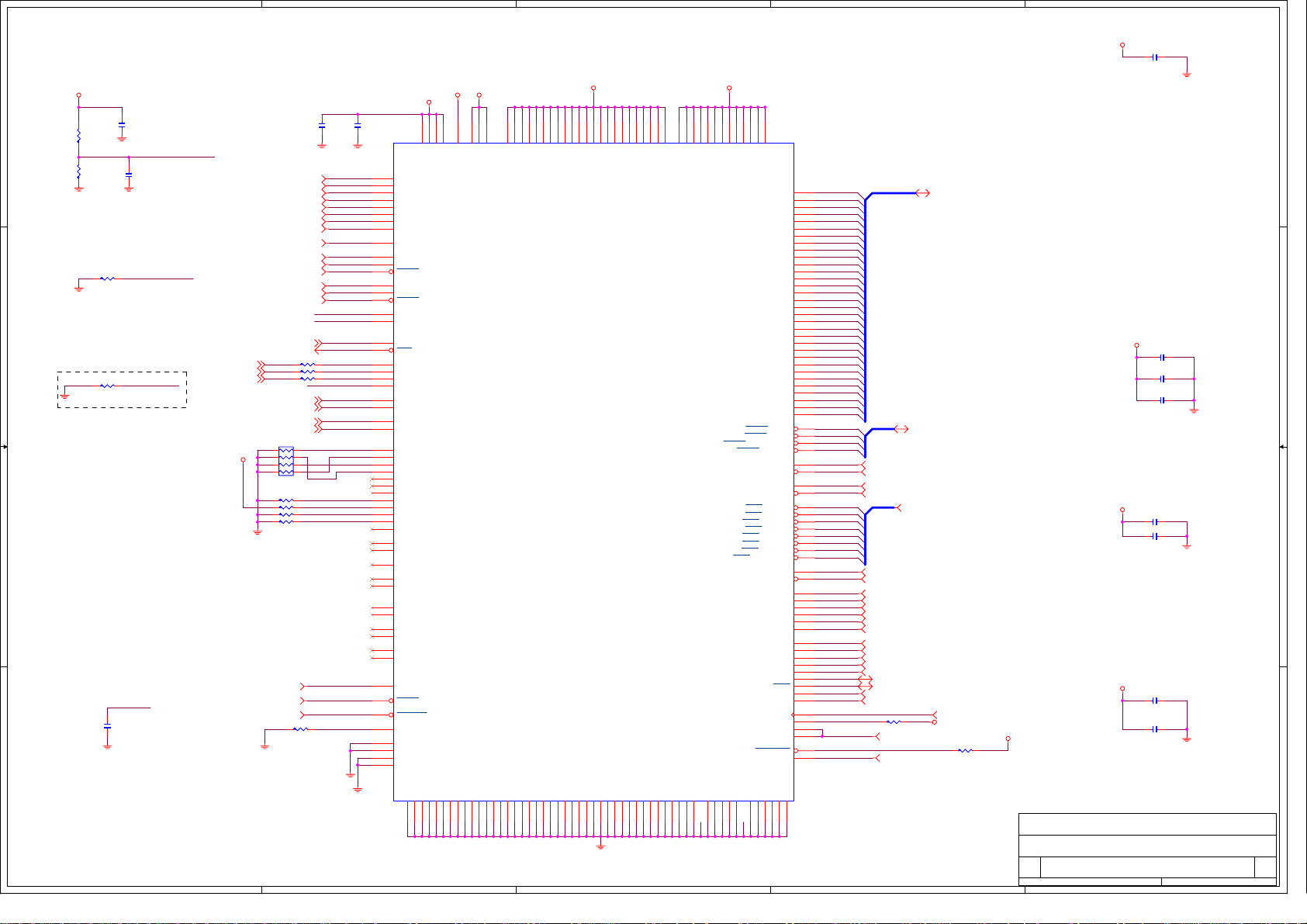

SOCKET_AB

H12

VCC_CORE1

H16

VCC_CORE2

H20

VCC_CORE3

H24

VCC_CORE4

M8

VCC_CORE5

P30

VCC_CORE6

R8

VCC_CORE7

T30

VCC_CORE8

V8

VCC_CORE9

D D

C C

B B

A A

VCORE

PLL25V

AMD ATHLON PROCESSORS MODEL 6

(OR GREATER) THERMAL DIODE

X30

AB30

AF14

AF18

AF22

AF26

AM34

AK36

AK34

AK30

AK26

AK22

AK18

AK14

AK10

AL5

AH26

AM30

AH22

AH18

AH14

AH10

AH4

AH2

AF36

AF34

AD6

AM26

AD4

AD2

AB36

AB34

AB32

X36

X34

AM22

X32

AM18

P36

P34

P32

K36

K34

K32

AM14

D32

D28

AM10

D24

D20

D16

D12

B36

B32

AM2

B28

B24

B20

B16

B12

AJ5

AC7

AJ23

Z8

Z6

Z4

Z2

V6

V4

V2

T36

T34

T32

R6

R4

R2

M4

M6

M2

H4

H2

F36

F34

F32

F28

F24

F20

F16

F12

D8

D4

D2

B8

B4

5

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VCC_Z

VCC_A

REV2.0

AD30

AD8

VCC_SRAM1

NC1

AA31

AC31

VCC_SRAM2

NC2

C_FS_1 <9>

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30F8H10

H28

H30

H32H6H8

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

SOCKETA

POWER & GND

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31J5L31

C11

3300P/X/6/X

THERMDA

C_FS_0 <9>

VCC_SRAM25

NC24

VCC_SRAM26

NC25

K30K8AJ7

VCC_SRAM27

NC27

4

AL7

AN7

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

NC28

NC29

NC30

NC31

NC32

N31

Q31

S31S7U31U7W31W7Y31Y5AG19

4

NC33

G25

KEY4

NC34

G17G9N7Y7AG7

KEY6

KEY8

KEY10

NC35

NC36

NC37

AG15

KEY12

KEY14

KEY16

NC42

NC43

NC44

G21

AG21

THERMDC

AG29G7Q7

KEY18

NC45

G19

3

VCORE

AA7

AG9

AG17

AG27

G15

G23

AH6

H14

VSS1

KEY

KEY

KEY

KEY

KEY

KEY

KEY

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

Socket_A/White

AN27

AL27

AN25

AL25

H18

KEY

VSS2

AMD

H22

VSS3

H26

VSS4

M30

VSS5

P8

VSS6

R30

VSS7

T8

VSS8

V30

VSS9

X8

VSS10

Z30

VSS11

AB8

VSS12

AF12

VSS13

AF16

VSS14

AF20

VSS15

AF24

VSS16

AM36

VSS17

AK32

VSS18

AK28

VSS19

AK24

VSS20

AK20

VSS21

AK16

VSS22

AK12

VSS23

AK4

VSS25

AK2

VSS26

AH36

VSS27

AM32

VSS28

AH34

VSS29

AH32

VSS30

AH28

VSS31

AH24

VSS32

AH20

VSS33

AH16

VSS34

AH12

VSS35

AF4

VSS37

AF2

VSS38

AD36

VSS39

AD34

VSS40

AD32

VSS41

AB6

VSS42

AB4

VSS43

AB2

VSS44

Z36

VSS45

Z34

VSS46

Z32

VSS47

X6

VSS48

AM28

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS_Z

X4

X2

V36

V34

V32

T6

T4

T2

R36

R34

AM24

R32

P6

P4

P2

M36

M34

M32

K6

K4

K2

AM20

H36

H34

F26

F22

F18

F14

F10

F6

F4

F2

AM16

D36

D34

D30

D26

D22

D18

D14

D10

D6

B34

AM12

B30

B26

B22

B18

B14

B10

B6

B2

AM4

AK6

AM6

AE7

3

(b)

THERMDA<18>

PSON_OUT

(CPU H/W

MONITOR)

FROM CPU

THERMAL DIODE

PIN

VCC

BC2 10U/8/X/6.3V

BC7 10U/8/X/6.3V

BC13 10U/8/X/6.3V

BC18 10U/8/X/6.3V/X SC7 0.1U/6/Y/25V/B/X

BC23 10U/8/X/6.3V

PLL25V

R1015

0/6/SHT/X

THERMDA

(a)

THERMDC

R949

0/6/SHT/X

單點接地

DISABLE PWM

R36

1K/6

3

D

GS

2

1

3

D

GS

2

1

Q5

2N7002/SOT23

Q6

2N7002/SOT23

FS <27>

PW+ <12,24>

2

VCC25

R33

0/6/SHT/X

1 8

SPKR<12,24>

2 7

3

RT

10K/1/0603

t

CPU

THEMISTOR

BUT ADD VREF

NO SUPPORT

2

BC3 10U/8/X/6.3V

BC8 10U/8/X/6.3V

BC14 10U/8/X/6.3V

BC19 10U/8/X/6.3V

BC24 10U/8/X/6.3V

PLL25V

CPU AMD K7 2.5V ONLY

R34 10/6

BC52

4.7U/8/Y/10V

U53 ATTP1

SIREN# 5VSB

GND VREF

PSON_IN#

PSON_OUT#

TXRTXD

BC451

0.1U/6/Y/25V/X

R1016

BC452

0.1U/6/Y/25V/X

6.98K/6/1

R1017 10K/6/1

PUT INSIDE THE CPU SOCKET,

DETECT CPU TEMP

1

VCOREVCORE

BC4 0.1U/6/Y/25V/X

BC9 0.1U/6/Y/25V/X

BC15 0.1U/6/Y/25V/X

BC28 0.1U/6/Y/25V/X

BC32 10U/8/X/6.3V

K7_P_VG <26>

BC53

33P/4/X

VCC

6

54

TEMP_A

BC453

0.1U/6/Y/25V

BC454

0.1U/6/Y/25V

TMPIN2

TMPIN2 <18>

Title

Size Document Number Rev

Custom

星期四, 六月

Date: Sheet

24, 2004

(2)

PSON_OUT

(1)

(RT H/W

MONITOR)

GIGABYTE

SOCKETA-2

XP-K7VM333

1

1.0

of

528

5

VT-KM266PRO (S2K BUS)

4

3

2

1

VCORE

PLACE CAPS AROUND NB

VCORE

R1126

121/6/1

R1127

100/6/1

0.1U/4/Y/25VBC56

0.1U/4/Y/25VBC57

0.1U/6/Y/25VBC58

-AOCLK

-AICLK

-AOCLK <4>

-AICLK <4>

S2K_VREF is set at 50% of VCC_CORE to NB

S2K_VREF

BC498

1U/6/Y/10V/X

BC499

0.1U/6/Y/25V

SC116

0.1U/4/Y/16V/B

SC86

1U/6/Y/10V/B

W22

B17

D20

B20

C20

A20

C21

E19

B21

B18

E18

A17

C18

A18

D18

C17

E20

A21

D21

C22

A26

C25

C23

D24

B26

E21

A23

B23

A22

D23

A25

C26

C24

E26

F26

G25

G26

H26

G24

H24

E22

E24

D25

D26

F25

F24

H22

M26

M25

M23

M24

K23

N22

M22

K22

K25

K26

N23

K24

C11

D11

E11

A12

B12

C12

D12

E12

VCC25

VCC25

G22

AVDD1

W21

VDD

AGND1

F21

U54A

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

J26

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

J25

D46

D47

L26

D48

D49

D50

D51

D52

D53

D54

D55

J24

D56

D57

D58

D59

J23

D60

D61

J22

D62

D63

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

F10

F15

F19

F20

P21

R21

V21

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

P23

P25

U23

U25

VCORE

J18

L18

R18

K18

P18

N18

M18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B22

D22

B25

E23

E25

H23

H25

L23

L25

VCC25

J14

M21

J13

J15

J17

J16

VTT

VTT

VTT

VTT

VTT

VDS2K

AIN2

AIN3

AIN4

AIN5

AIN6

AIN7

AIN8

AIN9

AIN10

AIN11

AIN12

AIN13

AIN14

AINCLK

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

AOUT9

AOUT10

AOUT11

AOUT12

AOUT13

AOUT14

AOUTCLK

DICLK0

DICLK1

DICLK2

DICLK3

DOCLK0

DOCLK1

DOCLK2

DOCLK3

DINVAL

CFWDRST

CONNECT

PROCRDY

HCLK

HCLK

TESTIN1

S2KCOMP

S2KVREF0

S2KVREF1

TESTIN0

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS2K

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D16

B19

D19

KM266 PRO/A2

K21

B13

D13

F14

T21

B16

E17

C16

A14

D17

A15

E16

B14

C15

E15

A16

D15

A13

C13

B15

N26

P22

N24

P26

N25

T22

P24

R22

T24

T23

R23

R26

R24

R25

A19

A24

G23

L24

C19

B24

F23

L22

E13

D14

C14

E14

G21

F22

E10

L21

F17

N21

F12

T26

U26

V26

T25

V25

U24

V24

V23

U22

V22

-AI2

-AI3

-AI4

-AI5

-AI6

-AI7-SDATA7

-AI8

-AI9-SDATA9

-AI10

-AI11

-AI12

-AI13

-AI14

-AICLK

-AO2

-AO3

-AO4

-AO5

-AO6

-AO7

-AO8

-AO9

-AO10

-AO11

-AO12

-AO13

-AO14

-AOCLK

-DICLK0

-DICLK1

-DICLK2

-DICLK3

-DOCLK0

-DOCLK1

-DOCLK2

-DOCLK3

R1125 1K/6

-VID

S2KCOMP

FOR KM400A

S2K_VREF

-TESTIN

R1124 1K/6

VCC25

-DICLK0 <4>

-DICLK1 <4>

-DICLK2 <4>

-DICLK3 <4>

-DIVAL <4>

R1123 49.9/6/1

-AI[2:14] <4>

-AO[2:14] <4>

-DOCLK[0:3] <4>

CLKFWDRST <4>

CONNECT <4>

PROCRDY <4>

HCLK <9>

-HCLK <9>

VCC25

VCC25

D D

C C

B B

2

HEATSINK

FANSINK/GOLD

1

FOR EMI

-SDATA[0:63]<4>

SC106

1U/6/Y/10V/B

-SDATA0

-SDATA1

-SDATA2

-SDATA3

-SDATA4

-SDATA5

-SDATA6

-SDATA8

-SDATA10

-SDATA11

-SDATA12

-SDATA13

-SDATA14

-SDATA15

-SDATA16

-SDATA17

-SDATA18

-SDATA19

-SDATA20

-SDATA21

-SDATA22

-SDATA23

-SDATA24

-SDATA25

-SDATA26

-SDATA27

-SDATA28

-SDATA29

-SDATA30

-SDATA31

-SDATA32

-SDATA33

-SDATA34

-SDATA35

-SDATA36

-SDATA37

-SDATA38

-SDATA39

-SDATA40

-SDATA41

-SDATA42

-SDATA43

-SDATA44

-SDATA45

-SDATA46

-SDATA47

-SDATA48

-SDATA49

-SDATA50

-SDATA51

-SDATA52

-SDATA53

-SDATA54

-SDATA55

-SDATA56

-SDATA57

-SDATA58

-SDATA59

-SDATA60

-SDATA61

-SDATA62

-SDATA63

VCC25

BC497

0.1U/6/Y/25V

A A

Title

Size Document Number Rev

Custom

Date: Sheet

5

4

3

2

星期四, 六月

GIGABYTE

KM266PRO (S2K BUS)

XP-K7VM333

24, 2004

1

1.0

of

628

5

4

3

2

1

VT-KM266PRO (DDR BUS)

VSS

AE22

AA21

VCC3

VSS

AC22

4

AA15

VCC3

VSS

AE19

U18

VCC3

VSS

AC19

T18

Y25

VCC3

VSS

V18

VCC3

VSS

AE16

DDR25V

V16

V17

VCC3

VSS

Y23

AC16

V15

VCC3

VSS

AE13

V14

VCC3

VSS

AC13

VCC3

VSS

V13

VCC3

VSS

AE10

V12

VCC3

VSS

AC10

V11

AE7

VCC3

VSS

AC7

VCC3

VSS

AE4

AA7V9V10

VCC3

VSS

AC4

VCC3

VSS

AE2

VSS

VSS

KM266 PRO/A2

AC3

MA10

MA11

MA12

MA13

MA14

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

SRASA

SCASA

SWEA

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MVREF1

MVREF0

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

CS0

CS1

CS2

CS3

CS4

CS5

AC11

AB12

AC12

AB14

AB16

AB17

AB15

AC18

AE17

AC17

AB10

AC9

AF17

AB18

AB19

AC21

AD24

AB22

AC24

AB20

AF24

AD6

AC5

AC6

AB6

AB7

AD5

AB11

AD7

AB9

Y26

AD25

AD22

AF19

AE15

AF12

AB8

AF4

Y24

AD26

AF22

AD19

AF15

AE12

AC8

AD4

AA10

AA18

0.1U/6/Y/25V/B

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

CKE0

CKE1

CKE2

CKE3

-CS0

-CS1

-CS2

-CS3

-CS4

-CS5

-SRASA

-SCASA

-SWEA

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

SC14

-DQSD0

-DQSD1

-DQSD2

-DQSD3

-DQSD4

-DQSD5

-DQSD6

-DQSD7

MAA[0:14] <13,14>

CKE0 <13>

CKE1 <13>

CKE2 <13>

CKE3 <13>

-CS0 <13,14>

-CS1 <13,14>

-CS2 <13,14>

-CS3 <13,14>

-CS4 <14>

-CS5 <14>

-SRASA <13,14>

-SCASA <13,14>

-SWEA <13,14>

MVREF_NB

BC513

1U/6/Y/10V

3

DQM[0:7] <13,14>

DDR25V

SC87

1U/6/Y/10V/B

100/6/1

R1152

100/6/1

VCC25

SC88

1U/6/Y/10V/B

SC89

1U/6/Y/10V/B

DDR25V

CAPS SCxx PLACE TO SOLDER SIDE ,CLOSE TO NB

BALL

+

EC45

1000U/D/6.3V/8E

0.1U/4/Y/25VBC65

0.1U/6/Y/25VBC67

2

VCC25

VSS

AA13

VCC

AA22Y21

AVDD2AGND2

VSS

AE25

VSS

AC25

21

21

W23

W24

AA25

AB26

W26

W25

AA26

AA24

AB25

AB24

AF25

AE24

AB23

AC26

AE26

AF26

AD23

AE23

AD21

AF21

AC23

AF23

AE21

AB21

AC20

AF20

AF18

AD18

AD20

AE20

AE18

AD17

AF16

AC15

AC14

AE14

AD16

AD15

AD14

AF14

AF13

AD12

AD11

AF11

AD13

AB13

AE11

AD10

AF10

AE9

AE8

AD9

AD8

AE6

AE3

AE5

AA23

U54B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

AF7

MD51

AF9

MD52

MD53

AF8

MD54

MD55

MD56

AF5

MD57

MD58

AF1

MD59

AF6

MD60

MD61

AF3

MD62

AF2

MD63

Y22

DCLKO

DCLKIN

D D

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD6

MDD7

MDD8

MDD9

MDD10

MDD11

MDD12

MDD13

MDD14

MDD15

MDD16

MDD17

MDD18

MDD19

MDD20

MDD21

MDD22

MDD23

MDD24

C C

B B

DCLKO<9>

DCLKI<9>

A A

R23 10/6 R1151

COUPON2

COUPON1

5

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

MDD31

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

MDD48

MDD49

MDD50

MDD51

MDD52

MDD53

MDD54

MDD55

MDD56

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63

DCLKO_1

DCLKI

BC512

5P/4/N/50V/X

COUPON1 COUPON/X

COUPON2 COUPON/X

DDR MD DAMPPING

Near DIMM 1

MDD0

MDD4

MDD5

MDD1

MDD2

MDD6

MDD7

MDD3

MDD15

MDD14

MDD10

MDD11

MDD8

MDD9

MDD13

MDD12

MDD20

MDD16

MDD17

MDD21

MDD18

MDD23

MDD19

MDD22

MDD24

MDD25

MDD29

MDD28

MDD27

MDD30

MDD26

MDD31

MDD34

MDD38

MDD35

MDD39

MDD36

MDD33

MDD32

MDD37

MDD40

MDD44

MDD45

MDD41

MDD42

MDD43

MDD46

MDD47

MDD61

MDD57

MDD60

MDD56

MDD48

MDD53

MDD49

MDD52

MDD62

MDD58

MDD63

MDD59

MDD54

MDD50

MDD51

MDD55

-DQSD0

-DQSD1

-DQSD2

-DQSD3

-DQSD4

-DQSD5

-DQSD6

-DQSD7

Title

Size Document Number Rev

Custom

Date: Sheet

星期四, 六月

GIGABYTE

KM266PRO (DDR bus)

XP-K7VM333

24, 2004

1

MDD[0:63] <13,14>

0 ~ 7

8 ~ 15

16 ~ 23

24 ~ 31

32 ~ 39

40 ~ 47

48 ~ 55

56 ~ 63

-DQSD[0:7] <13,14>

of

728

1.0

5

4

3

2

1

KM266PRO (AGP bus, 8 bit V_Link bus)

VCC25

AA6Y6T9

U9

K6L6V6W6AA11

AA12

AA19

AA20F8F9

F16

F18

H21

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N13

N14

N15

N16

P11

P12

P13

P14

AA8

AA9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

N12

VCC2

VCC2

VCC2

VCC2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L13

L14

L15

L16

M11

M12

M13

M14

M15

M16

N11

3

C3

B4

VCCRGB

PLLVDD1

PLLVDD2

VSS

VSS

VSS

T16

C10

C4

VCCDAC

VSS

VSS

T14

T15

AD3

VSUS25

VSS

VSS

T12

T13

VCC3SUS25V

J12

T11

VCC5

VSS

J11

R16

J10

VCC5

VSS

R15

VCC5

VSS

R14

VSS

J21

AA16

AA17

AA14

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

P15

P16

R11

R12

R13

VCC25

D D

The voltage level of

LVREF_NB is 0.625V

C C

Near N.B.

PIN NAME

B B

FP/TVD0

FP/TVD1

FP/TVD2

FP/TVD3

A A

C5

0.1U/6/Y/25V

R29

3K/6/1

R30

1K/6/1

R1131 360/6/1

R1134 160/6/1

C7

0.1U/6/Y/25V

VLCOMP_NB

VIARESET

VLREF_NB

DESCRIPTION

INTERNAL GRAPHIC INTERRUPT

( 0: ENABLE 1:DISABLE)

GRAPHIC I/O

( 0: ENABLE 1:DISABLE)

PCI BASE ADDRESS MAPPING

( 0: NORMAL 1:SPECIFIED)

EXTERNAL/INTERNAL GRAPHIC CLOCK

( 0: INTERNAL 1:EXTERNAL)

-RESET_NB

C314

1000P/6/X/50V

5

VLCOMP_NB

VLREF_NB

GUICLK

-INTA

VIARESET

VGAHSYNC

VGAVSYNC

SPCLK2

SPD2

TVD0

TVD1

TVD2

TVD3

TVD7

TVD8

TVD9

TVD10

-SUSST

BISTIN

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE0

UPCMD

UPSTB

-UPSTB

DNCMD

DNSTB

-DNSTB

BC503

1U/6/Y/10V

BC502

0.1U/6/Y/25V

VLAD0<10>

VLAD1<10>

VLAD2<10>

VLAD3<10>

VLAD4<10>

VLAD5<10>

VLAD6<10>

VLAD7<10>

VBE0<10>

UPCMD<10>

UPSTB<10>

-UPSTB<10>

DNCMD<10>

DNSTB<10>

-DNSTB<10>

GUICLK<9>

-INTA<11,15,16>

R1128 4.7/6

AR<19>

R1129 4.7/6

AG<19>

R1130 4.7/6

AB<19>

VGAHSYNC<19>

VGAVSYNC<19>

SPCLK2<19>

SPD2<19>

RN205

VCC3

12

34

56

78

8.2K/8P4R/X

R1284 8.2K/6/X

R1132 8.2K/6/X

R1133 8.2K/6/X

R1285 8.2K/6/X BC71 1U/6/Y/10V

-PWROK_NB<12>

-RESET_NB<26>

-SUSST<12>

R1135 1K/6

U54C

W4

VD0

W5

VD1

AA4

VD2

Y1

VD3

AC2

VD4

Y2

VD5

AB4

VD6

AC1

VD7

Y3

VBE

Y4

UPCMD

AA1

UPSTB

AA2

UPSTB

AB3

DNCMD

AB1

DNSTB

AB2

DNSTB

AB5

LCOMPP

Y5

LVREF

E6

XIN

F6

INTA

A3

AR

A2

AG

B3

AB

B5

RSET

B6

HSYNC

A6

VSYNC

C6

SPCLK2

D6

SPD2

D9

TVD00/DVP0D00

C9

TVD01/DVP0D01

B9

TVD02/DVP0D02

A9

TVD03/DVP0D03

E9

TVD04/DVP0D04

E8

TVD05/DVP0D05

B8

TVD06/DVP0D06

A8

TVD07/DVP0D07

C8

TVD08/DVP0D08

C7

TVD09/DVP0D09

B7

TVD10/DVP0D10

A7

TVD11/DVP0D11

B11

TVVS/DVP0VS

B10

TVHS/DVP0HS

D8

TVCLK/DVP0DCLK

A10

TVCLKIN/DVP0DET

A11

TVDE/DVP0DE

C5

DISPCLKO

D5

DISPCLKI

D10

GPO0

E7

GPOUT

F7

SPCLK1

D7

SPD1

AD1

PWROK

AE1

RESET

AD2

SUSSTAT

A5

BISTIN

B2

GNDDAC

A1

GNDRGB

E5

PLLGND1

D4

PLLGND2

4

VCC25

A4

VSS

VSS

U21

F11

F13

B1C2R9

VCC1

VCC1

VCC1

VCC1

VCC1

VCCQQ

ADSTB1F/FPD12/TVD00

ADSTB1S/FPDET/TVCLKIN

VSS

VSS

VSS

VSSQQ

VSS

AA3

L11

L12

AA5

VDDQ

J6N6P6R6T6U6K9L9M9N9P9

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

GD0/FPD10

GD1/FPD11

GD2/FPDVICLK

GD3/FPD09

GD4/FPD08

GD5/FPD07

GD6/FPD06

GD7/FPD05

GD8/FPDVIDET

GD9/FPDVIHS

GD10/FPD01

GD11/FPD23/TVD11

GD12/FPD00

GD13/FPD22/TVD10

GD14/FPD21/TVD09

GD15/FPD20/TVD08

GD16/FPD18/TVD06

GD17/FPD17/TVD05

GD18/FPD16/TVD04

GD19/FPDE/TVDE

GD20/FPD14/TVD02

GD21/FPCLK/TVCLK

GD22/FPD13/TVD01

GD23/FPD15/TVD03

GD24/DVP1D09

GD25

GD26/DVP1D10

GD27

GD28/DVP1D07

GD29/DVP1D06

GD30/DVP1D08

GD31/DVP1D04

GCBE0/FPD03

GCBE1/SB_DA

GCBE2/FPD19/TVD07

GCBE3/DVP1D11

ADSTB0F/FPD04

ADSTB0S/FPD02

SBA0/DVP1VS

SBA1/DVP1DE

SBA2/DVP1D00

SBA3/DVP1HS

SBA4/DVP1D05

SBA5/DVP1D03

SBA6/DVP1CLK

SBA7/DVP1CLK_N

SBSTBF/DVP1D01

SBSTBS/DVP1D02

GFRAME/FPHS/TVHS

GIRDY/SB_CK

GTRDY

GSTOP/FPDVICLK_N

GDEVSEL/FPVS/TVVS

GPAR/FPDVIVS

GGNT/DVI_DDCDA

GREQ/DVI_DDCCK

ST1/DVP1DET

DBIL

DBIH/PIPE

WBF/FPCLK_N

GCLK

AGPCOMP

AGPVREF0

AGPVREF1

AGP8XDET

GSERR/FPDVIDE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

W2

W1

V3

W3

V1

U2

U1

U3

T4

T5

R3

P2

R1

P1

P3

N3

N2

M1

M3

M5

L1

L4

L2

L3

J1

H5

J3

H4

H1

H3

H2

G4

T1

P4

N1

K3

T3

T2

K2

K1

D2

D3

E3

D1

G3

F1

G1

G2

E1

E2

N5

P5

R5

U5

N4

U4

E4

F5

G5

ST0

F3

J5

ST2

J4

K5

L5

K4

RBF

V5

C1

M6

H6

G6

R4

VSS

VSS

KM266 PRO/A2

F2J2M2R2V2F4M4V4J9

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

-GBE0

-GBE1

-GBE2

-GBE3

AD_STB0

-AD_STB0

AD_STB1

-AD_STB1

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STB

-SB_STB

ST0

ST1

ST2

DBIL

DBIH_PIPE

GCLKNB

AGPCOMP

AGPVREF

GD[0:31]

-GBE[0:3] <15>

AD_STB0 <15>

-AD_STB0 <15>

AD_STB1 <15>

-AD_STB1 <15>

SBA[0:7] <15>

SB_STB <15>

-SB_STB <15>

-GFRAME <15>

-GIRDY <15>

-GTRDY <15>

-GSTOP <15>

-GDEVSEL <15>

GPAR <15>

-GGNT <15>

-GREQ <15>

ST0 <15>

ST1 <15>

ST2 <15>

DBIL <15>

DBIH_PIPE <15>

-WBF <15>

-RBF <15>

R1136 60.4/6/1

AGPVREF <15>

-GSERR <15>

2

GD[0:31] <15>

GCLKNB <9>

VDDQ

R1140 1K/6

VDDQ

Title

KM266PRO (AGP bus, 8 bi t V_ Lin k bus )

Size Document Number Rev

Custom

Date: Sheet

星期四, 六月

VDDQ

0.1U/6/Y/25VBC501

VCC25

10U/8/X/6.3V/B/XSC97

1U/6/Y/10V/B/XSC98

10U/8/X/6.3V/B/XSC100

Decoupling capacitors

VDDQ

0.1U/4/Y/25VBC72

PLACE CAPS AROUND NB

VDDQ

1U/6/Y/10V/B/XSC41

1U/6/Y/10V/B/XSC44

CAPS SCxx PLACE TO SOLDER

SIDE,CLOSE TO NB BALL

GIGABYTE

XP-K7VM333

24, 2004

1

1.0

of

828

5

4

3

2

1

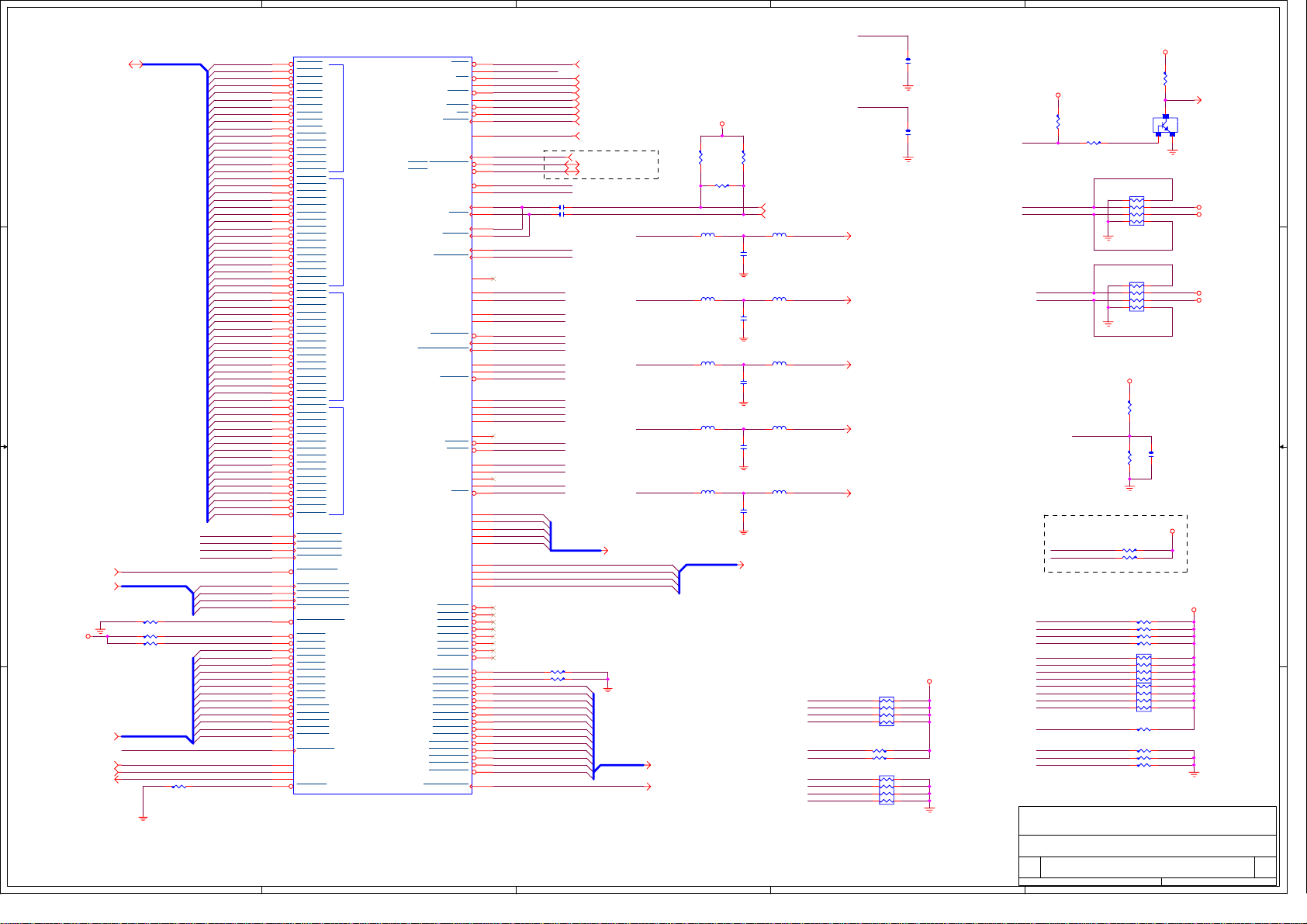

CLOCK GENERATOR

U4

50

VCC25_CPU

47

GNDCPU

40

VCC3/ VCC25_DDR

34

VCC3/ VCC25_DDR

39

GNDDDR

33

GNDDDR

51

VCC3_HCLK

5

VCC3_AGP

16

VCC3_PCI

23

VCC3_AVDD

22

VCC3_48M

55

VCC3_REF

19

GND48M

13

GNDPCI

9

GNDAGP

24

AGND

54

GNDHCLK

2

GND

56

VTTPWG/ REF1

25

IREF

26

RST /(PD)

27

SCLK

28

SDATA

HCLK_T+

HCLK_C-

CPUCLK_T+

CPUCLK_C-

AGPCLK0/ MODE

AGPCLK1/ SEL_CPU

AGPCLK2/ PCI_STOP

BUFFER_IN

FBOUT

DDR_T0/ SDRAM0

DDR_C0/ SDRAM1

DDR_T1/ SDRAM2

DDR_C1/ SDRAM3

DDR_T2/ SDRAM4

DDR_C2/ SDRAM5

DDR_T3/ SDRAM6

DDR_C3/ SDRAM7

DDR_T4/ SDRAM8

DDR_C4/ SDRAM9

DDR_T5/ SDRAM10

DDR_C5/ SDRAM11

PCICLK_F/ FS1

PCICLK_0/SEL_SD_DDR

PCICLK_1/MULT_SEL0

PCICLK_2

PCICLK_3

PCICLK_4

PCICLK_5

REF0/ FS0

24_48MHZ/ FS2

48MHZ/ FS3

RTM360-520/ SSOP56

R_HCLK

48

-R_HCLK

49

R_CPUCLK

53

-R_CPUCLK

52

MODE

6

SEL_CPU

7

-PCI_STP

8

DCLKO

45

DCLKIN

46

CKOUT2

44

-CKOUT2

43

CKOUT5

42

-CKOUT5

41

CKOUT1

38

-CKOUT1

37

CKOUT4

36

-CKOUT4

35

CKOUT3

32

-CKOUT3

31

CKOUT0

30

-CKOUT0

29

FS1

10

SEL_DDR

11

MULT_SEL

12

R_PCICLK0

14

R_PCICLK1

15

R_PCICLK2

17

-CPU_STP

18

FS0

1

FS2

21

FS3

20

U4_X1

3

X1

4

X2

U4_X2

X1

14.31818MHZ

BC90

10P/4/N/50V

12

R75 10/6

R76 10/6

R73 10/6

R74 10/6

R77 22/6

R78 22/6 C19 10P/4/N/50V/X

R79 22/6

R1137 15/6

CKOUT2 <13>

-CKOUT2 <13>

CKOUT5 <13>

-CKOUT5 <13>

CKOUT1 <13>

-CKOUT1 <13>

CKOUT4 <13>

-CKOUT4 <13>

CKOUT3 <13>

-CKOUT3 <13>

CKOUT0 <13>

-CKOUT0 <13>

R83 22/6

R1177 8.2K/6

RN23

33/8P4R

R89 22/6

R88 22/6

R91 22/6

R93 22/6

BC91

10P/4/N/50V

DCLKI

7

8

5

6

3

4

1

2

1

VCC3

HCLK

-HCLK

CPUCLK

-CPUCLK

GCLKNB

VCLK

AGPCLK

DCLKO <7>

DCLKI <7>

PCICLK_F

PCICLK0

PCICLK1

PCICLK2

LPC33

GUICLK

SIO_OSC

LPC24

USBCLK

HCLK <6>

-HCLK <6>

CPUCLK <4>

-CPUCLK <4>

GCLKNB <8>

VCLK <10>

AGPCLK <15>

PCICLK_F <10>

PCICLK0 <16>

PCICLK1 <16>

PCICLK2 <16>

LPC33 <18>

GUICLK <8>

SIO_OSC <12>

LPC24 <18>

USBCLK <11>

BC85

0.1U/4/Y/16V

BC82

0.1U/4/Y/16V

VCC25_CLK_1

BC98

0.1U/4/Y/16V

-CKGRST

SMBCLK

SMBDATA

C354

100P/4/N/50V/X

APICCLK

IREF

VCC25

BC94

0.1U/4/Y/16V

L7 FB200/8

BC535

0.1U/4/Y/16V

L8 1/8

BC95

0.1U/4/Y/16V

SMBCLK<12,13>

SMBDATA<12,13>

AUDIO14 <21>

PWROK<10,24,25>

BC81

1U/6/Y/10V

BC96

0.1U/4/Y/16V

VCC3

BC77

1U/6/Y/10V

BC97

0.1U/4/Y/16V

R103 0/6S/X

R104 4.7K/6/X

C353

100P/4/N/50V/X

VCC25

D D

MODE

IREF

VCC3_CLK

BC93

0.1U/6/Y/25V

AUDIO14

L9 1/8

VCC3

BC99

0.1U/4/Y/16V

R1138 8.2K/6

VCC3

R1139 8.2K/6

VCC3

C C

VCC3

R81 8.2K/6

R82 8.2K/6

R84 8.2K/6

R86 1K/6/X

R1150 10/6

-PCI_STP

-CPU_STP

SEL_CPU

SEL_DDR

CPUCLK

-CPUCLK

HCLK

-HCLK

GCLKNB

AGPCLK

VCLK

PCICLK_F

PCICLK0

PCICLK1

PCICLK2

LPC33

DCLKO

SIO_OSC

USBCLK

LPC24

FS1

0629 ADD APIC

C13 10P/4/N/50V/X

C14 10P/4/N/50V/X

C15 22P/4/N/50V

C16 22P/4/N/50V

C17 10P/4/N/50V

C18 10P/4/N/50V

C20 10P/4/50V/X

7

8

5

6

3

4

1

2

CN1 10P/8P4C/X

C22 10P/4

C24 10P/4/X

C25 10P/4/X

C26 10P/4/X

C28 10P/4/X

APICCLK

B B

FS1

FS2

FS3

KM400/CD STRAPPING FSB100/133/166/200MHZ

A A

R97 47/6

R101 33/6

RN29

1

1

2

3

4

5

6

7

8

1K/8P4R

CPU/CLK GEN.

FS0

100MHZ

133MHZ 1

166MHZ 1

200MHZ

FS1 SDA2

1

0

1

0

0

0

5

PICCLK0

R100

200/6

PICCLK1

R102

200/6/X

8235CD/CE

SDA0

0

0

0

1

11

0

1

0629 ADD APIC

CLK 3.3V--->2.5V

RN28

1

1

2

3

4

5

6

7

8

1K/8P4R

FS_2

FS_3

FS_3 <12>

PICCLK0 <4>

PICCLK1 <10>

VCC3

CPU CLOCK

JP1

SHORT

100

OPEN 133/166

AMD CPU FSB SENSE TABLE

C_FS_1 C_FS_0 FSB FREQ

1

1

0

0

0

1

1

0

RESERVE

133MHZ

166MHZ

200MHZ

4

FS100M

JP1

JP1

2

1

H1X2

JU1x2/B/[1-2]CLOSE

FS100M

Default ON

CLK H/W TRAP FREQ TABLE

H/W AUTO TRAP (100/133/166/200MHZ)

CPU AGP PCI FS3 FS2 FS1 FS0

100.00

133.33

166.66

200.00

66.66 33.33

66.66

66.66

66.66

33.33

33.33

33.33

1

0

1

1

00

1

0

0

3

3VDUAL

D67

1

3

2

BAT54C/SOT23

01

01

1

01

R1212

100K/6

U64

1

2

NC7SZ125/SOT23

SDA0 => CPU Clock Frequency

VCC3

0 - 100/200MHz (Default)

1 - 133/166MHz

5

43

R1214

1K/6

3VDUAL 3VDUAL

R1213

R961

1K/6

8.2K/6

SDA0FS_0FS0

SDA0 <12,17>

C_FS_0 <5>

2

FS100M

Title

Size Document Number Rev

Custom

Date: Sheet

星期四, 六月

132

24, 2004

VCC3

R960

100K/6

Q119

2N7002/SOT23

SOT23

GIGABYTE

CLOCK GENERATOR

XP-K7VM333

1

VCC3

U63

1

5

2

FS_3FS_2

43

NC7SZ125/SOT23

C_FS_1 <5>

928

1.0

of

Loading...

Loading...