Gigabyte ram disk 101 Schematics

5

4

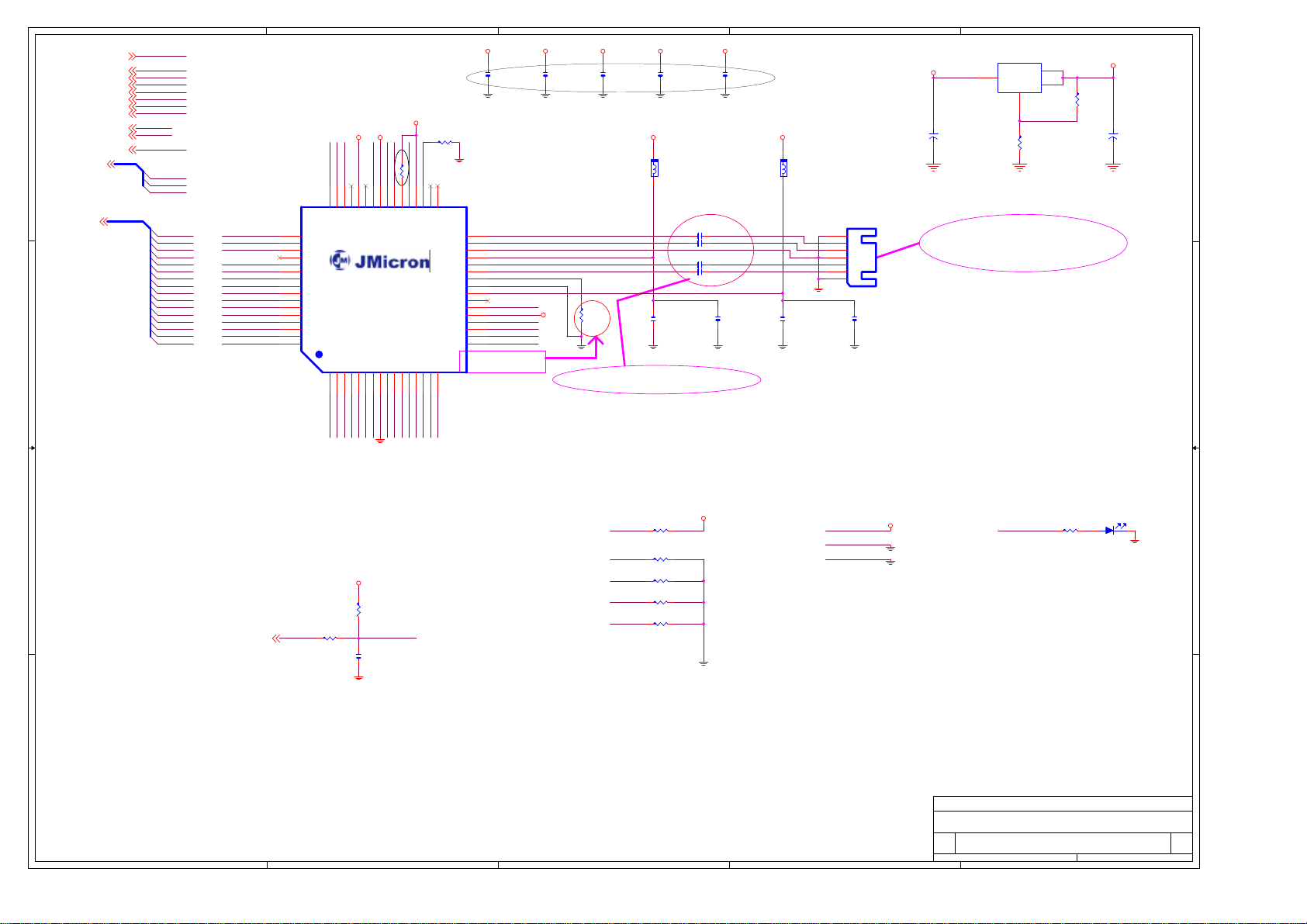

3

2

1

GIGABYTE GC-RAMDISK Schematics

SHEET TITLE

D D

C C

01

02

03

04

05

06

07

08

09

10

11

COVER SHEET

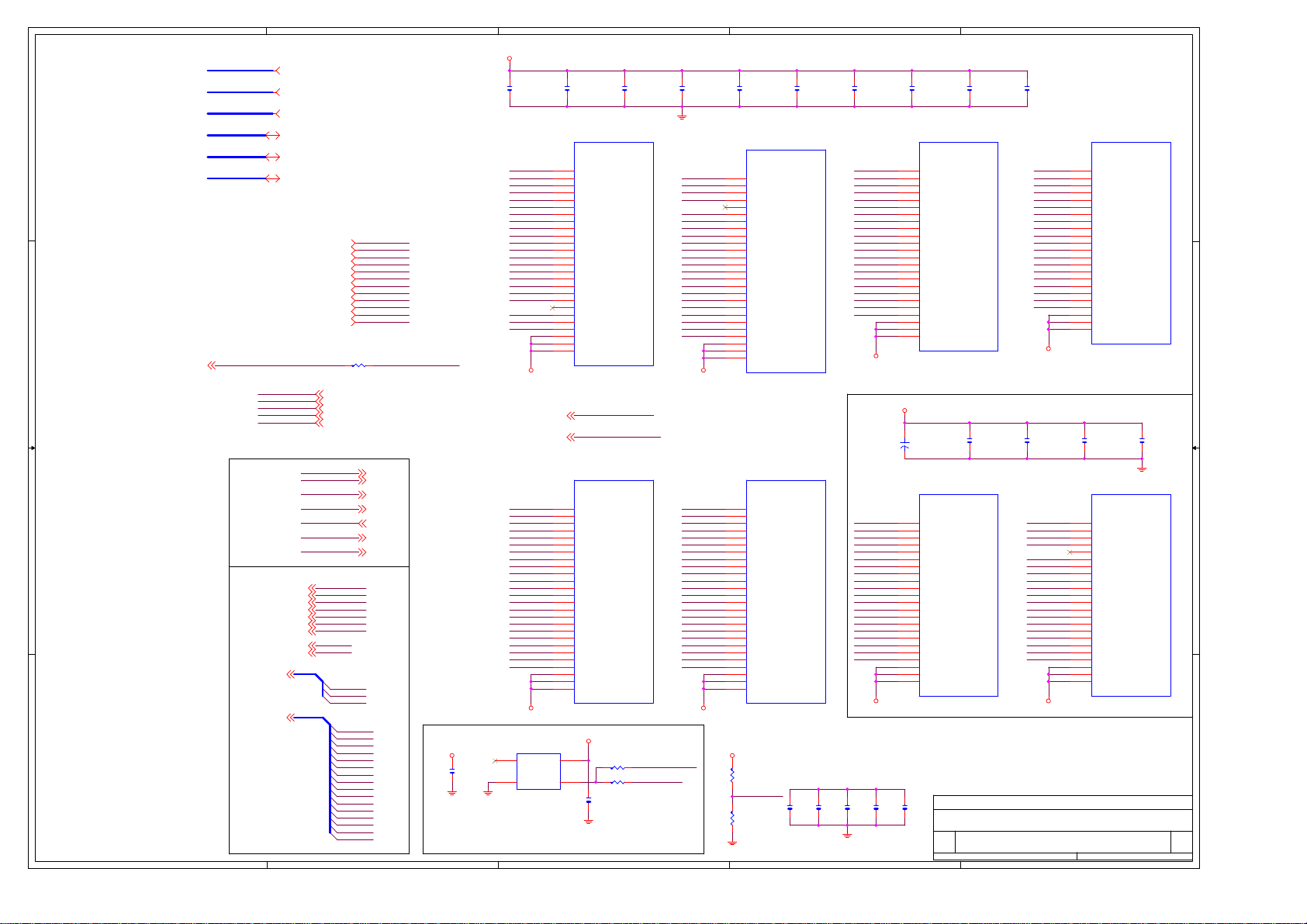

FPGA-V1000 1/2

FPGA-V1000 2/2

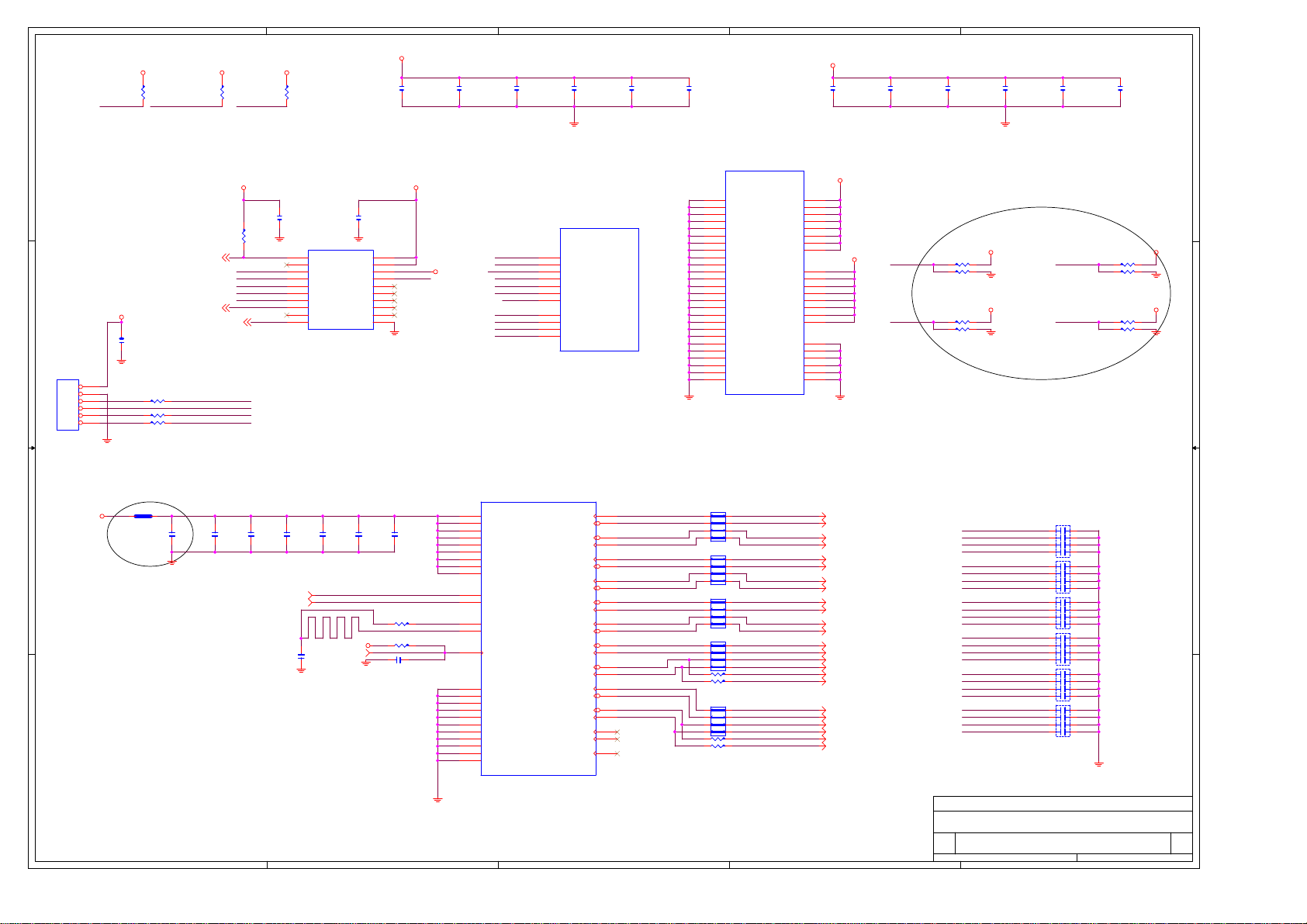

JM20330 SATA Bridge

DDR1,2

DDR3,4

DDR TERMINATION

Battery & Charger

POWER

PCI & PCIE Golden Finger

BOM & PCB MODIFY HISTORY

12

13

14

SHEET TITLE

23

24

25

26

27

28

29

30

31

32

33

34

35

36

Revision 1.0

B B

15

16

37

38

17

18

19

20

21

22

A A

5

4

3

2

PROCESS:C

Title

Size Document Number Rev

Custom

Date: Sheet of

GIGABYTE CORP.

COVER SHEET

GC-RAMDISK 1.0

1

COMPONENT SIDE

(0.5 oz. Copper)

VCC SIDE

(1 oz. Copper)

GND SIDE

(1 oz. Copper)

SOLDER SIDE

(0.5 oz. Copper)

1 11

5

BA[0:1]

-CS[0:7]

CKE[0:7]

DCLKO3

MAA[0..13]

DQS[0..7]

MD[0..63]

To DIMM

module

data

mask pin

To DIMM

module

control

pin

DCLKO

D D

C C

BA[0:1] 5,6,7

-CS[0:7] 5,6,7

CKE[0:7] 5,6,7

MAA[0..13] 5,6,7

DQS[0..7] 7

MD[0..63] 7

Debub0

Debub1

Debub2

Debub3

HD_LED

-CAS05,7

-WE05,7

-RAS05,7

-CAS15,7

-WE15,7

-RAS15,7

-CAS26,7

-WE26,7

-RAS26,7

-CAS36,7

-WE36,7

-RAS36,7

R1 22/6

Debug0 8

Debug1 8

Debug2 8

Debug3 8

HD_LED 8

To DIMM differential clock input

SMBCLK

SMBDATA

SSC_EN

OSC_SATA

XC_DOUT

XC_INIT

B B

RESETn4

DMACKn4

DIOWn4

DIORn4

IORDY4

INTRQ4

DMARQ4

CS0n4

CS1n4

DA[0..2]4

DD[0..15]4

A A

5

-RESET

RESETn

DMACKn

DIOWn

DIORn

IORDY

INTRQ

DMARQ

CS0n

CS1n

SMBCLK 3,5,6,7,8

SMBDATA 3,5,6,7,8

SSC_EN 4

OSC_SATA 4

XC_DOUT 3

XC_INIT 3

-RESET 10

DA0

DA1

DA2

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

4

4

-CAS0

-WE0

-RAS0

-CAS1

-WE1

-RAS1

-CAS2

-WE2

-RAS2

-CAS3

-WE3

-RAS3

F_DCLK0

VCC3

BC16

0.1U/4/Y5V/16V/Z

OSC 25MHz/[10OC3-925000-01;10OC3-125000-01]

3

FPGA25V

BC1

0.1U/4/Y5V/16V/Z

DQS1

MD0

MD3

MD1

MD2

DQS0

SSTL2_REF

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

SSTL2_REF

MD12

MD13

MD14

F_DCLK0

MD15

SSTL2_REF

FPGA25V FPGA25V

POWER_DET10

MD47

MD32

MD33

MD34

MD35

DQS4

SSTL2_REF

MD37

MD38

MD39

MD36

MD40

MD41

MD42

MD43

MD44

MD45

SSTL2_REF

MD46

CKE4

CKE5

DQS5

SSTL2_REF

FPGA25V FPGA25V

X1

1

NC

2 3

GND OSC

-RESET10

OSC

BC2

0.1U/4/Y5V/16V/Z

U1-3

G16

IO

B16

IO_L01N_2/VRP_2

C16

IO_L01P_2/VRN_2

C15

IO_L16N_2

D14

IO_L16P_2

D15

IO_L17N_2

D16

IO_L17P_2/VREF_2

E13

IO_L19N_2

E14

IO_L19P_2

E15

IO_L20N_2

E16

IO_L20P_2

F12

IO_L21N_2

F13

IO_L21P_2

F14

IO_L22N_2

F15

IO_L22P_2

G12

IO_L23N_2/VREF_2

G13

IO_L23P_2

G14

IO_L24N_2

G15

IO_L24P_2

H13

IO_L39N_2

H14

IO_L39P_2

H15

IO_L40N_2

H16

IO_L40P_2/VREF_2

G11

VCCO_2

H11

VCCO_2

H12

VCCO_2

XCS1000/[10HB1-151000-10]

U1-7

K1

IO

R1

IO_L01N_6/VRP_6

P1

IO_L01P_6/VRN_6

P2

IO_L16N_6

N3

IO_L16P_6

N2

IO_L17N_6

N1

IO_L17P_6/VREF_6

M4

IO_L19N_6

M3

IO_L19P_6

M2

IO_L20N_6

M1

IO_L20P_6

L5

IO_L21N_6

L4

IO_L21P_6

L3

IO_L22N_6

L2

IO_L22P_6

K5

IO_L23N_6

K4

IO_L23P_6

K3

IO_L24N_6/VREF_6

K2

IO_L24P_6

J4

IO_L39N_6

J3

IO_L39P_6

J2

IO_L40N_6

J1

IO_L40P_6/VREF_6

J5

VCCO_6

J6

VCCO_6

K6

VCCO_6

XCS1000/[10HB1-151000-10]

VCC3

4

VCC

BC3

0.1U/4/Y5V/16V/Z

BANK2

-RESET

POWER_DET

BANK6

R5 33/6

R7 33/6

OSC_SATA

BC17

0.1U/4/Y5V/16V/Z

3

OSC_CLKin

BC4

0.1U/4/Y5V/16V/Z

MD21

MD30

MD31

-RAS3

DQS3

SSTL2_REF

MD26

MD28

MD29

MD27

MD25

MD24

MD23

MD22

MD18

SSTL2_REF

MD20

MD19

MD17

MD16

SSTL2_REF

DQS2

DQS7

MD59

MD63

MD62

SSTL2_REF

MD58

MD60

SSTL2_REF

MD61

MD57

MD56

MD54

MD50

MD51

MD55

MD52

MD53

CKE6

CKE7

MD49

MD48

SSTL2_REF

DQS6

BC5

0.1U/4/Y5V/16V/Z

U1-4

K15

IO

P16

IO_L01N_3/VRP3

R16

IO_L01P_3/VRN3

P15

IO_L16N_3

P14

IO_L16P_3

N16

IO_L17N_3

N15

IO_L17P_3/VREF3

M14

IO_L19N_3

N14

IO_L19P_3

M16

IO_L20N_3

M15

IO_L20P_3

L13

IO_L21N_3

M13

IO_L21P_3

L15

IO_L22N_3

L14

IO_L22P_3

K12

IO_L23N_3

L12

IO_L23P_3/VREF_3

K14

IO_L24N_3

K13

IO_L24P_3

J14

IO_L39N_3

J13

IO_L39P_3

J16

IO_L40N_3/VREF3

K16

IO_L40P_3

J11

VCCO_3

J12

VCCO_3

K11

VCCO_3

XCS1000/[10HB1-151000-10]

U1-8

BANK7

G2

IO

C1

IO_L01N_7/VRP_7

B1

IO_L01P_7/VRN_7

C2

IO_L16N_7

C3

IO_L16P_7/VREF_7

D1

IO_L17N_7

D2

IO_L17P_7

E3

IO_L19N_7/VREF_7

D3

IO_L19P_7

E1

IO_L20N_7

E2

IO_L20P_87

F4

IO_L21N_7

E4

IO_L21P_7

F2

IO_L22N_7

F3

IO_L22P_7

G5

IO_L23N_7

F5

IO_L23P_7

G3

IO_L24N_7

G4

IO_L24P_7

H3

IO_L39N_7

H4

IO_L39P_7

H1

IO_L40N_7/VREF_7

G1

IO_L40P_7

G6

VCCO_7

H5

VCCO_7

H6

VCCO_7

XCS1000/[10HB1-151000-10]

FPGA25V

R6

75/6/1

SSTL2_REF

R8

75/6/1

2

Place each cap near the pin VCCO

BC8

0.1U/4/Y5V/16V/Z

U1-5

BANK4

T12

IO

T14

IO

N12

IO/VREF_4

P13

IO/VREF_4

T10

IO/VREF_4

R13

IO_L01N_4/VRP_4

T13

IO_L01P_4/VRN_4

P12

IO_L25N_4

R12

IO_L25P_4

M11

IO_L27N_4/DIN/D0

N11

IO_L27P_4/D1

P11

IO_L28N_4

R11

IO_L28P_4

M10

IO_L29N_4

N10

IO_L29P_4

P10

IO_L30N_4/D2

R10

IO_L30P_4/D3

N9

IO_L31N_4/INIT_B

P9

IO_L31P_4/DOUT/BUSY

R9

IO_L32N_4/GCLK1

T9

IO_L32P_4/GCLK0

L9

VCCO_4

L10

VCCO_4

M9

VCCO_4

XCS1000/[10HB1-151000-10]

VCC3

1

+

EC2

100U/D/10V/57

U1-1

BANK0

A5

IO

A7

IO

A3

IO/VREF_0

D5

IO/VREF_0

B4

IO_L01N_0/VRP_0

A4

IO_L01P_0/VRN_0

C5

IO_L25N_0

B5

IO_L25P_0

E6

IO_L27N_0

D6

IO_L27P_0

C6

IO_L28N_0

B6

IO_L28P_0

E7

IO_L29N_0

D7

IO_L29P_0

C7

IO_L30N_0

B7

IO_L30P_0

D8

IO_L31N_0

C8

IO_L31P_0/VREF_0

B8

IO_L32N_0/GCLK7

A8

IO_L32P_0/GCLK6

E8

VCCO_0

F7

VCCO_0

F8

VCCO_0

XCS1000/[10HB1-151000-10]

BC9

0.1U/4/Y5V/16V/Z

IDE interface signal

BC12

0.1U/4/Y5V/16V/Z

POWER_DET

BANK3

BC6

0.1U/4/Y5V/16V/Z

BC7

0.1U/4/Y5V/16V/Z

CKE1

CKE0

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

XC_DOUT

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CKE2

XC_INIT

CKE3

BA0

BA1

FPGA25V

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

DIORn

DIOWn

DA0

DA1 DA2

VCC3 VCC3

Place each cap near the pin SSTL2_REF

SSTL2_REF

BC18

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

BC19

BC20

0.1U/4/Y5V/16V/Z

2

BC21

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

BC22

Title

Size Document Number Rev

Custom

Date: Sheet of

GIGABYTE CORP.

FPGA PIN

GC-RAMDISK

BC10

0.1U/4/Y5V/16V/Z

-CS0

-CAS1

-CS3

-RAS1

-CS6

-CS7

-CS5

-CS4

-CS2

-CS1

-WE1

-CAS0

-CAS2

-WE2

-RAS2

-CAS3

-WE0

-RAS0

-WE3

MAA13

FPGA25V

BC13

0.1U/4/Y5V/16V/Z

DMACKn

IORDY

INTRQ

DMARQ

CS0n

CS1n

Debug0

Debug1

Debug2

RESETn

SSC_EN

Debug3

SMBCLK

SMBDATA

HD_LED

-RESET

OSC_CLKin

1

U1-6

BANK5

N5

IO

P7

IO

T5

IO

T8

IO/VREF_5

T3

IO_L01N_5/RDWR_B

R3

IO_L01P_5/CS_B

T4

IO_L10N_5/VRP_5

R4

IO_L10P_5/VRN_5

R5

IO_L27N_5/VREF_5

P5

IO_L27P_5

N6

IO_L28N_5/D6

M6

IO_L28P_5/D7

R6

IO_L29N_5

P6

IO_L29P_5/VREF_5

N7

IO_L30N_5

M7

IO_L30P_5

T7

IO_L31N_5/D4

R7

IO_L31P_5/D5

P8

IO_L32N_5/GCLK3

N8

IO_L32P_5/GCLK2

L7

VCCO_5

L8

VCCO_5

M8

VCCO_5

XCS1000/[10HB1-151000-10]

BC14

0.1U/4/Y5V/16V/Z

U1-2

BANK1

A9

IO

A12

IO

C10

IO

D12

IO/VREF_1

A14

IO_L01N_1/VRP_1

B14

IO_L01P_1/VRN_1

A13

IO_L10N_1/VREF_1

B13

IO_L10P_1

B12

IO_L27N_1

C12

IO_L27P_1

D11

IO_L28N_1

E11

IO_L28P_1

B11

IO_L29N_1

C11

IO_L29P_1

D10

IO_L30N_1

E10

IO_L30P_1

A10

IO_L31N_1/VREF_1

B10

IO_L31P_1

C9

IO_L32N_1/GCLK5

D9

IO_L32P_1/GCLK4

E9

VCCO_1

F9

VCCO_1

F10

VCCO_1

XCS1000/[10HB1-151000-10]

2 11Monday, July 11, 2005

1

BC15

0.1U/4/Y5V/16V/Z

1.0

5

FPGA25V

XC_CLK

J_TDI

XC_TMS

XC_TCK

PROG

XC_INIT

FPGA25VFPGA25V

R12

4.7K/4

BC35

0.1U/4/Y5V/16V/Z

XC_DOUT

CODEREY

U2

1

D0

2

(DNC)

3

CLK

4

TDI

5

TMS

6

TCK

7

/CF

8

OE/RESET

9

(DNC)

10 11

/CE GND

XCF04SVO20C/[10HP4-200420-10]

FPGA25V

R10

4.7K/4

XC_INIT PROG

D D

VCC3

C C

JP1

1

2

3

4

5

6

HEADER 6/X

BC37

0.1U/6/X7R/16V/K/X

R22 100/6

R23 100/6

R24 100/6

DONE

XC_DOUT2

R11

4.7K/4

XC_INIT2

CODEREY4,10

R13

4.7K/4

XC_TCK

J_TDO

J_TDI

XC_TMS

XCF04S

VCCO

VCCINT

(DNC)

(DNC)

(DNC)

(DNC)

BC36

0.1U/4/Y5V/16V/Z

20

VCCJ

19

18

17

TDO

16

15

14

13

/CEO

12

4

FPGA1_2V

XC_TDO

BC23

0.1U/4/Y5V/16V/Z

FPGA25V

VCC3

BC24

0.1U/4/Y5V/16V/Z

XC_CLK

DONE

XC_HSWAP

XC_TCK

FPGA CORE POWER

XC_M0

XC_M1

XC_M2

PROG

XC_TDO

J_TDO

XC_TMS

BC25

0.1U/4/Y5V/16V/Z

BC26

0.1U/4/Y5V/16V/Z

Config

T15

CCLK

R14

DONE

C4

HSWAP_EN

P3

M0

T2

M1

P4

M2

B3

PROG_B

C14

TCK

A2

TDI

A15

TDO

C13

TMS

XCS1000/[10HB1-151000-10]

U1-10

3

BC27

0.1U/4/Y5V/16V/Z

BC28

0.1U/4/Y5V/16V/Z

U1-9

POWER

A1

GND

A16

GND

B2

GND

B9

GND

B15

GND

F6

GND

F11

GND

G7

GND

G8

GND

G9

GND

G10

GND

H2

GND

H7

GND

H8

GND

H9

GND

H10

GND

J7

GND

J8

GND

J9

GND

J10

GND

J15

GND

K7

GND

K8

GND

K9

GND

K10

GND

L6 L11

GND GND

XCS1000/[10HB1-151000-10]

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

GND

GND

GND

GND

GND

N13

N4

M12

M5

E12

E5

D13

D4

T11

T6

L16

L1

F16

F1

A11

A6

T16

T1

R15

R8

R2

FPGA25V

FPGA1_2V

2

BC29

0.1U/4/Y5V/16V/Z

FPGA25V

FPGA AUX POWER

BC30

0.1U/4/Y5V/16V/Z

XC_M0

XC_M1 XC_HSWAP

BC31

0.1U/4/Y5V/16V/Z

R14

22/4/X

R16

22/4

R18

22/4/X

R20

22/4

BC32

0.1U/4/Y5V/16V/Z

FPGA25V FPGA25V

BC33

XC_M2

1

0.1U/4/Y5V/16V/Z

22/4/X

22/4

22/4/X

22/4

BC34

0.1U/4/Y5V/16V/Z

FPGA25VFPGA25V

R15

R17

R19

R21

L10 0/6S/X

FPGA25V

0.1U/4/Y5V/16V/Z

B B

CLOCK

BUFFER

A A

BC39

5

VCC25_CLK

0.1U/4/Y5V/16V/Z

BC40

0.1U/4/Y5V/16V/Z

BC41

0.1U/4/Y5V/16V/Z

SMBDATA2,5,6,7,8

5P/4/N/50V/X

BC42

SMBCLK2,5,6,7,8

C26

BC43

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

VCC25_CLK

DCLKO2

BC44

SMBCLK

SMBDATA

R25 10/6

R27 1K/6/X

BC45

0.1U/4/Y5V/16V/Z

5P/4/N/50V/XC1

4

U3

4

VDD2.5

11

VDD2.5

15

VDD2.5

21

VDD2.5

28

VDD2.5

34

VDD2.5

38

VDD2.5

45

VDD2.5

16

AVDD

12

SCLK

37

SDATA

33

FB_OUT

35

FB_INT

13

CLK_INT

17

AGND

1

GND

7

GND

8

GND

18

GND

24

GND

25

GND

31

GND

41

GND

42

GND

48

GND

ICS93735AF/S

CLKC0

CLKT0

CLKT1

CLKC1

CLKC2

CLKT2

CLKC3

CLKT3

CLKT4

CLKC4

CLKC9

CLKT9

CLKT8

CLKC8

CLKT7

CLKC7

CLKC6

CLKT6

CLKT5

CLKC5

R_CKOUT0

2

-R_CKOUT0

3

-R_CKOUT1

5

R_CKOUT1

6

R_CKOUT2

9

-R_CKOUT2

10

R_CKOUT3

19

-R_CKOUT3

20

-R_CKOUT4

22

R_CKOUT4

23

R_CKOUT5

26

-R_CKOUT5

27

-R_CKOUT6

29

R_CKOUT6

30

-R_CKOUT7

39

R_CKOUT7

40

R_CKOUT9

43

-R_CKOUT9

44

-R_CKOUT10

46

R_CKOUT10

47

14

N/C

32

N/C

36

N/C

3

RN1 22/8P4R/6

7 8

5 6

3 4

1

RN2 22/8P4R/6

7 8

5 6

3 4

1

RN3 22/8P4R/6

7 8

5 6

3 4

1

RN4 22/8P4R/6

7 8

5 6

3 4

1

R10122/6

R10222/6

RN5 22/8P4R/6

7 8

5 6

3 4

1

R104 22/6

R103 22/6

DCLK0

-DCLK0

-DCLK1

2

DCLK1

DCLK2

-DCLK2

DCLK3

2

-DCLK3

-DCLK4

DCLK4

DCLK5

2

-DCLK5

-DCLK6

DCLK6

-DCLK7

DCLK7

2

-DCLK8

DCLK8

DCLK9

-DCLK9

-DCLK10

DCLK10

2

-DCLK11

DCLK11

DCLK0 5

-DCLK0 5

-DCLK1 5

DCLK1 5

DCLK2 5

-DCLK2 5

DCLK3 5

-DCLK3 5

-DCLK4 5

DCLK4 5

DCLK5 5

-DCLK5 5

-DCLK6 6

DCLK6 6

-DCLK7 6

DCLK7 6

-DCLK8 6

DCLK8 6

DCLK9 6

-DCLK9 6

-DCLK10 6

DCLK10 6

-DCLK11 6

DCLK11 6

2

DCLK0

-DCLK0

DCLK1

-DCLK1

DCLK2

-DCLK2

DCLK3

-DCLK3

DCLK4

-DCLK4

DCLK5

-DCLK5

DCLK6

-DCLK6

DCLK7

-DCLK7

DCLK8

-DCLK8

DCLK9

-DCLK9

DCLK10

-DCLK10

DCLK11

-DCLK11

Title

Size Document Number Rev

Custom

Date: Sheet of

1

2

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

CN1

4

15P/8P4C/X

6

8

2

CN2

4

15P/8P4C/X

6

8

2

CN3

4

15P/8P4C/X

6

8

2

CN4

4

15P/8P4C/X

6

8

2

CN5

4

15P/8P4C/X

6

8

2

CN6

4

15P/8P4C/X

6

8

GIGABYTE CORP.

FPGA Configuration

GC-RAMDISK

1

3 11Monday, July 11, 2005

1.0

Place near to port

SSC_EN2

RESETn2

DMACKn2

DIOWn2

DIORn2

IORDY2

INTRQ2

DMARQ2

CS0n2

CS1n2

D D

OSC_SATA2

DA[0..2]2

DD[0..15]2

C C

5

SSC_EN

RESETn

DMACKn

DIOWn

DIORn

IORDY

INTRQ

DMARQ

CS0n

CS1n

OSC_SATA

DA0

DA1

DA2

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

DA2

DA0

DA1

INTRQ

DMACKn

IORDY

1_8V

GND

DIORn

DIOWn

DMARQ

DD15

DD0

DD14

DD1

JM20330/[10HP2-642033-10]

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

CS0n

48

U5

CS0n

DA2

DA0

DA1

GPIO2

INTRQ

DMACKn

IORDY

VCCK

GNDK

DIORn

DIOWn

DMARQ

DD15

DD0

DD14

DD1

DD13

123456789101112131415

DD13

4

VCC3

VCC3

1_8V

R31

CS1n

PATAOR

CS1n

VCC3

UAO

VCCO

PATAOR

10K/4

GND

GND

PHYRDY

1_8V

GND

UAI

VCCK

PMEN

GNDK

FXDMA

PHYRDY

CLKSEL1

JM20330

Device Normal Order

DD2

DD12

VCCO

DD3

DD11

DD4

GNDO

VCCK

DD10

DD5

DD9

DD10

1_8V

GND

DD5

DD4

DD2

DD12

VCC3

DD3

DD11

DD9

SSC_EN

VCC3

SSCEN

CLKSEL0

DD6

DD8

DD6

DD8

R281 0/4

333435363738394041424344454647

GPIO1

GPIO0

AGND

AVDDL

REXT

AGND

AVDDH

XTALO

XTALI

ATAIOEN

MODE2

MODE1

MODE0

PORn

DD7

RESETn

16

DD7

RESETn

VCC3 1_8VVCC3 1_8V1_8V

BC46

0.1U/4/Y5V/16V/Z

BC47

0.1U/4/Y5V/16V/Z

3

BC48

0.1U/4/Y5V/16V/Z

Bypass CAP, close to power pins

TXP

TXN

RXN

RXP

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

TXN

GND

AVDDL

RXN

RXP

REXT

GND

AVDDH

OSC_SATA

SA_MODE2

SA_MODE1

SA_MODE0

PORn

Close to Chip

VCC3

R32

12K/4

TXP

32

Place near to port

BC49

0.1U/4/Y5V/16V/Z

FB1

FB30/6/[10LF1-07300A-01]

0.01U/4/X7R/16V/KC3

0.01U/4/X7R/16V/KC4

0.01U/4/X7R/16V/KC5

0.01U/4/X7R/16V/KC6

BC93

10U/8/Y5V/10V/Z

BC50

0.1U/4/Y5V/16V/Z

BC51

1U/4/Y5V/6.3V/Z

VCC31_8V

FB2

FB30/6/[10LF1-07300A-01]

BC94

10U/8/Y5V/10V/Z

2

J1

7

7

6

6

5

5

4

4

3

3

2

2

1

1

SATA1/RED

BC52

1U/4/Y5V/6.3V/Z

VCC3

1

+

100U/D/10V/57

LEC1

U4 APL1087DC/SOT89/800mA

3

Vin

Port must close to

Chip as close as

possible. Max <1"

1

Vout

Vout

GND

R30

100/6/1

1

R29

220/6/1

1_8V

1

+

100U/D/10V/57

LEC2

2

4

R34 4.7K/4

IORDY

B B

VCC3

R33

R282 0/4

CODEREY3,10

A A

5

CODEREY

10K/6/X

PORn

BC53

0.1U/6/X7R/16V/K/X

4

DMARQ

INTRQ

DD7

PATAOR

3

R36 4.7K/4

R37 10K/4

R38 10K/4

R39 10K/4

VCC3

SA_MODE1

SA_MODE0

SA_MODE2

VCC3

Title

Size Document Number Rev

Custom

2

Date: Sheet of

GIGABYTE CORP.

JM20330 SATA BRIDGE

R35 330/6

PHYRDY

GC-RAMDISK

LED/B/6/S

4 11Monday, July 11, 2005

1

1.0

Loading...

Loading...