Gigabyte R96X128D Rev.2.0 Schematics

8

D D

7

6

5

4

3

2

1

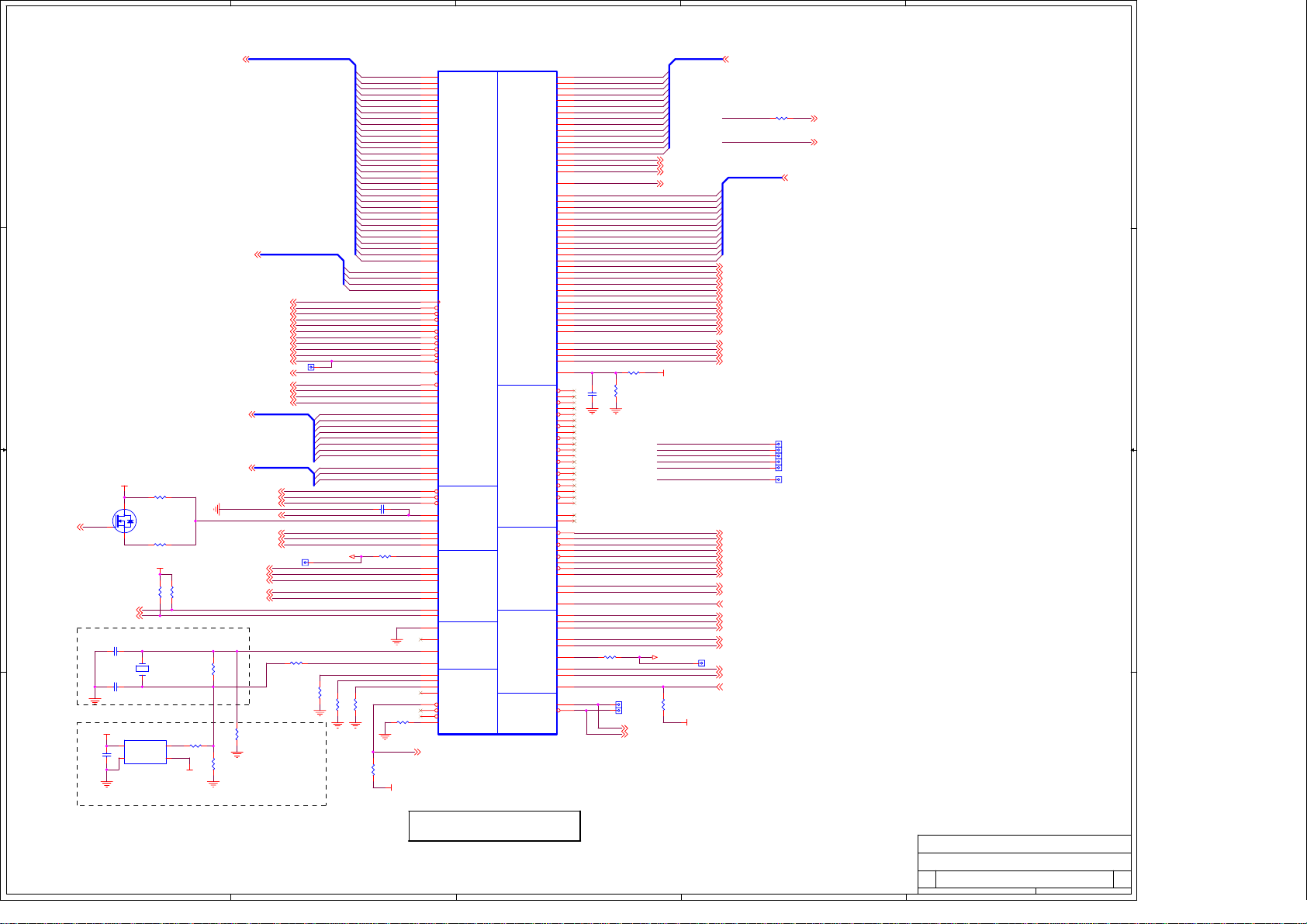

GIGABYTE GV-R96X128D

Schematics

TITLE

COVER SHEET

BOM & PCB MODIFY HISTORY

BLOCK DIAGRAM

AGP_4X/8X_BUS

C C

RV360 CORE

RV360 MEMORY INTERFACE

RV360 POWER

POWER_VDDC

SHEET

1

2

3

4

5

6

7

8

POWER_MVDDC 9

POWER_MVDDQ

10

SERIAL BIOS 11

VTT TERMINATION CH A 12

VTT TERMINATION CH B

BGA 4Mx32 DDR (a)

B B

BGA 4Mx32 DDR (b)

HIGH-DENSITY HEADER

OPTION STRAPS

DAC RGB FILTERS

VIDEO MUX & VIVO

TMDS & DVI-I

HEATSINK & MECHANICALS

MECHANICAL

ATI REV HISTORY

13

14

15

16

17

18

19

20

21

22

23

A A

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

B

8

7

6

5

4

3

Date: Sheet

2

COVER SHEET

GV-R96X128D

2.0

of

123Monday, January 03, 2005

1

5

4

3

2

1

Model Name: GV-R96X128D

Circuit or PCB layout change

for next version

Version: 2.0

PAGE Change Item Reason

D D

107.95mm X 171.45mm, 60+/-10%

Component value change history

PAGE Change Item Reason

03.10.21

03.11.18 CHANGE BOM FOR PVT

03.12.02

03.12.08 CHANGE PACKAGE

03.12.11 CHANGE STICKER

04.01.05

C C

04.01.13 REMOVE LM63CIMA

04.01.29 CHANGE TO SAMSUNG GC33 MEMORY

04.08.23

NEW MODEL ,NEW BOM FOR GIGABYTE

COMPONENT SOURCE

CHANGE R253 FROM

1.1K TO 1.24K

ADD SECOND SOURCE OF PERICOM

PI5V330W

CHANGE MODEL NAME TO R96X128D

2.0

03.10.17

03.11.11

03.12.08

ATI DEMO BOARD A034

20A

CHANGE VERSION TO

1.0

CHANGE VERSION TO

2.0

B B

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

GIGABYTE

BOM & PCB MODIFY HISTORY

GV-R96X128D 2.0

1

of

223Monday, January 03, 2005

5

4

3

2

1

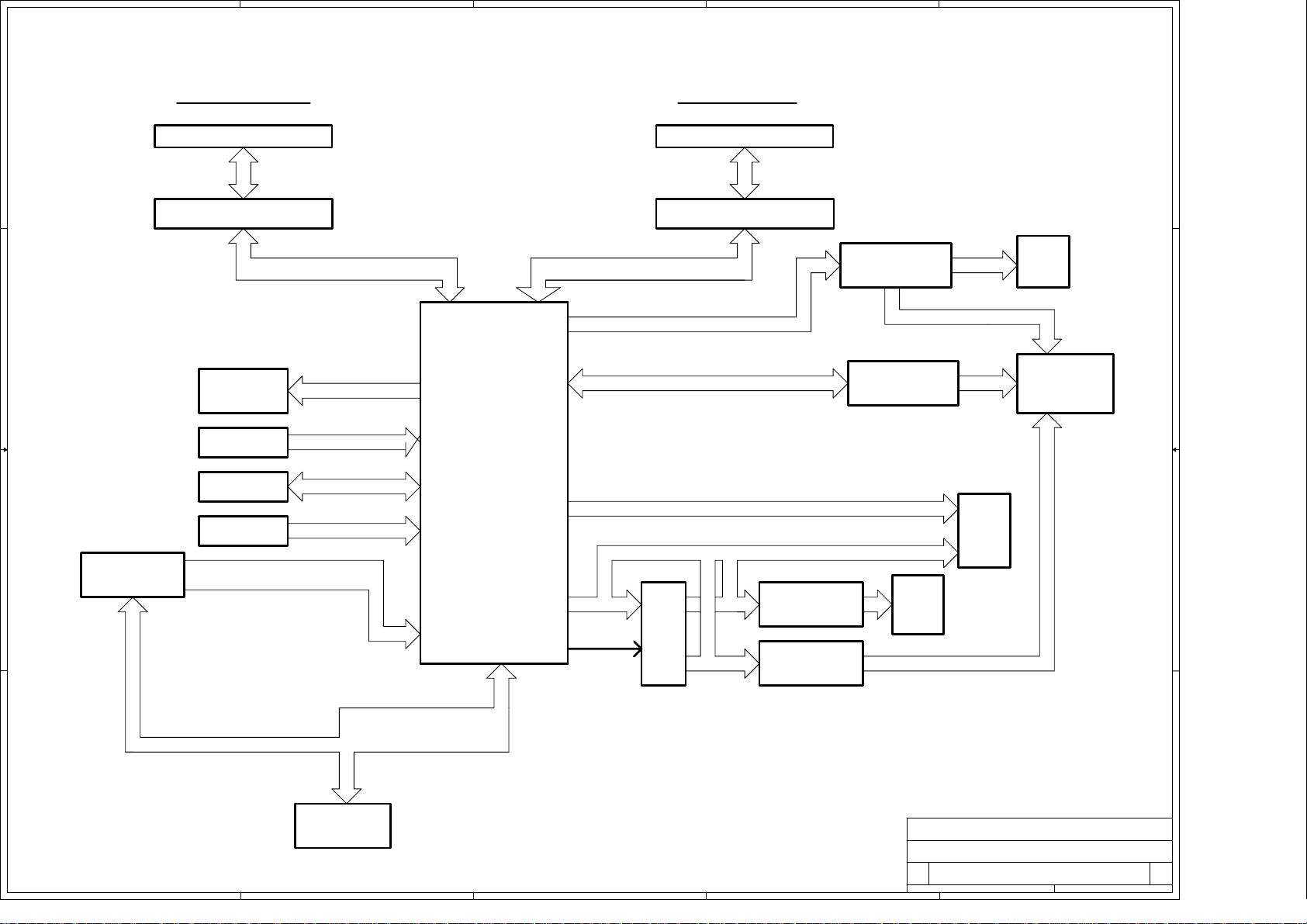

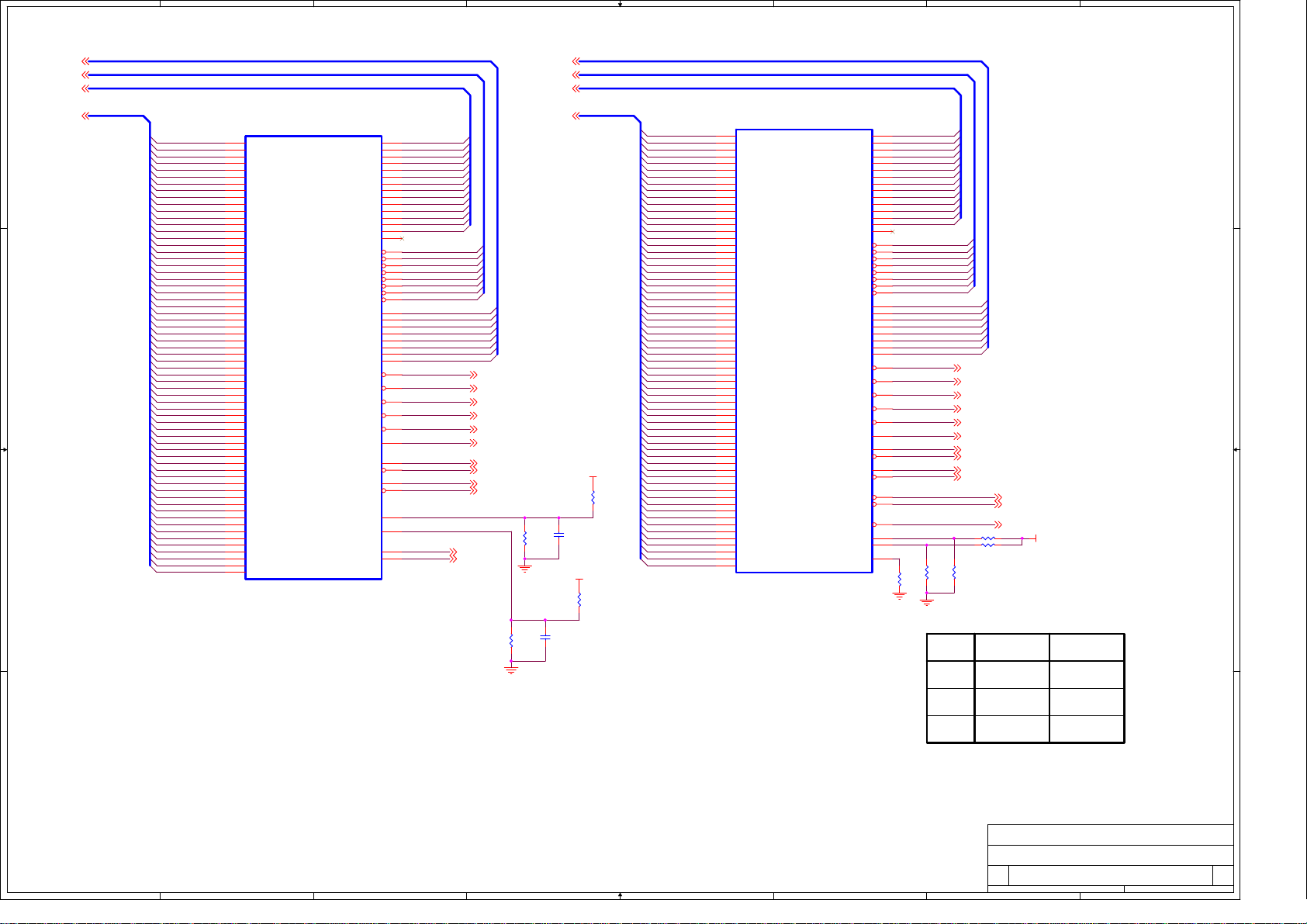

MEMORY CHANNEL A

D D

BGA Memory 4Mx32

MEMORY TERMINATIONS A

MDB[63..0] CS0B#

MA[14..0]

CASA#

RASA#

WEA#

QSA[7..0]

CS0A#MDA[63..0]

DQMA[0..7]

CLKA01CKEA

CLKA01#

MB[14..0]

CASB#

RASB#

WEA/B#

QSB[7..0]

MEMORY CHANNEL B

BGA Memory 4Mx32

MEMORY TERMINATIONS B

DQMB[0..7]

CKEB/D CLKB01

CLKB01#

PRIMARY CRT

LOGIC

VGA

DB15

CONN

MEM A MEM B

DAC1

C C

THERMAL

SENSOR

DPLUS DMINUS I2C_CLK I2C_DAT

TMDS

R G B HSY VSY DDC1DATA DDC1CLK

TMDS_TX[C,2..0]N TMDS_TX[C,2..0]P HPD, DDC2CLK DDC2DATA

INTEGRATED TMDS

LOGIC

DVI-I CONN

and/or VGA Slim

DB15 CONN

STRAPS

BIOS

HEATSINK/FAN

B B

POWER

REGULATION

VDDC VDDC_CT MVDDC MVDDQ VTT

PVDD TPVDD MPVDD

A2VDD Vref

ROMCS#

ROM

RV350

TVO

DDR DVO

VIP

DAC2

Y/R C/G COMP/B H2SYNC

D

E

DVO, VID ports

CRT2DDCDATA CRT2DDCCLK V2SYNC

TVOUT Filters

HDH

TVOUT

CONN

M

AGP/PCI

LCDDATA19

SEL

U

X

Secondary

CRT LOGIC

CPUCLK

TRDY#

INTR

ST2..0

WBF#

AD_STB0

STOP#

DEVSEL#

DBI_HI

SB_STB

AD_STB0#

RESET#

DBI_LO

SB_STB#

RBF#

Title

Size Document Number Rev

B

3

2

Date: Sheet

GIGABYTE

Block Diagram

GV-R96X128D 2.0

323Monday, January 03, 2005

1

of

CBE3..0

AD31..0

GNT#

IRDY#

FRAME#

CLK

AGPREF

+12V_BUS

+5V_BUS+3.3V_BUS

A A

5

+VDDQ_BUS

AGP BUS

4X/8X

AD_STB1

4

SBA[7..0]

AD_STB1#

PAR

REQ#

8

7

6

5

4

3

2

1

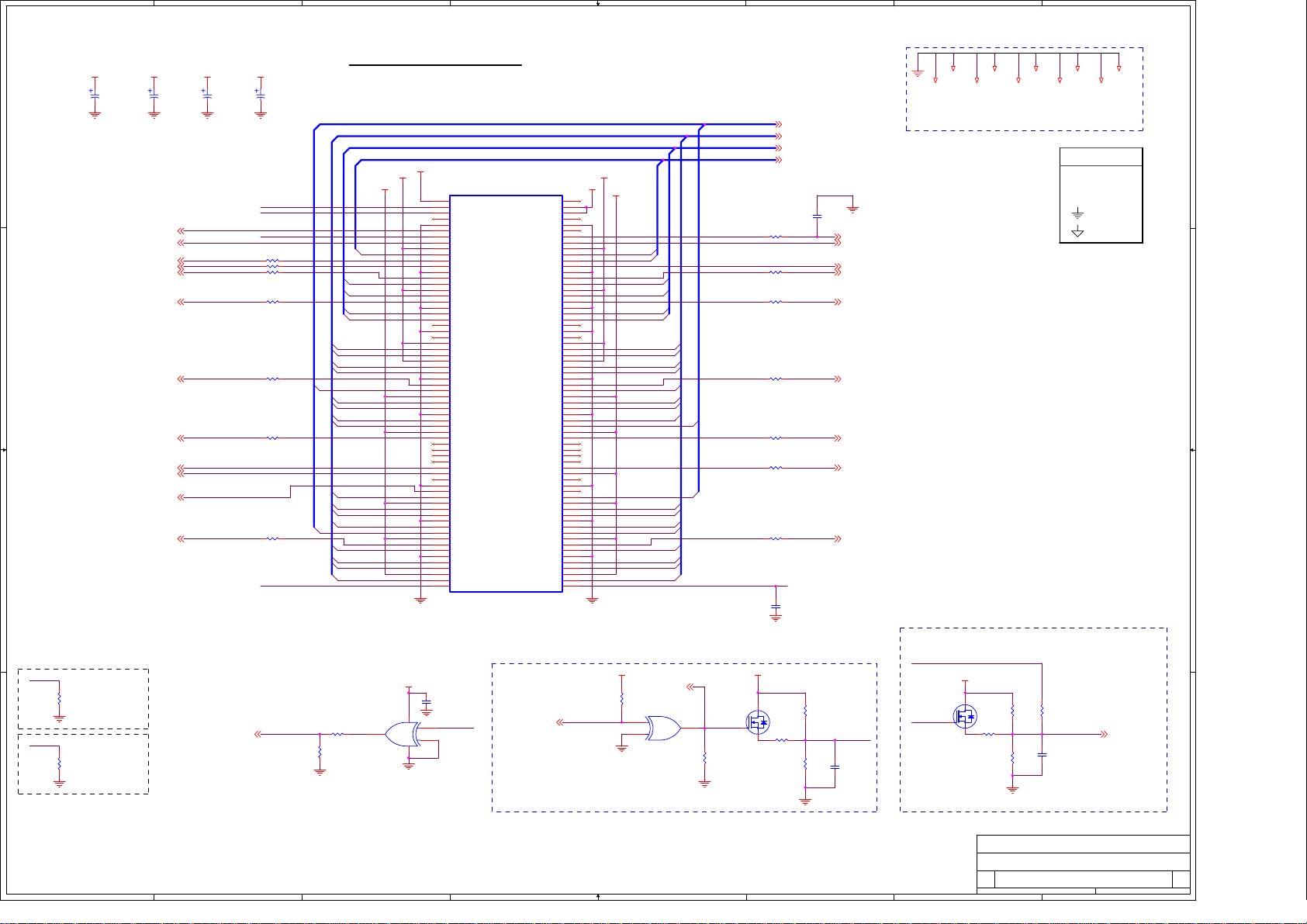

4X/8X AGP BUS

+12V_BUS +5V_BUS +3.3V_BUS GND_TPVSSGND_MPVSS

C10

100U/S/16V/65

D D

C C

B B

C5

100U/S/16V/65

AGP_INTR#(5)

AGP_GNT#(5)

AGP_MB_8X_DET#(5)

AGP_DBI_HI(5)

AGP_WBF#(5)

AGP_SBSTB#(5)

AGP_ADSTB1#(5)

AGP_FRAME#(5)

AGP_TRDY#(5)

AGP_STOP#(5)

AGP_PAR(5)

AGP_ADSTB0#(5)

C8

100U/S/16V/65

+VDDQ_BUS

TYDET

AGP_GC_8X_DET#

AGP_RST#

R15 0/6/S

R16 0/6/S

R18 0/6/S

R1 0/6

R5 0/6/S

R7 0/6

R12 0/6/S

AGP_VREFGC

USE 47uF TANTALUM

C2

CAPACITOR OR HIGHER

47U/S/6.3V/56

>=6.3V

+12V_BUS

+3.3V_BUS

+VDDQ_BUS

AGP_ST1

AGP_SBA1

AGP_SBA3

AGP_SBA5

AGP_SBA7

AGP_AD30

AGP_AD28

AGP_AD26

AGP_AD24

AGP_C/BE#3

AGP_AD22

AGP_AD20 AGP_AD19

AGP_AD18

AGP_AD16

AGP_PAR_R

AGP_AD15

AGP_AD13

AGP_AD11

AGP_AD9

AGP_C/BE#0

AGP_AD6

AGP_AD4

AGP_AD2

AGP_AD0

MAGP1

A1

12V

A2

TYPEDET#

A3

GC_DET#/RESERVED

A4

USB-

A5

GND

A6

INTA#

A7

RST#

A8

GNT#

A9

VCC3.3

A10

ST1

A11

MB_DET#/RESERVED

A12

DBI_HI/PIPE#

A13

GND

A14

WBF#

A15

SBA1

A16

VCC3.3

A17

SBA3

A18

SB_STB#

A19

GND

A20

SBA5

A21

SBA7

A22

RESERVED

A23

GND

A24

RESERVED

A25

VCC3.3

A26

AD30

A27

AD28

A28

VCC3.3

A29

AD26

A30

AD24

A31

GND

A32

AD_STB1#

A33

C/BE3#

A34

VDDQ1.5

A35

AD22

A36

AD20

A37

GND

A38

AD18

A39

AD16

A40

VDDQ1.5

A41

FRAME#

A42

KEY

A43

KEY

A44

KEY

A45

KEY

A46

TRDY#

A47

STOP#

A48

PME#

A49

GND

A50

PAR

A51

AD15

A52

VDDQ1.5

A53

AD13

A54

AD11

A55

GND

A56

AD9

A57

C/BE0#

A58

VDDQ1.5

A59

AD_STB0#

A60

AD6

A61

GND

A62

AD4

A63

AD2

A64

VDDQ1.5

A65

AD0

A66

VREFGC

1.5V_AGP_BUS/X

614NOPN062

OVRCNT#

DBI_LO/RESERVED

SB_STB

RESERVED

3.3VAUX

AD_STB1

VDDQ1.5

VDDQ1.5

DEVSEL#

VDDQ1.5

VDDQ1.5

VDDQ1.5

AD_STB0

VDDQ1.5

VREFCG

USB+

INTB#

REQ#

VCC3.3

RBF#

SBA0

VCC3.3

SBA2

SBA4

SBA6

VCC3.3

AD31

AD29

VCC3.3

AD27

AD25

AD23

AD21

AD19

AD17

C/BE2#

IRDY#

PERR#

SERR#

C/BE1#

AD14

AD12

AD10

+3.3V_BUS

+5V_BUS

+VDDQ_BUS

B1

B2

5.0V

B3

5.0V

B4

B5

GND

B6

B7

CLK

B8

B9

B10

ST0

B11

ST2

B12

B13

GND

B14

B15

B16

B17

B18

B19

GND

B20

B21

B22

B23

GND

B24

B25

B26

B27

B28

B29

B30

B31

GND

B32

B33

B34

B35

B36

B37

GND

B38

B39

B40

B41

B42

KEY

B43

KEY

B44

KEY

B45

KEY

B46

B47

B48

B49

GND

B50

B51

B52

B53

B54

B55

GND

B56

B57

AD8

B58

B59

B60

AD7

B61

GND

B62

AD5

B63

AD3

B64

B65

AD1

B66

AGP_ST0

AGP_ST2

AGP_SBA0

AGP_SBA2

AGP_SBA4

AGP_SBA6

AGP_AD31

AGP_AD29

AGP_AD27

AGP_AD25

AGP_AD23

AGP_AD21

AGP_AD17

AGP_C/BE#2

AGP_C/BE#1

AGP_AD14

AGP_AD12

AGP_AD10

AGP_AD8

AGP_AD7

AGP_AD5

AGP_AD3

AGP_AD1

AGP_C/BE#[3..0]

AGP_AD[31..0]

AGP_SBA[7..0]

AGP_ST[2..0]

AGP_AGPCLK_R

AGP_DBI_LO_R

AGP_SBSTB_R

AGP_ADSTB1_R

AGP_ADSTB0_R

AGP_AGPREF

AGP_C/BE#[3..0] (5)

AGP_AD[31..0] (5)

AGP_SBA[7..0] (5)

AGP_ST[2..0] (5)

R61 0/6

R62 0/6/S

R2 0/6

R6 0/6/S

R8 0/6

R10 0/6

R13 0/6

C1

1U/6/Y/10V/X

C4

10P/6/N/50V/X

AGP_AGPCLK (5)

AGP_REQ# (5)

AGP_RBF# (5)

AGP_DBI_LO (5)

AGP_SBSTB (5)

AGP_ADSTB1 (5)

AGP_IRDY# (5)

AGP_DEVSEL# (5)

AGP_ADSTB0 (5)

GND_PVSS GND_TXVSSR

NOTE: THIS IS A DRAWING. THESE

GROUNDS MUST BE MANUALLY

CONNECTED TO THE GROUND PLANE

GND_A2VSSN

GND_A2VSSQ

GND_AVSSQ GND_RSET

GND_R2SETGND_AVSSN

SYMBOL LEGEND

DNI

DO NOT

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

UNIVERSAL VREFCG CIRCUIT (4X, 8X)

AGP_AGPREF

TEST

2N7002E/SOT23/S

+VDDQ_BUS

32

1

Q5

2

R66

R64

324/6/1/S

0/6/X

R67

147/6/1/S

Title

Size Document Number Rev

C

Date: Sheet

AGP_AGPREFCG

C7

R65

0.01U/6/X/50V/S

100/6/1/S

*

GIGABYTE

VAGP_4X/8X_BUS

GV-R96X128D 2.0

AGP_AGPREFCG (5)

of

423Monday, January 03, 2005

1

TEST

R23

1K/6

+VDDQ_BUS+3.3V_BUS

1

Q1

2N7002E/SOT23

32

R21

147/6/1

R20

324/6/1

R24

100/6/1/S

3

AGP_VREFGC

C6

0.01U/6/X/50V/S

*

TYDET

AGP_GC_8X_DET#

A A

R19

2.2/6

R60

0/6/S

For retail, 1K ohm

pull-down causes AMD

system detects

AGP2X only

+12V, TYPEDET#

short protection

for OEM (1KR)

+5V_BUS

C11

1U/6/Y/10V

147

AGP_RST#

1

2

AGP_RESET#(5,16)

R4

180/6

R3

100/6

3

U6A

SN74ACT86D/SO14

AGP_MB_8X_DET#(5)

AGP_MB_8X_DET#

R17

47K/6

4

5

8X_DET#(5)

6

U6B

SN74ACT86D/SO14

UNIVERSAL VREFGC CIRCUIT (4X, 8X)

8

7

6

5

4

5

4

3

2

1

AGP_AD[31..0](4)

D D

*

AGP_C/BE#[3..0](4)

C C

AGP_SBA[7..0](4)

R46

4.7K/6/S

AGP_ST[2..0](4)

AGP_AGPREFCG(4)

AGP_MB_8X_DET#(4)

A_R/C_DAC2(16,19)

A_G/Y_DAC2(16,19)

A_B/COMP_DAC2(16,19)

A_HSYNC_DAC2(18)

A_VSYNC_DAC2(18)

+VDDQ_BUS

R37

32

47/6/S

Q2

2N7002E/SOT23/X

8X_DET#(4)

B B

1

R38

71.5/6/1/X

+3.3V_BUS

R45

4.7K/6/S

SCL(16,21)

SDA(16,21)

OPTION 1: Crystal Circuit

C71

22P/6/X

+3.3V_BUS

C3

0.1U/6/X/16V

A A

C72

22P/6/X

8

4

2 1

Y2

VDD

GND

27.000MHz/D

Y1

27_MHZ/X

OUT

E/D

5

1

+3.3V_BUS

R27

150/6

R32

1M/6/X

R28

100/6/1

OPTION 2: Oscillator Circuit

5

AGP_AD[31..0]

AGP_C/BE#[3..0]

AGP_AGPCLK(4)

AGP_RESET#(4,16)

AGP_REQ#(4)

AGP_GNT#(4)

AGP_PAR(4)

AGP_STOP#(4)

AGP_DEVSEL#(4)

AGP_TRDY#(4)

AGP_IRDY#(4)

AGP_FRAME#(4)

AGP_INTR#(4)

AGP_WBF#(4)

AGP_RBF#(4)

AGP_ADSTB0(4)

AGP_ADSTB1(4)

AGP_SBSTB(4)

AGP_SBA[7..0]

AGP_ST[2..0]

AGP_SBSTB#(4)

AGP_ADSTB0#(4)

AGP_ADSTB1#(4)

AGP_DBI_LO(4)

AGP_DBI_HI(4)

R29

0/8

OSCILLATOR CAN BE

CONNECTED TO XTALIN

OR XTALOUT

When RV350_XTALOUT is

used by the oscillator, XTALIN

should be grounded to prevent

the input buffers from picking

up noise.

OPTIONAL SCAN PIN_PERMISSION

TP10

PLACE C83 CLOSE TO ASIC PIN

GND_R2SET

TP6

R14

0/6

R33

0/6

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

C83 0.1U/6/X/16V/S

R40 715/6/1

TESTEN

R42

0/6/S

R41

0/6/S

R36

4.7K/6

4

U1A

H29

AD0

Part 1 of 6

H28

AD1

J29

AD2

J28

AD3

K29

AD4

K28

AD5

L29

AD6

L28

AD7

N28

AD8

P29

AD9

P28

AD10

R29

AD11

R28

AD12

T29

AD13

T28

AD14

U29

AD15

N25

AD16

R26

AD17

P25

AD18

R27

AD19

R25

AD20

T25

AD21

T26

AD22

U25

AD23

V27

AD24

W26

AD25

W25

AD26

Y26

AD27

Y25

AD28

AA26

AD29

AA25

AD30

AA27

AD31

N29

C/BE#0

U28

C/BE#1

P26

C/BE#2

U26

C/BE#3

AG30

PCICLK

AG28

RST#

AF28

REQ#

AD26

GNT#

M25

PAR

N26

STOP#

V29

DEVSEL#

V28

TRDY#

W29

IRDY#

W28

FRAME#

AE26

INTA#

AC26

WBF#

AE29

RBF#

M28

AD_STBF_0

V25

AD_STBF_1

AB29

SB_STBF

AD28

SBA0

AD29

SBA1

AC28

SBA2

AC29

SBA3

AA28

SBA4

AA29

SBA5

Y28

SBA6

Y29

SBA7

AF29

ST0

AD27

ST1

AE28

ST2

AB28

SB_STBS

M29

ADSTBS_0

V26

ADSTBS_1

M26

AGPREF

M27

AGPTEST

AB26

DBI_LO

AB25

DBI_HI

AC25

AGP_DET#

AK21

R2SET

AJ23

C_R

AJ22

Y_G

AK22

COMP_B

AJ24

H2SYNC

AK24

V2SYNC

AG23

DDC3CLK

AG24

DDC3DATA

AK25

NC

AJ25

NC

AH28

XTALIN

AJ29

XTALOUT

AH27

TESTEN

E8

TEST_YCLK

B6

TEST_MCLK

AE25

PLLTEST

AG26

STEREOSYNC

AH30

NC

AH29

NC

AG29

RSTB_MSK

R30

RV360

0/6

STEREOSYNC (19)

+3.3V_BUS

IT IS RECOMMENDED TO ALLOW SERIES RESISTOR

FOOT PRINTS ON THE INDICATED AGP CONTROL SIGNALS

TO ADDRESS ANY LAYOUT NOISE RELATED

SIGNAL DAMPING REQUIREMENTS

AGP

PCI / AGPAGP2X4X

8X

DAC2CLK

ZV_LCDDATA0

ZV_LCDDATA1

ZV_LCDDATA2

ZV_LCDDATA3

ZV_LCDDATA4

ZV_LCDDATA5

ZV_LCDDATA6

ZV_LCDDATA7

ZV_LCDDATA8

ZV_LCDDATA9

DVO / EXT TMDS / GPIOTMDSDAC1

ZV_LCDDATA10

ZV_LCDDATA11

ZV_LCDDATA12

ZV_LCDDATA13

ZV_LCDDATA14

ZV_LCDDATA15

ZV_LCDDATA16

ZV_LCDDATA17

ZV_LCDDATA18

ZV_LCDDATA19

ZV_LCDDATA20

ZV_LCDDATA21

ZV_LCDDATA22

ZV_LCDDATA23

ZV_LCDCNTL0

ZV_LCDCNTL1

ZV_LCDCNTL2

ZV_LCDCNTL3

THERM

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

DVOMODE

VREFG

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

DDC2CLK

DDC2DATA

HPD1

HSYNC

VSYNC

RSET

DDC1DATA

DDC1CLK

AUXWIN

DPLUS

DMINUS

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

R

G

B

AJ5

AH5

AJ4

AK4

AH4

AF4

AJ3

AK3

AH3

AJ2

AH2

AH1

AG3

AG1

AG2

AF3

AF2

AE10

AH6

AJ6

AK6

AH7

AK7

AJ7

AH8

AJ8

AH9

AJ9

AK9

AH10

AE6

AG6

AF6

AE7

AF7

AE8

AG8

AF8

AE9

AF9

AG10

AF10

AJ10

AK10

AJ11

AH11

AG4

AK16

AH16

AH17

AJ16

AH18

AJ17

AK19

AH19

AK18

AJ18

AG16

AF16

AG17

AF17

AF18

AE18

AH20

AG20

AF19

AG19

AE12

AG12

AJ13

AH14

AJ14

AH15

AJ15

AK15

AH13

AK13

AE13

AE14

AF12

AK27

AJ27

AJ26

AG25

AH25

AH26

AF25

AF24

AF26

AF11

AE11

AUXWIN

3

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

DVOMODE

VID/DVO0

VID/DVO1

VID/DVO2

VID/DVO3

VID/DVO4

VID/DVO5

VID/DVO6

VID/DVO7

VID/DVO8

VID/DVO9

VID/DVO10

VID/DVO11

VID/DVO12

VID/DVO13

VID/DVO14

VID/DVO15

VID/DVO16

VID/DVO17

VID/DVO18

VID/DVO19

VID/DVO20

VID/DVO21

VID/DVO22

VID/DVO23

LCDCNTL0

LCDCNTL1

LCDCNTL2

LCDCNTL3

R34

1K/6/1/S

C74

0.1U/6/X/16V/S

R39 499/6/1/S

TP11

TP12

D+ (21)

D- (21)

GPIO[13..0]

HPD_ExtTMDS (16)

Mem_Strap1 (17)

Mem_Strap0 (17)

DVOMODE (16,17)

+3.3V_BUS

R35

1K/6/1/S

Boundary scan test

A_HSYNC_DAC1

SCL

CRT1DDCDATA

CRT1DDCCLK

A_VSYNC_DAC1

TESTEN

GND_RSET

R63

4.7K/6/S

TP7

+3.3V_BUS

GPIO[13..0] (11,16,17)

GPIO7

GPIO10

VID/DVO[11..0]

PKGTYPE (17)

DC_Strap2 (16)

DC_Strap3 (16,19)

DC_Strap4 (16)

LCDDATA16 (17)

LCDDATA17 (17)

PAL/NTSC (16)

DEMUX_SEL (16,19)

VHAD0 (16,17)

VHAD1 (16)

VPHCTL (16)

CLK_VIPCLK (16)

LCDCNTL0 (16)

LCDCNTL1 (16)

LCDCNTL2 (16)

CLK_VID/DVO (16)

TRST/

TDO

TDI

TMS

TCK

TMDS_TX0N (20)

TMDS_TX0P (20)

TMDS_TX1N (20)

TMDS_TX1P (20)

TMDS_TX2N (20)

TMDS_TX2P (20)

TMDS_TXCN (20)

TMDS_TXCP (20)

DVIDDCCLK (18)

DVIDDCDATA (18)

HPD (20)

A_R_DAC1 (18)

A_G_DAC1 (18)

A_B_DAC1 (18)

A_HSYNC_DAC1 (18)

A_VSYNC_DAC1 (18)

CRT1DDCDATA (18)

CRT1DDCCLK (18)

INT_ALERT (21)

R31

0/6/S

VID/DVO[11..0] (16)

TP1

TP2

TP3

TP4

TP5

TP8

2

EXT_PWR (9)

DC_Strap1 (11,16)

Title

Size Document Number Rev

Custom

Date: Sheet

GIGABYTE

RV350 core

GV-R96X128D 2.0

1

of

523Monday, January 03, 2005

1

2

3

4

5

6

7

8

QSA[7..0](12) QSB[7..0](13)

DQMA#[7..0](12)

MAA[13..0](12)

MDA[63..0](12)

A A

B B

C C

QSA[7..0]

DQMA#[7..0]

MAA[13..0]

MDA[63..0]

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

DQMB#[7..0](13)

MAB[13..0](13)

MDB[63..0](13)

U1B

L25

DQA0

L26

DQA1

K25

DQA2

K26

DQA3

J26

DQA4

H25

DQA5

H26

DQA6

G26

DQA7

G30

DQA8

D29

DQA9

D28

DQA10

E28

DQA11

E29

DQA12

G29

DQA13

G28

DQA14

F28

DQA15

G25

DQA16

F26

DQA17

E26

DQA18

F25

DQA19

E24

DQA20

F23

DQA21

E23

DQA22

D22

DQA23

B29

DQA24

C29

DQA25

C25

DQA26

C27

DQA27

B28

DQA28

B25

DQA29

C26

DQA30

B26

DQA31

F17

DQA32

E17

DQA33

D16

DQA34

F16

DQA35

E15

DQA36

F14

DQA37

E14

DQA38

F13

DQA39

C17

DQA40

B18

DQA41

B17

DQA42

B15

DQA43

C13

DQA44

B14

DQA45

C14

DQA46

C16

DQA47

A13

DQA48

A12

DQA49

C12

DQA50

B12

DQA51

C10

DQA52

C9

DQA53

B9

DQA54

B10

DQA55

E13

DQA56

E12

DQA57

E10

DQA58

F12

DQA59

F11

DQA60

E9

DQA61

F9

DQA62

F8

DQA63

RV360

Part 2 of 6

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

RASA#

CASA#

WEA#

CSA0#

CSA1#

CKEA

CLKA0

CLKA0#

CLKA1

CLKA1#

MEMORY INTERFACE

A

MVREFD

MVREFS

DIMA_0

DIMA_1

MAA0

E22

MAA1

B22

MAA2

B23

MAA3

B24

MAA4

C23

MAA5

C22

MAA6

F22

MAA7

F21

MAA8

C21

MAA9

A24

MAA10

C24

MAA11

A25

MAA12

E21

MAA13

B20

C19

DQMA#0

J25

DQMA#1

F29

DQMA#2

E25

DQMA#3

A27

DQMA#4

F15

DQMA#5

C15

DQMA#6

C11

DQMA#7

E11

QSA0

J27

QSA1

F30

QSA2

F24

QSA3

B27

QSA4

E16

QSA5

B16

QSA6

B11

QSA7

F10

RASA#

A19

CASA#

E18

WEA#

E19

CSA#0

E20

CSA#1

F20

CKEA

B19

CLKA0

B21

CLKA#0

C20

CLKA1

C18

CLKA#1

A18

B7

B8

DIMA0

D30

DIMA1

B13

RASA# (12)

CASA# (12)

WEA# (12)

CSA#0 (12)

CSA#1 (12)

CKEA (12)

CLKA0 (12,14,15)

CLKA#0 (12,14,15)

CLKA1 (12,14,15)

CLKA#1 (12,14,15)

DIMA0 (14,15)

DIMA1 (14,15)

R57

100/6/1/S

QSB[7..0]

DQMB#[7..0]

MAB[13..0]

MDB[63..0]

+MVDDQ

C151

0.1U/6/X/16V/S

+MVDDQ

R58

47/6/S

R56

133/6/1/S

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

U1C

D7

DQB0

F7

DQB1

E7

DQB2

G6

DQB3

G5

DQB4

F5

DQB5

E5

DQB6

C4

DQB7

B5

DQB8

C5

DQB9

A4

DQB10

B4

DQB11

C2

DQB12

D3

DQB13

D1

DQB14

D2

DQB15

G4

DQB16

H6

DQB17

H5

DQB18

J6

DQB19

K5

DQB20

K4

DQB21

L6

DQB22

L5

DQB23

G2

DQB24

F3

DQB25

H2

DQB26

E2

DQB27

F2

DQB28

J3

DQB29

F1

DQB30

H3

DQB31

U6

DQB32

U5

DQB33

U3

DQB34

V6

DQB35

W5

DQB36

W4

DQB37

Y6

DQB38

Y5

DQB39

U2

DQB40

V2

DQB41

V1

DQB42

V3

DQB43

W3

DQB44

Y2

DQB45

Y3

DQB46

AA2

DQB47

AA6

DQB48

AA5

DQB49

AB6

DQB50

AB5

DQB51

AD6

DQB52

AD5

DQB53

AE5

DQB54

AE4

DQB55

AB2

DQB56

AB3

DQB57

AC2

DQB58

AC3

DQB59

AD3

DQB60

AE1

DQB61

AE2

DQB62

AE3

DQB63

Part 3 of 6

RV360

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

RASB#

CASB#

WEB#

CSB0#

CSB1#

MEMORY INTERFACE

B

CKEB

CLKB0

CLKB0#

CLKB1

CLKB1#

DIMB_0

DIMB_1

ROMCS#

MEMVMODE_0

MEMVMODE_1

MEMTEST

MAB0

N5

MAB1

M1

MAB2

M3

MAB3

L3

MAB4

L2

MAB5

M2

MAB6

M5

MAB7

P6

MAB8

N3

MAB9

K2

MAB10

K3

MAB11

J2

MAB12

P5

MAB13

P3

P2

DQMB#0

E6

DQMB#1

B2

DQMB#2

J5

DQMB#3

G3

DQMB#4

W6

DQMB#5

W2

DQMB#6

AC6

DQMB#7

AD2

QSB0

F6

QSB1

B3

QSB2

K6

QSB3

G1

QSB4

V5

QSB5

W1

QSB6

AC5

QSB7

AD1

RASB#

R2

CASB#

T5

WEB#

T6

CSB#0

R5

CSB#1

R6

CKEB

R3

CLKB0

N1

CLKB#0

N2

CLKB1

T2

CLKB#1

T3

DIMB0

E3

DIMB1

AA3

AF5

C6

C7

C8

R55

47/6/S

R53

4.7K/6

RASB# (13)

CASB# (13)

WEB# (13)

CSB#0 (13)

CSB#1 (13)

CKEB (13)

CLKB0 (13,14,15)

CLKB#0 (13,14,15)

CLKB1 (13,14,15)

CLKB#1 (13,14,15)

R51 4.7K/6

R52 4.7K/6/X

R54

4.7K/6/X

DIMB0 (14,15)

DIMB1 (14,15)

ROMCS# (11)

+VDDC_CT

C152

R59

0.1U/6/X/16V

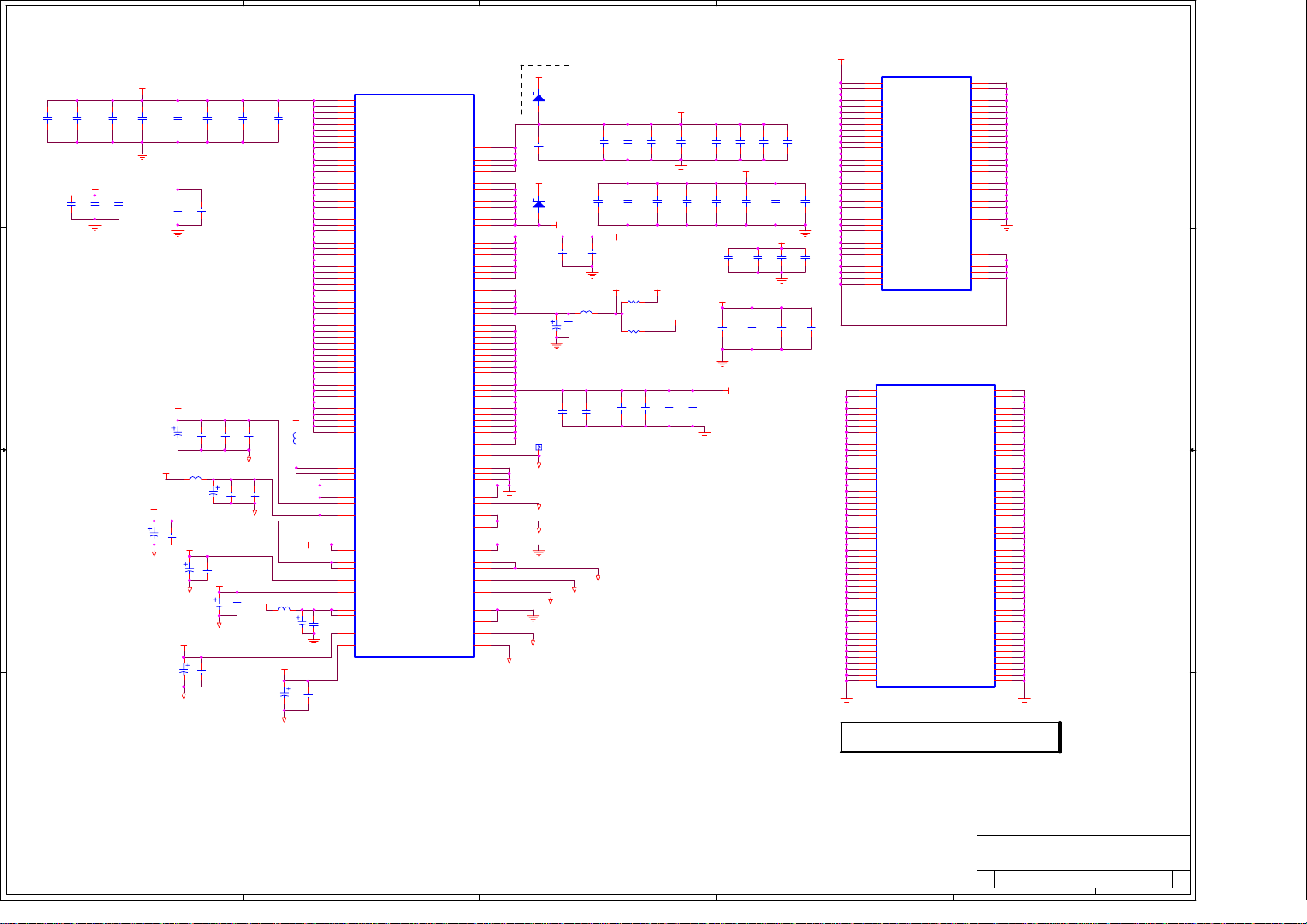

MEMORY CHANNEL A

D D

1

2

3

51/6/S

4

MEMORY CHANNEL B

5

VDDR1 MEMVMODE_0 MEMVMODE_1

1.8V

2.5V

2.8V

6

+VDDC_CT GND

+VDDC_CT +VDDC_CT

Title

Size Document Number Rev

Custom

Date: Sheet

7

+VDDC_CTGND

GIGABYTE

RV350 memory interface

GV-R96X128D 2.0

623Monday, January 03, 2005

of

8

5

+MVDDQ

8 1

1U/6/Y/10V/S

CP6A

10N/8P4C/S

C32

D D

C C

B B

CP6B

7 2

10N/8P4C/S

+MVDDQ

CP6C

10N/8P4C/S

6 3

C35

C33

1U/6/Y/10V/S

1U/6/Y/10V/S

10U/12/X5R/6.3V/S

10U/12/X5R/6.3V/S

GND_A2VSSN

CP6D

10N/8P4C/S

5 4

+MVDDQ

C57

+VDDR4

10U/12/X5R/6.3V/S

+A2VDD

C61

10U/12/X5R/6.3V/S

GND_A2VSSQ

10U/12/X5R/6.3V/S

+PVDD

C54

10U/12/X5R/6.3V

GND_PVSS

CP5A

10N/8P4C/S

8 1

C39

10U/12/Y/10V/S

+TPVDD

B11

200/8/S/S

C62

1U/6/Y/10V/S

+A2VDDQ

C63

C59

C67

CP5B

10N/8P4C/S

7 2

C38

10U/12/Y/10V/S

C43

1U/6/Y/10V

C64

1U/6/Y/10V/S

+AVDD

GND_AVSSN

C53

1U/6/Y/10V/S

CP5C

10N/8P4C/S

6 3

C73

C58

100P/6/N/50V

1U/6/Y/10V

GND_TPVSS

C60

1U/6/Y/10V/S

C81

100P/6/N/50V/S

GND_TXVSSR

+VDDR4

C68

1U/6/Y/10V/S

10U/12/X5R/6.3V/S

10U/12/X5R/6.3V/S

GND_MPVSS

+MPVDD

C52

CP5D

5 4

10N/8P4C/S

+A2VDD

+MVDDQ

B12 200/8/S/S

C66

B10

200/8/S

C51

1U/6/Y/10V

4

U1D

T7

VDDR1

R4

R1

N8

N7

M4

L27

L8

J24

J23

J8

J7

J4

J1

H10

H13

H15

H17

T8

V4

V7

V8

AA1

AA4

AA7

AA8

A3

A9

A15

A21

A28

B1

B30

D26

D23

D20

D17

D14

D11

D8

D5

E27

F4

G7

G10

G13

G15

G19

G22

G27

H22

H19

AD4

T4

N4

D19

D13

AE17

AE20

AE15

AF21

AJ20

AK12 AJ12

AF13

AF14

F18

N6

AG21

AH21

AF22

AH24

AE24

AE22

C65

1U/6/Y/10V/S

AK28 AJ28

A7 A6

Part 4 of 6

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

I/O

NC

NC

NC

NC

NC

TPVDD TPVSS

TXVDDR

TXVDDR

VDDRH0

VDDRH1

A2VDD

A2VDD

A2VDDQ

AVDD

VDD1DI

VDD2DI

PVDD PVSS

MPVDD MPVSS

RV360

POWER

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC15

VDDC15

VDDC15

VDDC15

VDDC15

VDDC15

VDDC15

VDDC15

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR4

VDDR4

VDDR4

VDDR4

VDDR4

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

AVSSQ

TXVSSR

TXVSSR

TXVSSR

VSSRH0

VSSRH1

A2VSSN

A2VSSN

A2VSSQ

AVSSN

VSS1DI

VSS2DI

3

DIODE SUPPLIES POWER

TO VDDC RAIL

WHILE VDDC REGULATOR

STABALIZES DURING POWER ON

+3.3V_BUS

D30

MMSZ4681T1/2.4V/S

2 1

8 1

CP3A

10N/8P4C/S

8 1

C44

1U/6/Y/10V/S

C46

1U/6/Y/10V/S

+VDD_DVO

B53 200/8/S/S

C69

1U/6/Y/10V/S

C36

1U/6/Y/10V/S

C37

1U/6/Y/10V/S

GND_A2VSSN

CP2A

10N/8P4C/S

+3.3V_BUS

8 1

C24

AC13

AD13

AD15

AC15

AC17

P8

Y8

AC11

AC20

Y23

L23

H20

H11

AD7

AD19

AD21

AD22

AC22

AC21

AC19

AC8

AG7

AD9

AC9

AC10

AD10

J30

AF27

AE30

AC27

AC23

AB30

AA24

AA23

Y27

W30

V23

V24

M23

M24

N30

P23

P27

T23

T24

T30

U27

AD24

AF20

NC

AE19

NC

AE16

NC

AF15

NC

AJ19

NC

AH12

AG13

AG14

F19

M6

AH22

AJ21

AF23

AH23

AE23

AE21

GND_MPVSS

10U/12/Y/10V/S

+3.3V_BUS

2 1

C70

10U/12/X5R/6.3V/S

>= 6.3V

TP9

GND_AVSSQ

GND_TPVSS

GND_TXVSSR

GND_AVSSN

GND_PVSS

D31

MMSZ4681T1/2.4V/S/S

+VDDC_CT

GND_A2VSSQ

CP2B

7 2

10N/8P4C/S

7 2

CP3B

10N/8P4C/S

CP9A

10N/8P4C/S

CP2C

10N/8P4C/S

6 3

6 3

+VDDR4

R68

0/6/X

R69

0/6/S

CP9B

7 2

10N/8P4C/S

+VDDC

CP3C

10N/8P4C/S

+3.3V_BUS

CP9C

10N/8P4C/S

6 3

CP2D

5 4

10N/8P4C/S

5 4

CP3D

10N/8P4C/S

CP9D

10N/8P4C/S

5 4

CP8A

10N/8P4C/S

8 1

CP4A

10N/8P4C/S

8 1

C26

1U/6/Y/10V/S

+VDDC_CT

C49

1U/6/Y/10V/S

+VDDQ_BUS

7 2

+VDDC

CP8B

10N/8P4C/S

7 2

CP4B

10N/8P4C/S

CP8C

10N/8P4C/S

6 3

6 3

+VDDC

C27

1U/6/Y/10V/S

C48

1U/6/Y/10V/S

5 4

CP4C

10N/8P4C/S

C28

1U/6/Y/10V/S

C47

1U/6/Y/10V/S

CP8D

10N/8P4C/S

5 4

CP4D

C29

1U/6/Y/10V/S

2

+VDDC

U1F

P17

VDDC

Part 6 of 6

P18

VDDC

P19

VDDC

U12

VDDC

U13

VDDC

U14

VDDC

U17

VDDC

U18

VDDC

U19

VDDC

V19

VDDC

V18

VDDC

CENTER

V17

VDDC

V14

VDDC

ARRAY

V13

VDDC

V12

VDDC

N18

VDDC

N17

VDDC

N14

VDDC

W17

VDDC

W18

VDDC

W12

VDDC

W13

VDDC

W14

VDDC

N13

10N/8P4C/S

C45

1U/6/Y/10V/S

VDDC

N19

VDDC

M19

VDDC

M18

VDDC

M12

VDDC

N12

VDDC

M13

VDDC

M14

VDDC

P12

VDDC

P13

VDDC

P14

VDDC

M17

VDDC

RV350

U1E

A2

VSS

A10

A16

A22

A29

C1

C3

C28

C30

D27

D24

D21

D18

D15

D12

D9

D6

D4

F27

G9

G12

G16

G18

G21

G24

H27

H23

H21

H18

H16

H14

H12

H9

H8

H4

K30

K27

K24

K23

AG15

AD12

AE27

AG5

AG9

AG11

AG18

AG22

AG27 AJ1

E4

AB4

ADD ASIC DECOUPLING FOR ALL POWER AS REQUIRED

PLACED CLOSE TO THE POWER/GND PINS

WITH AS MANY AS POSSIBLE PLACED UNDER THE ASIC

Part 5 of 6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CORE GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

VSS

VSS

RV360

VDDC1

VDDC1

VDDC1

VDDC1

VDDC1

M16

VSS

N16

VSS

N15

VSS

P15

VSS

P16

VSS

R18

VSS

R17

VSS

R16

VSS

R15

VSS

R14

VSS

R13

VSS

R12

VSS

T13

VSS

T14

VSS

T15

VSS

W15

VSS

V16

VSS

V15

VSS

U15

VSS

U16

VSS

T19

VSS

T18

VSS

T17

VSS

T16

VSS

W19

W16

M15

R19

T12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K8

K7

K1

L4

M30

M8

M7

N23

N24

N27

P4

R7

R8

R23

R24

R30

T27

T1

U4

U8

U23

V30

W7

W8

W23

W24

W27

Y4

AA30

AB27

AB24

AB23

AB8

AB7

AB1

AC4

AC12

AC14

AD16

AC16

AC18

AD30

AD25

AD18

AK2

AK29

AJ30

D10

D25

1

A A

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

GIGABYTE

RV350 power

GV-R96X128D 2.0

1

of

723Monday, January 03, 2005

Loading...

Loading...