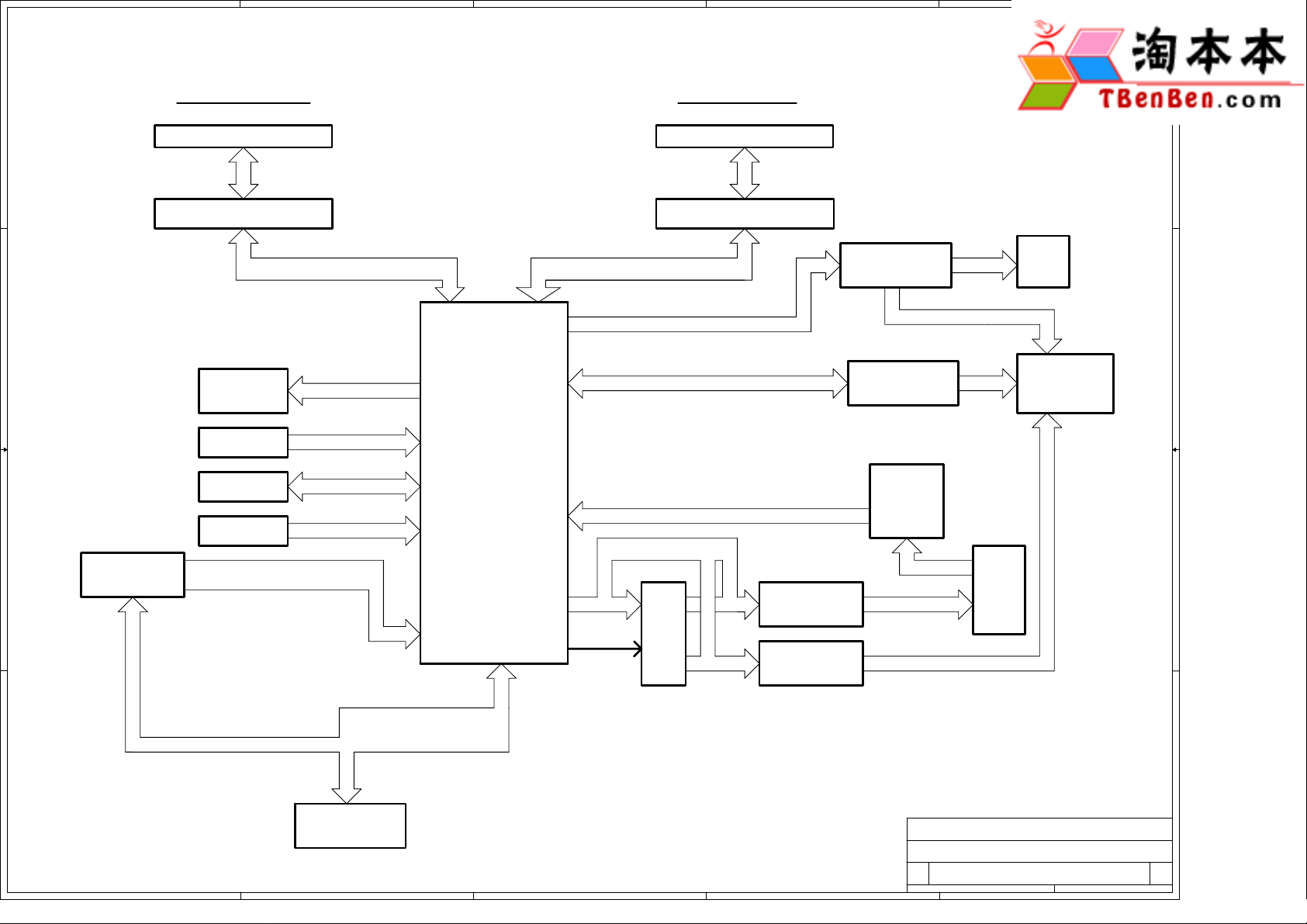

Gigabyte R38128-IU Rev.1.0 Schematics

5

4

3

2

1

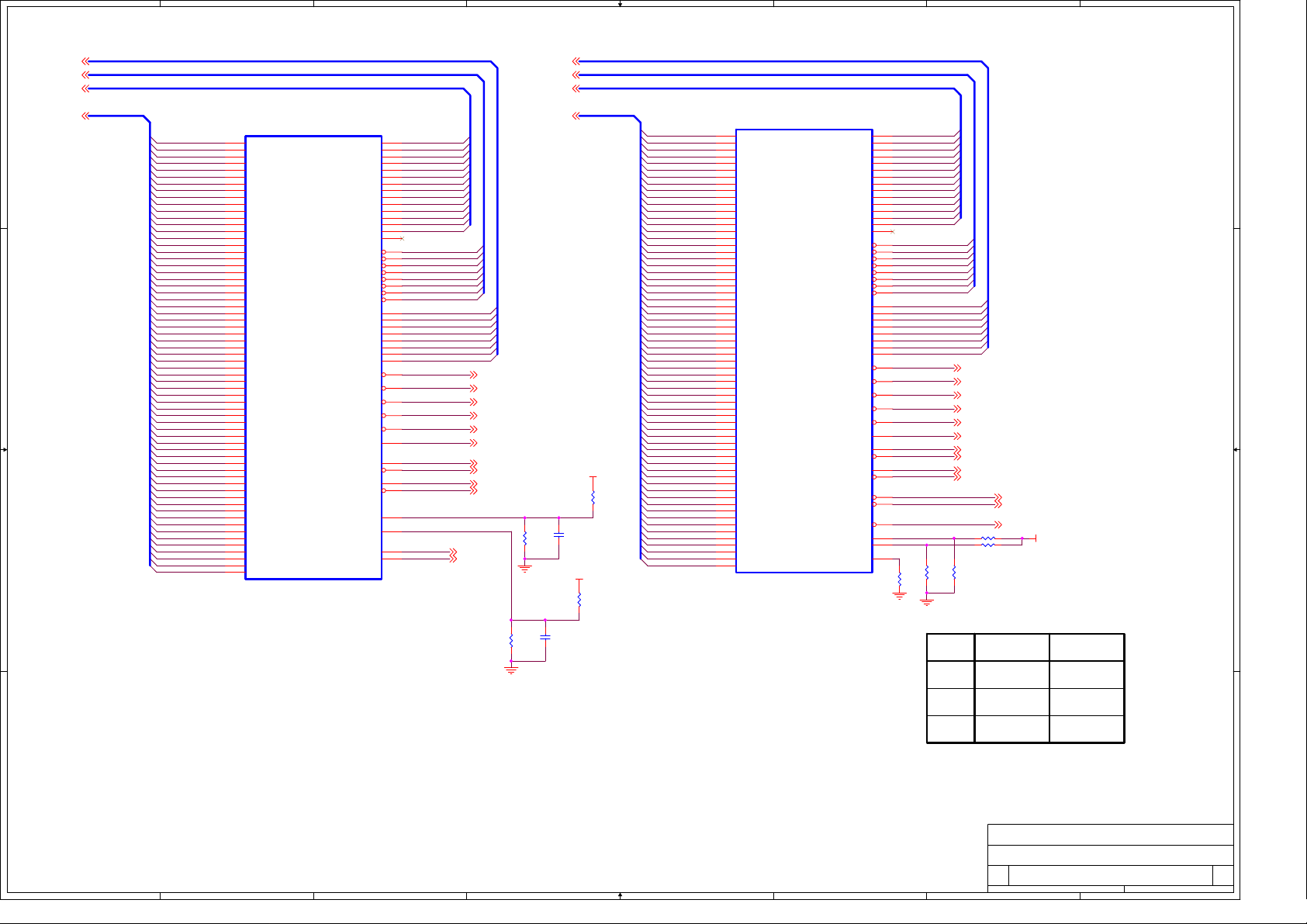

MEMORY CHANNEL A

D D

BGA Memory 4Mx32

MEMORY TERMINATIONS A

MDB[63..0] CS0B#

MA[14..0]

CASA#

RASA#

WEA#

QSA[7..0]

CS0A#MDA[63..0]

DQMA[0..7]

CLKA01CKEA

CLKA01#

MB[14..0]

CASB#

RASB#

WEA/B#

QSB[7..0]

MEMORY CHANNEL B

BGA Memory 4Mx32

MEMORY TERMINATIONS B

DQMB[0..7]

CKEB/D CLKB01

CLKB01#

PRIMARY CRT

LOGIC

VGA

DB15

CONN

MEM A MEM B

DAC1

C C

THERMAL

SENSOR

DPLUS DMINUS I2C_CLK I2C_DAT

TMDS

R G B HSY VSY DDC1DATA DDC1CLK

TMDS_TX[C,2..0]N TMDS_TX[C,2..0]P HPD, DDC2CLK DDC2DATA

INTEGRATED TMDS

LOGIC

DVI-I CONN

STRAPS

BIOS

HEATSINK/FAN

B B

POWER

REGULATION

VDDC VDDC_CT MVDDC MVDDQ VTT

PVDD TPVDD MPVDD

A2VDD Vref

ROMCS#

ROM

RV380

TVO

DDR DVO

VIP

DAC2

DVO, VID ports

Y/R C/G COMP/B H2SYNC

CRT2DDCDATA CRT2DDCCLK V2SYNC

D

E

TVOUT Filters

Rage

Theatre 1

TVOUT,

VIDEO IN

CONN

M

PCIe

LCDDATA19

SEL

U

X

Secondary

CRT LOGIC

+3.3V_BUS

A A

+12V_BUS

PCIe Edge Connector

Title

Size Document Number Rev

B

5

4

3

2

Date: Sheet

GIGABYTE CORP.

Block Diagram

GV-R38128-IU 1.0

123

1

of

8

7

6

5

4

3

2

1

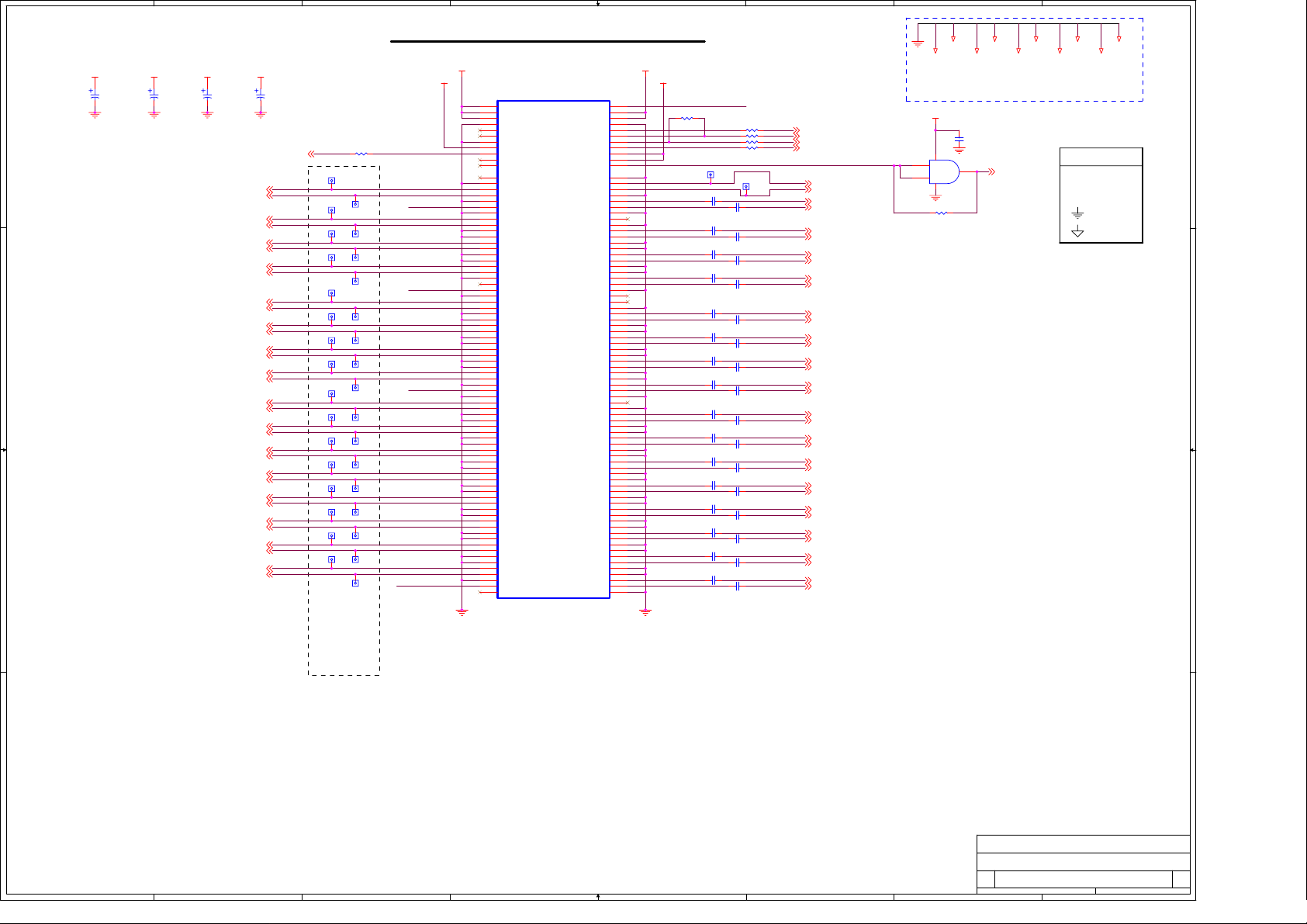

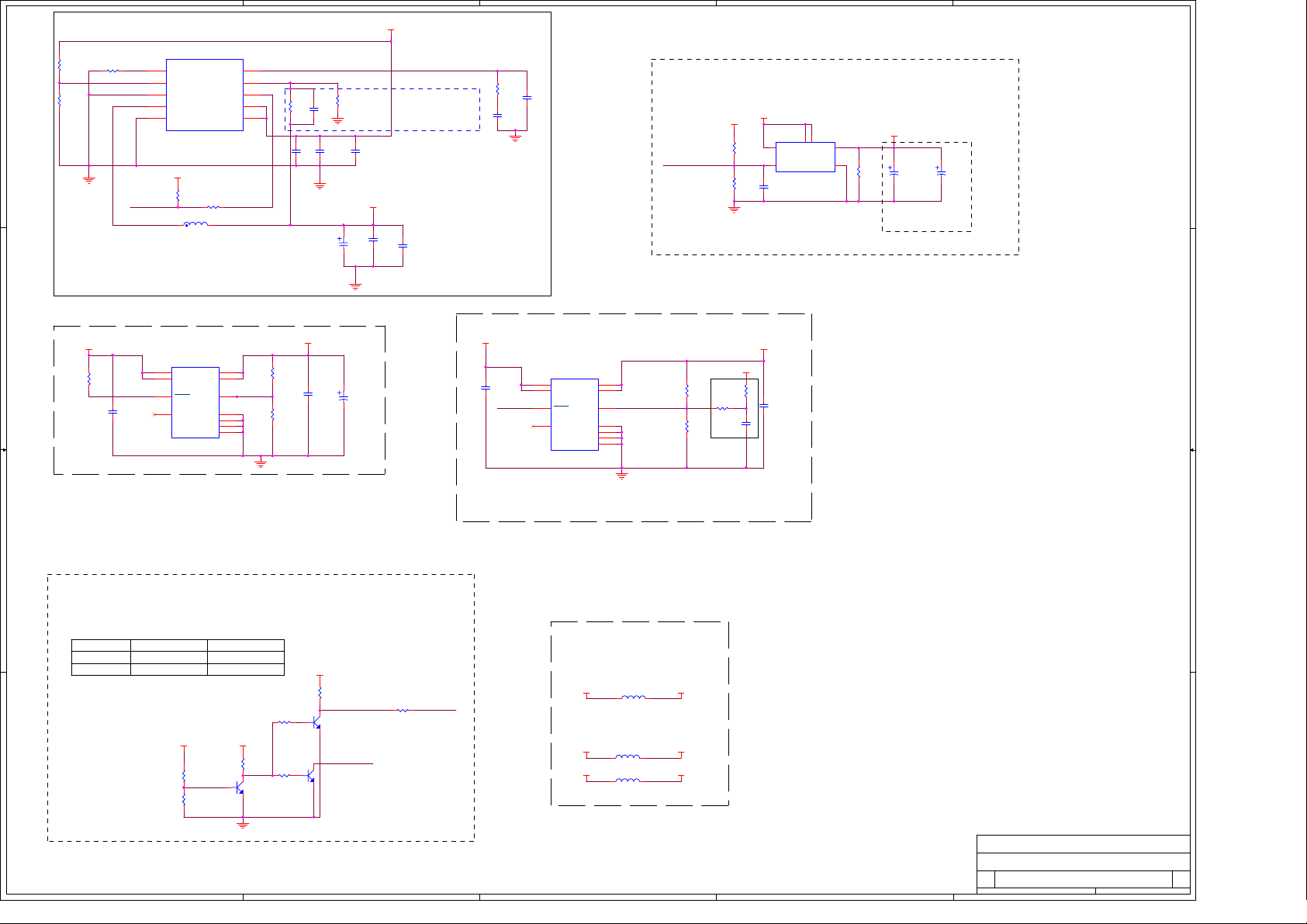

PCI-EXPRESS EDGE CONNECTOR

+12V_BUS+12V_BUS +3.3V_BUS+3.3V_BUS

C10

100uF_16V

D D

C C

B B

C5

100uF_16V

C8

100uF_16V

PETp0_GFXRp0(3)

PETn0_GFXRn0(3)

PETp1_GFXRp1(3)

PETn1_GFXRn1(3)

PETp2_GFXRp2(3)

PETn2_GFXRn2(3)

PETp3_GFXRp3(3)

PETn3_GFXRn3(3)

PETp4_GFXRp4(3)

PETn4_GFXRn4(3)

PETp5_GFXRp5(3)

PETn5_GFXRn5(3)

PETp6_GFXRp6(3)

PETn6_GFXRn6(3)

PETp7_GFXRp7(3)

PETn7_GFXRn7(3)

PETp8_GFXRp8(3)

PETn8_GFXRn8(3)

PETp9_GFXRp9(3)

PETn9_GFXRn9(3)

PETp10_GFXRp10(3)

PETn10_GFXRn10(3)

PETp11_GFXRp11(3)

PETn11_GFXRn11(3)

PETp12_GFXRp12(3)

PETn12_GFXRn12(3)

PETp13_GFXRp13(3)

PETn13_GFXRn13(3)

PETp14_GFXRp14(3)

PETn14_GFXRn14(3)

PETp15_GFXRp15(3)

PETn15_GFXRn15(3)

A_HSYNC_DAC1(3,17)

C2

47uF_16V

>=6.3V

USE 47uF TANTALUM

CAPACITOR OR HIGHER

R1008 0R

TP28

TP30

TP32

TP34

TP36

TP38

TP40

TP42

TP44

TP46

TP48 C624

TP50 C631

TP52

TP54

TP56

TP58

Place as Close to

the ASIC as

possible. Making

the Test point

Paris

equi-distant from

the balls.

TP29

TP31

TP33

TP35

TP37

TP39

TP41

TP43

TP45

TP47

TP49

TP51

TP53

TP55

TP57

TP59

DNI

PRESENCE

+12V_BUS

+3.3V_BUS +3.3V_BUS

MPCI1

JTAG_TRST#

PRESENT_NULL

PRESENT_NULL

PRESENT_NULL

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

RSVD#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

x16 PCIe

Mechanical Key

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLK-

GND#A15

GND#A18

RSVD#A19

GND#A20

GND#A23

GND#A24

GND#A27

GND#A28

GND#A31

RSVD#A32

RSVD#A33

GND#A34

GND#A37

GND#A38

GND#A41

GND#A42

GND#A45

GND#A46

GND#A49

RSVD#A50

GND#A51

GND#A54

GND#A55

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

JTAG2

JTAG3

JTAG4

JTAG5

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

+12V_BUS

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

DNI

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

PRESENCE

R12440R

RP194D 0R

RP194C 0R

RP194B 0R

RP194A 0R

TP26

TP27

C607

100nF

C608

100nF

C617

100nF

C618

100nF

C626

C627

100nF

100nF

C601

100nF

C602

100nF

C611

C612

100nF

100nF

C622

100nF

C623

100nF

C621

100nF

C630

100nF

C605

C606

100nF

100nF

C615

C616

100nF

100nF

100nF

C625

100nF

C600

100nF

100nF

C609

100nF

C610

100nF

C619

100nF

C620

100nF

C628

C629

100nF

100nF

C603

100nF

C604

100nF

C613

C614

100nF

100nF

54

63

72

81

DNI

A_VSYNC_DAC1 (3,17)

DNI

CRT1DDCDATA (3,17)

DNI

SCL (3,16)

DNI

CRT1DDCCLK (3,17)

PERST#

PCIE_REFCLKP (3)

PCIE_REFCLKN (3)

GFXTp0_PERp0 (3)

GFXTn0_PERn0 (3)

GFXTp1_PERp1 (3)

GFXTn1_PERn1 (3)

GFXTp2_PERp2 (3)

GFXTn2_PERn2 (3)

GFXTp3_PERp3 (3)

GFXTn3_PERn3 (3)

GFXTp4_PERp4 (3)

GFXTn4_PERn4 (3)

GFXTp5_PERp5 (3)

GFXTn5_PERn5 (3)

GFXTp6_PERp6 (3)

GFXTn6_PERn6 (3)

GFXTp7_PERp7 (3)

GFXTn7_PERn7 (3)

GFXTp8_PERp8 (3)

GFXTn8_PERn8 (3)

GFXTp9_PERp9 (3)

GFXTn9_PERn9 (3)

GFXTp10_PERp10 (3)

GFXTn10_PERn10 (3)

GFXTp11_PERp11 (3)

GFXTn11_PERn11 (3)

GFXTp12_PERp12 (3)

GFXTn12_PERn12 (3)

GFXTp13_PERp13 (3)

GFXTn13_PERn13 (3)

GFXTp14_PERp14 (3)

GFXTn14_PERn14 (3)

GFXTp15_PERp15 (3)

GFXTn15_PERn15 (3)

NOTE: THIS IS A DRAWING. THESE

GROUNDS MUST BE MANUALLY

CONNECTED TO THE GROUND PLANE

+3.3V_BUS

1

2

GND_PVSS GND_TXVSSR

C972

100nF

53

TC7SZ08FU

4

U102

0R

R1453

GND_TPVSSGND_MPVSS

PERST#_buf (3,20)

GND_A2VSSN

GND_A2VSSQ

GND_AVSSQ GND_RSET

GND_R2SETGND_AVSSN

SYMBOL LEGEND

DNI

DO NOT

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

A A

Title

Size Document Number Rev

C

8

7

6

5

4

3

Date: Sheet

2

GIGABYTE CORP.

PCI-E Edge Connector

GV-R38128-IU 1.0

of

223

1

5

4

3

2

1

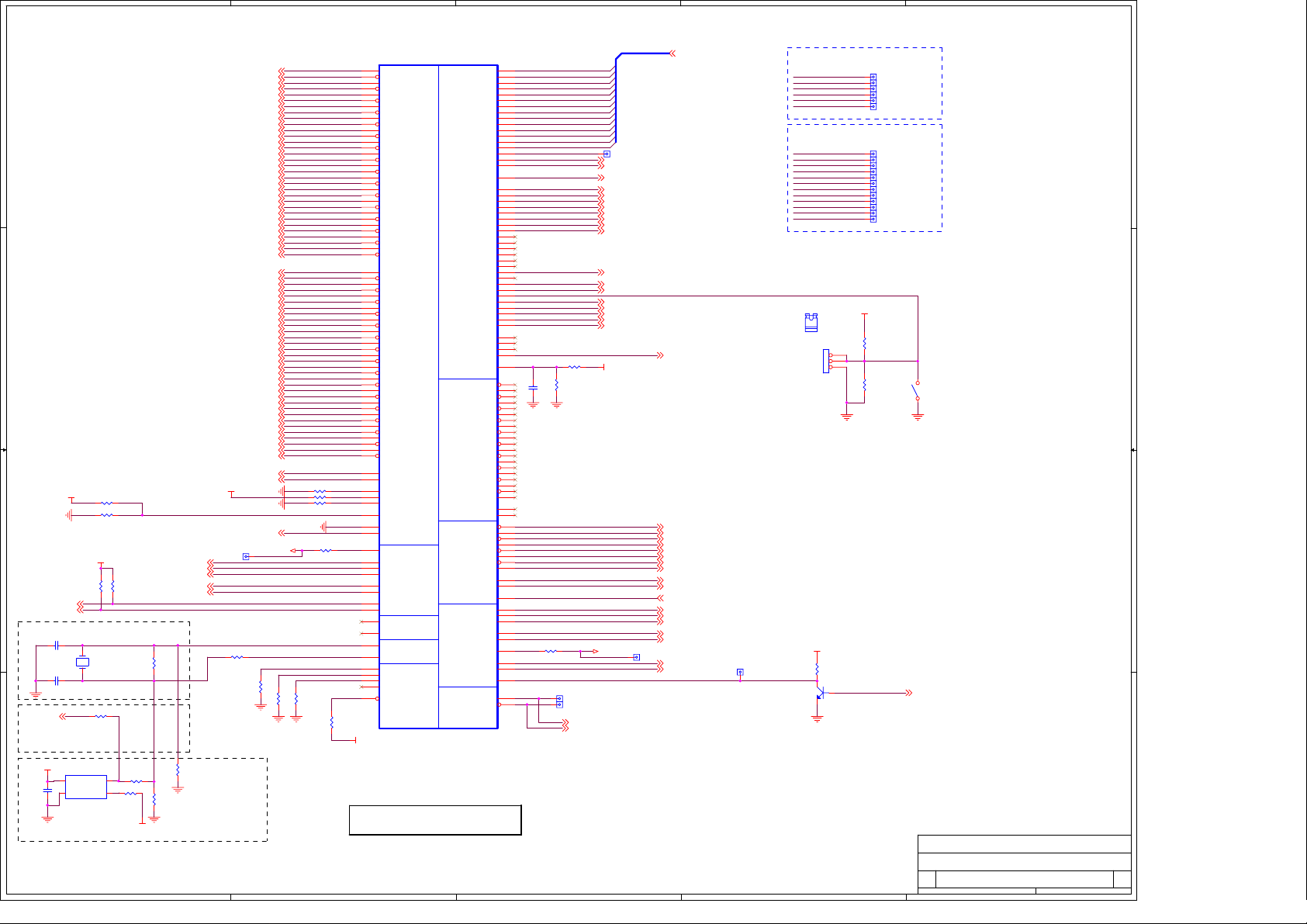

TP60

Mem_Strap1 (14)

Mem_Strap0 (14)

DVOMODE (14)

VID/DVO0 (20)

VID/DVO1 (20)

VID/DVO2 (20)

VID/DVO3 (20)

VID/DVO4 (20)

VID/DVO5 (20)

VID/DVO6 (20)

VID/DVO7 (20)

DC_Strap3 (21)

LCDDATA16 (14)

LCDDATA17 (14)

DEMUX_SEL (18)

VHAD0 (14,20)

VHAD1 (20)

VPHCTL (20)

CLK_VIPCLK (20)

+3.3V_BUS

GND_RSET

GPIO[13..0]

U1A

PETp0_GFXRp0(2)

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

GFXTp10_PERp10(2)

GFXTn10_PERn10(2)

GFXTp11_PERp11(2)

GFXTn11_PERn11(2)

GFXTp12_PERp12(2)

GFXTn12_PERn12(2)

GFXTp13_PERp13(2)

GFXTn13_PERn13(2)

GFXTp14_PERp14(2)

GFXTn14_PERn14(2)

GFXTp15_PERp15(2)

GFXTn15_PERn15(2)

PCIE_REFCLKP(2)

PCIE_REFCLKN(2)

PCIE_VDDR

TP6

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

GFXTp0_PERp0(2)

GFXTn0_PERn0(2)

GFXTp1_PERp1(2)

GFXTn1_PERn1(2)

GFXTp2_PERp2(2)

GFXTn2_PERn2(2)

GFXTp3_PERp3(2)

GFXTn3_PERn3(2)

GFXTp4_PERp4(2)

GFXTn4_PERn4(2)

GFXTp5_PERp5(2)

GFXTn5_PERn5(2)

GFXTp6_PERp6(2)

GFXTn6_PERn6(2)

GFXTp7_PERp7(2)

GFXTn7_PERn7(2)

GFXTp8_PERp8(2)

GFXTn8_PERn8(2)

GFXTp9_PERp9(2)

GFXTn9_PERn9(2)

R1009 150R

R1010 100R

R1011 10K

PERST#_buf(2,20)

GND_R2SET

R40 715R

D D

C C

+3.3V_BUS

R1452 10K

R1089 10K

B B

+3.3V_BUS

R45

R46

4.7K

SCL(2,16)

SDA(16)

4.7K

A_R/C_DAC2(18)

A_G/Y_DAC2(18)

A_B/COMP_DAC2(18)

A_HSYNC_DAC2(17)

A_VSYNC_DAC2(17)

OPTION 1: Crystal Circuit

C71

DNI

DNI

22pF

CLK_RT(16)

Option for using RageTheatre

reference Clock. R? and R27

should be as close as possible to

each other with no stub.

+3.3V_BUS

A A

C3

100nF

Y1

27_MHZ

2 1

C72

DNI

22pF

R1454 0R

Y2

4

VCC

2

GND

27.000MHz

OPTION 2: Oscillator Circuit

R27

150R

3

OUT

R1090 1K

1

E/D

+3.3V_BUS

5

DNI

R32

1M

R29

0R

OSCILLATOR CAN BE

CONNECTED TO XTALIN

R28

OR XTALOUT

100R

When RV350_XTALOUT is

used by the oscillator, XTALIN

should be grounded to prevent

the input buffers from picking

up noise.

R33

1.00K

TESTEN

R41

1K

R42

1K

R14

0R

AH30

PCIE_RX0P

AG30

PCIE_RX0N

AG29

PCIE_RX1P

AF29

PCIE_RX1N

AE29

PCIE_RX2P

AE30

PCIE_RX2N

AD30

PCIE_RX3P

AD29

PCIE_RX3N

AC29

PCIE_RX4P

AB29

PCIE_RX4N

AB30

PCIE_RX5P

AA30

PCIE_RX5N

AA29

PCIE_RX6P

Y29

PCIE_RX6N

W29

PCIE_RX7P

W30

PCIE_RX7N

V30

PCIE_RX8P

V29

PCIE_RX8N

U29

PCIE_RX9P

T29

PCIE_RX9N

T30

PCIE_RX10P

R30

PCIE_RX10N

R29

PCIE_RX11P

P29

PCIE_RX11N

N29

PCIE_RX12P

N30

PCIE_RX12N

M30

PCIE_RX13P

M29

PCIE_RX13N

L29

PCIE_RX14P

K29

PCIE_RX14N

K30

PCIE_RX15P

J30

PCIE_RX15N

AF26

PCIE_TX0P

AE26

PCIE_TX0N

AC25

PCIE_TX1P

AB25

PCIE_TX1N

AC27

PCIE_TX2P

AB27

PCIE_TX2N

AC26

PCIE_TX3P

AB26

PCIE_TX3N

Y25

PCIE_TX4P

W25

PCIE_TX4N

Y27

PCIE_TX5P

W27

PCIE_TX5N

Y26

PCIE_TX6P

W26

PCIE_TX6N

U25

PCIE_TX7P

T25

PCIE_TX7N

U27

PCIE_TX8P

T27

PCIE_TX8N

U26

PCIE_TX9P

T26

PCIE_TX9N

P25

PCIE_TX10P

N25

PCIE_TX10N

P27

PCIE_TX11P

N27

PCIE_TX11N

P26

PCIE_TX12P

N26

PCIE_TX12N

L25

PCIE_TX13P

K25

PCIE_TX13N

L27

PCIE_TX14P

K27

PCIE_TX14N

L26

PCIE_TX15P

K26

PCIE_TX15N

AF27

PCIE_REFCLKP

AE27

PCIE_REFCLKN

AC23

PCIE_CALRP

AB24

PCIE_CALRN

AB23

PCIE_CALI

AE25

PCIE_TEST

AD24

PWRGD_MASK

AD25

PWRGD

AH21

R2SET

AJ22

C_R_PR

AK21

Y_G

AK22

COMP_B_PB

AJ24

H2SYNC

AK24

V2SYNC

AG22

DDC3CLK

AG23

DDC3DATA

AJ23

NC#AJ23

AH24

NC#AH24

AH28

XTALIN

AJ29

XTALOUT

AH27

TESTEN

E8

TEST_YCLK

B6

TEST_MCLK

AF25

PLLTEST

AH25

STEREOSYNC

R1091

10K

RV370GL

+3.3V_BUS

IT IS RECOMMENDED TO ALLOW SERIES RESISTOR

FOOT PRINTS ON THE INDICATED AGP CONTROL SIGNALS

TO ADDRESS ANY LAYOUT NOISE RELATED

SIGNAL DAMPING REQUIREMENTS

4

PCI Express

DAC2CLK

Part 1 of 6

GPIO_PWRCNTL

GPIO_MEMSSIN

DVO / EXT TMDS / GPIOTMDSDAC1

GPIO__AUXWIN

THERM

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

DVOVMODE

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPCNTL_3

VREFG

NC#AH15

NC#AH16

NC#AJ16

NC#AJ17

NC#AJ18

NC#AK18

NC#AJ20

NC#AJ21

NC#AK19

NC#AJ19

NC#AG16

NC#AG17

NC#AF16

NC#AF17

NC#AE18

NC#AE19

NC#AF19

NC#AF20

NC#AG19

NC#AG20

NC#AE12

NC#AG12

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

DDC2CLK

DDC2DATA

HPD1

HSYNC

VSYNC

RSET

DDC1DATA

DDC1CLK

DPLUS

DMINUS

R

G

B

GPIO0

AJ5

GPIO1

AH5

GPIO2

AJ4

GPIO3

AK4

GPIO4

AH4

GPIO5

AF4

GPIO6

AJ3

GPIO7

AK3

GPIO8

AH3

GPIO9

AJ2

GPIO10

AH2

GPIO11

AH1

GPIO12

AG3

GPIO13

AG1

AG2

AF3

AF2

DVOMODE

AE10

AH6

AJ6

AK6

AH7

AK7

AJ7

AH8

AJ8

AH9

AJ9

AK9

AH10

AE6

AG6

VID/DVO14

AF6

AE7

VID/DVO16

AF7

VID/DVO17

AE8

VID/DVO18 PAL/NTSC

AG8

VID/DVO19

AF8

VID/DVO20

AE9

VID/DVO21

AF9

VID/DVO22

AG10

VID/DVO23

AF10

AJ10

AK10

AJ11

LCDCNTL3

AH11

AG4

AH15

AH16

AJ16

AJ17

AJ18

AK18

AJ20

AJ21

AK19

AJ19

AG16

AG17

AF16

AF17

AE18

AE19

AF19

AF20

AG19

AG20

AE12

AG12

AK13

AJ13

AJ14

AJ15

AK15

AK16

AJ12

AK12

AE13

AE14

AF12

AK27

AJ27

AJ26

AJ25

AK25

AH26

AG25

AF24

AG24

AF11

AE11

R39 499R

AUXWIN

C74

100nF

R34

1.00K

TP11

TP12

D+ (16)

D- (16)

3

R35

1.00K

GPIO[13..0] (14,15)

CLK_VID/DVO (20)

TMDS_TX0N (19)

TMDS_TX0P (19)

TMDS_TX1N (19)

TMDS_TX1P (19)

TMDS_TX2N (19)

TMDS_TX2P (19)

TMDS_TXCN (19)

TMDS_TXCP (19)

DVIDDCCLK (17)

DVIDDCDATA (17)

HPD (19)

A_R_DAC1 (17)

A_G_DAC1 (17)

A_B_DAC1 (17)

A_HSYNC_DAC1 (2,17)

A_VSYNC_DAC1 (2,17)

TP7

CRT1DDCDATA (2,17)

CRT1DDCCLK (2,17)

BOUNDARY SCAN TEST ACCESS

A_HSYNC_DAC1

SCL

CRT1DDCDATA

CRT1DDCCLK

A_VSYNC_DAC1

TESTEN

TP1

TP2

TP3

TP4

TP5

TP8

DEBUG BUS ACCESS

+VDD_DVO

R584

10K

402

R585

10K

ALT

402

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

TP25

VID/DVO16

VID/DVO17

VID/DVO18

VID/DVO19

VID/DVO20

VID/DVO21

VID/DVO22

VID/DVO23

GPIO10

GPIO11

GPIO12

GPIO13

P1

PLUG

OPT

1

2

3

JU2

Header_3_Pin_1X3

Default: Pin2,3 close (LOW) => H/W stapping is PAL

Pin1,2 close (High) => H/W stapping is NTSC

+3.3V_BUS

TP13

CMPT3904

2

R65

4.7K

402

1

Q43

2 3

TRST/

TDO

TDI

TMS

TCK

TESTOUT(0)

TESTOUT(1)

TESTOUT(2)

TESTOUT(3)

TESTOUT(4)

TESTOUT(5)

TESTOUT(6)

TESTOUT(7)

TESTOUT(8)

TESTOUT(9)

TESTOUT(10)

TESTOUT(11)

41

SW1A

DIP_SWX2

ThermINT (16)

Title

Size Document Number Rev

Custom

Date: Sheet

GIGABYTE CORP.

RV380 main

GV-R38128-IU 1.0

1

323

of

5

4

3

2

1

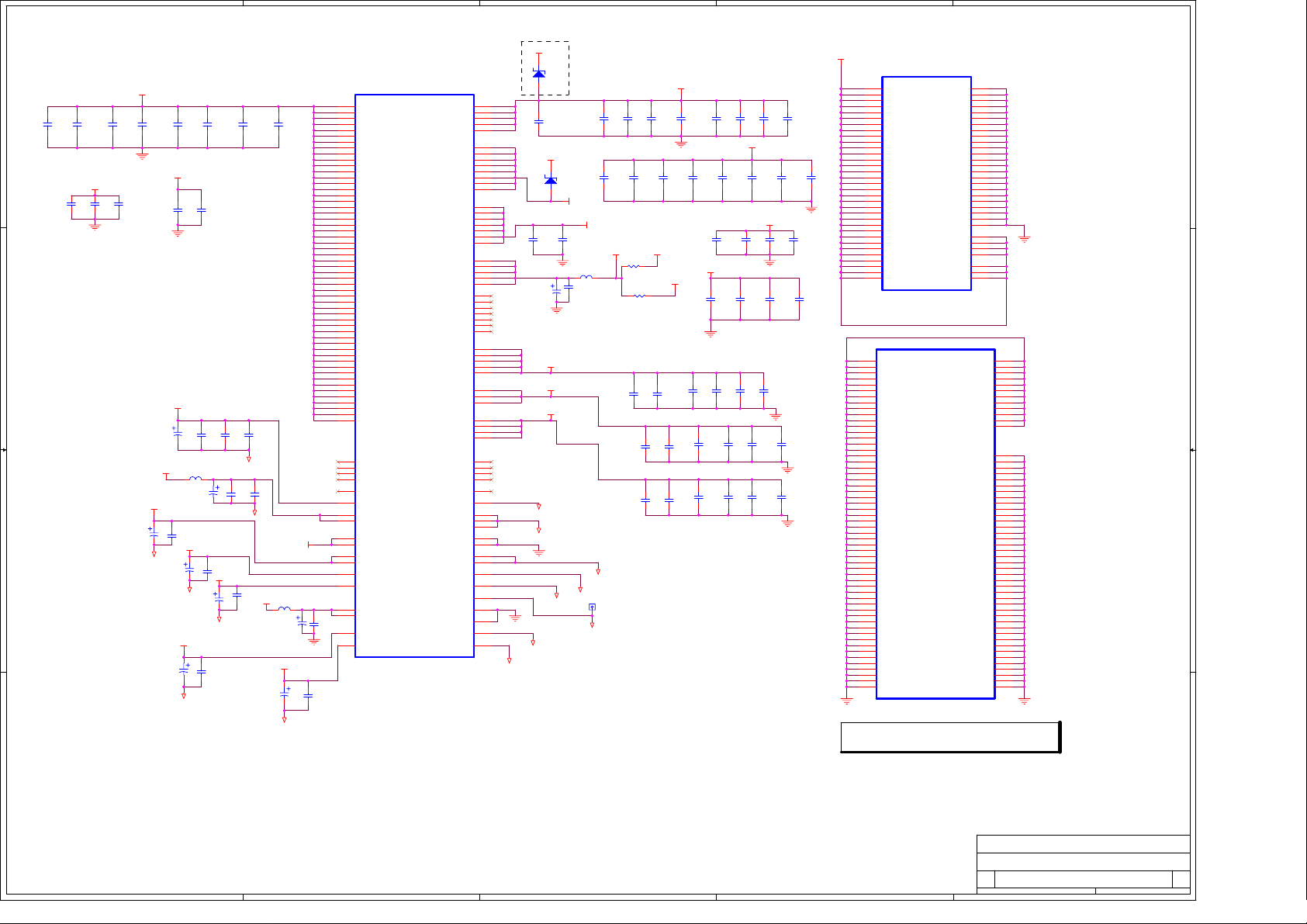

D30

2.4V

2 1

C24

10uf

+3.3V_BUS

D31

2 1

C46

1.0uF

C70

10uF_16V

PCIE_VDDR

PCIE_PVDD_12

PCIE_PVDD_18

GND_AVSSN

DIODE SUPPLIES POWER

TO VDDC RAIL

WHILE VDDC REGULATOR

STABALIZES DURING POWER ON

8 1

2.4V

8 1

+VDDC_CT

+3.3V_BUS

C44

1.0uF

200R

B53

C69

1.0uF

GND_A2VSSN

GND_A2VSSQ

TP9

GND_AVSSQ

CP2A

10nF

CP3A

10nF

+VDDC

+VDDC

CP2D

CP8A

8 1

1.0uF

+VDDC_CT

C49

1.0uF

7 2

CP10A

10nF

CP11A

10nF

10nF

8 1

C26

CP9B

10nF

CP4A

10nF

7 2

7 2

CP10B

10nF

CP11B

10nF

7 2

+VDDC

6 3

CP8B

10nF

1.0uF

C48

1.0uF

CP9C

10nF

CP2C

CP2B

10nF

7 2

CP3B

10nF

7 2

C36

1.0uF

+VDDR4+VDD_DVO

R68

0R

DNI

6 3

R69

0R

C968

1.0uF

C970

1.0uF

10nF

CP3C

10nF

6 3

+3.3V_BUS

C37

1.0uF

C969

1.0uF

C971

1.0uF

10nF

5 4

CP3D

10nF

5 4

CP9A

10nF

8 1

8 1

8 1

7 2

+VDDC

C27

6 3

6 3

CP4B

10nF

CP10C

10nF

CP11C

10nF

CP8D

CP8C

10nF

10nF

5 4

6 3

CP4D

CP4C

10nF

10nF

5 4

6 3

C28

C29

1.0uF

1.0uF

C45

C47

1.0uF

1.0uF

CP9D

10nF

5 4

CP10D

10nF

5 4

CP11D

10nF

5 4

U1F

Part 6 of 6

P17

VDDC#P17

P18

VDDC#P18

P19

VDDC#P19

U12

VDDC#U12

U13

VDDC#U13

U14

VDDC#U14

U17

VDDC#U17

U18

VDDC#U18

U19

VDDC#U19

V19

VDDC#V19

V18

VDDC#V18

V17

VDDC#V17

V14

VDDC#V14

V13

VDDC#V13

V12

VDDC#V12

N18

VDDC#N18

N17

VDDC#N17

N14

VDDC#N14

W17

VDDC#W17

W18

VDDC#W18

W12

VDDC#W12

W13

VDDC#W13

W14

VDDC#W14

N13

VDDC#N13

N19

VDDC#N19

M19

VDDC#M19

M18

VDDC#M18

M12

VDDC#M12

N12

VDDC#N12

M13

VDDC#M13

M14

VDDC#M14

P12

VDDC#P12

P13 P14

VDDC#P13 VDDC#P14

RV370GL

U1E

A2

A10

A16

A22

A29

C1

C3

C28

C30

D27

D24

D21

D18

D15

D12

D6

D4

D10

F27

G9

G12

G16

G18

G21

G24

H27

H23

H21

H18

H16

H14

H12

H9

H8

H4

J23

J24

AD12

AG5

AG9

AG11

R7

P4

M7

M8

L4

K1

K7

K8

R8

T1

W8

W7

U8

U4

Y4

RV370GL

ADD ASIC DECOUPLING FOR ALL POWER AS REQUIRED

PLACED CLOSE TO THE POWER/GND PINS

WITH AS MANY AS POSSIBLE PLACED UNDER THE ASIC

VSS#A2

VSS#A10

VSS#A16

VSS#A22

VSS#A29

VSS#C1

VSS#C3

VSS#C28

VSS#C30

VSS#D27

VSS#D24

VSS#D21

VSS#D18

VSS#D15

VSS#D12

VSS#D6

VSS#D4

VSS#D10

VSS#F27

VSS#G9

VSS#G12

VSS#G16

VSS#G18

VSS#G21

VSS#G24

VSS#H27

VSS#H23

VSS#H21

VSS#H18

VSS#H16

VSS#H14

VSS#H12

VSS#H9

VSS#H8

VSS#H4

VSS#J23

VSS#J24

VSS#AD12

VSS#AG5

VSS#AG9

VSS#AG11

VSS#R7

VSS#P4

VSS#M7

VSS#M8

VSS#L4

VSS#K1

VSS#K7

VSS#K8

VSS#R8

VSS#T1

VSS#W8

VSS#W7

VSS#U8

VSS#U4

VSS#Y4

Part 5 of 6

CORE GND

VSS#M16

VSS#N16

VSS#N15

VSS#P15

VSS#P16

VSS#R18

VSS#R17

VSS#R16

VSS#R15

VSS#R14

VSS#R13

VSS#R12

VSS#W15

VSS#V16

VSS#V15

VSS#U15

VSS#U16

CENTER ARRAY

VDDCI#W16

VDDCI#M15

VDDCI#R19

VDDCI#T12

VDDC#W19

VDDC#M17

VSS#T13

VSS#T14

VSS#T15

VSS#T19

VSS#T18

VSS#T17

VSS#T16

VSS#AB8

VSS#AB7

VSS#AB1

VSS#AC4

VSS#AC12

VSS#AC14

VSS#AD16

VSS#AC16

VSS#AC18

VSS#AD18

VSS#AK2

VSS#AJ1

PCIE_VSS#K28

PCIE_VSS#L28

PCIE_VSS#M24

PCIE_VSS#M25

PCIE_VSS#M26

PCIE_VSS#M27

PCIE_VSS#M28

PCIE_VSS#N28

PCIE_VSS#P28

PCIE_VSS#R23

PCIE_VSS#R24

PCIE_VSS#R25

PCIE_VSS#R26

PCIE_VSS#R27

PCIE_VSS#R28

PCIE_VSS#T24

PCIE_VSS#T28

PCIE_VSS#U28

PCIE_VSS#V24

PCIE_VSS#V25

PCIE_VSS#V26

PCIE_VSS#V27

PCIE_VSS#V28

PCIE_VSS#W24

PCIE_VSS#W28

PCIE_VSS#Y28

PCIE_VSS#AA23

PCIE_VSS#AA24

PCIE_VSS#AA25

PCIE_VSS#AA26

PCIE_VSS#AA27

PCIE_VSS#AA28

PCIE_VSS#AB28

PCIE_VSS#AC28

PCIE_VSS#AD26

PCIE_VSS#AD27

PCIE_VSS#AD28

PCIE_VSS#AE28

PCIE_VSS#AF28

PCIE_VSS#AH29

M16

N16

N15

P15

P16

R18

R17

R16

R15

R14

R13

R12

T13

T14

T15

W15

V16

V15

U15

U16

T19

T18

T17

T16

W16

M15

R19

T12

W19

M17

AB8

AB7

AB1

AC4

AC12

AC14

AD16

AC16

AC18

AD18

AK2

AJ1

K28

L28

M24

M25

M26

M27

M28

N28

P28

R23

R24

R25

R26

R27

R28

T24

T28

U28

V24

V25

V26

V27

V28

W24

W28

Y28

AA23

AA24

AA25

AA26

AA27

AA28

AB28

AC28

AD26

AD27

AD28

AE28

AF28

AH29

+3.3V_BUS

+MVDDQ

D D

C C

B B

CP6B

CP6A

10nF

8 1

1.0uF

10nF

7 2

+MVDDQ

C32

1.0uF

CP6C

10nF

6 3

C33

C35

1.0uF

C61

10uF_16V

GND_A2VSSN

CP6D

10nF

5 4

C57

10uF_16V

+A2VDD

+VDDR4

10uF_16V

GND_A2VSSQ

10uF_16V

8 1

+MVDDQ

+TPVDD

B11

200R

C62

1.0uF

C63

+PVDD

C54

GND_PVSS

CP5A

10nF

C39

10uf

10uF_16V

+A2VDDQ

10uF_16V

C59

C67

CP5B

10nF

7 2

C38

10uf

C43

1.0uF

C64

1.0uF

+AVDD

GND_AVSSN

C53

1.0uF

6 3

C58

1.0uF

GND_TPVSS

C60

1.0uF

GND_TXVSSR

C68

1.0uF

CP5C

10nF

C73

100pF

10uF_16V

C81

100pF

+VDDR4

CP5D

10nF

5 4

+MVDDQ

B12

200R

C66

10uF_16V

+MPVDD

C52

GND_MPVSS

U1D

T7

R4

R1

N8

N7

M4

L8

K23

K24

L23

J8

J7

J4

J1

H10

H13

H15

H17

T8

V4

V7

V8

AA1

AA4

AA7

AA8

A3

A9

A15

A21

A28

B1

B30

D26

D23

D20

D17

D14

D11

D8

D5

E27

F4

G7

G10

G13

G15

G19

G22

G27

H22

H19

AD4

N4

AE15

AE16

AE17

AF15

AH19

AH13 AH12

AF13

AF14

F18

N6

AE20

AF21

AF23

AH23

AE23

AE22

C65

1.0uF

AK28 AJ28

A7 A6

RV370GL

C51

1.0uF

Part 4 of 6

VDDR1#T7

VDDR1#R4

VDDR1#R1

VDDR1#N8

VDDR1#N7

VDDR1#M4

VDDR1#L8

VDDR1#K23

VDDR1#K24

VDDR1#L23

VDDR1#J8

VDDR1#J7

VDDR1#J4

VDDR1#J1

VDDR1#H10

VDDR1#H13

VDDR1#H15

VDDR1#H17

VDDR1#T8

VDDR1#V4

VDDR1#V7

VDDR1#V8

VDDR1#AA1

VDDR1#AA4

VDDR1#AA7

VDDR1#AA8

VDDR1#A3

VDDR1#A9

VDDR1#A15

VDDR1#A21

VDDR1#A28

VDDR1#B1

VDDR1#B30

VDDR1#D26

VDDR1#D23

VDDR1#D20

VDDR1#D17

VDDR1#D14

VDDR1#D11

VDDR1#D8

VDDR1#D5

VDDR1#E27

VDDR1#F4

VDDR1#G7

VDDR1#G10

VDDR1#G13

VDDR1#G15

VDDR1#G19

VDDR1#G22

VDDR1#G27

VDDR1#H22

VDDR1#H19

VDDR1#AD4

VDDR1#N4

NC#AE15

NC#AE16

NC#AE17

NC#AF15

NC#AH19

TPVDD TPVSS

TXVDDR#AF13

TXVDDR#AF14

VDDRH0

VDDRH1

A2VDD#AE20

A2VDD#AF21

A2VDDQ

AVDD

VDD1DI

VDD2DI

PVDD PVSS

MPVDD MPVSS

PCIE_VDDR_12#AG26

PCIE_VDDR_12#AG27

PCIE_VDDR_12#AG28

PCIE_VDDR_12#AJ30

PCIE_VDDR_12#AK29

PCIE_PVDD_12#N23

PCIE_PVDD_12#N24

PCIE_PVDD_12#P23

PCIE_PVDD_18#T23

PCIE_PVDD_18#U23

PCIE_PVDD_18#V23

PCIE_PVDD_18#W23

I/O POWER

VDDC#AC13

VDDC#AC15

VDDC#AC17

VDDC#AD13

VDDC#AD15

VDD15#H11

VDD15#H20

VDD15#M23

VDD15#P8

VDD15#Y23

VDD15#Y8

VDD15#AC11

VDD15#AC20

VDDR3#AC8

VDDR3#AC19

VDDR3#AC21

VDDR3#AC22

VDDR3#AD7

VDDR3#AD19

VDDR3#AD21

VDDR4#AC9

VDDR4#AC10

VDDR4#AD9

VDDR4#AD10

VDDR4#AG7

NC#D9

NC#D13

NC#D19

NC#D25

NC#E4

NC#T4

NC#AB4

NC#AF18

NC#AG15

NC#AG18

NC#AH17

NC#AH18

TXVSSR#AH14

TXVSSR#AG13

TXVSSR#AG14

VSSRH0

VSSRH1

A2VSSN#AH20

A2VSSN#AG21

A2VSSQ

AVSSN

AVSSQ

VSS1DI

VSS2DI

AC13

AC15

AC17

AD13

AD15

H11

H20

M23

P8

Y23

Y8

AC11

AC20

AC8

AC19

AC21

AC22

AD7

AD19

AD21

AC9

AC10

AD9

AD10

AG7

D9

D13

D19

D25

E4

T4

AB4

AG26

AG27

AG28

AJ30

AK29

N23

N24

P23

T23

U23

V23

W23

AF18

AG15

AG18

AH17

AH18

AH14

AG13

AG14

F19

M6

AH20

AG21

AF22

AH22

AD22

AE24

AE21

GND_MPVSS

>= 6.3V

GND_TPVSS

GND_TXVSSR

GND_PVSS

A A

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

GIGABYTE CORP.

RV380 power

1

GV-R38128-IU 1.0

of

423

1

2

3

4

5

6

7

8

QSA[7..0](10) QSB[7..0](11)

DQMA#[7..0](10)

MAA[13..0](10)

MDA[63..0](10)

A A

B B

C C

QSA[7..0]

DQMA#[7..0]

MAA[13..0]

MDA[63..0]

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

DQMB#[7..0](11)

MAB[13..0](11)

MDB[63..0](11)

U1B

H28

DQA_0

H29

DQA_1

J28

DQA_2

J29

DQA_3

J26

DQA_4

H25

DQA_5

H26

DQA_6

G26

DQA_7

G30

DQA_8

D29

DQA_9

D28

DQA_10

E28

DQA_11

E29

DQA_12

G29

DQA_13

G28

DQA_14

F28

DQA_15

G25

DQA_16

F26

DQA_17

E26

DQA_18

F25

DQA_19

E24

DQA_20

F23

DQA_21

E23

DQA_22

D22

DQA_23

B29

DQA_24

C29

DQA_25

C25

DQA_26

C27

DQA_27

B28

DQA_28

B25

DQA_29

C26

DQA_30

B26

DQA_31

F17

DQA_32

E17

DQA_33

D16

DQA_34

F16

DQA_35

E15

DQA_36

F14

DQA_37

E14

DQA_38

F13

DQA_39

C17

DQA_40

B18

DQA_41

B17

DQA_42

B15

DQA_43

C13

DQA_44

B14

DQA_45

C14

DQA_46

C16

DQA_47

A13

DQA_48

A12

DQA_49

C12

DQA_50

B12

DQA_51

C10

DQA_52

C9

DQA_53

B9

DQA_54

B10

DQA_55

E13

DQA_56

E12

DQA_57

E10

DQA_58

F12

DQA_59

F11

DQA_60

E9

DQA_61

F9

DQA_62

F8

DQA_63

RV370GL

Part 2 of 6

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

MVREFD

MVREFS

MEMORY

INTERFACE A

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

RASAb

CASAb

WEAb

CSAb_0

CSAb_1

CKEA

CLKA0

CLKA0b

CLKA1

CLKA1b

DIMA_0

DIMA_1

MAA0

E22

MAA1

B22

MAA2

B23

MAA3

B24

MAA4

C23

MAA5

C22

MAA6

F22

MAA7

F21

MAA8

C21

MAA9

A24

MAA10

C24

MAA11

A25

MAA12

E21

MAA13

B20

C19

DQMA#0

J25

DQMA#1

F29

DQMA#2

E25

DQMA#3

A27

DQMA#4

F15

DQMA#5

C15

DQMA#6

C11

DQMA#7

E11

QSA0

J27

QSA1

F30

QSA2

F24

QSA3

B27

QSA4

E16

QSA5

B16

QSA6

B11

QSA7

F10

RASA#

A19

CASA#

E18

WEA#

E19

CSA#0

E20

CSA#1

F20

CKEA

B19

CLKA0

B21

CLKA#0

C20

CLKA1

C18

CLKA#1

A18

B7

B8

DIMA0

D30

DIMA1

B13

RASA# (10)

CASA# (10)

WEA# (10)

CSA#0 (10)

CSA#1 (10)

CKEA (10)

CLKA0 (10,12,13)

CLKA#0 (10,12,13)

CLKA1 (10,12,13)

CLKA#1 (10,12,13)

DIMA0 (12,13)

DIMA1 (12,13)

R57

100R

+MVDDQ

C151

100nF

+MVDDQ

QSB[7..0]

DQMB#[7..0]

MAB[13..0]

MDB[63..0]

R56

100R

R58

47R

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

U1C

D7

DQB_0

F7

DQB_1

E7

DQB_2

G6

DQB_3

G5

DQB_4

F5

DQB_5

E5

DQB_6

C4

DQB_7

B5

DQB_8

C5

DQB_9

A4

DQB_10

B4

DQB_11

C2

DQB_12

D3

DQB_13

D1

DQB_14

D2

DQB_15

G4

DQB_16

H6

DQB_17

H5

DQB_18

J6

DQB_19

K5

DQB_20

K4

DQB_21

L6

DQB_22

L5

DQB_23

G2

DQB_24

F3

DQB_25

H2

DQB_26

E2

DQB_27

F2

DQB_28

J3

DQB_29

F1

DQB_30

H3

DQB_31

U6

DQB_32

U5

DQB_33

U3

DQB_34

V6

DQB_35

W5

DQB_36

W4

DQB_37

Y6

DQB_38

Y5

DQB_39

U2

DQB_40

V2

DQB_41

V1

DQB_42

V3

DQB_43

W3

DQB_44

Y2

DQB_45

Y3

DQB_46

AA2

DQB_47

AA6

DQB_48

AA5

DQB_49

AB6

DQB_50

AB5

DQB_51

AD6

DQB_52

AD5

DQB_53

AE5

DQB_54

AE4

DQB_55

AB2

DQB_56

AB3

DQB_57

AC2

DQB_58

AC3

DQB_59

AD3

DQB_60

AE1

DQB_61

AE2

DQB_62

AE3

DQB_63

RV370GL

Part 3 of 6

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

ROMCSb

MEMVMODE_0

MEMVMODE_1

MEMTEST

MEMORY

INTERFACE B

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

RASBb

CASBb

WEBb

CSBb_0

CSBb_1

CKEB

CLKB0

CLKB0b

CLKB1

CLKB1b

DIMB_0

DIMB_1

MAB0

N5

MAB1

M1

MAB2

M3

MAB3

L3

MAB4

L2

MAB5

M2

MAB6

M5

MAB7

P6

MAB8

N3

MAB9

K2

MAB10

K3

MAB11

J2

MAB12

P5

MAB13

P3

P2

DQMB#0

E6

DQMB#1

B2

DQMB#2

J5

DQMB#3

G3

DQMB#4

W6

DQMB#5

W2

DQMB#6

AC6

DQMB#7

AD2

QSB0

F6

QSB1

B3

QSB2

K6

QSB3

G1

QSB4

V5

QSB5

W1

QSB6

AC5

QSB7

AD1

RASB#

R2

CASB#

T5

WEB#

T6

CSB#0

R5

CSB#1

R6

CKEB

R3

CLKB0

N1

CLKB#0

N2

CLKB1

T2

CLKB#1

T3

DIMB0

E3

DIMB1

AA3

AF5

C6

C7

C8

R55

47R

R53

4.7K

RASB# (11)

CASB# (11)

WEB# (11)

CSB#0 (11)

CSB#1 (11)

CKEB (11)

CLKB0 (11,12,13)

CLKB#0 (11,12,13)

CLKB1 (11,12,13)

CLKB#1 (11,12,13)

DIMB0 (12,13)

DIMB1 (12,13)

ROMCS# (15)

R51 4.7K

R52 4.7K

R54

4.7K

+VDDC_CT

C152

R59

100nF

MEMORY CHANNEL A

D D

1

2

3

51R

4

MEMORY CHANNEL B

5

VDDR1 MEMVMODE_0 MEMVMODE_1

1.8V

2.5V

2.8V

6

+VDDC_CT GND

+VDDC_CT +VDDC_CT

Title

Size Document Number Rev

Custom

Date: Sheet

7

+VDDC_CTGND

GIGABYTE CORP.

RV380 memory interface

GV-R38128-IU 1.0

523

of

8

5

REG32

R1082

10K

R1083 330K

R1084

D D

10K

LTC3411EMS

1

SHDN/RT

2

SYNC/MODE

3

SGND

4 7

SW SVIN

+3.3V_BUS

PVDD12_EN

1 2

R1095

100K

L104

1.5uH

R1096 0R

ITH

VFB

PGOOD

PVINPGND

VDDR_GOOD

10

9

8

65

R1086

100K

C963

1.0uF

C962

22pF

C964

22uF_6.3V

R1085

100K

4

C965

22uF_6.3V

PCIE_VDDR

C966

33uF

+3.3V_BUS

R1085 -> 1.74M 0603 =

3240174400

R1086 -> 887K 0603 =

3240887300

C967

1.0uF

C978

22uF

R1081

15K

C961

470pF

C960

47pF

3

Alt. regulator for PCIE_VDDR

Vout = 1.2V

Iout = 3000mA MAX

+3.3V_BUS

+VDDR4

MREG32

R141

1 5

IN VOUT

VDDC_GOOD

604R

4 2

R142

1.24K

C975

1.0uF

REFEN GND

RT9173ACL5

2

R143

1K

402

PCIE_VDDR

***

***

C160

100uF_16V

MC160

470uF

3

6

TAB

VCNTL

1

Dual footprint

+3.3V_BUS

REG31

C956

1.0uF

PVDD12_EN PCIE_PVDD_12_SET

MAX1935ETA

2

IN2

4

SHDN

3

POK

81

OUTIN

7

OUT7

6

SET

5

GND

9

TH_GND9

10

TH_GND10

11

TH_GND11

COST Reduction options

for sharing 1.2V Rails

PCIE_PVDD_12 PCIE_VDDR

+VDDC

L106 1.8uH

+VDDC

L107 1.8uH

L105

1.8uH

PCIE_VDDR

PCIE_PVDD_12

R1076

1.0K

R1080

2K

DNI

R1078

30.1K

100pF

1.0K

+PVDD

R1077

C959

PCIE_PVDD_12

C958

10uf

R395

20K

402

PCIE_PVDD_18

R1075

6.81K

R1079

5.49K

402

R397

100R

402

1

+3.3V_BUS

1

C957

10uf

2 3

R153

100K

402

2 3

CMPT3904

Q29

CMPT3904

Q157

C980

470uF

VDDC_GOOD_PU

VDDC_GOOD

R1442 0R

PVDD12_EN

C C

B B

A A

+3.3V_BUS

R1074

100K

PVDD12_EN

C955

1.0uF

Circuit to hold PCI-E voltage low and wait for +VDDC for proper power

sequence

+1.3V

Rq3

1.5K

2

4

3

Rq3

Rq4

REG30

MAX1935ETA

IN2

SHDN

POK

R396

100R

81

OUTIN

7

OUT7

6

SET

5

GND

9

TH_GND9

10

TH_GND10

11

TH_GND11

Rq4+VDDC

2.4K

+VDDC +12V_BUS

R393

CMPT3904

1.5K

Q158

1

R394

2.4K

2 3

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

GIGABYTE CORP.

RV380 PCI-E Power

GV-R38128-IU 1.0

1

of

623

8

7

6

5

4

3

2

1

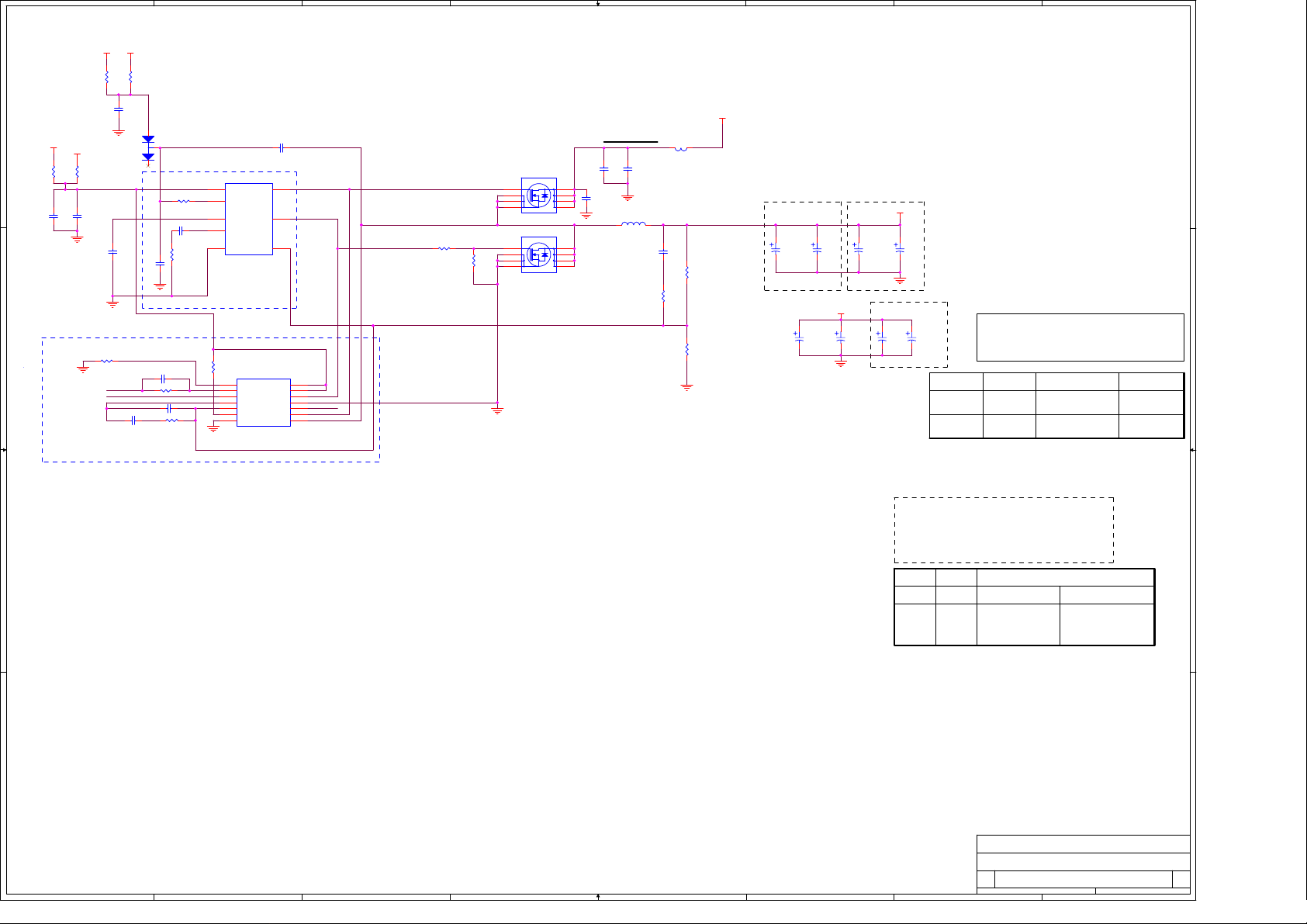

+VDDC Switching Regulator

+12V_BUS

+5V

R1070

R1071

0R

0R

DNI

C937

R1056

0R

DNI

C943

220nF

C945

22nf

R1064 51K

VIN_VDDC

SS_VDDC

COMP_VDDC

C950 10nF

220nF

1

D125

BAT54SLT1

3

2

R1057 5.1R

C944

C947

1uF

DNI

C948 1nf

R1066 3K

C949 33pF

R1067 15K

SS_VDDC

2.2nF

R1059

27K

DNI

BOOT_VDDC

COMP_VDDC

DNI

U100

DNI

2

Vcc

6

Vc

7

Comp

4

GND

IRU3037ACS

Alternate part IRU3037CS

Alternative 1

R1065

10K

U101

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

C938 100nF

HDrv

LDrvSS

Fb

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

VIN_VDDC

C940

C939

10uF

10uF

C941

6

100nF

7

8

6

7

8

L1032.2uH

Cd1

R1060

10K

DNI

Q155

4 5

3

2

1

IRF7413A

Q156

4 5

3

2

1

IRF7413A

5

38

1

R1058 0R

Rd4

141

VCCRT

13

12

11

BOOT_VDDC

10

9

8

D D

+12V_BUS

+5V

R1055

0R

C942

220nF

C C

Alternative 2

B B

C946

10nF

R1062

1.5K

+12V_BUS

B80

***

60R

***

***

C109

22uF_16V

+VDDC

C167

C107

470uF

470uF_10V

***

C97

C997

470uF

470uF_10V

DNI

***

Dual footprint

Part

IRU3037

IRU3037A

ISL6522CB

Regulator for VDDC (RV350 Core)

Vin = 3.3V_BUS

Vout = 1.2V

Iout = 7A MAX (load consumption)

Iout = 3A MAX (Power rail consumption)

470uF thru hole capacitor has 30mR ESR

Cout1

where as 470uF SMT capacitor has

22mR ESR. For current below 4.5A, 1

thru 470uF is enough.

INSTALL DO NOT INSTALL

Compensation Circuit

Alternative1

Alternative2

Indicates number of vias required for the connection

***

C166, C167 alternate parts for C106, C107

Place C102 capacitor very close to the Q21 pin s

Common, and Either Alt.

Compensation 1, or Alt .

Compensation 2

Common and Alt.

Compensation 2

Cc4, Rc6

Alternative 2

Alternative1

R1061

1%

1.00K

Rc1

R1063

2K

1%

Rc2

Cout1

***

***

Dual footprint Dual footprint

C166

C106

470uF

470uF_10V

DNI DNI

+VDDC

******

C108

22uF_16V

**

REG. VOLTAGE RESISTORS

ISL6522C

Rc1

1.2V

1.00K (p/n 3240100100) 2K (p/n 3240200100)

1.25V

1.3V

1.10K (p/n 3240110100)

Rc2

1K78 (p/n 3240178100)1.00K (p/n 3240100100)

1K78 (p/n 3240178100)

A A

Title

Size Document Number Rev

C

8

7

6

5

4

3

Date: Sheet

2

GIGABYTE CORP.

VDDC

GV-R38128-IU 1.0

of

723

1

Loading...

Loading...