Gigabyte gv-nx66t128vp-sp_10_pvt Schematics

1

2

3

4

P216-A02 DESIGN -- NV43, 128 MB DDR3, VGA, DVI-I, SD/HDTV, VIVO

5

6

7

8

HGFEDCBA

1

A A

2

B B

3

C C

PAGE SUMMARY:

1

2

3

4

SKU

VARIANT ASSEMBLY

B

BASE

000

1

2

001

3

002

4

003

5

<UNDEFINED>

6

<UNDEFINED>

7

<UNDEFINED>

8

<UNDEFINED>

9

<UNDEFINED>

10

<UNDEFINED>

11

<UNDEFINED>

<UNDEFINED>

12

<UNDEFINED>

D D

5

13

14

15

<UNDEFINED>

<UNDEFINED>

X01

ASSEMBLY

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARR ANTIES INCLU DING, WITHOU T LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

2

3

PAGE DETAIL

4

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

TABLE OF CONTENTS & REVISION HISTORY

E GC

5

NVPN

600-10216-base-sch

602-10216-0000-200

602-10216-0001-200

602-10216-0002-200

602-10216-0003-200

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

NV43-U 500/500MHz 128MB DDR3 8MX32 DVI+VGA+HDTV OUT

NV43-U 500/500MHZ 128MB DDR3 8MX32 DVI+VGA+H D/V IVO

NV43-U 350/350MHZ 128MB DDR3 8MX32 DVI+VGA+HDTV OUT

NV43-U 400/400MHZ 128MB DDR3 8MX32 DVI+VGA+HDTV OUT

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

6

Tuesday, October 25, 2005

GIGABYTE

Cover Page

GV-NX66T128VP-SP

Title

Size Document Number Rev

Custom

Date: Sheet of

7

126

8

1.0

4

5

1

3V3

1

A A

2

B B

3

C C

4

D D

5

3V3AUX

C949

.01UF

16V

10%

X7R

0402

COMMON

GND

C94

.100UF

25V

10%

X7R

0603

COMMON

Place Close to fingers

C916

.1UF

10V

10%

X5R

0402

COMMON

GND

12V

3V3

3V3AUX

PRSNT

NTP_PE_PRSNT2_A

NTP_PE_RSVD2

NTP_PE_PRSNT2_B

NTP_PE_RSVD3

NTP_PE_RSVD4

NTP_PE_RSVD5

NTP_PE_PRSN T2_C

NTP_PE_RSVD6

NTP_PE_RSVD7

NTP_PE_RSVD8

C95

10UF

16V

20%

X5R

1206

COMMON

GND

CN2

NONPHY-X16

COMMON

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

GND

END OF X1

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

END OF X4

GND

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

GND

END OF X8

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

END OF X16

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARR ANTIES INCLU DING, WITHOU T LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

12V

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

C950

.01UF

25V

10%

X7R

0402

COMMON

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

2

C915

C93

.1UF

10UF

16V

16V

10%

20%

X7R

X5R

0603

1206

COMMON

COMMON

GND

NTP_JTAG_TRST*

B9

NTP_JTAG_TCLK

A5

JTAG_TDI_TDO

A6

A7

NTP_JTAG_TMS

A8

this resistor stradles the TDI/TDO pair

NTP_PEX_SMCLK

B5

NTP_PEX_SMDAT

B6

NTP_PEX_WAKE*

B11

WAKE

PEX_PWRGD*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4 PEX_TXX4

A35

PEX_TXX4* PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TXX9

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

B66

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

C97

1UF

6.3V

10%

X5R

0402

COMMON

R704

0/X

5%

0402

NS

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

3.5MIL

3.5MIL

COMMON

3.5MIL

3.5MIL

2

3

3V3

1

2

GND

2.1G<> 21.3B<

OUT

2.1G<> 21.3B<

OUT

2.1G<>

IN

21.3G>

2.1G<>

IN

21.3G>

C948

.1UF

0402X5R 10% 10V

C946

.1UF

0402X5R 10% 10V

C944

.1UF

0402X5R 10% 10V

C942

.1UF

0402X5R 10% 10V

C940

.1UF

0402X5R 10% 10V

C938

.1UF

0402X5R 10% 10V

C936

.1UF

0402X5R 10% 10V

C934

.1UF

0402X5R 10% 10V

C932

.1UF

0402X5R 10% 10V

C930

.1UF

0402X5R 10% 10V

C928

.1UF

0402X5R 10% 10V

C926

.1UF

0402X5R 10% 10V

C924

.1UF

0402X5R 10% 10V

C922

.1UF

0402X5R 10% 10V

C920

.1UF

0402X5R 10% 10V

C918

.1UF

0402X5R 10% 10V

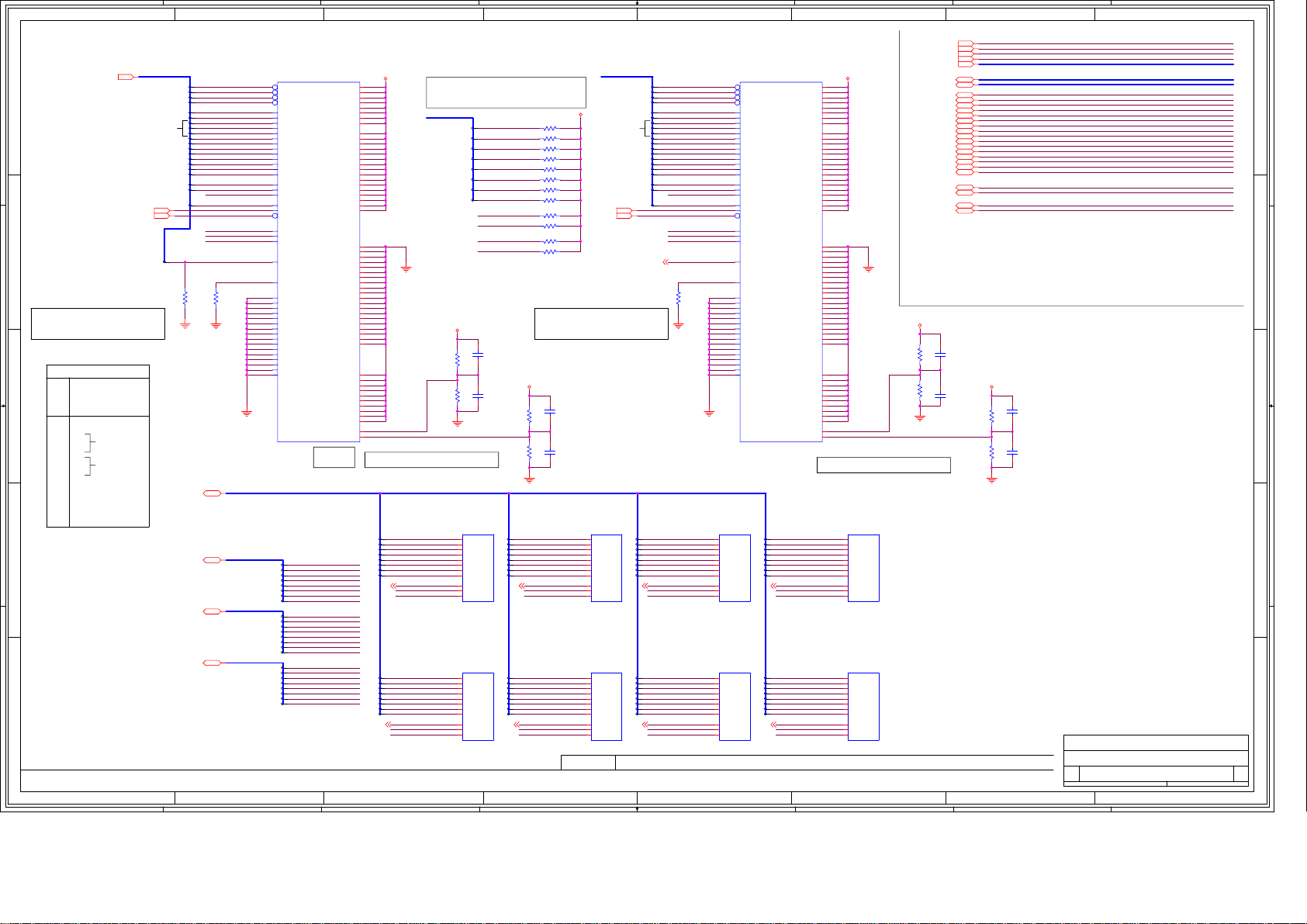

16X PCIe Interface

short duration contention possible

3.3V^2/100 = 108mW

5

U14

UNNAMED_2_R_I543_1

R110

4

0402

5%

SC70-5

COMMON

3

1/16W

R83 0/X

0402 COMMON

5%

BYPASS

TP_PEXCAPD_VDDQ

TP_PEXCALPD_GND

3.5MIL

PEX_TEST_PLLCLK_OUT

PEX_TEST_PLLCLK_OUT_N

3.5MIL

GPU_PEX_REFCLK

GPU_PEX_REFCLK*

C947

.1UF

0402 10% X5R10V

C945 .1UF

3.5MIL

3.5MIL

0402 10%10V X5R COMMON

C943 .1UF

3.5MIL

3.5MIL

0402 10%10V X5R COMMON

C941

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C939

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C937

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C935

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C933

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C931

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C929

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C927

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C925

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C923

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C921

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C919

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

C917

.1UF

3.5MIL

3.5MIL

0402 X5R10%10V

100

COMMON

R102

200/X

04025%COMMON

PEX_TX0

3.5MIL

PEX_TX0*

3.5MIL

COMMON

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

COMMON

PEX_TX4

PEX_TX4*

COMMON

PEX_TX5

PEX_TX5*

COMMON

PEX_TX6

PEX_TX6*

COMMON

PEX_TX7

PEX_TX7*

COMMON

PEX_TX8

PEX_TX8*

COMMON

PEX_TX9

PEX_TX9*

COMMON

PEX_TX10

PEX_TX10*

COMMON

PEX_TX11

PEX_TX11*

COMMON

PEX_TX12

PEX_TX12*

COMMON

PEX_TX13

PEX_TX13*

COMMON

PEX_TX14

PEX_TX14*

COMMON

PEX_TX15

PEX_TX15*

COMMON

GND

PEX_PWRGD_BUF*

3

R111

10K

5%

0402

COMMON

AH15

AG12

AH13

AM12

AM11

AH14

AJ14

AJ15

AK15

AK13

AK14

AH16

AG16

AM14

AM15

AG17

AH17

AL15

AL16

AG18

AH18

AK16

AK17

AK18

AJ18

AL17

AL18

AJ19

AH19

AM18

AM19

AG20

AH20

AK19

AK20

AG21

AH21

AL20

AL21

AK21

AJ21

AM21

AM22

AJ22

AH22

AK22

AK23

AG23

AH23

AL23

AL24

AK24

AJ24

AM24

AM25

AJ25

AH25

AK25

AK26

AH26

AG26

AL26

AL27

AK27

AJ27

AM27

AM28

AJ28

AH27

AL28

AL29

4

U11A

BGA820

COMMON

1/14 PCI_EXPRESS

PEX_RST

RFU

RFU

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

4

ASSEMBLY

PAGE DETAIL

5

VALUES TBD

Place near balls

600mA

PEX_IO_VDD

C846

C845

.022UF

.022UF

16V

AD23

PEX_IOVDD

AF23

PEX_IOVDD

AF24

PEX_IOVDD

AF25

PEX_IOVDD

AG24

PEX_IOVDD

AG25

PEX_IOVDD

AC16

PEX_IOVDDQ

AC17

PEX_IOVDDQ

AC21

PEX_IOVDDQ

AC22

PEX_IOVDDQ

AE18

PEX_IOVDDQ

AE21

PEX_IOVDDQ

AE22

PEX_IOVDDQ

AF12

PEX_IOVDDQ

AF18

PEX_IOVDDQ

AF21

PEX_IOVDDQ

AF22

PEX_IOVDDQ

K16

VDD

K17

VDD

N13

VDD

N14

VDD

N16

VDD

N17

VDD

N19

VDD

P13

VDD

P14

VDD

P16

VDD

P17

VDD

P19

VDD

R16

VDD

R17

VDD

T13

VDD

T14

VDD

T15

VDD

T18

VDD

T19

VDD

U13

VDD

U14

VDD

U15

VDD

U18

VDD

U19

VDD

V16

VDD

V17

VDD

W13

VDD

W14

VDD

W16

VDD

W17

VDD

W19

VDD

Y13

VDD

Y14

VDD

Y16

VDD

Y17

VDD

Y19

VDD

Y20

VDD

P20

VDD_LP

T20

VDD_LP

T23

VDD_LP

U20

VDD_LP

U23

VDD_LP

W20

VDD_LP

NVVDD_SENSE

N20

VDD_SENSE

GND_SENSE

M21

GND_SENSE

AC11

VDD33

AC12

VDD33

AC24

VDD33

AD24

VDD33

AE11

VDD33

AE12

VDD33

H7

VDD33

J7

VDD33

K7

VDD33

L10

VDD33

L7

VDD33

L8

VDD33

M10

VDD33

AF15

PEX_PLLAVDD

AE15

PEX_PLLDVDD

AE16

PEX_PLLGND

GND

NTP_GPU_AM10_NC

AM8

NC

NTP_GPU_AM8_NC

AM9

NC

NTP_GPU_AM9_NC

B32

NC

NTP_GPU_B32_NC

J6

NC

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PCI EXPRESS 16X, NVVDD DECOUPLING CAPS,PEX_IOVDD/Q DECOUPLING C APS

E GC

5

10%

X7R

0402

COMMON

PEX_IO_VDDQ

C849

.022UF

16V

10%

X7R

0402

COMMON

R6295%0

VDD33

PEX_PLL_VDD

C747

0.47UF

6.3V

10%

X5R

0402

COMMON

C675

.1UF

10V

10%

X5R

0402

COMMON

C804

0.47UF

6.3V

10%

X5R

0402

COMMON

C773

0.47UF

6.3V

10%

X5R

0402

COMMON

VALUES TBD

COMMON0402

16V

10%

X7R

0402

COMMON

VALUES TBD

Place near balls

C857

.022UF

16V

10%

X7R

0402

COMMON

C780

.1UF

10V

10%

X5R

0402

COMMON

C781

.1UF

10V

10%

X5R

0402

COMMON

C756

.1UF

10V

10%

X5R

0402

COMMON

C796

.1UF

10V

10%

X5R

0402

COMMON

C751

.001UF

50V

10%

X7R

0402

GND

180mA

Place near balls

20mA

C842

4700PF

25V

X7R

0402

COMMON

COMMON

Place near balls

C833

.1UF

10V 10%

X5R

0402

COMMON

C847

.01UF

16V

10%

X7R

0402

COMMON

Place near balls

OUT

Place near balls

C826

.1UF

10V

10%

X5R

0402

COMMON

C853

.1UF

10V

10%

X5R

0402

COMMON

10%

C786

0.47UF

6.3V

10%

X5R

0402

COMMON

C801

0.47UF

6.3V

10%

X5R

0402

COMMON

C798

.1UF

10V

10%

X5R

0402

COMMON

C762

.1UF

10V

10%

X5R

0402

COMMON

C738

4700PF

25V

10%

X7R

0402

COMMON

C745

4700PF

25V

10%

X7R

0402

COMMON

C831

470PF

16V

10%

X7R

0402

COMMON

C848

.01UF

16V

10%

X7R

0402

COMMON

C825

.01UF

16V

10%

X7R

0402

COMMON

22.2G< 2.5G<>

6

Place Close to GPU

C883

4.7UF

6.3V

X5R

0603

COMMON

C799

.1UF

10V

10%

X5R

0402

COMMON

C758

0.47UF

6.3V

10%

X5R

0402

COMMON

C746

0.47UF

6.3V

10%

X5R

0402

COMMON

C744

0.47UF

6.3V

10%

X5R

0402

COMMON

C844

.022UF

16V

10%

X7R

0402

COMMON

C854

.022UF

16V

10%

X7R

0402

COMMON

6

220R@100MHz

LB530

BEAD_0805 COMMON

10%

Place Close to GPU

C850

.01UF

16V

10%

X7R

0402

COMMON

C794

0.47UF

6.3V

10%

X5R

0402

COMMON

C777

.1UF

10V

10%

X5R

0402

COMMON

C727

0.47UF

6.3V

10%

X5R

0402

COMMON

3V3

LB531

120R@100MHz/X

NS

BEAD_0603

Place Near BGA

0.02R3A

0/8

3A

LB9

BEAD_0805

C96

4.7UF

10%

6.3V

X5R

0603

COMMON

C790

.1UF

10V

10%

X5R

0402

COMMON

C721

.022UF

16V

10%

X7R

0402

COMMON

C843

.022UF

16V

10%

X7R

0402

COMMON

Place Near BGA

150-220R@100MHz

C828

4.7UF

X5R

0603

COMMON

C894

4.7UF

6.3V

X5R

0603

COMMON

0.02R

COMMON

C757

.1UF

10V

10%

X5R

0402

COMMON

C784

10UF

6.3V

20%

X5R

0805

COMMON

C742

10UF

6.3V

20%

X5R

0805

COMMON

C797

0.47UF

6.3V

10%

X5R

0402

COMMON

A3V3

LB532

120R@100MHz

COMMON

BEAD_0603

GND

GND

LB524

BEAD_0603 COMMON

10%6.3V

PEX1V2

10%

PEX1V2

C908

22UF

20%

6.3V

X5R

0805

COMMON

GND

C783

10UF

6.3V

20%

X5R

0805

COMMON

C659

.1UF

10V

10%

X5R

0402

COMMON

C769

.1UF

10V

10%

X5R

0402

COMMON

C734

1UF

10V

10%

X7R

0603

COMMON

GND

22.2G< 2.3F>

GND

21.3B< 2.2C>

21.3G> 2.2C<

NVVDD

GND

GND

GND

GND

PEX1V2

C812

4.7UF

6.3V 10 %

X5R

0603

COMMON

GND

7

NET2A

PEX_REFCLK

BI

PEX_REFCLK*

GPU_PEX_REFCLK

BI

GPU_PEX_REFCLK*

BI

BI

PEX_TX0

BI

PEX_TX0*

BI

PEX_TX1

BI

PEX_TX1*

BI

PEX_TX2

BI

PEX_TX2*

BI

PEX_TX3

BI

PEX_TX3*

BI

PEX_TX4

BI

PEX_TX4*

BI

PEX_TX5

BI

PEX_TX5*

BI

PEX_TX6

BI

PEX_TX6*

BI

PEX_TX7

BI

PEX_TX7*

BI

PEX_TX8

BI

PEX_TX8*

BI

PEX_TX9

BI

PEX_TX9*

BI

PEX_TX10

BI

PEX_TX10*

BI

PEX_TX11

BI

PEX_TX11*

BI

PEX_TX12

BI

PEX_TX12*

BI

PEX_TX13

BI

PEX_TX13*

BI

PEX_TX14

BI

PEX_TX14*

BI

PEX_TX15

BI

PEX_TX15*

BI

PEX_TXX0

BI

PEX_TXX0*

BI

PEX_TXX1

BI

PEX_TXX1*

BI

PEX_TXX2

BI

PEX_TXX2*

BI

PEX_TXX3

BI

PEX_TXX3*

BI

BI

BI

PEX_TXX5

BI

PEX_TXX5*

BI

PEX_TXX6

BI

PEX_TXX6*

BI

PEX_TXX7

BI

PEX_TXX7*

BI

PEX_TXX8

BI

PEX_TXX8*

BI

PEX_TXX9

BI

PEX_TXX9*

BI

PEX_TXX10

BI

PEX_TXX10*

BI

PEX_TXX11

BI

PEX_TXX11*

BI

PEX_TXX12

BI

PEX_TXX12*

BI

PEX_TXX13

BI

PEX_TXX13*

BI

PEX_TXX14

BI

PEX_TXX14*

BI

PEX_TXX15

BI

PEX_TXX15*

BI

PEX_RX0

BI

PEX_RX0*

BI

PEX_RX1

BI

PEX_RX1*

BI

PEX_RX2

BI

PEX_RX2*

BI

PEX_RX3

BI

PEX_RX3*

BI

PEX_RX4

BI

PEX_RX4*

BI

PEX_RX5

BI

PEX_RX5*

BI

PEX_RX6

BI

PEX_RX6*

BI

PEX_RX7

BI

PEX_RX7*

BI

PEX_RX8

BI

PEX_RX8*

BI

PEX_RX9

BI

PEX_RX9*

BI

PEX_RX10

BI

PEX_RX10*

BI

PEX_RX11

BI

PEX_RX11*PEX_RX12

BI

PEX_RX12PEX_R X12 *

BI

PEX_RX12*

BI

PEX_RX13

BI

PEX_RX13*

BI

PEX_RX14

BI

PEX_RX14*

BI

PEX_RX15

BI

PEX_RX15*

BI

NVVDD_SENSE

BI

GND_SENSE

BI

BI

Title

Size Document Number Rev

Custom

Tuesday, October 25, 2005

Date: Sheet of

DIFFPAIR

GPU_PEX_REFCLK 20MIL_G2G_30MIL_USER_DI FF

GPU_PEX_REFCLK 20MIL_G2G_30MIL_USER_DI FF

PEX_TX0 20MIL_G2G_30MIL_US ER_DIFF

PEX_TX0 20MIL_G2G_30MIL_US ER_DIFF

PEX_TX5 20MIL_G2G_30MIL_US ER_DIFF

PEX_TX7 20MIL_G2G_30MIL_US ER_DIFF

PEX_TX8 20MIL_G2G_30MIL_US ER_DIFF

PEX_TX9 20MIL_G2G_30MIL_US ER_DIFF

PEX_TX13 20MIL_G2G_30MIL_US ER_DIFF

PEX_TXX7 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX7 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX8 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX9 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX10 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX11 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX12 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX13 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX14 20MIL_G2G_30MIL_USER_DIFF

PEX_TXX14 20MIL_G2G_30MIL_USER_DIFF

PEX_RX0 20MIL_G2G_30MIL_USER_DIFF

PEX_RX8 20MIL_G2G_30MIL_USER_DIFF

PEX_RX9 20MIL_G2G_30MIL_USER_DIFF

PEX_RX9 20MIL_G2G_30MIL_USER_DIFF

PEX_RX10 20MIL_G2G_30MIL_USER_DIFF

PEX_RX10 20MIL_G2G_30MIL_USER_DIFF

PEX_RX15 20MIL_G2G_30MIL_USER_DIFF

PEX_RX15 20MIL_G2G_30MIL_USER_DIFF

PEX_PLL_VDD

GIGABYTE

16X PCIe Interface

GV-NX66T128VP-SP

7

8

HGFEDCBA

NET_SPACING_RULE

20MIL_G2G_30MIL_USER_DI FFPEX_REFCLK

20MIL_G2G_30MIL_USER_DI FFPEX_REFCLK

20MIL_G2G_30MIL_USER_DIFFPEX_TX1

20MIL_G2G_30MIL_USER_DIFFPEX_TX1

20MIL_G2G_30MIL_USER_DIFFPEX_TX2

20MIL_G2G_30MIL_USER_DIFFPEX_TX2

20MIL_G2G_30MIL_USER_DIFFPEX_TX3

20MIL_G2G_30MIL_USER_DIFFPEX_TX3

20MIL_G2G_30MIL_USER_DIFFPEX_TX4

20MIL_G2G_30MIL_USER_DIFFPEX_TX4

20MIL_G2G_30MIL_USER_DIFFPEX_TX5

20MIL_G2G_30MIL_USER_DIFFPEX_TX6

20MIL_G2G_30MIL_USER_DIFFPEX_TX6

20MIL_G2G_30MIL_USER_DIFFPEX_TX7

20MIL_G2G_30MIL_USER_DIFFPEX_TX8

20MIL_G2G_30MIL_USER_DIFFPEX_TX9

20MIL_G2G_30MIL_USER_DIFFPEX_TX10

20MIL_G2G_30MIL_USER_DIFFPEX_TX10

20MIL_G2G_30MIL_USER_DIFFPEX_TX11

20MIL_G2G_30MIL_USER_DIFFPEX_TX11

20MIL_G2G_30MIL_USER_DIFFPEX_TX12

20MIL_G2G_30MIL_USER_DIFFPEX_TX12

20MIL_G2G_30MIL_USER_DIFFPEX_TX13

20MIL_G2G_30MIL_USER_DIFFPEX_TX14

20MIL_G2G_30MIL_USER_DIFFPEX_TX14

20MIL_G2G_30MIL_USER_DIFFPEX_TX15

20MIL_G2G_30MIL_USER_DIFFPEX_TX15

20MIL_G2G_30MIL_USER_DIFFPEX_TXX0

20MIL_G2G_30MIL_USER_DIFFPEX_TXX0

20MIL_G2G_30MIL_USER_DIFFPEX_TXX1

20MIL_G2G_30MIL_USER_DIFFPEX_TXX1

20MIL_G2G_30MIL_USER_DIFFPEX_TXX2

20MIL_G2G_30MIL_USER_DIFFPEX_TXX2

20MIL_G2G_30MIL_USER_DIFFPEX_TXX3

20MIL_G2G_30MIL_USER_DIFFPEX_TXX3

20MIL_G2G_30MIL_USER_DIFFPEX_TXX4

20MIL_G2G_30MIL_USER_DIFFPEX_TXX4

20MIL_G2G_30MIL_USER_DIFFPEX_TXX5

20MIL_G2G_30MIL_USER_DIFFPEX_TXX5

20MIL_G2G_30MIL_USER_DIFFPEX_TXX6

20MIL_G2G_30MIL_USER_DIFFPEX_TXX6

20MIL_G2G_30MIL_USER_DIFFPEX_TXX8

20MIL_G2G_30MIL_USER_DIFFPEX_TXX9

20MIL_G2G_30MIL_USER_DIFFPEX_TXX10

20MIL_G2G_30MIL_USER_DIFFPEX_TXX11

20MIL_G2G_30MIL_USER_DIFFPEX_TXX12

20MIL_G2G_30MIL_USER_DIFFPEX_TXX13

20MIL_G2G_30MIL_USER_DIFFPEX_TXX15

20MIL_G2G_30MIL_USER_DIFFPEX_TXX15

20MIL_G2G_30MIL_USER_DIFFPEX_RX0

20MIL_G2G_30MIL_USER_DIFFPEX_RX1

20MIL_G2G_30MIL_USER_DIFFPEX_RX1

20MIL_G2G_30MIL_USER_DIFFPEX_RX2

20MIL_G2G_30MIL_USER_DIFFPEX_RX2

20MIL_G2G_30MIL_USER_DIFFPEX_RX3

20MIL_G2G_30MIL_USER_DIFFPEX_RX3

20MIL_G2G_30MIL_USER_DIFFPEX_RX4

20MIL_G2G_30MIL_USER_DIFFPEX_RX4

20MIL_G2G_30MIL_USER_DIFFPEX_RX5

20MIL_G2G_30MIL_USER_DIFFPEX_RX5

20MIL_G2G_30MIL_USER_DIFFPEX_RX6

20MIL_G2G_30MIL_USER_DIFFPEX_RX6

20MIL_G2G_30MIL_USER_DIFFPEX_RX7

20MIL_G2G_30MIL_USER_DIFFPEX_RX7

20MIL_G2G_30MIL_USER_DIFFPEX_RX8

20MIL_G2G_30MIL_USER_DIFFPEX_RX11

20MIL_G2G_30MIL_USER_DIFFPEX_RX11

20MIL_G2G_30MIL_USER_DIFFPEX_RX12

20MIL_G2G_30MIL_USER_DIFFPEX_RX12

20MIL_G2G_30MIL_USER_DIFFPEX_RX13

20MIL_G2G_30MIL_USER_DIFFPEX_RX13

20MIL_G2G_30MIL_USER_DIFFPEX_RX14

20MIL_G2G_30MIL_USER_DIFFPEX_RX14

MIN_LINE_WIDTH

10MIL

10MIL

10MIL

226

8

1

2

3

4

5

1.0

1

03 FBA MEMORY INTERFACE

4.4B<> 4.1G<>

1

A A

2

B B

4.4B<> 4.1G<>

3

4.5B<> 4.1G<>

C C

4.4B<> 4.1G<>

FBVDD

FBAD[63..0]

BI

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

FBADQM[7..0]

OUT

BI

BI

FBADQS_WP[7..0]

FBADQS_RN[7..0]

0

FBADQM0

1

FBADQM1

2

FBADQM2

3

FBADQM3

4

FBADQM4

5

FBADQM5

6

FBADQM6

7

FBADQM7

0

FBADQS_WP0

1

FBADQS_WP1

2

FBADQS_WP2

3

FBADQS_WP3

4

FBADQS_WP4

5

FBADQS_WP5

6

FBADQS_WP6

7

FBADQS_WP7

0

FBADQS_RN0

1

FBADQS_RN1

2

FBADQS_RN2

3

FBADQS_RN3

4

FBADQS_RN4

5

FBADQS_RN5

6

FBADQS_RN6

7

FBADQS_RN7

4

C652

.1UF/X

10V

COMMON

Rtop

Rbot

D D

5

GND

R602 1K

R607 2.55K

1%

0402

COMMON0402

1%

10%

X5R

0402

NS

C660

.1UF

10V

10%

X5R

0402

COMMON

VREF = FB VDDQ * Rbot/(Rtop + Rbot)

VREF = 0.70 * FBVDDQ

1.26V = 1.8V * 2.7K/(1.15K + 2.7K)

DDR3:

FBA_VREF

2

U11B

ALL FBVDD PINS ARE NC ON NV43 DESKTOP G3 PACKAGE

BGA820

COMMON

AD29

AE29

AD28

AC28

AB29

AA30

AB30

AM30

AF30

AJ31

AJ30

AJ32

AK29

AM31

AL30

AE32

AE30

AE31

AD30

AC31

AC32

AB32

AB31

AG27

AF28

AH28

AG28

AG29

AD27

AF27

AE28

AA29

AK30

AC30

AG30

AB28

AL32

AF32

AH30

AA28

AL31

AF31

AH29

N27

M27

N28

L29

K27

K28

J29

J28

P30

N31

N30

N32

L31

L30

J30

L32

H30

K30

H31

F30

H32

E31

D30

E30

H28

H29

E29

J27

F27

E27

E28

F28

Y28

M29

M30

G30

F29

L28

K31

G32

G28

M28

K32

G31

G27

E32

2/14 FBA

FBAD0

FBAD1

FBAD2

FBAD3

FBAD4

FBAD5

FBAD6

FBAD7

FBAD8

FBAD9

FBAD10

FBAD11

FBAD12

FBAD13

FBAD14

FBAD15

FBAD16

FBAD17

FBAD18

FBAD19

FBAD20

FBAD21

FBAD22

FBAD23

FBAD24

FBAD25

FBAD26

FBAD27

FBAD28

FBAD29

FBAD30

FBAD31

FBAD32

FBAD33

FBAD34

FBAD35

FBAD36

FBAD37

FBAD38

FBAD39

FBAD40

FBAD41

FBAD42

FBAD43

FBAD44

FBAD45

FBAD46

FBAD47

FBAD48

FBAD49

FBAD50

FBAD51

FBAD52

FBAD53

FBAD54

FBAD55

FBAD56

FBAD57

FBAD58

FBAD59

FBAD60

FBAD61

FBAD62

FBAD63

FBADQM0

FBADQM1

FBADQM2

FBADQM3

FBADQM4

FBADQM5

FBADQM6

FBADQM7

FBADQS_WP0

FBADQS_WP1

FBADQS_WP2

FBADQS_WP3

FBADQS_WP4

FBADQS_WP5

FBADQS_WP6

FBADQS_WP7

FBADQS_RN0

FBADQS_RN1

FBADQS_RN2

FBADQS_RN3

FBADQS_RN4

FBADQS_RN5

FBADQS_RN6

FBADQS_RN7

FB_VREF1

FBAD0

FBAD1

FBAD2

FBAD3

FBAD4

FBAD5

FBAD6

FBAD7

FBAD8

FBAD9

FBAD10

FBAD11

FBAD12

FBAD13

FBAD14

FBAD15

FBAD16

FBAD17

FBAD18

FBAD19

FBAD20

FBAD21

FBAD22

FBAD23

FBAD24

FBAD25

FBAD26

FBAD27

FBAD28

FBAD29

FBAD30

FBAD31

FBAD32

FBAD33

FBAD34

FBAD35

FBAD36

FBAD37

FBAD38

FBAD39

FBAD40

FBAD41

FBAD42

FBAD43

FBAD44

FBAD45

FBAD46

FBAD47

FBAD48

FBAD49

FBAD50

FBAD51

FBAD52

FBAD53

FBAD54

FBAD55

FBAD56

FBAD57

FBAD58

FBAD59

FBAD60

FBAD61

FBAD62

FBAD63

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_DEBUG

FBA_REFCLK

FBA_REFCLK

FBA_PLLVDD

FBA_PLLAVDD

FBA_PLLGND

3

NTP_GPU_A12

A12

NTP_GPU_A15

A15

NTP_GPU_A18

A18

NTP_GPU_A21

A21

NTP_GPU_A24

A24

NTP_GPU_A27

A27

NTP_GPU_A3

A3

NTP_GPU_A30

A30

NTP_GPU_A6

A6

NTP_GPU_A9

A9

NTP_GPU_AA32

AA32

NTP_GPU_AD32

AD32

NTP_GPU_AG32

AG32

NTP_GPU_AK32

AK32

NTP_GPU_C32

C32

NTP_GPU_F32

F32

NTP_GPU_J32

J32

NTP_GPU_M32

M32

NTP_GPU_R32

R32

NTP_GPU_V32

V32

AA25

AA26

AB25

AB26

G11

G12

G15

G18

G21

G22

H11

H12

H15

H18

H21

H22

L25

L26

M25

M26

R25

R26

V25

V26

FBA_CMD[26..0]

0

FBA_CMD0

P32

U27

P31

U30

Y31

W32

W31

T32

V27

T28

T31

U32

W29

W30

T27

V28

V30

U31

R27

V29

T30

W28

R29

R30

P29

U28

Y32

P28

R28

Y27

AA27

TP NOW

Y30

RFU

AC26

RFU

AC27

D32

D31

G23

G25

G24

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

NTP_FBA_CMD<7>

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

NTP_FBA_CMD<26>

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

TP_FBA_DBI0

TP_FBA_DBI1

TP_FBA_DEBUG

FBA_REFCLK

FBA_REFCLK*

FBA_PLLAVDD

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

OUT

OUT

OUT

OUT

GND

4

PLACE BELOW GPU

C792

.1UF

10V

10%

X5R

0402

COMMON

OUT

PLACE close to GPU

FBVDD

4.1G<

4.2A<

R596

4.1G<

100/X

4.2D<

1%

0402

COMMON

FBA_REFCLK*

R593

100

1%

0402

COMMON

GND

5

FBVDD

C754

C708

C806

C730

.1UF

10V

10%

X5R

0402

COMMON

C5

.1UF

10V

10%

X5R

0402

COMMON

C6

.1UF

10V

10%

X5R

0402

COMMON

C50

.1UF

10V

10%

X5R

0402

COMMON

C68

.1UF

10V

10%

X5R

0402

COMMON

C824

1UF

10V

10%

X7R

0603

COMMON

C697

1UF

10V

10%

X7R

0603

COMMON

GND

GND

GND

GND

C705

0.47UF

6.3V

10%

X5R

0402

COMMON

C704

.1UF

10V

10%

X5R

0402

COMMON

0.47UF

6.3V

10%

X5R

0402

COMMON

C750

0.47UF

6.3V

10%

X5R

0402

COMMON

C698

.1UF

10V

10%

X5R

0402

COMMON

0.47UF

6.3V

10%

X5R

0402

COMMON

C707

.1UF

10V

10%

X5R

0402

COMMON

C722

0.47UF

6.3V

10%

X5R

0402

COMMON

.1UF

10V

10%

X5R

0402

COMMON

C755

.1UF

10V

10%

X5R

0402

COMMON

C800

0.47UF

6.3V

10%

X5R

0402

COMMON

GND

4.1G< 4.1A<

6

IN

IN

IN

IN

FBVDD

C740

10UF

6.3V

20%

X5R

0805

COMMON

PLACE MIDWAY B ET W EE N G P U A ND MEMORY

FBA_REFCLK

FBA_REFCLK*

C856

10UF

6.3V

20%

X5R

0805

COMMON

FBA_PLLVDD

FBA_PLLAVDD

DIFFPAIR

C594

10UF

6.3V

20%

X5R

0805

COMMON

PLACE NEAR GPU

7

C597

10UF

6.3V

20%

X5R

0805

COMMON

GND

MIN_LINE_WIDTHNET

4MIL 10MIL

10MIL

10MIL

FBA_CMD11

NET_SPACING_RULE

10MIL4MIL

FBVDD

R638

10K/X

5%

0402

NS

R640

10K

5%

0402

COMMON

8

HGFEDCBA

1

2

3

GND

CKE Stuff options fo r DDR3 configation for

R599

100/X

1%

0402

COMMON

R601

100

1%

0402

COMMON

PLACE close to balls

FBA_PLLVDD

C689

.01UF

16V

10%

X7R

0402

COMMON

C710

.01UF

16V

10%

X7R

0402

COMMON

C692

.1UF

10V

10%

X5R

0402

COMMON

C685

.1UF

10V

10%

X5R

0402

COMMON

FB_DLLVDD

ON NV3x version's of G3

FB_DLLVDD will be routed on FB_PLLVDD

150-220R@100MHz

LB507

BEAD_0603 COMMON

C674

1UF

6.3V

10%

X5R

0402

COMMON

150-220R@100MHz

LB509

BEAD_0603 COMMON

C672

1UF

6.3V

10%

X5R

0402

COMMON

NVVDD

C662

4.7UF

6.3V

10%

X5R

0603

COMMON

C654

4.7UF

6.3V

10%

X5R

0603

COMMON

A3V3

GND

on-die terminations at the memor y

IMPORTANT FOR POWER ON INITIALIZATION OF DDR3 MEMS

DDR3: DETERMINES THE ODT VALUE FOR ADDR AND CONTROL PINS

CKE = 0 --> ODT = ZQ/2

CKE = 1 --> ODT = ZQ

4

GND

FBA_AVDD is TBD. This may not be hooked up on the Package.

5

ASSEMBLY

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARR ANTIES INCLU DING, WITHOU T LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

2

3

PAGE DETAIL

4

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

FBA MEMORY INTERFACE, GPU FBVDD/Q DECOUPLING CAPS

E GC

5

Title

Size Document Number Rev

Custom

Date: Sheet of

6

7

GIGABYTE

FBA MEMORY INTERFACE

GV-NX66T128VP-SP

Tuesday, October 25, 2005

1.0

326

8

1

4 FrameBuffer: Partition A 8Mx32 BGA144 DDR3

FBA_CMD[26..0]

3.2D> 4.1G<

IN

1

A A

Low Sub-Partition

3.3D> 4.1G<

3.4D> 4.1G<

2

B B

DDR3:

ZQ = 6x desired output

impedence of DQ drivers

Impedence = 240 / 6 = 40 ohm

144BGA CMD Mapping

ADDRCMD

CMD15 RAS*

CAS*

CMD25

WE*

CMD9

CMD11 CKE

CMD12

3

C C

RESET

CS0*

CMD8

CMD7

CS1**notused

A<0>

CMD1

CMD3

A<1>

CMD2

A<2>

CMD0

A<3>

Low Sub-Partition

A<4>

CMD24

CMD22

A<5>

CMD13

A<2>

A<3>

CMD4

CMD5

CMD6

CMD21

CMD23

CMD19

CMD20

CMD17

CMD16

CMD14

CMD10

CMD18

Hi Sub-Partition

A<4>

A<5>

A<6>

A<7>

A<8>

A<9>

A<10

A<11>

A<12>

BA0

BA1

4

D D

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARR ANTIES INCLU DING, WITHOU T LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

IN

IN

12

15

25

9

8

1

3

2

0

24

22

21

23

19

20

17

16

14

10

18

11

FBA_CMD12

R643

10K

5%

0402

COMMON

GND GND

3.1A<> 4.1G<>

3.3A> 4.1G<>

3.4A<> 4.1G<>

3.3A<> 4.1G<>

2

A-CS0-LOW-32bit

U8E

BGA144

BGA144

GND

FBAD[63..0]

FBADQM[7..0]

FBADQS_RN[7..0]

FBADQS_WP[7..0]

COMMON

M5

RAS

N6

CAS

N9

WE

M10

CS

N2

A0

N3

A1

M3

A2

L3

A3

L12

A4

M12

A5

N12

A6

N13

A7

N11

A8

M11

A9

M4

A10

N4

A11

L9

NC/A<12>

N5

BA<0>

N10

BA<1>

L6

NC/BA<2>

M7

CKE

N7

CLK

N8

CLK

NC/RFU

E3

NC/RFU

E12

NC/RFU

M8

RESET

M6

M9

ZQ

F6

THERM

F7

THERM

F8

THERM

F9

THERM

G6

THERM

G7

THERM

G8

THERM

G9

THERM

H6

THERM

H7

THERM

H8

THERM

H9

THERM

J6

THERM

J7

THERM

J8

THERM

J9

THERM

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

VREF:

M2 - DATA

M13 - ADDR

FBADQM0

FBADQM1

FBADQM2

FBADQM3

FBADQM5

FBADQM6

FBADQM7

FBADQS_RN0

FBADQS_RN1

FBADQS_RN2

FBADQS_RN3

FBADQS_RN4

FBADQS_RN5

FBADQS_RN6

FBADQS_RN7

FBADQS_WP0

FBADQS_WP1

FBADQS_WP2

FBADQS_WP3

FBADQS_WP4

FBADQS_WP5

FBADQS_WP6

FBADQS_WP7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VREF

VREF

FBA_CMD15 FBA_CMD15

FBA_CMD25 FBA_CMD25

FBA_CMD9 FBA_CMD9

CS0

FBA_CMD8 FBA_CMD8

FBA_CMD1 FBA_CMD1

FBA_CMD3 FBA_CMD3

FBA_CMD2

FBA_CMD0

FBA_CMD24

FBA_CMD22

FBA_CMD21 FBA_CMD21

FBA_CMD23 FBA_CMD23

FBA_CMD19 FBA_CMD19

FBA_CMD20 FBA_CMD20

FBA_CMD17 FBA_CMD17

FBA_CMD16 FBA_CMD16

FBA_CMD14 FBA_CMD14

FBA_CMD10 FBA_CMD10

FBA_CMD18 FBA_CMD18

TP_FBA0_BA<2>

FBA_CMD11 FBA_CMD11

FBA_CLK0

FBA_CLK0*

TP_FBA0_NC1

TP_FBA0_NC2

TP_FBA0_NC3

FBA_CMD12 FBA_CMD12

FBA_ZQ0 FBA_ZQ1

R61

240

1%

0603

COMMON

BI

BI

BI

BI

2

FBVDD

D7

D8

E4

E11

L4

L7

L8

L11

C4

C5

C7

C8

C10

C11

F4

F11

G4

G11

H4

H11

J4

J11

K4

K11

B4

B11

D4

D5

D6

D9

D10

D11

E6

E9

F5

F10

G5

G10

H5

H10

J5

J10

K5

K10

E5

E7

E8

E10

K6

K7

K8

K9

L5

L10

FBA_VREF_DATA0

M2

FBA_VREF_ADDR0

M13

VREF = FBVDDQ * R2/(R1 + R2)

DDR3:

VREF = 0.70 * FBVDDQ

1.26V = 1.8V * 2.7K/(1.15K + 2.7K)

0

1

2

3

4

5

6

7

32

33

34

35

36

37

38

39

3

GND

FBAD0

FBAD1

FBAD2

FBAD3

FBAD4

FBAD5

FBAD6

FBAD7

FBADQM0

FBADQS_RN0

FBADQS_WP0

FBAD32

FBAD33

FBAD34

FBAD35

FBAD36

FBAD37

FBAD38

FBAD39

FBADQM4

FBADQS_RN4

FBADQS_WP4

3

FBA_CMD[26..0]

FBA Partition

Termination for Sub-Partition and CLK

MUST BE PLACED as close as possible to

the BGA memory on the line BEFORE the

MEMORY pin!!

Minimize the stub length!!

2

FBA_CMD2

0

FBA_CMD0

24

FBA_CMD24

22

FBA_CMD22

13

FBA_CMD13

4

FBA_CMD4

5

FBA_CMD5

6

FBA_CMD6

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBVDD

C772

.1UF/X

R639

10V

1K

R1

10%

1%

X5R

0402

0402

COMMON

NS

R635

C753

2.55K

.1UF

R2

1%

10V

0402

10%

COMMON

X5R

0402

COMMON

GND

U8A

BGA144

BGA144

COMMON

L2

DQ0

K2

DQ1

G2

DQ2

J2

DQ3

F2

DQ4

F3

DQ5

G3

DQ6

K3

DQ7

J3

DQM

H3

DQSR

H2

DQSW

U12E

BGA144

BGA144

COMMON

G12

DQ0

L13

DQ1

K12

DQ2

J13

DQ3

G13

DQ4

K13

DQ5

F12

DQ6

F13

DQ7

J12

DQM

H12

DQSR

H13

DQSW

COMMON

COMMON

4

COMMON

COMMON

COMMON

COMMON

COMMON

60.4/4/1

60.4/4/1

60.4/4/1

COMMON

60.4/4/1

COMMON

120

120

120

120

120

120

120

120

DDR3:

R627

0402

5%

R628

0402COMMON

5%

R611

0402

5%

R610

0402

5%

R674

0402

5%

R675

0402COMMON

5%

R647

0402

5%

R646

0402COMMON

5%

R68

0402COMMON

5%

R67

0402COMMON

5%

R94

0402

5%

R92

0402

5%

ZQ = 6x desired output

impedence of DQ drivers

Impedence = 240 / 6 = 40 ohm

FBA_CMD[26..0]

FBVDD

Hi Sub-Partition

3.4D> 4.1G<

3.4D> 4.1G<

15

25

9

8

CS0

1

3

13

FBA_CMD13

4

FBA_CMD4

5

FBA_CMD5

6

FBA_CMD6

21

23

19

20

17

16

14

10

18

11

IN

IN

FBA_CLK1

FBA_CLK1*

GND

FBVDD

C648

.1UF/X

R597

10V

1K

R1

10%

1%

X5R

0402

0402

NS

R605

C655

2.55K

.1UF

R2

1%

10V

0402

10%

X5R

0402

COMMON

GND

U8B

BGA144

BGA144

ASSEMBLY

PAGE DETAIL

COMMON

E2

DQ0

D2

DQ1

C2

DQ2

D3

DQ3

B5

DQ4

B6

DQ5

B7

DQ6

C6

DQ7

C3

DQM

B3

DQSR

B2

DQSW

U12A

BGA144

BGA144

COMMON

D2

DQ0

B7

DQ1

B6

DQ2

B5

DQ3

C6

DQ4

E2

DQ5

D3

DQ6

C2

DQ7

C3

DQM

B3

DQSR

B2

DQSW

8

FBAD8

9

FBAD9

10

FBAD10

11

FBAD11

12

FBAD12

13

FBAD13

14

FBAD14

15

FBAD15

FBADQM1

FBADQS_RN1

FBADQS_WP1

40

FBAD40

41

FBAD41

42

FBAD42

43

FBAD43

44

FBAD44

45

FBAD45

46

FBAD46

47

FBAD47

FBADQM5

FBADQS_RN5

FBADQS_WP5

16

FBAD16

17

FBAD17

18

FBAD18

19

FBAD19

20

FBAD20

21

FBAD21

22

FBAD22

23

FBAD23

FBADQM2

FBADQS_RN2

FBADQS_WP2

48

FBAD48

49

FBAD49

50

FBAD50

51

FBAD51

52

FBAD52

53

FBAD53

54

FBAD54

55

FBAD55

FBADQM6

FBADQS_RN6

FBADQS_WP6

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

FBA 8Mx32 DDR3 MEMORIES, FBA COMMAND BUS PU'S, FBA CLK PU'S

4

TP_FBA1_BA<2>

TP_FBA1_NC1

TP_FBA1_NC2

TP_FBA1_NC3

R88

240

1%

0603

COMMON

5

A-CS0-HI-32bit

U12C

BGA144

BGA144

COMMON

M5

RAS

N6

CAS

N9

WE

M10

CS

N2

A0

N3

A1

M3

A2

L3

A3

L12

A4

M12

A5

N12

A6

N13

A7

N11

A8

M11

A9

M4

A10

N4

A11

L9

NC/A<12>

N5

BA<0>

N10

BA<1>

L6

NC/BA<2>

M7

CKE

N7

CLK

N8

CLK

NC/RFU

E3

NC/RFU

E12

NC/RFU

M8

RESET

M6

M9

ZQ

F6

THERM

F7

THERM

F8

THERM

F9

THERM

G6

THERM

G7

THERM

G8

THERM

G9

THERM

H6

THERM

H7

THERM

H8

THERM

H9

THERM

J6

THERM

J7

THERM

J8

THERM

J9

THERM

GND

D7

VDD

D8

VDD

E4

VDD

E11

VDD

L4

VDD

L7

VDD

L8

VDD

L11

VDD

C4

VDDQ

C5

VDDQ

C7

VDDQ

C8

VDDQ

C10

VDDQ

C11

VDDQ

F4

VDDQ

F11

VDDQ

G4

VDDQ

G11

VDDQ

H4

VDDQ

H11

VDDQ

J4

VDDQ

J11

VDDQ

K4

VDDQ

K11

VDDQ

B4

VSSQ

B11

VSSQ

D4

VSSQ

D5

VSSQ

D6

VSSQ

D9

VSSQ

D10

VSSQ

D11

VSSQ

E6

VSSQ

E9

VSSQ

F5

VSSQ

F10

VSSQ

G5

VSSQ

G10

VSSQ

H5

VSSQ

H10

VSSQ

J5

VSSQ

J10

VSSQ

K5

VSSQ

K10

VSSQ

E5

VSS

E7

VSS

E8

VSS

E10

VSS

K6

VSS

K7

VSS

K8

VSS

K9

VSS

L5

VSS

L10

VSS

M2

VREF

M13

VREF

DDR3: VREF = 0 . 70 * FBV D D Q

FBVDD

FBA_VREF_DATA1

FBA_VREF_ADDR1

VREF = FBVDDQ * R2/(R1 + R2)

1.26V = 1.8V * 2.7K/(1.15K + 2.7K)

6

3.3D> 4.2A<

IN

3.4D> 4.2A<

IN

3.4D> 4.2D<

IN

3.4D> 4.2D<

IN

3.2D> 4.1A<

IN

3.1A<> 4.4B<>

BI

3.3A> 4.4B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

3.4A<> 4.4B<>

BI

3.3A<> 4.5B<>

BI

FBA_VREF_DATA0

BI

FBA_VREF_ADDR0

BI

FBA_VREF_DATA1

BI

FBA_VREF_ADDR1

BI

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_CMD[26..0]

FBAD[63..0]

FBADQM[7..0]

FBADQS_RN0

FBADQS_WP0

FBADQS_RN1

FBADQS_WP1

FBADQS_RN2

FBADQS_WP2

FBADQS_RN3

FBADQS_WP3

FBADQS_RN4

FBADQS_WP4

FBADQS_RN5

FBADQS_WP5

FBADQS_RN6

FBADQS_WP6

FBADQS_RN7

FBADQS_WP7

7

DIFFPAIR MIN_LINE_ WIDTH SPACINGNET

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

5MIL

5MIL

5MIL

5MIL

12MIL

12MIL

12MIL

12MIL

HGFEDCBA

15MIL_G2G_25MIL

15MIL_G2G_25MIL

15MIL_G2G_25MIL

15MIL_G2G_25MIL

15MIL

15MIL

15MIL

15MILFBADQS_RN0

15MILFBADQS_RN0

15MILFBADQS_RN1

15MILFBADQS_RN1

15MILFBADQS_RN2

15MILFBADQS_RN2

15MILFBADQS_RN3

15MILFBADQS_RN3

15MILFBADQS_RN4

15MILFBADQS_RN4

15MILFBADQS_RN5

15MILFBADQS_RN5

15MILFBADQS_RN6

15MILFBADQS_RN6

15MILFBADQS_RN7

15MILFBADQS_RN7

8

1

2

GND

FBVDD

R689

C907

1K

.1UF/X

R1

10V

1%

0402

10%

COMMON

X5R

0402

NS

COMMON

R684

2.55K

R2

1%

0402

GND

C898

.1UF

10V

10%

X5R

0402

COMMON

COMMON

COMMON

FBVDD

C803

.1UF/X

R642

10V

1K

R1

10%

1%

X5R

0402

0402

NS

R644

C818

2.55K

.1UF

R2

10V

1%

0402

10%

X5R

0402

COMMON

3

GND

U8C

BGA144

BGA144

COMMON

B10

DQ0

B8

DQ1

B9

DQ2

C13

DQ3

C9

DQ4

D12

DQ5

E13

DQ6

D13

DQ7

C12

DQM

B12

DQSR

B13

DQSW

U12B

BGA144

BGA144

COMMON

B9

DQ0

B8

DQ1

C9

DQ2

B10

DQ3

D12

DQ4

C13

DQ5

D13

DQ6

E13

DQ7

C12

DQM

B12

DQSR

B13

DQSW

E GC

5

24

FBAD24

25

FBAD25

26

FBAD26

27

FBAD27

28

FBAD28

29

FBAD29

30

FBAD30

31

FBAD31

FBADQM3FBADQM4

FBADQS_RN3

FBADQS_WP3

56

FBAD56

57

FBAD57

58

FBAD58

59

FBAD59

60

FBAD60

61

FBAD61

62

FBAD62

63

FBAD63

FBADQM7

FBADQS_RN7

FBADQS_WP7

U8D

BGA144

BGA144

COMMON

F12

DQ0

G12

DQ1

G13

DQ2

F13

DQ3

J13

DQ4

K12

DQ5

L13

DQ6

K13

DQ7

J12

DQM

H12

DQSR

H13

DQSW

U12D

BGA144

BGA144

COMMON

L2

DQ0

F3

DQ1

G2

DQ2

K2

DQ3

F2

DQ4

K3

DQ5

J2

DQ6

G3

DQ7

J3

DQM

H3

DQSR

H2

DQSW

Title

Size Document Number Rev

Custom

Date: Sheet of

6

7

GIGABYTE

FBA 8Mx32 DDR3 MEMORIES

GV-NX66T128VP-SP

Tuesday, October 25, 2005

426

8

4

5

1.0

1

2

3

05.FRAME BUFFER: PARTITION A DECOUPLING

4

5

6

7

8

HGFEDCBA

1

A A

Decoupling for FBA 0..31

C529

4.7UF

6.3V

10%

X5R

0603

COMMON

PLACE NEAR MEMORY FBVDD PINS

C841

.1UF

10V

10%

X5R

0402

COMMON

C718

.01UF

25V

10%

X7R

0402

COMMON

PLACE NEAR MEMORY FBVDDQ PINS

C642

0.47UF

6.3V

10%

X5R

0402

COMMON

C541

.1UF

10V

10%

X5R

0402

COMMON

C765

.1UF

10V

10%

X5R

0402

COMMON

C678

.01UF

25V

10%

X7R

0402

COMMON

C48

.01UF

25V

10%

X7R

0402

COMMON

C571

.1UF

10V

10%

X5R

0402

COMMON

C725

.01UF

25V

10%

X7R

0402

COMMON

C680

.01UF

16V

10%

X7R

0402

COMMON

C683

.01UF

25V

10%

X7R

0402

COMMON

C691

.1UF

10V

10%

X5R

0402

COMMON

C767

0.47UF

6.3V

10%

X5R

0402

COMMON

GND

GND

C716

.01UF

25V

10%

X7R

0402

C706

.01UF

25V

10%

X7R

0402

COMMON

COMMON

C719

.01UF

25V

10%

X7R

0402

COMMON

C717

.01UF

25V

10%

X7R

0402

COMMON

C682

.01UF

25V

10%

X7R

0402

COMMON

GND

GND

2

FBVDD

C832

1UF

10V

10%

X7R

0603

COMMON

B B

3

C C

4

FBVDD

C887

1UF

10V

10%

X7R

0603

COMMON

C749

1UF

10V

10%

X7R

0603

COMMON

C543

4.7UF

6.3V

10%

X5R

0603

COMMON

C641

4.7UF

6.3V

10%

X5R

0603

COMMON

C681

.1UF

10V

10%

X5R

0402

COMMON

C512

.1UF

10V

10%

X5R

0402

COMMON

C527

.1UF

10V

10%

X5R

0402

COMMON

C712

.1UF

10V

10%

X5R

0402

COMMON

Decoupling for FBA 32..63

FBVDD

C670

C542

4.7UF

6.3V

10%

X5R

0603

COMMON

C544

.1UF

10V

10%

X5R

0402

COMMON

C875

.1UF

10V

10%

X5R

0402

COMMON

C572

.1UF

10V

10%

X5R

0402

COMMON

C528

.1UF

10V

10%

X5R

0402

COMMON

C668

.1UF

10V

10%

X5R

0402

COMMON

FBVDD

1UF

10V

10%

X7R

0603

COMMON

C562

1UF

10V

10%

X7R

0603

COMMON

C658

4.7UF

6.3V

10%

X5R

0603

COMMON

C578

4.7UF

6.3V

10%

X5R

0603

COMMON

C536

1UF

10V

10%

X7R

0603

COMMON

PLACE NEAR MEMORY FBVDD PINS

C902

C715

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C859

.01UF

25V

10%

X7R

0402

COMMON

PLACE NEAR MEMORY FBVDDQ PINS

C876

.01UF

25V

10%

X7R

0402

COMMON

C858

.01UF

16V

10%

X7R

0402

COMMON

C878

.01UF

25V

10%

X7R

0402

COMMON

C726

0.47UF

6.3V

10%

X5R

0402

COMMON

C866

.01UF

25V

10%

X7R

0402

COMMON

GND

GND

C855

C871

.01UF

25V

10%

X7R

0402

COMMON

C861

.01UF

25V

10%

X7R

0402

COMMON

C882

.01UF

25V

10%

X7R

0402

COMMON

C879

.01UF

25V

10%

X7R

0402

COMMON

C860

.01UF

25V

10%

X7R

0402

COMMON

C877

.01UF

25V

10%

X7R

0402

COMMON

.01UF

25V

10%

X7R

0402

COMMON

GND

GND

1

2

3

4

D D

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARR ANTIES INCLU DING, WITHOU T LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

2

3

4

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

FBA MEMORY FBVDD/Q DECOUPLING CAPS

E GC

5

Title

Size Document Number Rev

Custom

Date: Sheet of

6

7

GIGABYTE

FBA MEMORY FBVDD/Q CAPS

GV-NX66T128VP-SP

Tuesday, October 25, 2005

526

8

5

1.0

1

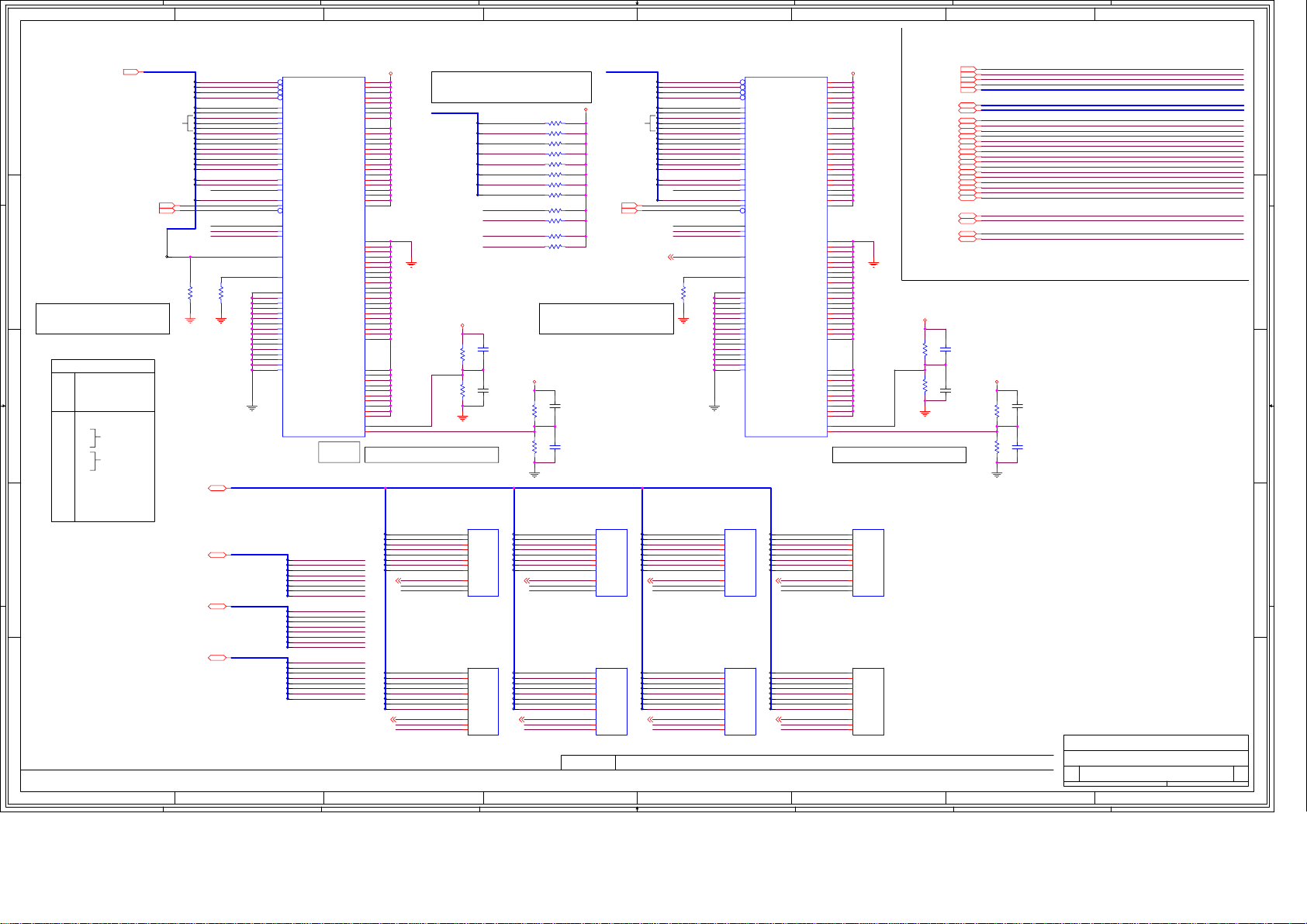

7.1G<> 7.4B<>

1

A A

FBCD[63..0]

BI

2

B B

3

C C

7.1G<> 7.4B<>

7.1G<> 7.2G<> 7.5B<>

7.1G<> 7.2G<> 7.4B<>

FBCDQM[7..0]

OUT

FBCDQS_WP[7..0]

BI

FBCDQS_RN[7..0]

BI

4

D D

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARR ANTIES INCLU DING, WITHOU T LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

TP_FBC_VREF

FBCD0

FBCD1

FBCD2

FBCD3

FBCD4

FBCD5

FBCD6

FBCD7

FBCD8

FBCD9

FBCD10

FBCD11

FBCD12

FBCD13

FBCD14

FBCD15

FBCD16

FBCD17

FBCD18

FBCD19

FBCD20

FBCD21

FBCD22

FBCD23

FBCD24

FBCD25

FBCD26

FBCD27

FBCD28

FBCD29

FBCD30

FBCD31

FBCD32

FBCD33

FBCD34

FBCD35

FBCD36

FBCD37

FBCD38

FBCD39

FBCD40

FBCD41

FBCD42

FBCD43

FBCD44

FBCD45

FBCD46

FBCD47

FBCD48

FBCD49

FBCD50

FBCD51

FBCD52

FBCD53

FBCD54

FBCD55

FBCD56

FBCD57

FBCD58

FBCD59

FBCD60

FBCD61

FBCD62

FBCD63

FBCDQM0

FBCDQM1

FBCDQM2

FBCDQM3

FBCDQM4

FBCDQM5

FBCDQM6

FBCDQM7

FBCDQS_WP0

FBCDQS_WP1

FBCDQS_WP2

FBCDQS_WP3

FBCDQS_WP4

FBCDQS_WP5

FBCDQS_WP6

FBCDQS_WP7

FBCDQS_RN0

FBCDQS_RN1

FBCDQS_RN2

FBCDQS_RN3

FBCDQS_RN4

FBCDQS_RN5

FBCDQS_RN6

FBCDQS_RN7

2

U11C

BGA820

COMMON

3/14 FBC

B7

FBCD0

A7

FBCD1

C7

FBCD2

A2

FBCD3

B2

FBCD4

C4

FBCD5

A5

FBCD6

B5

FBCD7

F9

FBCD8

F10

FBCD9

D12

FBCD10

D9

FBCD11

E12

FBCD12

D11

FBCD13

E8

FBCD14

D8

FBCD15

E7

FBCD16

F7

FBCD17

D6

FBCD18

D5

FBCD19

D3

FBCD20

E4

FBCD21

C3

FBCD22

B4

FBCD23

C10

FBCD24

B10

FBCD25

C8

FBCD26

A10

FBCD27

C11

FBCD28

C12

FBCD29

A11

FBCD30

B11

FBCD31

B28

FBCD32

C27

FBCD33

C26

FBCD34

B26

FBCD35

C30

FBCD36

B31

FBCD37

C29

FBCD38

A31

FBCD39

D28

FBCD40

D27

FBCD41

F26

FBCD42

D24

FBCD43

E23

FBCD44

E26

FBCD45

E24

FBCD46

F23

FBCD47

B23

FBCD48

A23

FBCD49

C25

FBCD50

C23

FBCD51

A22

FBCD52

C22

FBCD53

C21

FBCD54

B22

FBCD55

E22

FBCD56

D22

FBCD57

D21

FBCD58

E21

FBCD59

E18

FBCD60

D19

FBCD61

D18

FBCD62

E19

FBCD63

A4

FBCDQM0

E11

FBCDQM1

F5

FBCDQM2

C9

FBCDQM3

C28

FBCDQM4

F24

FBCDQM5

C24

FBCDQM6

E20

FBCDQM7

C5

FBCDQS_WP0

E10

FBCDQS_WP1

E5

FBCDQS_WP2

B8

FBCDQS_WP3

A29

FBCDQS_WP4

D25

FBCDQS_WP5

B25

FBCDQS_WP6

F20

FBCDQS_WP7

C6

FBCDQS_RN0

E9

FBCDQS_RN1

E6

FBCDQS_RN2

A8

FBCDQS_RN3

B29

FBCDQS_RN4

E25

FBCDQS_RN5

A25

FBCDQS_RN6

F21

FBCDQS_RN7

A28

FB_VREF2

2

3

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBC_CMD0

FBC_CMD1

FBC_CMD2

FBC_CMD3

FBC_CMD4

FBC_CMD5

FBC_CMD6

FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD25

FBC_CMD26

FBC_CLK0

FBC_CLK0

FBC_CLK1

FBC_CLK1

FBC_DEBUG

FBC_REFCLK

FBC_REFCLK

FBC_PLLVDD

FBC_PLLAVDD

FBC_PLLGND

FBCAL_PD_VDDQ

FBCAL_PU_GND

FBCAL_TERM_GND

3

4

Place near BGA

AA23

AB23

H16

H17

J10

J23

J24

J9

K11

K12

K21

K22

K24

K9

L23

M23

T25

U25

Value TBD

FBVDD

C782

1UF

10V

10%

X7R

0603

COMMON

GND

5

6

NET NET_SPACING_RULE

FBC_REFCLK

IN

FBC_REFCLK*

IN

FBC_PLLVDD

IN

FBC_PLLAVDD

IN

7

DIFFPAIR MIN_LINE_WIDTH

4MIL 10MIL

10MIL

10MIL

8

HGFEDCBA

10MIL

1

2

PLACE NEAR GPU

FBC_CMD[26..0]

FBC_CMD23

FBC_CMD24

FBC_CMD25

NTP_FBC_CMD<26>

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

7.1G< 7.2A<

OUT

7.1G< 7.2A<

OUT

7.1G< 7.2D<

OUT

7.1G< 7.2D<

OUT

FBC_CMD0

C13

FBC_CMD1

A16

FBC_CMD2

A13

FBC_CMD3

B17

FBC_CMD4

B20

FBC_CMD5

A19

FBC_CMD6

B19

NTP_FBC_CMD<7>

B14

FBC_CMD8

E16

FBC_CMD9

A14

FBC_CMD10

C15

FBC_CMD11

B16

FBC_CMD12

F17

FBC_CMD13

C19

FBC_CMD14

D15

FBC_CMD15

C17

FBC_CMD16

A17

FBC_CMD17

C16

FBC_CMD18

D14

FBC_CMD19

F16

FBC_CMD20

C14

FBC_CMD21

C18

FBC_CMD22

E14

B13

E15

F15

A20

FBC_CLK0

E13

FBC_CLK0*

F13

FBC_CLK1

F18

FBC_CLK1*

E17

TP NOW

TP_FBC_DBI0

C20

RFU

TP_FBC_DBI1

D1

RFU

TP_FBC_DEBUG

F12

FBC_REFCLK

B1

FBC_REFCLK*

C1

FBC_PLLVDD

G8

FBC_PLLAVDD

G10

G9

GND

FBCAL_PD

R624

K26

FBCAL_PU

H26

FBCAL_TERM

J26

04021%COMMON

R621

0402

1%

R625

0402 COMMON

5%

49.9

49.9

COMMON

40.2

FBVDD

GND

4

OUT

ASSEMBLY

PAGE DETAIL

7.1A< 7.1G<

PLACE close to GPU

FBVDD

R45

R44

100/X

100/X

1%

1%

0402

0402

COMMON

COMMON

R46

R43

100

100

1%

1%

0402

0402

COMMON

COMMON

GND

C713

C701

.01UF

.1UF

16V

10V

10%

10%

X7R

X5R

0402

0402

COMMON

COMMON

GND