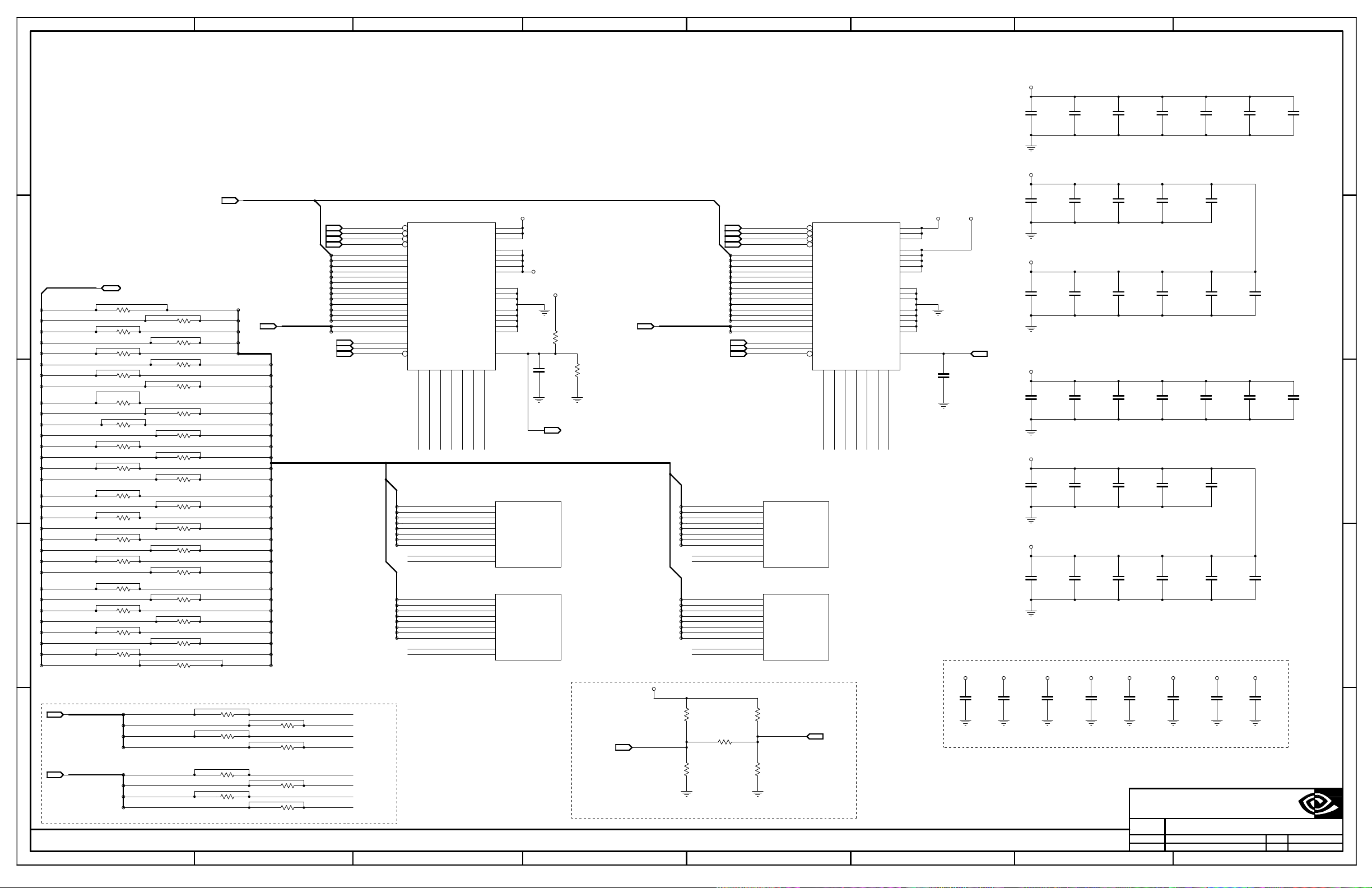

Gigabyte GV-N52128D Schematic REV1.0

5

4

3

2

1

Model Name :

GV-N52128D

Revision 1.0

D D

Component value change history

MODE

1.0A 09/03

Change Item ReasonBOM Rev Date

Initial Version

second source

1.0B 10/23

更正替料重覆位置

1.0B 11/05 Correct Package

1.0B 12/15 Add ne w G a m e C D

1.0B 12/30 Add second source

1.0B 02/03 Add second source

C C

Circuit or PCB layout change for

next version history

PCB Rev

1.0 09/03 Initial Version1.0B 10/09 Change Memory &

Date Change Item Reason

B B

A A

GIGABYTE

Title

BOM & PCB Modify History

Size Document Number Rev

C

5

4

3

2

Date: Sheet

GV-N52128D

1

11Monday, February 02, 2004

1.0

of

5

4

3

2

1

F G H

PAGE

DATE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

DETAIL

ID

NAME

D E

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCBA

P162, NV34, 16Mx16DDR, 64 bit, 128MB, DVI, TV, VGA

Page Overview

1 Overview

2 AGP Interface

3 NV34 Frame Buffer

4 Frame Buffer 0..31

5 Frame Buffer 32..63

6 Frame Buffer 64..95

7 Frame Buffer 96..127

8 DAC A,B, DAC B MUX, PLL, Video OUT

9 DAC A,B RGB filter

10 Power Supply A3V3, FBVDD/FBVDDQ, Mechanicals.

11 BIOS and Strapping

12 DVO,GPIOs and Xtal.

13 TMDS LinkA and its power supplies, Backdrive.

14 NVVDD SW.

15 Current Supplement and Fan control.

16 Net Rules.

P162-A00 History:

1-Added P162 specific features:

- SW PS,TMDS LinkA, Backdrive, new slim VGA, Fan Cntl.

- Added Current sharing, TMDS IO and PLL linear regulators.

2-Added TH parts in PS section as ALT.

3-Added SST serial support.

4-Changed AGP_PLL_VDD, FB_PLLVDD, DAC_A/B_VDD and PLL_VDD to A3V3.

5-Added 10 caps as part of P160 sync up.

6-Added PU resitors on Jtag TMS and TDI

7-Incorporated recommendations from PS Vendor.

8-Added extra X elements near connectors to bridge CGND and GND cut.

9-Added an option to use a single dual FET for low end bd.

10-Fixed error on 6529 power good and current supplement.

11-Changed C302 to 0603 (too big pkg for .1uf in 0805)

12-Deleted C296 and C293 (shared them with C313, C324)

13-Changed C329 and C324 to 0603 pkg.

14-Removed alternate Semtech SW (could not route).

Changes after the design review:

1-Remove C301 and R137-left over from Semtech PS circuit.

2-Remove sync buffer bypass resistors.

3-Remove R122 and R123 from Intersil power rails.

4-Add snubber circuit for NVVDD PS.

5-Add PD res on TP_XTALOUTBUF to terminate the signal.

6-Fan controler PU to 3V3 from A3V3.

7-Cleaned up Unnamed nets.

============================

8-Split CGND into 2 nets (added CGND1 to J6.25 and J2. 16).

9-Added PD resistor on FAN_ON.

10-Added 8 caps for DQS/DQM routings that break plane reference.

P162-A01 History:

Merged net IFPBIOVDD with IFPAIOVDD.

P160 HISTORY:

INITIAL VERSIONX00

X01

X02

X03

X04

X05

X06

X07

X08

Cleaned up schematics - changes from initial design review meeting

Imported board file #65 and synchronized with latest version of schematics.

Nov 18/02 - Replaced LB502 with an 805 bead, changed PLLVDD rail to 3V3

instead of A3V3, and removed AGPVDDQ deoupling caps C130, C257, and C570.

Nov 21/02 - C75 is changed to decouple 3V3 to GND.

Nov 22/02 - VIP interface rail changed to 3V3 instead of A3V3 due to

short between VIPVDDQ and VDD33.

Nov 25/02 - FRWR_VAUXP rail changed to 3V3.

Nov 26/02 - Changed DACB_LOAD_TEST GPIO assignment for NV34.

Dec 02/02 - AGP_PLL_VDD and FB_DLLVDD are supplied from A3V3 rail.

P162-C00 History:

Added PUs on TMDS diff pairs by the GPU and series Rs by the conn.

Merged Q4 and Q5 into one package.

Implemented TV signal return scheme thru zero Ohm resistors.

P162-A02 History:

The main changes for this revision is to improve routing for DAC B and

add 100ps inter-pair skew to pass EMC as modeled on A01 board. See 149- document for detail.

P162-A03 History:

Merged CGND and GND to become GND net to pass EMI at 16x12. This modificaiton was tested on P162-A02

P162-B00 History:

Removed TMDS backdrive prevention circuit.

Changed memory FBVDD(Q) to be regulated from AGP3.3V (was from AGP5V)

Added power sequencing (BUGID 74855)

Isolated 5VCLAMP and I2C PU from AGP5V.

P162-B01 History:

Modified Current Supplement circuit to prevent bacdrive into AGP3V3 from AGP5V. GPIO5 state is

unknown before valid PCICLK.

Isolated IFPA/BIOGND from the main digital GND to improve 16x12 TMDS emission.

Moved Sync buffer VDD and Fuse to 5VCLAMP (was 5V)--BugID:78364.

602-10162-0005-200

DRAWING DETAIL

CONTINUED...

p162

mlao

1 OF 19

SEP 03 2001

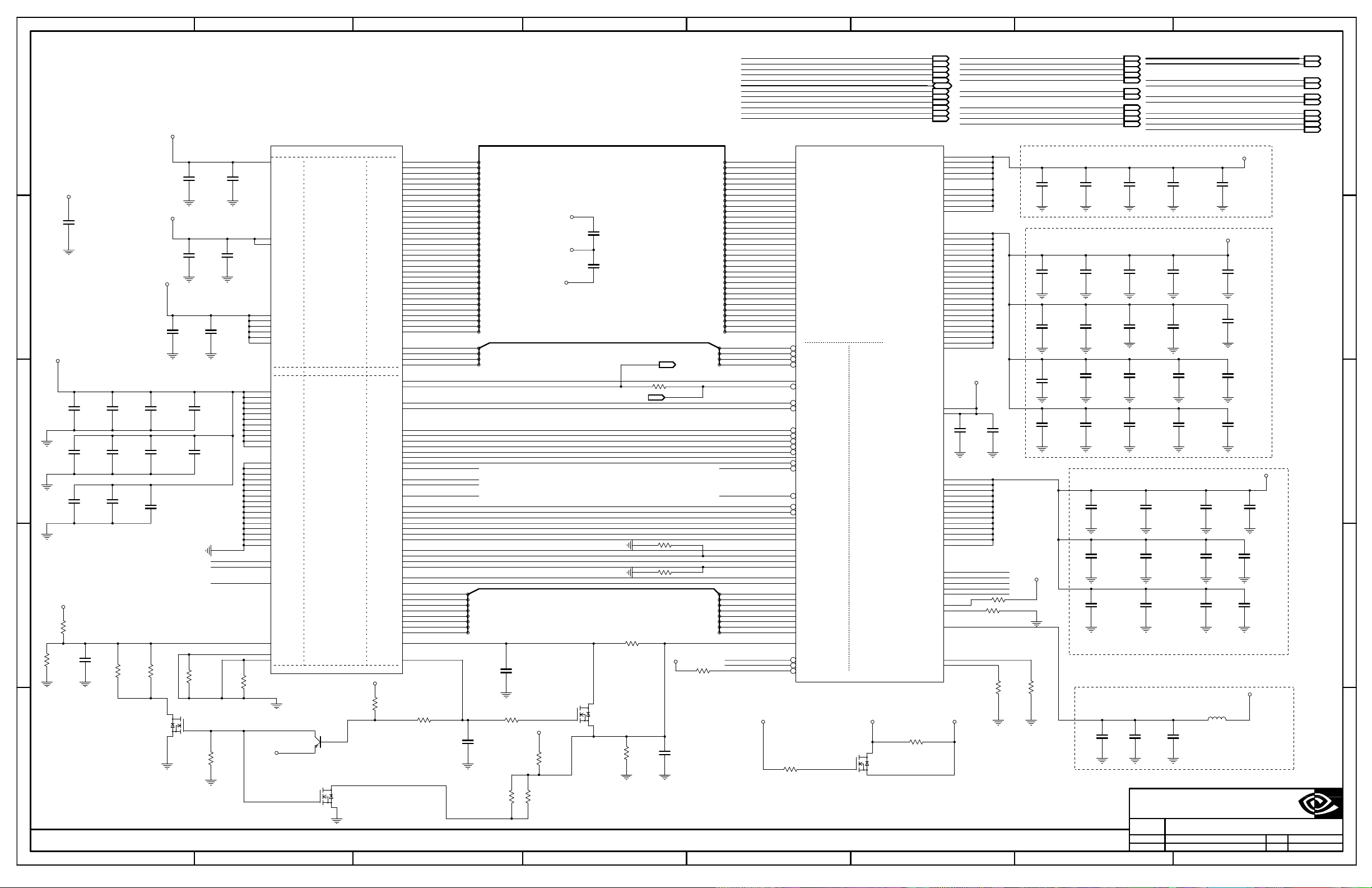

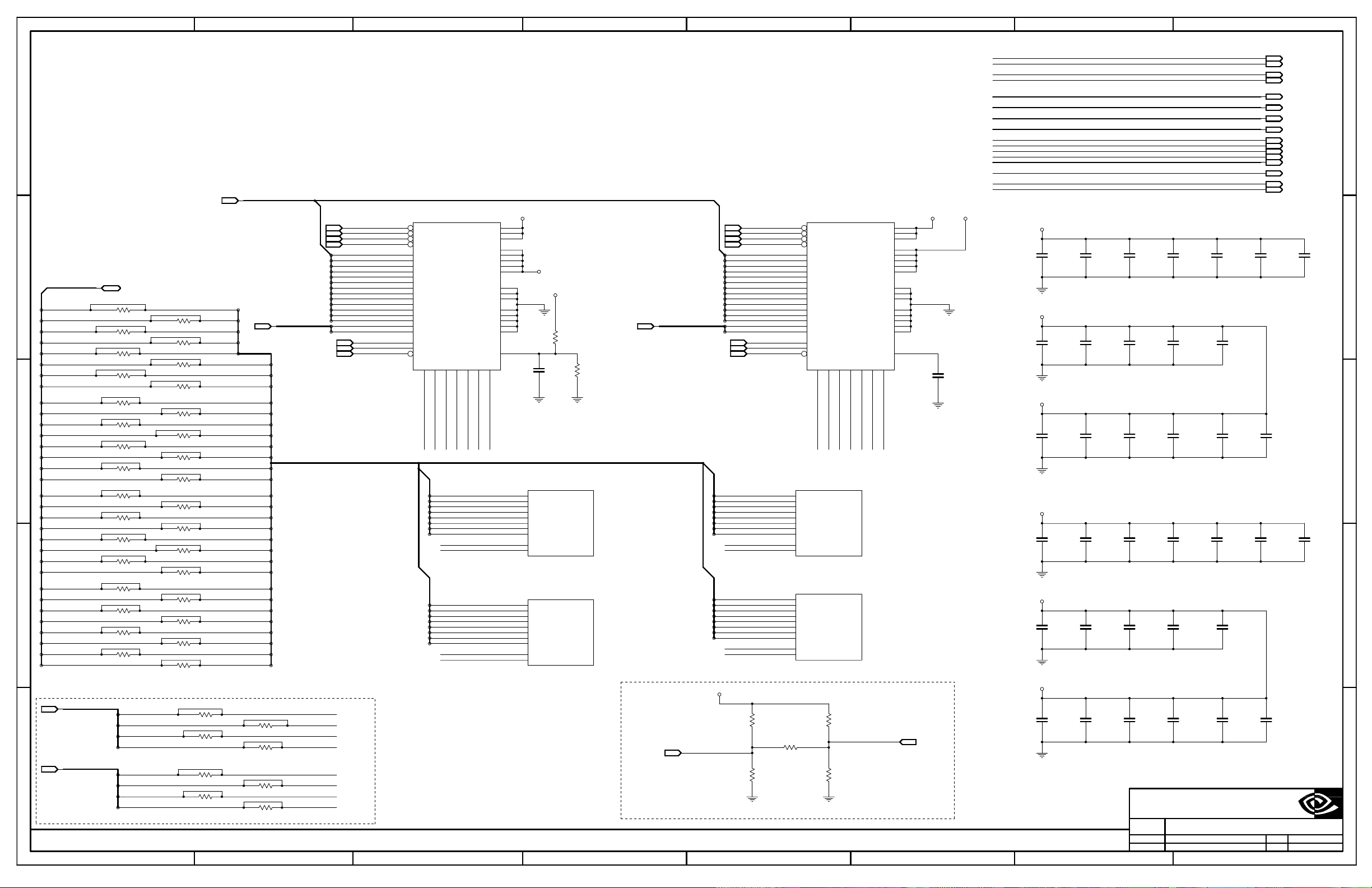

NV18/NV3X AGP SECTION AND AGP CONNECTOR

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIOUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

AGP 8x

[...] = NOT USED ON NV31/34

[..] = NOT USED ON NV18

1/11 PCI/AGP

AGP 2x,4x

AGPVDDQ

AGPVDDQ

AGPVDDQ

AGPVDDQ

AGPVDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AGPVDDQ

AGPVDDQ

AGPVDDQ

AGPVDDQ

AGPVDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VD50CLAMP0

VDD33

VD50CLAMP1

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

NC

NC

NC

NC

NC

..AGP_PLLVDD

VDD33

VDD33

VDD33

VDD33

VDD33

AGPCALPD_VDDQ

AGPCALPU_GND

..TESTMEMCLK

TESTMODE

STOP*

BUSY*

MBDET*

SBA7*

AGPVREF

SBA6*

SBA5*

SBA4*

SBA3*

SBA2*

SBA1*

SBA0*

SBSTBS

SBSTBF

ADSTBS1

ADSTBF1

ADSTBS0

ADSTBF0

DBI_LO

DBI_HI

DEVSEL

FRAME

C3*/BE3

C2*/BE2

C1*/BE1

C0*/BE0

PCIAD<2>

PCIAD<3>

PCIAD<1>

PCIAD<0>

PCIAD<4>

PCIAD<23>

PCIAD<22>

PCIAD<24>

PCIAD<21>

PCIAD<20>

PCIAD<18>

PCIAD<19>

PCIAD<15>

PCIAD<16>

PCIAD<14>

PCIAD<12>

PCIAD<13>

PCIAD<10>

PCIAD<11>

PCIAD<9>

PCIAD<7>

PCIAD<8>

PCIAD<6>

PCIAD<5>

PCIAD<17>

PCIAD<25>

REQ

RST*

CLK

PCIREQ*

PCIRST*

PCICLK

PCIC3/BE3*

PCIC2/BE2*

PCIAD<26>

PCIAD<27>

PCIAD<28>

PCIAD<29>

PCIAD<30>

PCIAD<31>

PCIC0/BE0*

PCIC1/BE1*

PCIGNT* GNT

RBF

WBF

IRDY

TRDY

STOP

INTA

PAR

INTB

AGPRBF*

AGPPIPE*

AGPWBF*

FRWR_PME...

PCIFRAME*

PCIIRDY*

PCIDEVSEL*

PCITRDY*

PCISTOP*

PCIINTA*

PCIPAR

PCIINTB*

ST1

ST0

ST2

AGPSBA<6>

AGPSBA<5>

AGPSBA<4>

AGPSBA<3>

AGPSBA<2>

AGPSBA<1>

AGPSBA<0>

AGPSBSTB*

AGPSBSTB

AGPADSTB1*

AGPADSTB1

AGPADSTB0*

AGPADSTB0

AGPST1

AGPST0

AGPST2

.

AGPSBA<7>

AGPVREF

AGPBUSY*

AGPSTOP*

.

DGD

G

AGP2x4x

AGP2x4x

AGP2x4x

AGP8x

AGP8x

AGP univ

AGP8x

AGP2x4x

AGP2x4x

AGP2x4x

AD<0>

AD<1>

AD<2>

AD<7>

AD<5>

AD<9>

AD<11>

AD<13>

AD<20>

AD<18>

AD<19>

AD<22>

AD<21>

AD<15>

AD<16>

AD<17>

AD<10>

AD<8>

AD<12>

AD<3>

AD<4>

AD<14>

AD<6>

C0/BE0*

AD<31>

AD<30>

AD<29>

AD<28>

AD<25>

AD<23>

AD<24>

AD<27>

AD<26>

CLK

RST*

C3/BE3*

C2/BE2*

C1/BE1*

CLK

RST*

RBF*

PME*

REQ*

FRAME*

PAR

INTA*

DEVSEL*

STOP*

TRDY*

IRDY*

GNT*

INTB*

PERR*

SERR*

RBF

PME

REQ

FRAME

PAR

INTA

DEVSEL

STOP

TRDY

IRDY

GNT

INTB

PERR

SERR

ADSTB1

ADSTB0*

ST2

ST1

ST0

<resvd>

PIPE

WBF*

SBA1

SBA2

SBA3

SBA4

SBA0

SBSTB*

SBSTB

ADSTB1*

ADSTB0

ST2

ST1

ST0

DBILO

DBIHI

WBF

SBA1*

SBA2*

SBA3*

SBA4*

SBA0*

SBSTBS

SBSTBF

SBA5SBA5*

VREFCG

SBA6

<resvd>

SBA7

SBA6*

*MBDET

SBA7*

VREFCG

ADSTBF1

ADSTBS0

C0*/BE0

ADSTBS1

ADSTBF0

C3*/BE3

C2*/BE2

C1*/BE1

+12V

+5V

+5V

+3V3

+3V3

+3V3

+3V3

+3V3

+3V3

+VDDQ

+VDDQ

+VDDQ

+VDDQ

+VDDQ

+VDDQ

+VDDQ

+VDDQ

+VDDQ

GND

GND

GND

GND

+VDDQ

+VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

USB+

USB-

OVRCNT*

VREFGC

TYPEDET*

GCDET*

VREFGC

TYPEDET*

<resvd>

CBDGD

G

5

4

3

2

1

F G H

PAGE

DATE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

DETAIL

ID

NAME

D E

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCBA

12V

TP_P12V

C147

.022UF

25V

10%

X7R

3V3

GND

C75

.022UF

X7R

0402

COMMON

10%25V

3V3

0402

COMMON

GND

5V

C35

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

GND

1G1D1S

1

GND

C129

1UF.047UF.047UF.047UF

10V

10%

X7R

0603

COMMON

C256

.047UF

16V

10%

X7R

0402

COMMON

GND

AGP_VREFGC

R534

0

5%

0402

NO STUFF

GND

C525

.022UF

25V

10%

X7R

0402

COMMON

NTP_USB

NTP_USB*

NTP_OVRCNT

R86

10K

5%

0402

COMMON

C70

4.7UF

6.3V

10%

R85

6.49K

1%

0603

COMMON

COMMON

C105C110

16V

10%

X7R

0402

COMMON

C107

.01UF

16V

10%

X7R

0402

COMMON

C261

.01UF

16V

10%

X7R

0402

COMMON

3

Q2

2

GND

GND

X5R

0805

COMMON

AGPVDDQ

GND

GND

GND

GND

AGPVDDQ

R645

2.32K

1%

0603

COMMON

R547

2.32K

1%

0603

COMMON

C114

16V

10%

X7R

0402

COMMON

C115

.01UF

16V

10%

X7R

0402

COMMON

C259

.01UF

16V

10%

X7R

0402

COMMON

GND

C568

.01UF

16V

10%

X7R

0402

COMMON

16V

10%

X7R

0402

COMMON

C111

.01UF

16V

10%

X7R

0402

COMMON

C260

.01UF

16V

10%

X7R

0402

COMMON

R646

1.21K

1%

0603

COMMON

AGPVREFGCEN

SOT23_1G1D1S

CONTINUOUS_CURRENT=3A

MAX_WATTAGE=0.5W@70C

IRLML2502

MAX_VOLTAGE=20V

R_DS_ON=0.080R

MAX_CURRENT=20A

V_BE_GS=+/-8V

NO STUFF

CN501

CON_AGP

A1

C148

.047UF

16V

10%

X7R

0402

COMMON

GND

B2

B3

C34

.022UF

25V

10%

X7R

0402

COMMON

B9

A9

B16

A16

B28

A28

B34

A34

B40

A40

B47

B52

A52

B58

A58

B64

A64

B5

A5

B13

A13

B19

A19

B31

A31

B37

A37

B49

A49

B55

A55

B61

A61

B4

A4

B1

A66

A2

A3

R253

0

5%

0402

NO STUFF

A3V3

GND

SOT23_1B1C1E

MMBT4403

COMMON

3AGPMBDETEN

Q3

2

1G1D1S

3

MBDETB1

1B1C1E

1

4

Q4

FDC6301N

SOT23_6_DUAL_1G1D1S

COMMON

2

MAX_VOLTAGE=25V

CONTINUOUS_CURRENT=0.22A

R_DS_ON=5R

MAX_CURRENT=0.5A

MAX_WATTAGE=0.7W@125C

V_BE_GS=8V

GND

A3V3

R87

10K

5%

0402

COMMON

R93

0402

A65

B65

A63

B63

A62

B62

A60

B60

B57

A56

B56

A54

B54

A53

B53

A51

A39

B38

A38

B36

A36

B35

A35

B33

A30

B30

A29

B29

A27

B27

A26

B26

A57

B51

B39

A33

B7

A7

B8

A8

A41

B41

A46

B46

A47

A50

A6

B6

B48

B50

A48

B12

A14

A12

B14

B10

A10

B11

B59

A59

B32

A32

B18

A18

B15

A15

B17

A17

B20

A20

B21

A21

B66

A11

5%

PCICBE<0>

PCICBE<1>

PCICBE<2>

PCICBE<3>

NTP_PCIINTB*

NTP_PERR*

NTP_SERR*

NTP_AGP_PME*

SBA<0>

SBA<1>

SBA<2>

SBA<3>

SBA<4>

SBA<5>

SBA<6>

SBA<7>

AGP_VREFCG

AGPMBDET

1K

COMMON

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

1

2

3

0

1

2

3

4

5

6

7

GND

AGPVREFLCL

C243

.022UF

25V

X7R

0402

COMMON

NO STUFF

PLACE NEAR AGP

GND

R94

0402

5%

10%

R104

240K

5%

0402

Split plane decoupling

place top, near AGP connector

AGPVDDQ

NVVDD

C245

.22UF

16V

10%

X7R

0603

COMMON

MBDETG1

1K

COMMON

AGPVDDQ

R551

301K

1%

0603

COMMON

R101

158K

1%

0402

COMMON

For NV18B rev A02 and lower R101= 121K

For NV18B rev A03 and higher and NV31/34r R101= 158K

PCIAD<31..0>

C102

.022UF

25V

10%

X7R

3V3

Split plane decoupling

place bottom, near PCICLK

0402

COMMON

C516

.022UF

25V

10%

X7R

0402

COMMON

PCICBE<3..0>

PCICLK

PCIRST*

PCIREQ*

PCIGNT*

PCIFRAME*

PCIIRDY*

PCITRDY*

PCIDEVSEL*

PCISTOP*

PCIPAR

PCIINTA*

AGPRBF*

AGPWBF*

AGPDBI_HI

AGPDBI_LO

AGPST0

AGPST1

AGPST2

AGPSTB0

AGPSTB0*

AGPSTB1

AGPSTB1*

SBSTB

SBSTB*

SBA<7..0>

R103

0402

15.1D>

GND GND

5%

R163

0603

R517

0402

R524

0402

0

NO STUFF

.05R

5%

5%

0

COMMON

220K

COMMON

220K

COMMON

BPCIRST*

3V3

0402

if easier to connect

1G1D1S

1

6

Q4

FDC6301N

SOT23_6_DUAL_1G1D1S

COMMON

5

GND

R552

221K

1%

0603

COMMON

use A3V3 instead of 3V3

C244

.01UF

16V 10%

X7R

0402

COMMON

GND

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

PCICBE<0>

0

PCICBE<1>

1

PCICBE<2>

2

PCICBE<3>

3

15.1A< 2.1H>

TP_PCIINTB*

TP_AGP_PME*

SBA<0>

0

SBA<1>

1

SBA<2>

2

SBA<3>

3

SBA<4>

4

SBA<5>

5

SBA<6>

6

SBA<7>

7

NV_VREF

TP_AGPBUSY*

10KR525

COMMON5%

PLACE NEAR GPU

NV_VREF

AGP_VREFGC

AGP_VREFCG

AGPSTOP

AGPMBDET

SBA<7..0>

SBSTB

SBSTB*

AGPSTB0

AGPSTB0*

AGPSTB1

AGPSTB1*

AGPMBDET

AGPSTOP

12V

12MIL_TRACE

12MIL_TRACE 10MIL

U8

NV34_DKTP_V_A1

BGA701

COMMONCHG

AJ28

AK28

AH27

AK27

AJ27

AH26

AJ26

AH25

AH23

AJ23

AH22

AJ22

AJ21

AK21

AH20

AJ20

AG26

AE24

AG25

AG24

AF24

AG23

AE22

AF22

AE21

AG20

AG19

AF19

AE19

AF18

AG18

AE18

AJ24

AH19

AF25

AG22

AG12

AF15

AF13

AE15

AK16

AG16

AJ17

AJ16

AH17

AK18

AG15

AE10

AF10

AG14

AG17

AJ18

AJ19

AG13

AE16

AE13

AK24

AJ25

AG21

AF21

AK13

AJ13

AJ11

AH11

AJ12

AH12

AJ14

AH14

AJ15

AH15

AK29

AF16

AF12

AG11

5VCLAMPG

1K

R57

COMMON

0603

5%

1G1D1S

NET_SPACING_TYPEAGP BUS

AGPST0

AGPST1

AGPST2

PCIDEVSEL*

PCIPAR

PCIINTA*

PCIINTB*

AGPRBF*

AGPWBF*

AGPDBI_HI

AGPDBI_LO

15MIL

15MIL

15MIL

10MIL

10MIL

10MIL

10MIL

10MIL

10MIL

20MIL

20MIL

PCICBE<3..0>

PCICLK

PCIRST*

PCIREQ*

PCIGNT*

PCIFRAME*

PCIIRDY*

PCITRDY*

PCISTOP*

20MILPCIAD<31..0>

20MIL

20MIL

10MIL

10MIL

10MIL

10MIL

10MIL

10MIL

10MIL

10MIL12MIL_TRACE

10MIL

10MIL

10MIL

20MIL

25MIL

25MIL

25MIL

25MIL

25MIL

25MIL

AD11

AE11

AD14

AE14

AD17

AE17

AD20

AE20

AD23

AE23

L11

N11

P11

U11

V11

Y11

L13

Y13

L14

Y14

L17

Y17

AA17

L18

Y18

AA18

L20

N20

P20

U20

V20

Y20

N4

AE9

5VCLAMP

C249

.1UF

10V

10%

X7R

0402

COMMON

AGPVDDQ Decoupling

.022UF

25V

10%

X7R

0402

COMMON

NVVDD Decoupling

C520

100PF

16V

10%

X7R

0402

COMMON

C522

100PF

16V

10%

X7R

0402

COMMON

C521

100PF

16V

10%

X7R

0402

COMMON

C163

C569

.1UF

10V

10%

X7R

0402

COMMON

100PF

16V

10%

X7R

0402

COMMON

C502C501

.022UF

25V

10%

X7R

0402

COMMON

C517

470PF

50V

X7R

0402

COMMON

C514

470PF

50V 10%

X7R

0402

COMMON

C511

470PF

50V

X7R

0402

COMMON

C165

470PF

50V

X7R

0402

COMMON

C504

25V

10%

X7R

0402

COMMON

C509

1000PF

16V

10%

X7R

0402

COMMON

C508

1000PF

16V

X7R

0402

COMMON

C510

1000PF

16V

10%

X7R

0402

COMMON

C258

1000PF

16V

10%

X7R

0402

COMMON

C266

.022UF .1UF.022UF

25V

10%

X7R

0402

COMMON

C512

4700PF

16V

10%

20%

X7R

0402

COMMON

C515

4700PF

16V

10%

20%

X7R

0402

COMMON

C518

4700PF

10%

10%

16V

20%

X7R

0402

COMMON

C263

4700PF

16V

20%

X7R

0402

COMMON

NVVDD

AGPVDDQ

C267

10V

X7R

0402

COMMON

C524

1UF

10V

X7R

0603

COMMON

C506

1UF

10V 10%

X7R

0603

COMMON

C513

1UF

10V 10%

X7R

0603

COMMON

C265

1UF

X7R

0603

COMMON

10%

10%

10%10V

A3V3

C37

1UF

10V

X7R

0603

COMMON

C131

1UF

10V

X7R

0603

COMMON

C264

.1UF

10V

X7R

0402

COMMON

3V3

10%

10%

10%

2 OF 19

SEP 03 2001

H6

U6

AC6

H7

U7

AC7

AD12

G14

AD15

AD16

AD19

AD22

P24

A1

AK30

G6

R7

T7

ACALPD

AA13

AA14

ACALPU

AE12

G24

AE5

0R69

NO STUFF

5V

5VCLAMP

0603

3

Q7

IRLML2502

SOT23_1G1D1S

1

COMMON

2

MAX_VOLTAGE=20V

CONTINUOUS_CURRENT=3A

R_DS_ON=0.080R

MAX_CURRENT=20A

MAX_WATTAGE=0.5W@70C

V_BE_GS=+/-8V

.05R

NTP_NC1

NTP_NC2

NTP_NC3

NTP_NC4

NTP_NC5

R92

0402

R91

0402

AGP_PLL_VDD

TESTMEMCLK

TESTMODE

For NV18B A02 and

lower R92 = 56.2

49.9

COMMON

1%

49.9

COMMON

1%

R89

10K

5%

0402

COMMON

AGPVDDQ

R9

10K

5%

0402

COMMON

3V3 Decoupling

C68

.022UF

25V

10%

X7R

0402

COMMON

C67

4700PF

16V

20%

X7R

0402

COMMON

C164

4700PF

16V

20%

X7R

0402

COMMON

AGP_PLL_VDD

C247

C246

4700PF

470PF

16V

50V

20%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C62

.1UF

10V

X7R

COMMON

C61

.022UF

25V

10%

X7R

0402

COMMON

C250

.022UF

25V

10%

X7R

0402

COMMON

10%

C51

1UF

10V

X7R

06030402

COMMON

C52

.1UF

10V

X7R

0402

COMMON

C262

.1UF

10V

X7R

0402

COMMON

10%

10%

10%

NOT USED ON NV18

LB604

BEAD_0603

C248

1UF

10V

10%

X7R

0603

COMMON

NVxx AGP Section and AGP connector

p162

mlao

150-220R@100MHz

COMMON

[...] = USED FOR DDR2 ONLY

[..] = NOT USED ON NV18

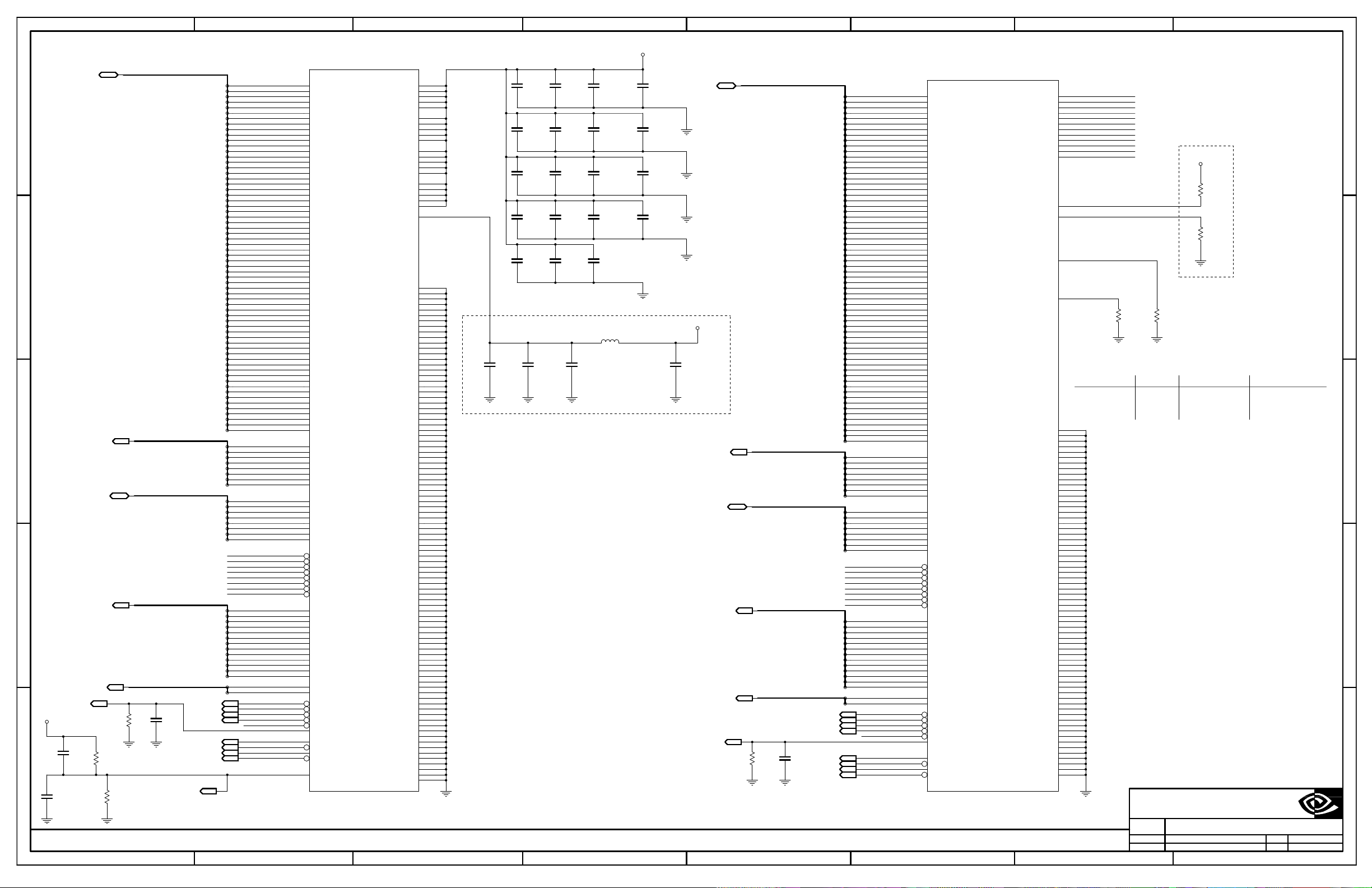

3/11 MEM_C

...VTT

...VTT

...VTT

...VTT

...VTT

...VTT

...VTT

...VTT

...VTT

...VTT

...VTT

...VTT

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

GND_THERMAL

...FBCAL_CLK_GND

...FBCAL_TERM_GND

...FBCAL_PU_GND

...FBCAL_PD_VDDQ

FBCD<0>

FBCD<1>

FBCD<2>

FBCD<3>

FBCD<4>

FBCD<5>

FBCD<6>

FBCD<7>

FBCD<11>

FBCD<10>

FBCD<9>

FBCD<8>

FBCD<12>

FBCD<17>

FBCD<16>

FBCD<13>

FBCD<14>

FBCD<15>

FBCD<19>

FBCD<20>

FBCD<18>

FBCD<21>

FBCD<22>

FBCD<26>

FBCD<27>

FBCD<23>

FBCD<24>

FBCD<25>

FBCD<29>

FBCD<28>

FBCD<32>

FBCD<31>

FBCD<30>

FBCD<35>

FBCD<37>

FBCD<34>

FBCD<33>

FBCD<36>

FBCD<41>

FBCD<38>

FBCD<39>

FBCD<40>

FBCD<42>

FBCD<46>

FBCD<47>

FBCD<44>

FBCD<43>

FBCD<45>

FBCD<48>

FBCD<51>

FBCD<49>

FBCD<52>

FBCD<50>

FBCD<53>

FBCD<58>

FBCD<57>

FBCD<54>

FBCD<55>

FBCD<56>

FBCD<59>

FBCD<60>

FBCD<61>

FBCD<62>

FBCD<63>

FBCDQM<2>

FBCDQM<1>

FBCDQM<0>

FBCDQM<3>

FBCDQM<4>

FBCDQM<7>

FBCDQM<6>

FBCDQM<5>

FBCDQS<0>

FBCDQS<1>

FBCDQS<2>

FBCDQS<5>

FBCDQS<4>

FBCDQS<3>

FBCDQS<6>

FBCDQS<7>

FBCDQS<9>...

FBCDQS<8>...

FBCDQS<10>...

FBCDQS<15>...

FBCDQS<14>,,,

FBCDQS<13>,,,

FBCDQS<12>...

FBCDQS<11>...

FBCA<1>

FBCA<3>

FBCA<4>

FBCA<5>

FBCA<6>

FBCA<0>

FBCA<2>

FBCA<7>

FBCA<8>

FBCA<9>

FBCA<12>..

FBCA<11>

FBCA<10>

FBCCAS

FBCRAS

FBCBA<1>

FBCBA<0>

FBCCS0

FBCWE

FBCCLK0

FBCCLK0

FBCCLK1

FBCCKE

FBCCS1

FBCCLK1

BI

OUTBIOUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIOUT

OUT

OUT

OUT

[...] = USED FOR DDR2 ONLY

[..] = NOT USED ON NV18

2/11 MEM_A

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

GND

GND

GND

GND

GND

GND

..FB_DLLVDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

FBADQS<1>...

FBADQS<2>...

FBADQS<3>...

FBADQS<6>...

FBADQS<4>...

FBADQS<5>...

FBADQS<7>...

FBADQS<0>...

FBAD<1>

FBAD<0>

FBAD<3>

FBAD<6>

FBAD<7>

FBAD<9>

FBAD<8>

FBAD<10>

FBAD<11>

FBAD<4>

FBAD<5>

FBAD<2>

FBAD<12>

FBAD<13>

FBAD<15>

FBAD<14>

FBAD<17>

FBAD<16>

FBAD<18>

FBAD<19>

FBAD<20>

FBAD<21>

FBAD<22>

FBAD<27>

FBAD<26>

FBAD<28>

FBAD<30>

FBAD<29>

FBAD<31>

FBAD<24>

FBAD<25>

FBAD<23>

FBAD<32>

FBAD<33>

FBAD<34>

FBAD<35>

FBAD<36>

FBAD<37>

FBAD<38>

FBAD<40>

FBAD<39>

FBAD<41>

FBAD<42>

FBAD<44>

FBAD<45>

FBAD<48>

FBAD<50>

FBAD<51>

FBAD<49>

FBAD<52>

FBAD<43>

FBAD<46>

FBAD<47>

FBAD<53>

FBAD<54>

FBAD<56>

FBAD<55>

FBAD<57>

FBAD<58>

FBAD<61>

FBAD<59>

FBAD<60>

FBAD<62>

FBAD<63>

FBADQM<0>

FBADQM<1>

FBADQM<2>

FBADQM<3>

FBADQM<4>

FBADQM<5>

FBADQM<6>

FBADQM<7>

FBADQS<0>

FBADQS<3>

FBADQS<2>

FBADQS<1>

FBADQS<4>

FBADQS<5>

FBADQS<7>

FBADQS<6>

FBAA<0>

FBAA<1>

FBAA<3>

FBAA<2>

FBAA<5>

FBAA<4>

FBAA<6>

FBAA<7>

FBAA<8>

FBAA<9>

FBAA<11>

FBAA<10>

FBAA<12>..

FBABA<0>

FBABA<1>

FBARAS

FBACAS

FBACS1

FBACKE

FBACLK0

FBACLK1

FBACLK1

FBACLK0

FBACS0

FBAWE

FB_VREF

OUT

OUT

OUT

OUT

OUTBIOUT

OUT

OUT

OUT

5

4

3

2

1

F G H

PAGE

DATE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

DETAIL

ID

NAME

D E

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCBA

4.2A<> 5.1H> 5.2A<>

FBAD<63..0>

5.1H>

FBVDDQ

GND

5.5A< 5.1H>

5.5A< 5.1H>

5.2B< 5.1H>

5.1H>

4.2E<

C252

.1UF

10V

10%

X7R

0402

COMMON

4.5A<

4.5A<

4.2B<

4.2B<

4.2D<

5.2B<

5.2D<

4.2B<

5.2B< 5.2E<

C251

.1UF

R95

10V

1K

10%

1%

X7R

0402

0402

COMMON

COMMON

GND

FBACKE

R96

1K

1%

0402

COMMON

GND

FBADQM<7..0>

FBADQS<7..0>

FBAA<12..0>

FBABA<1..0>

R75

10K

1%

0402

COMMON

5.2E< 5.5F<

GND

5.2B<

5.2E<

5.1H>

4.2E<

C53

4.2B<

.1UF

4.2E<

10V

5.2B<

10%

X7R

0402

NO STUFF

4.5E< 4.2E<

5.2E< 5.2B<

5.2B< 5.1H>

16.3D>

5.2E<

5.1H>

4.2B<

4.2E<

5.2B<

5.2E<

4.2B<

5.1H>

5.1H>

4.2B<

5.1H>

5.5D<

FBAD<0>

0

FBAD<1>

1

FBAD<2>

2

FBAD<3>

3

FBAD<4>

4

FBAD<5>

5

FBAD<6>

6

FBAD<7>

7

FBAD<8>

8

FBAD<9>

9

FBAD<10>

10

FBAD<11>

11

FBAD<12>

12

FBAD<13>

13

FBAD<14>

14

FBAD<15>

15

FBAD<16>

16

FBAD<17>

17

FBAD<18>

18

FBAD<19>

19

FBAD<20>

20

FBAD<21>

21

FBAD<22>

22

FBAD<23>

23

FBAD<24>

24

FBAD<25>

25

FBAD<26>

26

FBAD<27>

27

FBAD<28>

28

FBAD<29>

29

FBAD<30>

30

FBAD<31>

31

FBAD<32>

32

FBAD<33>

33

FBAD<34>

34

FBAD<35>

35

FBAD<36>

36

FBAD<37>

37

FBAD<38>

38

FBAD<39>

39

FBAD<40>

40

FBAD<41>

41

FBAD<42>

42

FBAD<43>

43

FBAD<44>

44

FBAD<45>

45

FBAD<46>

46

FBAD<47>

47

FBAD<48>

48

FBAD<49>

49

FBAD<50>

50

FBAD<51>

51

FBAD<52>

52

FBAD<53>

53

FBAD<54>

54

FBAD<55>

55

FBAD<56>

56

FBAD<57>

57

FBAD<58>

58

FBAD<59>

59

FBAD<60>

60

FBAD<61>

61

FBAD<62>

62

FBAD<63>

63

FBADQM<0>

0

FBADQM<1>

1

FBADQM<2>

2

FBADQM<3>

3

FBADQM<4>

4

FBADQM<5>

5

FBADQM<6>

6

FBADQM<7>

7

FBADQS<0>

0

FBADQS<1>

1

FBADQS<2>

2

FBADQS<3>

3

FBADQS<4>

4

FBADQS<5>

5

FBADQS<6>

6

FBADQS<7>

7

NTP_FBADQS<0>*

NTP_FBADQS<1>*

NTP_FBADQS<2>*

NTP_FBADQS<3>*

NTP_FBADQS<4>*

NTP_FBADQS<5>*

NTP_FBADQS<6>*

NTP_FBADQS<7>*

FBAA<0>

0

FBAA<1>

1

FBAA<2>

2

FBAA<3>

3

FBAA<4>

4

FBAA<5>

5

FBAA<6>

6

FBAA<7>

7

FBAA<8>

8

FBAA<9>

9

FBAA<10>

10

FBAA<11>

11

FBAA<12>

12

FBABA<0>

0

1

FBARAS*

FBACAS*

FBAWE*

FBACS0*

TP_FBACS1

FBACLK0 U21

FBACLK0*

FBACLK1

FBACLK1*

FBVREF

N25

N27

N26

M25

K26

K27

J27

H27

N29

M29

M28

L29

J29

J28

H29

G30

K25

J26

J25

G26

F28

F26

E27

D27

H28

G29

F29

E29

C30

C29

B30

A30

AJ29

AJ30

AH29

AH30

AF29

AE29

AD29

AC28

AG28

AF27

AE26

AE28

AD25

AB25

AB26

AA25

AD30

AC29

AB28

AB29

Y29

W28

W29

V29

AC27

AB27

AA27

AA26

W25

V26

V27

V25

L27

K29

G25

E28

AF28

AD27

AA30

Y27

M27

K30

G27

D30

AG30

AD26

AA29

W27

M26

L28

F27

D29

AG29

AE27

Y28

W26

V30

U28

U29

T28

T29

T27

T30

T26

T25

R27

R25

R30

U24

R26

R29FBABA<1>

P28

P29

R28

U27

P27

N30

V21

N21

P21

C28

U8

NV34_DKTP_V_A1

BGA701

COMMONCHG

F8

G8

F11

G11

F14

F17

F20

G20

F23

G23

H24

L24

Y24

AC24

H25

L25

P25

U25

Y25

AC25

C27

F1

J1

M1

T1

W1

AB1

AE1

C3

G3

K3

N3

AH3

D4

AG4

E5

K5

AA5

AF5

A6

F6

AE6

AK6

C7

J7

AH7

E8

L8

Y8

AF8

A9

AK9

C10

AH10

E11

H11

AC11

AF11

A12

AK12

C13

AH13

E14

AF14

AK15

AH16

E17

AF17

C18

AH18

A19

AK19

E20

H20

AC20

AF20

C21

AH21

A22

AK22

E23

L23

Y23

AF23

C24

AH24

A25

F25

AE25

AK25

H26

L26

P26

U26

Y26

AC26

AF26

AG27

D28

G28

K28

N28

V28

AA28

AD28

AH28

F30

J30

M30

W30

AB30

AE30

FB_DLLVDD

GND

C97

470PF

50V

10%

0402

COMMON

C98

4700PF

16V

20%

X7R

0402

COMMON

C99

4700PF

16V

20%

X7R

0402

COMMON

C100

4700PF

16V

20% 10%

X7R

0402

COMMON

C101

4700PF

16V

20%

X7R

0402

COMMON

C60

1UF

10V

10%

X7R

0603

COMMON

NOT USED ON NV18B

25MIL_TRACE

C103

4700PF

16V

20%

X7RX7R

0402

COMMON

C104

.022UF

25V

10%

X7R

0402

COMMON

C64

.022UF

25V

10%

X7R

0402

COMMON

C106

.022UF

25V

X7R

0402

COMMON

C66

.022UF

25V

10%

X7R

0402

COMMON

C108

1UF

10V

10%

X7R

0603

COMMON

C71

.1UF

10V

X7R

0402

COMMON

C76

.1UF

10V

X7R

0402

COMMON

C112

.1UF

10V

X7R

0402

COMMON

C113

.1UF

10V

X7R

0402

COMMON

C94

1UF

10V

10%

X7R

0603

COMMON

FBVDDQ

C95

.1UF

10%

10%

10%

10%

10V

X7R

0402

COMMON

C116

.1UF

10V

X7R

0402

COMMON

C117

.1UF

10V

X7R

0402

COMMON

C118

.1UF

10V

X7R

0402

COMMON

6.2A<>

7.1H>

10%

7.2A<>

10%

GND

10%

GND

10%

GND

GND

GND

A3V3

LB13

C109

1UF

10V

10%

X7R

0603

COMMON

GNDGNDGND

150-220R@100MHz

COMMONBEAD_0603

7.2D<

7.2E<

GND

7.5A< 7.1H>

7.2B<

7.1H> 6.2E< 6.2B<

7.2B<

C271

4.7UF

6.3V

10%

X5R

0805

NO STUFF

7.5A< 7.1H>

7.1H> 7.1B< 6.1A<

6.5A<

6.5A<

FBCD<63..0>

FBCDQM<7..0>

FBCDQS<7..0>

FBCA<12..0>

7.2E<

7.2E<

7.2E<

FBCCKE

FBCBA<1..0>

7.2B< 7.2E<

7.2B<

7.2B<

7.2B<

R76

10K

1%

0402

COMMON

6.2B< 6.2D< 7.1H>

GND

GND

7.1H>

7.1H>

7.1H>

7.1H>

6.2E<

6.2E<

6.2E<

6.2E<

C91

.1UF

10V

10%

X7R

0402

NO STUFF

6.2B<

6.2B<

6.2B<

6.2B<

6.5D<

6.2B<

6.2E<

7.1H>

7.2E<

7.1H>

7.2B<

7.5F<

FBCD<0>

0

FBCD<1>

1

FBCD<2>

2

FBCD<3>

3

FBCD<4>

4

FBCD<5>

5

FBCD<6>

6

FBCD<7>

7

FBCD<8>

8

FBCD<9>

9

FBCD<10>

10

FBCD<11>

11

FBCD<12>

12

FBCD<13>

13

FBCD<14>

14

FBCD<15>

15

FBCD<16>

16

FBCD<17>

17

FBCD<18>

18

FBCD<19>

19

FBCD<20>

20

FBCD<21>

21

FBCD<22>

22

FBCD<23>

23

FBCD<24>

24

FBCD<25>

25

FBCD<26>

26

FBCD<27>

27

FBCD<28>

28

FBCD<29>

29

FBCD<30>

30

FBCD<31>

31

FBCD<32>

32

FBCD<33>

33

FBCD<34>

34

FBCD<35>

35

FBCD<36>

36

FBCD<37>

37

FBCD<38>

38

FBCD<39>

39

FBCD<40>

40

FBCD<41>

41

FBCD<42>

42

FBCD<43>

43

FBCD<44>

44

FBCD<45>

45

FBCD<46>

46

FBCD<47>

47

FBCD<48>

48

FBCD<49>

49

FBCD<50>

50

FBCD<51>

51

FBCD<52>

52

FBCD<53>

53

FBCD<54>

54

FBCD<55>

55

FBCD<56>

56

FBCD<57>

57

FBCD<58>

58

FBCD<59>

59

FBCD<60>

60

FBCD<61>

61

FBCD<62>

62

FBCD<63>

63

FBCDQM<0>

0

FBCDQM<1>

1

FBCDQM<2>

2

FBCDQM<3>

3

FBCDQM<4>

4

FBCDQM<5>

5

FBCDQM<6>

6

FBCDQM<7>

7

FBCDQS<0>

0

FBCDQS<1>

1

FBCDQS<2>

2

FBCDQS<3>

3

FBCDQS<4>

4

FBCDQS<5>

5

FBCDQS<6>

6

FBCDQS<7>

7

NTP_FBCDQS<0>*

NTP_FBCDQS<1>*

NTP_FBCDQS<2>*

NTP_FBCDQS<3>*

NTP_FBCDQS<4>*

NTP_FBCDQS<5>*

NTP_FBCDQS<6>*

NTP_FBCDQS<7>*

FBCA<0>

0

FBCA<1>

1

FBCA<2>

2

FBCA<3>

3

FBCA<4>

4

FBCA<5>

5

FBCA<6>

6

FBCA<7>

7

FBCA<8>

8

FBCA<9>

9

FBCA<10>

10

FBCA<11>

11

FBCA<12>

12

FBCBA<0>

0

FBCBA<1>

1

FBCRAS*

FBCCAS*

FBCWE*

FBCCS0*

TP_FBCCS1

FBCCLK0

FBCCLK0*

FBCCLK1

FBCCLK1*

U8

NV34_DKTP_V_A1

BGA701

COMMONCHG

NTP_VTT_01

F13

D13

E13

F12

E10

D10

B13

B12

C12

B11

F10

B29

A29

B28

A28

B26

B25

B24

C23

E26

D26

E25

C25

E24

F22

E22

F21

A24

B23

C22

B22

B20

C19

B19

B18

D23

D22

D21

E21

F19

E18

D18

F18

D11

B10

C26

F24

B21

D20

D12

A10

A27

D24

A21

D19

E12

C11

B27

D25

C20

E19

A18

C17

B17

C16

B16

D16

A16

E16

F16

D15

F15

A15

G17

E15

B15

C14

B14

C15

D17

D14

A13

K18

K17

K13

K14

D9

D8

B9

C9

B8

A7

E9

F9

F7

C6

E6

D5

C4

C8

B7

B6

B5

A3

B3

A2

B2

D7

C5

E7

A4

D6

B4

G9

NTP_VTT_02

G12

NTP_VTT_03

G15

NTP_VTT_04

G16

NTP_VTT_05

G19

NTP_VTT_06

G22

NTP_VTT_07

J24

NTP_VTT_08

M24

NTP_VTT_09

R24

NTP_VTT_10

T24

NTP_VTT_11

W24

NTP_VTT_12

AB24

FBCAL_PD_VDDQ

F5

FBCAL_PU_GND

E4

FBCAL_TERM_GND

D3

FBCAL_CLK_GND

E3

PIN DESCRIPTION

FBCAL_TERM_GND

FBCAL_CLK_GND

FBCAL_PU_GND

M12

N12

P12

R12

T12

U12

V12

W12

M13

N13

P13

R13

T13

U13

V13

W13

M14

N14

P14

R14

T14

U14

V14

W14

M15

N15

P15

R15

T15

U15

V15

W15

M16

N16

P16

R16

T16

U16

V16

W16

M17

N17

P17

R17

T17

U17

V17

W17

M18

N18

P18

R18

T18

U18

V18

W18

M19

N19

P19

R19

T19

U19

V19

W19

GND

R40

549

1%

0402

COMMON

NV18B

NOT USED

NOT USED

NOT USED

NOT USED 50 OHM 1% TO FBVDDQ 50 OHM 1% TO FBVDDQFBCAL_PD_VDDQ

GND

R12

0

5%

0402

COMMON

NOT USED ON NV18B

FBVDDQ

R34

49.9

1%

0402

COMMON

R35

49.9

1%

0402

COMMON

GND

TARGET RESISTANCE IS 550 OHM

1.2V / 550 ohm = 2.2 mA

1.2V / 550 ohm = 2.2 mA

NV31

TIE TO GND

550 OHM 1% TO GND

50 OHM 1% TO GND

GND

DRAWING DETAIL

CONTINUED...

p162

mlao

NV34

NOT USED

NOT USED

50 OHM 1% TO GND

3 OF 19

SEP 03 2001

IN

VDD

VDD

VDD

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

NC

Vref

NCNCNC

RAS

CAS

WE

A<3>

A<1>

A<0>

A<4>

A<6>

A<5>

A<2>

CS

A<7>

BA<0>

A<12>

A<11>

AP/A<10>

A<8>

BA<1>

A<9>

CKE

CLK

NCNCNC

CLK

INININININININ

IN

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

IN

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

OUT

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

IN

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

VDD

VDD

VDD

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

NC

Vref

NCNCNC

RAS

CAS

WE

A<3>

A<1>

A<0>

A<4>

A<6>

A<5>

A<2>

CS

A<7>

BA<0>

A<12>

A<11>

AP/A<10>

A<8>

BA<1>

A<9>

CKE

CLK

NCNCNC

CLK

INININININININININBIIN

IN

5

4

3

2

1

F G H

PAGE

DATE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

DETAIL

ID

NAME

D E

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCBA

MEMORY 1st bank 0..31

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

NV31 FB i/f can be configured in two ways:

2x64 bits or 2x32 bits

THIS REQUIRES THAT BOTH PARTITIONS

TO BE CONNECTED TO BE FUNCTIONAL

FBVDD

GND

FBVDDQ

C173

.022UF

25V

10%

X7R

0402

COMMON

C177

4700PF

16V

20%

X7R

0402

COMMON

C229

.022UF

25V

10%

X7R

0402

COMMON

C222

4700PF

16V

20%

X7R

0402

COMMON

C238

.022UF

25V

10%

X7R

0402

COMMON

C242

4700PF

16V

20%

X7R

0402

COMMON

C234

4.7UF

6.3V

10%

X5R

0805

COMMON

0

1

2

3

4

5.2B< 5.2E<

5.2B< 5.2E<

5.2B< 5.2E<

5.2B< 5.2E<

5.2D<

5.1H>

3.5A>

4.2D<

5.2B<

FBAA<12..0>

4.2E< 3.5B>

5.1H>

4.2E< 3.5B>

5.1H>

4.2E<

5.1H>

4.2E<

5.1H>

FBABA<1..0>

5.2B< 5.2E<

4.5D< 4.2E<

5.1H>

4.5E< 4.2E<

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

3.5B>

3.5B>

4.2E< 5.1H>

3.5A>

3.5B>

3.5B>

5.1H>

0

1

2

3

4

5

6

7

8

9

10

11

12

0

1

FBARAS*

FBACAS*

FBAWE*

FBACS0*

FBAA<0>

FBAA<1>

FBAA<2>

FBAA<3>

FBAA<4>

FBAA<5>

FBAA<6>

FBAA<7>

FBAA<8>

FBAA<9>

FBAA<10>

FBAA<11>

FBAA<12>

FBABA<0>

FBABA<1>

FBACKE

FBACLK0

23

22

21

24

29

30

31

32

35

36

37

38

39

40

28

41

42

26

27

44

45

46FBACLK0*

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

U14

16MX16DDR-5

16M66

16M66

COMMONCHG

17

14

NTP_MEM1_NC2

NTP_MEM1_NC1

FBAD<63..0>

FBAD<0>

FBAD<1>

FBAD<2>

FBAD<3>

FBAD<4>

FBAD<5>

FBAD<6>

FBAD<7>

FBADQM<0>

FBADQS<0>

FBAD<8>

FBAD<9>

FBAD<10>

FBAD<11>

FBAD<12>

FBAD<13>

FBAD<14>

FBAD<15>

FBADQM<1>

FBADQS<1>

25

19

NTP_MEM1_NC5

NTP_MEM1_NC4

NTP_MEM1_NC3

1

18

33

3

9

15

55

61

34

48

66

6

12

52

58

64

49

534350

NTP_MEM1_NC7

NTP_MEM1_NC6

U12

16MX16DDR-5

16M66

COMMONCHG

7

8

5

4

2

10

11

13

20

16

U11

16MX16DDR-5

16M66

COMMONCHG

2

4

5

7

8

10

11

13

20

16

FBVDD

VREF_A

FBVDDQ

FBVDDQ

GND

C225

.047UF

16V

10%

X7R

0402

COMMON

5.1H>

R72

1K

1%

0402

COMMON

R74

1K

1%

0402

COMMON

GNDGND

4.2F< 5.1H>

4.2B<

5.2D<

5.2E< 5.2B<

5.2E< 5.2B<

5.2E< 5.2B<

5.2E< 5.2B<

3.5A>

5.2B<

5.2E<

5.1H>

5.1H>

5.1H>

5.1H>

FBABA<1..0>

5.2B<

5.1H>

5.1H>

5.1H> 4.2B<

4.5D< 4.2B<

4.5E< 4.2B<

16

FBAD<16>

17

FBAD<17>

18

FBAD<18>

19

FBAD<19>

20

FBAD<20>

21

FBAD<21>

22

FBAD<22>

23

FBAD<23>

FBADQM<2>

FBADQS<2>

24

FBAD<24>

25

FBAD<25>

26

FBAD<26>

27

FBAD<27>

28

FBAD<28>

29

FBAD<29>

30

FBAD<30>

31

FBAD<31>

FBADQM<3>

FBADQS<3>

0

1

2

3

4

5

6

7

8

9

10

11

12

0

1

FBARAS*

FBACAS*

FBAWE*

FBACS0*

FBAA<0>

FBAA<1>

FBAA<2>

FBAA<3>

FBAA<4>

FBAA<5>

FBAA<6>

FBAA<7>

FBAA<8>

FBAA<9>

FBAA<10>

FBAA<11>

FBAA<12>

FBABA<0>

FBABA<1>

FBACKE

FBACLK0

FBACLK0*

U12

16MX16DDR-5

16M66

COMMONCHG

54

56

57

65

63

62

60

59

47

51

U11

16MX16DDR-5

16M66

COMMONCHG

54

56

57

59

60

62

63

65

47

51

3.5B> 4.2B<

3.5B> 4.2B<

3.5B> 4.2B<

3.5B> 4.2B<

3.5A>

3.5B>

3.5B>

3.4A> 5.2B< 5.1H>

FBAD<63..0>

FBAD<0>

0

FBAD<1>

1

FBAD<2>

2

FBAD<3>

3

FBAD<4>

4

FBAD<5>

5

FBAD<6>

6

FBAD<7>

7

FBAD<8>

8

FBAD<9>

9

FBAD<10>

10

FBAD<11>

11

FBAD<12>

12

FBAD<13>

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

FBAD<14>

FBAD<15>

FBAD<16>

FBAD<17>

FBAD<18>

FBAD<19>

FBAD<20>

FBAD<21>

FBAD<22>

FBAD<23>

FBAD<24>

FBAD<25>

FBAD<26>

FBAD<27>

FBAD<28>

FBAD<29>

FBAD<30>

FBAD<31>

0402X4

0402X4

0402X4

0402X4

0402X4 NO STUFF

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

RP517

RP517

RP516

RP516

RP505

RP505

RP513

RP513

RP514

RP514

RP518

RP518

RP501

RP501

RP4

RP4

2

5%

3

5%

1

5%

3

5%

4

5%

2

5%

4

5%

2

5%

1

5%

3

5%

1

5%

3

5%

4

5%

2

5%

4

5%

2

5%

15

7

NO STUFF

15

6

NO STUFF

15

8

NO STUFF

15

6

NO STUFF

15

5

15

7

NO STUFF

15

5

NO STUFF

15

7

NO STUFF

15

8

NO STUFF

15

6

NO STUFF

15

8

NO STUFF

15

6

NO STUFF

15

5

NO STUFF

15

7

NO STUFF

15

5

NO STUFF

15

7

NO STUFF

BYTE0

BYTE0

BYTE0

BYTE0

BYTE1

BYTE1

BYTE1

BYTE1

BYTE2

BYTE2

BYTE2

BYTE2

BYTE3

BYTE3

BYTE3

BYTE3

5.2A<> 5.1H> 3.1A<>

RP517

0402X4

RP517

0402X4

RP516

0402X4

RP516

0402X4

RP505

0402X4

RP505

0402X4

RP513

0402X4

RP513

0402X4

RP514

0402X4

RP514

0402X4

RP518

0402X4

RP518

0402X4

RP501

0402X4

RP501

0402X4

RP4

0402X4

RP4

0402X4

1

5%

4

5%

2

5%

4

5%

3

5%

1

5%

3

5%

1

5%

2

5%

4

5%

2

5%

4

5%

3

5%

1

5%

3

5%

1

5%

BYTE0

15

8

NO STUFF

BYTE0

15

5

NO STUFF

BYTE0

15

7

NO STUFF

BYTE0

15

5

NO STUFF

BYTE1

15

6

NO STUFF

BYTE1

15

8

NO STUFF

BYTE1

15

6

NO STUFF

BYTE1

15

8

NO STUFF

BYTE2

15

7

NO STUFF

BYTE2

15

5

NO STUFF

BYTE2

15

7

NO STUFF

BYTE2

15

5

NO STUFF

BYTE3

15

6

NO STUFF

BYTE3

15

8

NO STUFF

BYTE3

15

6

NO STUFF

BYTE3

15

8

NO STUFF

FBVDDQ

100R502

COMMON

GND

R504

120

5%

0402

NO STUFF

FBACLK0*

R671

120

5%

0402

NO STUFF

R501

GND

120

5%

0402

NO STUFF

R670

120

5%

0402

NO STUFF

0603

5%

FBADQM<7..0>

FBADQS<7..0>

0

1

2

3

0

1

2

3

FBADQM<0>

FBADQM<1>

FBADQM<2>

FBADQM<3>

FBADQS<0>

FBADQS<1>

FBADQS<2>

FBADQS<3>

RP515

0402X4

RP515

0402X4

RP515

0402X4

RP515

0402X4

2

5%

3

5%

1

5%

4

5%

15

7

NO STUFF

15

6

NO STUFF

15

8

NO STUFF

15

5

NO STUFF

RP503

0402X4

RP503

0402X4

RP503

0402X4

RP503

0402X4

3

5%

2

5%

4

5%

1

5%

15

6

NO STUFF

15

7

NO STUFF

15

5

NO STUFF

15

8

NO STUFF

3.5B>

4.2B<

4.2E<

5.1H>

Place the differential termination resistor at the end of the transmission line.

FBACLK0

23

22

21

24

29

30

31

32

35

36

37

38

39

40

28

41

42

26

27

44

45

46

U13

16MX16DDR-5

16M66

16M66

COMMONCHG

14

17

NTP_MEM1_NC8

NTP_MEM1_NC9

4.2E<

3.5B>

4.2B<

5.1H>

50

431925

NTP_MEM1_NC11

NTP_MEM1_NC12

NTP_MEM1_NC13

NTP_MEM1_NC10

1

18

33

3

9

15

55

61

34

48

66

6

12

52

58

64

49

53

NTP_MEM1_NC14

C181

220PF

25V

5%

NPO

FBVDDQFBVDD

0402

COMMON

GND

FBVDDQ

C204

16V

10%

X7R

0402

GND

COMMON

GND

GND

VREF_A

C218

.047UF

16V

10%

X7R

0402

COMMON

5.1H> 4.3D>

FBVDD

C172

.022UF

25V

X7R

0402

COMMON

GND

FBVDDQ

C208

220PF

25V

5%

NPO

0402

COMMON

GND

FBVDDQ

C186

.047UF

16V

10%

X7R

0402

COMMON

GND

Place plane decoupling caps near DQS-DQM pairs.

C257

.01UF

16V

10%

X7R

0402

COMMON

FBVDDQ

GND

FBVDDQ

GND

C26

.01UF

16V

10%

X7R

0402

COMMON

FBVDDQ

GND

C270

.01UF

16V

10%

X7R

0402

COMMON

C197

220PF

25V

5%

NPO

0402

COMMON

C213

4700PF.047UF

16V

20%

X7R

0402

COMMON

C176

4700PF

16V

X7R

0402

COMMON

C192

220PF

25V

5%

NPO

0402

COMMON

C212

4700PF

16V

20%

X7R

0402

COMMON

FBVDDQ

GND

C217

220PF

25V

5%

NPO

0402

COMMON

C205

16V

20%

X7R

0402

COMMON

C228

.022UF

25V

X7R

0402

COMMON

C216

220PF

25V

5%

NPO

0402

COMMON

C203

4700PF

16V

20%

X7R

0402

COMMON

FBVDDQ

C293

.01UF

16V

10%

X7R

0402

COMMON

GND

C193

220PF

25V

5%

NPO

0402

COMMON

C189

4700PF4700PF

16V

20%

X7R

0402

COMMON

C221

4700PF

16V

X7R

0402

COMMON

C196

220PF

25V

5%

NPO

0402

COMMON

C187

4700PF

16V

20%

X7R

0402

COMMON

FBVDDQ

C296

.01UF

16V

10%

X7R

0402

COMMON

C302

.01UF

16V

10%

X7R

0402

COMMON

GND

MEMORY 64MB 4/8MX16 Bits 0..31

p162

mlao

C237

.022UF

25V

X7R

0402

COMMON

FBVDDQ

GND

C209

220PF

25V

5%

NPO

0402

COMMON

C188

.047UF

16V

10%

X7R

0402

COMMON

C180

220PF

25V

5%

NPO

0402

COMMON

C202

.047UF

16V

10%

X7R

0402

COMMON

C304

.01UF

16V

10%

X7R

0402

COMMON

FBVDDQ

GND

C169

4.7UF

6.3V

10%

X5R

0805

COMMON

C241

4700PF

16V

X7R

0402

COMMON

C168

4.7UF

6.3V

10%

X5R

0805

COMMON

C307

.01UF

16V

10%

X7R

0402

COMMON

C233

4.7UF

6.3V

10%20%10%20%10%20%10%

X5R

0805

COMMON

4 OF 19

SEP 03 2001

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

VDD

VDD

VDD

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

NC

Vref

NCNCNC

RAS

CAS

WE

A<3>

A<1>

A<0>

A<4>

A<6>

A<5>

A<2>

CS

A<7>

BA<0>

A<12>

A<11>

AP/A<10>

A<8>

BA<1>

A<9>

CKE

CLK

NCNCNC

CLK

INININININININ

IN

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

IN

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

IN

DQ<4>

DQ<3>

DQ<2>

DQ<0>

DQ<1>

DQ<5>

DQS

DQM

DQ<6>

DQ<7>

VDD

VDD

VDD

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

NC

Vref

NCNCNC

RAS

CAS

WE

A<3>

A<1>

A<0>

A<4>

A<6>

A<5>

A<2>

CS

A<7>

BA<0>

A<12>

A<11>

AP/A<10>

A<8>

BA<1>

A<9>

CKE

CLK

NCNCNC

CLK

INININININININININBIIN

IN

5

4

3

2

1

F G H

PAGE

DATE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

DETAIL

ID

NAME

D E

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCBA

MEMORY 1st bank 32..63

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

32

33

34

35

36

FBAA<12..0>

5.1H> 5.2E<

5.1H> 5.2E<

5.1H> 5.2E<

5.1H> 5.2E<

5.2E<

RP11

0402X4

RP11

0402X4

RP11

0402X4

RP11

0402X4

4.2E<

4.2E<

4.2E<

4.2E<

5.1H>

5.5D<

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

4

5%

1

5%

3

5%

2

5%

5

8

6

7

4.2B< 3.5B>

4.2B< 3.5B>

4.2B<

4.2B<

FBABA<1..0>

5.2E< 5.1H>

5.2E< 5.1H>

15

NO STUFF

15

NO STUFF

15

NO STUFF

15

NO STUFF

3.5B>

3.5B>

4.2B< 4.2E<

3.5A>

3.5B>

3.5B>

5.5F<

0

1

2

3

4

5

6

7

8

9

10

11

12

0

1

FBARAS*

FBACAS*

FBAWE*

FBACS0*

FBAA<0>

FBAA<1>

FBAA<2>

FBAA<3>

FBAA<4>

FBAA<5>

FBAA<6>

FBAA<7>

FBAA<8>

FBAA<9>

FBAA<10>

FBAA<11>

FBAA<12>

FBABA<0>

FBABA<1>

FBACKE

FBACLK1

FBAD<63..0>

23

22

21

24

29

30

31

32

35

36

37

38

39

40

28

41

42

26

27

44

45

46FBACLK1*

U12

16MX16DDR-5

16M66

16M66

COMMONCHG

17

14

NTP_MEM2_NC2

NTP_MEM2_NC1

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

53

502543

19

NTP_MEM2_NC6

NTP_MEM2_NC7

NTP_MEM2_NC4

NTP_MEM2_NC5

NTP_MEM2_NC3

FBAD<32>

FBAD<33>

FBAD<34>

FBAD<35>

FBAD<36> 8

FBAD<37>

FBAD<38>

FBAD<39>

FBADQM<4>

FBADQS<4>

FBAD<40>

FBAD<41>

FBAD<42>

FBAD<43>

FBAD<44>

FBAD<45>

FBAD<46>

FBAD<47>

FBADQM<5>

FBADQS<5>

1

18

33

3

9

15

55

61

34

48

66

6

12

52

58

64

FBVDD

2

4

5

7

10

11

13

20

16

8

7

5

4

2

10

11

13

20

16

VREF_B49

GND

U14

16MX16DDR-5

16M66

COMMONCHG

U13

16MX16DDR-5

16M66

COMMONCHG

FBVDDQ

GND

FBVDDQ

C54

.047UF

16V

10%

X7R

0402

COMMON

R46

1K

1%

0402

COMMON

GND

4.2D<

R45

1K

1%

0402

COMMON

4.2B<

5.2B<

5.2B< 5.1H>

5.2B< 5.1H>

5.2B< 5.1H>

5.2B< 5.1H>

3.5A>

5.1H>

5.2B<

5.2E<

3.5B> 5.1H>

5.2B<

5.1H>

5.5D<

5.5F<

4.2B< 3.5B>

4.2E<

4.2B< 3.5B>

4.2E<

4.2B<

4.2E<

4.2B<

4.2E<

FBABA<1..0>

5.2B< 5.1H>

5.2B< 5.1H>

FBACLK1

3.5B>

3.5B>

3.5A> 4.2B< 4.2E<

3.5B>

3.5B>

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

FBVDDQ

0

1

2

3

4

5

6

7

8

9

10

11

12

0

1

FBAD<48>

FBAD<49>

FBAD<50>

FBAD<51>

FBAD<52>

FBAD<53>

FBAD<54>

FBAD<55>

FBADQM<6>

FBADQS<6>

FBAD<56>

FBAD<57>

FBAD<58>

FBAD<59>

FBAD<60>

FBAD<61>

FBAD<62>

FBAD<63>

FBADQM<7>

FBADQS<7>

FBARAS*

FBACAS*

FBAWE*

FBACS0*

FBAA<0>

FBAA<1>

FBAA<2>

FBAA<3>

FBAA<4>

FBAA<5>

FBAA<6>

FBAA<7>

FBAA<8>

FBAA<9>

FBAA<10>

FBAA<11>

FBAA<12>

FBABA<0>

FBABA<1>

FBACKE

FBACLK1

R505

120

5%

0402

NO STUFF

R672

120

5%

0402

NO STUFF

GND

R506

0603

2

5%

4

5%

2

5%

4

5%

2

5%

4

5%

2

5%

4

5%

3

5%

1

5%

2

5%

4

5%

2

5%

4

5%

3

5%

4

5%

0402X4

0402X4

0402X4

0402X4

3.4A>

BYTE4

15

7

NO STUFF

BYTE4

15

5

NO STUFF

BYTE4

15

7

NO STUFF

BYTE4

15

5

NO STUFF

BYTE5

15

7

NO STUFF

BYTE5

15

5

NO STUFF

BYTE5

15

7

NO STUFF

BYTE5

15

5

NO STUFF

BYTE6

15

6

NO STUFF

BYTE6

15

8

NO STUFF

BYTE6

15

7

NO STUFF

BYTE6

15

5

NO STUFF

BYTE7

15

7

NO STUFF

BYTE7

15

5

NO STUFF

BYTE7

15

6

NO STUFF

BYTE7

15

5

NO STUFF

RP9

4

5%

RP9

1

5%

RP9

3

5%

2

5%

15

5

NO STUFF

15

8

NO STUFF

15

6

NO STUFF

15RP9

7

NO STUFF

5.1H> 4.2B<

FBAD<63..0>

FBAD<32>

32

FBAD<33>

33

FBAD<34>

34

FBAD<35>

35

FBAD<36>

36

FBAD<37>

37

FBAD<38>

38

FBAD<39>

39

FBAD<40>

40

FBAD<41>

41

FBAD<42>

42

FBAD<43>

43

FBAD<44>

44

FBAD<45>

45

FBAD<46>

46

FBAD<47>

47

FBAD<48>

48

FBAD<49>

49

FBAD<50>

50

FBAD<51>

51

FBAD<52>

52

FBAD<53>

53

FBAD<54>

54

FBAD<55>

55

FBAD<56>

56

FBAD<57>

57

FBAD<58>

58

FBAD<59>

59

FBAD<60>

60

FBAD<61>

61

FBAD<62>

62

FBAD<63>

63

FBADQS<7..0>

FBADQM<7..0>

0402X4

0402X4

0402X4

0402X4

RP504

0402X4 NO STUFF

RP504

0402X4

0402X4

0402X4

RP512

0402X4

RP512

0402X4

0402X4

0402X4

RP510

0402X4

RP510

0402X4

RP502

0402X4

RP502

0402X4

RP1

RP1

RP2

RP2

RP3

RP3

RP5

RP5

1

5%

3

5%

1

5%

3

5%

1

5%

3

5%

1

5%

3

5%

4

5%

2

5%

1

5%

3

5%

1

5%

3

5%

1

5%

2

5%

4

5

6

7

4

5

6

7

BYTE4

15

8

NO STUFF

BYTE4

15

6

NO STUFF

BYTE4

15

8

NO STUFF

BYTE4

15

6

NO STUFF

BYTE5

15

8

BYTE5

15

6

NO STUFF

BYTE5

15

8

NO STUFF

BYTE5

15

6

NO STUFF

BYTE6

15

5

NO STUFF

BYTE6

15

7

NO STUFF

BYTE6

15

8

NO STUFF

BYTE6

15

6

NO STUFF

BYTE7

15

8

NO STUFF

BYTE7

15

6

NO STUFF

BYTE7

15

8

NO STUFF

BYTE7

15

7

NO STUFF

FBADQS<4>

FBADQS<5>

FBADQS<6>

FBADQS<7>

FBADQM<4>

FBADQM<5>

FBADQM<6>

FBADQM<7>

RP1

0402X4

RP1

0402X4

RP2

0402X4

RP2

0402X4

RP504

0402X4

RP504

0402X4

RP3

0402X4

RP3

0402X4

RP512

0402X4

RP512

0402X4

RP5

0402X4

RP5