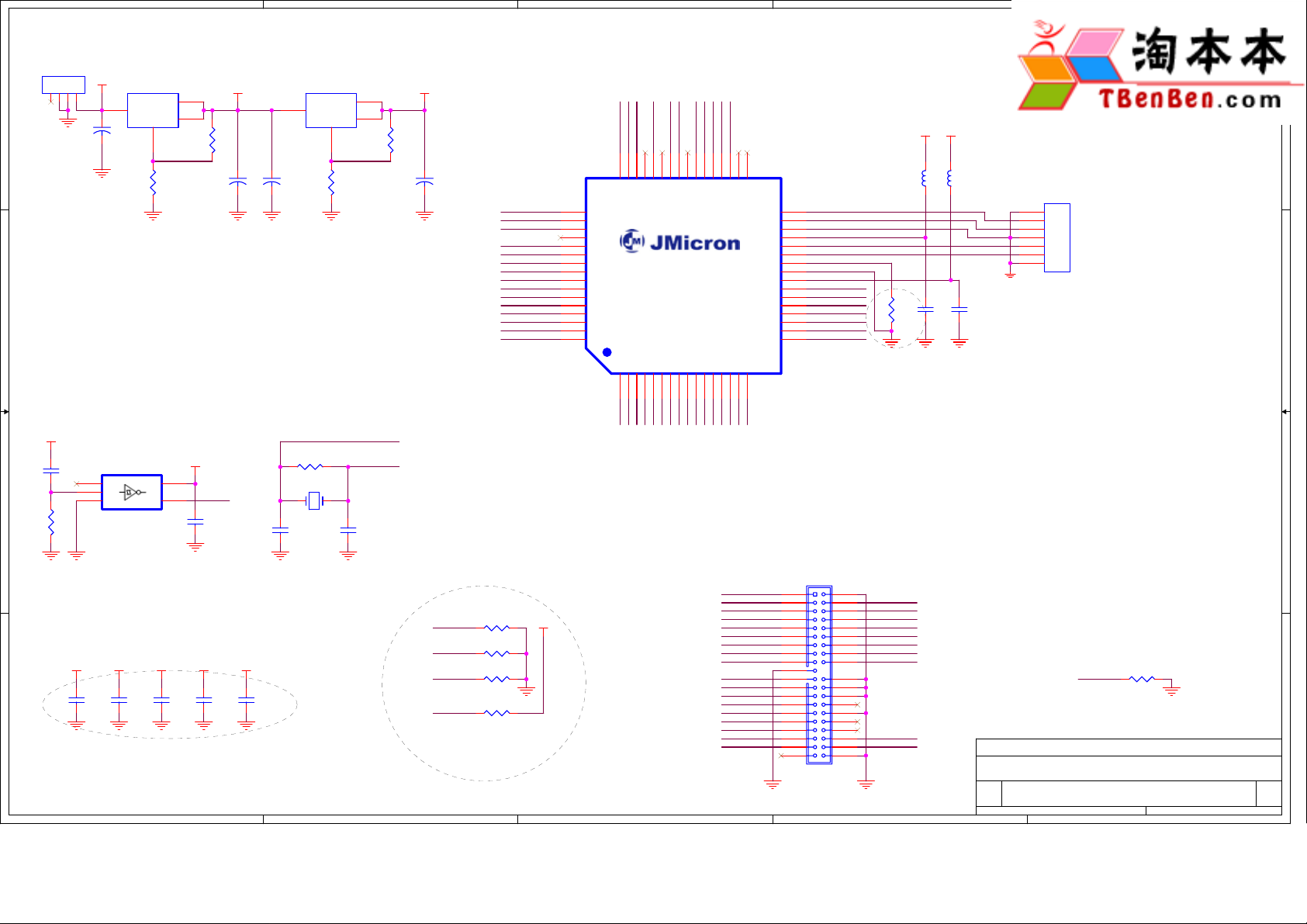

Gigabyte GC-SBP REV.1.0 Schematic

5

J1

CON4/X

D D

C C

D3V3

B B

4

C6

0.1uF/Y/6

R14

10K/6

123

VCC_5V

U1 APL1087

Vout

3

Vin

Vout

GND

C2

1

10uF/10V/8

U4

1

NC

A

GND Y

74LVC1G14

VCC

2

3 4

R3

330/6

5

2

4

10uF/10V/8

D3V3

D3V3

R1

200/6

C1

PORn

C7

0.1uF/Y/6

U3 APL1087

3

Vin

C15

10uF/10V/8

R10 1M/6

X1

Xtal 25MHz

C8

10pF/6

Vout

Vout

GND

1

R6

100/6

2

4

C9

10pF/6

XTALI

XTALO

4

D1V8

R4

220/6

C5

10uF/10V/8

DA2

DA0

DA1

INTRQ

DMACKn

IORDY

D1V8

GND

DIORn

DIOWn

DMARQ

DD15

DD0

DD14

DD1

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

U2

DA2

DA0

DA1

GPIO2

INTRQ

DMACKn

IORDY

VCCK

GNDK

DIORn

DIOWn

DMARQ

DD15

DD0

DD14

DD1

JM20330

3

D3V3

CS1n

CS0n

48

CS0n

CS1n

PATAOR

PATAOR

D1V8

GND

GND

UAI

UAO

GNDK

VCCO

VCCK

GND

GND

GND

D3V3

PMEN

FXDMA

PHYRDY

CLKSEL0

CLKSEL1

JM20330

Device Normal Order

DD13

DD2

DD12

VCCO

DD3

DD11

DD4

GNDO

VCCK

DD10

DD5

DD9

DD6

123456789101112131415

DD12

DD13

DD2

DD4

DD3

DD11

D3V3

DD6

DD5

DD9

DD8

DD10

GND

D1V8

GPIO0

SSCEN

ATAIOEN

DD8

DD7

DD7

RESETn

333435363738394041424344454647

GPIO1

AGND

AVDDL

REXT

AGND

AVDDH

XTALO

XTALI

MODE2

MODE1

MODE0

PORn

RESETn

16

TXP

TXN

RXN

RXP

2

D3V3D1V8

SL1

TXP

32

TXN

31

GND

30

AVDDL

29

RXN

28

RXP

27

REXT

26

GND

25

AVDDH

24

XTALO

23

XTALI

22

D3V3

21

GND

20

D3V3

19

GND

18

PORn

17

R5

12K/6/1

R18 Place

near IC

SL2

S_ATA1

1

GND

2

A+

3

A-

4

GND

5

B-

6

B+

7

GND

SATA/1*7/HOUSING/X

C4

C3

0.1uF/Y/6

0.1uF/Y/6

close to power pins

1

RESETn

DD7

R15 5.6K/6

DMARQ

R16 10K/6

INTRQ

C12

0.1uF/Y/6

D3V3D1V8 D1V8 D1V8

C13

0.1uF/Y/6

SC14

0.1uF/Y/6

DD7

IORDY

R17 10K/6

R19 4.7K/6

D3V3

C11

C10

0.1uF/Y/6

A A

0.1uF/Y/6

D3V3

Bypass CAP, close to power pins

DD6

DD5

DD4

DD3

DD2

DD1

DD0

DMARQ

DIOWn

DIORn

IORDY

DMACKn

INTRQ

DA1

DA0

CS0n

close to IDE Connector

5

4

3

J2

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

11NH2-020220-11

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

(#20 key-pin)

(#28 CSEL)

(#32 IOCS16)

(#34 PDIAGn)

DA2

CS1n

2

R18 10K/6

PATAOR

Gigabyte Technology Corp.

Title

Size Document Number Rev

B

星期一, 八月

Date: Sheet

GC-SBP

JM20330A3 Device Bridge 1.0

16, 2004

11

1

of

Loading...

Loading...