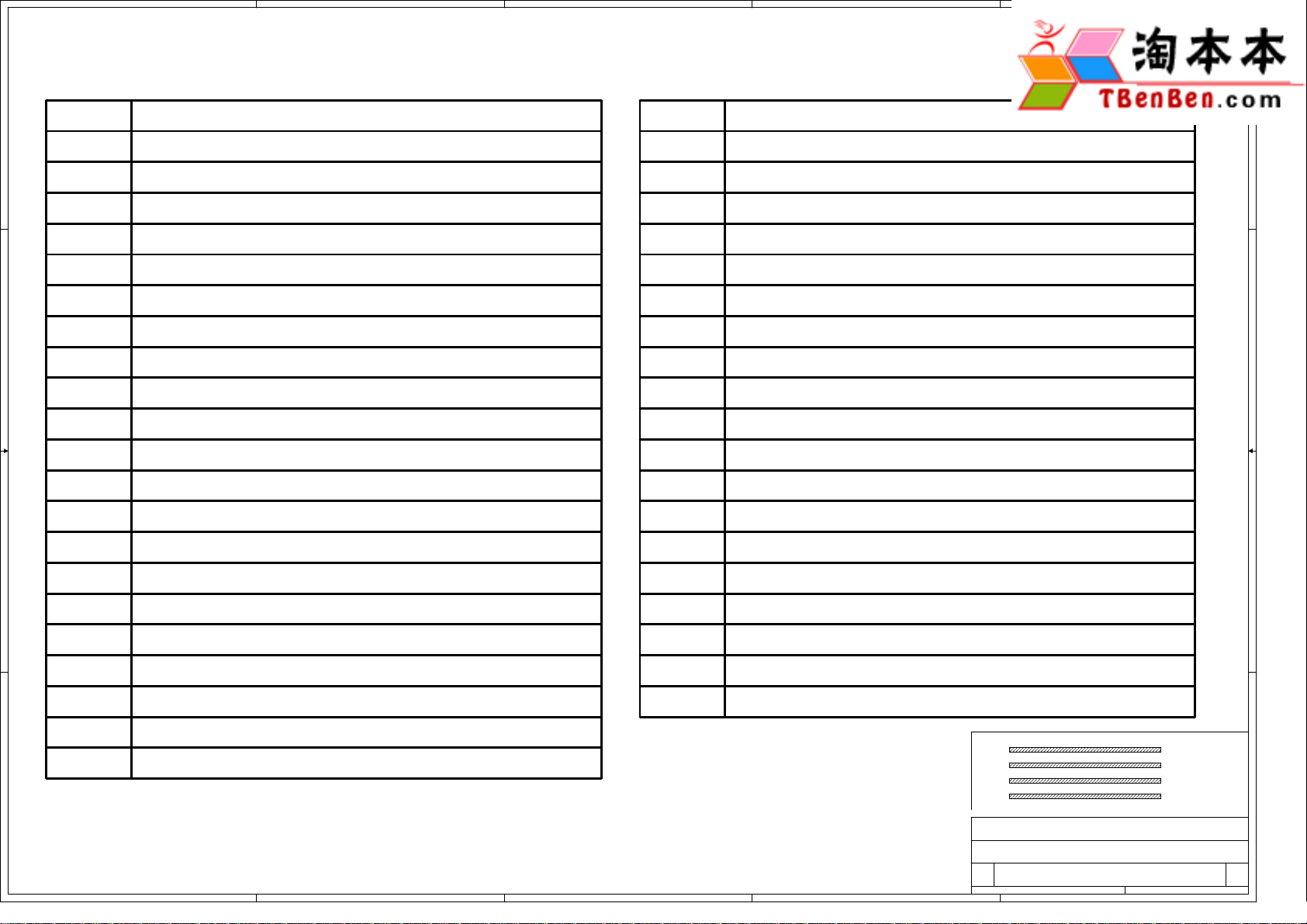

Gigabyte GC-RAMDISK Schematics

5

4

3

2

1

GIGABYTE GC-RAMDISK Schematics

SHEET TITLE

D D

C C

01

02

03

04

05

06

07

08

09

10

11

COVER SHEET

FPGA-V1000 1/2

FPGA-V1000 2/2

JM20330 SATA Bridge

DDR1,2

DDR3,4

DDR TERMINATION

Battery & Charger

POWER

PCI & PCIE Golden Finger

BOM & PCB MODIFY HISTORY

12

13

SHEET TITLE

23

24

25

26

27

28

29

30

31

32

33

34

35

Revision 1.3

14

B B

15

16

36

37

38

17

18

19

20

21

22

A A

5

4

3

2

PROCESS:C

Title

Size Document Number Rev

Custom

Date: Sheet

GIGABYTE CORP.

COVER SHEET

GC-RAMDISK 1.3

1

COMPONENT SIDE

(0.5 oz. Copper)

VCC SIDE

(1 oz. Copper)

GND SIDE

(1 oz. Copper)

SOLDER SIDE

(0.5 oz. Copper)

110

of

5

4

3

2

1

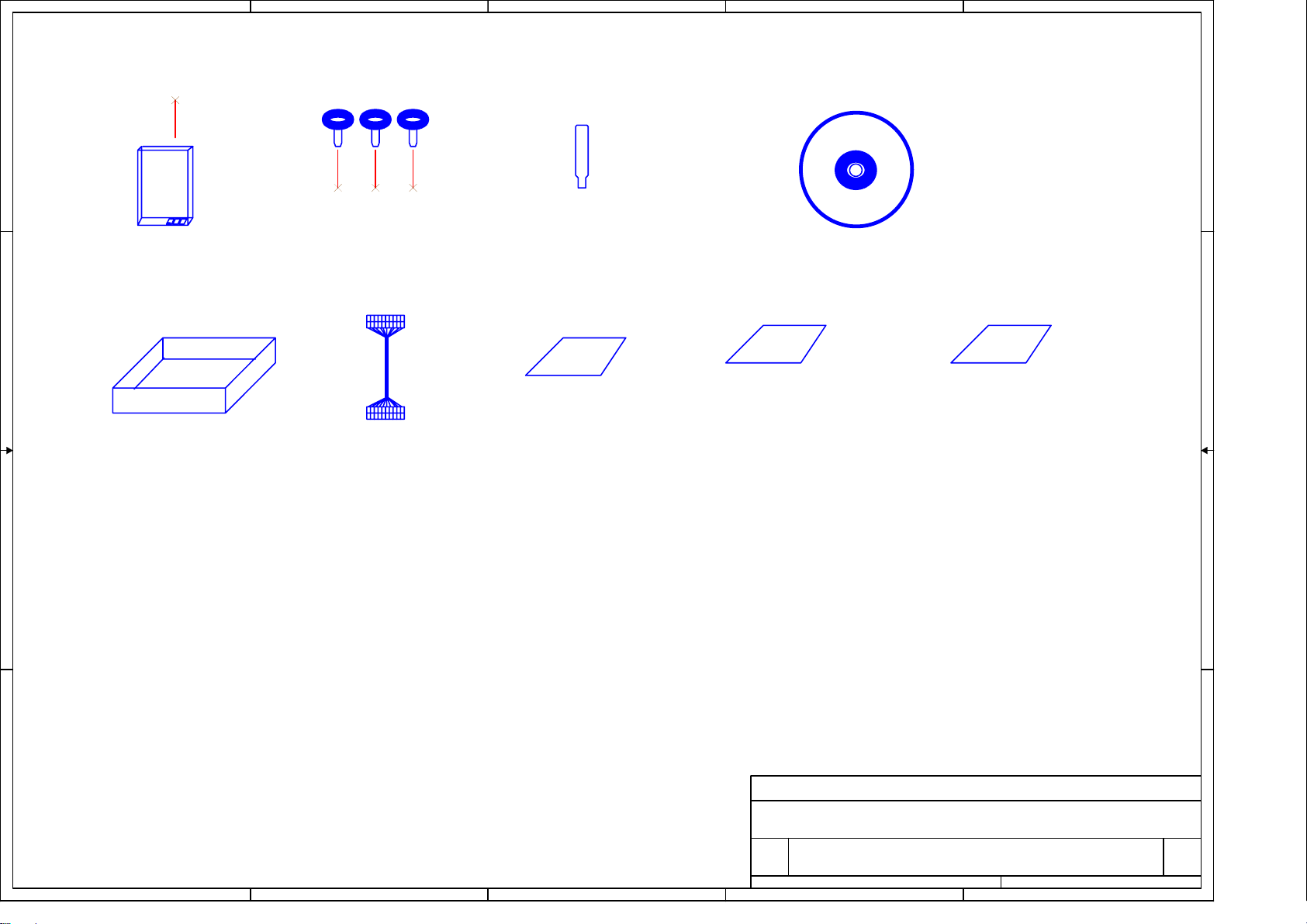

RIVET1

D D

BAT2

1

1

RIVET2

1

1

RIVET3

BRACKET

1

1

1

1

BRACKET

CD1

BRACKET/[12AC1-PCI001-01]

RIVET/[12SRP-010004-01R]

RIVET/[12SRP-010004-01R]

BAT/[11BL4-503010-01]

RIVET/[12SRP-010004-01R]

CD/[12CD1-RAMDISK-00R]

CABLE1

BOX

C C

COLOR BOX/[12BB1-RAMDISK-00R]

SATA/[12CF1-1ID150-81]

ESD BAG

靜電袋

SHIELD BAG/[12B2-004017-00]

MANUAL/[12MD-RAMDISK-102R]

MANUAL

BOX SPR

BOX SPR/[12BB2--RAMDISK-00R]

B B

A A

Title

<Title>

Size Document Number Rev

<Doc> 1.3

A

5

4

3

Date: Sheet

2

11Friday, December 09, 2005

of

1

5

4

3

2

1

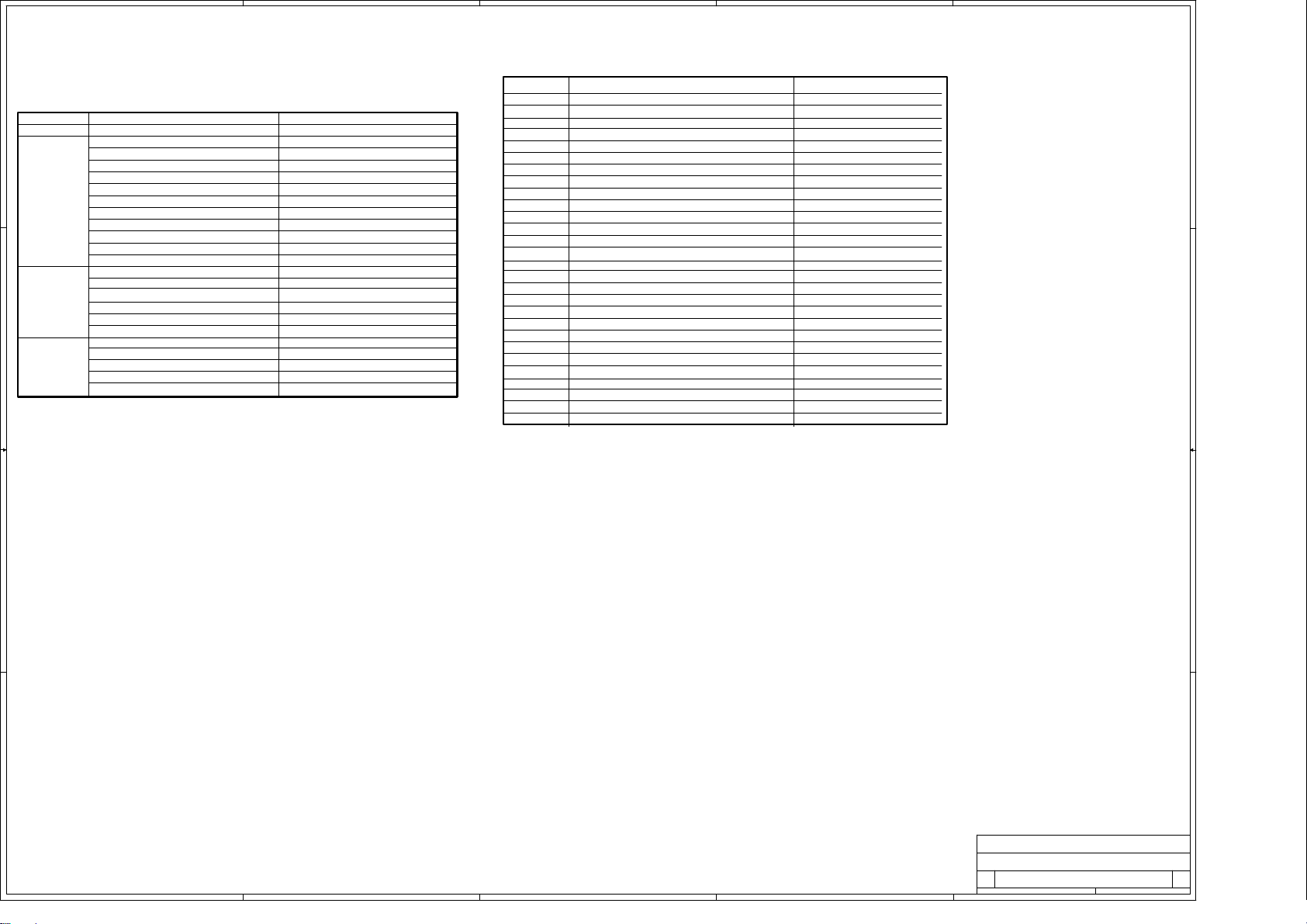

Model Name: GC-RAMDISK

Circuit or PCB layout history

Component history

Date

D D

1.0

Change Item

New RELEASE

1.01

xilinx codr@down pin

修改

修改電池腳座

1.02

修改

RN8 RN14

修改

xilinx codr@down pin

增加電池顯識

1.11

阻值

LED

燈號

Reason

Date

1.0A

Change Item

NEW RELEASE

Reason

C C

B B

A A

1.2

1.21

增加電池顯識

FOR MAC PCI SLOT

LED

燈號

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

GIGABYTE CORP.

BOM & PCB MODIFY HISTORY

GC-RAMDISK 1.3

1

of

11

5

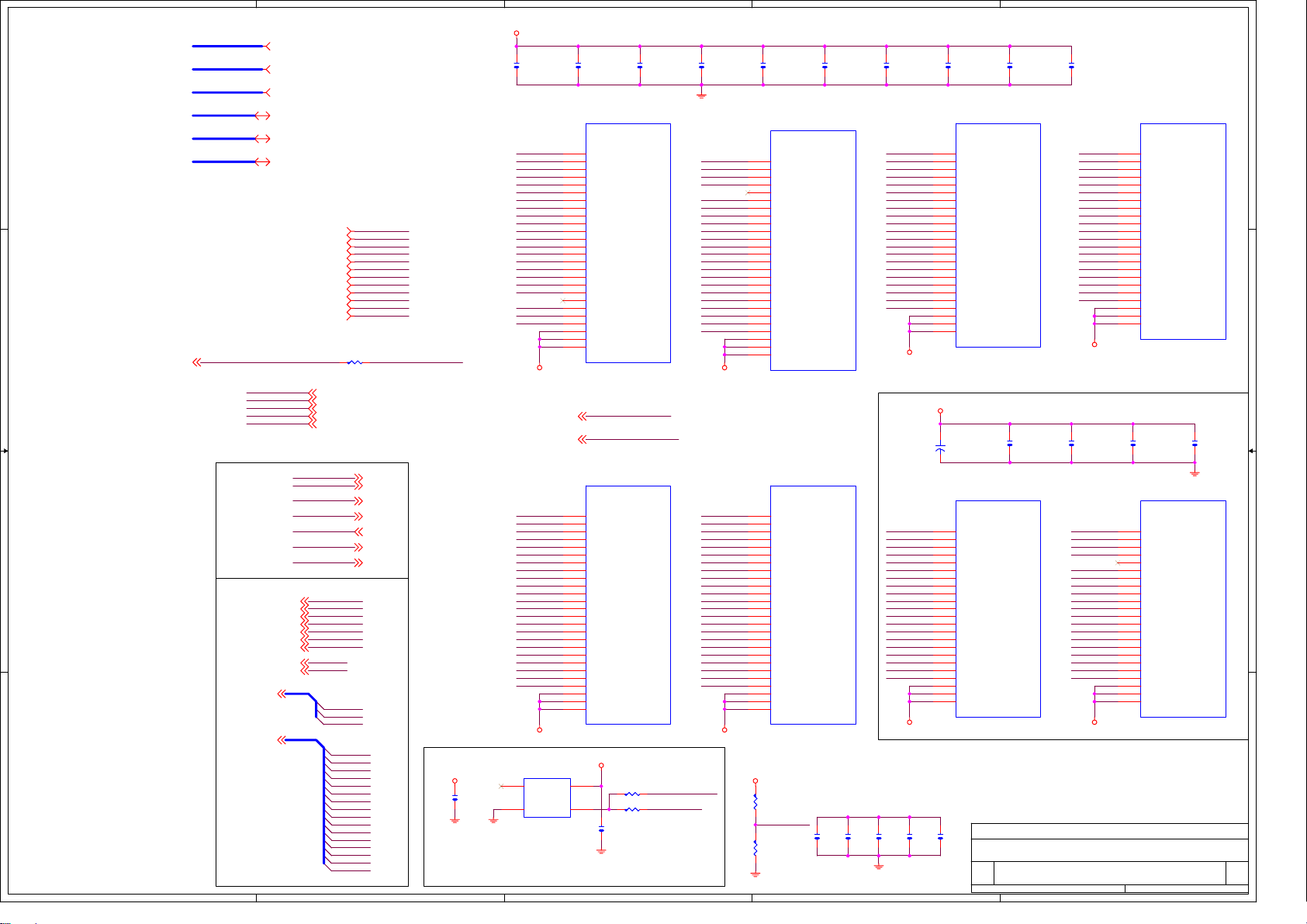

BA[0:1]

-CS[0:7]

CKE[0:7]

DCLKO3

MAA[0..13]

DQS[0..7]

MD[0..63]

To DIMM

module

data

mask pin

To DIMM

module

control

pin

DCLKO

D D

C C

BA[0:1] 5,6,7

-CS[0:7] 5,6,7

CKE[0:7] 5,6,7

MAA[0..13] 5,6,7

DQS[0..7] 7

MD[0..63] 7

Debub0

Debub1

Debub2

Debub3

HD_LED

-CAS05,7

-WE05,7

-RAS05,7

-CAS15,7

-WE15,7

-RAS15,7

-CAS26,7

-WE26,7

-RAS26,7

-CAS36,7

-WE36,7

-RAS36,7

R1 22/6

Debug0 8

Debug1 8

Debug2 8

Debug3 8

HD_LED 8

To DIMM differential clock input

SMBCLK

SMBDATA

SSC_EN

OSC_SATA

XC_DOUT

XC_INIT

B B

RESETn4

DMACKn4

DIOWn4

DIORn4

IORDY4

INTRQ4

DMARQ4

CS0n4

CS1n4

DA[0..2]4

DD[0..15]4

A A

5

-RESET

RESETn

DMACKn

DIOWn

DIORn

IORDY

INTRQ

DMARQ

CS0n

CS1n

DA0

DA1

DA2

SMBCLK 3,5,6,7

SMBDATA 3,5,6,7

SSC_EN 4

OSC_SATA 4

XC_DOUT 3

XC_INIT 3

-RESET

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

4

-CAS0

-CAS1

4

-WE0

-RAS0

-WE1

-RAS1

-CAS2

-WE2

-RAS2

-CAS3

-WE3

-RAS3

F_DCLK0

VCC3

BC16

0.1U/4/Y5V/16V/Z

OSC 25MHz/[10OC3-925000-01;10OC3-125000-01]

3

FPGA25V

BC1

0.1U/4/Y5V/16V/Z

DQS1

MD0

MD3

MD1

MD2

F_DCLK0

SSTL2_REF

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

SSTL2_REF

MD12

MD13

MD14

DQS0

MD15

SSTL2_REF

FPGA25V FPGA25V

POWER_DET10

MD47

MD32

MD33

MD34

MD35

MD46

SSTL2_REF

MD37

MD38

MD39

MD36

MD40

MD41

MD42

MD43

MD44

MD45

SSTL2_REF

DQS4

CKE4

CKE5

DQS5

SSTL2_REF

FPGA25V FPGA25V

X1

1

NC

OSC

2 3

GND OSC

-RESET

VCC

BC2

0.1U/4/Y5V/16V/Z

U1-3

G16

IO

B16

IO_L01N_2/VRP_2

C16

IO_L01P_2/VRN_2

C15

IO_L16N_2

D14

IO_L16P_2

D15

IO_L17N_2

D16

IO_L17P_2/VREF_2

E13

IO_L19N_2

E14

IO_L19P_2

E15

IO_L20N_2

E16

IO_L20P_2

F12

IO_L21N_2

F13

IO_L21P_2

F14

IO_L22N_2

F15

IO_L22P_2

G12

IO_L23N_2/VREF_2

G13

IO_L23P_2

G14

IO_L24N_2

G15

IO_L24P_2

H13

IO_L39N_2

H14

IO_L39P_2

H15

IO_L40N_2

H16

IO_L40P_2/VREF_2

G11

VCCO_2

H11

VCCO_2

H12

VCCO_2

XCS1000/[10HB1-151000-10]

U1-7

K1

IO

R1

IO_L01N_6/VRP_6

P1

IO_L01P_6/VRN_6

P2

IO_L16N_6

N3

IO_L16P_6

N2

IO_L17N_6

N1

IO_L17P_6/VREF_6

M4

IO_L19N_6

M3

IO_L19P_6

M2

IO_L20N_6

M1

IO_L20P_6

L5

IO_L21N_6

L4

IO_L21P_6

L3

IO_L22N_6

L2

IO_L22P_6

K5

IO_L23N_6

K4

IO_L23P_6

K3

IO_L24N_6/VREF_6

K2

IO_L24P_6

J4

IO_L39N_6

J3

IO_L39P_6

J2

IO_L40N_6

J1

IO_L40P_6/VREF_6

J5

VCCO_6

J6

VCCO_6

K6

VCCO_6

XCS1000/[10HB1-151000-10]

VCC3

4

BC3

0.1U/4/Y5V/16V/Z

BANK2

-RESET

POWER_DET

BANK6

R5 33/6

R7 33/6

OSC_SATA

BC17

0.1U/4/Y5V/16V/Z

3

OSC_CLKin

BC4

0.1U/4/Y5V/16V/Z

MD21

MD30

MD31

-RAS3

DQS2

SSTL2_REF

MD26

MD28

MD29

MD27

MD25

MD24

MD23

MD22

MD18

SSTL2_REF

MD20

MD19

MD17

MD16

SSTL2_REF

DQS3

DQS7

MD59

MD63

MD62

SSTL2_REF

MD58

MD60

SSTL2_REF

MD61

MD57

MD56

MD54

MD50

MD51

MD55

MD52

MD53

CKE6

CKE7

MD49

MD48

SSTL2_REF

DQS6

BC5

0.1U/4/Y5V/16V/Z

U1-4

K15

IO

P16

IO_L01N_3/VRP3

R16

IO_L01P_3/VRN3

P15

IO_L16N_3

P14

IO_L16P_3

N16

IO_L17N_3

N15

IO_L17P_3/VREF3

M14

IO_L19N_3

N14

IO_L19P_3

M16

IO_L20N_3

M15

IO_L20P_3

L13

IO_L21N_3

M13

IO_L21P_3

L15

IO_L22N_3

L14

IO_L22P_3

K12

IO_L23N_3

L12

IO_L23P_3/VREF_3

K14

IO_L24N_3

K13

IO_L24P_3

J14

IO_L39N_3

J13

IO_L39P_3

J16

IO_L40N_3/VREF3

K16

IO_L40P_3

J11

VCCO_3

J12

VCCO_3

K11

VCCO_3

XCS1000/[10HB1-151000-10]

U1-8

BANK7

G2

IO

C1

IO_L01N_7/VRP_7

B1

IO_L01P_7/VRN_7

C2

IO_L16N_7

C3

IO_L16P_7/VREF_7

D1

IO_L17N_7

D2

IO_L17P_7

E3

IO_L19N_7/VREF_7

D3

IO_L19P_7

E1

IO_L20N_7

E2

IO_L20P_87

F4

IO_L21N_7

E4

IO_L21P_7

F2

IO_L22N_7

F3

IO_L22P_7

G5

IO_L23N_7

F5

IO_L23P_7

G3

IO_L24N_7

G4

IO_L24P_7

H3

IO_L39N_7

H4

IO_L39P_7

H1

IO_L40N_7/VREF_7

G1

IO_L40P_7

G6

VCCO_7

H5

VCCO_7

H6

VCCO_7

XCS1000/[10HB1-151000-10]

FPGA25V

R6

75/6/1

SSTL2_REF

R8

75/6/1

2

Place each cap near the pin VCCO

BC8

0.1U/4/Y5V/16V/Z

U1-5

BANK4

T12

IO

T14

IO

N12

IO/VREF_4

P13

IO/VREF_4

T10

IO/VREF_4

R13

IO_L01N_4/VRP_4

T13

IO_L01P_4/VRN_4

P12

IO_L25N_4

R12

IO_L25P_4

M11

IO_L27N_4/DIN/D0

N11

IO_L27P_4/D1

P11

IO_L28N_4

R11

IO_L28P_4

M10

IO_L29N_4

N10

IO_L29P_4

P10

IO_L30N_4/D2

R10

IO_L30P_4/D3

N9

IO_L31N_4/INIT_B

P9

IO_L31P_4/DOUT/BUSY

R9

IO_L32N_4/GCLK1

T9

IO_L32P_4/GCLK0

L9

VCCO_4

L10

VCCO_4

M9

VCCO_4

XCS1000/[10HB1-151000-10]

VCC3

1

+

EC2

100U/D/10V/57

U1-1

BANK0

A5

IO

A7

IO

A3

IO/VREF_0

D5

IO/VREF_0

B4

IO_L01N_0/VRP_0

A4

IO_L01P_0/VRN_0

C5

IO_L25N_0

B5

IO_L25P_0

E6

IO_L27N_0

D6

IO_L27P_0

C6

IO_L28N_0

B6

IO_L28P_0

E7

IO_L29N_0

D7

IO_L29P_0

C7

IO_L30N_0

B7

IO_L30P_0

D8

IO_L31N_0

C8

IO_L31P_0/VREF_0

B8

IO_L32N_0/GCLK7

A8

IO_L32P_0/GCLK6

E8

VCCO_0

F7

VCCO_0

F8

VCCO_0

XCS1000/[10HB1-151000-10]

BC9

0.1U/4/Y5V/16V/Z

IDE interface signal

BC12

0.1U/4/Y5V/16V/Z

POWER_DET

BANK3

BC6

0.1U/4/Y5V/16V/Z

BC7

0.1U/4/Y5V/16V/Z

CKE1

CKE0

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

XC_DOUT

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CKE2

XC_INIT

CKE3

BA0

BA1

FPGA25V

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

DIORn

DIOWn

DA0

DA1 DA2

VCC3 VCC3

Place each cap near the pin SSTL2_REF

SSTL2_REF

BC18

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

BC19

BC20

0.1U/4/Y5V/16V/Z

2

BC21

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

BC22

Title

Size Document Number Rev

Custom

Date: Sheet

GIGABYTE CORP.

FPGA PIN

GC-RAMDISK

BC10

0.1U/4/Y5V/16V/Z

-CS0

-CAS1

-CS3

-RAS1

-CS6

-CS7

-CS5

-CS4

-CS2

-CS1

-WE1

-CAS0

-CAS2

-WE2

-RAS2

-CAS3

-WE0

-RAS0

-WE3

MAA13

FPGA25V

BC13

0.1U/4/Y5V/16V/Z

DMACKn

IORDY

A12

INTRQ

C10

DMARQ

D12

A14

CS0n

B14

CS1n

A13

Debug0

B13

Debug1

B12

Debug2

C12

RESETn

D11

SSC_EN

E11

Debug3

B11

SMBCLK

C11

SMBDATA

D10

E10

HD_LED

A10

-RESET

B10

OSC_CLKin

F10

1

U1-6

BANK5

N5

IO

P7

IO

T5

IO

T8

IO/VREF_5

T3

IO_L01N_5/RDWR_B

R3

IO_L01P_5/CS_B

T4

IO_L10N_5/VRP_5

R4

IO_L10P_5/VRN_5

R5

IO_L27N_5/VREF_5

P5

IO_L27P_5

N6

IO_L28N_5/D6

M6

IO_L28P_5/D7

R6

IO_L29N_5

P6

IO_L29P_5/VREF_5

N7

IO_L30N_5

M7

IO_L30P_5

T7

IO_L31N_5/D4

R7

IO_L31P_5/D5

P8

IO_L32N_5/GCLK3

N8

IO_L32P_5/GCLK2

L7

VCCO_5

L8

VCCO_5

M8

VCCO_5

XCS1000/[10HB1-151000-10]

BC14

0.1U/4/Y5V/16V/Z

U1-2

BANK1

A9

IO

IO

IO

IO/VREF_1

IO_L01N_1/VRP_1

IO_L01P_1/VRN_1

IO_L10N_1/VREF_1

IO_L10P_1

IO_L27N_1

IO_L27P_1

IO_L28N_1

IO_L28P_1

IO_L29N_1

IO_L29P_1

IO_L30N_1

IO_L30P_1

IO_L31N_1/VREF_1

IO_L31P_1

C9

IO_L32N_1/GCLK5

D9

IO_L32P_1/GCLK4

E9

VCCO_1

F9

VCCO_1

VCCO_1

XCS1000/[10HB1-151000-10]

210Friday, December 09, 2005

1

BC15

0.1U/4/Y5V/16V/Z

of

1.3

Loading...

Loading...