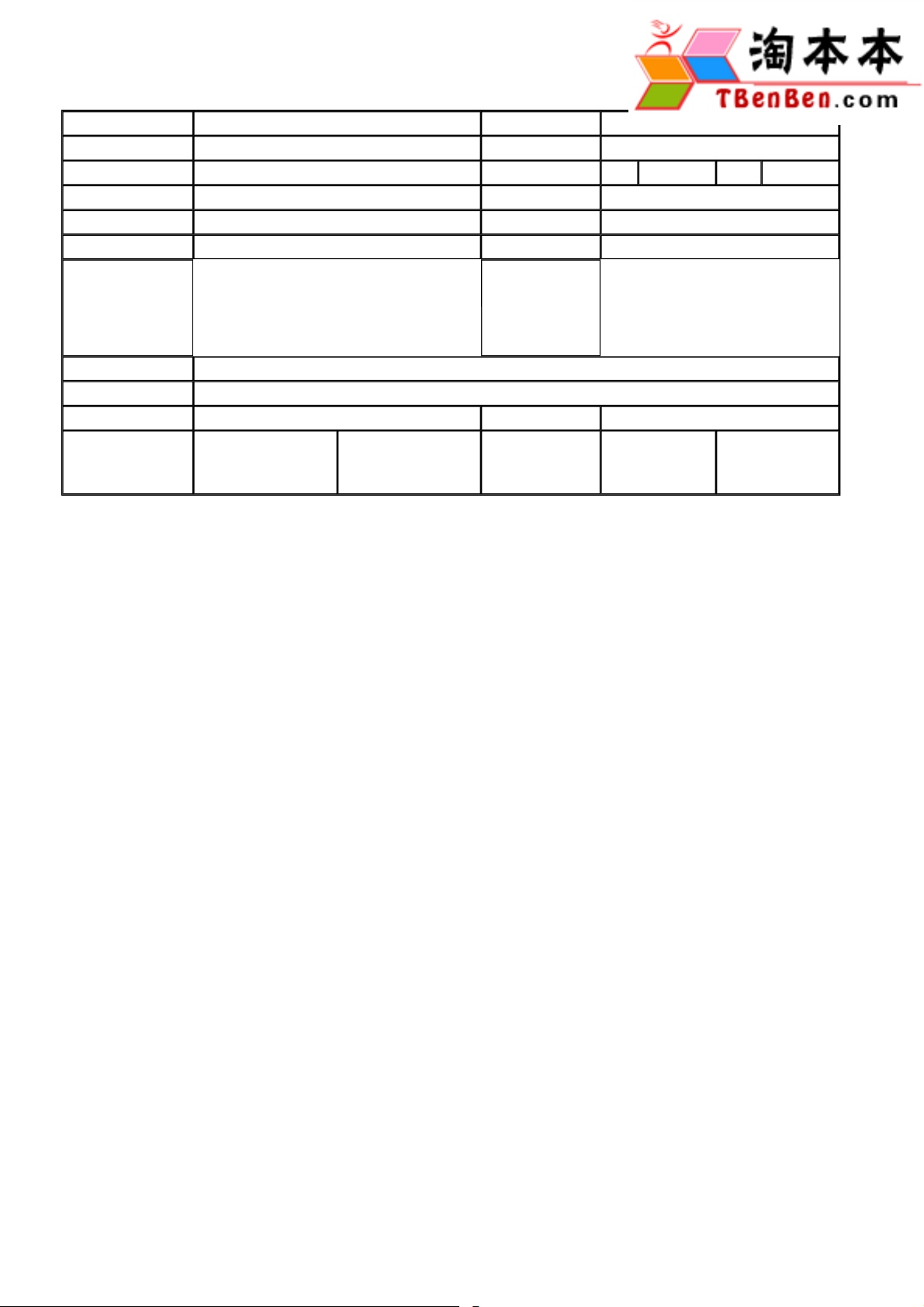

第 1 頁,共 1 頁Technical Information Release Notice

Technical Information Release Notice

Doc Type Schematic Date 2005/8/11 上午 11:25:16

Project Code S94019-0 Customer ACER

Project Name GS-T022 Revision Old N/A New 1.0

Model Name GC-BAT4E IT Doc No DR058119

P/N 9LBAT4E00-AE-* RD Doc No

PCB Rev. 1.0 Check Sum N/A

R N M

SATA 4PORTS B.P.B GC-BAT4E

P/N Description

1.0A FINISHED GOOD ACER

Description GC-BAT4E v_1.0 SATA 4 Ports BPB SAF-TE VSC-420

Remark

Approved By daniel.hou 2005/8/12 下午 04:20:35 Applicant collie.chung

Research

Management

Mimosa.Kao

2005/8/12 下午

04:31:30

Validation Manager 890622(何士弘 ) Project Manager 937029(傅燕祥)

Effected Class

gfedc gfedcb gfedc

A B C D E F

gfedc

gfedcb

A B

gfedc gfedcb

gfedc gfedc

gfedc gfedc

I

I

T

T

R

R

e

e

s

s

e

e

a

a

r

r

c

c

2

2

h

h

0

0

M

M

0

0

5

5

a

a

/

/

n

n

8

8

/

/

a

a

1

1

g

g

2

2

e

e

m

m

e

e

n

n

t

t

FinePrint - www.fineprint.com 用 列印 可在 訂購

2005/8/12http://gwfap/ef2kweb/CHT/Forms/RTC009/RTC009_P.asp

Mimosa.Kao

5

4

3

2

1

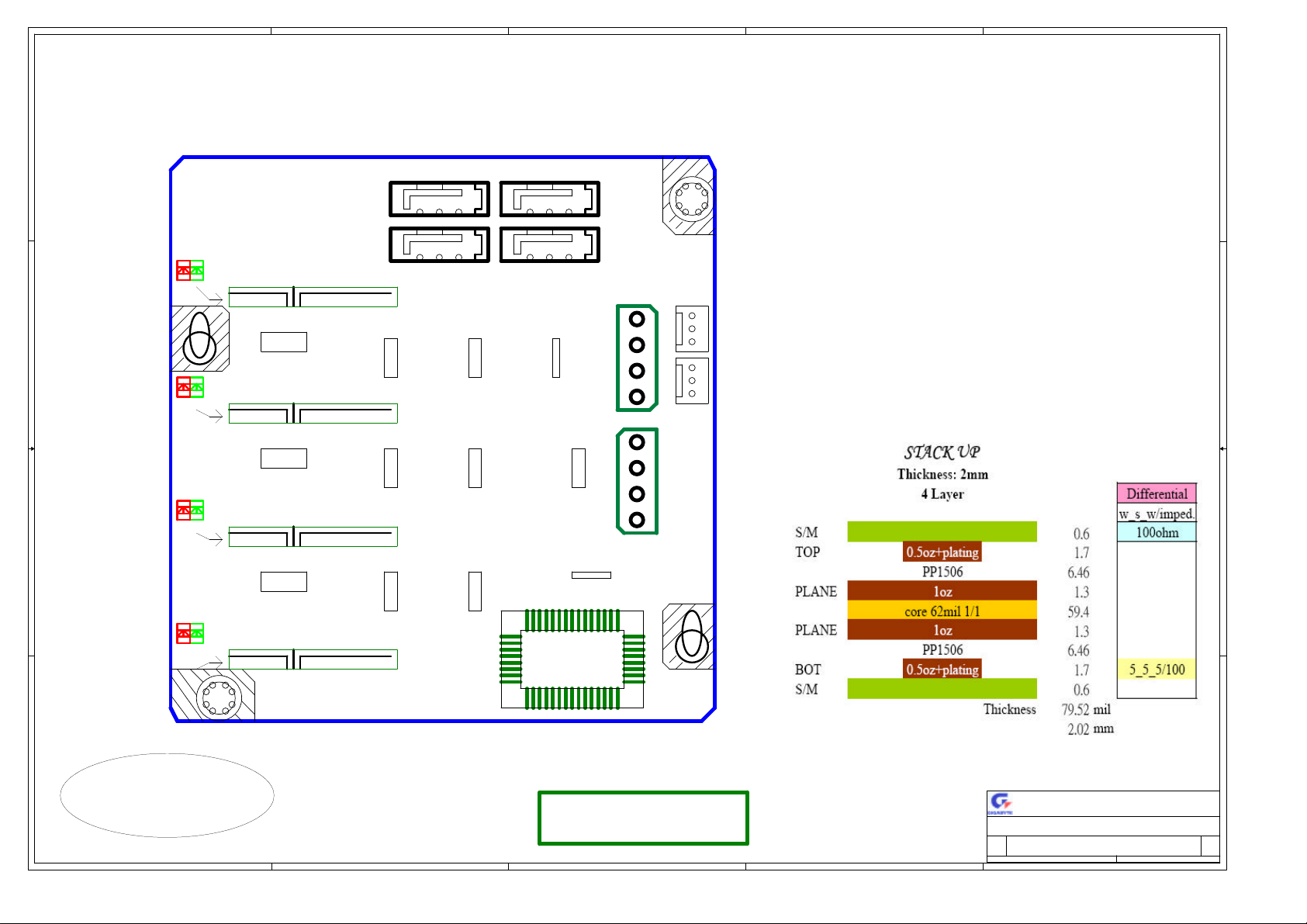

Acer_Sirius_SATA_BPB

Page01: COVER/INDEX

GC-BAT4E

D D

SATA_CON0 SATA_CON2

SATA_CON1

SATA_CON3

SATA0

C C

SATA1

SATA2

B B

Page02: SATA CONNECTOR (0,1,2,3)

Page03: LED&PWR_CONN&GPIO CONN.

Page04: SAF-TE(VSC420)-1

Page05: SAF-TE(VSC420)-2

Page06: HDD POWER LED FOR GBT

Page07: HOT-SWAP POWER CONTROL

Page08: HARDWARE MONITOR(W83792D)

Page09: PWM FAN CONTROL(1,2)

Page10: SATA DIFFERENTIAL COUPON

Page11: 2 PCS BPB COLLOCATION

Page12: REVISION HISTORY

SATA3

VITESS

VSC-420

SAF-TE

A A

Revised Date : 07/18/05'

5

4

Project code : S94019-0

R&D : Collie Chung

PM : Nelson Fu

3

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

2

Date: Sheet of

COVER/INDEX

GC-BAT4E

1

1 12Thursday, August 04, 2005

1.0

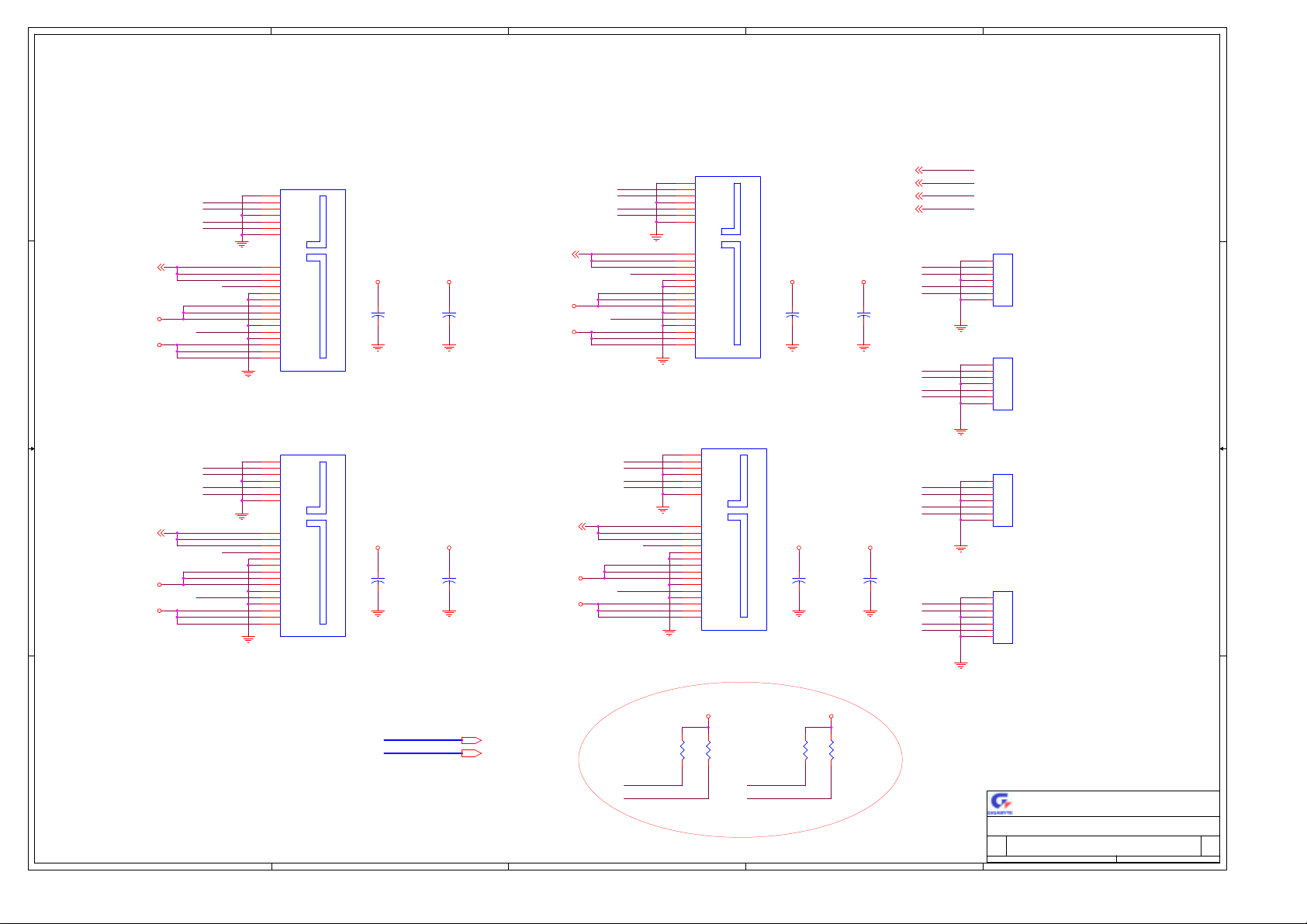

5

D D

4

3

2

1

2

SATA1

MATED4

S1

S2

S3

S4

S5

S6

S7

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

S1

S2

S3

S4

S5

S6

S7

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

GND0

A+

AGND1

BB+

GND2

VCC3_1

VCC3_2

VCC3_3

GND3

GND4

GND5

VCC5_0

VCC5_1

VCC5_2

GND6

RESERVED

GND7

VCC12_0

VCC12_1

VCC12_2

SATA 7+15 Female

SATA3

GND0

A+

AGND1

BB+

GND2

VCC3_1

VCC3_2

VCC3_3

GND3

GND4

GND5

VCC5_0

VCC5_1

VCC5_2

GND6

RESERVED

GND7

VCC12_0

VCC12_1

VCC12_2

SATA 7+15 Female

4

+5VB

12

+

EC3

220U/10V/EC6D10MM

12

+

EC7

220U/10V/EC6D10MM

12

+

EC4

470uF/16V/8X10

12

+

1

SATA0

S1

TXP0

TXN0

RXN0

RXP0

VCC3_A{7}

MATED1

+5VA

C C

B B

+12VA

VCC3_C{7}

+5VC

+12VC

HD_ACCESS1

TXP2

TXN2

RXN2

RXP2

MATED3

HD_ACCESS3

S2

S3

S4

S5

S6

S7

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

SATA2

S1

S2

S3

S4

S5

S6

S7

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

GND0

A+

AGND1

BB+

GND2

VCC3_1

VCC3_2

VCC3_3

GND3

GND4

GND5

VCC5_0

VCC5_1

VCC5_2

GND6

RESERVED

GND7

VCC12_0

VCC12_1

VCC12_2

SATA 7+15 Female

3

GND0

A+

AGND1

BB+

GND2

VCC3_1

VCC3_2

VCC3_3

GND3

GND4

GND5

VCC5_0

VCC5_1

VCC5_2

GND6

RESERVED

GND7

VCC12_0

VCC12_1

VCC12_2

SATA 7+15 Female

VCC3_B{7}

+12VA +12VB+5VA

12

+

EC1

220U/10V/EC6D10MM

+5VC +5VD +12VD

12

+

EC5

220U/10V/EC6D10MM

+12VC

12

+

12

+

EC2

470uF/16V/8X10

EC6

470uF/16V/8X10

+5VB

+12VB

VCC3_D{7}

+5VD

+12VD

TXP1

TXN1

RXN1

RXP1

MATED2

HD_ACCESS2

TXP3

TXN3

RXN3

RXP3

HD_ACCESS4

MATED1{3,6,7}

MATED2{3,6,7}

MATED3{3,6,7}

MATED4{3,6,7}

EC8

470uF/16V/8X10

MATED1

MATED2

MATED3

MATED4

TXP0

TXN0

RXN0

RXP0

TXP1

TXN1

RXN1

RXP1

TXP2

TXN2

RXN2

RXP2

TXP3

TXN3

RXN3

RXP3

SATA_CON0

1

G0

2

A+

3

A-

4

G1

5

B-

6

B+

7

G2

H1X7-SATA2-1

SATA_CON1

1

G0

2

A+

3

A-

4

G1

5

B-

6

B+

7

G2

H1X7-SATA2-1

SATA_CON2

1

G0

2

A+

3

A-

4

G1

5

B-

6

B+

7

G2

H1X7-SATA2-1

SATA_CON3

1

G0

2

A+

3

A-

4

G1

5

B-

6

B+

7

G2

H1X7-SATA2-1

Rev : 1.0

+5V+5V

12

HD_ACCESS[1:4]

A A

5

MATED[1:4]

4

HD_ACCESS[1:4] {3}

MATED[1:4] {3,6,7}

HD_ACCESS1

HD_ACCESS2

3

12

10K/6

R190

R189

10K/6

HD_ACCESS3

HD_ACCESS4

12

10K/6

R192

12

10K/6

R191

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

2

Date: Sheet of

SATA CONNECTOR (0,1,2,3)

GC-BAT4E

1

2 12Thursday, August 11, 2005

1.0

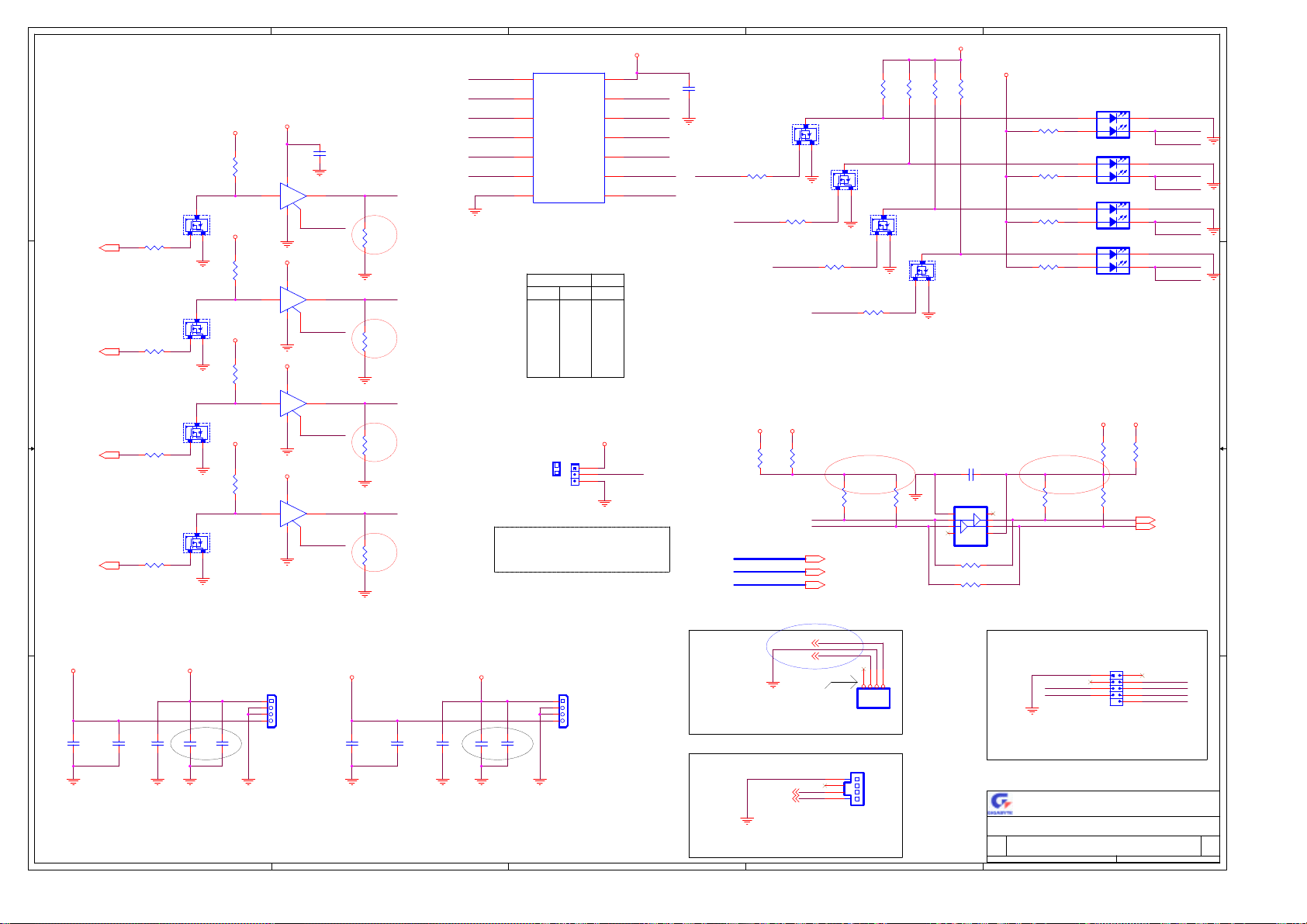

5

R112

4.7K/6

R119

4.7K/6

R125

4.7K/6

R132

4.7K/6

+3V

U16A

2 3

+3V

5 6

+3V

9 8

+3V

12 11

147

74LCX126/TSSOP14

1

74126_CTR

147

U16B

74LCX126/TSSOP14

4

74126_CTR

147

U16C

74LCX126/TSSOP14

10

74126_CTR

147

U16D

74LCX126/TSSOP14

13

74126_CTR

12

C92

0.1U/6

D D

R116

MATED1{2,6,7}

C C

MATED2{2,6,7}

MATED3{2,6,7}

B B

MATED4{2,6,7}

1 2

330/6

R124

1 2

330/6

R129

1 2

330/6

R138

1 2

330/6

+3V

1 2

Q14

D

G

S

+3V

SOT23

SDG

2N7002

1 2

Q17

D

G

S

+3V

SOT23

SDG

2N7002

1 2

Q18

D

G

S

SOT23

SDG

2N7002

1 2

Q19

D

G

S

2N7002

SOT23

SDG

4

HD_ACCESS1

HDD_B1

HDD_Y1

HD_ACCESS2

HDD_Y2

HDD_B1 HDD_Y3

R115

10K/6

1 2

U15

1

1A

2

1B

3

1Y

4

2A

5

2B

6

2Y

7 8

GND 3Y

SN74LV86ADGVR

Input

HDD_B2

A

L

H

R122

10K/6

1 2

HDD_B3

R126

10K/6

1 2

HDD_B4

R137

10K/6

1 2

L

L H

H

H

BLACK

J2

H1X3

JUMPER

JP?*2P/1-2 SHORT

SHORT 1-2 : LINK LED ON

SHORT 2-3 : LINK LED DARK

VCC

Output

1

2

3

4B

4A

4Y

3B

3A

+3V+3V

14

13

12

11

10

9

YB

LL

H

LH

74126_CTR

3

+5V

HD_ACCESS4

HD_ACCESS3

HDD_B4

HDD_Y4

HDD_B3HDD_B2

2

12

GREEN1

1 2

GREEN2

Q13

D

S

SOT23

SDG

2N7002

R123

1 2

330/6

VCC_9515_Y

12

R107

330/6

GREEN3

Q15

D

G

S

SOT23

SDG

2N7002

VCC_9515 need to 20mils

R134

4.7K/6/X

R_SDA

1 2

R_SCL

12

C91

0.1U/6

Q12

D

G

S

SOT23

SDG

R117

1 2

330/6

HDD_Y3

+5V

R131

0/6/X

1 2

2N7002

G

R120

1 2

330/6

HDD_Y4

R133

4.7K/6/X

HD_ACCESS[1:4] {2}

3125_GPIO[0:7] {5}

3125_2GPIO[0:7] {5}

HDD_Y1

R113

1 2

330/6

HDD_Y2

+3V

R130

0/6/X

1 2

HD_ACCESS[1:4]

3125_GPIO[0:7]

3125_2GPIO[0:7]

12

R108

330/6

GREEN4

D

G

S

SDG

2N7002

+3V

3V3_LED

12

R109

R110

330/6

330/6

Q16

SOT23

C93 0.1U/6/X

12

U17

4 5

GND

EN

3

6

2

7

81

VCC

NC

9515/SO8/X

12

R139 0/6

12

R140 0/6

R135

2.2K/6/X

SDA

SCL

1 2

1 2

1 2

1 2

VCC_9515_Z

1 2

GREEN LED

RED LED

D1

R111330/6

LED/GREEN/RED

D2

R114330/6

LED/GREEN/RED

D3

R118330/6

LED/GREEN/RED

D4

R121330/6

LED/GREEN/RED

R127

0/6/X

R136

2.2K/6/X

1

-

G

R

G

R

G

R

G

R

1 2

1 2

R128

0/6/X

3125_GPIO0

3125_2GPIO4

-

3125_GPIO1

3125_2GPIO5

-

3125_GPIO2

3125_2GPIO6

-

3125_GPIO3

3125_2GPIO7

+5V+3V

1 2

SDA {4,8}

SCL {4,8}

12V can supply 14A

5V can supply 7A

+5V

12

12

C94

C95

220u/16v/6x7

A A

220u/16v/6x7

+12V

CN1

1

2

3

PWR_CON1X4

4

12

C127

220u/16v/6x7

5

12

C96

C97

1 2

0.1U/6/16V

Close CN1Close HDD Close HDD

10U/12/X/25V

+5V

12

12

220u/16v/6x7

C99

C98

220u/16v/6x7

4

12

C126

220u/16v/6x7

+12V

CN2

1

2

3

PWR_CON1X4

4

12

C100

C101

1 2

0.1U/6/16V

Close CN1

10U/12/X/25V

3

SMBUS Connect from

LSI Raid card

SMBUS(W83792D)

Connect From Host

v0.4

SDA{4,8}

SCL{4,8}

SDA0

SDA0{4}

SCL0

SCL0{4}

Cut Pin

CDIN/1*4 HEADER[BLACK]

1

2

3

4

4

J3

IPMB_H1X4

J5

2

J4

132

3125_GPIO4

4

5 6

3125_GPIO5

3125_GPIO6

87

3125_GPIO7

10

R_SDA

123

R_SCL

BoxHead2x5/-9/yellow

CONNECT ANOTHER BPB

GIGABYTE TECHNOLOGY CO., LTD.

Title

LED&PWR_CONN&GPIO CONN.

Size Document Number Rev

Date: Sheet of

GC-BAT4E

1

3 12Thursday, August 04, 2005

1.0

5

4

3

2

1

+5V Transfer to +3V with APL1084

Trimmed Current Limit : 5A Typ. at TJ=125 °C

+5V

CLK_OSC

R99

1M/6

1 2

R77 150K/6

1 2

RESET/

1 2

C51

1U/6

140ms power-on RESET delay (minimum)

NOTICE LIBRARY PIN DEFINE

U12

RXD

33

RXD0

TXD

34

TXD0

SIRXD

31

SIRXD

SITXD

32

SITXD

P2.7

P2.6

P2.5

P2.4

P2.3

P2.2

P2.1

P2.0

P3.1

P3.0

R102 0/4

29

RXD1

30

TXD1

69

P0.0

68

P0.1_FT

65

P0.2

64

P0.3

63

P0.4

62

P0.5

61

P0.6

60

P0.7_RTS

17

P1.7

18

P1.6

19

P1.5

20

P1.4

21

P1.3

22

P1.2

23

P1.1

24

P1.0

5

P2.7

6

P2.6

7

P2.5

8

P2.4

9

P2.3

10

P2.2

11

P2.1

12

P2.0

25

P3.1

26

P3.0

2

OSCI

1

OSCO

99

CLKSEL

98

TEST0

97

TEST1

96

TEST2

12

ICMB_RXD{5}

ICMB_TXD{5}

P0_0{5}

420_GPIO0

420_GPIO1

420_GPIO2

420_GPIO3

420_GPIO4

420_GPIO5

420_GPIO6

420_GPIO7

12

VOUT=(R1+R2)/R1*1.250V

+3V

D D

For Debug use

C60

0.1U/6/16V

123

4

JP2

H1X4

C C

(Red LED)

GPIO Pin

Assign

P1.0

P1.2

B B

P1.3

P1.4

P1.5

P1.6

P1.7

High -> Red LED (Off)

Low -> Red LED (ON)

C62

0.1U/6/16V

RS232_RXD

RS232_TXD

RS232_SIRXD

RS232_SITXD

HDD

Status

1 2

1 2

1

3

4

5

13

8

7

HDD

Normal

High

High

High

High

High

High

High

High

U11

C1+

C1C2+

C2R1IN

R2IN

T2OUT

MAX232A

+5V

2

6

15

11

1214

10

9

HDD

Error

(Raid)

Low

LowP1.1

Low

Low

Low

Low

Low

Low

C56

0.1U/6/16V

1 2

C61

0.1U/6/16V

1 2

TXD

RXD

SITXD

SIRXD

High/Low

High/Low

High/Low

High/Low

High/Low

High/Low

High/Low

High/Low

C59

0.1U/6/16V

1 2

HDD

Rebuild

(Raid)

1U/6/X/10V

16

VCC

R1OUTTIOUT

R2OUT

V+

V-

GND

T1IN

T2IN

1

+

EC9

C57

100U/D/16V/6*8

Reserve Layout

0.1U/6/X/25V

C64

0.1U/6/16V

Clock Options:

1) Populate Y1, 40MHz Oscillator, only

OR

2) Populate Y2, 10MHz crystal, with

C8, C12, R2, and R3

R79

100/6/1

C58

420_GPIO[0:7]

SCL2

SDA2

SCL1

SDA1

SCL0

+3V

1

1 2

APL1084/TO252

Q11

O

R81

165/6/1

420_GPIO[0:7] {5}

+5V

1 2

1 2

1 2

1 2

1 2

1 2

MUST BE 3.3V CLOCK

Y1

CLKVDD

OE

GND

40MHz/X

I

A

R10310K/6

R10410K/6

R10510K/6

R10610K/6

R18510K/6

R18610K/6

34

2

High/Low -> Blinking

C52

0.1U/6/X/25V

TP1

v0.3

10MHz/20p/30ppm/H/D

12

Y2

C65

30P/6/N/50V

1 2

+5V

12

C53

4.7U/12/10V

R82 4.7K/4

R83 4.7K/4

R84 4.7K/4

R85 4.7K/4

R86 4.7K/4

R87 4.7K/4

R88 4.7K/4

R89 4.7K/4

R90 4.7K/4

R91 4.7K/4

R92 4.7K/4

R93 4.7K/4

R94 4.7K/4

R95 4.7K/4

R96 4.7K/4

R97 4.7K/4

R98 4.7K/4

1 2

1 2

R100 390/6

+5V

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+5V

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C63

30P/6/N/50V

+3V

R101 0/4/X

Q9

2

GND

VCC

1

RESET#

FM809/SOT23

20mils

31541678716285971

AVDD

VDDIO

VDDIO

VDDCORE

VDDCORE

VDDCORE

VDDCORE

VSC420

A6_BUSTYPE

AVSS

VSSCORE

VSSCORE

VSSCORE

VSSCORE

VSSIO

VSSIO

41440668613275870

v0.4

VSSIO

R101,R102 Change to

R0402 for DFM issue

20mils

3

+5V

+3V

95

57

D0

56

D1

VDDIO

VDDIO

VDDIO

55

D2

54

D3

53

D4

52

D5

51

D6

50

D7

93

A0

92

A1

91

A2

90

A3

89

A4

88

A5_GPIOEN

85

84

A7_IFSEL0

83

A8_IFSEL1

82

A9_IFSEL2

81

A10_LPCSH

80

A11_LPCSH

79

A12

78

A13

77

A14

76

A15

75

A16

74

A17

73

A18

72

A19

49

RD/

48

WR/

47

ROMCS/

46

CS0/

45

CS1/

44

CS2/

43

RESET/

39

SCL2

42

SDA2

37

SCL1

38

SDA1

35

SCL0

36

SDA0

VSSIO

VSSIO

VSSIO

I2C Connector to LSI Raid card

94

100

RESET/{8}

RESET/

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MA0

MA1

MA2

MA3

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15

MA16

MA17

MA18

MA19SDA0

CS1/

SCL2

SDA2

SCL1

SDA1

RESET/

1 2

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15MA4

MA16

MA17

MA18

Unused

R188 0/4

R187 0/4

SCL0 {3}

SDA0 {3}

R78 100/6

12

12

C54

0.1U/6/X

R80

1K/6/X

MA[0..19] {5}

U13 AT29C040A_P

12 13

A0 I/O0

11

A1

I/O1

10

A2

I/O2

9

A3

I/O3

8

A4

I/O4

7

A5

I/O5

6

A6

I/O6

5

A7

I/O7

27

A8

26

A9

23

A10

25

A11

4

A12

28

A13

29

A14

3

A15

2

A16

30

A17

1

A18

31

WE

24

OE

22

CE

12

12

Firmware update By SMBUS

20mils

D

G

14

15

17

18

19

20

21

SCL {3,8}

SDA {3,8}

S

2N7002

SDG

20mils

12

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

+3V

Q10

SOT23

C55

0.1U/6

v0.4

3V3_LED

Rev : 1.0

10U/12/X/25V

0.1U/6/16V

C70

+5V+5V

12

1 2

10U/12/X/25V

C71

A A

1 2

10U/12/X/25V

C67

C68

12

0.1U/6/16V

1 2

C69

5

C66

12

0.1U/6/16V

C72

0.1U/4/16V

+3V

6

1 2

1 2

4

C73

0.1U/4/16V

3

C74

0.1U/4/16V

10CM0-161003-20R

C76

0.1U/4/16V

27

28 67 73

1 2

1 2

C75

0.1U/4/16V

25 26 40

Decoupling for VSC420

4

C78

0.1U/4/16V

41

1 2

1 2

C77

0.1U/4/16V

52

1 2

1 2

C79

0.1U/4/16V

7266

C80

0.1U/4/16V

895 53

86

1 2

88

1 2

C81

0.1U/4/16V

87

C82

0.1U/4/16V

+5V+5V

C84

0.1U/4/16V

1 2

1 2

C83

0.1U/4/16V

ROM & SRAM Decoupling

10CM0-161003-20R

3

1 2

C85

0.1U/4/16V

10U/8/X/10V

1 2

+5V

C86

Bulk Decoupling

4.7uF to 10uF

C87

10U/8/X/10V

10U/8/X/6.3V

+3V

C89

10U/8/X/6.3V

C90

C88

Bulk Decoupling

4.7uF to 10uF

10U/8/X/6.3V

2

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

Date: Sheet of

SAF-TE(VSC420)-1

GC-BAT4E

1

4 12Thursday, August 04, 2005

1.0

5

4

3

2

1

Can be used to power-up sense eight user - defined conditionMA19~MA12

+5V

D D

SHORT 1-2 : 1st BPB

SHORT 2-3 : 2nd BPB

+3V

U6

NC7S14/SOT23-5

+3V

R43

330/6

J1

H1X3

1 2

1

2BPB_CTR

2

3

JUMPER

C C

JP?*2P/1-2 SHORT

RED

B B

53

2 4

+3V

53

2 4

NC7S14/SOT23-5/X

R180

0/6

U8

12

C45

0.1U/6/X/16V

U5

14

13

10

4

1

7

FST3125/TSSOP14

Switch GPIO(0,1,2,3)

+5V

12

C46

0.1U/6/X/16V

1 2

U7

14

13

10

4

1

7

FST3125/TSSOP14

+5V

12

C47

0.1U/6/X/16V

U9

14

13

10

4

1

7

FST3125/TSSOP14

VCC

OE3

OE2

OE1

OE0

GND

FST3125

VCC

OE3

OE2

OE1

OE0

GND

FST3125

VCC

OE3

OE2

OE1

OE0

GND

FST3125

SW_1

3125_GPIO(0~3)

connect to LED

12

A3

11

Y3

9

A2

8

Y2

5

A1

6

Y1

2

A0

3

Y0

3125_GPIO(4~7)

SW_2

connect to Cascad

connector

12

A3

11

Y3

9

A2

8

Y2

5

A1

6

Y1

2

A0

3

Y0

SW_3

3125_2GPIO(4~7)

connect to LED

12

A3

11

Y3

9

A2

8

Y2

5

A1

6

Y1

2

A0

3

Y0

420_GPIO3

3125_GPIO3

420_GPIO2

3125_GPIO2

420_GPIO1

3125_GPIO1

420_GPIO0

3125_GPIO0

420_GPIO7

3125_GPIO7

420_GPIO6

3125_GPIO6

420_GPIO5

3125_GPIO5

420_GPIO4

3125_GPIO4

3125_GPIO7

3125_2GPIO7

3125_GPIO6

3125_2GPIO6

3125_GPIO5

3125_2GPIO5

3125_GPIO4

3125_2GPIO4

MA11 , MA10 Adjust the LPC Interface setup and hold times

High

Low

MA9~MA7 Can be used to power-up sense the interface register set.

LFRAME# input will function normally.

1ns of additional hold margin will be inserted in the LFRAME# input

High

The LAD bus inputs will function normally.

Low

1ns of additional hold margin will be inserted in the LAD bus inputs.

If pilled up , the register set is configuration for "SMIC" operation.

If pilled down , the register set is configuration for "KCS" operation.

Can be used to power-up sense the system interface bus type.MA6~MA5

MA6 , MA5

High High

Low High

High Low

Low Low

MA4 Enable the chip select swap function to power-up sense the boot ROM

XBUS Mode

LPC Mode

GPIO Mode

(Reserved Mode)

chip select output.

MA4

High

Low

MA3~MA0

ROMCS is activated as the boot ROM chip select.

CS0 is activated as the boot ROM chip select and ROMCS is swapped to

CS0 space.

Can be used to enable the half ROM function which determines the size

of the memory device attached to ROMCS# and forces the boot location to

start at the half way point in the memory device.

Each bit can be used select one of the four available sizes,

MA3

MA2

MA1

MA0

1024K bytes

512K bytes

256K bytes

128K bytes

Pull-downs should only be used on A3 through A0 when

operation from the half way point in the memory device

attached to ROMCS# is desired.

v0.4

(L)

(L)

(L)

(L)

(H)

(L)

(H)

(L)

(L)

(L)

(H)

(H)

(H)

(H)

(H)

(H)

(H)

(H)

(H)

(H)

MA0

R30 4.7K/6/X

MA1

R32 4.7K/6/X

MA2

R34 4.7K/6/X

MA3

R36 4.7K/6/X

MA4

R38 4.7K/6/X

MA5

R40 4.7K/6

MA6

R42 4.7K/6/X

MA7

R45 4.7K/6

MA8

R47 4.7K/6

MA9

R49 4.7K/6

MA10

R51 4.7K/6/X

MA11

R53 4.7K/6/X

MA12

R55 4.7K/6/X

MA13

R57 4.7K/6/X

MA14

R59 4.7K/6/X

MA15

R61 4.7K/6/X

MA16

R63 4.7K/6/X

MA17

R65 4.7K/6/X

MA18

R67 4.7K/6/X

MA19

R69 4.7K/6/X

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R70

C48

22P/6/N/50V

1.2K/6

1 2

12

R76

1.2K/6

1 2

R72 22/6

1 2

1 2

R74 22/6

+5V

C49

22P/6/N/50V

1 2

1 2

C50

22P/6/N/50V

JP1

1

2

3

4

MA[0:19]

MA[0:19] {4}

H1X4

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

2

Date: Sheet of

SAF-TE(VSC420)-2

GC-BAT4E

1

5 12Thursday, August 04, 2005

1.0

+5V

U10 LTC1487

A A

420_GPIO[0:7]

3125_GPIO[0:7]

3125_2GPIO[0:7]

420_GPIO[0:7] {4}

3125_GPIO[0:7] {3}

3125_2GPIO[0:7] {3}

5

ICMB/RS485 Termination Options:

1) No Termination: Populate R71 - R74 with 0 ohm;

NO POP all others.

OR

2) Populate R71 - R74, C48-C50; NO POP: R70 OR

R76.

3) Populate R70 - R76, Replace C48 w/ 120 ohm,

Replace R71 - R74 w/ 0 ohm; NO POP: C49 C50.

4

ICMB_RXD{4}

P0_0{4}

ICMB_TXD{4}

R75

4.7K/6

1

RO

VCC

2

RE/

3

DE

4 5

12

DI GND

3

R71 22/6

1 2

8

7

B

6

A

1 2

R73 22/6

5

D D

4

3

2

1

v0.4

v0.3

C C

+3V

12

R183

SATA2

560/6

D9

LED/GREEN

SATA3

D10

LED/GREEN

MATED3

MATED4

+3V

12

R184

560/6

MATED3 {2,3,7}

For GBT HDD Tray

MATED4 {2,3,7}

+3V

12

R181

SATA0

560/6

D7

LED/GREEN

SATA1

D8

LED/GREEN

MATED1

MATED2

+3V

12

R182

560/6

MATED1 {2,3,7}

MATED2 {2,3,7}

B B

A A

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

HDD POWER LED FOR GBT

GC-BAT4E

1

6 12Thursday, August 04, 2005

1.0

5

VCC3_A{2}

VCC3_B{2}

VCC3_C{2}

VCC3_D{2}

MATED1{2,3,6}

D D

MATED2{2,3,6}

MATED3{2,3,6}

MATED4{2,3,6}

VCC3_A

VCC3_B

VCC3_C

VCC3_D

MATED1

MATED2

MATED3

MATED4

1 2

+12V

12

R8

2.2K/6

+12V

R4 30K/6

1 2

R2 2K/6

1 2

12

C4

10U/12/16V

C2

0.1U/6

+5V

Q2

D

G

S

R12

1 2

+5V

SDG

MATED1

2N7002

SOT23

R10

10K/6

1 2

10K/6

C C

+12V

R16 30K/6

12

+12V

1 2

R14 2K/6

1 2

12

C16

0.1U/6

12

R20

2.2K/6

+5V

Q4

D

G

S

2N7002

SOT23

B B

R24

1 2

+5V

SDG

MATED3

C18

10U/12/16V

R22

10K/6

1 2

10K/6

+5VA

C14

0.1U/6/16V/X

1 2

+5VC

1

2

3

4 5

C28

0.1U/6/16V/X

1 2

4

U2

1

S1

2

3

4 5

FDS8958A

1 2

C12 0.1U/6/16V

G1

S2

G2

R6 330/6

1 2

D1

N

D2

P

U4

S1

D1

G1

N

S2

D2

G2

P

FDS8958A

R18 330/6

1 2

C26 0.1U/6/16V

1 2

+3V +3V

3

+5V

8

7

6

12

C8

10U/12/16V

+12VA

12

C9

10U/12/16V

12

0.1U/6/16V

+12V

R3 30K/6

1 2

+12V

C10

12

R7

2.2K/6

1 2

R1 2K/6

1 2

12

C3

10U/12/16V

C1

+5VB

0.1U/6

2

U1

1

S1

2

G1

N

3

S2

4 5

G2

P

FDS8958A

R5 330/6

1 2

C11 0.1U/6/16V

1 2

1

+5V +12VB

8

7

D1

6

D2

12

C5

10U/12/16V

12

C6

10U/12/16V

12

C7

0.1U/6/16V

+5V

Q1

D

G

S

R11

1 2

+5V

SDG

MATED2

2N7002

SOT23

R9

10K/6

1 2

10K/6

12

C22

10U/12/16V

+12VC

12

C23

10U/12/16V

12

C24

0.1U/6/16V

+12V

12

R19

2.2K/6

+12V

R15 30K/6

12

1 2

+5V

8

7

6

+5V

Q3

D

G

S

R23

1 2

+5V

SDG

MATED4

2N7002

SOT23

R21

10K/6

1 2

10K/6

1 2

+5VD

C15

0.1U/6

1 2

R13 2K/6

12

C17

10U/12/16V

C13

0.1U/6/16V/X

U3

1

S1

2

G1

3

S2

4 5

G2

FDS8958A

C25 0.1U/6/16V

C27

0.1U/6/16V/X

1 2

N

P

R17 330/6

1 2

1 2

+5V

+12VD

8

7

D1

6

D2

12

C19

10U/12/16V

12

C20

10U/12/16V

12

C21

0.1U/6/16V

+3V

+3V

Q5

1 2

G

C31

0.1U/6/16V/X

D

S

SDG

Title

P4602CM

SOT23

Q6

Q7

C36

0.1U/6/16V/X

1 2

D

G

S

P4602CM

SOT23

SDG

VCC3_B VCC3_C

C32

0.1U/6

1 2

12

C33

100U/1210/X5R/6.3V

+12VC

R27 2K/6

1 2

C37

0.1U/6/16V/X

1 2

+3V

C41

0.1U/6/X/16V/X

C42

0.1U/6/X/16V/X

C43

0.1U/6/X/16V/X

C44

0.1U/6/X/16V/X

Q8

D

G

1 2

C40

0.1U/6/16V/X

S

SDG

P4602CM

SOT23

VCC3_A

C38

0.1U/6

1 2

+12VA

R28 2K/6

1 2

A A

v0.4

+12VB

12

C39

100U/1210/X5R/6.3V

2K/6

1 2

R26

P4602CM-->P/N:10IF1-504602-01

D

G

S

P4602CM

SOT23

SDG

C34

0.1U/6

1 2

v0.4v0.4

+12VD

12

C35

100U/1210/X5R/6.3V

R25 2K/6

1 2

Size Document Number Rev

5

4

3

2

Date: Sheet of

v0.4

VCC3_D

12

C30

0.1U/6

GIGABYTE TECHNOLOGY CO., LTD.

C29

100U/1210/X5R/6.3V

1 2

HOT-SWAP POWER CONTROL

GC-BAT4E

1

7 12Thursday, August 04, 2005

1.0

5

Voltage Sensor

AGND

OUT+

CPUD-

3

VIN4_791D ---> +5VE

VIN5_791D ---> +5VF

VIN6_791D ---> +5VG

VIN7_791D ---> +5VH

VREF

VTIN2

VTIN1

HM_SMI1_

L2 FB30/8

HMCLK

GND

37

VREF

38

VTIN3

39

VTIN2

40

VTIN1

41

SMI#/IRQ

42

OVT#

43

FAN_OUT4/GPIOA0

44

FANIN4/GPIOA1

45

FAN_OUT5/GPIOA2

46

FANIN5/GPIOA3

47

WDTRST#/FAN_OUT6

48

SYSRSTIN#/FANIN6

W83792D

VIN6_792D_GPO : H --> Sense +12VC

VIN6_792D_GPO : L --> Sense +12VD

VIN0_791D ---> +5VA

VIN1_791D ---> +5VB

VIN2_791D ---> +5VC

C114

0.1U/6

+3V

12

VIN3_791D ---> +5VD

U20

4

VCC

2 1

GND NC/OUT-

OSC/14.318MHZ

D D

C C

4

VIN0_792D

VIN1_792D

VIN2_792D

VIN3_792D

VIN4_792D

VIN5_792D

VIN6_792D

CPUD-

3635343332313029282726

VIN0

VIN1

VIN2

VIN3

VBAT

VCOREA

VRM_EN

CASEOPEN

VCOREB/VIN4

VIDA0/GPIOA4

VIDA1/GPIOA5

VIDA2/GPIOA6

VIDA3/GPIOA7

VIDA4/GPIOB0

VIDA5/GPIOB1

1234567891011

VIN6_792D_GPO

1 2

R149 4.7K/6

25

GND

+5VSB

THERMTRIPB

THERMTRIPA

PWRBTN#

FANIN1

FANIN2

FANIN3

FAN_OUT1/A0

FAN_OUT2/A1

FAN_OUT3/VID90_10

VIDB0/GPIOB2

VIDB1/GPIOB3

VIDB2/GPIOB4

VIDB3/GPIOB5

VIDB4/GPIOB6

VIDB5/GPIOB7

12

SDA

SCL

CLK

VDD

U18

24

23

22

21

20

19

18

17

16

15

14

13

W83792D_0

CPUD-

HMCLK

FAN_OUT1

FAN_OUT2

SDA

SCL

FANIN1

FANIN2

C112

10U/8

35MIL

C102

10U/8

SDA {3,4}

SCL {3,4}

12

3

VIN0_792D

VIN1_792D

VIN2_792D

VIN3_792D

VIN4_792D

VIN5_792D

R158

10K/6/1%

P12V_C

P12V_D

CPUD-

12

12

C103

.1U/6

+5V

FANIN1 {9}

FANIN2 {9}

FAN_OUT1 {9}

FAN_OUT2 {9}

12

C113

.1U/6

CPUD-

VREF

VTIN2

+5V_DL

L1 FB30/8

SYSTEM THEMISTOR2

NEAR SYS FAN

HEADER

2

+5VA

R141

47K/6/1%

R150

15K/6/1

C104

0.1U/6

SYSTEM THEMISTOR3

NEAR SYS FAN

HEADER

VREF

VTIN1

+5VB

R142

47K/6/1%

C105

0.1U/6

R151

15K/6/1

R143

10K/6/1%

C106

0.1U/6

R159

10K/6/1%

R152

10K/6/1

+12VA

R145

R144

30K/6/1%

10K/6/1%

R153

10K/6/1

C107

C108

0.1U/6

0.1U/6

P12V_D

P12V_C

VIN6_792D_GPO

BE : L-> C = A

BE : H -> C = B

+12VB

R154

10K/6/1

U19

6

A

4 5

B C

1

BE

PI5C3303

R146

30K/6/1

C109

0.1U/6

1

R155

10K/6/1

VCC

GND

+12VC

USE

GPIOA4

CONTROL

2

3

R147

30K/6/1

C110

0.1U/6

+5V

R156

10K/6/1

VIN6_792D

+12VD+5VD+5VC

R148

30K/6/1

R157

10K/6/1

C111

0.1U/6

+5V delay power for W83792

B B

P-channel: 3A

+5V

+12V

12

R164

2.2K/6

30K/6

1 2

2N7002

D

G

S

Q21

RESET/{4}

A A

C119

R165

12

SOT23

SDG

10U/12/16V

5

PN:10IF1-305203-01

Q20

S

D

S

D

G

G

SOT23

IRLML5203

U21

1

S1

2

3

4 5

10IF2-504532-01

P-channel: 5A

N-channel: 7A

G1

S2

G2

FDS8958A/X

1 2

0.1U/6/16V

N

P

C121

D1

D2

HM_SMI1_

8

+5V_DL

7

6

12

C120

10U/12/16V

4

+5V_DL

12

R160

4.7K/6

JUMPER

JP?*2P/1-2 SHORT

+5V

R163

100K/6

FAN_OUT1

WHITE

3

FAN_OUT2

12

C115

0.1U/6

+5V

R161

100K/6/X

12

RT/SMD

RT1

C116

0.1U/6

CPUD-

+5V

R162

100K/6

792D_ID1

1

2

3

H1X3

R167

R166

100K/6

100K/6/X

12

C117

0.1U/6

12

RT/SMD

RT2

C118

0.1U/6

CPUD-

W83792D ADDR. SELECT

Close 1-2 --> 5EH(Default)

Close 2-3 --> 5AH

A1=1

A1=0

0x58

0x5A

0x5C

0x5EA0=1

Title

Size Document Number Rev

Date: Sheet of

A0=0

2

GIGABYTE TECHNOLOGY CO., LTD.

HARDWARE MONITOR(W83792D)

GC-BAT4E

1

8 12Thursday, August 04, 2005

1.0

5

D D

C C

B B

4

Q21,Q23,Q27,Q28,Q33,Q34,Q22,Q25,Q29,Q31,Q36,Q37-->

Change to 10IF1-305203-01/ILRML5203IR

FAN1

R169 1.5K/6

1 2

R170

1K/6

1 2

R172 1.5K/6

1 2

+12V

Q24

D

G

S

2N7002

SOT23

FAN_OUT1{8}

FAN_OUT1

SDG

FAN2

R175 1.5K/6

1 2

R176

1K/6

1 2

R178 1.5K/6

1 2

+12V

Q27

D

G

S

2N7002

SOT23

FAN_OUT2{8}

FAN_OUT2

SDG

3

R168

1 2

0/6/X

Q22

B

E

IRLML5203

SOT23

Q23

B

E

IRLML5203/X

SOT23

1000P/6/16V

R174

1 2

0/6/X

Q25

B

E

IRLML5203

SOT23

Q26

B

E

IRLML5203/X

SOT23

1000P/6/16V

C125

2

+5V

12

D5

50_MIL

C

12V1

C

C123

1 2

50_MIL

C

C

1 2

1N5817/X

+5V+12V

12

R171

10K/6

C122

4700P/6

1 2

R173 510/6

1 2

2134

CVS

FAN1

FAN_CON

+5V

12

D6

1N5817/X

+5V+12V

12

R177

C124

10K/6

4700P/6

1 2

R179 510/6

1 2

2134

CVS

FAN2

FAN_CON

FANIN1

FANIN212V2

FANIN1 {8}

FANIN2 {8}

1

A A

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

PWM FAN CONTROL(1,2)

GC-BAT4E

1

9 12Thursday, August 04, 2005

1.0

5

D D

4

3

2

1

SATA Differential Pair

BOTTOM AND Reference L3(GND)

COUPON1A COUPON1B

C C

COUPON1

1 2

COUPON

3

6000mil6000mil

COUPON2

1 2

COUPON

3

K1

1

Fiducial_Point

1

Fiducial_Point

B B

A A

5

1

Fiducial_Point

1

Fiducial_Point

1

Fiducial_Point

1

Fiducial_Point

K2

1

Fiducial_Point

K3

K4

1

Fiducial_Point

K5

K6

1

Fiducial_Point

K7

K8

1

Fiducial_Point

K10

K9

1

Fiducial_Point

K12

K11

1

Fiducial_Point

I1

1

POSITION

I2

1

POSITION

I3

1

POSITION

I4

1

POSITION

4

淚滴孔

螺絲孔

固定孔

光學點

MH1

923

45

678

X 2 (MH3,MH4)

X 2 (MH1,MH2)

X 4

X 12

MH2

923

45

1

1

678

MH3

923

678

3

MH4

923

45

45

1

1

678

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

2

Date: Sheet of

SATA DIFFERENTIAL COUPON

GC-BAT4E

1

10 12Thursday, August 04, 2005

1.0

5

4

3

2

1

SATA RAID

CONTROLLER

D D

First SATA BPB Second SATA BPB

J5

J3

I2C/SCL & SDA

3125_GPIO(0~3) / 3125_2GPIO(4~7)

HDD_0

HDD_1

C C

SCL0 & SDA0 SCL0 & SDA0

HDD_2

HDD_3

(On)

3125_GPIO(0~3)

VSC 420

SAF-TE

420_GPIO(4~7)

SW_1

420_GPIO(0~3)

VSC 420

SAF-TE

420_GPIO(4~7)

(Off)

(On)

SW_2 SW_3

B B

3125_GPIO(4~7)

3125_GPIO(4~7)

3125_GPIO(4~7)

9515 9515

3125_2GPIO(4~7)

1

W83792D W83792D

2

3

SHORT 1-2 : 1st BPB

SHORT 2-3 : 2nd BPB

(Off)

3125_GPIO(4~7)

3125_GPIO(4~7)

Cascade Conn. BPB No. Jumper

J5

J3

I2C/SCL & SDA

420_GPIO(0~3)

SW_2

3125_GPIO(4~7)

Cascade Conn.

3125_GPIO(0~3) / 3125_2GPIO(4~7)

(Off)

3125_GPIO(0~3)

SW_1

(On)

SW_3

3125_2GPIO(4~7)

HDD_0

HDD_1

HDD_2

HDD_3

1

2

3

BPB No. Jumper

SHORT 1-2 : 1st BPB

SHORT 2-3 : 2nd BPB

A A

3125_GPIO(4~7) / R_ SCL & R_ SDA

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

2 PCS BPB COLLOCATION

GC-BAT4E

1

11 12Thursday, August 04, 2005

1.0

5

4

3

2

1

Schematic changes:

Page

D D

C C

Author

ModificationRevision

BOM changes:

Page

Mod.

LocationRevision

B B

A A

A: ADD D: Delete V: Value Change

GIGABYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

REVISION HISTORY

GC-BAT4E

1

12 12Thursday, August 04, 2005

1.0

Loading...

Loading...