Gigabyte GA-M68MT-S2 REV 1.35 Schematic

GA-M68MT-S2

SHEET

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

TITLE

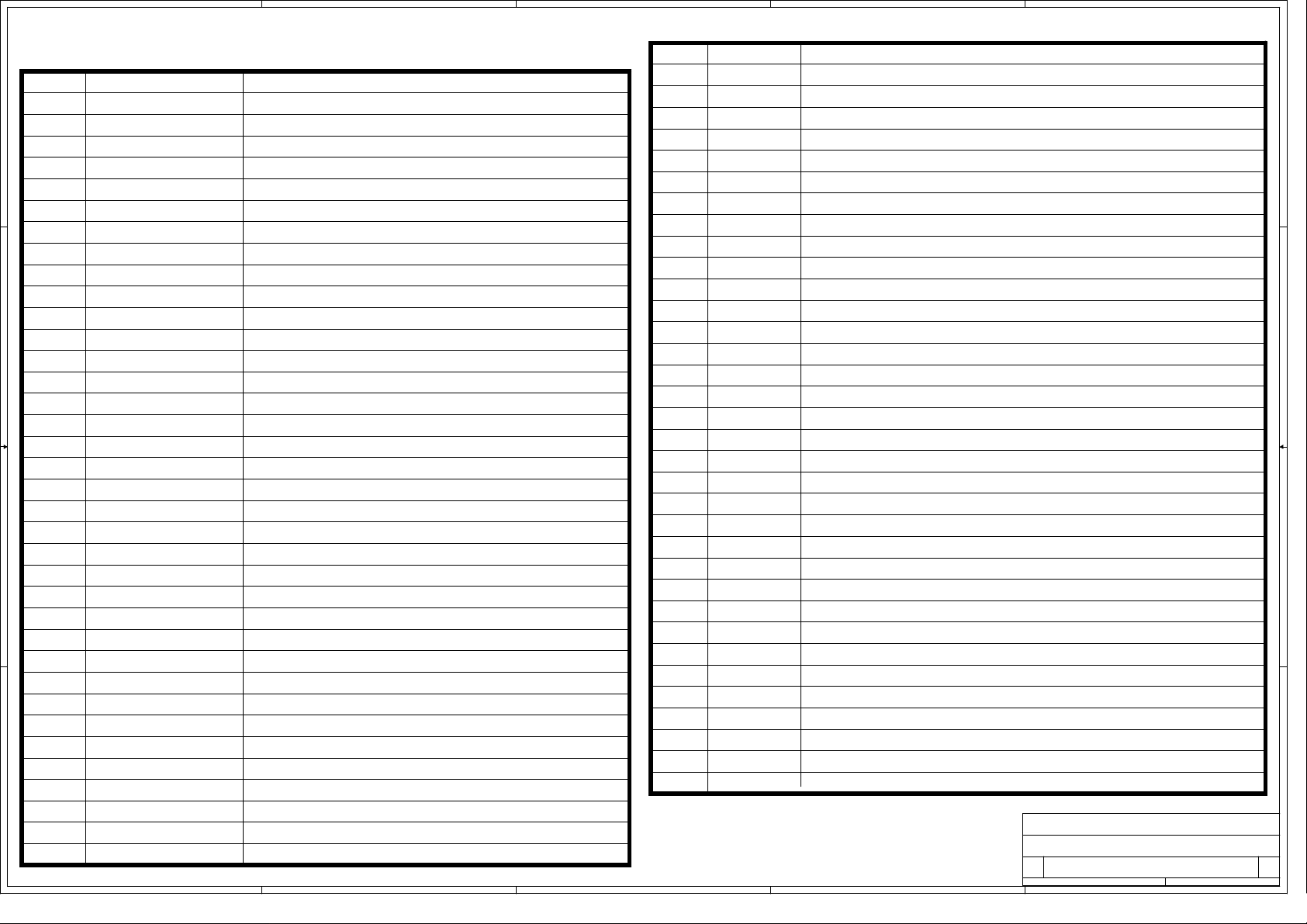

COVER SHEET

BOM & PCB MODIFY HISTORY

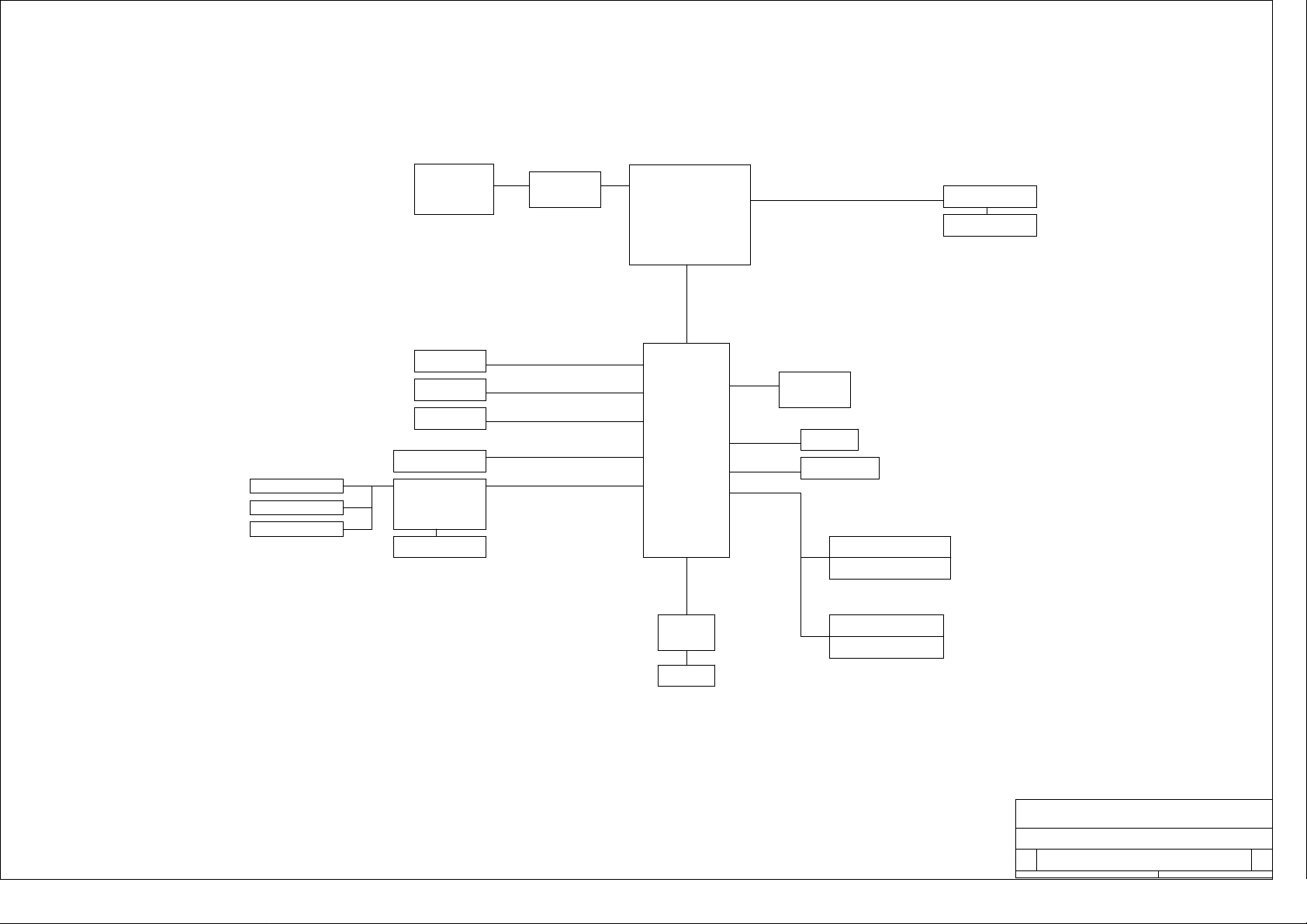

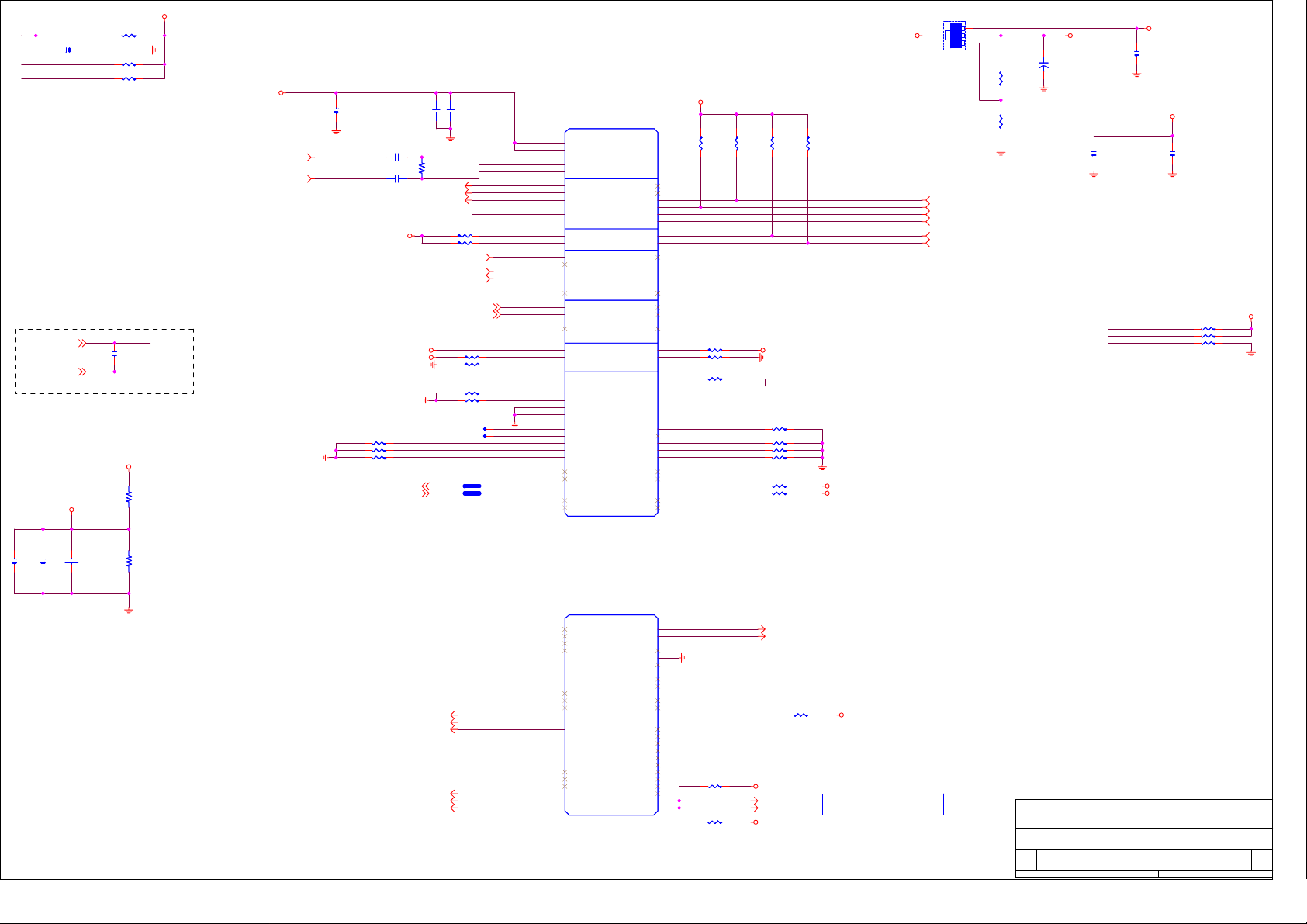

BLOCK DIAGRAM

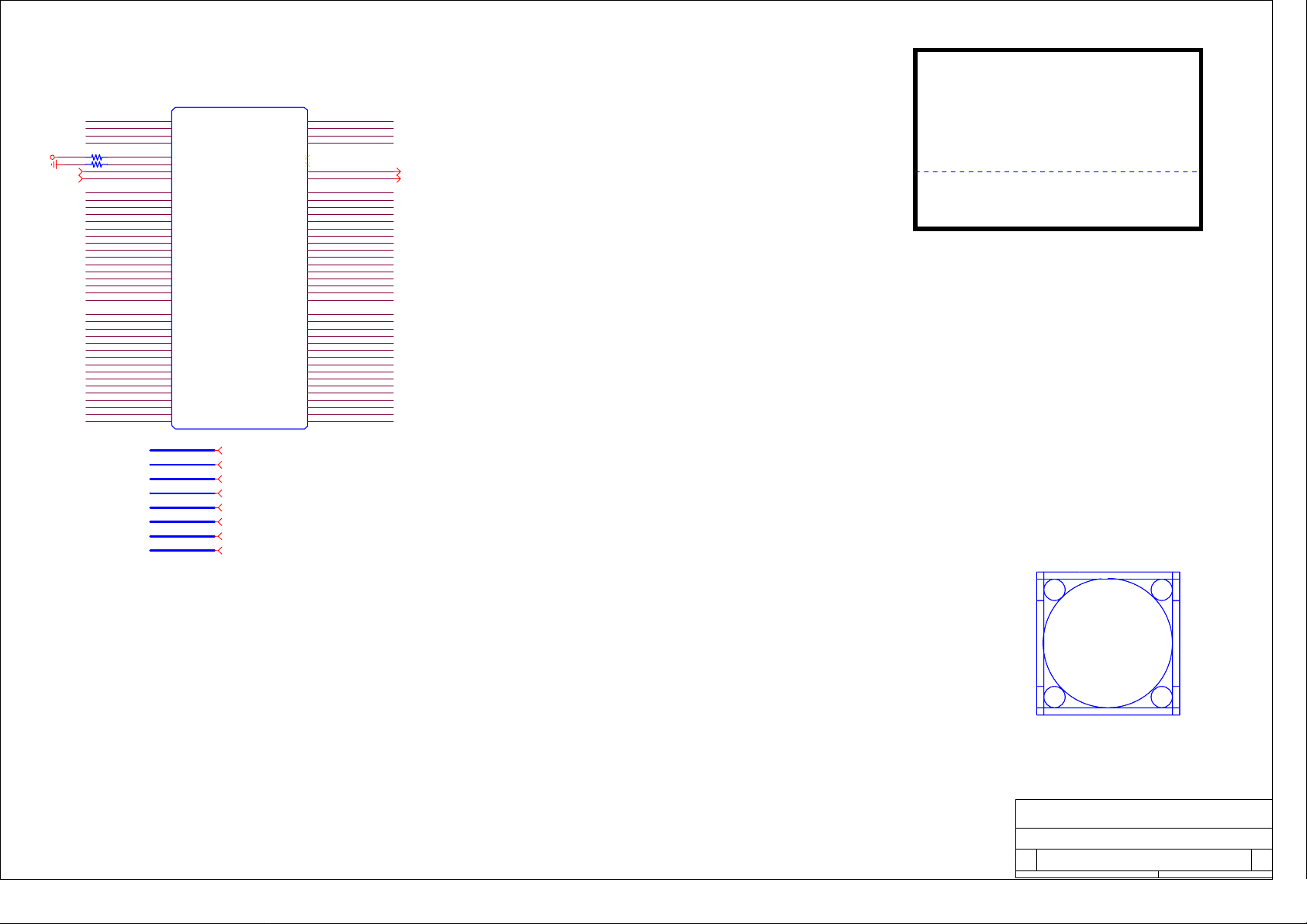

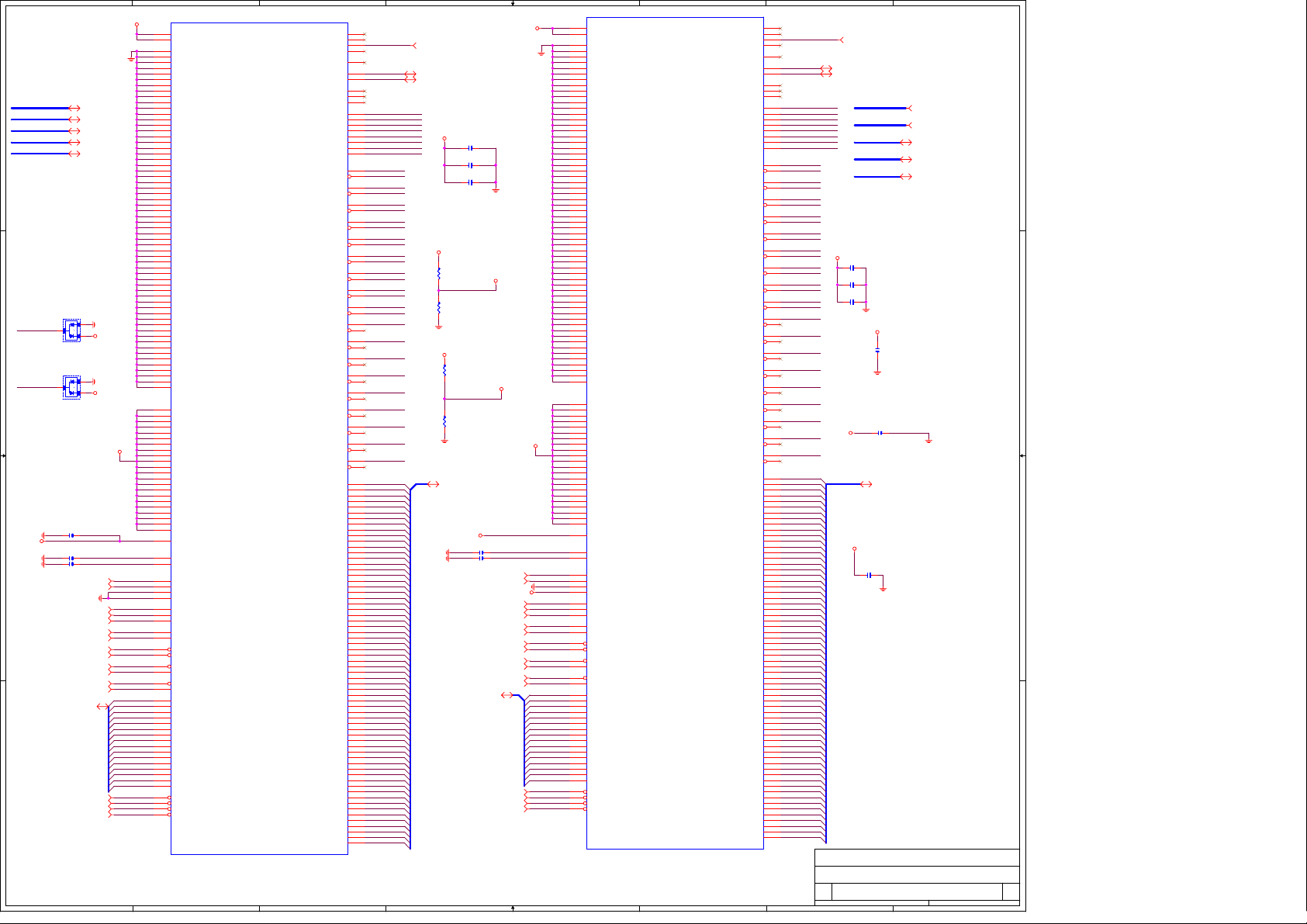

PROCESSOR HT INTERFACE

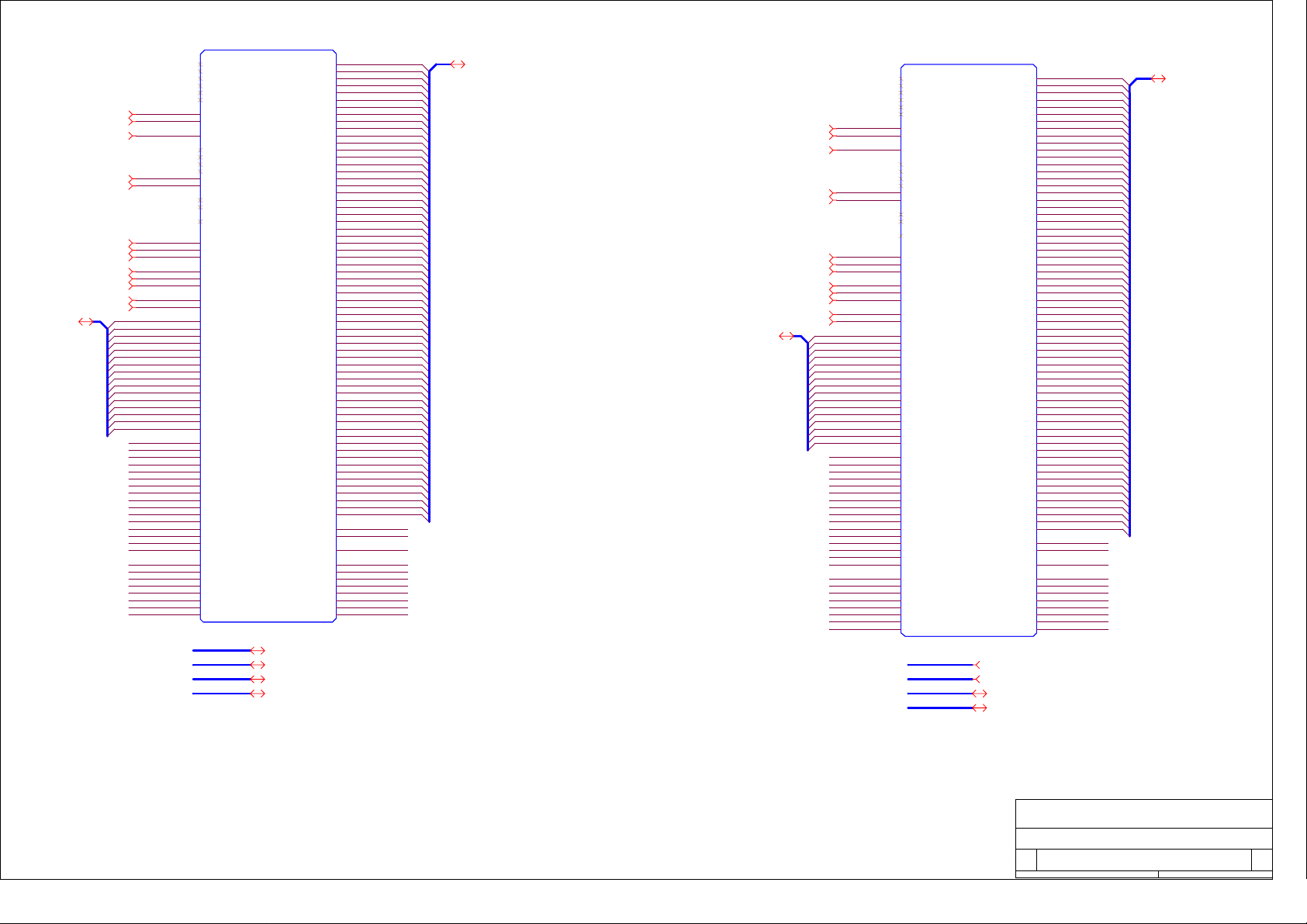

PROCESSOR DDR INTERFACE

PROCESSOR CONTROL & DEBUG

PROCESSOR Power & Gnd

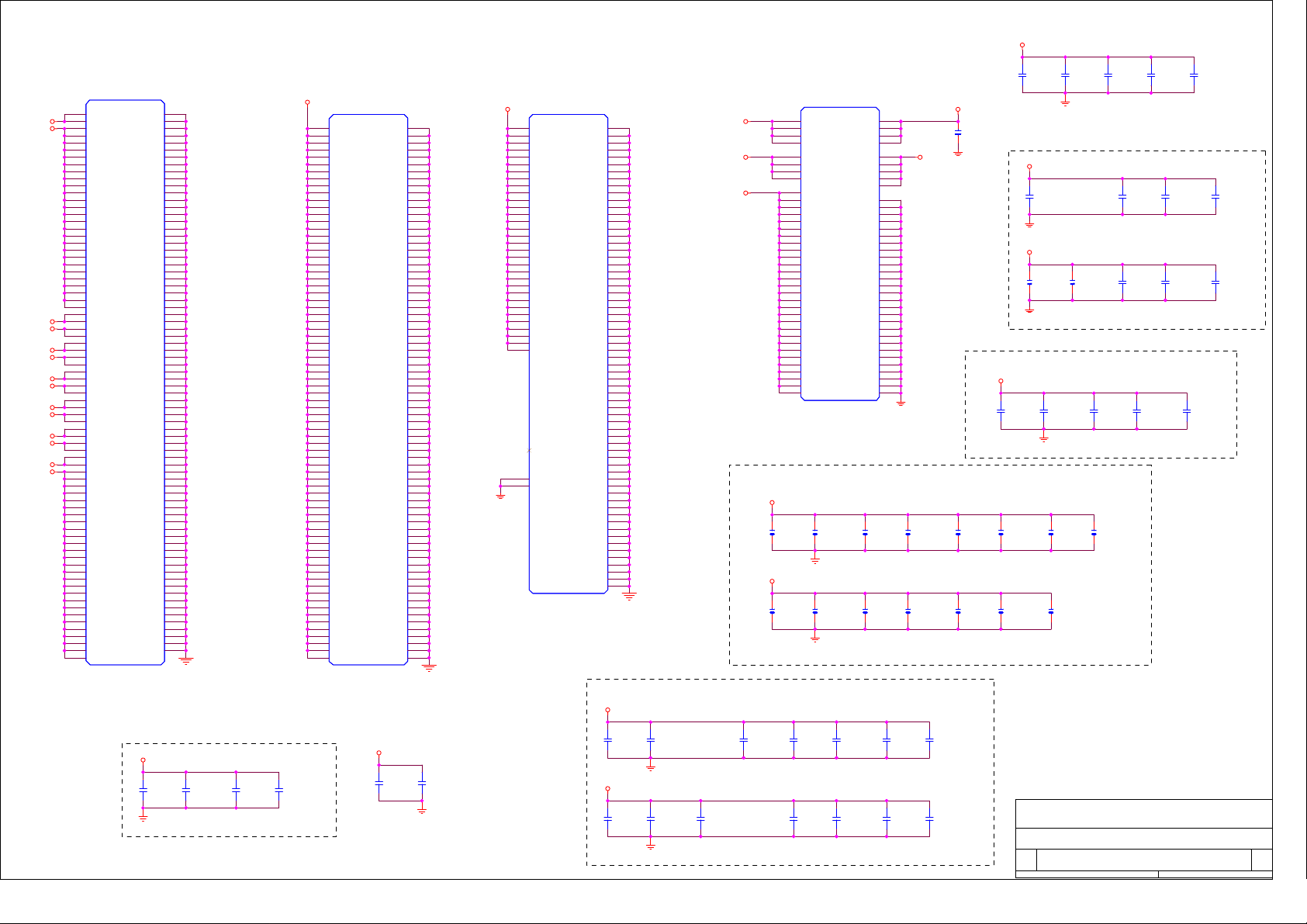

DIMM 1,2

MCP61-CPU

MCP61-PCIe

MCP61-DAC, RGMII

MCP61-PCI

MCP61-SATA, IDE

MCP61-USB, HD-Audio, GPIO

MCP61-Power, Gnd

P-Code:U96133-0

SHEET

TITLE

Revision: 1.35

16

17

18

19

20

21

22

23

24

25

PCI EXPRESS x16, x1 SLOT

PCI SLOT

COM,LPT

ITE 8720GB/JX

Realtek 8211 CL

H/W MONITOR & FAN CONTROL

ALC888B HD-AUDIO

AUDIO JACK

POWER SEQ

ATX, VCC12_DUAL, VDDA25

F_PANEL

DDR POWER

PWM ISL6324A

USB

GIGABYTE

GIGABYTE

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

GIGABYTE

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

GA-M68MT-S2

GA-M68MT-S2

GA-M68MT-S2

125Friday, November 05, 2010

125Friday, November 05, 2010

125Friday, November 05, 2010

of

of

of

1.35

1.35

1.35

5

Model Name:GA-M68MT-S2 Rev:1.35

Component value change history

Date

2010.06.29

D D

2010.11.05

C C

Change Item

10A E_BOM issue PCB:1.0

13A E_BOM issue PCB:1.31

13D E_BOM issue PCB:1.35

Copy from M68MT-S2P 2.3A BOM, change os-con capactior

Print port issue & D22 BAV70 change to BAT54A & U17_PWR only pull up +12V2010.10.12

ADD CROSS MOAT FOR CORE UNLOCK ISSUE

4

Reason

P-Code: U96133-0

3

2

Circuit or PCB layout change for next version

ReasonChange ItemDate

1.3 Gerber out2010.09.21

1.3X Gerber out2010.10.XX Modify from M68MT-D3 2.31.

2010.10.22 Core Boost issue (NV_TCK & NV_TMS SWAP)1.32 Gerber out

2010.10.29 1.33 Gerber out 1. change Core Boost GPIO PIN 2.move core boost schmatic to chipset an end

2010.11.5 1.35 Gerber out

Modify from M68MT-D3 2.31.

print port & core boost issue 2010.10.15 1.31 Gerber out

1. +12V <->5VDUAL 0.1u*2 2.+12V<->VCC 0.1u 3. 5VDUAL <->GND 22u 4. VCC<->5VDUAL 0.1u

1

B B

A A

GIGABYTE

GIGABYTE

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GIGABYTE

BOM & PCB MODIFY HISTORY

BOM & PCB MODIFY HISTORY

BOM & PCB MODIFY HISTORY

GA-M68MT-S2

GA-M68MT-S2

GA-M68MT-S2

1

1.35

1.35

225Friday, November 05, 2010

225Friday, November 05, 2010

225Friday, November 05, 2010

1.35

of

of

of

BLOCK DIAGRAM

www.schematic-x.blogspot.com

POWER

SUPPLY

CONNECTOR

PCI_EXPRESS X16 PCI EXPRESS X16 CONNECTOR

PCI_EXPRESS X1 VGA

X4 - SATA CONN

PARALLEL CONN SIO ITE 8720 JX/GB

SERIAL CONN

8Mb SPI FLASH

VREG

PCI EXPRESS X1 CONNECTOR

PCI EXPRESS X1 CONNECTORPCI_EXPRESS X1

INTEGRATED SATA

LPC BUS 33MHZPS2/KB CONN

AMD CPU

SOCKET AM3

HT 16X16 1GHZ

NVIDIA

MCP61PA

RGMII

RTL8211CL

10/100/1G PHY

PCI 33MHZ

AZILIA

USB2.0 X8 PORT

128-BIT 200/266/333/400MHZ

PCI SLOT

RTL ALC888B CODEC

BACK PANEL

USB2.0 PORTS 0-1

USB2.0 PORTS 2-3

FRONT PANEL

USB2.0 PORTS 4-5

USB2.0 PORTS 6-7

X2

X2/10/100/1G LAN

DDRIII 800/1066/1200/1666

DDRIII SDRAM CONN 1

DDRIII SDRAM CONN 2

1L

1H

RJ45

BACK PANEL

GIGABYTE

GIGABYTE

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

GIGABYTE

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

GA-M68MT-S2

GA-M68MT-S2

GA-M68MT-S2

of

of

of

325Friday, November 05, 2010

325Friday, November 05, 2010

325Friday, November 05, 2010

1.35

1.35

1.35

VCC12_HT

L0_CTLIN_H0{9}

GND

L0_CTLIN_L0{9}

M2CPUA

M2CPUA

HYPERTRANSPORT

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

N6

P6

N3

N2

49.9/4/1R3 49.9/4/1R3

V4

49.9/4/1R4 49.9/4/1R4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

L0_CADIN_L[0..15]

L0_CADIN_H[0..15]

L0_CLKIN_L[0..1]

L0_CLKIN_H[0..1]

L0_CADOUT_L[0..15]

L0_CADOUT_H[0..15]

L0_CLKOUT_L[0..1]

L0_CLKOUT_H[0..1]

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

L0_CADIN_L[0..15] {9}

L0_CADIN_H[0..15] {9}

L0_CLKIN_L[0..1] {9}

L0_CLKIN_H[0..1] {9}

L0_CADOUT_L[0..15] {9}

L0_CADOUT_H[0..15] {9}

L0_CLKOUT_L[0..1] {9}

L0_CLKOUT_H[0..1] {9}

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CTLOUT_H0 {9}

L0_CTLOUT_L0 {9}

CPU_VDD_RUN = VCORE

CPU_VDDA_RUN = VDDA25

VLDT_RUN = VCC12_HT

CPU_VDDIO_SUS = DDR18V

CPU_VTT_SUS = DDRVTT

VLDT_A = VCC12_HT

VLDT_B = HT12B

M2CPU

M2CPU

AM2RM/PP/BU/PB/[12KRC-04K812-14R_12KRC-04K812-12R]

AM2RM/PP/BU/PB/[12KRC-04K812-14R_12KRC-04K812-12R]

GIGABYTE

GIGABYTE

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

GIGABYTE

CPU HYPER TRANSPORT

CPU HYPER TRANSPORT

CPU HYPER TRANSPORT

GA-M68MT-S2

GA-M68MT-S2

GA-M68MT-S2

425Friday, November 05, 2010

425Friday, November 05, 2010

425Friday, November 05, 2010

of

of

of

1.35

1.35

1.35

M2CPUB

M2CPUB

MEMORY INTERFACE A

AG21

AG20

G19

H19

U27

U26

-CSA1

-CSA0

MODT_A0

DCLKA0

-DCLKA0

-SCASA

-SWEA

-SRASA

SBAA2

SBAA1

SBAA0

CKEA1

CKEA0

MAAA15

MAAA14

MAAA13

MAAA12

MAAA11

MAAA10

MAAA9

MAAA8

MAAA7

MAAA6

MAAA5

MAAA4

MAAA3

MAAA2

MAAA1

MAAA0

DQSA7

-DQSA7

DQSA6

-DQSA6

DQSA5

-DQSA5

DQSA4

-DQSA4

DQSA3

-DQSA3

DQSA2

-DQSA2

DQSA1

-DQSA1

DQSA0

-DQSA0

DMA7

DMA6

DMA5

DMA4

DMA3

DMA2

DMA1

DMA0

AC25

AA24

AC28

AE20

AE19

AD27

AA25

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

G20

G21

V27

W27

N25

Y27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

D29

C29

C25

D25

E19

G15

B29

E24

E18

H15

L27

T25

T27

F19

F15

-CSA1{8}

-CSA0{8}

MODT_A0{8}

A00P

DCLKA0{8}

A00N

-DCLKA0{8}

-SCASA{8}

-SWEA{8}

-SRASA{8}

SBAA2{8}

SBAA1{8}

SBAA0{8}

CKEA1{8}

CKEA0{8}

MAAA[0..15]{8}

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

-DQSA[0..8]

DQSA[0..8]

MA_CK[0..8]

DMA[0:8]

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

-DQSA[0..8] {8}

DQSA[0..8] {8}

MA_CK[0..8] {8}

DMA[0..8] {8}

MDA63

AE14

MDA62

AG14

MDA61

AG16

MDA60

AD17

MDA59

AD13

MDA58

AE13

MDA57

AG15

MDA56

AE16

MDA55

AG17

MDA54

AE18

MDA53

AD21

MDA52

AG22

MDA51 MODT_B0

AE17

MDA50

AF17

MDA49

AF21

MDA48

AE21

MDA47

AF23

MDA46

AE23

MDA45

AJ26

MDA44

AG26

MDA43

AE22

MDA42

AG23

MDA41

AH25

MDA40

AF25

MDA39

AJ28

MDA38

AJ29

MDA37

AF29

MDA36

AE26

MDA35

AJ27

MDA34

AH27

MDA33

AG29

MDA32

AF27

MDA31

E29

MDA30

E28

MDA29

D27

MDA28

C27

MDA27

G26

MDA26

F27

MDA25

C28

MDA24

E27

MDA23

F25

MDA22

E25

MDA21

E23

MDA20

D23

MDA19

E26

MDA18

C26

MDA17

G23

MDA16

F23

MDA15

E22

MDA14

E21

MDA13

F17

MDA12

G17

MDA11

G22

MDA10

F21

MDA9

G18

MDA8

E17

MDA7

G16

MDA6

E15

MDA5

G13

MDA4

H13

MDA3

H17

MDA2

E16

MDA1

E14

MDA0

G14

DQSA8

J28

-DQSA8

J27

DMA8

J25

MA_CK7

K25

MA_CK6

J26

MA_CK5

G28

MA_CK4

G27

MA_CK3

L24

MA_CK2

K27

MA_CK1

H29

MA_CK0

H27

MDA[0..63] {8}

B00P

B00N

MAAB[0..15]{8}

M2CPUC

M2CPUC

MEMORY INTERFACE B

AJ19

AK19

A18

A19

U31

U30

-CSB1

-CSB0

DCLKB0

-DCLKB0

-SCASB

-SWEB

-SRASB

SBAB2

SBAB1

SBAB0

CKEB1

CKEB0

MAAB15

MAAB14

MAAB13

MAAB12

MAAB11

MAAB10

MAAB9

MAAB8

MAAB7

MAAB6

MAAB5

MAAB4

MAAB3

MAAB2

MAAB1

MAAB0

DQSB7

-DQSB7

DQSB6

-DQSB6

DQSB5

-DQSB5

DQSB4

-DQSB4

DQSB3

-DQSB3

DQSB2

-DQSB2

DQSB1

-DQSB1

DQSB0

-DQSB0

DMB7

DMB6

DMB5

DMB4

DMB3

DMB2

DMB1

DMB0

AE30

AC31

AD29

AL19

AL18

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

M31

M29

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

C19

D19

N31

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

-CSB1{8}

-CSB0{8}

MODT_B0{8}

DCLKB0{8}

-DCLKB0{8}

-SCASB{8}

-SWEB{8}

-SRASB{8}

SBAB2{8}

SBAB1{8}

SBAB0{8}

CKEB1{8}

CKEB0{8}

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

-DQSB[0..8]

DQSB[0..8]

MB_CK[0..8]

DMB[0..8]

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

-DQSB[0..8] {8}

DQSB[0..8] {8}

MB_CK[0..8] {8}

DMB[0..8] {8}

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MDB63

MDB62

MDB61

MDB60

MDB59

MDB58

MDB57

MDB56

MDB55

MDB54

MDB53

MDB52

MDB51

MDB50

MDB49

MDB48

MDB47

MDB46

MDB45

MDB44

MDB43

MDB42

MDB41

MDB40

MDB39

MDB38

MDB37

MDB36

MDB35

MDB34

MDB33

MDB32

MDB31

MDB30

MDB29

MDB28

MDB27

MDB26

MDB25

MDB24

MDB23

MDB22

MDB21

MDB20

MDB19

MDB18

MDB17

MDB16

MDB15

MDB14

MDB13

MDB12

MDB11

MDB10

MDB9

MDB8

MDB7

MDB6

MDB5

MDB4

MDB3

MDB2

MDB1

MDB0

DQSB8

-DQSB8

DMB8

MB_CK7

MB_CK6

MB_CK5

MB_CK4

MB_CK3

MB_CK2

MB_CK1

MB_CK0

MDB[0..63] {8}

GIGABYTE

GIGABYTE

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

GIGABYTE

CPU DDRII MEMORY

CPU DDRII MEMORY

CPU DDRII MEMORY

GA-M68MT-S2

GA-M68MT-S2

GA-M68MT-S2

of

of

of

525Friday, November 05, 2010

525Friday, November 05, 2010

525Friday, November 05, 2010

1.35

1.35

1.35

-HTSTOP_L

BC19 150P/4/Y5V/16V/Z/XBC19 150P/4/Y5V/16V/Z/X

-CPURST

CPU_PWRGD

COREFB-{25}

COREFB+{25}

CPUVREF

40 MILS WIDTH

CPU_M_VREF

SBC31

SBC31

SBC12

SBC12

1N/4/X7R/50V/K

1N/4/X7R/50V/K

12

SC35

SC35

1u/6/Y5V/10V/Z

1u/6/Y5V/10V/Z

R21 300/4R21 300/4

R22 300/4R22 300/4

R23 300/4R23 300/4

BC8

BC8

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

DDR15V

SR19

SR19

16.9/4/1

16.9/4/1

SR20

SR20

16.9/4/1

16.9/4/1

DDR15V

VDDA25

2.5V/0.25A

CPUCLK0_H{9}

CPUCLK0_L{9}

C3

C3

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

CPUCLK0_H

CPUCLK0_L

3.9n/4/X7R/50V/K

3.9n/4/X7R/50V/K

3.3n/4/X7R/50V/K

3.3n/4/X7R/50V/K

C1

C1

3.9n/4/X7R/50V/K

3.9n/4/X7R/50V/K

C2

C2

DDR15V

CPU_M_VREF

DDR15V

R169 300/4/XR169 300/4/X

R170 300/4R170 300/4

R168 1K/4/1R168 1K/4/1

GNDA{18}

TMPIN3{18,20}

C13

C13

CLKIN_H

R5

CLKIN_L

169/4/1R5169/4/1

CPU_PWRGD{9}

-HTSTOP_L{9}

-CPURST{9}

R17 300/4R17 300/4

R19 300/4R19 300/4

CPU_TCK{12}

CPU_TMS{12}

R11 39.2/4/1R11 39.2/4/1

R12 39.2/4/1R12 39.2/4/1

R13 300/4R13 300/4

R14 300/4R14 300/4

CPU_TEST15

CPU_TEST14

CPU_TEST12

C4

C4

0.22u/6/X7R/16V/K

0.22u/6/X7R/16V/K

CPU_PWRGD

-HTSTOP_L

-CPURST

CPU_PRESENT_L

COREFB+{25}

COREFB-{25}

TP89TP89

TP91TP91

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TEST25_H

CPU_TEST25_L

CPU_TDI{12}

R15 0/4/SHT/XR15 0/4/SHT/X

R16 0/4/SHT/XR16 0/4/SHT/X

DDR15V

M2CPUD

M2CPUD

MISC

C10

D10

A8

B8

C9

D8

C7

AL3

SIC

AL6

SID

AK6

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/15u/[10SC1-A01941-04R_10SC1-A01941-05R]

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

THERMTRIP_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

D2

D1

C1

1

E3

1

E2

E1

AK7

AL7

AK10

B6

AK11

AL11

F1

R53 44.2/4/1R53 44.2/4/1

V8

R54 44.2/4/1R54 44.2/4/1

V7

R55 80.6/4/1/XR55 80.6/4/1/X

C11

D11

CPU_TEST24

AK8

AH8

CPU_TEST22

AJ9

CPU_TEST21

AL8

CPU_TEST20

AJ8

J10

H9

CPU_TEST27

AK9

CPU_TEST26

AK5

G7

D4

LAYOUT: Route trace 50 mils wide and

500 to 750 mils long between these caps.

R59

R59

1K/4/1

1K/4/1

R65

R65

R57

R57

1K/4/1

1K/4/1

300/4

300/4

VCC12_HT

R174 1K/4/1R174 1K/4/1

R39 1K/4/1R39 1K/4/1

R47 300/4R47 300/4

R175 1K/4/1R175 1K/4/1

R33 300/4R33 300/4

R37 300/4R37 300/4

L1117LG/N/SOT223/1A

R60

R60

300/4

300/4

L1117LG/N/SOT223/1A

THERMTRIP_L

-PROCHOT

Q41

Q41

3

2

VDDA25 VDDA25

4

1.25(1+100/100)=2.5

VID3 {25}

VID2 {25}

VID1 {25}

VID0 {25}

THERMTRIP_L {9}

-PROCHOT {9}

1

R341

R341

100/4/1

100/4/1

R344

R344

100/4/1

100/4/1

Route as 80-Ohm differential impedance

Keep trace to resistor less than 1" from CPU pin

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

DDR15V

DDR15V

1

1

+

+

EC40

EC40

100u/D/10V/57

100u/D/10V/57

BC136

BC136

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

VCC

BC303

BC303

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

VDDA25

BC1

BC1

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

R49 1K/4/1/XR49 1K/4/1/X

R42 510/4/1R42 510/4/1

R43 510/4/1R43 510/4/1

DDR15V

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

M2CPUE

M2CPUE

INTERNAL MISC

INTERNAL MISC

L25

RSVD1

L26

RSVD2

L31

RSVD3

L30

RSVD4

W26

DCLKA2

AM3 only

DCLKA1{8}

-DCLKA1{8}

MODT_A1{8}

DCLKA1

-DCLKA1

MODT_A1

AM3 only

DCLKB1{8}

-DCLKB1{8}

MODT_B1{8}

DCLKB1

-DCLKB1

MODT_B1 MA_EVENT_L

W25

AE27

AE28

AG31

W31

AF31

DCLKA2MODT_A3

U24

DCLKA1

V24

DCLKA1MODT_A1

Y31

DCLKB2

Y30

DCLKB2MODT_B3

V31

DCLKB1

DCLKB1MODT_B1

MA_RESETMB_RESET-

RSVD19

RSVD20

RSVD21

RSVD22

M_VDDIO_PWRGD

COREFB_NB+

COREFB_NB-

CORE_TYP_DET

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

MB_EVENT_L

MA_EVENT_L

AM3 only

MA_RESET_L

E20

MB_RESET_L

B19

AL4

AK4

AK3

F2

F3

G4

G3

CORE_TYPE_DET

G5

AD25

AM2: high, AM2R2: low

AE24

AE25

AJ18

AJ20

C18

C20

AM3 =>DRAM Thermal Event Status

G24

R103 1K/4/1R103 1K/4/1

G25

H25

MB_EVENT_L

V29

W30

R102 1K/4/1R102 1K/4/1

MA_RESET_L {8}

MB_RESET_L {8}

DDR15V

MB_EVENT_L {8}

MA_EVENT_L {8}

DDR15V

EVENT pins are for future AM3r2

R86 1K/4/1R86 1K/4/1

DDR15V

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

GIGABYTE

GIGABYTE

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

GIGABYTE

CPU CONTROL

CPU CONTROL

CPU CONTROL

GA-M68MT-S2

GA-M68MT-S2

GA-M68MT-S2

of

of

of

625Friday, November 05, 2010

625Friday, November 05, 2010

625Friday, November 05, 2010

1.35

1.35

1.35

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

AA10

AA12

AA14

AA16

AA18

AB11

AC10

AE10

AA8

AB7

AB9

AC4

AC5

AC8

AD2

AD3

AD7

AD9

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

G10

G12

H11

H23

K11

K13

K15

K17

K19

K21

K23

Y17

Y19

VCORE_NB

VLDT_RUN_B is connected to the VLDT_RUN power

supply through the package or on the die. It is only connected

M2CPUF

M2CPUF

VDD1

VDD1

A4

VDD1

A6

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

VDD49

VDD50

H7

VDD51

VDD52

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

VDD150

VDD151

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

GND

VCORE

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

P11

P13

P15

P17

P19

R10

R12

R14

R16

R18

R20

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

V21

W10

W12

W14

W16

W18

W20

Y11

Y13

Y15

Y21

VCORE

M2CPUH

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

M21

M23

N20

N22

P21

P23

R22

U22

V23

W22

Y23

H20

AE7

M2CPUH

VDD3

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

T23

VDD28

VDD29

VDD30

VDD31

VDD32

B2

NB/RSVD

NP/VSS1

NP/VSS2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

GND

M2CPUG

M2CPUG

VDD2

L14

L16

L18

T11

T13

T15

T17

T19

T21

VDD2

VDD1

VDD2

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

N8

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

P7

VDD19

P9

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

U8

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

V9

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

VDD72

VDD73

VDD74

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

GND

on the board to decoupling near the CPU package.

M2CPUI

M2CPUI

VDDIO

VCC12_HT

VCC12_HT

DDR15V

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

P24

P26

P28

P30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VDDR_4

VDDR_3

VDDR_2

VDDR_1

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO29

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

T24

T26

T28

T30

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDR_9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AG12

AH12

AJ12

AK12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

VCC12_HT

BUTTOM SIDE

VCORE

SC16

SC16

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

VCORE

SC24

SC24

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC17

SC17

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

GND

SC25

SC25

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

GND

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC18

SC18

SC26

SC26

SC19

SC19

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

SC27

SC27

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

HT12B

BC795

BC795

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

SC20

SC20

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC28

SC28

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

DDR15V

DDR15V

VCORE

SC11

SC11

0.22u/6/X7R/16V/K

0.22u/6/X7R/16V/K

SC21

SC21

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

SC29

SC29

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

C1343

C1343

C1344

C1344

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

1U/6/Y5V/10V/Z

1U/6/Y5V/10V/Z

GND

SC2

SC2

0.22u/6/X7R/16V/K

0.22u/6/X7R/16V/K

SC9

SC9

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

BUTTOM SIDE

SC12

SC12

0.22u/6/X5R/10V/K/X

0.22u/6/X5R/10V/K/X

GND

SC22

SC22

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC30

SC30

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC10

SC10

SC13

SC13

0.22u/6/X5R/10V/K/X

0.22u/6/X5R/10V/K/X

SC23

SC23

22u/8/X5R/6.3V/M/X

22u/8/X5R/6.3V/M/X

C1345

C1345

C1342

C1342

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

0.01u/4/X7R/25V/K

0.01u/4/X7R/25V/K

BUTTOM SIDE

SC4

SC4

SC5

SC5

0.01u/6/X7R/25V/K/X

0.01u/6/X7R/25V/K/X

0.22u/6/X5R/10V/K/X

0.22u/6/X5R/10V/K/X

SC8

SC8

SC7

SC7

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z/X

4.7u/8/Y5V/10V/Z/X

SC14

SC14

0.01u/6/X7R/25V/K/X

0.01u/6/X7R/25V/K/X

C1346

C1346

180P/4/NPO/50V/J

180P/4/NPO/50V/J

SC6

SC6

180P/6/NPO/50V/J

180P/6/NPO/50V/J

SC31

SC31

180P/6/NPO/50V/J/X

180P/6/NPO/50V/J/X

SC15

SC15

180P/6/NPO/50V/J

180P/6/NPO/50V/J

VCC12_HT

C1330

C1330

0.22u/6/X7R/16V/K

0.22u/6/X7R/16V/K

GND

C1331

C1331

0.22u/6/X7R/16V/K

0.22u/6/X7R/16V/K

C1332

C1332

180P/6/NPO/50V/J

180P/6/NPO/50V/J

C1333

C1333

180P/6/NPO/50V/J

180P/6/NPO/50V/J

DDR15V

C1324

C1324

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

C1325

C1325

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

GND

VCC12_HT

C1316

C1316

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

VCC12_HT

C1334

C1334

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

C1317

C1317

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

GND

C1335

C1335

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

GND

C1336

C1336

0.22u/6/X7R/16V/K

0.22u/6/X7R/16V/K

C1319

C1319

0.22u/6/X7R/16V/K

0.22u/6/X7R/16V/K

1n/6/X7R/50V/K

1n/6/X7R/50V/K

1n/6/X7R/50V/K

1n/6/X7R/50V/K

C1320

C1320

C1338

C1338

C1321

C1321

1n/6/X7R/50V/K

1n/6/X7R/50V/K

C1339

C1339

1n/6/X7R/50V/K

1n/6/X7R/50V/K

180P/6/NPO/50V/J

180P/6/NPO/50V/J

C1322

C1322

180P/6/NPO/50V/J

180P/6/NPO/50V/J

C1340

C1340

C1323

C1323

180P/6/NPO/50V/J

180P/6/NPO/50V/J

C1341

C1341

180P/6/NPO/50V/J

180P/6/NPO/50V/J

GIGABYTE

GIGABYTE

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

GIGABYTE

CPU POWER & GND

CPU POWER & GND

CPU POWER & GND

GA-M68MT-S2

GA-M68MT-S2

GA-M68MT-S2

of

of

of

725Friday, November 05, 2010

725Friday, November 05, 2010

725Friday, November 05, 2010

1.35

1.35

1.35

8

DDRVTT

MODT_A[0..3]

-DQSA[0..8]

D D

DQSA[0..8]

DMA[0..8]

MA_CK[0..7]

MEM_SMBDATA

C C

MEM_SMBCLK

VCC3

B B

A A

MODT_A[0..3] {5,6}

-DQSA[0..8] {5}

DQSA[0..8] {5}

DMA[0..8] {5}

MA_CK[0..7] {5}

D3

D3

2

3

1

3VDUAL

BAV99/SOT23/300mA

BAV99/SOT23/300mA

SOT23

SOT23

D4

D4

2

3

1

3VDUAL

BAV99/SOT23/300mA

BAV99/SOT23/300mA

SOT23

SOT23

C275 0.1u/4/Y5V/16V/ZC275 0.1u/4/Y5V/16V/Z

C283 0.1u/4/Y5V/16V/ZC283 0.1u/4/Y5V/16V/Z

C282 0.1u/4/Y5V/16V/ZC282 0.1u/4/Y5V/16V/Z

MEM_SMBCLK{14}

MEM_SMBDATA{14}

SBAA2{5}

SBAA1{5}

SBAA0{5}

CKEA1{5}

CKEA0{5}

-CSA1{5}

-CSA0{5}

-DCLKA1{6}

DCLKA1{6}

-DCLKA0{5}

DCLKA0{5}

MAAA[0..15]{5}

MA_RESET_L{6}

-SCASA{5}

-SRASA{5}

-SWEA{5}

8

DDR15V

VREFCA_A

VREFDQ_A

MEM_SMBCLK

MEM_SMBDATA

SBAA2

SBAA1

SBAA0

CKEA1

CKEA0

-CSA0

-DCLKA1

DCLKA1

-DCLKA0

DCLKA0

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

MA_RESET_L

-SCASA

-SRASA

-SWEA

7

DDR3_1

DDR3_1

120

VTT

240

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

7

6

FREE

FREE

FREE

FREE

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

DQS0

DQS0*

DQS1

DQS1*

DQS2

DQS2*

DQS3

DQS3*

DQS4

DQS4*

DQS5

DQS5*

DQS6

DQS6*

DQS7

DQS7*

DQS8

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DDR3/240/BU/VA/D

DDR3/240/BU/VA/D

6

5

BC4

BC4

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

BC5

BC5

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

BC6

BC6

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

VREFDQ_A

VREFCA_A

Trace min 10/10

MEM_SMBCLK{14}

MEM_SMBDATA{14}

-DCLKB1{6}

DCLKB1{6}

-DCLKB0{5}

DCLKB0{5}

MAAB[0..15]{5}

MB_RESET_L{6}

-SCASB{5}

-SRASB{5}

SBAB2{5}

SBAB1{5}

SBAB0{5}

CKEB1{5}

CKEB0{5}

-CSB1{5}

-CSB0{5}

-SWEB{5}

DDRVTT

DDR15V

VCC3

48

49

MA_EVENT_L

187

198

79

77

195

68

53

167

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

MODT_A1

MODT_A0

MA_CK0

MA_CK1

MA_CK2

MA_CK3

MA_CK4

MA_CK5

MA_CK6

MA_CK7

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DQSA8

-DQSA8

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MA_EVENT_L {6}

MODT_A1 {6}

MODT_A0 {5}

DDR15V Decouple

DDR15V

DDR15V

R101

R101

15/4/1

15/4/1

VREFDQ_A

Trace min 10/10

R66

R66

15/4/1

15/4/1

DDR15V

R68

R68

15/4/1

15/4/1

VREFCA_A

R10

R10

15/4/1

15/4/1

MDA[0..63] {5}

VCC3

C284 0.1u/4/Y5V/16V/ZC284 0.1u/4/Y5V/16V/Z

C285 0.1u/4/Y5V/16V/ZC285 0.1u/4/Y5V/16V/Z

5

VREFCA_A

VREFDQ_A

MEM_SMBCLK

MEM_SMBDATA

SBAB2

SBAB1

SBAB0

CKEB1

CKEB0

-CSB1

-CSB0

-DCLKB1

DCLKB1

-DCLKB0

DCLKB0

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

MAAB14

MAAB15

MB_RESET_L

-SCASB

-SRASB

-SWEB

4

DDR3_2

DDR3_2

120

VTT

240

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

4

3

DDR3/240/BU/VA/D

DDR3/240/BU/VA/D

3

FREE

FREE

FREE

FREE

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

DQS0

DQS0*

DQS1

DQS1*

DQS2

DQS2*

DQS3

DQS3*

DQS4

DQS4*

DQS5

DQS5*

DQS6

DQS6*

DQS7

DQS7*

DQS8

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

2

48

49

MB_EVENT_L

187

198

79

MODT_B1

77

MODT_B0

195

68

53

167

MB_CK0

39

CB0

MB_CK1

40

CB1

MB_CK2

45

CB2

MB_CK3

46

CB3

MB_CK4

158

CB4

MB_CK5

159

CB5

MB_CK6

164

CB6

MB_CK7

165

CB7

DQSB0

7

-DQSB0

6

DQSB1

16

-DQSB1

15

DQSB2

25

-DQSB2

24

DQSB3

34

-DQSB3

33

DQSB4

85

-DQSB4

84

DQSB5

94

-DQSB5

93

DQSB6

103

-DQSB6

102

DQSB7

112

-DQSB7

111

DQSB8

43

-DQSB8

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

MDB0

3

DQ0

MDB1

4

DQ1

MDB2

9

DQ2

MDB3

10

DQ3

MDB4

122

DQ4

MDB5

123

DQ5

MDB6

128

DQ6

MDB7

129

DQ7

MDB8

12

DQ8

MDB9

13

DQ9

MDB10

18

MDB11

19

MDB12

131

MDB13

132

MDB14

137

MDB15

138

MDB16

21

MDB17

22

MDB18

27

MDB19

28

MDB20

140

MDB21

141

MDB22

146

MDB23

147

MDB24

30

MDB25

31

MDB26

36

MDB27

37

MDB28

149

MDB29

150

MDB30

155

MDB31

156

MDB32

81

MDB33

82

MDB34

87

MDB35

88

MDB36

200

MDB37

201

MDB38

206

MDB39

207

MDB40

90

MDB41

91

MDB42

96

MDB43

97

MDB44

209

MDB45

210

MDB46

215

MDB47

216

MDB48

99

MDB49

100

MDB50

105

MDB51

106

MDB52

218

MDB53

219

MDB54

224

MDB55

225

MDB56

108

MDB57

109

MDB58

114

MDB59

115

MDB60

227

MDB61

228

MDB62

233

MDB63

234

MB_EVENT_L {6}

MODT_B1 {6}

MODT_B0 {5}

-DQSB[0..8]

DQSB[0..8]

DMB[0..8]

MODT_B[0..3]

MB_CK[0..7]

DDR15V Decouple

DMB0

DMB1

DMB2

DMB3

DMB4

DMB5

DMB6

DMB7

DMB8

DDR15V

DDRVTT

BC131

BC131

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

BC129

BC129

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

BC125

BC125

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

DDRVTT

BC118

BC118

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

BC9 1U/6/Y5V/10V/ZBC9 1U/6/Y5V/10V/Z

MDB[0..63] {5}

DDRVTT Decouple

DDRVTT

BC149

BC149

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

GIGABYTE

GIGABYTE

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

GIGABYTE

DDRII CHANNEL A

DDRII CHANNEL A

DDRII CHANNEL A

GA-M68MT-S2 1.35

GA-M68MT-S2 1.35

GA-M68MT-S2 1.35

-DQSB[0..8] {5}

DQSB[0..8] {5}

DMB[0..8] {5}

MODT_B[0..3] {5,6}

MB_CK[0..7] {5}

1

825

825

825

of

of

of

1

Loading...

Loading...