Page 1

Gigabyte confidential

GA-M55plus-S3G

Digitally signed by dd

DN: cn=dd, o=dd,

ou=dd,

email=dddd@yahoo.

com, c=US

Date: 2009.12.17

19:06:51 +07'00'

www.kythuatvitinh.com

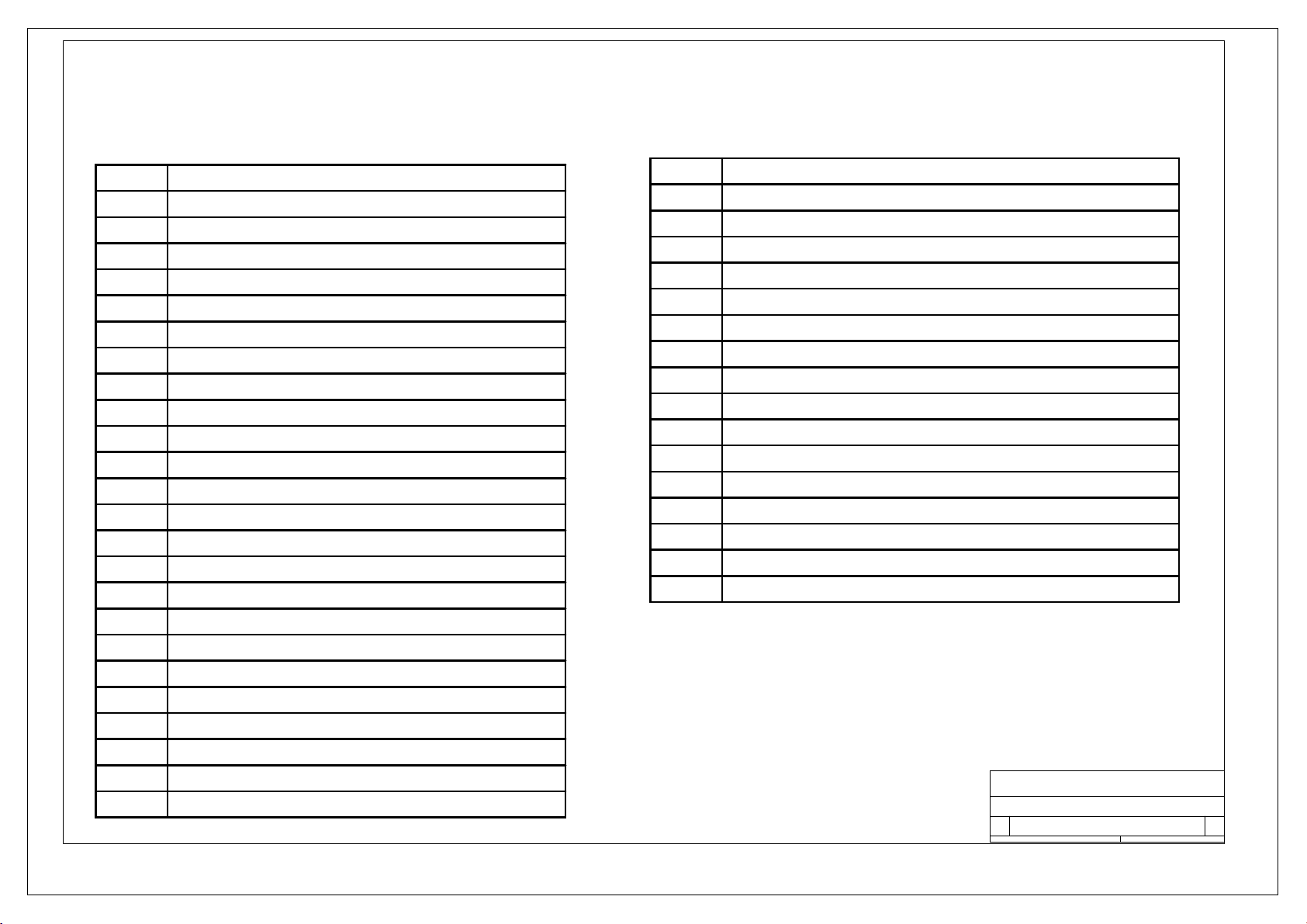

SHEET

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

TITLE

COVER SHEET

BOM & PCB MODIFY HISTORY

BLOCK DIAGRAM

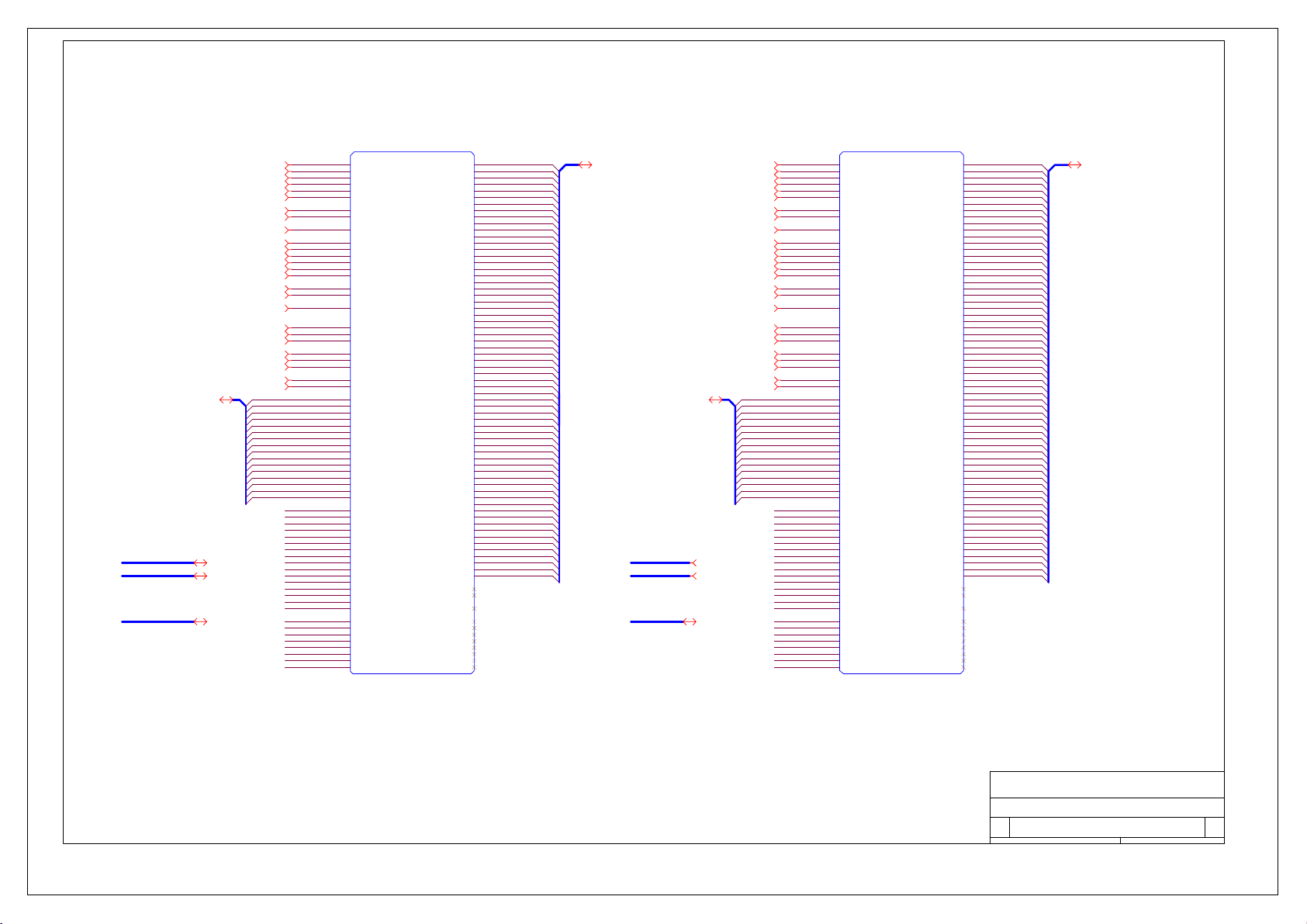

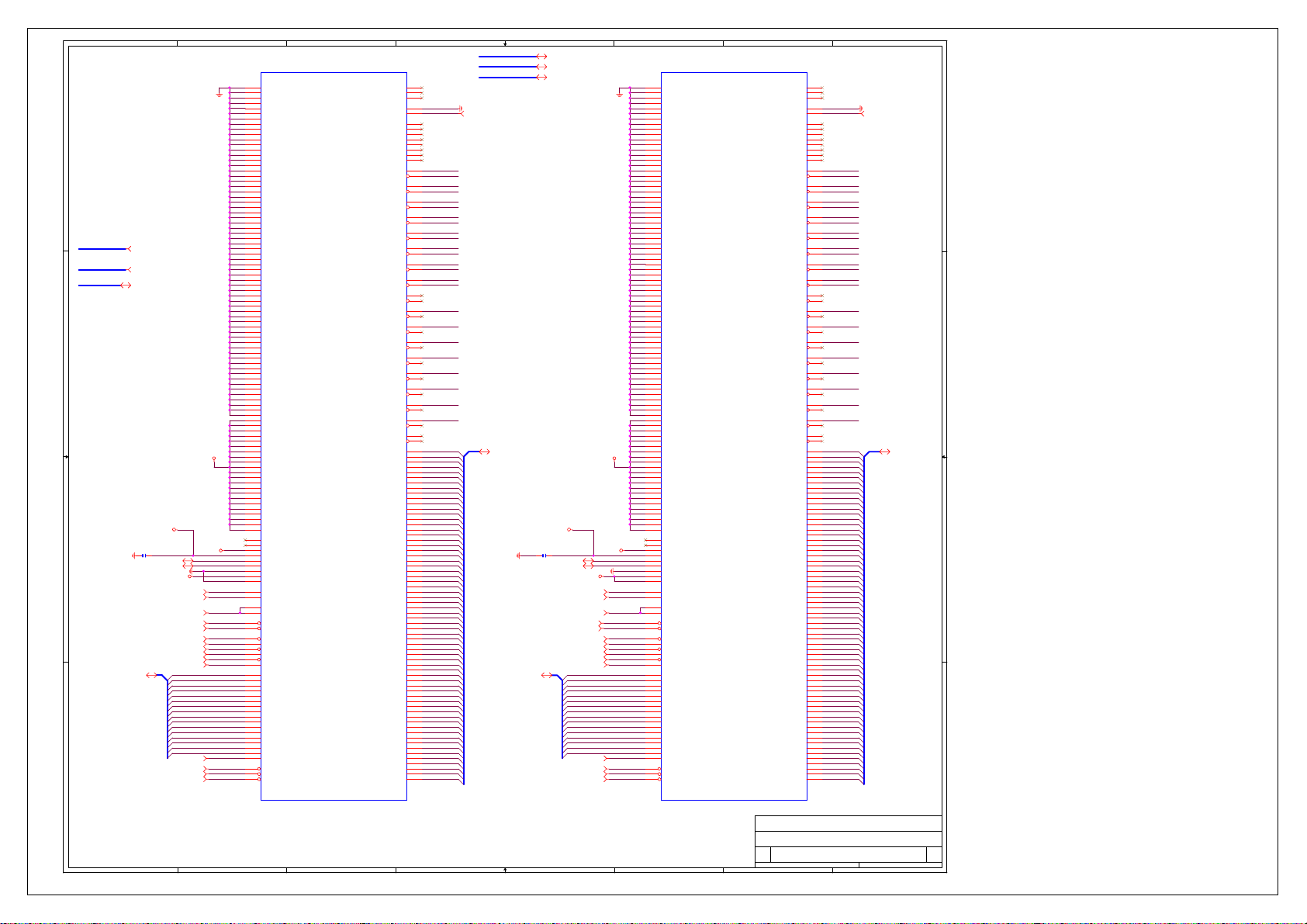

PROCESSOR HT INTERFACE

PROCESSOR DDR2 INTERFACE

PROCESSOR DDR2 INTERFACE

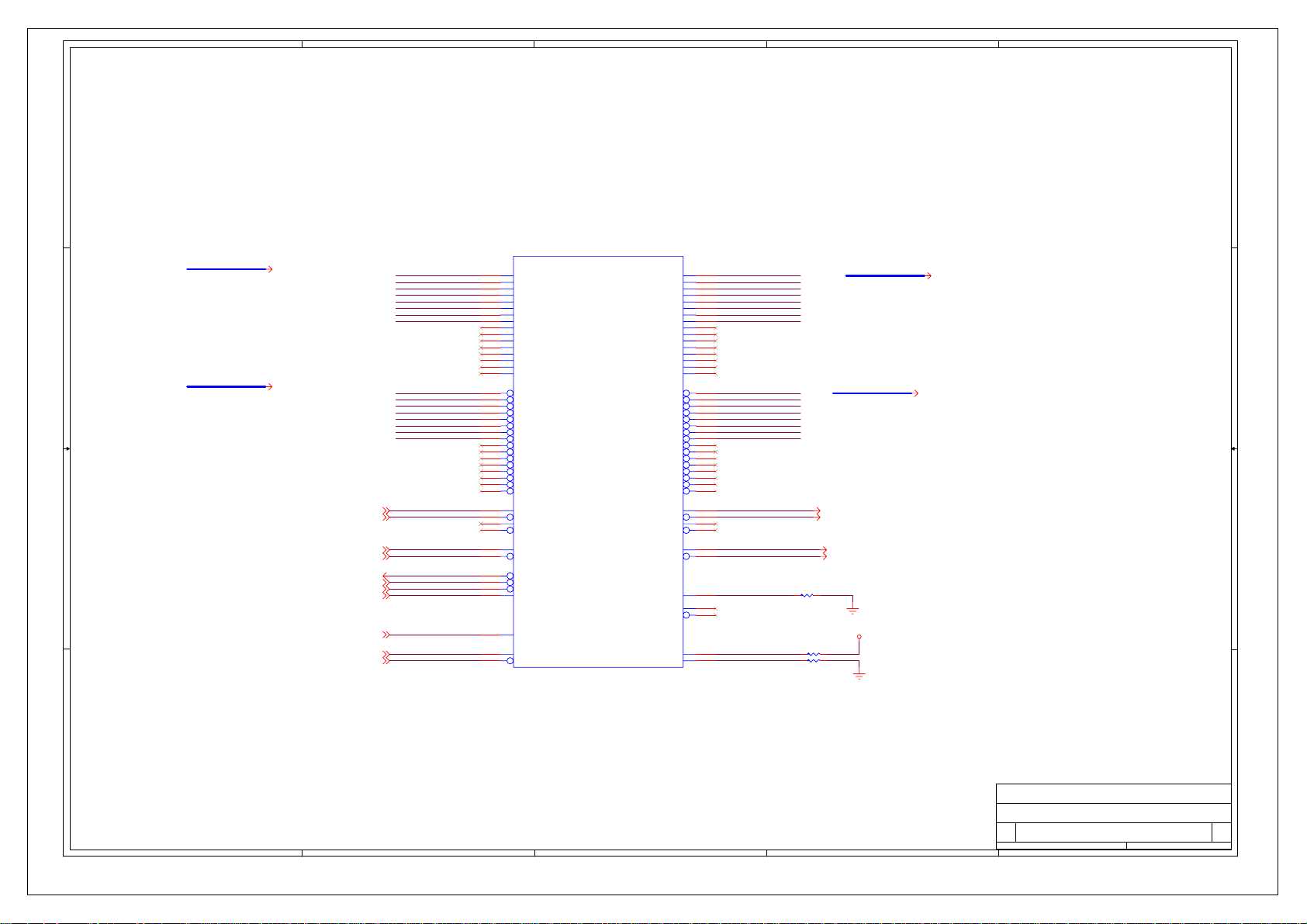

PROCESSOR CONTROL & DEBUG

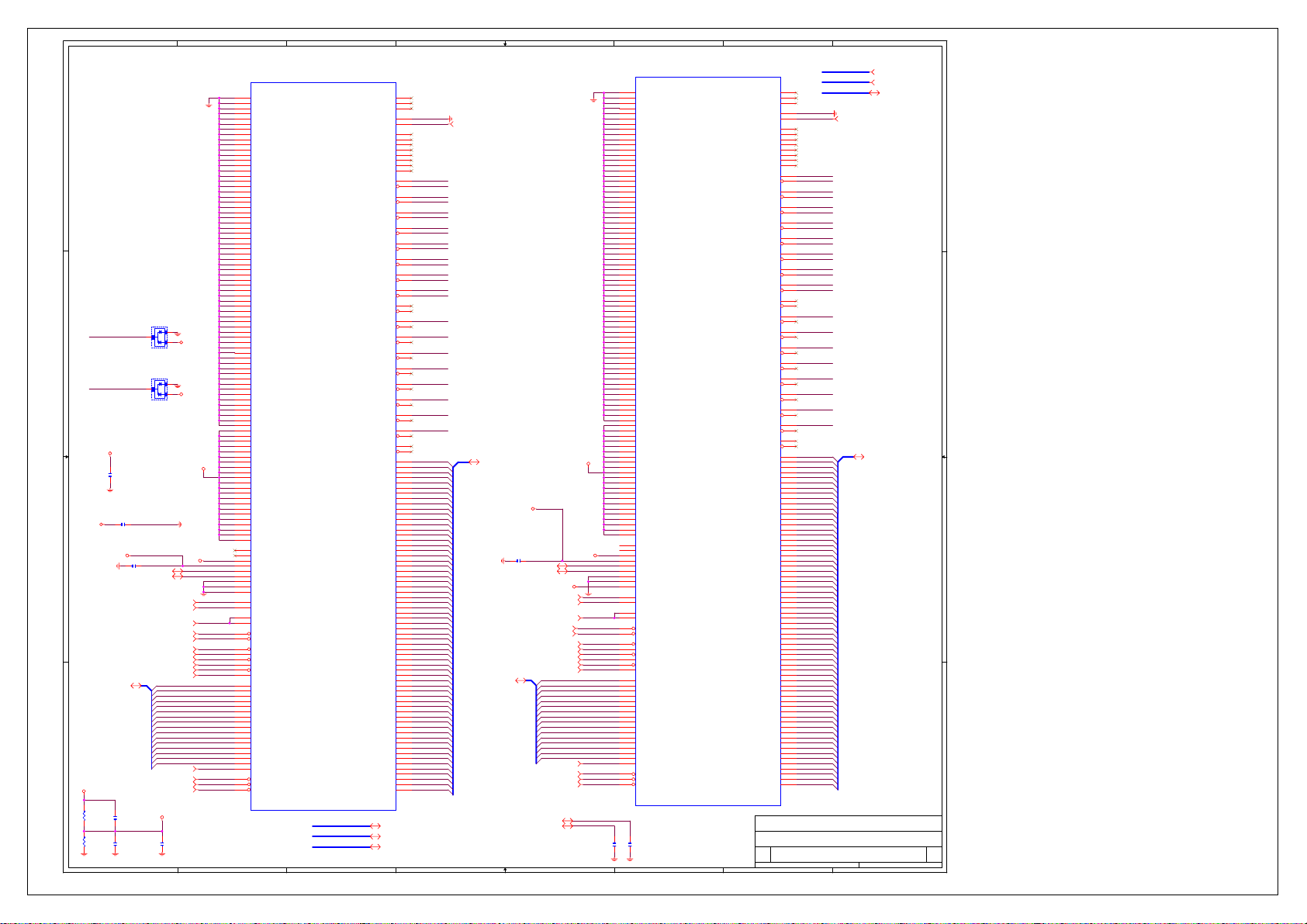

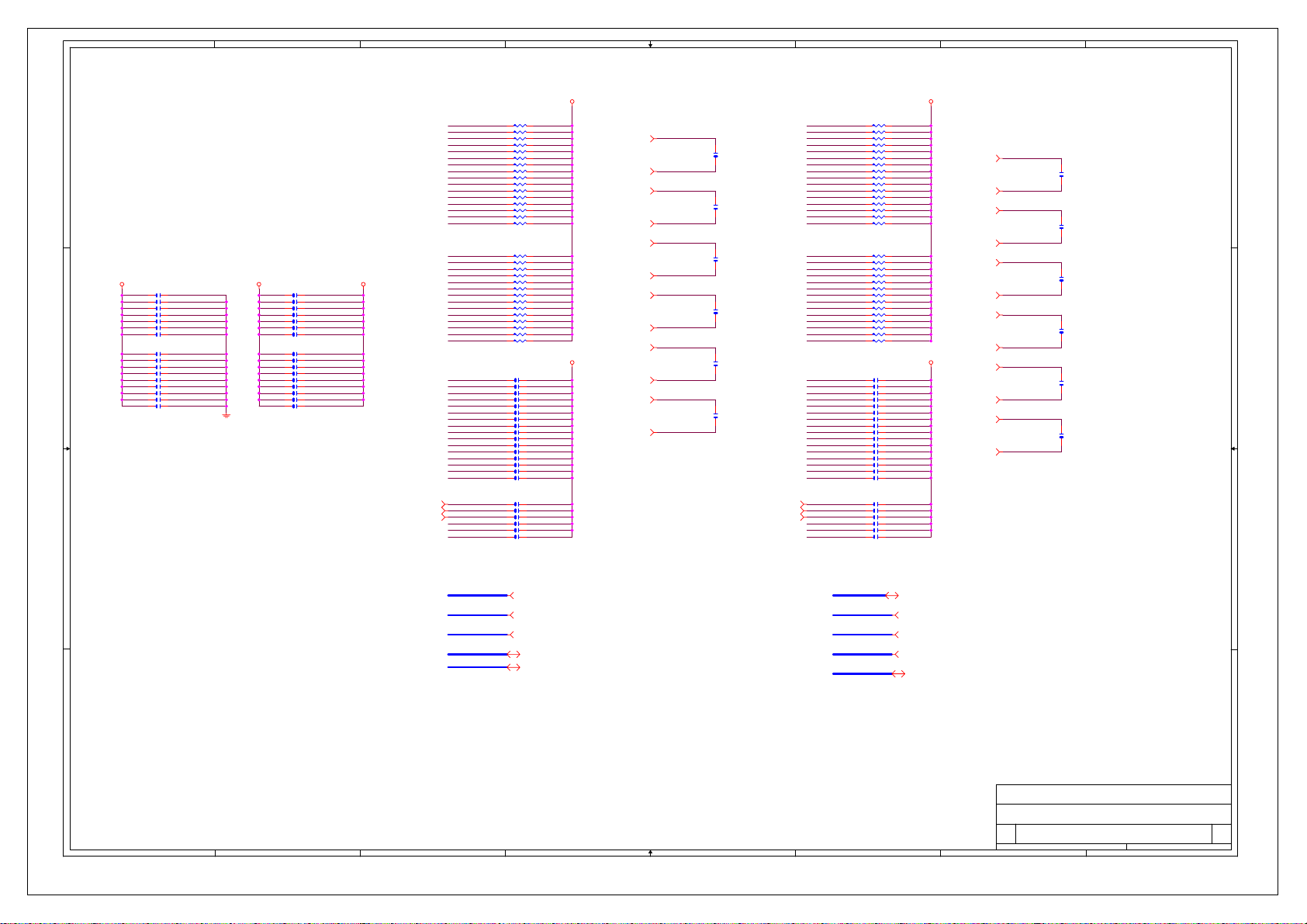

DIMM 1,2

DIMM 3,4

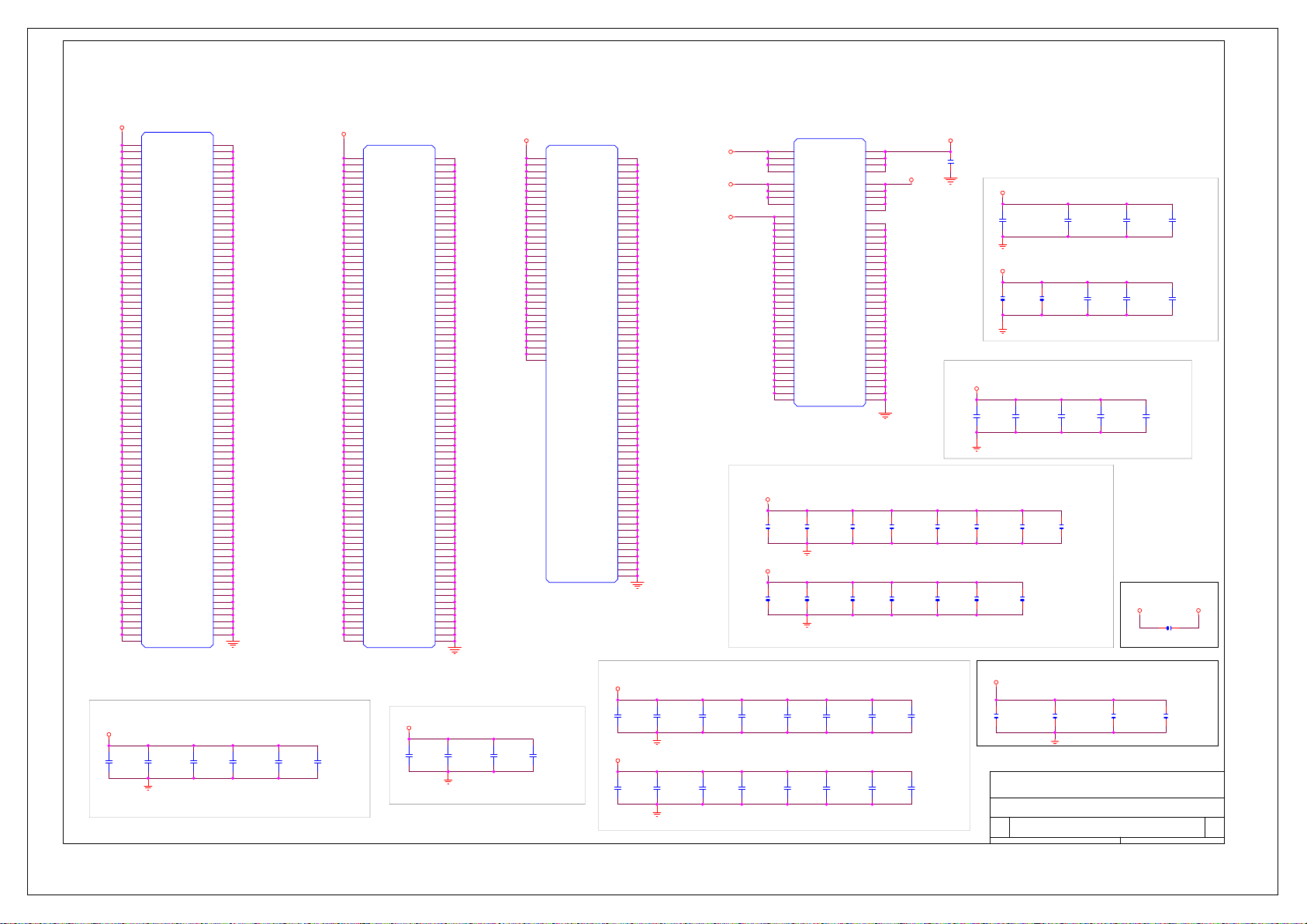

DIMM TERMINATION

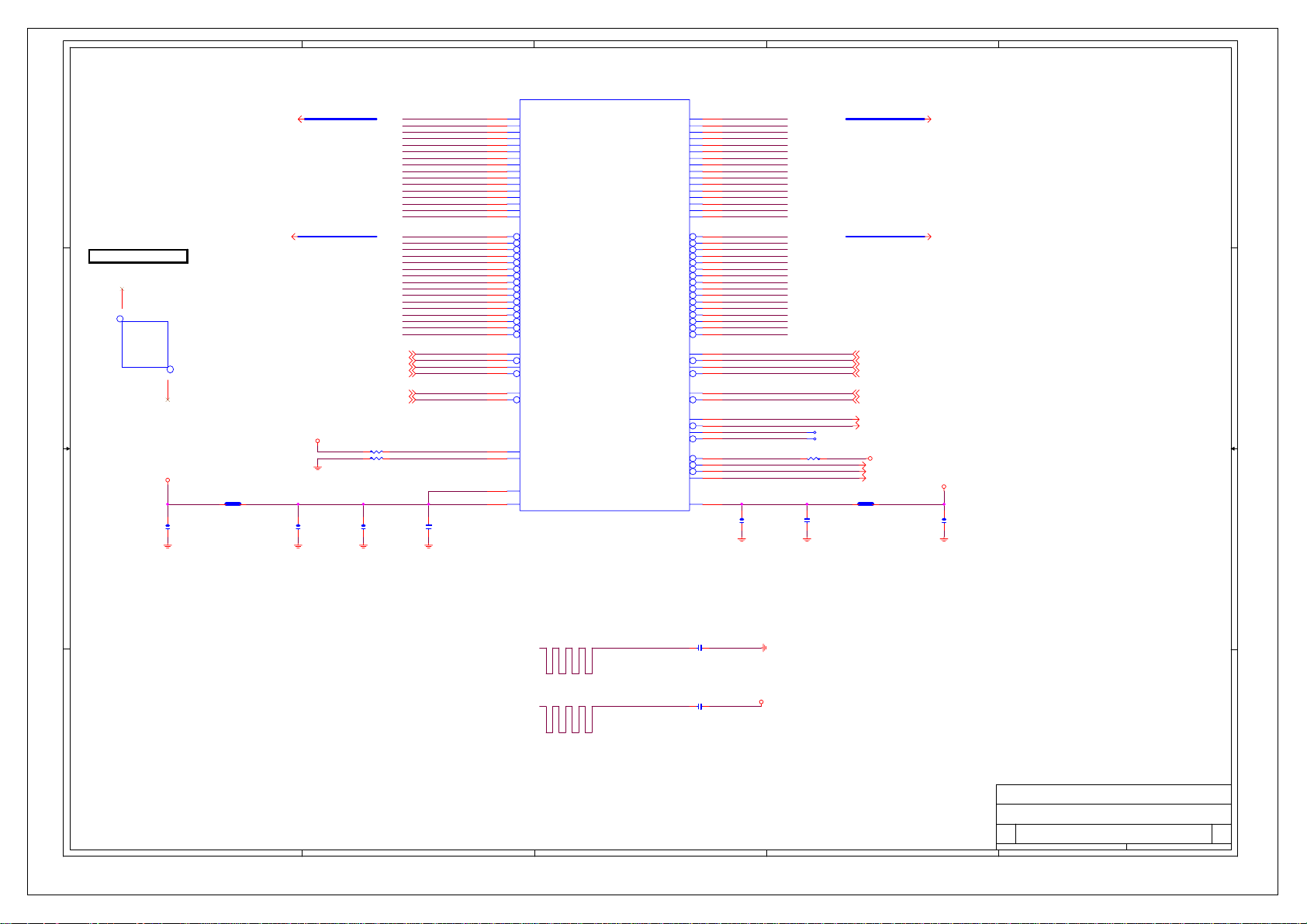

C51 CPU

C51 HT

C51 PCI-EXPRESS

C51 RGB

C51 PWR/GND

MCP51 HT BUS

MCP51 PCI BUS/CLOCK/RESET

MCP51 SATA/IDE

MCP51 AZILIA/USB

MCP51 RGMII

MCP51 PWR/GND

PCI EXPRESS X16 SLOT

F_USB1/F_USB2 CONN /PCI_E x1 SLOT

PCI 1,2,3 SLOT

PCI 4 SLOT

SHEET

26

27

28

29

30

31

32

33

34

34

35

36

37

38 TI TSB43AB23 1394

TITLE

CODEC ALC883

AUDIO JACK, L_OUT, F_AUDIO

H/W MONITOR & FAN CONTROL

IDE1/IDE2/FDD

PWM ISL6566

COMA, LPT PORT

DDR18V,DDRVTT,5VDAUL,VCC12, POWER

POWER SEQUENCE

BIOS ATX POWER CONNCTOR

FRONT PANEL

ITE 8716GB/CX

Marvell 88E1116

Revision:1.2

Title

Size Document Number Re v

Custom

Date: Sheet

GIGABYTE

BLOCK DIAGRAM

GA-M55plus-S3G

138Thursday, July 06, 2006

of

1.2

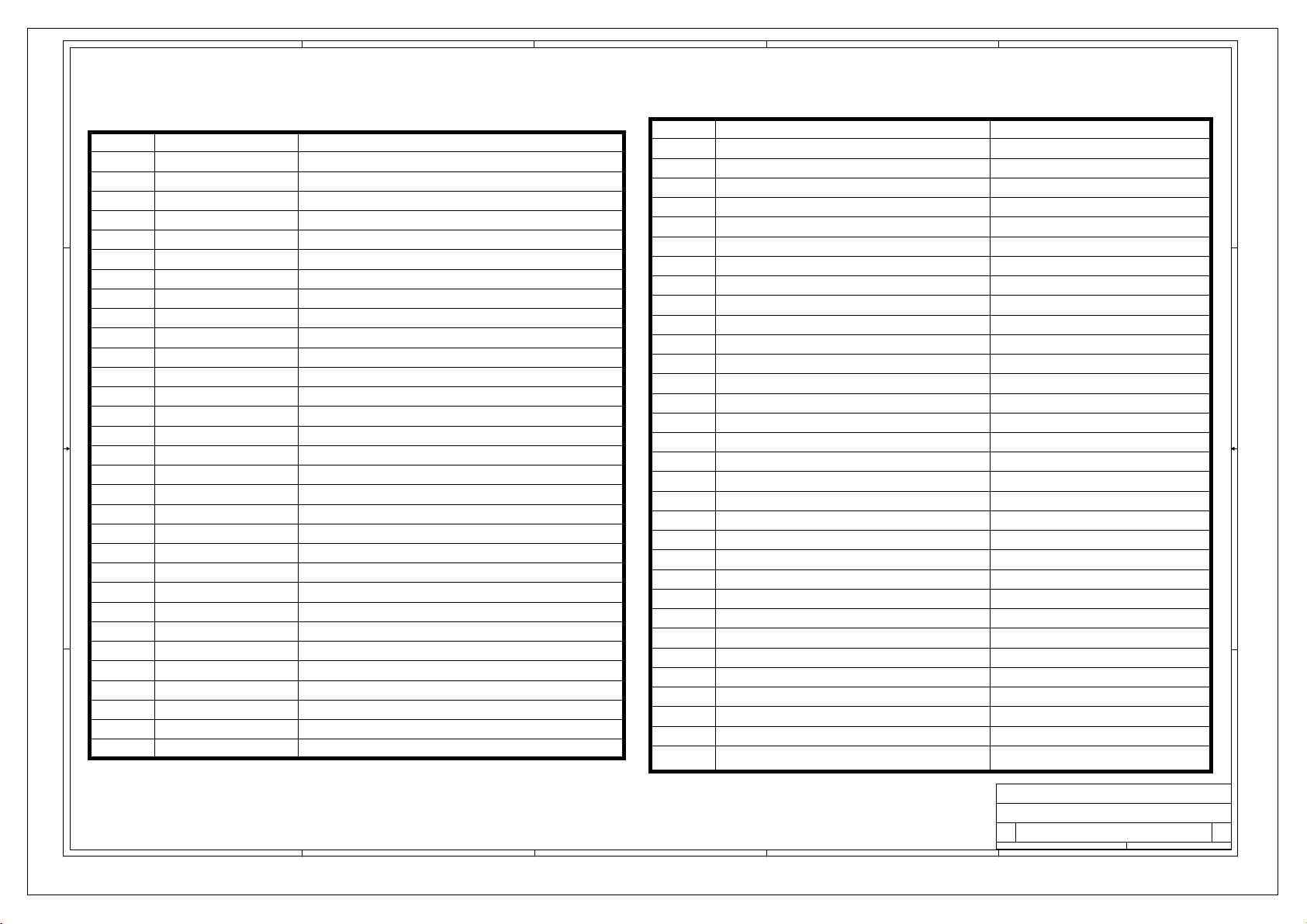

Page 2

Gigabyte confidential

5

www.kythuatvitinh.com

Model Name:GA-M55plus-S3G

4

3

2

1

Circuit or PCB layout change for next version

Date Change Item Reason

2006.03.17

2006.04.14

2006.06.06

2006.06.13

0.1 Gerber Out

1.0 Gerber Out

1.1 Gerber Out Modify DVI I2C PU ,74LVC08A change to SOIC

1.2 Gerber Out Change VDDA25 generate method.

Rename to GA-M55plus-S3G

BC7 for EMI

Version:1.2

P-Code:

Component value change history

Date Change Item Reason

D D

2006.03.22

2006.04.18 1.0A D_BOM Release. PCB:1.0

2006.05.02 RM change to o range. PCIE x16 change to blue. 11AC1-021164-81R

2006.05.08 1.0B ECN Release. PCB:1.0 Add VGA cap: 12PC1-V00001-01R, and Q74 2n d s o u r ce .

2006.06.07 1.1A E_BOM Release. PCB:1.1 Modify DVI I2C PU ,74LVC08A change to SOIC

2006.06.12 1.2A E_BOM Release. PCB:1.2 Change VDDA25 generate method.

2006.06.28 1.2A P_BOM Release. PCB:1.2 For PVT use. Add packing list.

C C

2006.07.06 1.2B P_BOM Release. PCB:1.2 Add ESD protect Diode. And combine repeat source.

B B

0.1 New BOM Release. PCB:0.1

1.0B P_BOM Release. PCB:1.0

LAN_USB re mov e 11NR6-702010-A1R

TPM no POP, Remove BIOS socket

Remove Power LED dua l col or sc hematic Add AMD Validation circuit

CPU fan speed. 15K-->8.2K Update new packing list

Remove BIOS socket

RM use plastic, F_PANEL use color

A A

Title

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

GIGABYTE

BOM & PCB MODIFY HISTORY

GA-M55plus-S3G

1

238Thursday, July 06, 2006

1.2

of

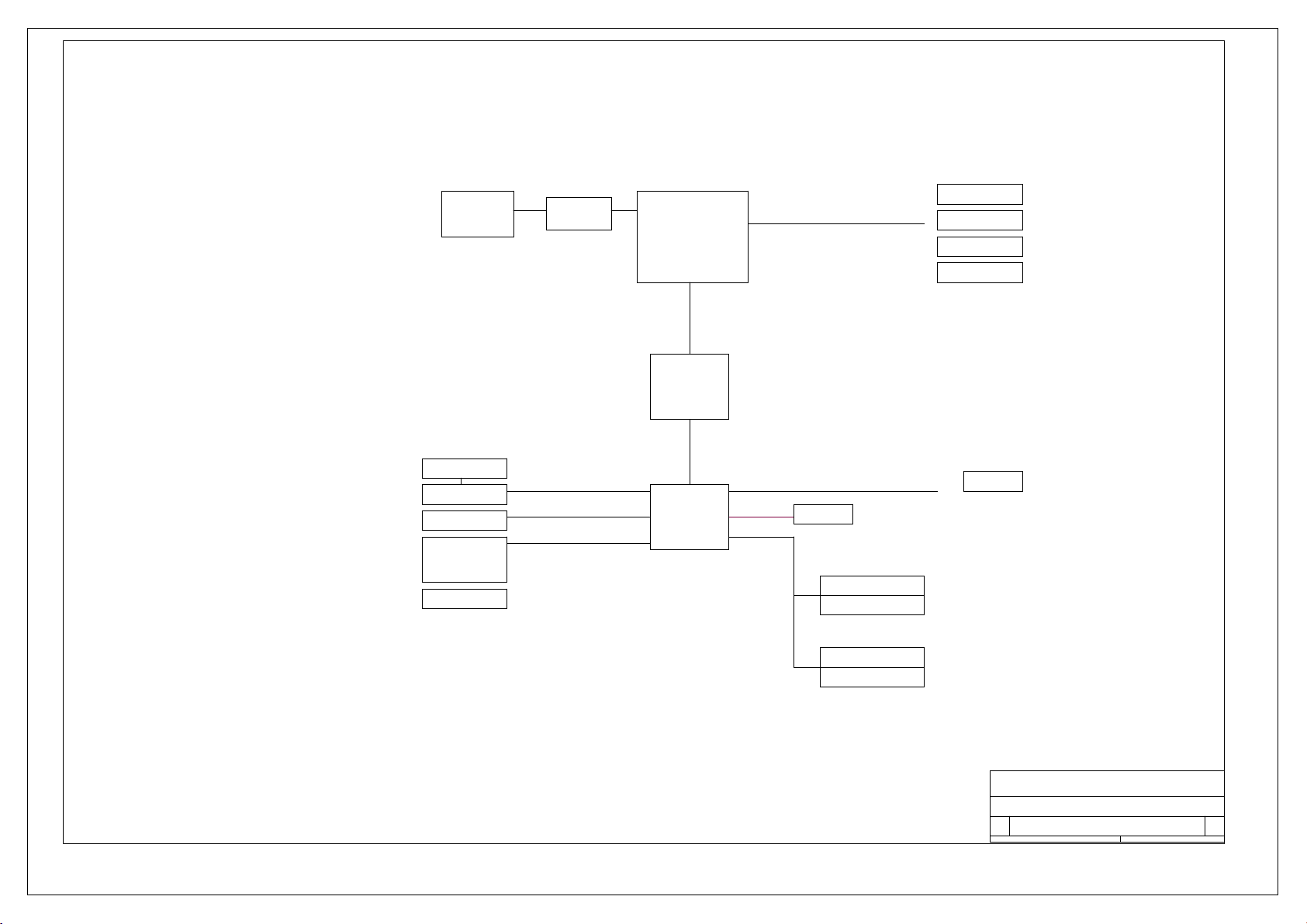

Page 3

Gigabyte confidential

BLOCK DIAGRAM

www.kythuatvitinh.com

POWER

SUPPLY

CONNECTOR

PRIMARY IDE

SECONDARY IDE

SATA2 CONN x4

FLOPPY CONN

PS2/KB CONN

PARALLEL CONN

SERIAL CONN 4MB FLASH

SIO

VREG

ATA 133

INTEGRATED SATA

LPC BUS 33MHZ

AMD K8 CPU

SOCKET AM2

HT 16X16 1GHZ

NVIDIA

C51G

HT 8X8 1GHZ

NVIDIA

MCP51

PCI 33MHZ

AZILIA

USB2.0 X8 PORT

128-BIT 200/266/333/400MHZ

RTL883 CODEC

BACK PANEL

USB2.0 PORTS 0-1

X2/1394

USB2.0 PORTS 2-3

X2/GBIT LAN

DDRII SDRAM CONN 1

DDRII SDRAM CONN 2

DDRII SDRAM CONN 3

DDRII SDRAM CONN 4

PCI SLOT 1

PCI SLOT 2

1L

1H

2L

2H

FRONT PANEL

USB2.0 PORTS 4-5

USB2.0 PORTS 6-7

Title

Size Document Number Re v

Custom

Date: Sheet

GIGABYTE

BLOCK DIAGRAM

GA-M55plus-S3G

338Thursday, July 06, 2006

1.2

of

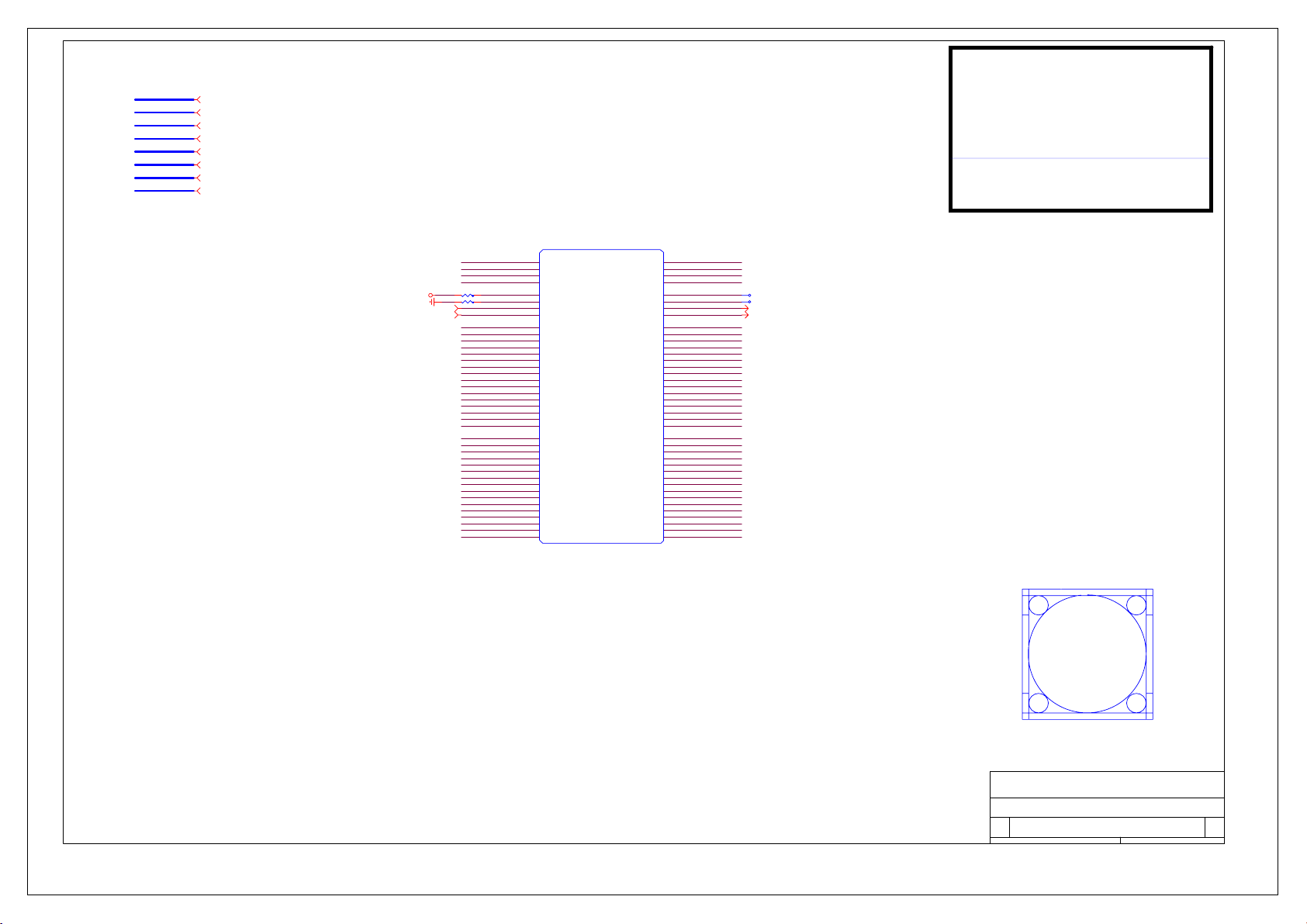

Page 4

Gigabyte confidential

L0_CADIN_L[0..15]

www.kythuatvitinh.com

L0_CADIN_H[0..15]

L0_CLKIN_L[0..1]

L0_CLK IN_H[0..1]

L0_CADOUT _L[0..15]

L0_CADOUT_H[0..15]

L0_CLKOUT_L[0..1]

L0_CLKOUT_H[0..1]

L0_CADIN_L[0..15] <11>

L0_CADIN_H[0..15] <11>

L0_CLKIN_L[0..1] <11>

L0_CLKIN_ H[0..1] <11>

L0_CADOUT_L[0..15] <11>

L0_CADOUT_H[0..15] <11>

L0_CLKOUT_L[0..1] <11>

L0_CLKOUT_H[0..1] <11>

CPU_VDD_RUN = VCORE

CPU_VDDA_RUN = VDDA25

VLDT_RUN = VCC12_HT

CPU_VDDIO_SUS = DDR18V

CPU_VTT_SUS = DDRVTT

VLDT_A = VCC12_HT

VLDT_B = HT12B

VCC12_HT

L0_CTLIN_H0<11>

GND

L0_CTLIN_L0<11>

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

R3 49.9/4/1

R4 49.9/4/1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

N6

L0_CLKIN_H(1)

P6

L0_CLKIN_L(1)

N3

L0_CLKIN_H(0)

N2

L0_CLKIN_L(0)

V4

L0_CTLIN_H(1)

V5

L0_CTLIN_L(1)

U1

L0_CTLIN_H(0)

V1

L0_CTLIN_L(0)

U6

L0_CADIN_H(15)

V6

L0_CADIN_L(15)

T4

L0_CADIN_H(14)

T5

L0_CADIN_L(14)

R6

L0_CADIN_H(13)

T6

L0_CADIN_L(13)

P4

L0_CADIN_H(12)

P5

L0_CADIN_L(12)

M4

L0_CADIN_H(11)

M5

L0_CADIN_L(11)

L6

L0_CADIN_H(10)

M6

L0_CADIN_L(10)

K4

L0_CADIN_H(9)

K5

L0_CADIN_L(9)

J6

L0_CADIN_H(8)

K6

L0_CADIN_L(8)

U3

L0_CADIN_H(7)

U2

L0_CADIN_L(7)

R1

L0_CADIN_H(6)

T1

L0_CADIN_L(6)

R3

L0_CADIN_H(5)

R2

L0_CADIN_L(5)

N1

L0_CADIN_H(4)

P1

L0_CADIN_L(4)

L1

L0_CADIN_H(3)

M1

L0_CADIN_L(3)

L3

L0_CADIN_H(2)

L2

L0_CADIN_L(2)

J1

L0_CADIN_H(1)

K1

L0_CADIN_L(1)

J3

L0_CADIN_H(0)

J2

L0_CADIN_L(0)

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_C

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

M2CPUA

ADOUT_L(2)

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

1

TP78

1

TP79

L0_CTLOUT_H0 <11>

L0_CTLOUT_L0 <11>

SOCKET_M2 M2/[12KRC-04K807-41R]

Title

Size Document Number Re v

Custom

Date: Sheet

GIGABYTE

CPU HYPER TRANSPORT

GA-M55plus-S3G

438Thursday, July 06, 2006

1.2

of

Page 5

Gigabyte confidential

M2CPUB

www.kythuatvitinh.com

L27

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

A_DQS_L(3)

M

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

A_DATA(13)

M

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MDA63

MDA62

MDA61

MDA60

MDA59

MDA58

MDA57

MDA56

MDA55

MDA54

MDA53

MDA52

MDA51

MDA50

MDA49

MDA48

MDA47

MDA46

MDA45

MDA44

MDA43

MDA42

MDA41

MDA40

MDA39

MDA38

MDA37

MDA36

MDA35

MDA34

MDA33

MDA32

MDA31

MDA30

MDA29

MDA28

MDA27

MDA26

MDA25

MDA24

MDA23

MDA22

MDA21

MDA20

MDA19

MDA18

MDA17

MDA16

MDA15

MDA14

MDA13

MDA12

MDA11

MDA10

MDA9

MDA8

MDA7

MDA6

MDA5

MDA4

MDA3

MDA2

MDA1

MDA0

MDA[0..63] <8,9> MDB[0..63] <8,9>

DQSB[0..8 ]

DCLKA2

-DCLKA2

DCLKA1

-DCLKA1

DCLKA0

-DCLKA0

MODT_A0

DCLKA5

-DCLKA5

DCLKA4

-DCLKA4

DCLKA3

-DCLKA3

MODT_A1

-SCASA

-SWEA

-SRASA

SBAA2

SBAA1

SBAA0

CKEA1

CKEA0

DQSA7

-DQSA7

DQSA6

-DQSA6

DQSA5

-DQSA5

DQSA4

-DQSA4

DQSA3

-DQSA3

DQSA2

-DQSA2

DQSA1

-DQSA1

DQSA0

-DQSA0

DMA7

DMA6

DMA5

DMA4

DMA3

DMA2

DMA1

DMA0

AG21

AG20

AC25

AA24

AC28

AE20

AE19

AD27

AA25

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

G19

H19

U27

U26

G20

G21

V27

W27

N25

Y27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

DCLKA2<8,10>

-DCLKA2<8,10>

DCLKA1<8,10>

-DCLKA1<8,10>

DCLKA0<8,10>

-DCLKA0<8,10>

-CSA1<8,10>

-CSA0<8,10>

MODT_A0<8,10>

DCLKA5<9,10>

-DCLKA5<9,10>

DCLKA4<9,10>

-DCLKA4<9,10>

DCLKA3<9,10> DCLKB3<9,10>

-DCLKA3<9,10>

-CSA3<9,10>

-CSA2<9,10>

MODT_A1<9,10>

-SCASA<8,9,10>

-SWEA<8 ,9,10>

-SRASA<8,9,10>

SBAA2<8,9,10>

SBAA1<8,9,10>

SBAA0<8,9,10>

CKEA1<9,10>

CKEA0<8,10>

MAAA15

MAAA[0..15]<8,9,10> MAAB[0..15]<8,9,10>

-DQSA[0..8] -DQSB[0..8]

DQSA[0..8 ]

DMA[0:8] DMB[0..8]

-DQ SA[0..8 ] <8,9>

DQSA[0..8] <8,9>

DMA [0..8] <8,9> DMB [0..8] <8,9>

MAAA14

MAAA13

MAAA12

MAAA11

MAAA10

MAAA9

MAAA8

MAAA7

MAAA6

MAAA5

MAAA4

MAAA3

MAAA2

MAAA1

MAAA0

-DQS B[0..8] <8,9>

DQS B[0..8] <8,9>

M2CPUC

A18

A19

U31

U30

C19

D19

N31

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

B_DQS_L(3)

M

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

DCLKB2

-DCLKB2

DCLKB1

-DCLKB1

DCLKB0

-DCLKB0

MODT_B0

DCLKB5

-DCLKB5

DCLKB4

-DCLKB4

DCLKB3

-DCLKB3

MODT_B1

-SCASB

-SWEB

-SRASB

SBAB2

SBAB1

SBAB0

CKEB1

CKEB0

DQSB7

-DQSB7

DQSB6

-DQSB6

DQSB5

-DQSB5

DQSB4

-DQSB4

DQSB3

-DQSB3

DQSB2

-DQSB2

DQSB1

-DQSB1

DQSB0

-DQSB0

DMB7

DMB6

DMB5

DMB4

DMB3

DMB2

DMB1

DMB0

AJ19

AK19

AE30

AC31

AD29

AL19

AL18

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

W29

W28

M31

M29

DCLKB2<8,10>

-DCLKB2<8,10>

DCLKB1<8,10>

-DCLKB1<8,10>

DCLKB0<8,10>

-DCLKB0<8,10>

-CSB1<8,10>

-CSB0<8,10>

MODT_B0<8,10>

DCLKB5<9,10>

-DCLKB5<9,10>

DCLKB4<9,10>

-DCLKB4<9,10>

-DCLKB3<9,10>

-CSB3<9,10>

-CSB2<9,10>

MODT_B1<9,10>

-SCASB<8,9,10>

-SWEB<8,9 ,10>

-SRASB<8,9,10>

SBAB2<8,9,10>

SBAB1<8,9,10>

SBAB0<8,9,10>

CKEB1<9,10>

CKEB0<8,10>

MAAB15

MAAB14

MAAB13

MAAB12

MAAB11

MAAB10

MAAB9

MAAB8

MAAB7

MAAB6

MAAB5

MAAB4

MAAB3

MAAB2

MAAB1

MAAB0

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A2

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MDB63

MDB62

MDB61

MDB60

MDB59

MDB58

MDB57

MDB56

MDB55

MDB54

MDB53

MDB52

MDB51

MDB50

MDB49

MDB48

MDB47

MDB46

MDB45

MDB44

MDB43

MDB42

MDB41

MDB40

MDB39

MDB38

MDB37

MDB36

MDB35

MDB34

MDB33

MDB32

MDB31

MDB30

MDB29

MDB28

7

MDB27

MDB26

MDB25

MDB24

MDB23

MDB22

MDB21

MDB20

MDB19

MDB18

MDB17

MDB16

MDB15

MDB14

MDB13

MDB12

MDB11

MDB10

MDB9

MDB8

MDB7

MDB6

MDB5

MDB4

MDB3

MDB2

MDB1

MDB0

Title

Size Document Number Re v

Custom

Date: Sheet

GIGABYTE

CPU DDRII MEMORY

GA-M55plus-S3G

538Thursday, July 06, 2006

1.2

of

Page 6

Gigabyte confidential

DDR18V

www.kythuatvitinh.com

-CPURST_C

CPU_PWRGD_C

HTSTOP_L_C

12

13

GND

-HTMCP_PWRGD<12,16>

CPU_PWRGD<11>

-HTMCP_PWRGD<12,16>

-HTMCP_PWRGD<12,16>

CPUVREF

40 MILS WIDTH

CPU_M_VREF

SBC31

SBC12

1N/4/X7R/50V/K

0.1U/4/Y5V/16V/Z

R21 300/4

R22 300/4

R23 300/4

DDR18V

U3D

147

11

74LVC08AD/SO14[10TC1-117408-01R_10TC1-117408-02R]

GND

-HTMCP_PWRGD

CPU_PWRGD

-HTMCP_PWRGD

-CPURST<11>

12

VCC

5VSB

-HTSTOP_L

-HTMCP_PWRGD

-CPURST

SC35

1u/6/Y5V/10V/Z

R988 10K/4

R989 8.2K/4

PWOK<23,32,34,35,37>

THERMTRIP_CPU_L

DDR18V

SR19

16.9/4/1

SR20

16.9/4/1

GND

C1048

1U/6/Y5V/10V/Z

-CPURST

R992 8.2K/4/X

R991 8.2K/4

-HTSTOP_L<11>

-CPURST

CPU_PWRGD

-HTSTOP_L

VDDA25

DDR18V

U3A

147

1

2

74LVC08AD/SO14[10TC1-117408-01R_10TC1-117408-02R]

GND

DDR18V

U3B

147

4

5

74LVC08AD/SO14[10TC1-117408-01R_10TC1-117408-02R]

GND

DDR18V

U3C

147

9

10

74LVC08AD/SO14[10TC1-117408-01R_10TC1-117408-02R]

GND

R990

8.2K/4

R26 1K/4

R33 1K/4

R36 1K/4

FB1 30/6/4A/S

CPUCLK0_H<11>

CPUCLK0_L<11>

CPU_PWRGD _C

3

HTSTOP_L_C

6

-CPURST_C

8

R986 4.7K/4

5VSB

84

U66B

5

+

6

-

KA393D/SO8

Q117

MMBT2222A/SOT23/600mA/40

SOT23

132

C1047

0.1U/6/Y5V/25V/Z

7

VDDA25

C3

4.7u/8/Y5V/10V/Z

GND

CPUCLK0_H

CPUCLK0_L

SI_DAT<36>

VCC

R987

1K/4

3.3n/4/X7R/50V/K

3.9n/4/X7R/50V/K

C1

C2

3.9n/4/X7R/50V/K

R58 300/4

GND

DDR18V

COREFB+<30>

COREFB-<30>

CPU_M_VREF

DDR18V

GND

GND

GNDA<36>

TMPIN3<28,36>

COREFB-<30>

COREFB+<30>

DR10 0/6/X

VCORE

COREFB-<30>

COREFB+<30>

COREFB-<30>

COREFB+<30>

For AMD Validation only

3

D

GS

2

1

3

D

GS

2

1

C13

C4

0.22u/6/X5R/10V/K

GND

CLKIN_H

R5

CLKIN_L

169/4/1

R8 22/4 /X

R9 22/4 /X

R17 300/4/X

-PWRBTSW <35,36>

Q114

2N7002/SOT23/60PF/5

CPUVDD_EN

Q1

2N7002/SOT23/60PF/5

CPU_PWRGD_C

-CPURST_C

CPU_PRESENT_L

TP81

TP83

TP84

TP85

TP86

39.2/6/1R11

39.2/6/1R12

CPU_TEST25_H

CPU_TEST25_L

300/4R13

300/4R14

TP89

TP91

TP93

TP95

TP96

0/4R15

0/4R16

C20

4.7u/8/Y5V/10V/Z/X

C21

0.1U/6/Y5V/25V/Z /X

BC8

0.1U/4/Y5V/16V/Z

CPUVDD_EN <16,30>

M2CPUD

C10

VDDA1

D10

VDDA2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

AL3

CPU_PRESENT_L

AL6

SID

SIC

AK6

SID

AL10

TDI

AJ10

TRST_L

AH10

TCK

AL9

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

E12

VTT_SENSE

F12

M_VREF

AH11

M_ZN

AJ11

M_ZP

A10

TEST25_H

B10

TEST25_L

F10

TEST19

E9

TEST18

AJ7

TEST13

F6

TEST9

GND

D6

TEST17

E7

TEST16

F8

TEST15

C5

TEST14

AH9

TEST12

E5

TEST7

AJ5

TEST6

AG9

THERMDC

AG8

THERMDA

AH7

TEST3

AJ6

TEST2

RS3 CLOSE CPU VR MOSFET

Plase at PH3 copper

MISC

CPU_VID5

D2

VID(5)

CPU_VID4HTSTOP_L_C

D1

VID(4)

CPU_VID3

C1

VID(3)

CPU_VID2

E3

VID(2)

CPU_VID1

E2

VID(1)

CPU_VID0

E1

VID(0)

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

AK7

AL7

AK10

B6

AK11

AL11

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

LAYOUT: Route trace 50 mils wide and

THERMTRIP_L

500 to 750 mils long between these caps.

VCC

R2068

R2069

12K/4/1/X

2.4K/4/1/X

RS3

R2071

1K/4/1/X

100K/1/6/S/X

HR100K/[10RH2-001003-21]

RN251

300/8P4R/X

R55 80.6/4/1

CPU_TEST21

CPU_TEST26

DDR18V

R65

300/4/X

1 2

3 4

5 6

7 8

THERMTRIP_L

TP82

TP87

TP88

VCC12_HT

44.2/6/1R53

44.2/6/1R54

TP90

TP92

TP94

TP97

R2067 6.98K/4/1/X

5VSB VCC

84

U66A

3

+

2

-

KA393D/SO8

C223

0.1U/6/Y5V/25V/Z/X

R57

R56

300/4

300/4

VID 5 <30>

VID 4 <30>

VID 3 <30>

VID 2 <30>

VID 1 <30>

VID 0 <30>

R176 1K/4R19 300/4/X

DDR18V

R174 1K/4

DDR18V

GND

Route as 80-Ohm differential impedance

R60

300/4

R175 1K/4

132

-PROCHOT

Q10

MMBT2222A/SOT23/600mA/40

SOT23

Keep trace to resistor less than 1" from CPU pin

Asserted at 131 degree

Deasserted at 116 degree

-PROCHOT

R2070

680/4/X

1

No pop

Q300

2N7002/SOT23/60PF/5/X

SOT23

132

3VDUAL

R59

1K/4

THERMTRIP_CPU_LSIC

Q9

MMBT222 2A/SOT23/600mA/40

SOT23

132

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

L25

L26

L31

L30

W26

W25

AE27

U24

V24

AE28

Y31

Y30

AG31

V31

W31

AF31

Title

Size Document Number Re v

Custom

Date: Sheet

THERMTRIP_CPU_L <16>SI_CLK<36>

CPU_TEST26

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST21

M2CPUE

INTERNAL MISC

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

GIGABYTE

CPU CONTROL

GA-M55plus-S3G

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

R37 300/4

R49 1K/4

R42 510/4

R43 510/4

R47 300/4

E20

B19

AL4

AK4

AK3

F2

F3

G4

G3

G5

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

638Thursday, July 06, 2006

of

DDR18V

GND

1.2

Page 7

Gigabyte confidential

VCORE

www.kythuatvitinh.com

AA10

AA12

AA14

AA16

AA18

AB11

AC10

AE10

VLDT_RUN_B is connected to the VLDT_RUN power

supply through the package or on the die. It is only connected

M2CPUF

VDD1

A4

VDD1

A6

VDD2

AA8

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

AB7

VDD9

AB9

VDD10

VDD11

AC4

VDD12

AC5

VDD13

AC8

VDD14

VDD15

AD2

VDD16

AD3

VDD17

AD7

VDD18

AD9

VDD19

VDD20

AF7

VDD21

AF9

VDD22

AG4

VDD23

AG5

VDD24

AG7

VDD25

2

AH

VDD26

AH3

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

E10

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

G10

VDD49

G12

VDD50

H7

VDD51

H11

VDD52

H23

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

K11

VDD64

K13

VDD65

K15

VDD66

K17

VDD67

K19

VDD68

K21

VDD69

K23

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

Y17

VDD150

Y19

D151

VD

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

52

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

GND

VCORE

M2CPUG

VDD2

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

DD28

V

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

W10

VDD62

W12

VDD63

W14

VDD64

W16

VDD65

W18

VDD66

W20

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

52

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

GND

VCORE

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

W22

M2CPUH

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

M21

VDD21

M23

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

VDD31

Y23

VDD32

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

52

DDRVTT

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

GND

on the board to decoupling near the CPU package.

M2CPUI

VDDIO

VCC12_HT

DDRVTT

DDR18V

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

AJ4

VLDT_A1

AJ3

VLDT_A2

AJ2

VLDT_A3

AJ1

VLDT_A4

D12

VTT1

C12

VTT2

B12

VTT3

A12

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

V

DDIO7

VDDIO8

VDDIO29

M24

VDDIO9

M26

VDDIO10

M28

VDDIO11

M30

VDDIO12

P24

VDDIO13

P26

VDDIO14

P28

VDDIO15

P30

VDDIO16

T24

VDDIO17

T26

VDDIO18

T28

VDDIO19

T30

VDDIO20

V25

VDDIO21

V26

VDDIO22

V28

VDDIO23

V30

VDDIO24

Y24

VDDIO25

Y26

VDDIO26

Y28

VDDIO27

Y29

VDDIO28

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

GND

BUTTOM SIDE

VCORE

SC16

SC17

SC25

SC18

22u/8/X5R/6.3V/M/X

SC26

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

VCORE

SC24

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M/X

GND

22u/8/X5R/6.3V/M

GND

DDRVTT

SC19

22u/8/X5R/6.3V/M/X

SC27

22u/8/X5R/6.3V/M/X

HT12B

BC795

4.7u/8/Y5V/1 0V/Z

GND

VCORE

GND

SC20

22u/8/X5R/6.3V/M

SC28

22u/8/X5R/6.3V/M

DDR18V

SC2

0.22u/6/X5R/10V/K

GND

DDR18V

SC9

22u/8/X5R/6.3V/M/X

GND

SC11

0.22u/6/X5R/10V/K

0.22u/6/X5R/10V/K/X

SC21

22u/8/X5R/6.3V/M/X

SC29

22u/8/X5R/6.3V/M/X

1021 EMI

DDRVTT

SC4

0.22u/6/X5R/10V/K/X

SC10

22u/8/X5R/6.3V/M

BUTTOM SIDE

SC13

SC12

0.22u/6/X5R/10V/K/X

SC23

SC22

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M/X

SC30

22u/8/X5R/6.3V/M

BUTTOM SIDE

SC5

0.01u/6/X7R/25V/K/X

SC8

SC7

4.7u/8/Y5V/10V/Z

4.7u/8/Y5V/10V/Z

SC14

0.01u/6/X7R/25V/K/X

1021 EMI

VCC12

100P/4/N PO/50V/J/X

SC6

180P/6/NPO/50V/J

SC31

180P/6/N PO/50V/J/X

SC15

180P/6/NPO/50V/J

DDRVTT

BC26

VCC12_HT

C1328

4.7u/8/Y5V/10V/Z

C1329

4.7u/8/Y5V/10V/Z

0.22u/6/X5R/10V/K

GND

C1330

C1331

0.22u/6/X5R/10V/K

180P/6/NPO/50V/J

C1332

C1333

180P/6/NPO/50V/J

DDR18V

C1324

4.7u/8/Y5V/10V/Z

C1325

4.7u/8/Y5V/10V/Z

GND

C1327

C1326

0.22u/6/X5R/10V/K

0.22u/6/X5R/10V/K

C1316

4.7u/8/Y5V/10V/Z

DDRVTT

C1334

4.7u/8/Y5V/10V/Z

C1317

4.7u/8/Y5V/10V/Z

GND

C1335

4.7u/8/Y5V/10V/Z

GND

C1318

C1319

0.22u/6/X5R/10V/K

0.22u/6/X5R/10V/K

C1336

C1337

0.22u/6/X5R/10V/K

0.22u/6/X5R/10V/K

C1320

1n/6/X7R/50V/K

C1338

1n/6/X7R/50V/K

C1321

1n/6/X7R/50V/K

C1339

1n/6/X7R/50V/K

C1322

C1323

180P/6/NPO/50V/J

180P/6/NPO/50V/J

C1340

C1341

180P/6/NPO/50V/J

180P/6/NPO/50V/J

BC20

100P/4/NPO/50V/J

Title

Size Document Number Re v

Custom

Date: Sheet

BC23

100P/4/N PO/50V/J/X

100P/4/N PO/50V/J/X

GIGABYTE

CPU POWER & GND

GA-M55plus-S3G

BC24

BC25

100P/4/NPO/50V/J/X

738Thursday, July 06, 2006

of

1.2

Page 8

Gigabyte confidential

8

www.kythuatvitinh.com

D D

D3

MEM_SMBDATA

C C

MEM_SMBCL K

VCC3

BC9

0.1U/6/Y5V/25V/Z

C14 0.1U/4/Y5V/16V/Z

VCC3

DDR_VREF

B B

A A

DDR18V

R154

59/6/1

R155

59/6/1

MAAA[0..15]<5,9,10>

C123 0.1U/4/Y5V/16V/Z

BC6

0.1U/6/Y/25V/X

BC10

0.1U/4/Y5V/16V/Z

8

2

3

1

3VDUAL

BAV99/SOT23/300mA

SOT23

D4

2

3

1

3VDUAL

BAV99/SOT23/300mA

SOT23

VCC3

MEM_SMBCLK<9,19> MEM_SMBDATA<9,19>

MEM_SMBDATA<9,19>

SBAA1<5,9,10>

SBAA0<5,9,10>

CKEA0<5,10>

-CSA1<5,10>

-CSA0<5,10>

-DCLKA2<5,10>

DCLKA2<5,10>

-DCLKA1<5,10>

DCLKA1<5,10>

-DCLKA0<5,10>

DCLKA0<5,10>

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

SBAA2<5,9,10>

-SCASA<5,9,10>

-SRASA<5,9,10>

-SWEA<5,9,10>

DDR_VREF

BC11

1N/4/X7R/50V/K C125

DDR18V

VREF_DDRA

MEM_SMBCLK

MEM_SMBDATA

SBAA1

SBAA0

CKEA0

-DCLKA2

DCLKA2

-DCLKA1

DCLKA1

-DCLKA0

DCLKA0

SBAA2

-SCASA

-SRASA

-SWEA

7

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

100

103

106

109

112

115

118

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

169

198

201

204

207

210

213

216

219

222

225

228

231

234

237

51

56

62

72

75

78

191

194

181

175

170

53

59

64

197

69

172

187

184

178

189

67

18

55

238

120

119

101

240

239

190

71

171

52

76

193

221

220

138

137

186

185

188

183

63

182

61

60

180

58

179

177

70

57

176

196

174

173

54

74

192

73

7

DDRII_1

2

VSS

5

VSS

8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

RC1

RC0

VDDSPD

1

VREF

SCL

SDA

SA2

SA1

SA0

BA1

BA0

CKE1

CKE0

S1*

S0*

CK2*/RFU

CK2/RFU

CK1*/RFU

CK1/RFU

CK0*

CK0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16/BA2

CAS*

RSA*

WE*

DDR2/240/YL/VA/D

6

-DQSA[0..8]

DQSA[0..8]

DMA[0:8]

6

5

68

NC

102

NC/TEST

19

NC

77

ODT1

MODT_A0

195

ODT0

42

CB(0)

43

CB(1)

48

CB(2)

49

CB(3)

161

CB(4)

162

CB(5)

167

CB(6)

168

CB(7)

7

DQS(0)

6

DQS*(0)

16

DQS(1)

15

DQS*(1)

28

DQS(2)

27

DQS*(27)

37

DQS(3)

36

DQS*(3)

84

DQS(4)

83

DQS*(4)

93

DQS(5)

92

DQS*(5)

105

DQS(6)

104

DQS*(6)

114

DQS(7)

113

DQS*(7)

46

DQS8

45

DQS8*

125

DM0/DQS9

126

NC/DQS9*

134

DM1/DQS10

135

NC/DQS10*

146

DM2/DQS11

147

NC/DQS11*

155

DM3/DQS12

156

NC/DQS12*

202

DM4/DQS13

203

NC/DQS13*

211

DM5/DQS14

212

NC/DQS14*

223

DM6/DQS15

224

NC/DQS15*

232

DM7/DQS16

233

NC/DQS16*

164

DM8/DQS17

165

NC/DQS17*

3

DQ(0)

4

DQ(1)

9

DQ(2)

10

DQ(3)

122

DQ(4)

123

DQ(5)

128

DQ(6)

129

DQ(7)

12

DQ(8)

13

DQ(9)

21

DQ(10)

22

DQ(11)

131

DQ(12)

132

DQ(13)

140

DQ(14)

141

DQ(15)

24

DQ(16)

25

DQ(17)

30

DQ(18)

31

DQ(19)

143

DQ(20)

144

DQ(21)

149

DQ(22)

150

DQ(23)

33

DQ(24)

34

DQ(25)

39

DQ(26)

40

DQ(27)

152

DQ(28)

153

DQ(29)

158

DQ(30)

159

DQ(31)

80

DQ(32)

81

DQ(33)

86

DQ(34)

87

DQ(35)

199

DQ(36)

200

DQ(37)

205

DQ(38)

206

DQ(39)

89

DQ(40)

90

DQ(41)

95

DQ(42)

96

DQ(43)

208

DQ(44)

209

DQ(45)

214

DQ(46)

215

DQ(47)

98

DQ(48)

99

DQ(49)

107

DQ(50)

108

DQ(51)

217

DQ(52)

218

DQ(53)

226

DQ(54)

227

DQ(55)

110

DQ(56)

111

DQ(57)

116

DQ(58)

117

DQ(59)

229

DQ(60)

230

DQ(61)

235

DQ(62)

236

DQ(63)

-DQSA[0 ..8] <5,9> MEM_SMBDATA<9,19>

DQSA[0..8] <5,9>

DMA[0..8] <5,9>

MODT_A0 <5,10>

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57 MDB58

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MDA[0..63] <5,9>

5

4

DDR18V

DDR_VREF

C124

VCC3

0.1U/4/Y5V/16V/Z

MEM_SMBCLK<9,19>

MAAB[0..15]<5,9,10>

MEM_SMBCLK<9,19>

VREF_DDRB

MEM_SMBCLK

MEM_SMBDATA

VCC3

SBAB1

SBAB1<5,9,10>

SBAB0

SBAB0<5,9,10>

CKEB0

CKEB0<5,10>

-CSB1<5,10>

-CSB0<5,10>

-DCLKB2

-DCLKB2<5,10>

DCLKB2

DCLKB2<5,10>

-DCLKB1

-DCLKB1<5,10>

DCLKB1

DCLKB1<5,10>

-DCLKB0

-DCLKB0<5,10>

DCLKB0

DCLKB0<5,10>

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13 MDB56

MAAB14

MAAB15

SBAB2

SBAB2<5,9,10>

-SCASB

-SCASB<5,9,10>

-SRASB

-SRASB<5,9,10>

-SWEB

-SWEB<5,9,10>

MEM_SMBCLK

MEM_SMBDATA

100P/4/NPO/50V/X

4

DDRII_2

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

100

VSS

103

VSS

106

VSS

109

VSS

112

VSS

115

VSS

118

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

169

VSS

198

VSS

201

VSS

204

VSS

207

VSS

210

VSS

213

VSS

216

VSS

219

VSS

222

VSS

225

VSS

228

VSS

231

VSS

234

VSS

237

VSS

51

VDDQ

56

VDDQ

62

VDDQ

72

VDDQ

75

VDDQ

78

VDDQ

191

VDDQ

194

VDDQ

181

VDDQ

175

VDDQ

170

VDDQ

53

VDD

59

VDD

64

VDD

197

VDD

69

VDD

172

VDD

187

VDD

184

VDD

178

VDD

189

VDD

67

VDD

18

RC1

55

RC0

238

VDDSPD

1

VREF

120

SCL

119

SDA

101

SA2

240

SA1

239

SA0

190

BA1

71

BA0

171

CKE1

52

CKE0

76

S1*

193

S0*

221

CK2*/RFU

220

CK2/RFU

138

CK1*/RFU

137

CK1/RFU

186

CK0*

185

CK0

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

A10/AP

57

A11

176

A12

196

A13

174

A14

173

A15

54

A16/BA2

74

CAS*

192

RSA*

73

WE*

DDR2/240/YL/VA/D

C126

100P/4/N/50V/X

3

3

2

DQSB[0..7]

-DQSB[0..7]

68

NC

102

NC/TEST

19

NC

77

ODT1

195

ODT0

42

CB(0)

43

CB(1)

48

CB(2)

49

CB(3)

161

CB(4)

162

CB(5)

167

CB(6)

168

CB(7)

7

DQS(0)

6

DQS*(0)

16

DQS(1)

15

DQS*(1)

28

DQS(2)

27

DQS*(27)

37

DQS(3)

36

DQS*(3)

84

DQS(4)

83

DQS*(4)

93

DQS(5)

92

DQS*(5)

105

DQS(6)

104

DQS*(6)

114

DQS(7)

113

DQS*(7)

46

DQS8

45

DQS8*

125

DM0/DQS9

126

NC/DQS9*

134

DM1/DQS10

135

NC/DQS10*

146

DM2/DQS11

147

NC/DQS11*

155

DM3/DQS12

156

NC/DQS12*

202

DM4/DQS13

203

NC/DQS13*

211

DM5/DQS14

212

NC/DQS14*

223

DM6/DQS15

224

NC/DQS15*

232

DM7/DQS16

233

NC/DQS16*

164

DM8/DQS17

165

NC/DQS17*

3

DQ(0)

4

DQ(1)

9

DQ(2)

10

DQ(3)

122

DQ(4)

123

DQ(5)

128

DQ(6)

129

DQ(7)

12

DQ(8)

13

DQ(9)

21

DQ(10)

22

DQ(11)

131

DQ(12)

132

DQ(13)

140

DQ(14)

141

DQ(15)

24

DQ(16)

25

DQ(17)

30

DQ(18)

31

DQ(19)

143

DQ(20)

144

DQ(21)

149

DQ(22)

150

DQ(23)

33

DQ(24)

34

DQ(25)

39

DQ(26)

40

DQ(27)

152

DQ(28)

153

DQ(29)

158

DQ(30)

159

DQ(31)

80

DQ(32)

81

DQ(33)

86

DQ(34)

87

DQ(35)

199

DQ(36)

200

DQ(37)

205

DQ(38)

206

DQ(39)

89

DQ(40)

90

DQ(41)

95

DQ(42)

96

DQ(43)

208

DQ(44)

209

DQ(45)

214

DQ(46)

215

DQ(47)

98

DQ(48)

99

DQ(49)

107

DQ(50)

108

DQ(51)

217

DQ(52)

218

DQ(53)

226

DQ(54)

227

DQ(55)

110

DQ(56)

111

DQ(57)

116

DQ(58)

117

DQ(59)

229

DQ(60)

230

DQ(61)

235

DQ(62)

236

DQ(63)

GIGABYTE

Title

Size Document Number Rev

Custom

Date: Shee t

2

DMB[0..7]

MODT_B0

MODT_B0 <5,10>

DQSB0

-DQSB0

DQSB1

-DQSB1

DQSB2

-DQSB2

DQSB3

-DQSB3

DQSB4

-DQSB4

DQSB5

-DQSB5

DQSB6

-DQSB6

DQSB7

-DQSB7

DMB0

DMB1

DMB2

DMB3

DMB4

DMB5

DMB6

DMB7

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB57

MDB59

MDB60

MDB61

MDB62

MDB63

DDRII CHANNEL A

GA-M55plus-S3G 1.2

1

DQSB[0..7] <5,9>

-DQSB[0..7] <5,9>

DMB[0..7] <5,9>

MDB[0..63] <5,9>

838

1

of

Page 9

Gigabyte confidential

8

www.kythuatvitinh.com

D D

-DQSB[0..8]

-DQSB[0 ..8] <5,8>

DQSB[0..8]

DQSB[0 ..8] <5,8>

DMB[0..8]

DMB[0..8] <5,8>

C C

DDR_VREF DDR_VREF

C121

0.1U/4/Y5V/16V/Z

B B

A A

MEM_SMBCLK<8,19>

MEM_SMBDATA<8,19>

VCC3

SBAA1<5,8,10>

SBAA0<5,8,10>

CKEA1<5,10>

-DCLKA5<5,10>

DCLKA5<5,10>

-DCLKA4<5,10>

DCLKA4<5,10>

-DCLKA3<5,10>

MAAA[0..15]<5,8,10>

DCLKA3<5,10>

SBAA2<5,8,10>

-SCASA<5,8,10>

-SRASA<5,8,10>

-SWEA<5,8,10>

8

7

DDRII_3

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

100

VSS

103

VSS

106

VSS

109

VSS

112

VSS

115

VSS

118

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

169

VSS

198

VSS

201

VSS

204

VSS

207

VSS

210

VSS

213

VSS

216

VSS

219

VSS

222

VSS

225

VSS

228

VSS

231

VSS

234

VSS

237

VSS

51

VDDQ

56

VDDQ

62

VDDQ

72

VDDQ

75

VDDQ

78

VDDQ

191

VDDQ

194

VDDQ

181

VDDQ

175

VDDQ

170

VDDQ

53

VDD

59

VDD

64

VDD

197

VDD

69

VDD

172

VDD

187

VDD

184

VDD

178

VDD

189

VDD

67

VDD

18

RC1

55

RC0

238

VDDSPD

1

VREF

120

SCL

119

SDA

101

SA2

240

SA1

239

SA0

SBAA1

190

BA1

SBAA0

71

BA0

171

CKE1

CKEA1

52

CKE0

76

S1*

193

S0*

221

CK2*/RFU

DCLKA5

220

CK2/RFU

138

CK1*/RFU

DCLKA4

137

CK1/RFU

-DCLKA3

186

CK0*

DCLKA3 MDA41

185

CK0

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

A10/AP

57

A11

176

A12

196

A13

174

A14

173

A15

SBAA2

54

A16/BA2

-SCASA

74

CAS*

-SRASA

192

RSA*

-SWEA

73

WE*

DDR2/240/RE/VA/D

7

-CSA3<5,10>

-CSA2<5,10>

DDR18V

VCC3

MEM_SMBCLK

MEM_SMBDATA

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

6

6

NC/TEST

DQS(0)

DQS*(0)

DQS(1)

DQS*(1)

DQS(2)

DQS*(27)

DQS(3)

DQS*(3)

DQS(4)

DQS*(4)

DQS(5)

DQS*(5)

DQS(6)

DQS*(6)

DQS(7)

DQS*(7)

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ(10)

DQ(11)

DQ(12)

DQ(13)

DQ(14)

DQ(15)

DQ(16)

DQ(17)

DQ(18)

DQ(19)

DQ(20)

DQ(21)

DQ(22)

DQ(23)

DQ(24)

DQ(25)

DQ(26)

DQ(27)

DQ(28)

DQ(29)

DQ(30)

DQ(31)

DQ(32)

DQ(33)

DQ(34)

DQ(35)

DQ(36)

DQ(37)

DQ(38)

DQ(39)

DQ(40)

DQ(41)

DQ(42)

DQ(43)

DQ(44)

DQ(45)

DQ(46)

DQ(47)

DQ(48)

DQ(49)

DQ(50)

DQ(51)

DQ(52)

DQ(53)

DQ(54)

DQ(55)

DQ(56)

DQ(57)

DQ(58)

DQ(59)

DQ(60)

DQ(61)

DQ(62)

DQ(63)

ODT1

ODT0

CB(0)

CB(1)

CB(2)

CB(3)

CB(4)

CB(5)

CB(6)

CB(7)

DQS8

DQ(0)

DQ(1)

DQ(2)

DQ(3)

DQ(4)

DQ(5)

DQ(6)

DQ(7)

DQ(8)

DQ(9)

5

68

NC

102

19

NC

77

MODT_A1

195

42

43

48

49

161

162

167

168

DQSA0

7

-DQSA0

6

DQSA1

16

-DQSA1

15

DQSA2

28

-DQSA2

27

DQSA3

37

-DQSA3

36

DQSA4

84

-DQSA4

83

DQSA5

93

-DQSA5

92

DQSA6

105

-DQSA6

104

DQSA7

114

-DQSA7

113

46

45

DMA0

125

126

DMA1

134

135

DMA2

146

147

DMA3

155

156

DMA4

202

203

DMA5

211

212

DMA6

223

224

DMA7

232

233

164

165

MDA0

3

MDA1

4

MDA2

9

MDA3

10

MDA4

122

MDA5

123

MDA6

128

MDA7

129

MDA8

12

MDA9

13

MDA10

21

MDA11

22

MDA12

131

MDA13

132

MDA14

140

MDA15

141

MDA16

24

MDA17

25

MDA18

30

MDA19

31

MDA20

143

MDA21

144

MDA22

149

MDA23

150

MDA24

33

MDA25

34

MDA26

39

MDA27

40

MDA28

152

MDA29

153

MDA30

158

MDA31

159

MDA32

80

MDA33

81

MDA34

86

MDA35

87

MDA36-DCLKA5

199

MDA37

200

MDA38-DCLKA4

205

MDA39

206

MDA40

89

90

MDA42

95

MDA43

96

MDA44

208

MDA45

209

MDA46

214

MDA47

215

MDA48

98

MDA49

99

MDA50

107

MDA51

108

MDA52

217

MDA53

218

MDA54

226

MDA55

227

MDA56

110

MDA57

111

MDA58

116

MDA59

117

MDA60

229

MDA61

230

MDA62

235

MDA63

236

5

-DQSA[0..7]

DQSA[0..7]

DMA[0:7]

MODT_A1 <5,10> MODT_B1 <5,10>

MDA[0..63] <5,8>

MAAB[0..15]<5,8,10>

4

-DQSA[0 ..7] <5,8>

DQSA[0..7] <5,8>

DMA[0..7] <5, 8>

DDR18V

C122

0.1U/4/Y5V/16V/Z

MEM_SMBCLK<8,19>

MEM_SMBDATA<8,19>

VCC3

MEM_SMBCLK

MEM_SMBDATA

VCC3

SBAB1

SBAB1<5,8,10>

SBAB0

SBAB0<5,8,10>

CKEB1

CKEB1<5,10>

-CSB3<5,10>

-CSB2<5,10>

-DCLKB5

-DCLKB5<5,10>

DCLKB5

DCLKB5<5,10>

-DCLKB4

-DCLKB4<5,10>

DCLKB4

DCLKB4<5,10>

-DCLKB3

-DCLKB3<5,10>

DCLKB3

DCLKB3<5,10>

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5 MDB48

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

MAAB14

MAAB15

SBAB2

SBAB2<5,8,10>

-SCASB

-SCASB<5,8,10>

-SRASB

-SRASB<5,8,10>

-SWEB

-SWEB<5,8,10>

4

DDRII_4

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

100

VSS

103

VSS

106

VSS

109

VSS

112

VSS

115

VSS

118

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

169

VSS

198

VSS

201

VSS

204

VSS

207

VSS

210

VSS

213

VSS

216

VSS

219

VSS

222

VSS

225

VSS

228

VSS

231

VSS

234

VSS

237

VSS

51

VDDQ

56

VDDQ

62

VDDQ

72

VDDQ

75

VDDQ

78

VDDQ

191

VDDQ

194

VDDQ

181

VDDQ

175

VDDQ

170

VDDQ

53

VDD

59

VDD

64

VDD

197

VDD

69

VDD

172

VDD

187

VDD

184

VDD

178

VDD

189

VDD

67

VDD

18

RC1

55

RC0

238

VDDSPD

1

VREF

120

SCL

119

SDA

101

SA2

240

SA1

239

SA0

190

BA1

71

BA0

171

CKE1

52

CKE0

76

S1*

193

S0*

221

CK2*/RFU

220

CK2/RFU

138

CK1*/RFU

137

CK1/RFU

186

CK0*

185

CK0

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

A10/AP

57

A11

176

A12

196

A13

174

A14

173

A15

54

A16/BA2

74

CAS*

192

RSA*

73

WE*

DDR2/240/RE/VA/D

3

3

2

68

NC

102

NC/TEST

19

NC

77

ODT1

MODT_B1

195

ODT0

42

CB(0)

43

CB(1)

48

CB(2)

49

CB(3)

161

CB(4)

162

CB(5)

167

CB(6)

168

CB(7)

DQSB0

7

DQS(0)

-DQSB0

6

DQS*(0)

DQS*(1)

DQS*(27)

DQS*(3)

DQS*(4)

DQS*(5)

DQS*(6)

DQS*(7)

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

GIGABYTE

Title

Size Document Number Rev

Custom

Date: Shee t

2

DQS(1)

DQS(2)

DQS(3)

DQS(4)

DQS(5)

DQS(6)

DQS(7)

DQS8*

DQ(10)

DQ(11)

DQ(12)

DQ(13)

DQ(14)

DQ(15)

DQ(16)

DQ(17)

DQ(18)

DQ(19)

DQ(20)

DQ(21)

DQ(22)

DQ(23)

DQ(24)

DQ(25)

DQ(26)

DQ(27)

DQ(28)

DQ(29)

DQ(30)

DQ(31)

DQ(32)

DQ(33)

DQ(34)

DQ(35)

DQ(36)

DQ(37)

DQ(38)

DQ(39)

DQ(40)

DQ(41)

DQ(42)

DQ(43)

DQ(44)

DQ(45)

DQ(46)

DQ(47)

DQ(48)

DQ(49)

DQ(50)

DQ(51)

DQ(52)

DQ(53)

DQ(54)

DQ(55)

DQ(56)

DQ(57)

DQ(58)

DQ(59)

DQ(60)

DQ(61)

DQ(62)

DQ(63)

DQS8

DQ(0)

DQ(1)

DQ(2)

DQ(3)

DQ(4)

DQ(5)

DQ(6)

DQ(7)

DQ(8)

DQ(9)

DQSB1

16

-DQSB1

15

DQSB2

28

-DQSB2

27

DQSB3

37

-DQSB3

36

DQSB4

84

-DQSB4

83

DQSB5

93

-DQSB5

92

DQSB6

105

-DQSB6

104

DQSB7

114

-DQSB7

113

46

45

DMB0

125

126

DMB1

134

135

DMB2

146

147

DMB3

155

156

DMB4

202

203

DMB5

211

212

DMB6

223

224

DMB7

232

233

164

165

MDB0

3

MDB1

4

MDB2

9

MDB3

10

MDB4

122

MDB5

123

MDB6

128

MDB7

129

MDB8

12

MDB9

13

MDB10

21

MDB11

22

MDB12

131

MDB13

132

MDB14

140

MDB15

141

MDB16

24

MDB17

25

MDB18

30

MDB19

31

MDB20

143

MDB21

144

MDB22

149

MDB23

150

MDB24

33

MDB25

34

MDB26

39

MDB27

40

MDB28

152

MDB29

153

MDB30

158

MDB31

159

MDB32

80

MDB33

81

MDB34

86

MDB35

87

MDB36

199

MDB37

200

MDB38

205

MDB39

206

MDB40

89

MDB41

90

MDB42

95

MDB43

96

MDB44

208

MDB45

209

MDB46

214

MDB47

215

98

MDB49

99

MDB50

107

MDB51

108

MDB52

217

MDB53

218

MDB54

226

MDB55

227

MDB56

110

MDB57

111

MDB58

116

MDB59

117

MDB60

229

MDB61

230

MDB62

235

MDB63

236

DDRII CHANNEL B

GA-M55plus-S3G 1.2

1

MDB[0..63] <5,8>

of

938

1

Page 10

Gigabyte confidential

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

DDRVTT

MAAA0

R94 47/4

MAAA1

R93 47/4 R116 47/4

MAAA2

R97 47/4

MAAA3

R96 47/4 R118 47/4

MAAA4

D D

DDRVTT

C1354 0.1U/4/Y5V /16V/Z

C1356 0.1U/4/Y5V /16V/Z

C1358 0.1U/4/Y5V /16V/Z

C1360 0.1U/4/Y5V /16V/Z

C1364 0.1U/4/Y5V /16V/Z

C1366 0.1U/4/Y5V /16V/Z

C1368 0.1U/4/Y5V /16V/Z

C C

B B

C1370 0.1U/4/Y5V /16V/Z

C1372 0.1U/4/Y5V /16V/Z

C1374 0.1U/4/Y5V /16V/Z

C1378 0.1U/4/Y5V /16V/Z

C1380 0.1U/4/Y5V /16V/Z

C1384 0.1U/4/Y5V /16V/Z

C1388 0.1U/4/Y5V /16V/Z

C1392 0.1U/4/Y5V /16V/Z

C1396 0.1U/4/Y5V /16V/Z

DDRVTT DDR18V

C6 0.1U/4/Y5V/16V/Z

C5 0.1U/4/Y5V/16V/Z

C12 0.1U/4/Y5V/16V/Z

C11 0.1U/4/Y5V/16V/Z

C16 0.1U/4/Y5V/16V/Z

C15 0.1U/4/Y5V/16V/Z

C35 0.1U/4/Y5V/16V/Z

C18 0.1U/4/Y5V/16V/Z

C17 0.1U/4/Y5V/16V/Z

C29 0.1U/4/Y5V/16V/Z

C19 0.1U/4/Y5V/16V/Z

C31 0.1U/4/Y5V/16V/Z

C30 0.1U/4/Y5V/16V/Z

C32 0.1U/4/Y5V/16V/Z

C34 0.1U/4/Y5V/16V/Z

C33 0.1U/4/Y5V/16V/Z

-SWEA<5,8,9>

-SCASA<5,8,9>

-SRASA<5,8,9>

R101 47/4

MAAA5

R100 47/4 R122 47/4

MAAA6

R103 47/4

MAAA7

R102 47/4 R129 47/4

MAAA8

R105 47/4

MAAA9

R104 47/4 R131 47/4

MAAA10

R107 47/4

MAAA11

R106 47/4

MAAA12

R109 47/4

MAAA13