Gigabyte GA-E350N-USB3 Schematic rev.1.02

5

GA-E350N-USB3

4

3

2

1

OCT.20, 2010

D D

Revision : 1.02

01 COVER SHEET

02

03

04

05

06

07

C C

08

09

10

11

12

13

14

15

B B

16

BOM & PCB MODIFY HISTORY

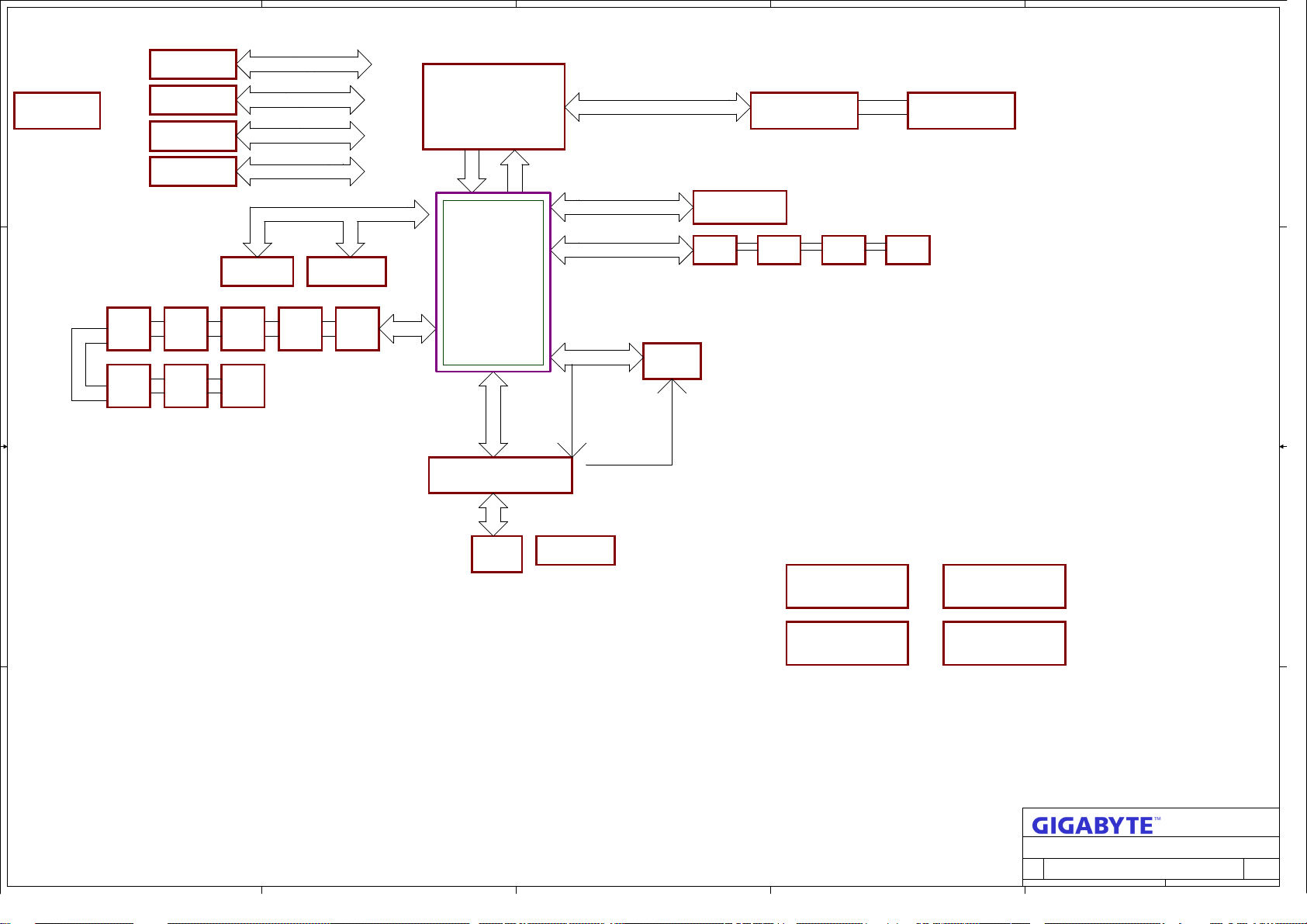

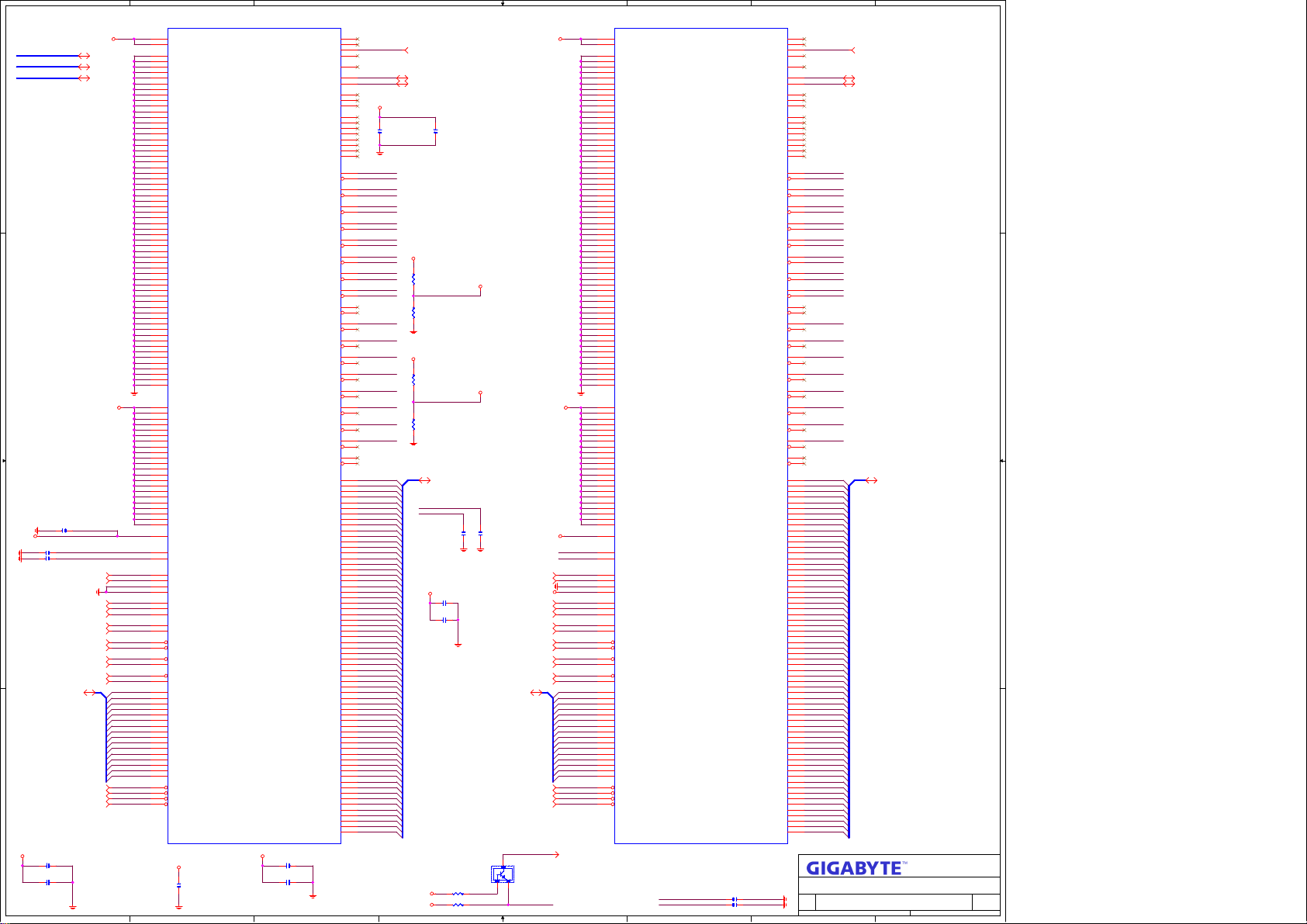

BLOCK DIAGRAM

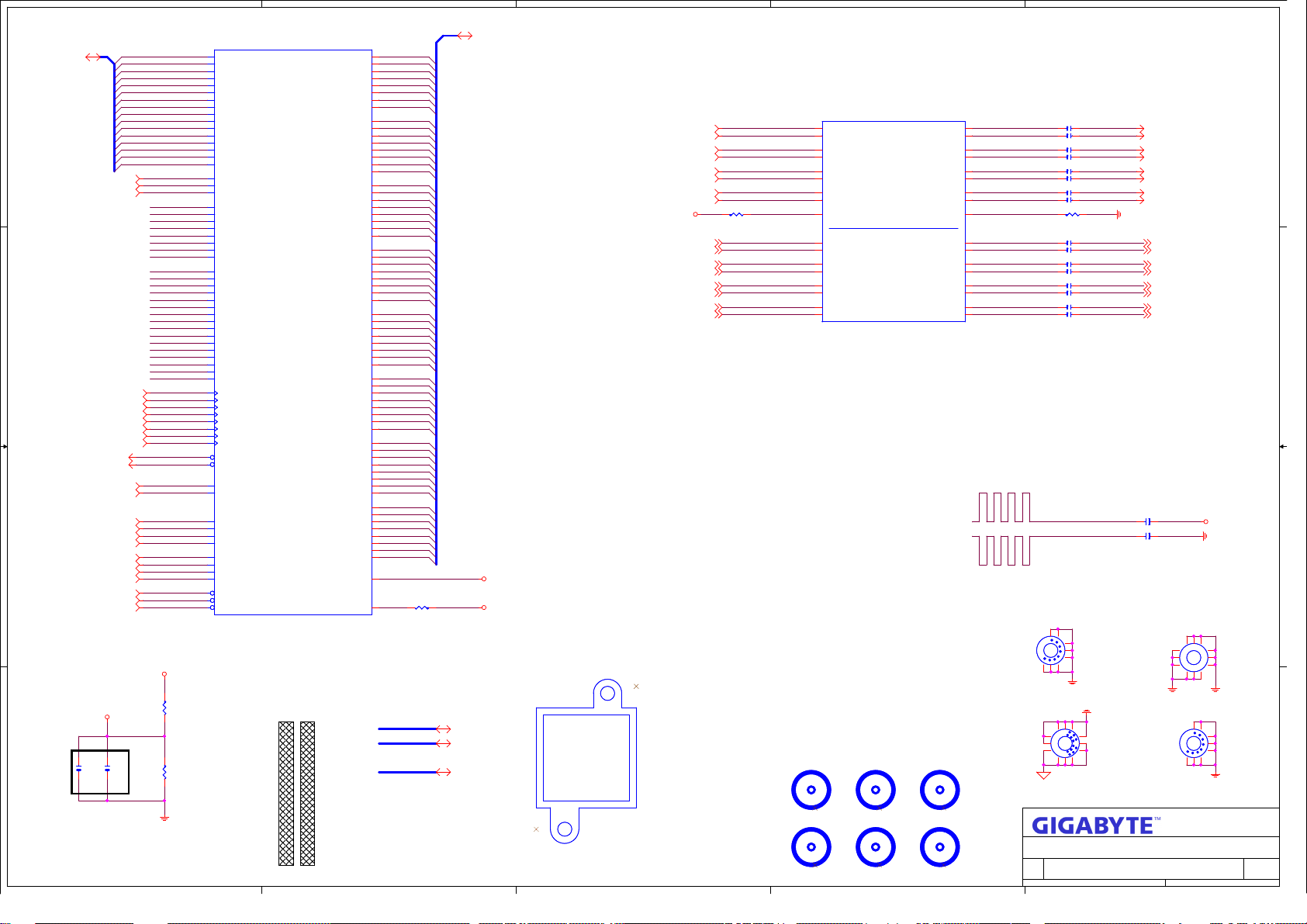

APU DDRIII, PCI_E

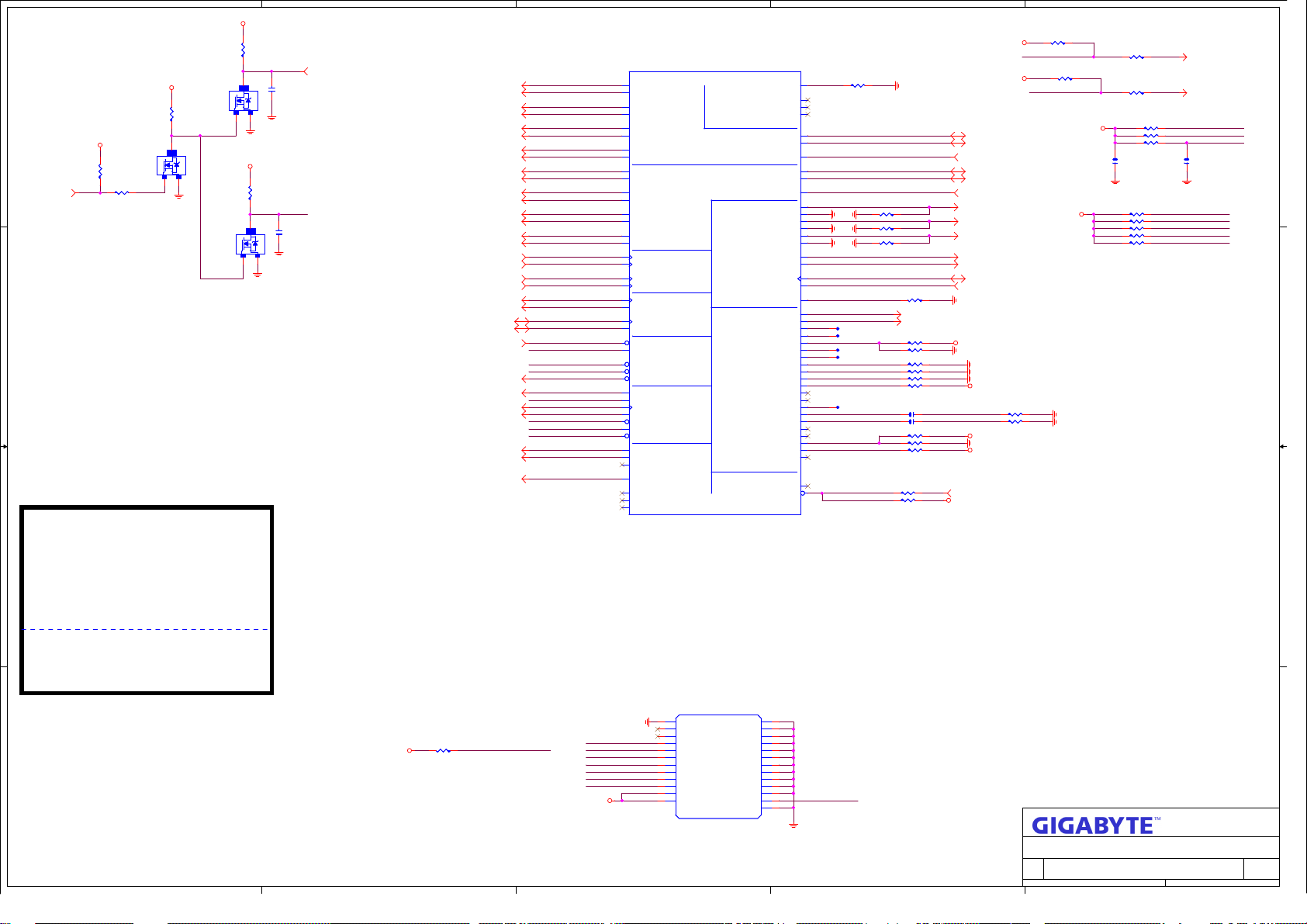

APU CONTROL

APU POWER & GND

DDRIII CHANNEL A

RTM880T-792/S

HUDSON PCIE/PCI/CPU/LPC/CLK

HUDSON ACPI/GPIO/USB/AUDIO

HUDSON SATA/IDE/HWM/SPI

HUDSON POWER & GND

PCI_E x4, VGA

HDMI ,DVI

ITE 8720 JX

ALC892 CODEC

17

18

19

20

21

22

23

A A

24

AUDIO JACK

F_USB, FAN, HWMO

POWER SEQUENCE ,EUP

VCORE (PWMISL6329+6612)

SB, APU18 V, APU10V, VCC11_DUAL POWER

DDR POWER , VCC18

LAN RTL8111E

NEC USB3 uP720200

25

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

COVER SHEET

COVER SHEET

COVER SHEET

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

1

1 24Tuesday, January 25, 2011

1 24Tuesday, January 25, 2011

1 24Tuesday, January 25, 2011

5

4

3

2

1

Model Name:GA-E350N-USB3

Component value change history

D D

2010/10/25 1.0A EVT BOM Release. PCB: 1.0

2010/12/02 1.0B DVT BOM Release. PCB:1.01

2010/12/28 1.0C PVT BOM Release. PCB:1.02 SAC1 Change 22u/8/X5R / DC2 --> 1N/4/X7R

C C

Change ItemDate

Modify from GA-BZ1 0.1

Fix PWM COMP &FB RC PR85 --> 2K for OV table 20mV/Step

delete R2430 add R8 for Power Seq. add AR24 Set HDMI

VGA RGB R1293~1295 add 10p fine tune RGB

SC1/SC2 change to 18p for SSC function

EC29 Change to 560uF for VDD10 power

U12 change to NCT3933U / Update Fan sink type

Reason

Version: 1.02

P-Code: U99054-0

Circuit or PCB layout change for next version

2010.08.23

2010.08.23

2010.12.01

2010.12.28

2010.12.28

Rev 0.1 Gerber-out

Rev 1.0 Gerber-out Change name from BZ1 to E350N-USB3

Rev 1.01 Gerber-out

Rev 1.02 Gerber-out Add F_PANEL text. SAC1 change to 22U for Vcore_NB ripple.

Rev 1.02 Gerber-out Change SAC1 Footprint (0805)

New Gerber out

Clock change to all SBCsrc, but Display clock.

Change APUCLK / SBSRC_CLK TO SRC PLL / SRCCLK_LAN Swiap to Pin27,28

ReasonDate Change Item

B B

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

BOM & PCB HISTORY

BOM & PCB HISTORY

BOM & PCB HISTORY

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

1

2 24Tuesday, January 25, 2011

2 24Tuesday, January 25, 2011

2 24Tuesday, January 25, 2011

5

4

3

2

1

FT1 CUSTOMER DESKTOP REFERENCE DESIGN

DVI

14

TMDS/HDMI

Clock

Generator

D D

RTM880T-792

8

HDMI

VGA

CON

PCIE SLOT

4X

14

13

13

NEC USB3

uP720200A

TMDS/HDMI

RGB

4X

1X PCIE INTERFACE

GIGABIT

24

RTL8111E

23

APU

FT1

DX11 IGP

OUT

HUDSON-M1

USB2.0

SATA III

AZALIA

ACPI

64bit

4,5,6

4 x1

Unified Media Interface

IN

DDRIII 1066,1333

HD AUDIO I/F

SATA III I/F

UNBUFFERED

DDRIII DIMM1

DDRIII FIRST LOGICAL DIMM

ALC892

HD AUDIO CODEC

SATA#0

16,17

SATA#1

11

UNBUFFERED

7

SATA#2

11

11

DDRIII DIMM2

DDRIII SECOND LOGICAL DIMM

SATA#3

11

7

LPC I/F

INT RTC

C C

USB-4

USB-5

USB-3

15

USB-6

USB-2

23

USB-1

23

USB-7

USB-0

23

USB 2.0

23

16,17,18,19

SPI I/F

SPI

Dual-BIOS

11

15 18 18

ITE LPC SIO

IT8720

LPC BUS

SB_SPI_CS ITE_SPI_CS1/2

15

B B

A A

5

4

KB_ MS

HW

MONITOR

15

15

DESKTOP FT1 Power

ISL6329

DDR3 MEMORY

POWER & DDRVTT

3VDUAL

3

20

2

APUVDD18 & APU10 &

VCC11_DUAL Power

Hudson CORE

POWER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

21

2122

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

1

3 24Tuesday, January 25, 2011

3 24Tuesday, January 25, 2011

3 24Tuesday, January 25, 2011

5

4

3

2

1

APUE

SR19

SR19

1K/4/1

1K/4/1

R17

H19

H18

H17

G17

H15

G18

W17

G15

R18

D15

D21

H22

AB20

AA16

R22

W22

AC20

AC21

AB16

AC16

M17

M16

M19

M18

W19

W15

W16

APUE

M_ADD0

ONTARIO (2.0)

ONTARIO (2.0)

M_ADD1

PART 1 OF 5

PART 1 OF 5

M_ADD2

J17

M_ADD3

M_ADD4

M_ADD5

M_ADD6

M_ADD7

M_ADD8

F19

M_ADD9

E19

M_ADD10

T19

M_ADD11

F17

M_ADD12

E18

M_ADD13

M_ADD14

E16

M_ADD15

M_BANK0

M_BANK1

T18

M_BANK2

F16

M_DM0

M_DM1

B19

M_DM2

M_DM3

M_DM4

P23

M_DM5

V23

M_DM6

M_DM7

M_DQS_H0

A16

M_DQS_L0

B16

M_DQS_H1

B20

M_DQS_L1

A20

M_DQS_H2

E23

M_DQS_L2

E22

M_DQS_H3

J22

M_DQS_L3

J23

M_DQS_H4

M_DQS_L4

P22

M_DQS_H5

M_DQS_L5

V22

M_DQS_H6

M_DQS_L6

M_DQS_H7

M_DQS_L7

M_CLK_H0

M_CLK_L0

M_CLK_H1

M_CLK_L1

M_CLK_H2

N18

M_CLK_L2

N19

M_CLK_H3

L18

M_CLK_L3

L17

M_RESET_L

L23

M_EVENT_L

N17

M_CKE0

F15

M_CKE1

E15

M0_ODT0

M0_ODT1

V15

M1_ODT0

U19

M1_ODT1

M0_CS_L0

T17

M0_CS_L1

M1_CS_L0

U17

M1_CS_L1

V16

M_RAS_L

U18

M_CAS_L

V19

M_WE_L

V17

MEMORY I/F

MEMORY I/F

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_VREF

M_ZVDDIO_MEM_S

APU_FT1

APU_FT1

MEM CHA

MAAA0

MAAA[0..15]<7>

D D

C C

MA_RESET_L<7>

MA_EVENT_L<7>

MODT_A0<7>

MODT_A1<7>

MODT_A2<7>

B B

MODT_A3<7>

CPUVREF

40 MILS WIDTH

CPU_M_VREF

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

SBAA0

SBAA0<7>

SBAA1

SBAA1<7>

SBAA2

SBAA2<7>

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DCLKA0

DCLKA0<7>

-DCLKA0

-DCLKA0<7>

DCLKA1

DCLKA1<7>

-DCLKA1

-DCLKA1<7>

DCLKA2

DCLKA2<7>

-DCLKA2

-DCLKA2<7>

DCLKA3

DCLKA3<7>

-DCLKA3

-DCLKA3<7>

MA_RESET_L

MA_EVENT_L

CKEA0

CKEA0<7>

CKEA1

CKEA1<7>

MODT_A0

MODT_A1

MODT_A2

MODT_A3

-CSA0

-CSA0<7>

-CSA1

-CSA1<7>

-CSA2

-CSA2<7>

-CSA3

-CSA3<7>

-SRASA

-SRASA<7>

-SCASA

-SCASA<7>

-SWEA

-SWEA<7>

DDR15V

MDA0

B14

MDA1

A15

MDA2

A17

MDA3

D18

MDA4

A14

MDA5

C14

MDA6

C16

MDA7

D16

MDA8

C18

MDA9

A19

MDA10

B21

MDA11

D20

MDA12

A18

MDA13

B18

MDA14

A21

MDA15

C20

MDA16

C23

MDA17

D23

MDA18

F23

MDA19

F22

MDA20

C22

MDA21

D22

MDA22

F20

MDA23

F21

MDA24

H21

MDA25

H23

MDA26

K22

MDA27

K21

MDA28

G23

MDA29

H20

MDA30

K20

MDA31

K23

MDA32

N23

MDA33

P21

MDA34

T20

MDA35

T23

MDA36

M20

MDA37

P20

MDA38

R23

MDA39

T22

MDA40

V20

MDA41

V21

MDA42

Y23

MDA43

Y22

MDA44

T21

MDA45

U23

MDA46

W23

MDA47

Y21

MDA48

Y20

MDA49

AB22

MDA50

AC19

MDA51

AA18

MDA52

AA23

MDA53

AA20

MDA54

AB19

MDA55

Y18

MDA56

AC17

MDA57

Y16

MDA58

AB14

MDA59

AC14

MDA60

AC18

MDA61

AB18

MDA62

AB15

MDA63

AC15

M23

AR23 39.2/4/1AR23 39.2/4/1

M22

-DQSA[0..7]

DQSA[0..7]

SBC12

SBC12

SBC31

SBC31

A A

1N/4/X7R/50V/K

1N/4/X7R/50V/K

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

SR20

SR20

1K/4/1

1K/4/1

5

A0 A1

DMA[0:7]

4

MDA[0..63] <7>

CPU_M_VREF

DDR15V

-DQSA[0..7] <7>

DQSA[0..7] <7>

DMA[0..7] <7>

NB_HEATSIN

NB_HEATSIN

CPU_HS

CPU_HS

2

1

NB_HS/[12SF2-S04028-01R]

NB_HS/[12SF2-S04028-01R]

3

GPP_RXP0<13>

GPP_RXN0<13>

GPP_RXP1<13>

GPP_RXN1<13>

GPP_RXP2<13>

GPP_RXN2<13>

GPP_RXP3<13>

GPP_RXN3<13>

APU10V

SAR2 2K/4/1SAR2 2K/4/1

A_RX0P<9>

A_RX0N<9>

A_RX1P<9>

A_RX1N<9>

A_RX2P<9>

A_RX2N<9>

A_RX3P<9>

A_RX3N<9>

APUA

AA12

AA10

AB10

AC10

AA6

AB4

AC4

AA1

AA2

Y14

Y12

Y10

AC7

AB7

Y6

Y4

Y3

1

1

APUA

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_ZVDD_10

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

K1

K1_ICT/XK1K1_ICT/X

K4

K1_ICT/XK4K1_ICT/X

ONTARIO (2.0)

ONTARIO (2.0)

PART 2 OF 5

PART 2 OF 5

1

1

PCIE I/F

PCIE I/F

UMI I/F

UMI I/F

K2

K1_ICT/XK2K1_ICT/X

K5

K1_ICT/XK5K1_ICT/X

2

GPP_RXP0

GPP_RXN0

GPP_RXP1

GPP_RXN1

GPP_RXP2

GPP_RXN2

GPP_RXP3

GPP_RXN3

P_ZVDD P_ZVSS

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_ZVSS

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

APU_FT1

APU_FT1

1

1

PCI_E slot TX need CAP close to slot side

Ref to GND.

GPP_TXP0

AB6

GPP_TXN0

AC6

GPP_TXP1

AB3

GPP_TXN1

AC3

GPP_TXP2

Y1

GPP_TXN2

Y2

GPP_TXP3

V3

GPP_TXN3

V4

AA14

A_TX0P_C

AB12

A_TX0N_C

AC12

A_TX1P_C

AC11

A_TX1N_C

AB11

A_TX2P_C

AA8

A_TX2N_C

Y8

A_TX3P_C

AB8

A_TX3N_C

AC8

PLACE THESE CAP CLOSE TO APU

Ref to GND.

AC1 0.1u/4/X7R/16V/KAC1 0.1u/4/X7R/16V/K

AC2 0.1u/4/X7R/16V/KAC2 0.1u/4/X7R/16V/K

AC3 0.1u/4/X7R/16V/KAC3 0.1u/4/X7R/16V/K

AC4 0.1u/4/X7R/16V/KAC4 0.1u/4/X7R/16V/K

AC18 0.1u/4/X7R/16V/KAC18 0.1u/4/X7R/16V/K

AC15 0.1u/4/X7R/16V/KAC15 0.1u/4/X7R/16V/K

AC16 0.1u/4/X7R/16V/KAC16 0.1u/4/X7R/16V/K

AC17 0.1u/4/X7R/16V/KAC17 0.1u/4/X7R/16V/K

SAR1 1.27K/4/1SAR1 1.27K/4/1

AC7 0.1u/4/X7R/16V/KAC7 0.1u/4/X7R/16V/K

AC8 0.1u/4/X7R/16V/KAC8 0.1u/4/X7R/16V/K

AC5 0.1u/4/X7R/16V/KAC5 0.1u/4/X7R/16V/K

AC6 0.1u/4/X7R/16V/KAC6 0.1u/4/X7R/16V/K

AC11 0.1u/4/X7R/16V/KAC11 0.1u/4/X7R/16V/K

AC12 0.1u/4/X7R/16V/KAC12 0.1u/4/X7R/16V/K

AC9 0.1u/4/X7R/16V/KAC9 0.1u/4/X7R/16V/K

AC10 0.1u/4/X7R/16V/KAC10 0.1u/4/X7R/16V/K

COUPON1

COUPON2

MH3

MH3

1

2

678

HOLE_4-RH-5MM-5PIN-1

MH1

MH1

345

2

1

12

K3

K1_ICT/XK3K1_ICT/X

K6

K1_ICT/XK6K1_ICT/X

11

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

GPP_TXPC0 <13>

GPP_TXNC0 <13>

GPP_TXPC1 <13>

GPP_TXNC1 <13>

GPP_TXPC2 <13>

GPP_TXNC2 <13>

GPP_TXPC3 <13>

GPP_TXNC3 <13>

A_TX0P <9>

A_TX0N <9>

A_TX1P <9>

A_TX1N <9>

A_TX2P <9>

A_TX2N <9>

A_TX3P <9>

A_TX3N <9>

COUPON1 COUPON/XCOUPON1 COUPON/X

COUPON2 COUPON/XCOUPON2 COUPON/X

3

4

5

HOLE_3/X

HOLE_3/X

6

7

8

HOLE_3/X

HOLE_3/X

9

10

21

21

MH8

MH8

12

MH5

MH5

HOLE_4-RH-5MM-5PIN-1HOLE_4-RH-5MM-1

COVER SHEET

COVER SHEET

COVER SHEET

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

1

VCC3

2

3

6

8

4

5

7

1

HOLE_3/X

HOLE_3/X

9

10

11

1

2

3

4

5

HOLE_3/X

HOLE_3/X

678

4 24Tuesday, January 25, 2011

4 24Tuesday, January 25, 2011

4 24Tuesday, January 25, 2011

5

4

3

2

1

VCC3

AR35 300/4/XAR35 300/4/X

DP1_AUXP <14>

DP1_AUXN <14>

DP1_HPD <14>

DP0_AUXP <14>

DP0_AUXN <14>

DP0_HPD <14>

DAC_RED <13>

DAC_GREEN <13>

DAC_BLUE <13>

DAC_HSYNC <13>

DAC_VSYNC <13>

DDCCLK <13>

DDCDATA <13>

APUVDD18

APUVDD18

AR19 51/4/1AR19 51/4/1

AR18 51/4/1AR18 51/4/1

APUVDD18

APUVDD18

AL_LDTSTP <9>

APUVDD18

DDR15V

-PROCHOT

AR32 300/4/XAR32 300/4/X

DDR15V

THERMTRIP_L

APUVDD18

VCC3

TEST35: high=>HDMI enable,

low=>HDMI disable.

AR37 0/4AR37 0/4

AR33 0/4AR33 0/4

AR43 1K/4/1AR43 1K/4/1

AR44 1K/4/1AR44 1K/4/1

AR45 300/4AR45 300/4

AC27

AC27

0.1U/4/Y5V/16V/Z

0.1U/4/Y5V/16V/Z

Cross MOAT use

AR46 1K/4/1AR46 1K/4/1

AR47 1K/4/1AR47 1K/4/1

AR49 1K/4/1AR49 1K/4/1

AR48 1K/4/1AR48 1K/4/1

AR50 1K/4/1AR50 1K/4/1

-PROCHOT_CPU <9>

THERMTRIP_CPU_L <10>

APU_SVC

APU_SVD

-CPURST

AC20

AC20

100P/4/NPO/50V/J/X

100P/4/NPO/50V/J/X

FCH_APU_SIC

FCH_APU_SID

-PROCHOT

THERMTRIP_L

ALERT_L

R2507

R2507

8.2K/4/1

8.2K/4/1

C1752

C1752

0.1u/4/Y5V/16V/Z/X

0.1u/4/Y5V/16V/Z/X

CPU_PWRGD

C1790

C1790

0.1u/4/Y5V/16V/Z/X

0.1u/4/Y5V/16V/Z/X

PWM_PWRGD <20>

Input clock for DisplayPort mode

Input clock for TMDS (DVI) mode

To DVI switch

To DP switch

DP1_TXP0<14>

DP1_TXN0<14>

DP1_TXP1<14>

DP1_TXN1<14>

DP1_TXP2<14>

DP1_TXN2<14>

DP1_TXP3<14>

DP1_TXN3<14>

DP0_TXP0<14>

DP0_TXN0<14>

DP0_TXP1<14>

DP0_TXN1<14>

DP0_TXP2<14>

DP0_TXN2<14>

DP0_TXP3<14>

DP0_TXN3<14>

APUCLK_H<8>

APUCLK_L<8>

DISP_CLK_H<8>

DISP_CLK_L<8>

APU_SVC<20>

APU_SVD<20>

FCH_APU_SIC<10>

FCH_APU_SID<10>

-CPURST<9,10>

ALERT_L<11>

CPU_TDI<10>

CPU_TCK<10>

CPU_TMS<10>

NBCOREFB+<20>

COREFB+<20>

COREFB-<20>

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

APUCLK_H

APUCLK_L

DISP_CLK_H

DISP_CLK_L

APU_SVC

APU_SVD

FCH_APU_SIC

FCH_APU_SID

-CPURST

CPU_PWRGD

-PROCHOT

THERMTRIP_L

ALERT_L

CPU_TDI

CPU_TDO

CPU_TCK

CPU_TMS

CPU_TRSTCPU_DBRDY

CPU_DBREQ

NBCOREFB+

COREFB+

COREFB-

3VDUAL

R2506

R2506

8.2K/4

D D

R2756

R2756

300/4

300/4

CPU_PG_SB<9>

C C

8.2K/4

DDR15V

Q309

Q309

G S

G S

R1 1K/4/1R1 1K/4/1

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

3

D

D

2

1

3

Q310

Q310

D

D

G S

G S

2

1

2N7002/SOT23/25pF/5

2N7002/SOT23/25pF/5

APUVDD18

3

Q355

Q355

D

D

G S

G S

2

2N7002/SOT23/25pF/5

2N7002/SOT23/25pF/5

R2754

R2754

300/4

300/4

1

APU_VDD_RUN = VCORE

CPU_VDDA_RUN = VDDA25

B B

VLDT_RUN = VCC12_HT

W11

A8

B8

B9

A9

D10

C10

A10

B10

B5

A5

D6

C6

A6

B6

D8

C8

V2

V1

D2

D1

J1

J2

P3

P4

T3

T4

U1

U2

T2

N2

N1

P1

P2

M4

M3

M1

F4

G1

F3

F1

B4

V5

APUB

APUB

TDP1_TXP0

TDP1_TXN0

TDP1_TXP1

TDP1_TXN1

TDP1_TXP2

TDP1_TXN2

TDP1_TXP3

TDP1_TXN3

LTDP0_TXP0

LTDP0_TXN0

LTDP0_TXP1

LTDP0_TXN1

LTDP0_TXP2

LTDP0_TXN2

LTDP0_TXP3

LTDP0_TXN3

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

SVC

SVD

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

VDDIO_MEM_S_SENSE

VSS_SENSE

RSVD_1

RSVD_2

RSVD_3

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DP MISC

DP MISC

DISPLAYPORT 0 DISPLAYPORT 1

DISPLAYPORT 0 DISPLAYPORT 1

CLK

CLK

SER

SER

JTAG CTRL

JTAG CTRL

ONTARIO (2.0)

ONTARIO (2.0)

PART 3 OF 5

PART 3 OF 5

TEST4

TEST5

TEST6

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST31

TEST35

TEST36

TEST37

TEST38

AR26 150/4/1AR26 150/4/1

H3

G2

H2

H1

DP1_AUXP

B2

DP1_AUXN

C2

DP1_HPD

C1

DP0_AUXP

A3

DP0_AUXN

B3

DP0_HPD

D3

C12

D13

A12

B12

A13

B13

DAC_HSYNC

E1

DAC_VSYNC

E2

DDCCLK

F2

DDCDATA

D4

DAC_RSET

D12

APU_THERMDA

R1

APU_THERMDC

R2

R6

TP3TP3

T5

TP14TP14

APU_TEST15

E4

K4

TP15TP15

L1

TP16TP16

APU_TEST18

L2

APU_TEST19

M2

APU_TEST25H

K1

APU_TEST25L

K2

L5

M5

M21

TP13TP13

APU_TEST33H

J18

APU_TEST33L

J19

U15

T15

APU_TEST35

H4

APU_TEST36

N5

R5

K3

-DMA_ACTIVE

T1

AR38 150/4/1AR38 150/4/1

AR39 150/4/1AR39 150/4/1

AR40 150/4/1AR40 150/4/1

AR41 499/4/1AR41 499/4/1

APU_THERMDA <11,15>

APU_THERMDC <11,15>

AR1 1K/4/1/XAR1 1K/4/1/X

AR2 1K/4/1AR2 1K/4/1

AR6 1K/4/1AR6 1K/4/1

AR7 1K/4/1AR7 1K/4/1

AR8 510/4/1AR8 510/4/1

AR13 510/4/1AR13 510/4/1

ABC4 0.1U/4/Y5V/16V/ZABC4 0.1U/4/Y5V/16V/Z

ABC5 0.1U/4/Y5V/16V/ZABC5 0.1U/4/Y5V/16V/Z

AR24 1K/4/1AR24 1K/4/1

AR21 1K/4/1/XAR21 1K/4/1/X

AR22 1K/4/1/XAR22 1K/4/1/X

AR42 0/4AR42 0/4

AR30 1K/4/1AR30 1K/4/1

DP_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

TDP1_AUXP

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_REDB

DAC_GREEN

DAC_GREENB

DAC_BLUE

DAC_BLUEB

DAC_HSYNC

VGA DAC

VGA DAC

TEST

TEST

DAC_VSYNC

DAC_SCL

DAC_SDA

DAC_ZVSS

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST33_H

TEST33_L

TEST34_H

TEST34_L

DMAACTIVE_L

APU_FT1

APU_FT1

APU_VDDIO_SUS = DDR15V

CPU_VDDR = CPU_VDDR12

VLDT_A = VCC12_HT

VLDT_B = HT12B

HDT

HDT

1

3

CPU_DBREQ

AR36 300/4AR36 300/4

DDR15V

A A

CPU_DBREQ

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRSTCPU_TDO

DDR15V

5

4

5

7

9

11

13

15

17

19

21

23

KEY

KEY

ASP-68200-07/X

ASP-68200-07/X

3

2

4

6

8

10

12

14

16

18

20

22

-CPURST

24

26

Title

Title

Title

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

COVER SHEET

COVER SHEET

COVER SHEET

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

1

5 24Tuesday, January 25, 2011

5 24Tuesday, January 25, 2011

5 24Tuesday, January 25, 2011

VCORE

VCORE_NB

DDR15V

W18

E11

E13

F12

G11

G13

H12

K11

K13

L10

L12

L14

M11

M12

M13

N10

N12

N14

P11

P13

G16

G19

E17

L16

L19

N16

R16

R19

U16

E5

E6

F5

F7

G6

G8

H5

H7

M6

M8

N7

R8

E8

F9

H9

J16

J6

J8

L7

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDCR_NB_10

VDDCR_NB_11

VDDCR_NB_12

VDDCR_NB_13

VDDCR_NB_14

VDDCR_NB_15

VDDCR_NB_16

VDDCR_NB_17

VDDCR_NB_18

VDDCR_NB_19

VDDCR_NB_20

VDDCR_NB_21

VDDCR_NB_22

VDDIO_MEM_S_1

VDDIO_MEM_S_2

VDDIO_MEM_S_3

VDDIO_MEM_S_4

VDDIO_MEM_S_5

VDDIO_MEM_S_6

VDDIO_MEM_S_7

VDDIO_MEM_S_8

VDDIO_MEM_S_9

VDDIO_MEM_S_10

VDDIO_MEM_S_11

APUC

APUC

ONTARIO (2.0)

ONTARIO (2.0)

PART 4 OF 5

PART 4 OF 5

POWER

POWER

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

VDD_18_5

VDD_18_6

VDD_18_7

VDD_18_DAC

VDDPL_10

VDD_10_1

VDD_10_2

VDD_10_3

VDD_10_4

VDD_33

APU_FT1

APU_FT1

APUVDD18

U8

W8

CHECK

CHECK

CHECKCHECK

U6

U9

W6

POWER

POWER

POWERPOWER

T7

V7

CHECK

CHECK

CHECKCHECK

POWER

POWER

POWERPOWER

W9

SAC6 1u/4/X5R/6.3V/KSAC6 1u/4/X5R/6.3V/K

SAC7 1u/4/X5R/6.3V/KSAC7 1u/4/X5R/6.3V/K

AC24 1U/6/Y5V/10V/ZAC24 1U/6/Y5V/10V/Z

APUVDD18

Ref to GND.

VDD_18DAC=> min 20mil, and 20mil away from others.

CHECK

CHECK

CHECKCHECK

POWER

POWER

POWERPOWER

U11

SAC4 1u/4/X5R/6.3V/KSAC4 1u/4/X5R/6.3V/K

SAC5 1u/4/X5R/6.3V/KSAC5 1u/4/X5R/6.3V/K

AC23 1U/6/Y5V/10V/ZAC23 1U/6/Y5V/10V/Z

APU10V

Ref to GND.

VDDPL_10=> min 15mil, and 20mil away from others.

APU10V

U13

W13

CHECK

CHECK

CHECKCHECK

V12

T12

POWER

POWER

POWERPOWER

A4

AC19 1u/4/X5R/6.3V/KAC19 1u/4/X5R/6.3V/K

VCC3

Ref to GND.

VDD_33=> min 20mil, and 20mil away from others.

APUD

APUD

ONTARIO (2.0)

ONTARIO (2.0)

VSS_1

A7

B7

B11

B17

B22

C4

D5

D7

D9

D11

D14

B15

D17

D19

E7

E9

E12

E20

F8

F11

F13

G4

G5

G7

G9

G12

G20

G22

H6

H11

H13

J4

J5

J7

J20

K10

K14

L4

L6

L8

L11

L13

L20

L22

M7

N4

N6

N8

N11

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

PART 5 OF 5

PART 5 OF 5

GROUND

GROUND

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSSBG_DAC

APU_FT1

APU_FT1

N13

N20

N22

P10

P14

R4

R7

R20

T6

T9

T11

T13

U4

U5

U7

U12

U20

U22

V8

V9

V11

V13

W1

W2

W4

W5

W7

W12

W20

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

AA4

AA22

AB2

AB5

AB9

AB13

AB17

AB21

AC5

AC9

AC13

A11

VCORE_NB

DDR15V

C1324

C1324

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

C1344

C1344

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

C1343

C1343

1U/6/X7R/16V/K

1U/6/X7R/16V/K

C1325

C1325

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

DDR15V

SC8

SC8

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

SAC8

SAC8

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

C1337

C1337

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

C1345

C1345

0.01u/4/X7R/25V/K

0.01u/4/X7R/25V/K

C1346

C1346

180P/4/NPO/50V/J

180P/4/NPO/50V/J

C1319

C1319

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

DDR15V

SC2

SC2

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

SAC1

SAC1

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

BUTTOM SIDE

SC4

SC4

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

SAC2

SAC2

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

SC5

SC5

0.01U/4/X7R/25V/K

0.01U/4/X7R/25V/K

SAC3

SAC3

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

SC6

SC6

180P/4/NPO/50V/J

180P/4/NPO/50V/J

VCORE

SC11

SC11

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

BUTTOM SIDE

SC14

SC14

0.01U/4/X7R/25V/K

0.01U/4/X7R/25V/K

SC15

SC15

180P/4/NPO/50V/J

180P/4/NPO/50V/J

VCORE

SC16

SC16

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

BUTTOM SIDE

SC17

SC17

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

SC20

SC19

SC19

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

SC20

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

CPU POWER & GND

CPU POWER & GND

CPU POWER & GND

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

SC26

SC26

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

6 24Tuesday, January 25, 2011

6 24Tuesday, January 25, 2011

6 24Tuesday, January 25, 2011

SC28

SC28

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

8

-DQSA[0..7]

DQSA[0..7]

DMA[0..7]

D D

C C

VCC3

C277 0.1u/4/X7R/16V/KC277 0.1u/4/X7R/16V/K

C279 0.1u/4/X7R/16V/KC279 0.1u/4/X7R/16V/K

B B

A A

DDRVTT Decouple

DDRVTT

DDRVTT

-DQSA[0..7] <4>

DQSA[0..7] <4>

DMA[0..7] <4>

DDR15V

C275 0.1u/4/Y5V/16V/ZC275 0.1u/4/Y5V/16V/Z

VREFCA_A

VREFDQ_A

SMBCLK

SMBCLK<8,10,20,21>

SMBDATA

SMBDATA<8,10,20,21>

SBAA2

SBAA2<4>

SBAA1

SBAA1<4>

SBAA0

SBAA0<4>

CKEA1

CKEA1<4>

CKEA0

CKEA0<4>

-CSA1

-CSA1<4>

-CSA0

-CSA0<4>

-DCLKA1

-DCLKA1<4>

DCLKA1

DCLKA1<4>

-DCLKA0

-DCLKA0<4> -DCLKA2<4>

DCLKA0 DCLKA2

DCLKA0<4>

-SCASA<4>

-SRASA<4>

-SWEA<4>

BC7

BC7

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

BC8

BC8

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

MA_RESET_L

-SCASA

-SRASA

-SWEA

MAAA[0..15]<4>

MA_RESET_L<4>

8

7

DDR3_0

DDR3_0

120

VTT

240

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

DDRVTT

BC152

BC152

4.7U/6/X5R/6.3V/K

4.7U/6/X5R/6.3V/K

7

DDR15V

6

FREE

FREE

FREE

FREE

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DQS0

DQS0*

DQS1

DQS1*

DQS2

DQS2*

DQS3

DQS3*

DQS4

DQS4*

DQS5

DQS5*

DQS6

DQS6*

DQS7

DQS7*

DQS8

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DDR3/240/BU/VA/D

DDR3/240/BU/VA/D

BC2

BC2

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

BC3

BC3

0.1u/4/Y5V/16V/Z

0.1u/4/Y5V/16V/Z

6

48

49

187

198

79

77

195

68

53

167

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

MA_EVENT_L

MODT_A1

MODT_A0

DDR15V

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MA_EVENT_L <4>

MODT_A1 <4>

MODT_A0 <4>

BC10

BC10

22U/8/X5R/6.3V/M

22U/8/X5R/6.3V/M

DDR15V

DDR15V

100p/4/NPO/50V/J/X

100p/4/NPO/50V/J/X

DDR15V

DDR15V

5

BC11

BC11

22U/8/X5R/6.3V/M

22U/8/X5R/6.3V/M

R101

R101

1K/4/1

1K/4/1

VREFDQ_A

Trace min 10/10

R23

R23

1K/4/1

1K/4/1

R24

R24

1K/4/1

1K/4/1

VREFCA_A

Trace min 10/10

R2

1K/4/1R21K/4/1

MDA[0..63] <4>

SMBDATA

SMBCLK

C205

C205

DDR15V

AR55 1K/4/1AR55 1K/4/1

AR56 1K/4/1AR56 1K/4/1

5

VREFDQ_A

VREFCA_A

C206

C206

100p/4/NPO/50V/J/X

100p/4/NPO/50V/J/X

BC131

BC131

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

BC125

BC125

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

DDRVTT

SMBCLK<8,10,20,21>

SMBDATA<8,10,20,21>

VCC3

SBAA2<4>

SBAA1<4>

SBAA0<4>

CKEA1<4>

CKEA0<4>

-CSA3<4>

-CSA2<4>

-DCLKA3<4>

DCLKA3<4>

DCLKA2<4>

MAAA[0..15]<4>

MA_RESET_L<4>

-SCASA<4>

-SRASA<4>

-SWEA<4>

MEM_HOTL

Q9

Q9

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

SOT23

SOT23

132

MA_EVENT_L

DDR15V

VCC3

4

VREFCA_A

VREFDQ_A

SMBCLK

SMBDATA

SBAA2

SBAA1

SBAA0

CKEA1

CKEA0

-CSA3

-CSA2

-DCLKA3

DCLKA3

-DCLKA2

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

MA_RESET_L

-SCASA

-SRASA

-SWEA

MEM_HOTL <10>

4

3

DDR3_1

DDR3_1

120

VTT

240

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

VREFDQ_A

VREFCA_A

3

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DDR3/240/BU/VA/D

DDR3/240/BU/VA/D

C528 1N/4/X7R/50V/KC528 1N/4/X7R/50V/K

C532 1N/4/X7R/50V/KC532 1N/4/X7R/50V/K

2

48

FREE

49

FREE

MA_EVENT_L

187

FREE

198

FREE

79

RSVD

77

ODT1

195

ODT0

68

53

167

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

7

DQS0

6

DQS0*

16

DQS1

15

DQS1*

25

DQS2

24

DQS2*

34

DQS3

33

DQS3*

85

DQS4

84

DQS4*

94

DQS5

93

DQS5*

103

DQS6

102

DQS6*

112

DQS7

111

DQS7*

43

DQS8

42

DQS8*

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

MODT_A3

MODT_A2

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

2

MA_EVENT_L <4>

MODT_A3 <4>

MODT_A2 <4>

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

MDA[0..63] <4>

DDR III CHANNEL B

DDR III CHANNEL B

DDR III CHANNEL B

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

1

7 24Tuesday, January 25, 2011

7 24Tuesday, January 25, 2011

7 24Tuesday, January 25, 2011

1

5

VCC3

BC893

BC892

BC892

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

D D

C C

SC1 18P/4/NPO/50V/JSC1 18P/4/NPO/50V/J

SC3 18P/4/NPO/50V/JSC3 18P/4/NPO/50V/J

B B

BC893

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

X7

X7

BC894

BC894

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

14.318M/16p/20ppm/49US/40/D

14.318M/16p/20ppm/49US/40/D

SMBCLK<7,10,20,21>

SMBDATA<7,10,20,21>

VCC3

RESET<19>

3VDUAL

R63 22/4R63 22/4

R64 1K/4/1/XR64 1K/4/1/X

BC895

BC895

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

VCC3

R62 1K/4/1R62 1K/4/1

BC896

BC896

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

1

5

20

21

30

37

42

45

49

9

6

12

19

22

29

33

36

43

44

48

54

7

8

13

14

52

53

4

BC897

BC897

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

U4

U4

VDDHTT

VDDREF

VDDSRC

VDDSRC

VDDSB

VDDATIG

VDD

VDDA

VDDCPU

VDD48

GNDREF

GND48

GNDSRC

GNDSRC

GNDSB

GNDATIG

GNDATIG

GND

GNDA

GNDCPU

GNDHTT

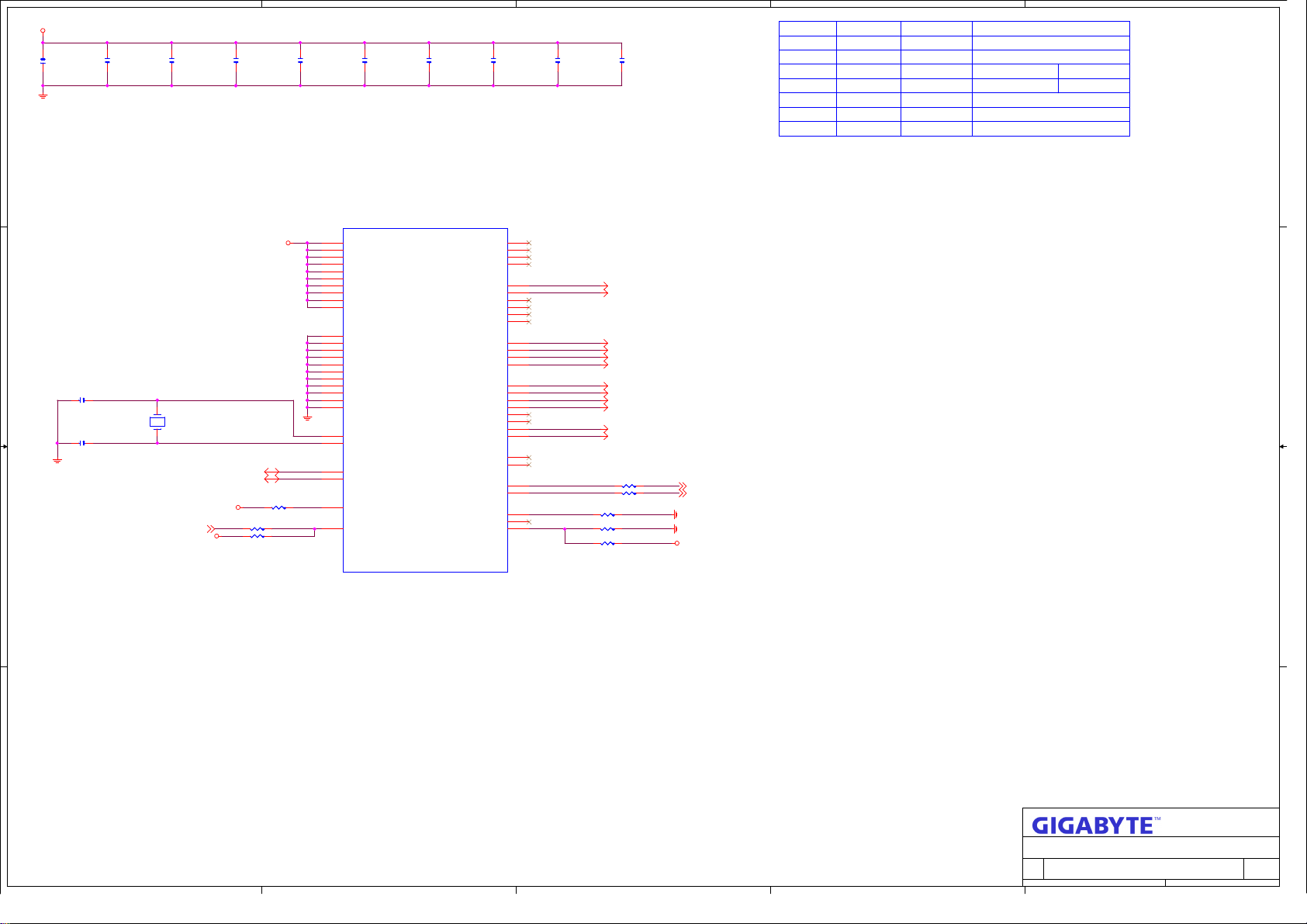

9LPRS482 / RTM880T-792

9LPRS482 / RTM880T-792

X1

X2

SMBCLK

SMBDAT

*PD#

*RESTORE#

BC898

BC898

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

CPUK8_0T

CPUK8_0C

CPUK8_1T

CPUK8_1C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

HTT0T/66M

HTT0C/66M

**SEL_HTT66/REF0

RTM880T-792/S

RTM880T-792/S

BC899

BC899

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

ATIG0T

ATIG0C

ATIG1T

ATIG1C

ATIG2T

ATIG2C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

SRC2C

SRC3T

SRC3C

48Mz_0

48Mz_1

REF1

REF2

51

50

47

46

41

40

39

38

35

34

32

31

28

27

26

25

24

23

18

17

16

15

56

55

11

10

4

3

2

SIO_CLOCK_R

48M_USB_R

BC59

BC59

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

DISP_CLK_H <5>

DISP_CLK_L <5>

APUCLK_H <5>

APUCLK_L <5>

SRCCLK_LAN <23>

-SRCCLK_LAN <23>

USB3_CLK <24>

-USB3_CLK <24>

SBSRC_CLKP <9>

SBSRC_CLKN <9>

SRCCLK_3GIO_B <13>

-SRCCLK_3GIO_B <13>

R58 22/4R58 22/4

R71 22/4R71 22/4

R72 1K/4/1R72 1K/4/1

R73 8.2K/4/1/XR73 8.2K/4/1/X

R74 8.2K/4/1/XR74 8.2K/4/1/X

3

BC903

BC903

0.1u/4/X7R/16V/K

0.1u/4/X7R/16V/K

LPC48 <15>

USB48M <10>

VCC3

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK*

GPP_REFCLK

GPPSB_REFCLK 100M DIFF 100M DIFF

RS740 RX780 RS780

66M SE(SE)

NC

14M SE (3.3V) 14M SE (1.8V) 14M SE (1.1V)

NC NC vref

100M DIFF

NC

100M DIFF

* the GFX_REFCLK input is required for all cases

2

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF(OUT)

1

100M DIFF

100M DIFF

A A

Title

Title

Title

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

RTM880T-792

RTM880T-792

RTM880T-792

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

GA-E350N-USB3 1.02

1

8 24Tuesday, January 25, 2011

8 24Tuesday, January 25, 2011

8 24Tuesday, January 25, 2011

Loading...

Loading...