Page 1

A

B

C

D

E

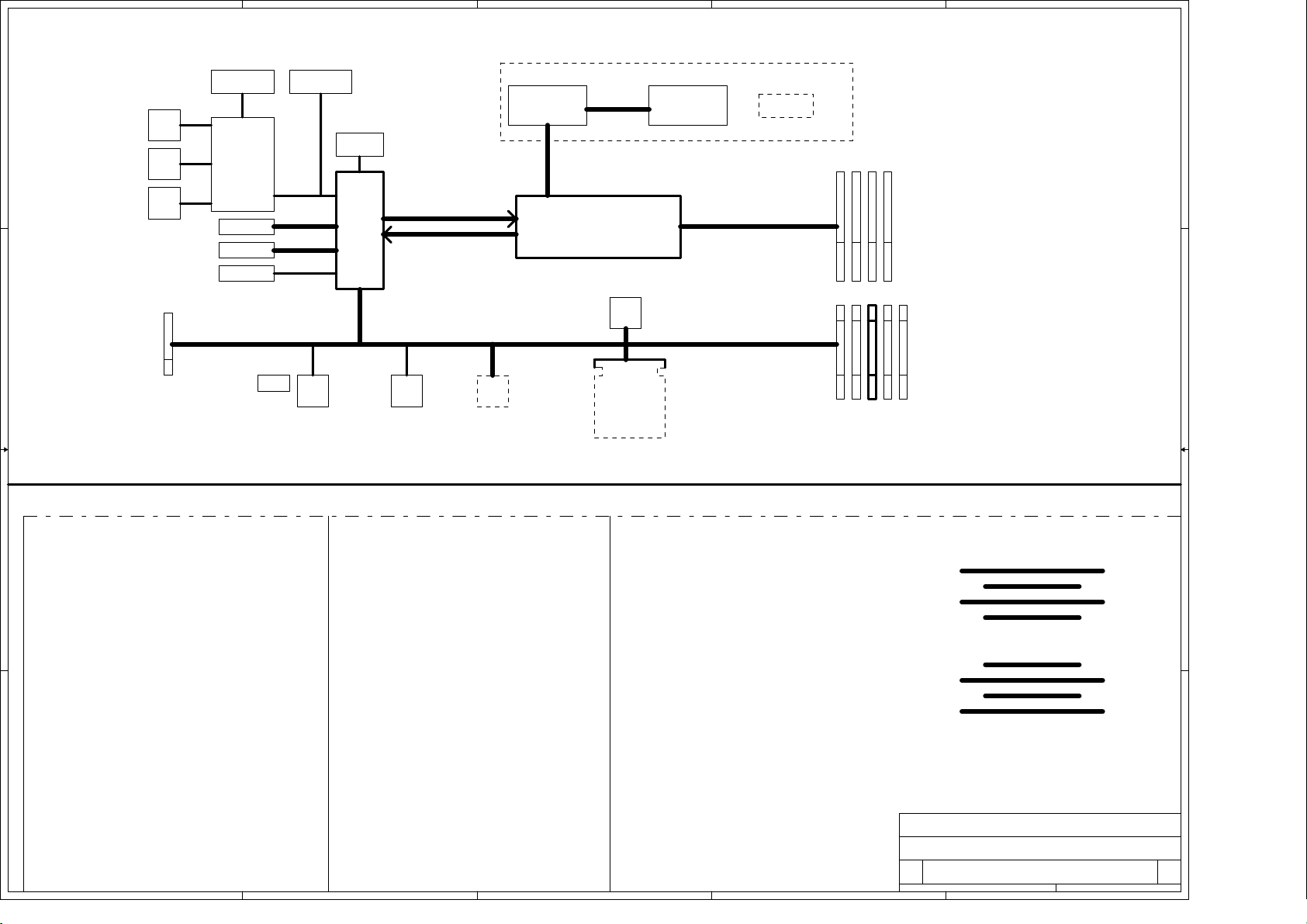

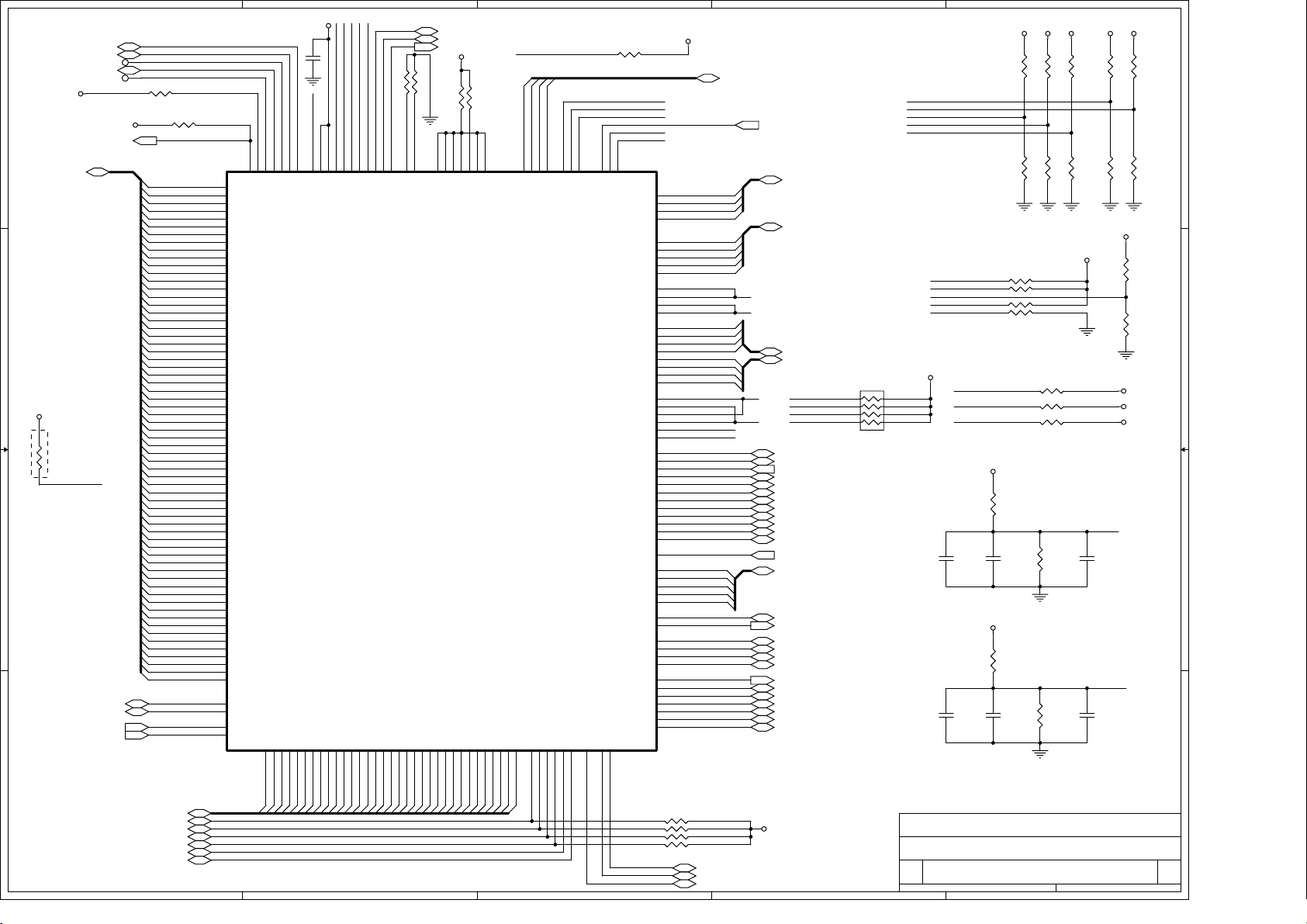

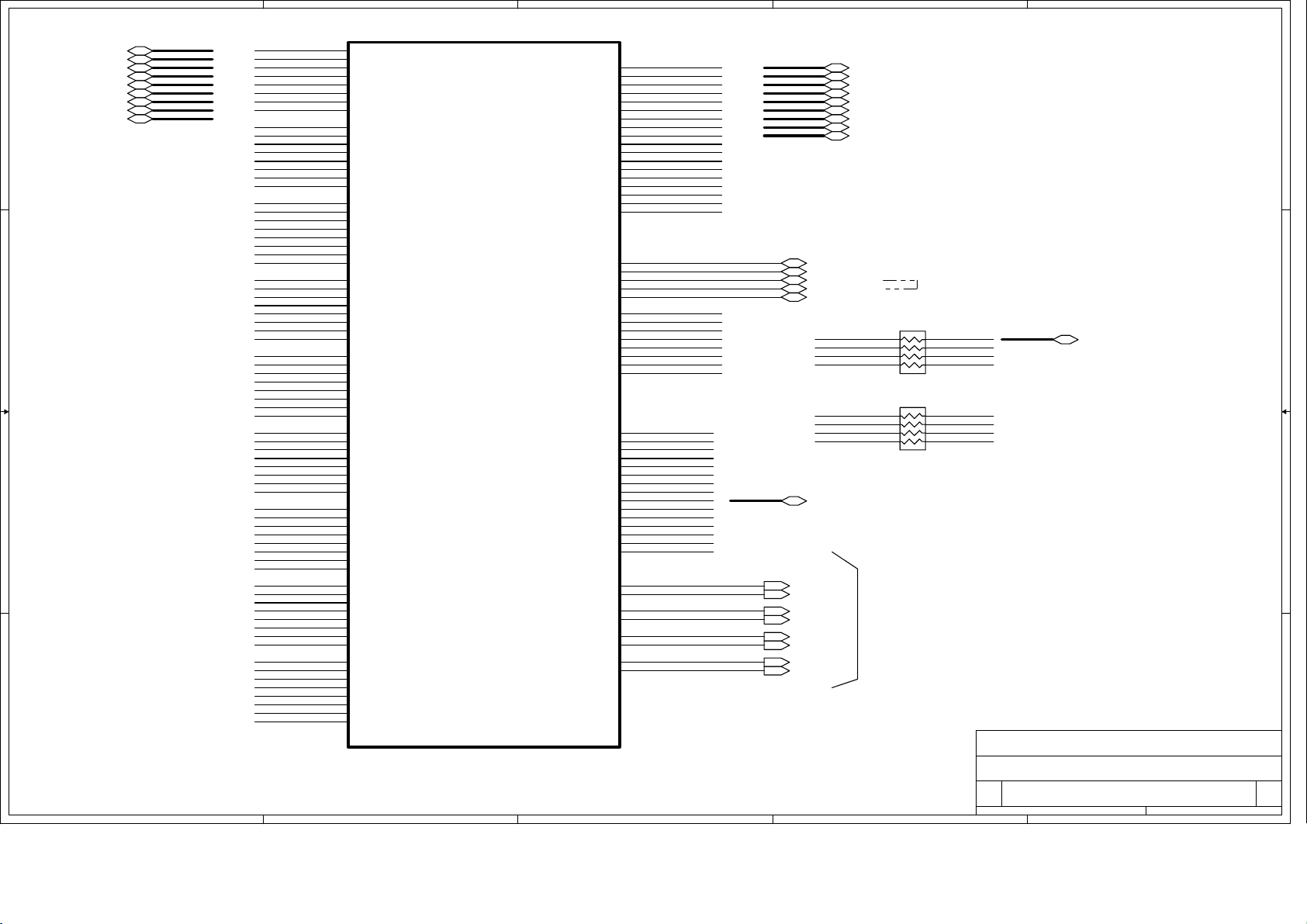

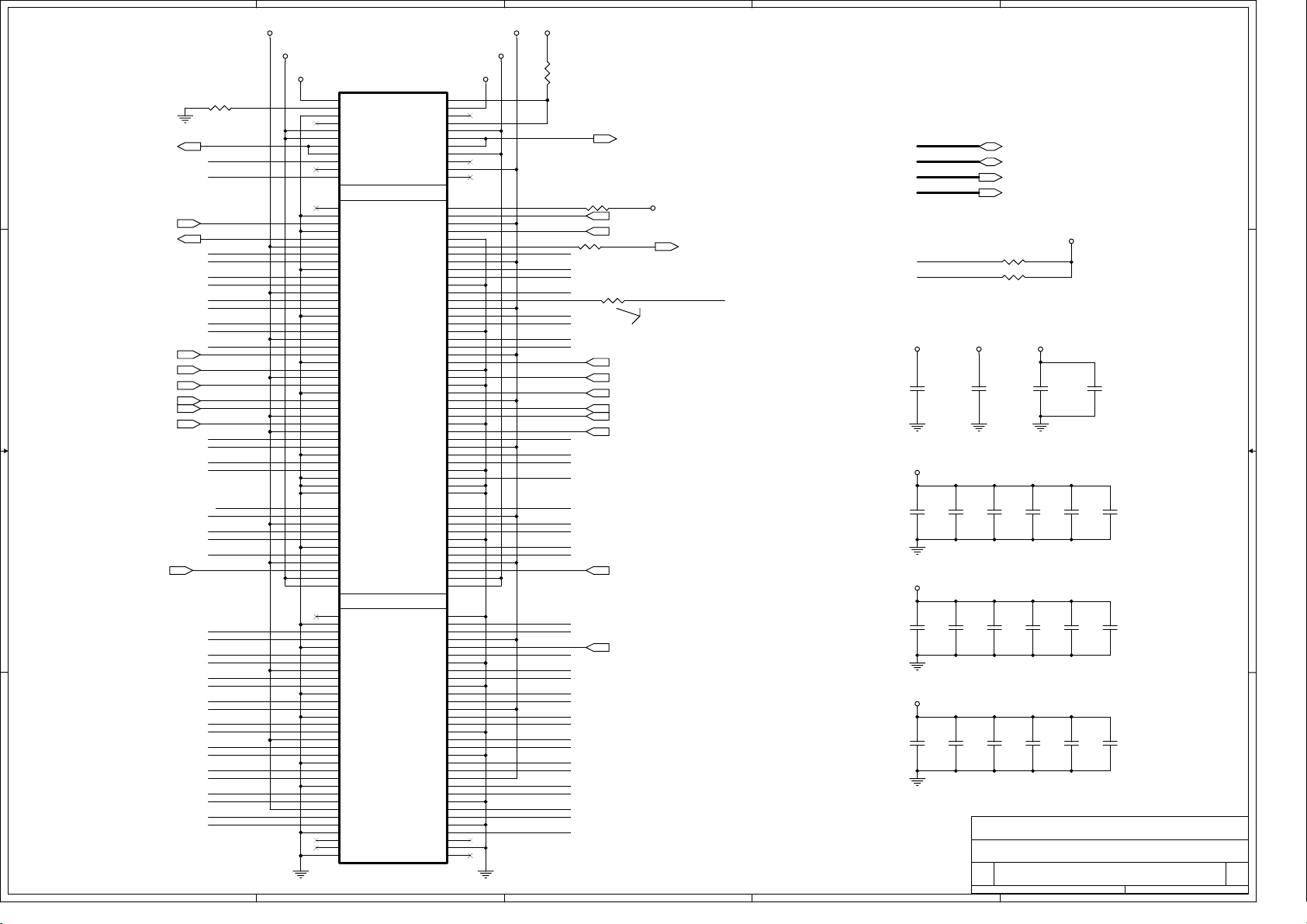

Dual Prestonia or Nocona 533MHz CPUs

FLASH

4 4

COM

x 2

PP

FDD

RAID

0/1/5

X-BUS

SIO NS

PC87417

IDE 1

IDE 2

IDE 3

IPMI

Module

LPC

Bus

ATA-100

ATA-100

ATA-66

USB

x 4

CSB6

Thin

IMB

200Mhz x 2

(800MB/Sec)

P4 Xeon

CPU 1

CPU Host Bus

(533MHz)

4GB/Sec

CMIC-SL

533MHz

BSP

P4 Xeon

CPU 2

VRM 9.1

MEMORY I/F

(266Mhz)

2.1GB/Sec

GA-8EGXDREL

V1.0

4GB Max

Registered ECC DDR266 DIMM x 4

FRODO

PCI

3 3

PCI BUS 0

64b/33Mhz

SATA

PCI 64b/33Mhz

4/8 PORTs

GLAN2 GLAN1

PCISLOT_6

33MHz/32b

8MB

SDRAM

ATi

Rage

XL

Intel

82540PM

PCI

32b/33Mhz

Intel

82545PM

PCI

64b/33Mhz

Raptor - Zero

Canhhel RAID

PCISLOT_1-5

33MHz/64b

INDEX

PAGE # DESCRIPTION

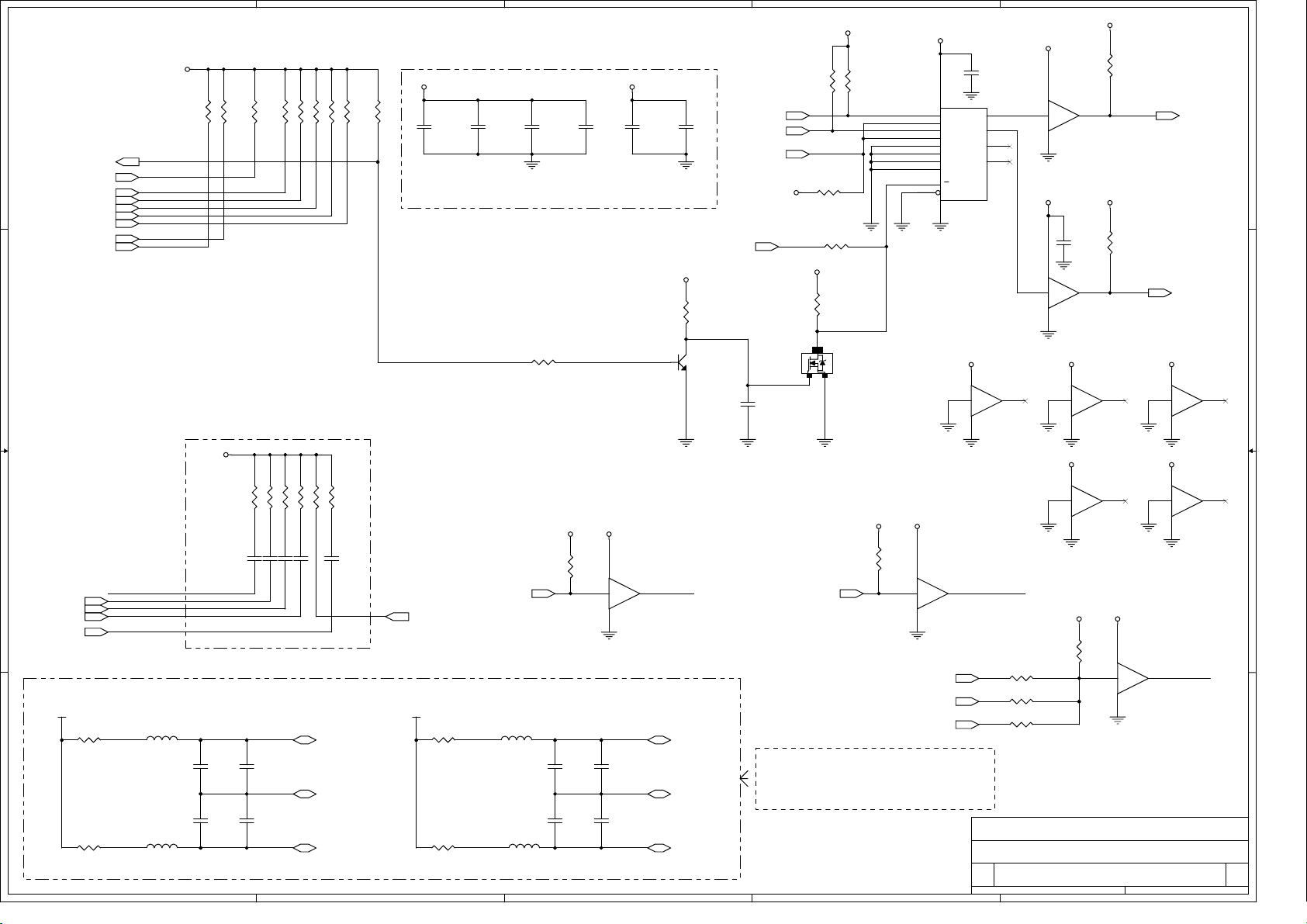

01. BLOCK DIAGRAM & INDEX

02.

RESET_&_CLOCK_BLOCK DIAGRAM

2 2

03.

04.

CPU_END_1_PWR

05.

CPU_MID_2

06.

CPU_MID_2_PWR

07.

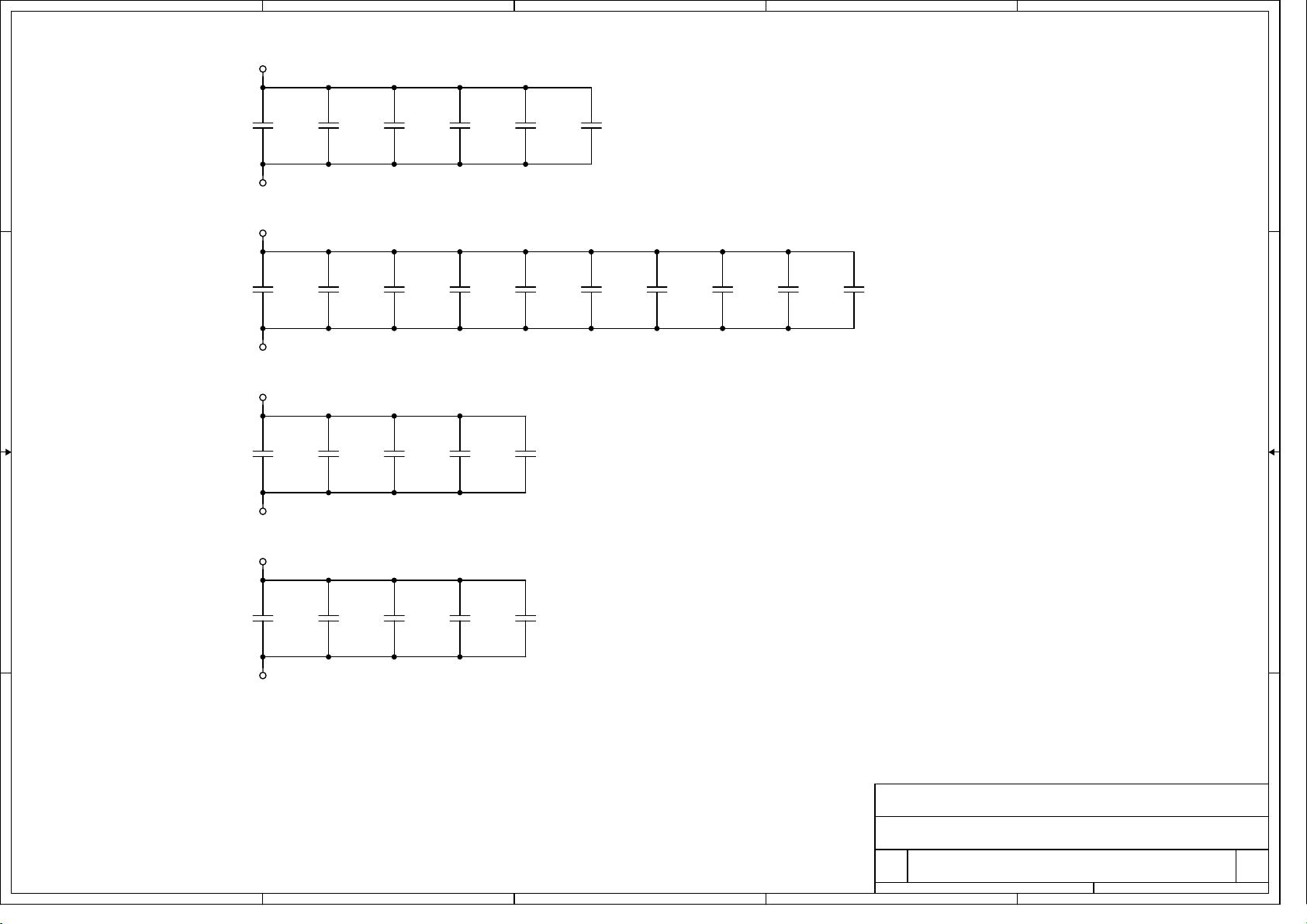

CPU_CAPS

VID_CONTROL_&_RESET_BUFFER

08.

09.

STITCHING CAP

10.

CPU_LEVEL_SHIFT_TERM

CMIC_CPU_IF

11.

CMIC_CIOB_IF

12.

CMIC_MEM_IF

13.

CMIC_PWR

14.

15.

CMIC_STRAPPING

16.

DDR_DIMM_1_&_2

17.

1 1

DDR_DIMM_3_&_4

18.

DDR_SERIAL_TERM

19.

DDR_1.25V_STLL2_TERM

20.

CLK_GENERATOR

21.

ZCR_RAPTOR

22.

GLAN2_82540EM_PCI

23.

GLAN2_82540EM_POWER

A

PAGE # DESCRIPTION PAGE # DESCRIPTION

24.

GLAN2_82540EM_RJ45

25.

PCI_X_SLOT1

26.

PCI_X_SLOT2

27.

PCI_X_SLOT_3_&_RADIOS

28.

PCI_X_SLOT4

29.

FRODO_PCI

30.

FRODO_PORT_0-3

31.

FRODO_PORT_4-7

32.

FRODO_POWER

33.

GLAN1_82545EM_PCI

34.

GLAN1_82545EM_ PWR

35.

GLAN1_82545EM_RJ45

36.

CSB6_PCI_&_IDE

37.

CSB6_IMB_GPORTS

38.

CSB6_POWER

39

PCI_IRQ_LATCH_LOGIC

40

PCI_SLOT_5_&_PULL_UP

41

PCI_SLOT_6

42

BLANK

43

ATI_RAGE_XL

44

FRAME_BUFFER_SDRAM

45

VGA_CON

46

PCI_ARBITOR

B

C

BLANK

47

48

W83791D_HW_MONITOR_&_IPMI

49CPU_END_1

SYSTEM_FAN

50

F_PANEL_&_SYSTEM_SWITCH

SIO417_LPC_&_GPIO

51

SIO417_COM_LPC_FDD

52

BIOS_WOL_WOM

53

USB_KB_MS

54

SSI_POWER_CONNECTORS

55

VCC25_&_VCC1_25

56

PCB_HOLE_&_RESUME_RESET

57

CPU_VRM_LOGIC

58

59

POWER_ROUTING_MAP

GSMI

60

RESET_LOGIC

61

I2C ADDRESS & PCIIRQ MAP

62

63

REV_HISTORY

64

I2C_ROUTING_MAP

8 Layer 5mil / 50 Ohm

Inner 1

Inner 2

CORE = 30 mil

Inner 3

Inner 4 PWR

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

D

星期二, 五月

BLOCK DIAGRAM, INDEX

8EGXDREL-01

06, 2003

E

PWR

GND

GND

of

1

1.0

64

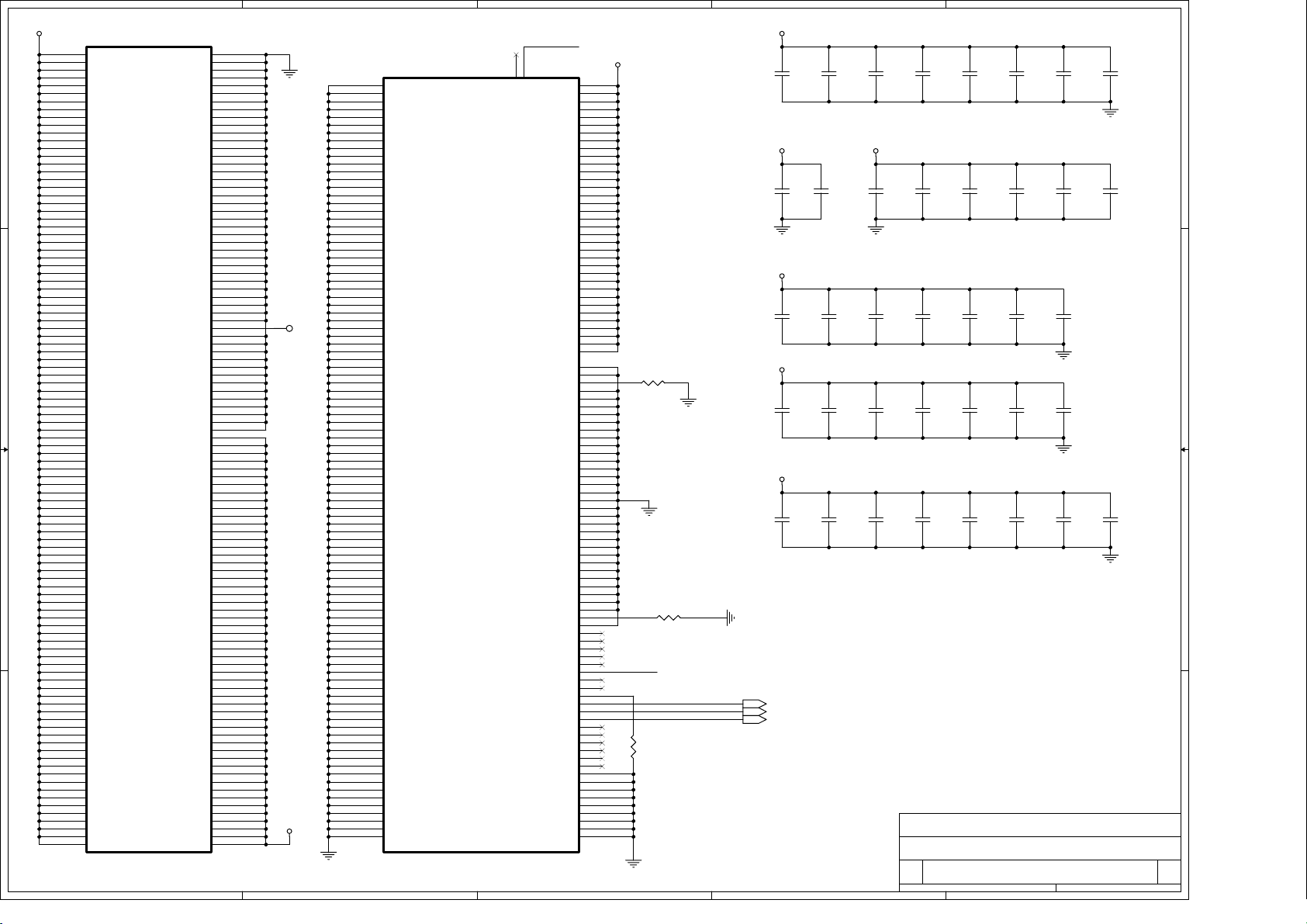

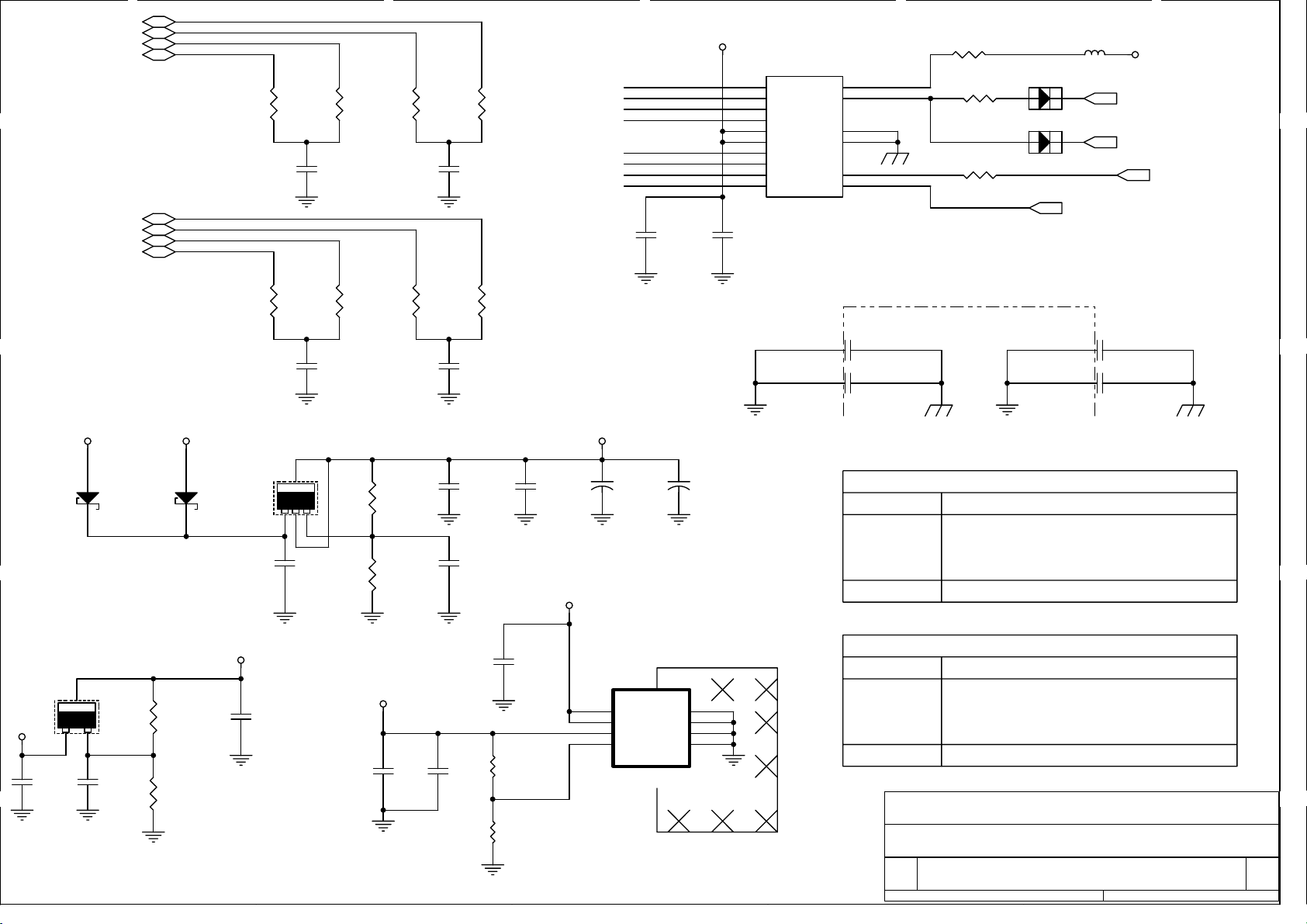

Page 2

A

B

C

D

E

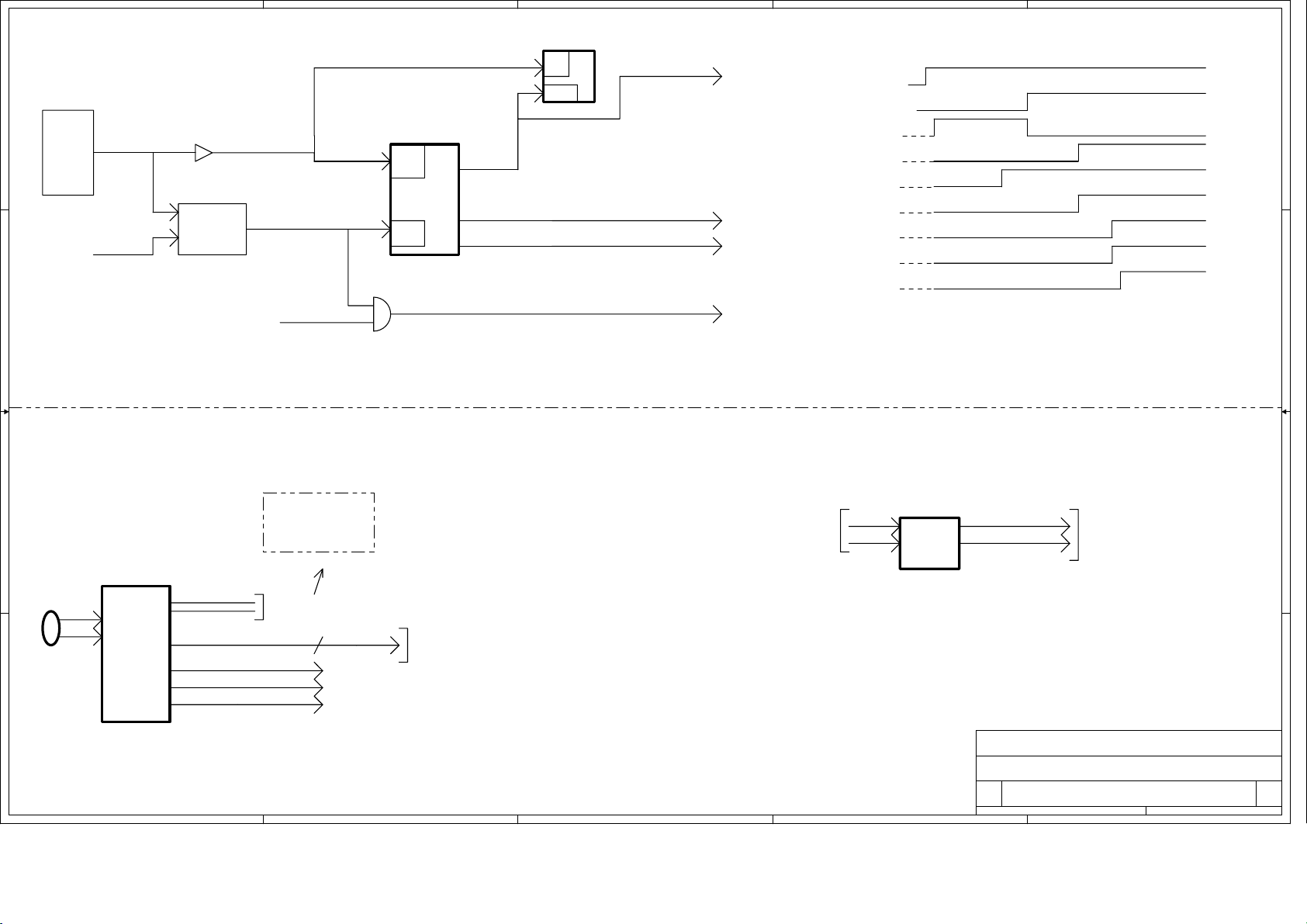

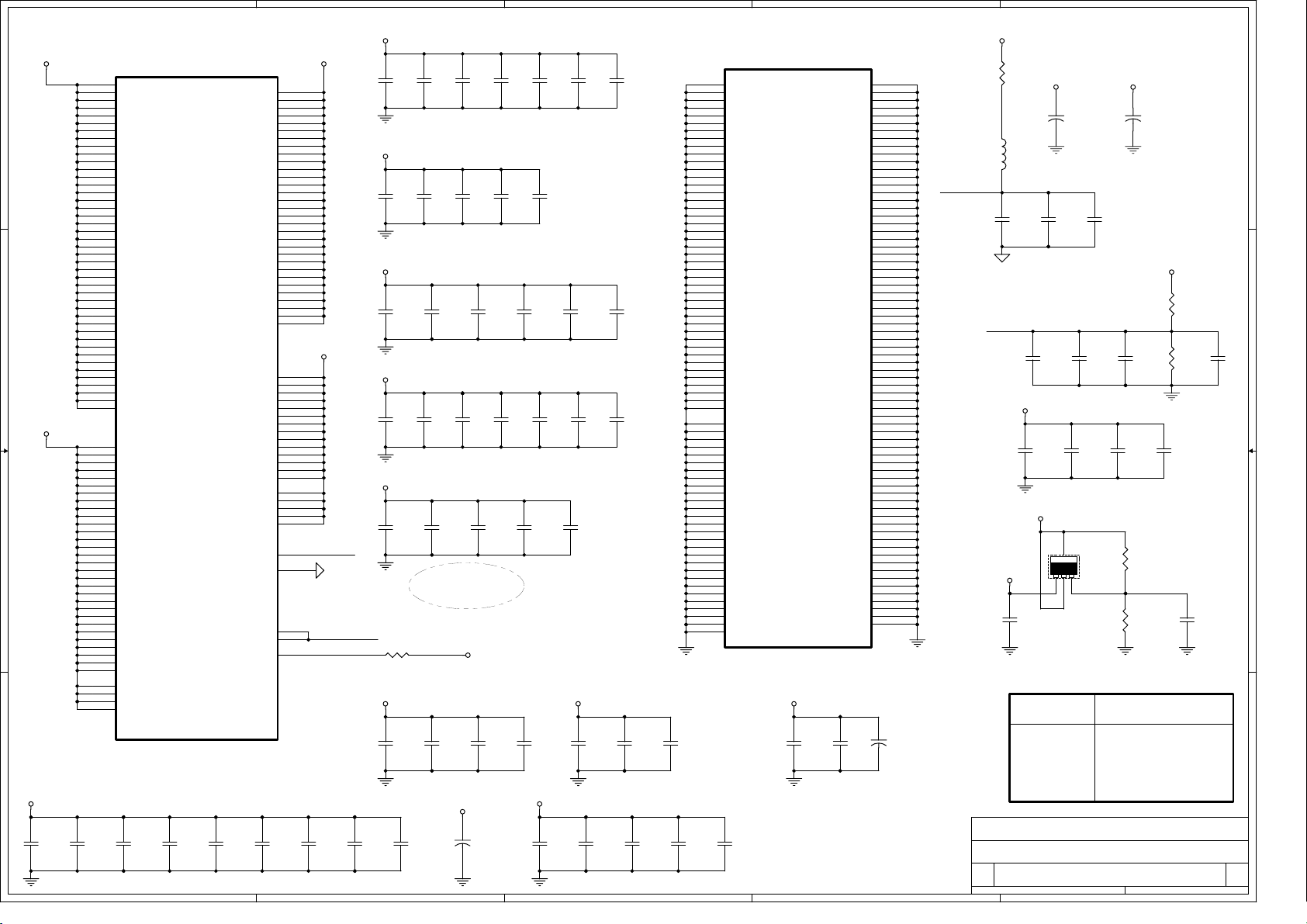

RESET SCHEME

PS_PWRGD#

4 4

3 3

ATX

POWER

SUPPLY

CONN.

PS_PWRGD

RESET SWITCH

INVERTER

RESET GEN

140mS PERIOD

RESET Vth =

4.5V

PS_PWRGD#

POWERGOOD

CPU_VRM_PWRGD

AND

PLLRST

SRESET#

PCIRST#

CMIC

RSB6

PLLRST

PCIRST#

PCIRST#

PROC_RESET#

RESETDLY#

CPU_PWRGD

RESET FOR RSB

PCI BUS

CPU RESET

Config RESET - 4

BCLK delay w.r.t.

PROC_RESET#

POWER

t0

PSU PWR GOOD

PLL RST

POWERGOOD

VRM POWERGOOD

PROCESSOR POWERGOOD

PROCESSOR RESET

PCI RESET

CONFIG RESET

t0+100mS

t0+100mS

t0+120mS

t0+50mS

t0+120mS

t0+120mS+1mS

t0+120mS+1mS

t0+120mS+1mS+4 clocks

CLOCKING SCHEME: 1 Main Synthesizer (CK408)

2 2

- CPU 0

- CPU 1

- CMIC_SL

From CLK

SYNTH.

BCLK

BCLK#

CMIC_SL

4 Pairs of 100MHz

Differential CLOCKs

for 4 DIMMs

CLK SYNTH.

BCLK

BCLK#

33MHz

14.318 MHz

X-TAL

1 1

48MHz

48MHz

14MHz

3 Pairs of 133MHz

Differential CLOCKs

n

48MHz USB CLK to RSB

48MHz CLK to SIO

14 MHz CLK to RSB

33MHz CLOCK TO RSB and

DEVICES behind it.

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

A

B

C

D

Date: Sheet

RESET and CLOCKING SCHEME

星期二, 五月

8EGXDREL-01

06, 2003

1.0

64

of

2

E

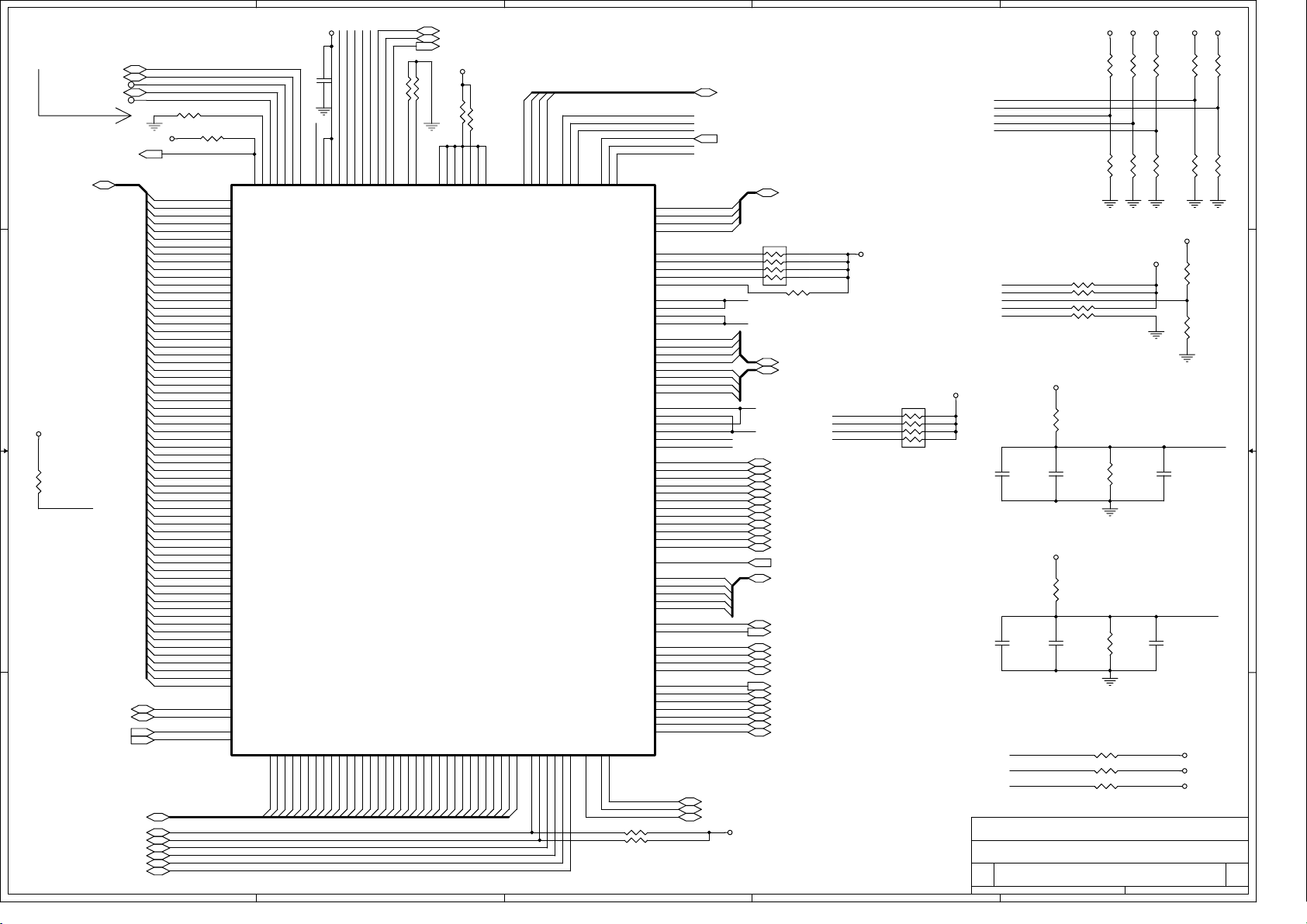

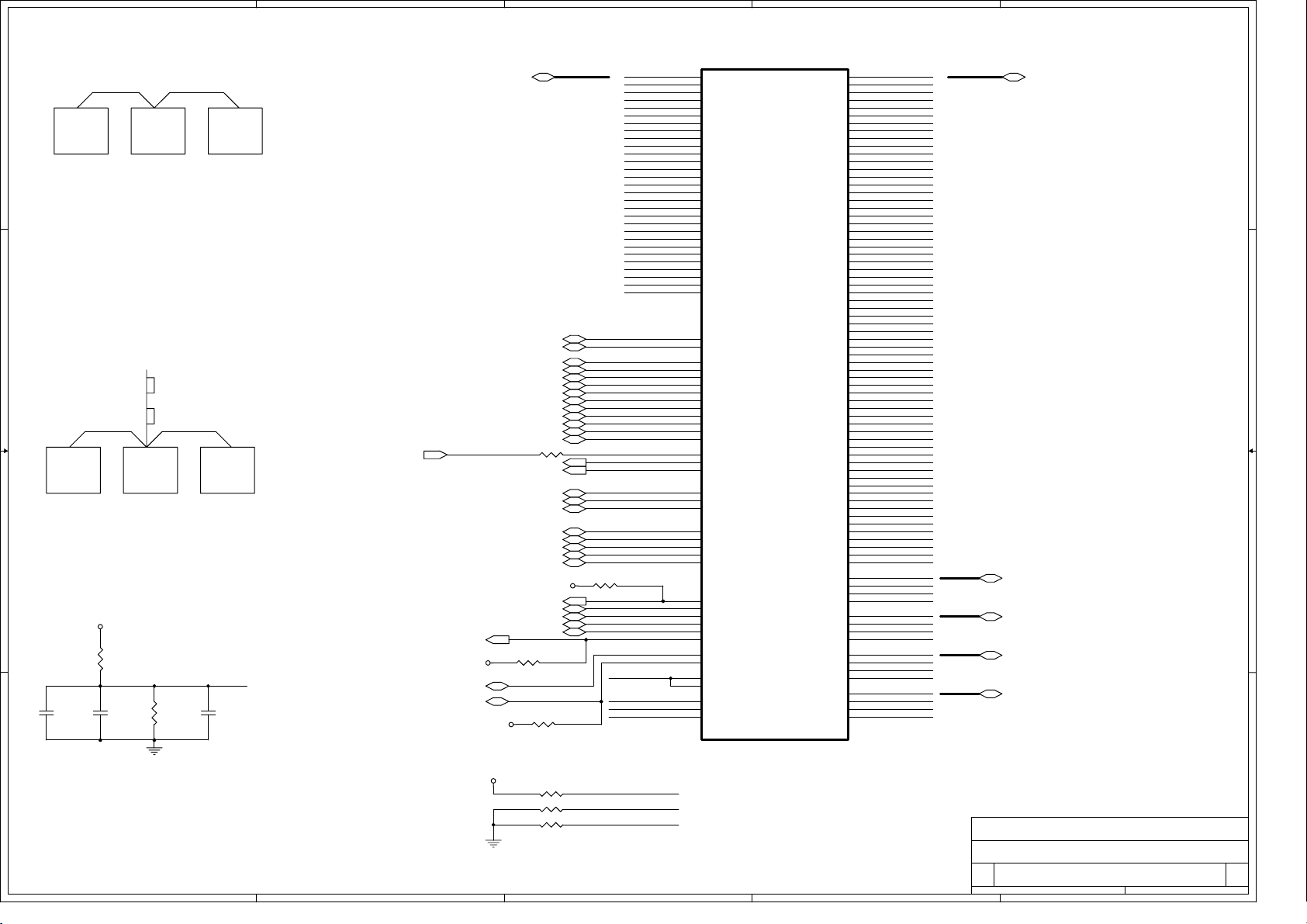

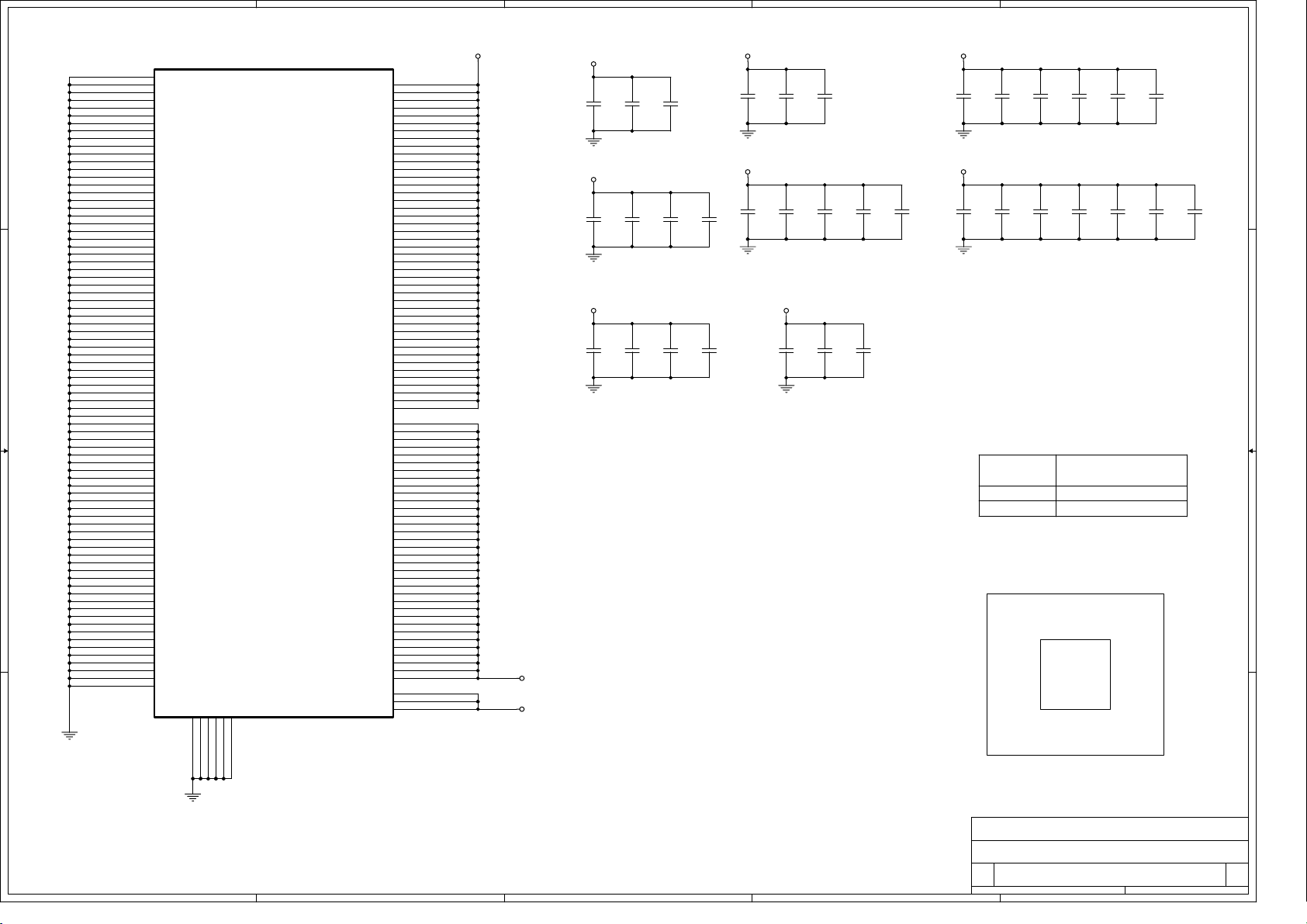

Page 3

A

VCC3

MID_CPU Pull-down

P1_VCCA10

P1_VCCIOPLL10

TP174

P1_VSSA10

TP175

4 4

HCLK120

-PD[0..63]

-AP05

-AP15

-PA[3..35]5,11

-BREQ15

-BREQ05,11

-BREQ25

-BREQ35

-BNR5,10,11

-BPRI5,11

VCC3

A

300/Intel

-CPU1_SKTOCC37,48,58,60

-PD[0..63]5,11

3 3

VCC3

DON'T STUFF

12

R822

1K/6/X

P1_SM_WP

2 2

HCLK1_N20

1 1

FSB_VCC_SENSE1

FSB_GND_SENSE1

1 2

R807 49.9/6/1

R808 1K/6

1 2

-PD0

-PD1

-PD2

-PD3

-PD4

-PD5

-PD6

-PD7

-PD8

-PD9

-PD10

-PD11

-PD12

-PD13

-PD14

-PD15

-PD16

-PD17

-PD18

-PD19

-PD20

-PD21

-PD22

-PD23

-PD24

-PD25

-PD26

-PD27

-PD28

-PD29

-PD30

-PD31

-PD32

-PD33

-PD34

-PD35

-PD36

-PD37

-PD38

-PD39

-PD40

-PD41

-PD42

-PD43

-PD44

-PD45

-PD46

-PD47

-PD48

-PD49

-PD50

-PD51

-PD52

-PD53

-PD54

-PD55

-PD56

-PD57

-PD58

-PD59

-PD60

-PD61

-PD62

-PD63

-AP0

-AP1

HCLK1

HCLK1_N

-PA[3..35]

P1_ODTEN

U69A

Y26

D0#

AA27

D1#

Y24

D2#

AA25

D3#

AD27

D4#

Y23

D5#

AA24

D6#

AB26

D7#

AB25

D8#

AB23

D9#

AA22

D10#

AA21

D11#

AB20

D12#

AB22

D13#

AB19

D14#

AA19

D15#

AE26

D16#

AC26

D17#

AD25

D18#

AE25

D19#

AC24

D20#

AD24

D21#

AE23

D22#

AC23

D23#

AA18

D24#

AC20

D25#

AC21

D26#

AE22

D27#

AE20

D28#

AD21

D29#

AD19

D30#

AB17

D31#

AB16

D32#

AA16

D33#

AC17

D34#

AE13

D35#

AD18

D36#

AB15

D37#

AD13

D38#

AD14

D39#

AD11

D40#

AC12

D41#

AE10

D42#

AC11

D43#

AE9

D44#

AD10

D45#

AD8

D46#

AC9

D47#

AA13

D48#

AA14

D49#

AC14

D50#

AB12

D51#

AB13

D52#

AA11

D53#

AA10

D54#

AB10

D55#

AC8

D56#

AD7

D57#

AE7

D58#

AC6

D59#

AC5

D60#

AA8

D61#

Y9

D62#

AB6

D63#

E10

AP0#

D9

AP1#

Y4

BCLK0

W5

BCLK1

SOCKET604

A3B5D26

ODTEN

SKTOCC#

A22

-PA3

AA5

B27

AD4

VSSA

VCCIOPLL

VSSSENSE

VCCSENSE

A3#

A4#

A5#

A6#

A20

B18

C18

-PA4

-PA5

-PA6

C1126

0.1U/6

AB4

VCCA

A7#

A19

-PA7

C17

-PA8

A8#

P1_SM_WP

AD29

D17

-PA9

12

AE29

SMB_WP

A9#

A13

-PA10

AE28

SM_VCC1

A10#

B16

-PA11

B

CPU_SDA 5,60

CPU_SCL 5,60

-CPU_SMBALERT 5,37

VCC_P

12

12

12

P1_SM_TS_ADDR1

Y29

SM_VCC

P1_SM_ADDR2

P1_SM_TS_ADDR0

AA28

AB28

SM_TS_A1

SM_TS_A0

P1_SM_ADDR0

P1_SM_ADDR1

AB29

AA29

SM_EP_A2

SM_EP_A1

AC29

AC28

SM_DAT

SM_EP_A0

SM_CLK

R803 49.9/6/1

AD28

SM_ALERT

P1_COMP1

E16

COMP1

P1_COMP0

AD16

COMP0

R804 49.9/6/1

W6W7W8Y6AA7

TESTHI0

TESTHI1

R805 49.9/6/1

TESTHI2

TESTHI3

12

AD5

TESTHI4

TESTHI5

R806 49.9/6/1

AE5

TESTHI6

PRESTONIA

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13A9B8

E13

D12

C11B7A6A7C9C8D20

-PA18

-PA13

-PA17

-PA15

-PA14

-PA12

-PA16

-PA19

B

-PA20

-PA21

-PA22

-PA23

-PA24

-PA25

-PA26

-PA30

-PA34

-PA29

-PA32

-PA31

-PA27

-PA33

-PA28

A34#

-PA35

-DP3

A35#

-DP2

AE17

DP3#

-DP1

AC15

AE19

DP2#

DP1#

BR0#

BR1#

F12

-BREQ1

-BREQ0

-DP0

AC18

DP0#

BR2#

BR3#

E11

D10

-BREQ2

-BREQ3

E25

F20

-BNR

C24

TDO

BNR#

D23

-BPRI

E24

TDI

TCK

BPRI#

BINIT#

F11

-BINIT

C

P1_TDO

P1_TDI

P1_TCK

-P_TRDY

-ITP_TRST

P1_TMS

E19

F24

A25

TMS

TRST#

DBI3#

TRDY#

DBI2#

DBI1#

DBI0#

VID0

VID1

VID2

VID3

VID4

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

SLP#

STPCLK#

SMI#

THERMTRIP#

PWRGD

PR0CH0T#

INIT#

LINIT1

LINIT0

FERR#

IGNNE#

A20M#

RESET#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

LOCK#

MCERR#

RSP#

RS2#

RS1#

RS0#

IERR#

DEFER#

HITM#

HIT#

ADS#

ADSTB0#

ADSTB1#

DBSY#

DRDY#

F18

E18

-DBSY

-DRDY

R795 49.9/6/1

12

R968 49.9/6/1

12

PLACE AT PROC MID 2

C

AB9

AE12

AD22

AC27

F3

E3

D3

C3

B3

F9

F23

W9

W23

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

F6

F8

E7

F5

E8

E4

AE6

D4

C27

F26

AB7

B25

D6

G23

B24

E27

C26

F27

Y8

B19

B21

C21

C20

B22

A17

D7

C6

F21

D22

E21

E5

C23

A23

E22

D19

F17

F14

-DINV3

-DINV2

-DINV1

-DINV0

P_VID0

P_VID1

P_VID2

P_VID3

P_VID4

P1_GTLREF1

P1_GTLREF0

-DSTBP3

-DSTBP2

-DSTBP1

-DSTBP0

-DSTBN3

-DSTBN2

-DSTBN1

-DSTBN0

-BPM2

-BPM3

-BPM2

-BPM3

-BPM4

-BPM5

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

-RS2

-RS1

-RS0

-P1_IERR

-DEFER

-HITM

-HIT

-ADS

-ADSTB0

-ADSTB1

-DRDY 5,11

-DBSY 5,11

-BINIT 5,10,11

-DP[0..3] 5,11

-P_TRDY 5,11

1 2

3 4

5 6

7 8

VCC_P

CPU END THERMAL SMBUS ADDRESS

= 98H

CPU END DATA SMBUS ADDRESS

= A0/A1

-DINV[0..3] 5,11

RN149

8P4R/1K

12

R944

1K/6

Differential Pair

-DSTBP[0..3] 5,11

-DSTBN[0..3] 5,11

PLACE NEAR CPU1

-BPM2

-BPM3

-BPM4

-BPM5

-SLP 5,10

-CPU_STPCLK 5,10

-SMI_AP 10

-P1_THERMTRIP 60,61

CPU1_PWRGD 61

-P1_PROC_HOT 8

-INIT 5,10

LINT1 5,8,10

LINT0 5,8,10

-FERR 5,8

-IGNNE 5,8,10

-A20M 5,8,10

-PROC_RESET 5,10,12

-HREQ[0..4] 5,11

-LOCK 5,10,11

-MCERR 5,10

-RSP 5

-RS2 5,11

-RS1 5,11

-RS0 5,11

-P1_IERR 8

-DEFER 5,11

-HITM 5,10,11

-HIT 5,10,11

-ADS 5,11

-ADSTB0 5,11

-ADSTB1 5,11

VCC

D

D

RN143

1 2

3 4

5 6

7 8

8P4R/51

E

VCC3 VCC3 VCC3 VCC3 VCC3

12

12

R798 1K/6/X

P1_SM_TS_ADDR1

P1_SM_TS_ADDR0

P1_SM_ADDR2

P1_SM_ADDR1

P1_SM_ADDR0

ITP termination

P1_TDO

P1_TDI

P1_TCK

P1_TMS

-ITP_TRST

VCC_P

12

SC1127

220P/6

12

SC1130

220P/6

-P1_PROC_HOT

-P1_THERMTRIP

-FERR

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

星期二, 五月

R815 150/6

1 2

R816 150/6

1 2

R817 40.2/6/1

1 2

R818 150/6

1 2

VCC_P

12

R820

49.9/6/1

12

SC1128

220P/6

VCC_P

12

R825

49.9/6/1

12

SC1131

220P/6

8EGXDREL-01

06, 2003

R799 1K/6/X12R800 1K/6/X

12

12

12

R811 1K/6

R810 1K/6

R809 1K/6

VCC_P

12

PLACE EACH 220pf OF GTLREF

NEAR PROC PIN

12

R824 56/6

R753 49.9/6/1

R957 49.9/6/1

R821

100/6/1

R826

100/6/1

12

12

12

12

C1129

1U/6

P1_GTLREF1

12

C1132

1U/6

PROCESSOR_1

3

E

R801 1K/6/X12R802 1K/6/X

12

R813 1K/6

R812 1K/6

VCC_P

12

R814

40.2/6/1/X

12

R819

27.4/6/1

P1_GTLREF0

VCC_P

VCC_P

VCC_P

of

12

12

1.0

64

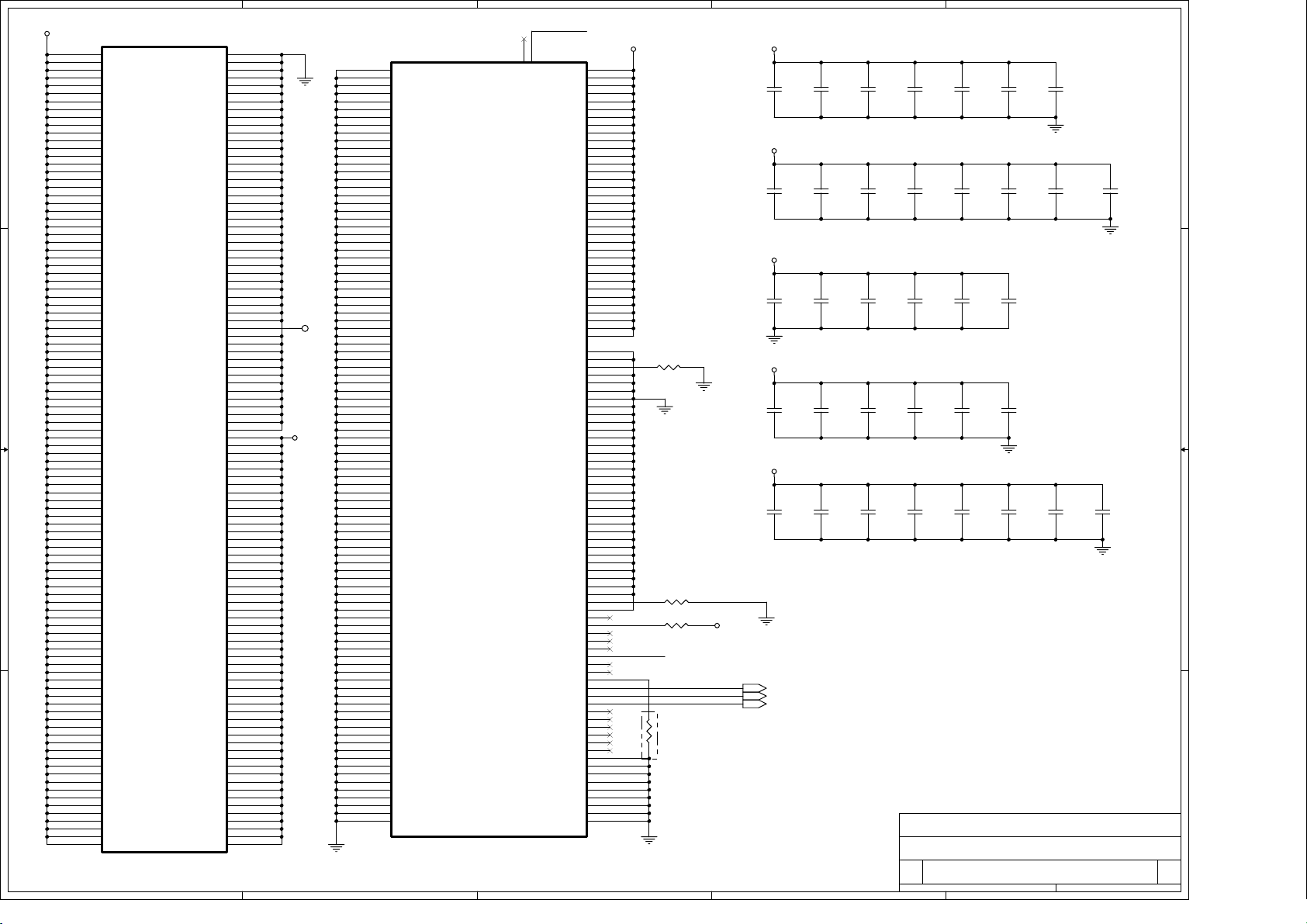

Page 4

A

VCC_P

U69B

A2

VCC

A8

VCC

A14

VCC

A18

VCC

A24

VCC

A28

VCC

B6

VCC

B12

VCC

B20

M23

M25

M27

M29

N23

N25

N27

N29

R23

R25

R27

W27

W25

B26

B29

C10

C16

C22

C28

D14

D18

D24

D29

E12

E20

E26

E28

F10

F16

F22

F29

G24

G26

G28

H23

H25

H27

H29

K23

K25

K27

K29

L24

L26

L28

P24

P26

P28

C2

C4

D8

E2

E6

F4

G2

G4

G6

G8

H3

H5

H7

H9

J24

J26

J28

K3

K5

K7

K9

L2

L4

L6

L8

M3

M5

M7

M9

N3

N5

N7

N9

P2

P4

P6

P8

R3

R5

R7

R9

J2

J4

J6

J8

SOCKET604

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

BOOT_SELECT/VSS

PRESTONIA

A

4 4

3 3

2 2

1 1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A5

A11

A21

A27

A29

B2

B9

B15

B17

B23

B28

C7

C13

C19

C25

C29

D2

D5

D11

D21

D27

D28

E9

E15

E17

E23

E29

F2

F7

F13

F19

F25

F28

G3

G5

G7

G9

G25

G27

G29

H2

H4

H6

H8

H24

H26

H28

J3

J5

W29

Y2

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

TP217

VCC_P

B

VCCVID_U69

A1

U69C

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

J29

VSS

K2

VSS

K4

VSS

K6

VSS

K8

VSS

K24

VSS

K26

VSS

K28

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

L23

VSS

L25

VSS

L27

VSS

L29

VSS

M2

VSS

M4

VSS

M6

VSS

M8

VSS

M24

VSS

M26

VSS

M28

VSS

N2

VSS

N4

VSS

N6

VSS

N8

VSS

N24

VSS

N26

VSS

N28

VSS

P3

VSS

P5

VSS

P7

VSS

P9

VSS

P23

VSS

P25

VSS

P27

VSS

P29

VSS

R2

VSS

R4

VSS

R6

VSS

R8

VSS

R24

VSS

R26

VSS

R28

T3

T5

T7

T9

T23

T25

T27

T29

U2

U4

U6

U8

U24

U26

U28

V3

V5

V7

V9

V23

V25

V27

V29

W2

W4

W24

W26

W28

Y5

Y7

Y13

Y19

Y25

AA2

AA9

AA15

AA17

AA23

AB5

AB11

AB21

AB27

AC2

AC7

AC13

AC19

AC25 AD3

B

PRESTONIA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

SOCKET604

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD1

GAL_VDD4

GAL_VDD5

GAL_VDD6

VCCVID/RSVD2

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

TESTLOW/GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

SLEW_CTRL/GAL_VSS33

GAL_VSS34

RSVD_604

FORCEPR#/RSVD3

RSVD4

RSVD5

RSVD8

VCCVIDLB/RSVD13

RSVD17

RSVD63

RSVD67

RSVD68

RSVD69

RSVD73

RSVD77

RSVD80

RSVD83

RSVD86

RSVD87

RSVD88

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

AE30

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

Y28

AA3

AB3

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

C

VCC_P

R1213 49.9/6/1%

1 2

VCCVID_U69

1 2

R1214 0/6

1 2

R1216 49.9/6/1%

1 2

10 mil min

CPU1_THERM_DA1

CPU1_THERM_DC1

CPU1_BSEL0

DON'T STUFF

R796

0/6/X

D

VCC_P

C1070

0.1U/6/X7R

C1093

10U/12

C1090

82U/1210

C1110

10U/12

C1117

1U/6

12

12

12

12

12

12

VCC_P

12

CPU1 CORE DECOUPLING

VCC_P

12

VCC_P

12

VCC_P

12

C1072

0.1U/6/X7R

C1100

10U/12

C1091

82U/1210

C1111

10U/12

C1118

1U/6

12

12

12

12

12

C1073

0.1U/6/X7R

C1101

10U/12

C1260

82U/1210

C1113

10U/12

C1119

1U/6

12

12

12

12

12

C1074

0.1U/6/X7R

C1102

10U/12

C1261

82U/1210

C1114

10U/12

C1120

1U/6

12

C1075

0.1U/6/X7R

12

C1105

10U/12

12

SC1262

10U/12

12

C1115

10U/12

12

C1121

1U/6

12

12

12

12

12

C1076

0.1U/6/X7R

SC1106

10U/12

SC1263

10U/12

C1116

10U/12

C1122

1U/6

E

12

C1077

0.1U/6/X7R

12

C1107

10U/12

12

C1123

1U/6

PLACE AROUND P1 SOCKET

P04, For Nocona CPU -->TESTLOW pull down to GND

TESTLOW pull down to GND

SLEW_CTRL pull down to GND

VCC_P

FORCEPR# Pull up in middle CPU

FORCEPR# floating in end CPU

C5 and A4 pins of the CPU connect together

CPU1_THERM_DA1 48

CPU1_THERM_DC1 48

CPU1_BSEL0 20

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

D

星期二, 五月

PROCESSOR_1_POWER

8EGXDREL-01

06, 2003

E

12

C1109

10U/12

12

C1124

1U/6

1.0

64

of

4

Page 5

5

VCC3

C1063

0.1U/6

P2_VCCA10

P2_VCCIOPLL10

TP172

P2_VSSA10

TP173

VCC_P

END_CPU Pull-up

D D

-PD[0..63]3,11

C C

VCC3

12

R790 1K/6/X

B B

A A

-CPU2_SKTOCC37,60

P2_SM_WP

VCC3

-PD[0..63]

-AP03

-AP13

HCLK220

HCLK2_N20

5

FSB_VCC_SENSE2

FSB_GND_SENSE2

R775 49.9/6/1

1 2

R778 1K/6

1 2

-PD0

-PD1

-PD2

-PD3

-PD4

-PD5

-PD6

-PD7

-PD8

-PD9

-PD10

-PD11

-PD12

-PD13

-PD14

-PD15

-PD16

-PD17

-PD18

-PD19

-PD20

-PD21

-PD22

-PD23

-PD24

-PD25

-PD26

-PD27

-PD28

-PD29

-PD30

-PD31

-PD32

-PD33

-PD34

-PD35

-PD36

-PD37

-PD38

-PD39

-PD40

-PD41

-PD42

-PD43

-PD44

-PD45

-PD46

-PD47

-PD48

-PD49

-PD50

-PD51

-PD52

-PD53

-PD54

-PD55

-PD56

-PD57

-PD58

-PD59

-PD60

-PD61

-PD62

-PD63

HCLK2

HCLK2_N

-PA[3..35]3,11

-BREQ03,11

-BREQ13

-BREQ23

-BREQ33

-BNR3,10,11

-BPRI3,11

P2_ODTEN

U68A

Y26

D0#

AA27

D1#

Y24

D2#

AA25

D3#

AD27

D4#

Y23

D5#

AA24

D6#

AB26

D7#

AB25

D8#

AB23

D9#

AA22

D10#

AA21

D11#

AB20

D12#

AB22

D13#

AB19

D14#

AA19

D15#

AE26

D16#

AC26

D17#

AD25

D18#

AE25

D19#

AC24

D20#

AD24

D21#

AE23

D22#

AC23

D23#

AA18

D24#

AC20

D25#

AC21

D26#

AE22

D27#

AE20

D28#

AD21

D29#

AD19

D30#

AB17

D31#

AB16

D32#

AA16

D33#

AC17

D34#

AE13

D35#

AD18

D36#

AB15

D37#

AD13

D38#

AD14

D39#

AD11

D40#

AC12

D41#

AE10

D42#

AC11

D43#

AE9

D44#

AD10

D45#

AD8

D46#

AC9

D47#

AA13

D48#

AA14

D49#

AC14

D50#

AB12

D51#

AB13

D52#

AA11

D53#

AA10

D54#

AB10

D55#

AC8

D56#

AD7

D57#

AE7

D58#

AC6

D59#

AC5

D60#

AA8

D61#

Y9

D62#

AB6

D63#

E10

AP0#

D9

AP1#

Y4

BCLK0

W5

BCLK1

SOCKET604

-PA[3..35]

A3B5D26

ODTEN

SKTOCC#

A22

-PA3

12

P2_SM_WP

AA5

B27

AD4

AB4

AD29

VSSA

VCCA

VCCIOPLL

VSSSENSE

VCCSENSE

A3#

A4#

A5#

A6#

A7#

A8#

A20

B18

C18

A19

C17

D17

-PA8

-PA5

-PA9

-PA7

-PA6

-PA4

4

CPU_SDA 3,60

CPU_SCL 3,60

-CPU_SMBALERT 3,37

R774 49.9/6/1

R776 49.9/6/1

W6W7W8Y6AA7

TESTHI0

TESTHI1

VCC_P

12

12

AD5

TESTHI2

TESTHI3

TESTHI4

12

12

P2_SM_ADDR0

P2_SM_ADDR2

P2_SM_ADDR1

P2_SM_TS_ADDR0

P2_SM_TS_ADDR1

AE29

AE28

Y29

AA28

SM_VCC

SMB_WP

SM_VCC1

SM_TS_A1

SM_TS_A0

R773 49.9/6/1

P2_COMP0

P2_COMP1

AB28

AB29

AA29

AC29

AC28

AD28

E16

AD16

COMP1

COMP0

SM_CLK

SM_DAT

SM_EP_A2

SM_EP_A1

SM_EP_A0

SM_ALERT

PRESTONIA

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13A9B8

E13

D12

C11B7A6A7C9C8D20

-PA10

-PA14

-PA18

-PA13

-PA16

-PA15

-PA11

-PA12

-PA19

-PA17

4

-PA26

-PA20

-PA21

-PA27

-PA23

-PA22

-PA29

-PA24

-PA25

-PA30

-PA28

3

DBI3#

DBI2#

DBI1#

DBI0#

VID0

VID1

VID2

VID3

VID4

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

SLP#

SMI#

INIT#

LINIT1

LINIT0

FERR#

IGNNE#

A20M#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

LOCK#

RSP#

RS2#

RS1#

RS0#

IERR#

HITM#

HIT#

ADS#

VCC3

-DINV3

AB9

-DINV2

AE12

-DINV1

AD22

-DINV0

AC27

M_VID0

F3

M_VID1

E3

M_VID2

D3

M_VID3

C3

M_VID4

B3

F9

P2_GTLREF1

F23

W9

P2_GTLREF0

W23

-DSTBP3

Y11

-DSTBP2

Y14

-DSTBP1

Y17

-DSTBP0

Y20

-DSTBN3

Y12

-DSTBN2

Y15

-DSTBN1

Y18

-DSTBN0

Y21

-2BPM2

F6

-2BPM3

F8

-2BPM2

E7

-2BPM3

F5

-2BPM4

E8

-2BPM5

E4

AE6

D4

C27

F26

AB7

B25

D6

G23

B24

E27

C26

F27

Y8

-HREQ0

B19

-HREQ1

B21

-HREQ2

C21

-HREQ3

C20

-HREQ4

B22

A17

D7

C6

-RS2

F21

-RS1

D22

-RS0

E21

-P2_IERR

E5

-DEFER

C23

-HITM

A23

-HIT

E22

-ADS

D19

-ADSTB0

F17

-ADSTB1

F14

R829 49.9/6/1

12

R967 49.9/6/1

12

R830 49.9/6/1

12

R831 49.9/6/1

12

-DRDY 3,11

-DBSY 3,11

-BINIT 3,10,11

-DP[0..3] 3,11

-CPU_SMBALERT

R777 49.9/6/1

-DP3

-DP1

-DP0

-DP2

E25

C24

AE17

AC15

AE19

AE5

TESTHI5

TESTHI6

A30#

A31#

A32#

-PA33

-PA32

-PA31

AC18

TDO

DP3#

DP2#

DP1#

DP0#

A33#

A34#

A35#

BR0#

BR1#

BR2#

BR3#

BNR#

F12

E11

D10

F20

D23

-PA35

-PA34

-BPRI

-BREQ1

-BREQ0

-BREQ3

-BREQ2

-BNR

TDI

BPRI#

E24

TCK

R958 10K/6

1 2

P2_TDO

P2_TDI

P2_TCK

-P_TRDY

-ITP_TRST2

P2_TMS

E19

F24

A25

TMS

TRST#

TRDY#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

STPCLK#

THERMTRIP#

PWRGD

PR0CH0T#

RESET#

MCERR#

DEFER#

ADSTB0#

ADSTB1#

BINIT#

DBSY#

DRDY#

F11

F18

E18

-BINIT

-DBSY

-DRDY

PLACE AT PROC END 2

3

CPU END THERMAL SMBUS ADDRESS

= 30H

-P_TRDY 3,11

CPU END DATA SMBUS ADDRESS =

A2/A3

Z = R/W bit

Differential Pair

-SLP 3,10

-CPU_STPCLK 3,10

-SMI_BSP 10

-P2_THERMTRIP 60,61

CPU2_PWRGD 61

-P2_PROC_HOT 8

-INIT 3,10

LINT1 3,8,10

LINT0 3,8,10

-FERR 3,8

-IGNNE 3,8,10

-A20M 3,8,10

-PROC_RESET 3,10,12

-HREQ[0..4] 3,11

-LOCK 3,10,11

-MCERR 3,10

-RSP 3

-RS2 3,11

-RS1 3,11

-RS0 3,11

-P2_IERR 8

-DEFER 3,11

-HITM 3,10,11

-HIT 3,10,11

-ADS 3,11

-ADSTB0 3,11

-ADSTB1 3,11

VCC_P

2

-DINV[0..3] 3,11

M_VID[0..4] 48,58

-DSTBP[0..3] 3,11

-DSTBN[0..3] 3,11

PLACE NEAR CPU2

-2BPM2

-2BPM3

-2BPM4

-2BPM5

2

RN142

1 2

3 4

5 6

7 8

8P4R/51

1

VCC3 VCC3 VCC3 VCC3 VCC3

12

12

VCC_P

12

12

12

P2_GTLREF0

12

P2_GTLREF1

12

R771 1K/6/X

R782 1K/6

C1066

1U/6

C1069

1U/6

12

R772 1K/6

12

R783 1K/6/X

VCC_P

12

R770 1K/6

R769 1K/6/X

12

R781 1K/6/X

R780 1K/6

R853 56/6

R823 49.9/6/1

R754 49.9/6/1

12

R792

100/6/1

PLACE EACH 220pf OF

GTLREF NEAR PROC

PIN

12

R794

100/6/1

12

12

12

R784

40.2/6/1/X

12

R789

27.4/6/1

VCC_P

VCC_P

VCC_P

P2_SM_TS_ADDR1

P2_SM_TS_ADDR0

P2_SM_ADDR2

P2_SM_ADDR1

P2_SM_ADDR0

ITP termination

P2_TDO

P2_TDI

P2_TCK

P2_TMS

-ITP_TRST2

VCC_P

-P2_PROC_HOT

-FERR

-P2_THERMTRIP

12

SC1064

220P/6

12

SC1067

220P/6

R785 150/6

1 2

R786 150/6

1 2

R787 40.2/6/1

1 2

R788 150/6

1 2

VCC_P

12

R791

49.9/6/1

12

SC1065

220P/6

VCC_P

12

R793

49.9/6/1

12

SC1068

220P/6

12

R768 1K/6/X

12

R779 1K/6

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

星期二, 五月

PROCESSOR_2

8EGXDREL-01

06, 2003

64

of

5

1

1.0

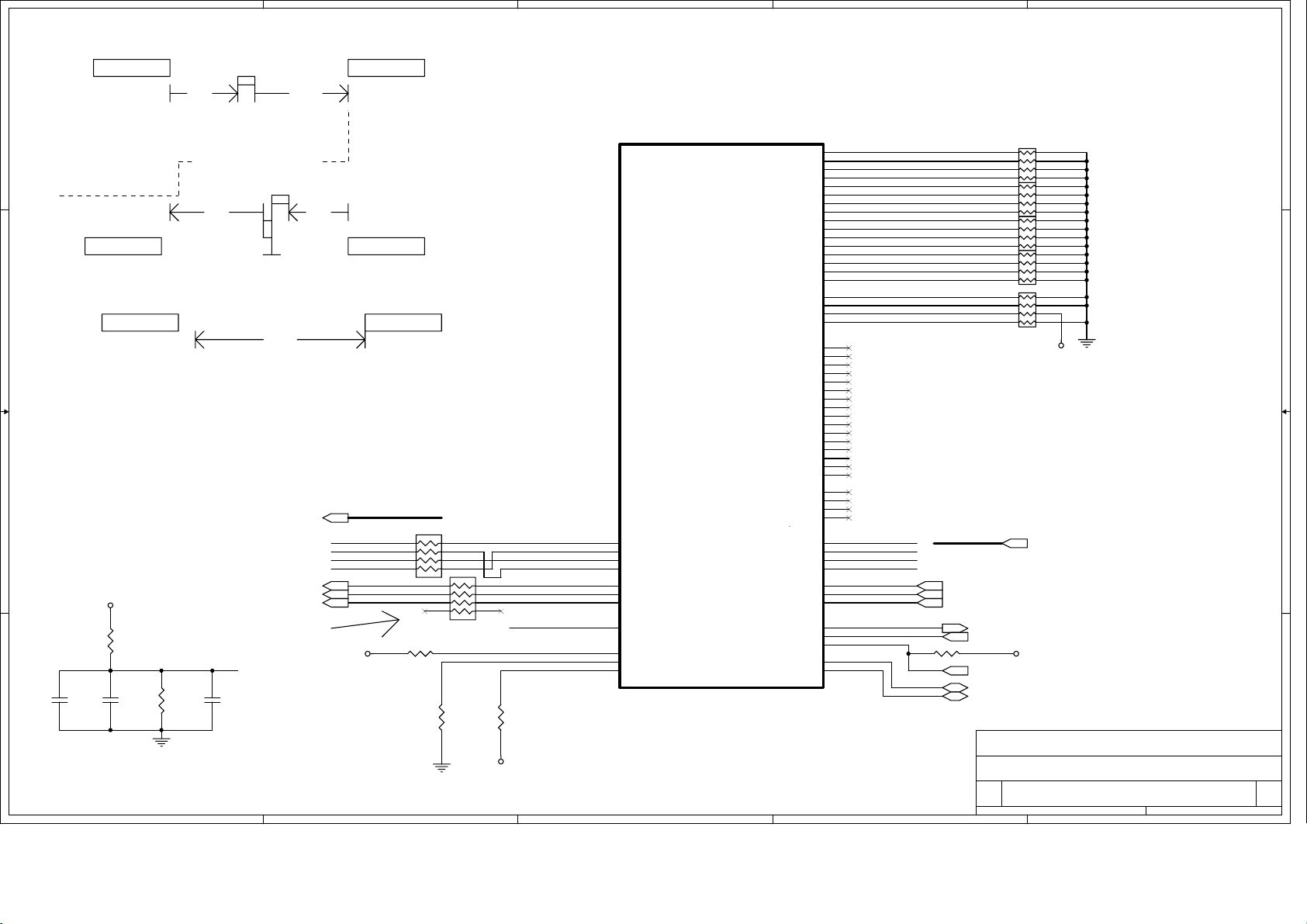

Page 6

5

VCC_P

D D

C C

B B

A A

A14

A18

A24

A28

B12

B20

B26

B29

C10

C16

C22

C28

D14

D18

D24

D29

E12

E20

E26

E28

G24

G26

G28

H23

H25

H27

H29

K23

K25

K27

K29

M23

M25

M27

M29

N23

N25

N27

N29

P24

P26

P28

R23

R25

R27

W27

W25

A2

A8

B6

C2

C4

D8

E2

E6

F4

F10

F16

F22

F29

G2

G4

G6

G8

H3

H5

H7

H9

J24

J26

J28

K3

K5

K7

K9

L2

L4

L6

L8

L24

L26

L28

M3

M5

M7

M9

N3

N5

N7

N9

P2

P4

P6

P8

R3

R5

R7

R9

U68B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J2

VCC

J4

VCC

J6

VCC

J8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SOCKET604

BOOT_SELECT/VSS

PRESTONIA

5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A5

A11

A21

A27

A29

B2

B9

B15

B17

B23

B28

C7

C13

C19

C25

C29

D2

D5

D11

D21

D27

D28

E9

E15

E17

E23

E29

F2

F7

F13

F19

F25

F28

G3

G5

G7

G9

G25

G27

G29

H2

H4

H6

H8

H24

H26

H28

J3

J5

W29

Y2

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

TP216

VCC_P

4

VCCVID_U68

U68C

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

J29

VSS

K2

VSS

K4

VSS

K6

VSS

K8

VSS

K24

VSS

K26

VSS

K28

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

L23

VSS

L25

VSS

L27

VSS

L29

VSS

M2

VSS

M4

VSS

M6

VSS

M8

VSS

M24

VSS

M26

VSS

M28

VSS

N2

VSS

N4

VSS

N6

VSS

N8

VSS

N24

VSS

N26

VSS

N28

VSS

P3

VSS

P5

VSS

P7

VSS

P9

VSS

P23

VSS

P25

VSS

P27

VSS

P29

VSS

R2

VSS

R4

VSS

R6

VSS

R8

VSS

R24

VSS

R26

VSS

R28

T3

T5

T7

T9

T23

T25

T27

T29

U2

U4

U6

U8

U24

U26

U28

V3

V5

V7

V9

V23

V25

V27

V29

W2

W4

W24

W26

W28

Y5

Y7

Y13

Y19

Y25

AA2

AA9

AA15

AA17

AA23

AB5

AB11

AB21

AB27

AC2

AC7

AC13

AC19

AC25 AD3

4

PRESTONIA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

SOCKET604

A1

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD1

GAL_VDD4

GAL_VDD5

GAL_VDD6

VCCVID/RSVD2

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

TESTLOW/GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

SLEW_CTRL/GAL_VSS33

GAL_VSS34

RSVD_604

FORCEPR#/RSVD3

RSVD4

RSVD5

RSVD8

VCCVIDLB/RSVD13

RSVD17

RSVD63

RSVD67

RSVD68

RSVD69

RSVD73

RSVD77

RSVD80

RSVD83

RSVD86

RSVD87

RSVD88

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

AE30

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

Y28

AA3

AB3

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

3

VCC_P

VCCVID_U68

3

R1209 49.9/6/1%

1 2

R1210 49.9/6/1%

1 2

10 mil min

CPU2_THERM_DA2

CPU2_THERM_DC2

CPU2_BSEL0

DON'T STUFF

R766

0/6/X

1 2

VCC_P

12

C1007

0.1U/6/X7R

2

12

C1008

0.1U/6/X7R

12

C1009

0.1U/6/X7R

12

C1010

0.1U/6/X7R

12

C1011

0.1U/6/X7R

12

C1012

0.1U/6/X7R

1

12

C1013

0.1U/6/X7R

12

C1014

0.1U/6/X7R

CPU2 CORE DECOUPLING

VCC_P

12

C1030

10U/12

12

C1036

10U/12

VCC_P

12

C1095

82U/1210

12

C1098

82U/1210

12

C1256

82U/1210

12

C1257

82U/1210

12

SC1258

10U/12

12

SC1259

10U/12

Top center

VCC_P

12

VCC_P

12

C1040

10U/12

C1047

10U/12

12

12

C1041

10U/12

C1048

10U/12

12

12

C1042

10U/12

C1049

10U/12

12

12

C1043

10U/12

C1050

10U/12

12

12

C1044

10U/12

C1051

10U/12

12

12

C1045

10U/12

C1052

10U/12

12

12

C1046

10U/12

C1053

10U/12

PLACE AROUND P2 SOCKET

VCC_P

12

C1054

1U/6

12

C1055

1U/6

12

C1056

1U/6

12

C1057

1U/6

12

C1058

1U/6

12

C1059

1U/6

12

C1060

1U/6

12

C1061

1U/6

P06, For Nocona CPU -->TESTLOW pull down to GND

TESTLOW pull down to GND

SLEW_CTRL pull down to GND

FORCEPR# Pull up in middle CPU

FORCEPR# floating in end CPU

C5 and A4 pins of the CPU connect together

CPU2_THERM_DA2 48

CPU2_THERM_DC2 48

CPU2_BSEL0 20

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

2

星期二, 五月

PROCESSOR_2_PWR

8EGXDREL-01

06, 2003

64

of

6

1

1.0

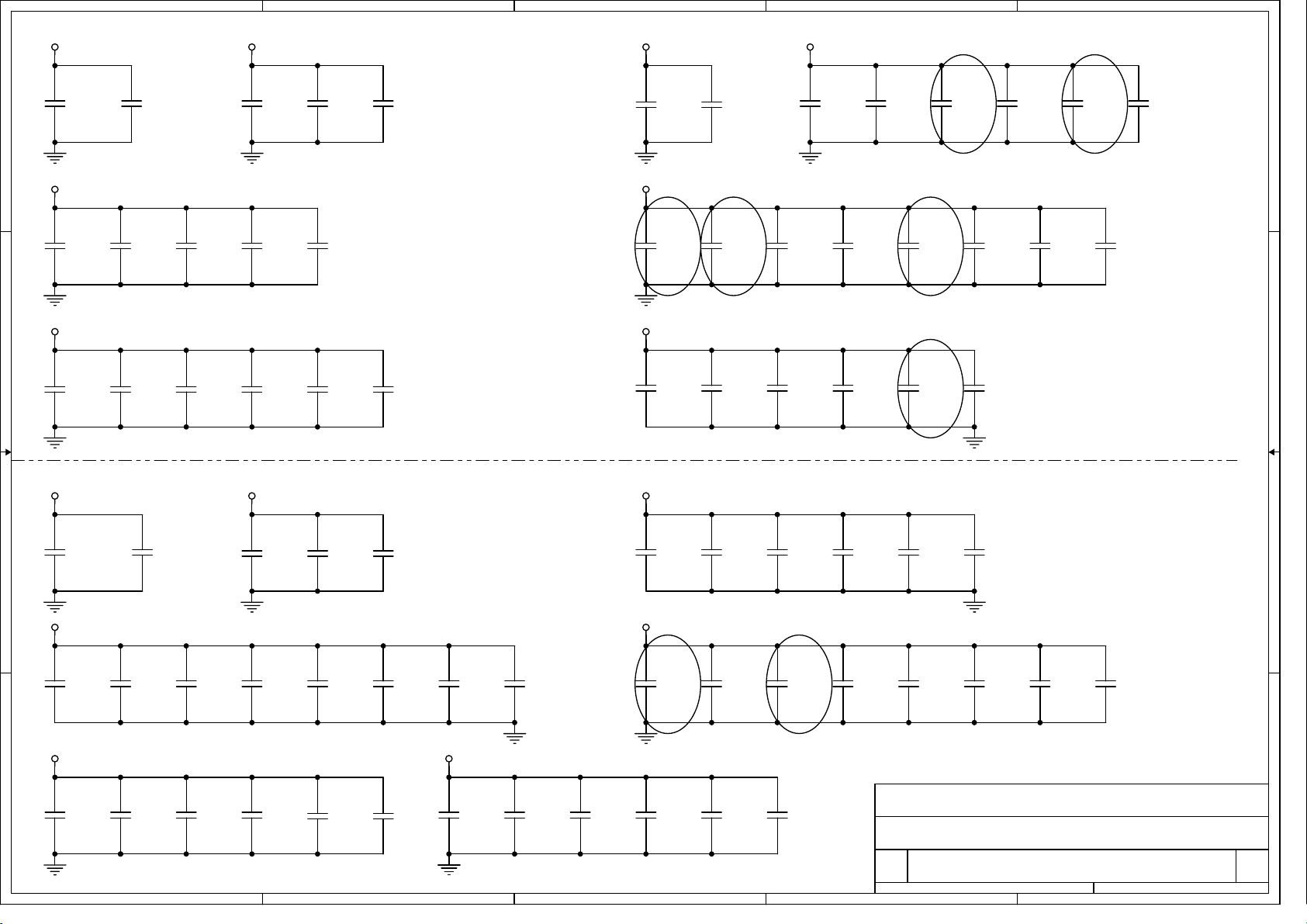

Page 7

5

4

3

2

1

VCC_P VCC_P

VCC_P

VCC_P

Btm side center

12

C927

D D

C C

1U/8/X7R

VCC_P

12

C929

0.1U/6/X7R

VCC_P VCC_P

SC933

10U/12

1 2

VCC_P

12

C928

1U/8/X7R

CPU 1

10U/12

12

1 2

12

C930

0.1U/6/X7R

SC934

1 2

C931

0.1U/6/X7R

SC935

10U/12

VCC_P

12

SBC30

10U/12

12

BC2

0.1U/6/X7R

SC937

10U/12

1 2

12

SC943

10U/12

12

BC4

0.1U/6/X7R

SC940

10U/12

1 2

12

1 2

SC946

10U/12

SC941

10U/12

1 2

VCC_P

12

12

VCC_P

SC919

10U/12

SC944

10U/12

SC952

10U/12

SC920

10U/12

1 2

12

SC947

10U/12

12

SC953

82U/1210

12

SC945

82U/1210

12

SC954

82U/1210

12

SC1028

82U/1210

12

SC942

82U/1210

12

SBC37

10U/12

12

SC1029

82U/1210

12

12

SC936

10U/12

SC956

10U/12

12

SC918

10U/12

12

12

SC939

10U/12

SC957

10U/12

12

SC917

82U/1210

12

SC938

10U/12

12

SC916

10U/12

12

SC932

10U/12

12

SC913

82U/1210

CPU2

12

SC967

VCC_P

12

VCC_P

10U/12

SC959

1U/8/X7R

B B

12

SC960

1U/8/X7R

12

SC981

10U/12

12

SC961

1U/8/X7R

SC949

10U/12

1 2

12

SC962

1U/8/X7R

SC950

10U/12

1 2

12

SC963

1U/8/X7R

SC951

10U/12

1 2

12

SC964

1U/8/X7R

12

VCC_P

SC965

1U/8/X7R

12

SC966

1U/8/X7R

12

VCC_P

12

SBC32

82U/1210

SC982

10U/12

12

SBC33

82U/1210

12

SC985

10U/12

12

SBC15

82U/1210

12

SC970

10U/12

12

SBC35

82U/1210

12

SC969

10U/12

12

SBC38

82U/1210

12

SC968

10U/12

12

12

SBC40

10U/12

SC984

10U/12

12

SC983

10U/12

12

SC986

10U/12

Btm side center

A A

12

SBC31

10U/12

12

SBC34

10U/12

5

12

SBC36

10U/12

12

SBC39

10U/12

1 2

SC955

10U/12

1 2

4

SC958

10U/12

12

SC1026

82U/1210

12

SC1027

10U/12

12

SC1031

10U/12

3

12

SC1032

10U/12

12

SC1033

82U/1210

12

SC1034

82U/1210

GIGABYTE TECHNOLOGY CORPORATION

Title

CPU_CAPS

Size Document Number Rev

Date: Sheet

2

星期二, 五月

06, 2003

8EGXDREL-01

7

1

64

of

1.0

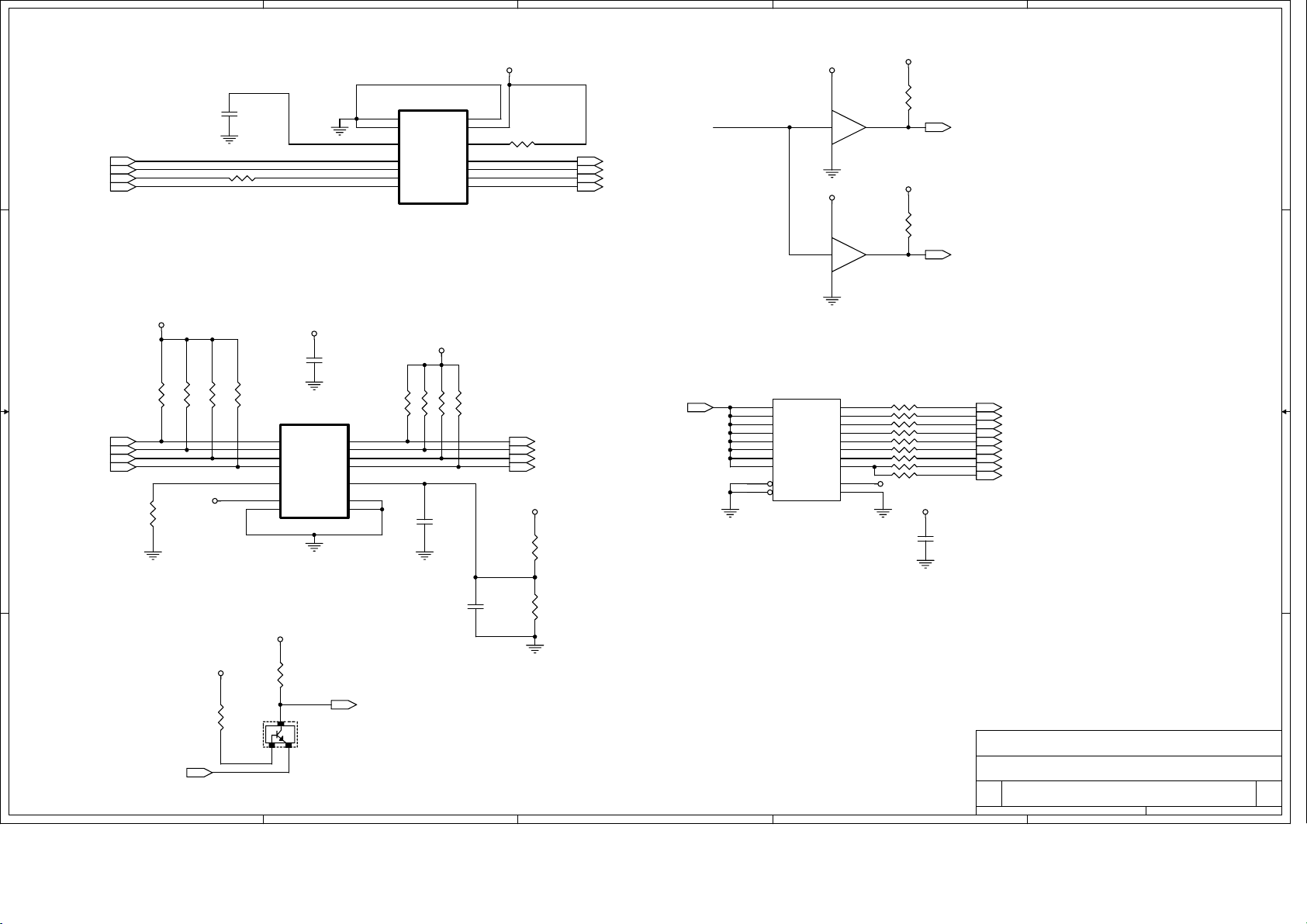

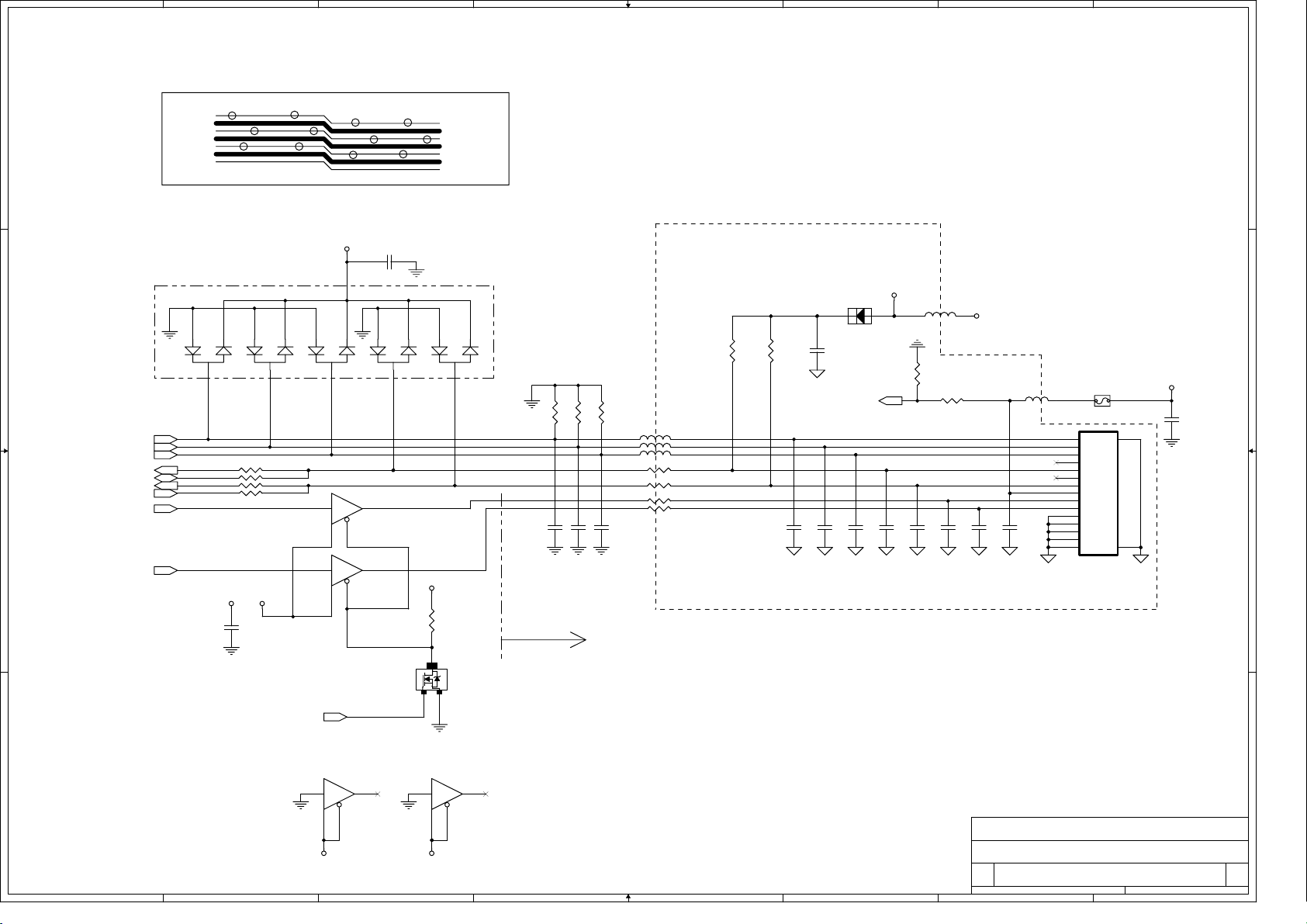

Page 8

A

B

C

D

E

VCC3VCC3

12

VCC3

R75649.9/6/1

12

R749 0/6

12

R75749.9/6/1

12

C908

0.01U/6

R75849.9/6/1

GTLREF_1

12

VCC3

U67 GTL2005

2

A1

3

A2

5

A3

6

A4

14

VDD

7

GND

-A20M_3V-RSB_A20M

12

C909

0.1U/6

B1

B2

B3

B4

GTLREFDIRB-A

GND

GND

4 4

INTR37

-RSB_IGNNE37

-RSB_A20M37

NMI37

3 3

-P1_PROC_HOT3

-P2_PROC_HOT5

-P1_IERR3

-P2_IERR5

2 2

INTR LINT0_3V

-RSB_IGNNE -IGNNE_3V

NMI LINT1_3V

VCC_P

12

R75549.9/6/1

R763

330/6

1 2

11

8

4 1

9

10

12

13

13

12

10

9

GTLREF_1

41

8

11

U65

GND

GND

GTLREF DIRB-A

B4

B3

B2

B1

GTL2005

VCC3

12

R760330/612R759330/6

12

GND

VDD

A4

A3

A2

A1

12

R7611K/6

C910

0.01U/6

7

14

R747 1K/6

1 2

6

5

3

2

12

R7621K/6

LINT0

-IGNNE

-A20M

LINT1

-RSB_P1_PROCHOT 37

-RSB_P2_PROCHOT 37

-RSB_P1_IERR 37,60 -PCIRST_S1_4 25,26,27,28

-RSB_P2_IERR 37,60

VCC_P

12

R750

49.9/6/1

LINT0 3,5,10

-IGNNE 3,5,10

-A20M 3,5,10

LINT1 3,5,10

-SL_PCIRST11

-SL_PCIRST

11

13

15

17

19

U72

2

1A1

4

1A2

6

1A3

8

1A4

2A1

2A2

2A3

2A4

1

1G

2G

74LCX244PWP/TSSOP20

147

U64E

11 10

74LCX07/TSSOP14

VCC3

147

U64F

13 12

74LCX07/TSSOP14

18

1Y1

16

1Y2

14

1Y3

12

1Y4

9

2Y1

7

2Y2

5

2Y3

3

2Y4

20

VDD

10

GND

VCC25

12

VCC3

12

R901 0/6

1 2

R902 0/6

1 2

R903 0/6

1 2

R905 0/6

1 2

R904 0/6

1 2

R1261 0/6

1 2

R1262 0/6

1 2

R1263 22/6

1 2

R1264 22/6

1 2

VCC3

VCC3

R751

51/6/1

R948

1K/6

12

-DIMM_RST 16,17

-SIO_LPCRST 51

C1369

0.1U/6

Routing

Sequentially

-PCIRST_6433 40,41,60

-PCIRST_LV 22,43

-BRSTDRV 36

-PCIRST_CSB6 36,37

-PCIRST_GLAN1 33

PCIRST_ARBITOR 46

-PCIRST_ZCR 21

-PCIRST_SATA 29

PCI SLOT 5, 6 & GSMI -PCIRST

82550 I, II& VGA -PCIRST

IDE

GLAN1_82545EM -PCIRST

PCI_ARBITOR -PCIRST

PCI SLOT_1_4

ZCR

SATA_FRODO

CSB6 -PWRGDCSB6 -PCIRST

12

C907

VCC3

VCC_P

12

1 1

-FERR3,5

A

R765

330/6

-FERR

12

R764

330/6

-RSB_FERR 37

Q54

2N3904

SOT23

132

B

0.01U/6

12

R752

100/6/1

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

C

D

Date: Sheet

VID_CONTROL_&_RESET_BUFFER

星期二, 五月

8EGXDREL-01

06, 2003

1.0

64

of

8

E

Page 9

A

B

C

D

E

VCC25

4 4

SC1185

0.01U/6

12

12

SC1186

0.01U/6

12

SC1187

0.01U/6

12

SC1188

0.01U/6

12

SC1189

0.01U/6

12

SC1190

0.01U/6

VCC3

VCC

12

SC1191

0.01U/6

3 3

VCC3

12

SC1192

0.01U/6

12

SC1193

0.01U/6

12

SC1194

0.01U/6

12

SC1195

0.01U/6

12

SC1196

0.01U/6

12

SC1197

0.01U/6

12

SC1198

0.01U/6

12

SC1199

0.01U/6

12

SC1200

0.01U/6

VCC25

12

SC1201

0.01U/6

12

SC1202

0.01U/6

12

SC1203

0.01U/6

12

SC1204

0.01U/6

12

SC1205

0.01U/6

VCC_P

VCC3

2 2

12

SC1206

0.01U/6

12

SC1207

0.01U/6

12

SC1208

0.01U/6

12

SC1209

0.01U/6

12

SC1210

0.01U/6

VCC_P

1 1

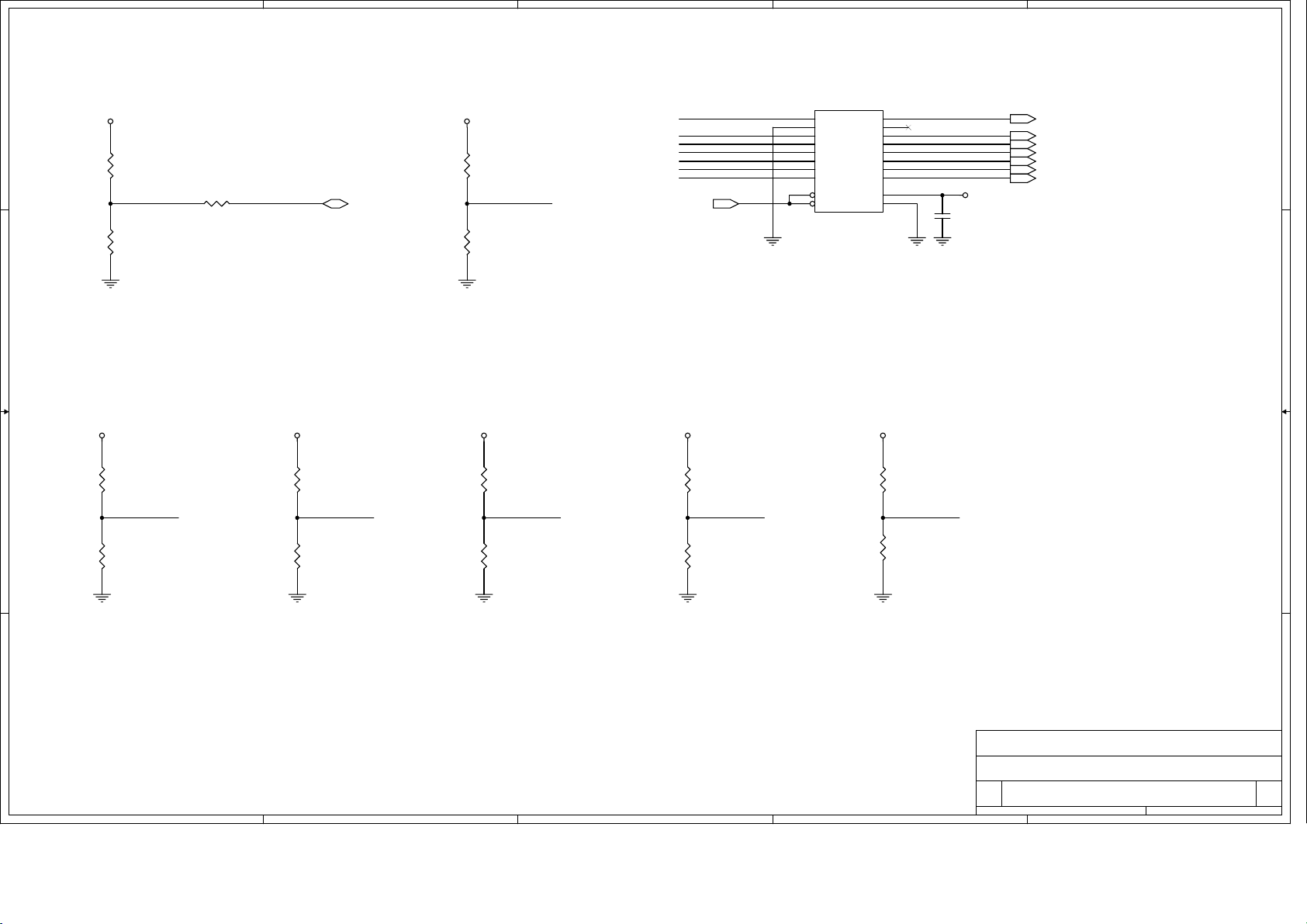

GIGABYTE TECHNOLOGY CORPORATION

Title

STITCHING CAPs

Size Document Number Rev

Date: Sheet

A

B

C

D

星期二, 五月

06, 2003

8EGXDREL-01

of

9

E

1.0

64

Page 10

A

PLACE THESE CLOSE TO CPU2

VCC_P

12

12

R72251/6/1/X

12

R72451/6/1

R72551/6/1

12

R72651/6/1

12

12

12

R72151/6/1

R72051/6/1

4 4

-PROC_RESET3,5,12

-BINIT3,5,11

-IGNNE3,5,8

-INIT3,5

-CPU_STPCLK3,5

LINT03,5,8

LINT13,5,8

-A20M3,5,8

-SLP3,5

3 3

-PROC_RESET

-BINIT

-IGNNE

-INIT

-CPU_STPCLK

LINT0

LINT1

-A20M

-SLP

PLACE NEAR CPU1

R72751/6/1

12

R72851/6/1

B

VCC_P

12

R72951/6/1

12

C884

0.1U/6

12

C885

0.1U/6

12

C886

0.1U/6

PLACE THE TERM CAPS NEAR THE

TRMINATION RESISTORS

-PROC_RESET -Q_CPU_RESET

R1148

1 2

1K/6

C

VCC_P

C888

0.1U/6

12

VCC3

12

2

1 3

-CPUBSP_TRI60 -SMI_BSP 5

C889

-CPUAP_TRI60

0.1U/6

-RESETDLY11

R1147

1K/6

Q83

MMBT2222A

12

12

C887

0.1U/6

R1048

1K/6

-RSB_SMI37

R1047 150/6

1 2

VCC3

R1173

1 2

0/6/X

VCC3

12

R1146

1K/6

3

D

GS

2

12

C1245

0.1U/6

1

VCC3

12

Q82

2N7002

D

VCC3

12

R731

1K/6

12

C1244

0.1U/6

168

U66

2

1A

3

VCCGND

1B

5

2A

6

2B

11

3A

10

3B

14

4A

13

4B

1

A/B

15

G

74LCX157/TSSOP16

4

1Y

7

2Y

9

3Y

12

4Y

VCC3 VCC3 VCC3

147

U83B

3 4

74LCX07/TSSOP14

VCC3

147

U64B

3 4

74LCX07/TSSOP14

VCC3

12

147

U83A

1 2

74LCX07/TSSOP14

5 6

147

U83C

74LCX07/TSSOP14

C1210

0.1U/6

VCC_P

VCC_P

E

12

R72351/6/1

-SMI_BSP

12

Near

R106151/6/1

CPU_Mid

-SMI_AP

-SMI_AP 3

147

U83D

9 8

74LCX07/TSSOP14

VCC_P

12

12

R73340.2/6/1

C8910.1U/6

12

12

R73440.2/6/1

C8920.1U/6

12

12

R73540.2/6/1

R736150/6/X

C8930.1U/6

12

P1_VCCA 3

P1_VSSA 3

P1_VCCIOPLL 3

12

12

R73740.2/6/1

C8940.1U/6

B

-LOCK 3,5,11

R744 0/8

1 2

R746 0/8

1 2

-RSB_SLP37

L14

1 2

4.7UH/8

L16

1 2

4.7UH/8

VCC3

12

12

12

C898

10U/12

C902

10U/12

R738

150/6

VCC3

147

U64C

5 6

74LCX07/TSSOP14

12

C899

10U/12

12

C903

10U/12

VCC3

VCC3

12

R730

150/6

147

-SLP -CPU_STPCLK

P2_VCCA 5

-RSB_STPCLK37

U64A

1 2

74LCX07/TSSOP14

-RSB_PINIT37

-KBD_INIT52

-CMIC_PINIT11

(Make small Cu Islands for

P2_VSSA 5

P2_VCCIOPLL 5

C

P1/P2_VCCA, P1/P2_VSSA

and P1/P2_VCCIOPLL nets )

D

R740 0/6

1 2

R741 0/6

1 2

R742 0/6

1 2

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

星期二, 五月

12

R73240.2/6/1

C8900.1U/6

12

2 2

-BNR3,5,11

-HIT3,5,11

-HITM3,5,11

-MCERR3,5

-BINIT

Place these Close to CPU1 Place these Close to CPU2

VCC_P VCC_P

R743 0/8

1 2

1 1

R745 0/8

1 2

L13

1 2

4.7UH/8

L15

1 2

4.7UH/8

A

12

12

C896

10U/12

C900

10U/12

12

12

C897

10U/12

C901

10U/12

147

U83E

11 10

74LCX07/TSSOP14

VCC25

VCC3

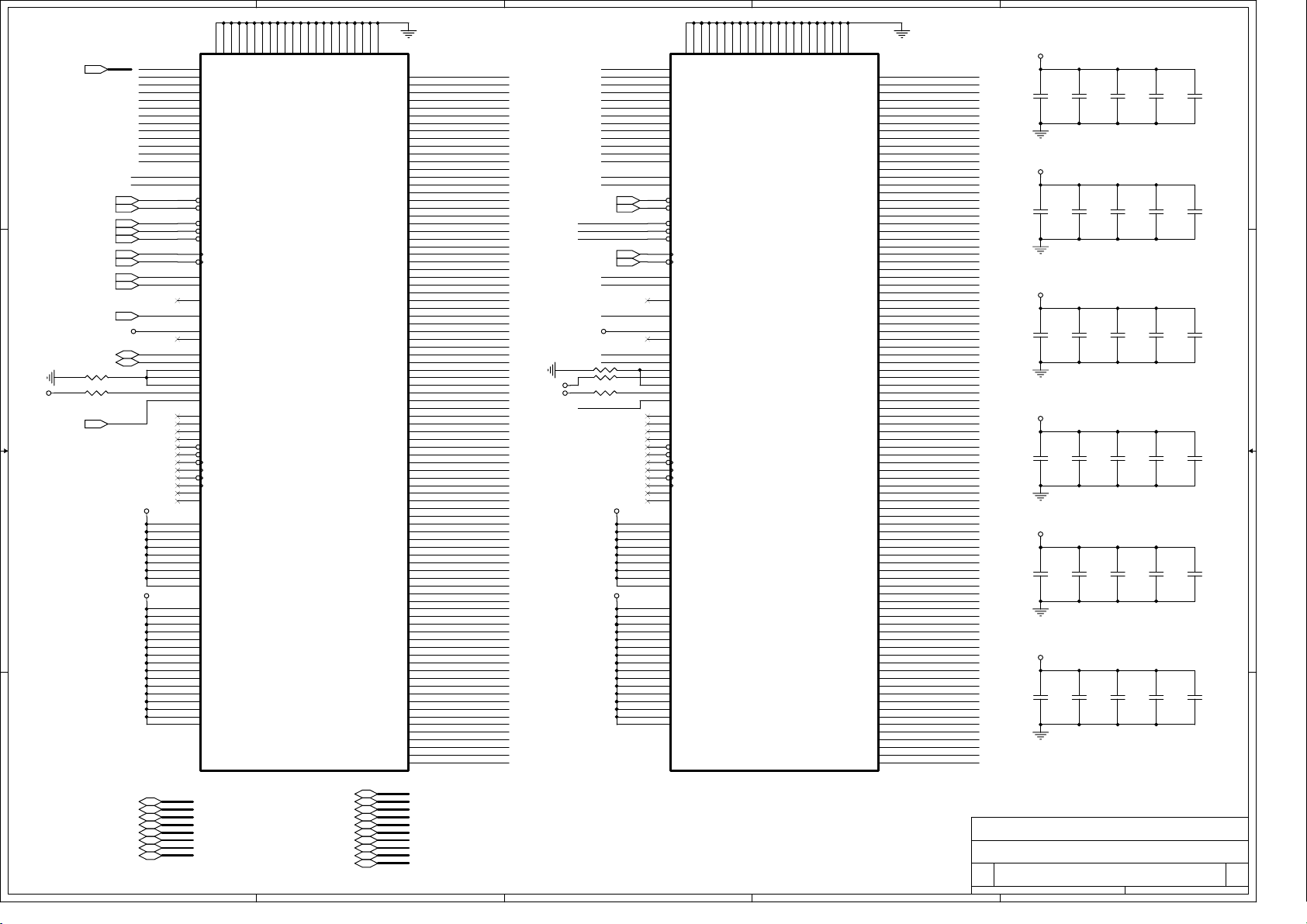

12

R739

150/6

9 8

CPU LEVEL SHIFT, MISC TERM

8EGXDREL-01

06, 2003

VCC3VCC3

13 12

147

U64D

74LCX07/TSSOP14

E

147

U83F

74LCX07/TSSOP14

-INIT

of

10

1.0

64

Page 11

A

B

C

D

E

@ Group ==> Pad to Pad distance < 10mil

@ Zt = 50_Ohm_+/- 10%

L1 = 3" ~ 10"

4 4

CMIC_SL

Source-Synchronus

L2 = 6" ~ 20"

CPU_ECPU_M

Associated Strobes

-PA[3..31]3,5

-PA[3..31]

Address and Data

T:S:C = 5mil/5mil/15milT:S = 5mil/15mil

-PD[15..0], -DINV0 -DSTBN0, -DSTBP0

-DSTBN1, -DSTBP1-PD[31..16], -DINV1

-DSTBN2, -DSTBP2-PD[47..32], -DINV3

-DSTBN3, -DSTBP3-PD[63..48], -DINV3

-PA[16..3], REQ[4..0]

-PA[35..17]

3 3

GND

40Ohm/6

L1 = 3" ~ 12" L2 = 6" ~ 20"

27P/6

CMIC_SL CPU_M CPU_E

AGTL Wire-OR signals

T:S = 5mil/15mil

-BINIT, -BNR, -HIT,

-HITM, -MCERR

2 2

VCC_P

12

12

SC881

220P/6

12

R713

49.9/6/1

C882

220P/6

P37: PU VCC25

GTL_VREF_CMIC

12

R715

100/6/1

12

C883

0.1U/6

-ADSTB0

-ADSTB1

-ADSTB03,5

-ADSTB13,5

-ADS3,5

-BNR3,5,10

-BPRI3,5

-DBSY3,5

-DRDY3,5

-HIT3,5,10

-HITM3,5,10

-LOCK3,5,10

-P_TRDY3,5

-DEFER3,5

-BREQ03,5

R963 0/6

VCC25

1 2

-RESETDLY10

-SL_PCIRST8

-RS03,5

-RS13,5

-RS23,5

-HREQ03,5

-HREQ13,5

-HREQ23,5

-HREQ33,5

-HREQ43,5

-CMIC_ALERT15,37

-BINIT3,5,10

-CMIC_PINIT10

HCLK_CMIC20

HCLK_CMIC_N20

R714 4.7K/6

1 2

-MEMOFFACK

R716 4.7K/6

1 2

VCC25

R712 4.7K/6

1 2

PLLRST37,61

-CMIC_FATAL15,37

VCC25

-MEMOFF15,37

-MEMOFFACK15

-PA3

-PA4

-PA5

-PA6

-PA7

-PA8

-PA9

-PA10

-PA11

-PA12

-PA13

-PA14

-PA15

-PA16

-PA17

-PA18

-PA19

-PA20

-PA21

-PA22

-PA23

-PA24

-PA25

-PA26

-PA27

-PA28

-PA29

-PA30

-PA31

-ADSTB0

-ADSTB1

-ADS

-BNR

-BPRI

-DBSY

-DRDY

-HIT

-HITM

-LOCK

-P_TRDY

-DEFER

-BREQ0

PLLRST_SLPLLRST

-RESETDLY

-SL_PCIRST

-RS0

-RS1

-RS2

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

-CMIC_FATAL

-MEMOFF

-MEMOFFACK

GTL_VREF_CMIC

GTL_COMP_PU

GTL_COMP_PD

GTL_RCOMP

U63A

C30

A3#

D31

A4#

E33

A5#

E31

A6#

D32

A7#

F32

A8#

F33

A9#

J30

A10#

G33

A11#

F30

A12#

K30

A13#

G30

A14#

G31

A15#

H30

A16#

L30

A17#

M30

A18#

J31

A19#

N30

A20#

N33

A21#

M32

A22#

L31

A23#

J33

A24#

K32

A25#

N31

A26#

P33

A27#

K33

A28#

L33

A29#

M33

A30#

P32

A31#

CMIC_SL

H32

ADSTB0#

H33

ADSTB1#

D3

ADS#

R33

BNR#

E3

BPRI#

A32

DBSY#

C1

DRDY#

B1

HIT#

D2

HITM#

E1

LOCK#

E4

TRDY#

D5

DEFER#

P30

BREQ0#

AC4

PLLRST

AE1

DLYRST

AD5

PCIRST#

C2

RS0#

A2

RS1#

C4

RS2#

C33

HREQ0#

E30

HREQ1#

C32

HREQ2#

B33

HREQ3#

B31

HREQ4#

AG1

ALERT#

T32

BINIT#

AF4

HINIT#

AF2

BCLKP

AF1

BCLKN

AG3

FATAL#

W30

MEMOFF#

W31

MEMOFFACK#

A11

GTL_VREF1

U31

GTL_VREF2

B10

GTL_COMP_PU

U30

GTL_COMP_PD

C11

GTL_RCOMP

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DP0#

DP1#

DP2#

DP3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

D10

D7

A3

B3

D9

B6

B4

D6

C5

C7

C9

A6

A7

A5

A9

A10

D17

C17

A17

D16

D14

D15

D11

D12

A15

A13

A12

D13

C15

B12

B16

A16

A19

D18

A18

A22

B18

C19

D19

A21

C21

B22

D20

C23

D23

D24

D21

D22

C25

D25

B24

A25

A24

D26

A27

C27

D27

D28

A31

C29

D29

A29

A28

B30

D8

C13

A23

B28

T33

T30

R30

R31

B8

A14

A20

B26

A8

B14

B20

A26

-PD0

-PD1

-PD2

-PD3

-PD4

-PD5

-PD6

-PD7

-PD8

-PD9

-PD10

-PD11

-PD12

-PD13

-PD14

-PD15

-PD16

-PD17

-PD18

-PD19

-PD20

-PD21

-PD22

-PD23

-PD24

-PD25

-PD26

-PD27

-PD28

-PD29

-PD30

-PD31

-PD32

-PD33

-PD34

-PD35

-PD36

-PD37

-PD38

-PD39

-PD40

-PD41

-PD42

-PD43

-PD44

-PD45

-PD46

-PD47

-PD48

-PD49

-PD50

-PD51

-PD52

-PD53

-PD54

-PD55

-PD56

-PD57

-PD58

-PD59

-PD60

-PD61

-PD62

-PD63

-DINV0

-DINV1

-DINV2

-DINV3

-DP0

-DP1

-DP2

-DP3

-DSTBN0

-DSTBN1

-DSTBN2

-DSTBN3

-DSTBP0

-DSTBP1

-DSTBP2

-DSTBP3

-PD[0..63]

-PD[0..63] 3,5

-DINV[0..3] 3,5

-DP[0..3] 3,5

-DSTBN[0..3] 3,5

-DSTBP[0..3] 3,5

VCC_P

1 1

Inter-Group Space = 25mil

Signal / Signal = 5mil / 15mil

Signal / Strobe = 5mil / 15mil

A

B

R717 100/6/1

1 2

R718 300/6/1

1 2

R719 20.5/6/1

1 2

GTL_COMP_PD

GTL_COMP_PU

GTL_RCOMP

C

CMIC_SL

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

D

星期二, 五月

CMIC PROCESSOR I/F

8EGXDREL-01

06, 2003

1.0

64

of

11

E

Page 12

A

B

C

D

E

CMIC_SL

4 4

Transmit Link

T_IMB_D_T[0..3]

T_IMB_CLK_TR

T_TIMB_CON_T

T_TIMB_PAR_T

33_Ohm

L0

0"~1.0"

1"~11"

100MHz, DDR

Inner Layer

( 5mil, 50Ohm )

( T:S = 1:3 )

L1

1"~11"

L1

L0

0"~1.0"

150_OhmCMIC_SL

3 3

CMIC_SL

Transmit Link

A_IMB_D_T[0..15]

A_IMB_CON_T

A_IMB_PAR_T

400MHz, DDR

Inner Layer 2,3

L0

1"~12"

( 6mil, 45Ohm )

( T:S = 1:3 )

A_IMB_CLK_T_P

A_IMB_CLK_T_N

On the Same Layer

2 2

VCC15

12

R708

100/6/1

IMB_VREF_CMIC

C878

220P/6

12

12

1 1

C879

220P/6

12

A

R711

100/6/1

12

T_IMB_D_T[0..3]37

T_IMB_CLK_T37 T_IMB_CLK_R 37

T_IMB_CON_T37

T_IMB_PAR_T37

SWAPABLE

C880

0.1U/6

CSB6

100MHz, 50_Ohm

Receive Link

T_IMB_D_R[0..3]

T_IMB_CLK_R

T_TIMB_CON_R

T_TIMB_PAR_R56_Ohm

100MHz, 50_Ohm

CSB6

CIOB2X

Receive Link

A_IMB_D_R[0..15]

A_IMB_CON_R

A_IMB_PAR_R

A_IMB_CLK_R_P

A_IMB_CLK_R_N

On the Same Layer

T_IMB_D_T[0..3]

T_IMB_D_T0

T_IMB_D_T3

T_IMB_D_T2

T_IMB_D_T1

VCC15

RN138 8P4R/33

T_IMB_CLK_T

T_IMB_CON_T

T_IMB_PAR_T

1 2

B

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN139 8P4R/33

R706 100/6/1

1 2

R709

255/6/1

R_T_IMB_D_T0

R_T_IMB_D_T1

R_T_IMB_D_T2

R_T_IMB_D_T3

R_T_IMB_CLK_TR

R_T_IMB_CON_T

R_T_IMB_PAR_T

IMB_VREF_CMIC

CMIC_IMB_COMP_PD

CMIC_IMB_COMP_PU

CMIC_IMB_RCOMP

R710

100/6/1

1 2

VCC15

U63B

AH2

T_IMBD_T0

AJ3

T_IMBD_T1

AG4

T_IMBD_T2

AH1

T_IMBD_T3

P2

IMB_VREF

R3

IMB_COMP_PD

Y4

IMB_COMP_PU

N3

IMB_RCOMP

CMIC_SL

CMIC_SL

C

AIMBD_R0

AIMBD_R1

AIMBD_R2

AIMBD_R3

AIMBD_R4

AIMBD_R5

AIMBD_R6

AIMBD_R7

AIMBD_R8

AIMBD_R9

AIMBD_R10

AIMBD_R11

AIMBD_R12

AIMBD_R13

AIMBD_R14

AIMBD_R15

AIMBCON_R

AIMBCLK_R_P

AIMBCLK_R_N

AIMBPAR_R

AIMBD_T0

AIMBD_T1

AIMBD_T2

AIMBD_T3

AIMBD_T4

AIMBD_T5

AIMBD_T6

AIMBD_T7

AIMBD_T8

AIMBD_T9

AIMBD_T10

AIMBD_T11

AIMBD_T12

AIMBD_T13

AIMBD_T14

AIMBD_T15

AIMBCON_T

AIMBCLK_T_P

AIMBCLK_T_N

AIMBPAR_T

T_IMBD_R0

T_IMBD_R1

T_IMBD_R2

T_IMBD_R3

T_IMBCLK_RT_IMBCLK_T

T_IMBCON_RT_IMBCON_T

T_IMBPAR_RT_IMBPAR_T

CPURST#

SRESET#

TESTMODE#

SDA

SCLK

G3

G4

G1

H2

J1

J3

H4

H1

J4

M2

M1

L3

L1

K4

M4

N4

L4

K2

K1

N1

T2

U3

T1

T4

R4

R1

U4

V4

U1

AB1

Y1

Y2

AA3

W3

W1

AA4

AA1

V1

V2

W4

AN2

AL1

AM2

AK4

AM1AK2

AL3AH4

AN3AJ1

U33

AD4

AF5

AE3

AE4

A_IMB_D_R0

A_IMB_D_R1

A_IMB_D_R2

A_IMB_D_R3

A_IMB_D_R4

A_IMB_D_R5

A_IMB_D_R6

A_IMB_D_R7

A_IMB_D_R8

A_IMB_D_R9

A_IMB_D_R10

A_IMB_D_R11

A_IMB_D_R12

A_IMB_D_R13

A_IMB_D_R14

A_IMB_D_R15

A_IMB_CON_R

A_IMB_CLK_R_P

A_IMB_CLK_R_N

A_IMB_PAR_R

T_IMB_D_R0

T_IMB_D_R1

T_IMB_D_R2

T_IMB_D_R3

T_IMB_CLK_R

T_IMB_CON_R

T_IMB_PAR_R

D

T_IMB_D_R[0..3]

T_IMB_CON_R 37

T_IMB_PAR_R 37

R707 4.7K/6

1 2

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

VCC15

T_IMB_D_R[0..3] 37

-PROC_RESET 3,5,10

POWERGOOD_CMIC 15,61

VCC25

-TESTMODE 15

RCC_SDA 15,16,17,20,50,60

RCC_SCL 15,16,17,20,50,60

RN150

8P4R-100

RN151

8P4R-100

RN152

8P4R-100

RN153

8P4R-100

RN154

8P4R-100

GIGABYTE TECHNOLOGY CORPORATION

Title

Size Document Number Rev

Date: Sheet

星期二, 五月

06, 2003

CMIC IMB I/F

8EGXDREL-01

E

of

12

1.0

64

Page 13

A

R_A_SD0_[0..7]18

R_A_SD1_[0..7]18

R_A_SD2_[0..7]18

R_A_SD3_[0..7]18

R_A_SD4_[0..7]18

R_A_SD5_[0..7]18

R_A_SD6_[0..7]18

4 4

3 3

2 2

1 1

R_A_SD7_[0..7]18

R_A_SD8_[0..7]18

A

R_A_SD0_0

R_A_SD0_1

R_A_SD0_2

R_A_SD0_3

R_A_SD0_4

R_A_SD0_5

R_A_SD0_6

R_A_SD0_7

R_A_SD1_0

R_A_SD1_1

R_A_SD1_2

R_A_SD1_3

R_A_SD1_4

R_A_SD1_5

R_A_SD1_6

R_A_SD1_7

R_A_SD2_0

R_A_SD2_1

R_A_SD2_2

R_A_SD2_3

R_A_SD2_4

R_A_SD2_5

R_A_SD2_6

R_A_SD2_7

R_A_SD3_0

R_A_SD3_1

R_A_SD3_2

R_A_SD3_3

R_A_SD3_4

R_A_SD3_5

R_A_SD3_6

R_A_SD3_7

R_A_SD4_0

R_A_SD4_1

R_A_SD4_2

R_A_SD4_3

R_A_SD4_4

R_A_SD4_5

R_A_SD4_6

R_A_SD4_7

R_A_SD5_0

R_A_SD5_1

R_A_SD5_2

R_A_SD5_3

R_A_SD5_4

R_A_SD5_5

R_A_SD5_6

R_A_SD6_0

R_A_SD6_1

R_A_SD6_2 MA3

R_A_SD6_3

R_A_SD6_4

R_A_SD6_5

R_A_SD6_6

R_A_SD6_7

R_A_SD7_0

R_A_SD7_1

R_A_SD7_2

R_A_SD7_3

R_A_SD7_4

R_A_SD7_5

R_A_SD7_6

R_A_SD7_7

R_A_SD8_0

R_A_SD8_1

R_A_SD8_2

R_A_SD8_3

R_A_SD8_4

R_A_SD8_5

R_A_SD8_6

R_A_SD8_7

Y30

Y32

AA31

AB30

AA30

Y33

AA33

AC30

AC31

AD30

AF33

AF32

AE30

AC33

AE33

AE31

AF30

AG33

AH30

AK33

AG30

AG31

AJ33

AJ31

AK24

AL27

AL25

AM24

AK26

AK25

AN27

AN25

AK16

AL17

AN15

AL15

AK17

AN17

AK15

AK14

AM14

AL13

AN11

AL11

AN14

AN13

AK13

AK12

AK11

AM10

AK10

AK9

AN9

AN10

AL9

AK8

AN7

AK6

AL5

AM4

AK7

AL7

AN5

AK5

AN23

AL23

AK22

AK21

AK23

AN24

AL21

AK20

B

U63C

A_SD0_0

A_SD0_1

A_SD0_2

A_SD0_3

A_SD0_4

A_SD0_5

A_SD0_6

A_SD0_7

A_SD1_0

A_SD1_1

A_SD1_2

A_SD1_3

A_SD1_4

A_SD1_5

A_SD1_6

A_SD1_7

A_SD2_0

A_SD2_1

A_SD2_2

A_SD2_3

A_SD2_4

A_SD2_5

A_SD2_6

A_SD2_7

A_SD3_0

A_SD3_1

A_SD3_2

A_SD3_3

A_SD3_4

A_SD3_5

A_SD3_6

A_SD3_7

A_SD4_0

A_SD4_1

A_SD4_2

A_SD4_3

A_SD4_4

A_SD4_5

A_SD4_6

A_SD4_7

A_SD5_0

A_SD5_1

A_SD5_2

A_SD5_3

A_SD5_4

A_SD5_5

A_SD5_6

A_SD5_7

A_SD6_0

A_SD6_1

A_SD6_2

A_SD6_3

A_SD6_4

A_SD6_5

A_SD6_6

A_SD6_7

A_SD7_0

A_SD7_1

A_SD7_2

A_SD7_3

A_SD7_4

A_SD7_5

A_SD7_6

A_SD7_7

A_SD8_0

A_SD8_1

A_SD8_2

A_SD8_3

A_SD8_4

A_SD8_5

A_SD8_6

A_SD8_7

CMIC_SL

B

CMIC_SL

A_DQS0_0

A_DQS0_1