Page 1

5

GA-890FXA-UD7

PAGE

TITLE

4

Revision : 2.01

26

27

3

TITLEPAGE

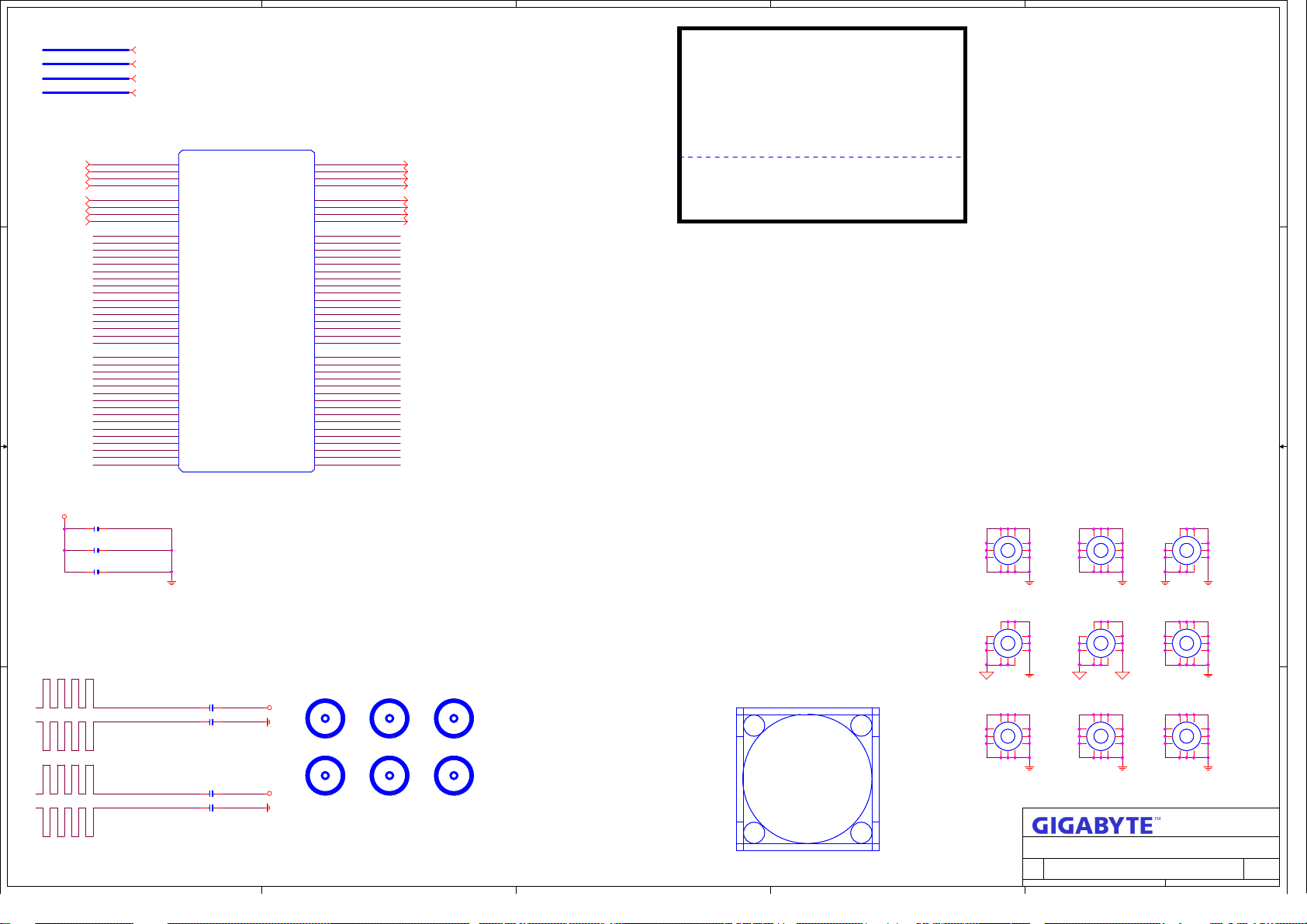

AUDIO JACK

FAN/HWMO, EC

2

1

D D

C C

B B

01 COVER SHEET

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

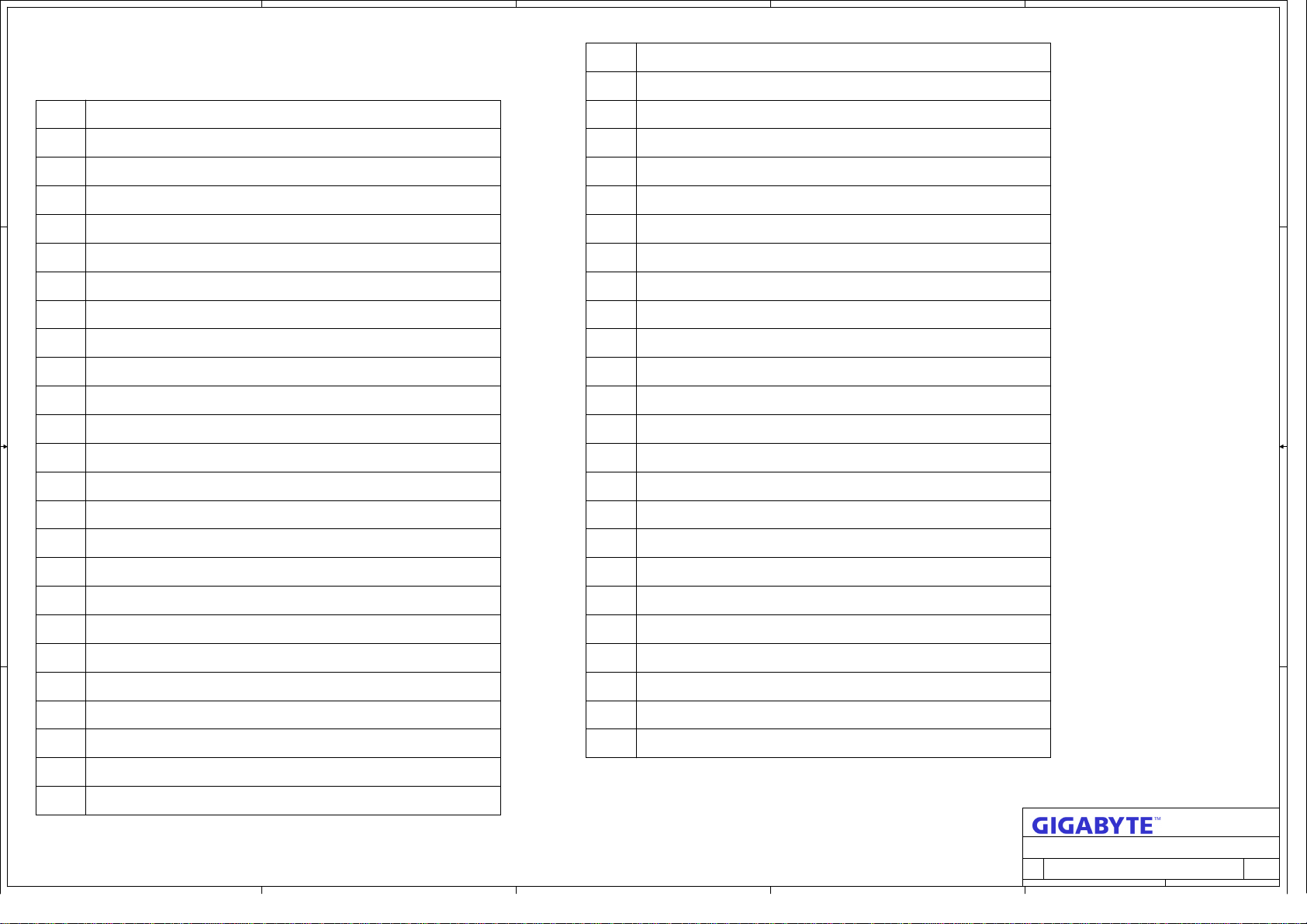

BOM & PCB MODIFY HISTORY

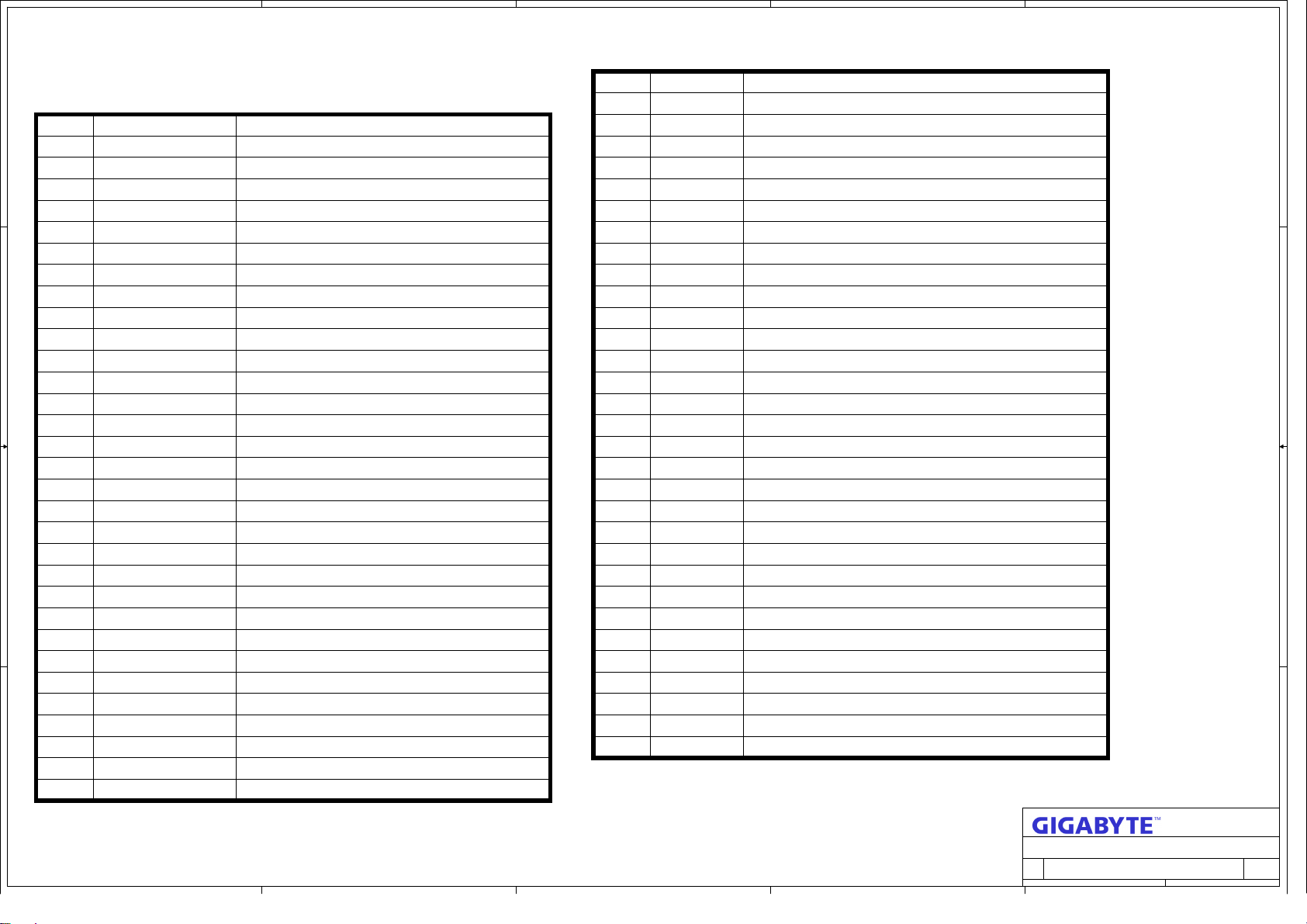

BLOCK DIAGRAM

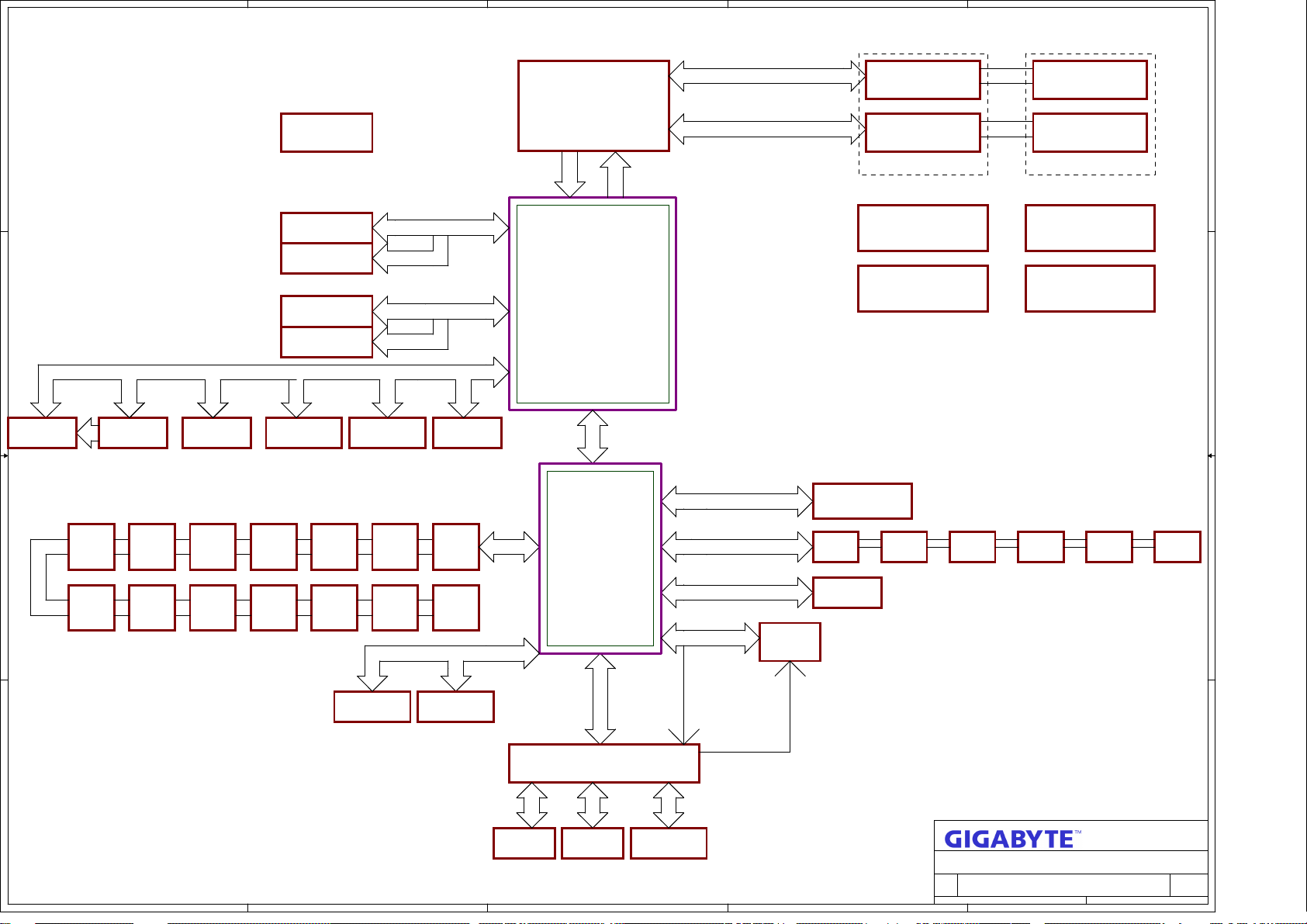

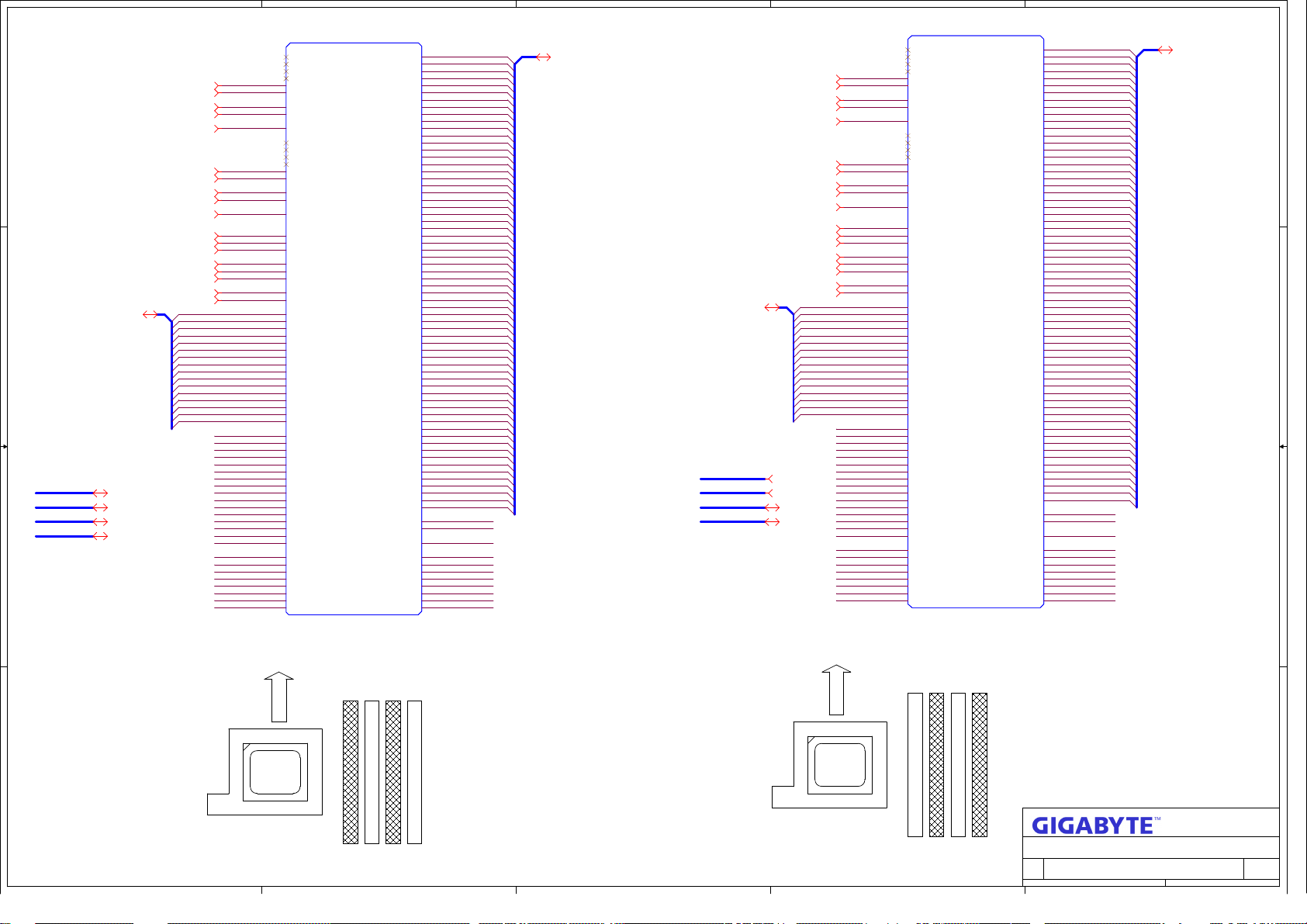

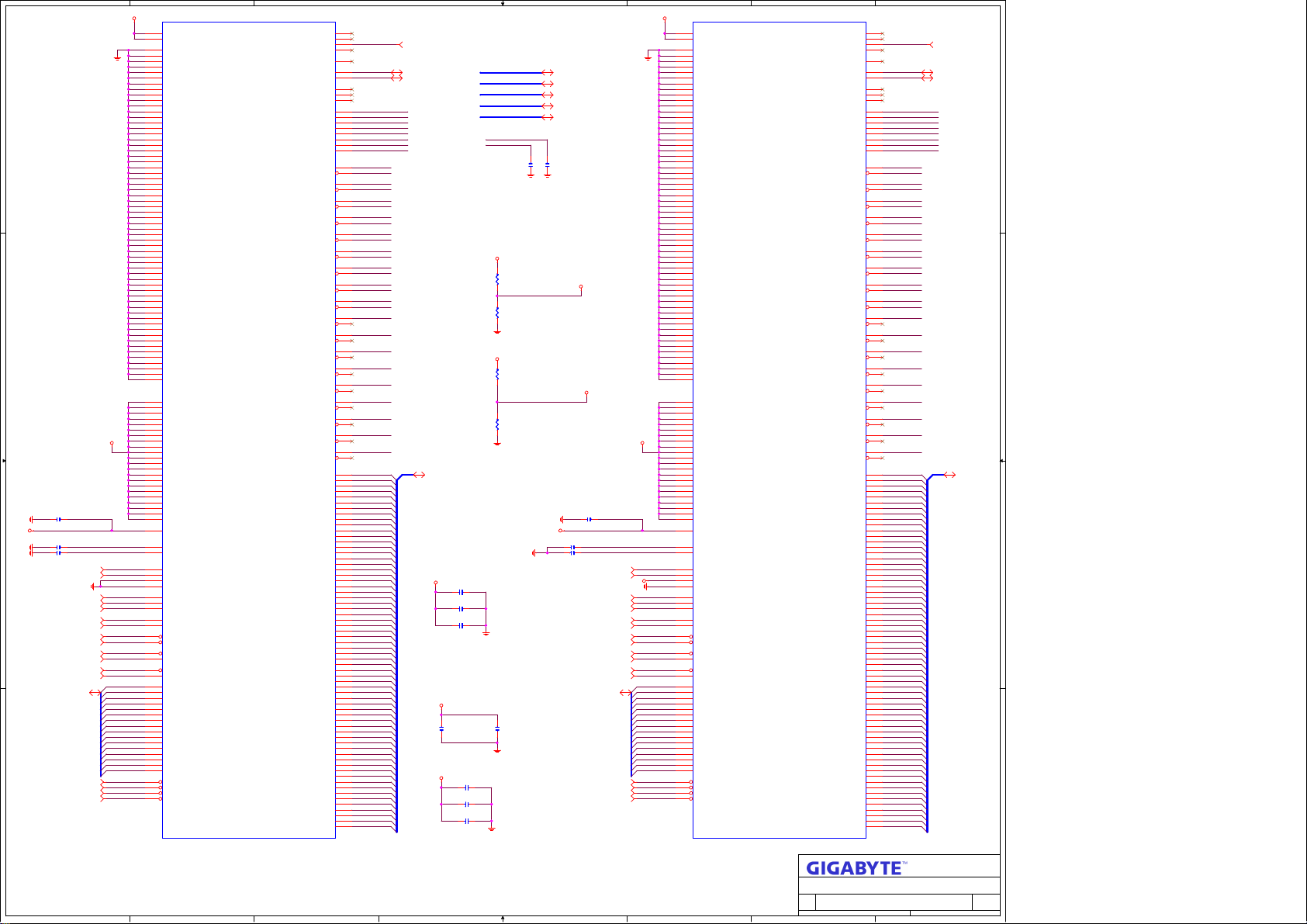

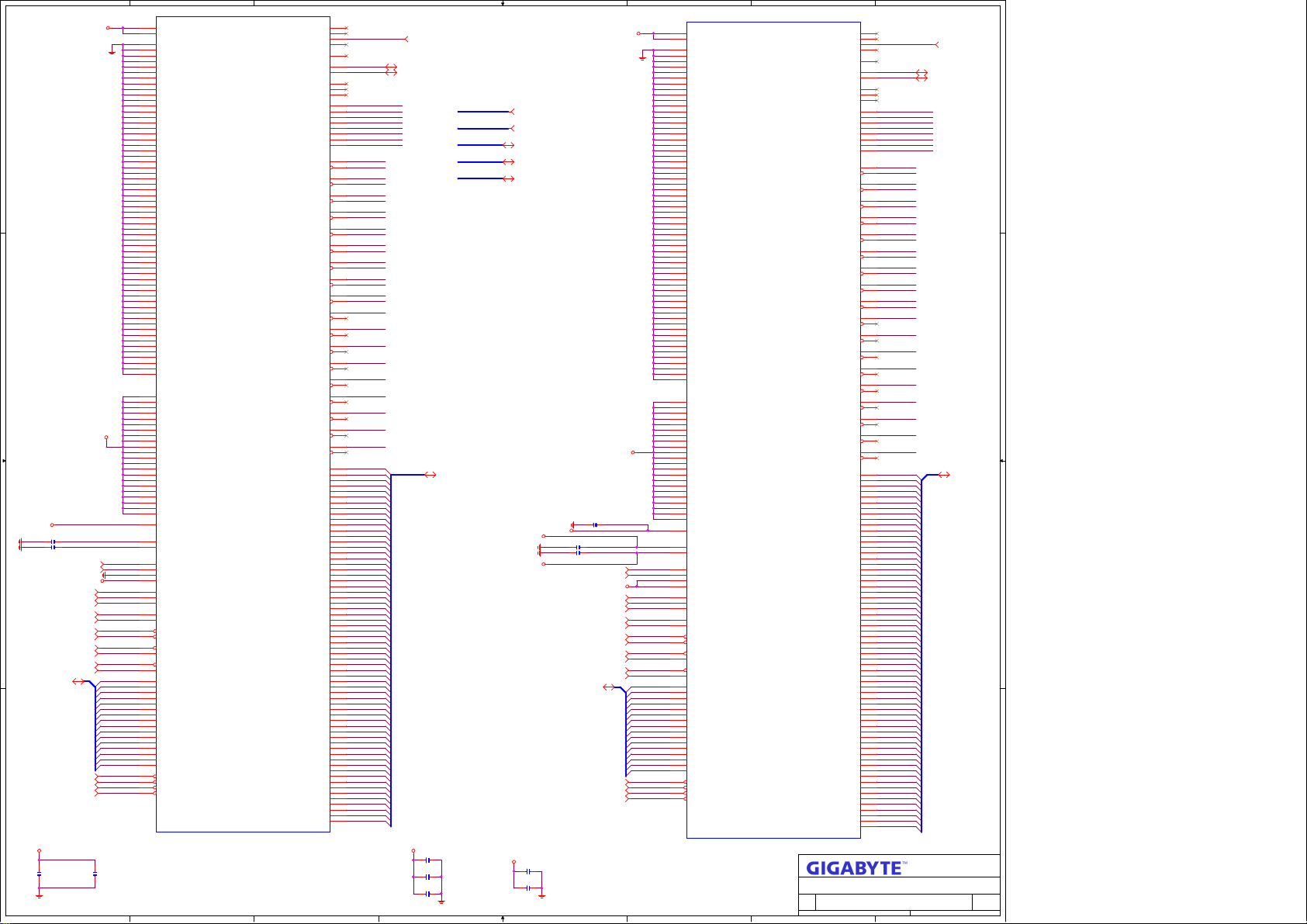

CPU HYPER TRANSPORT

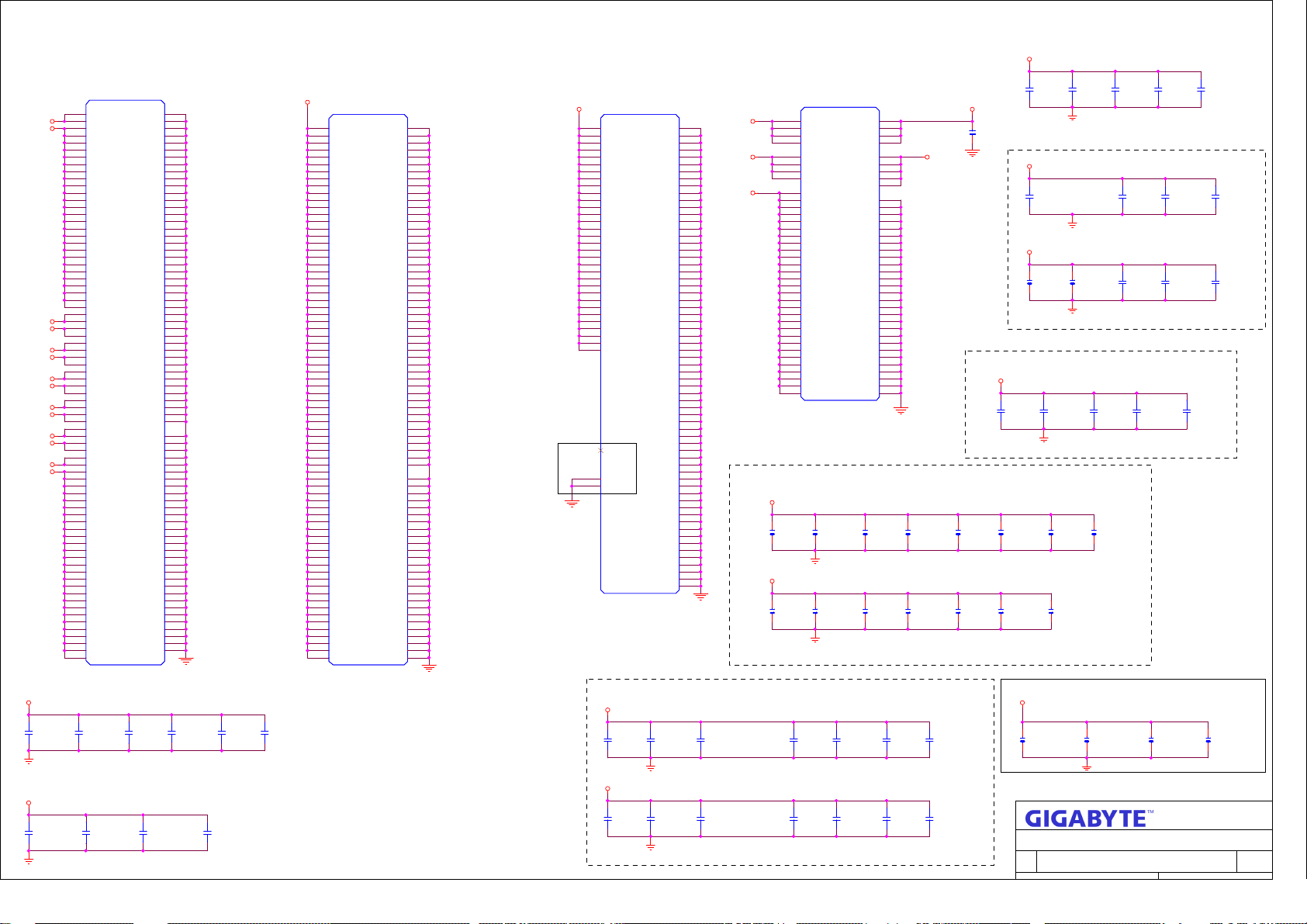

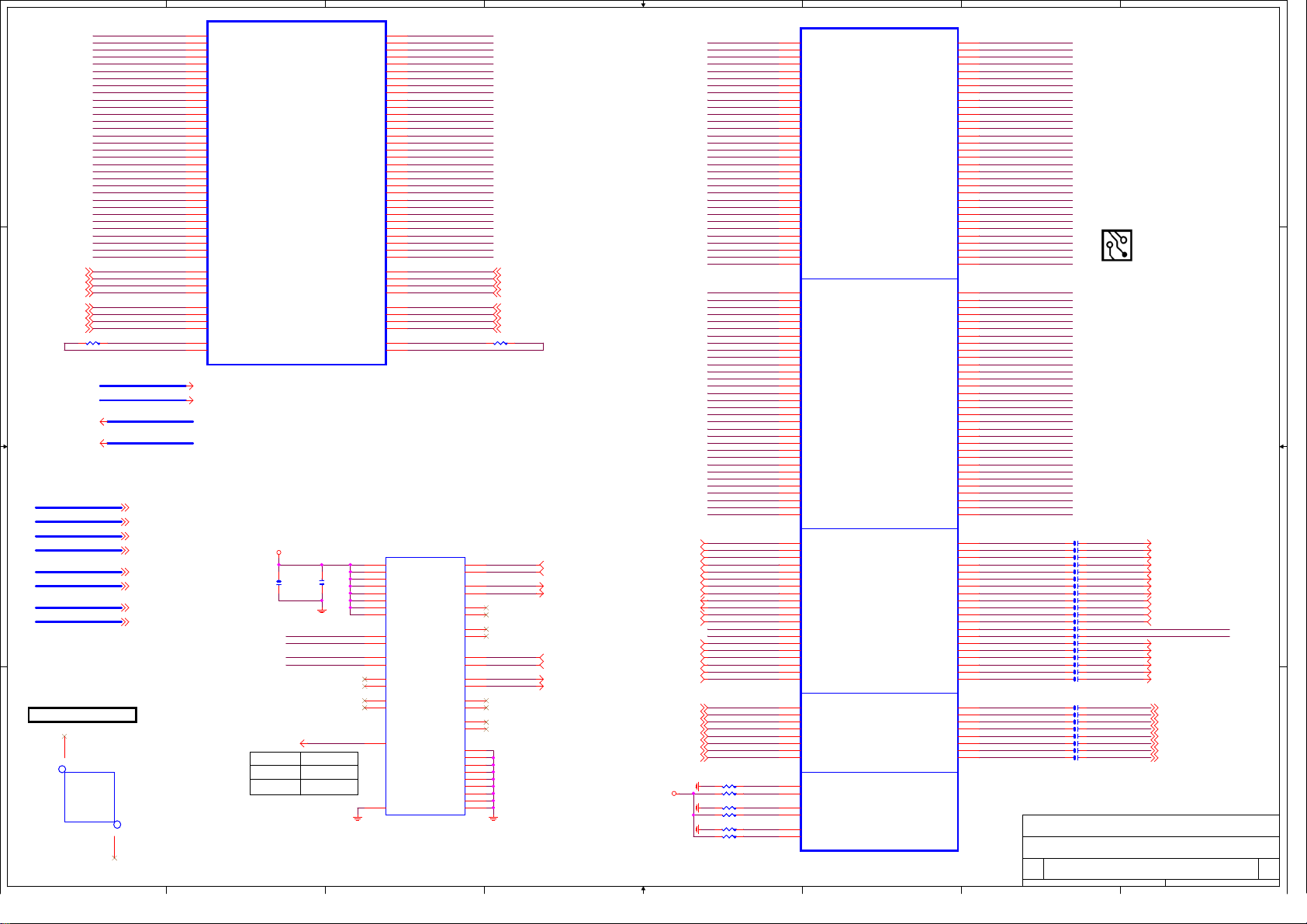

CPU DDR3 MEMORY

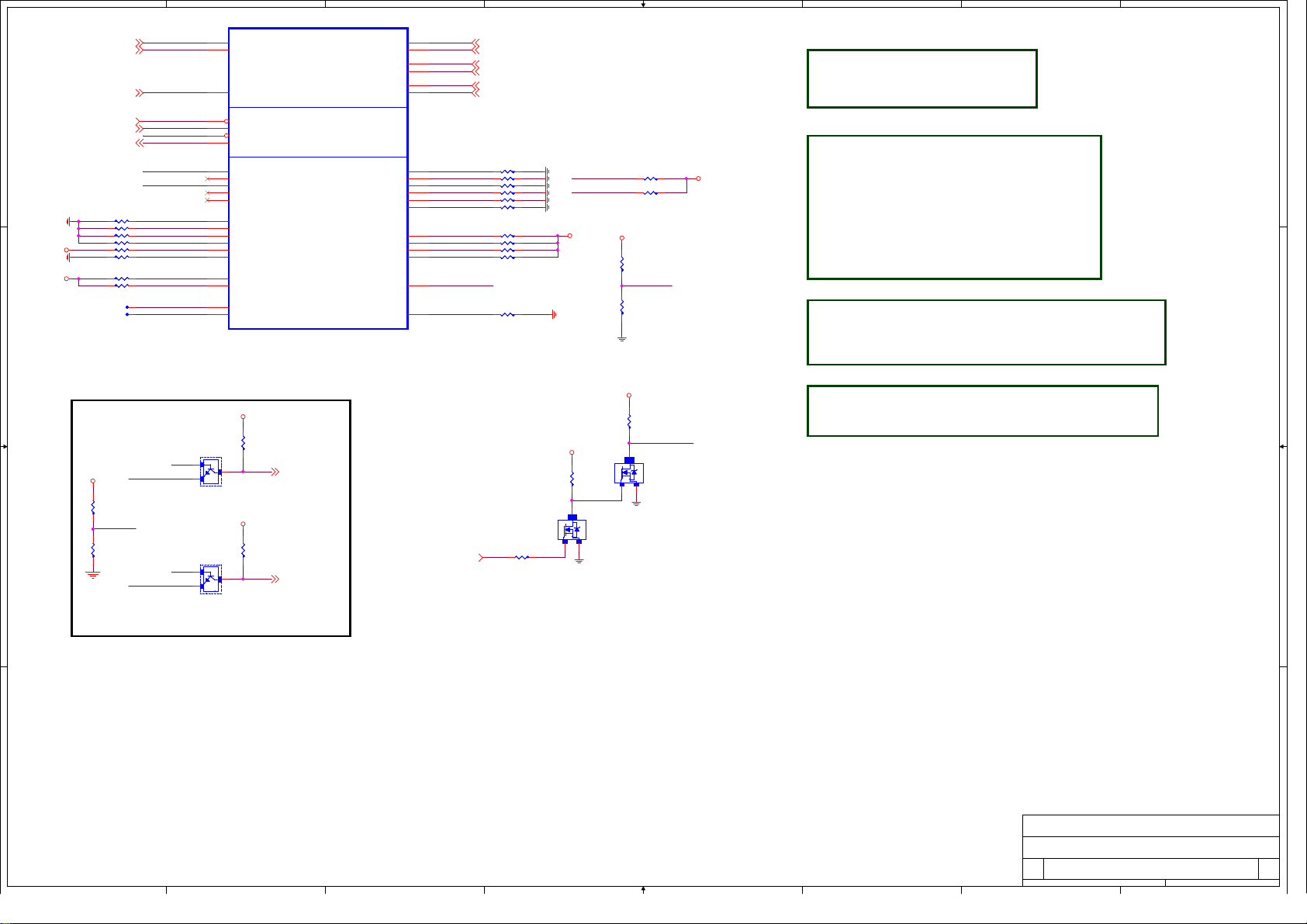

CPU CONTROL

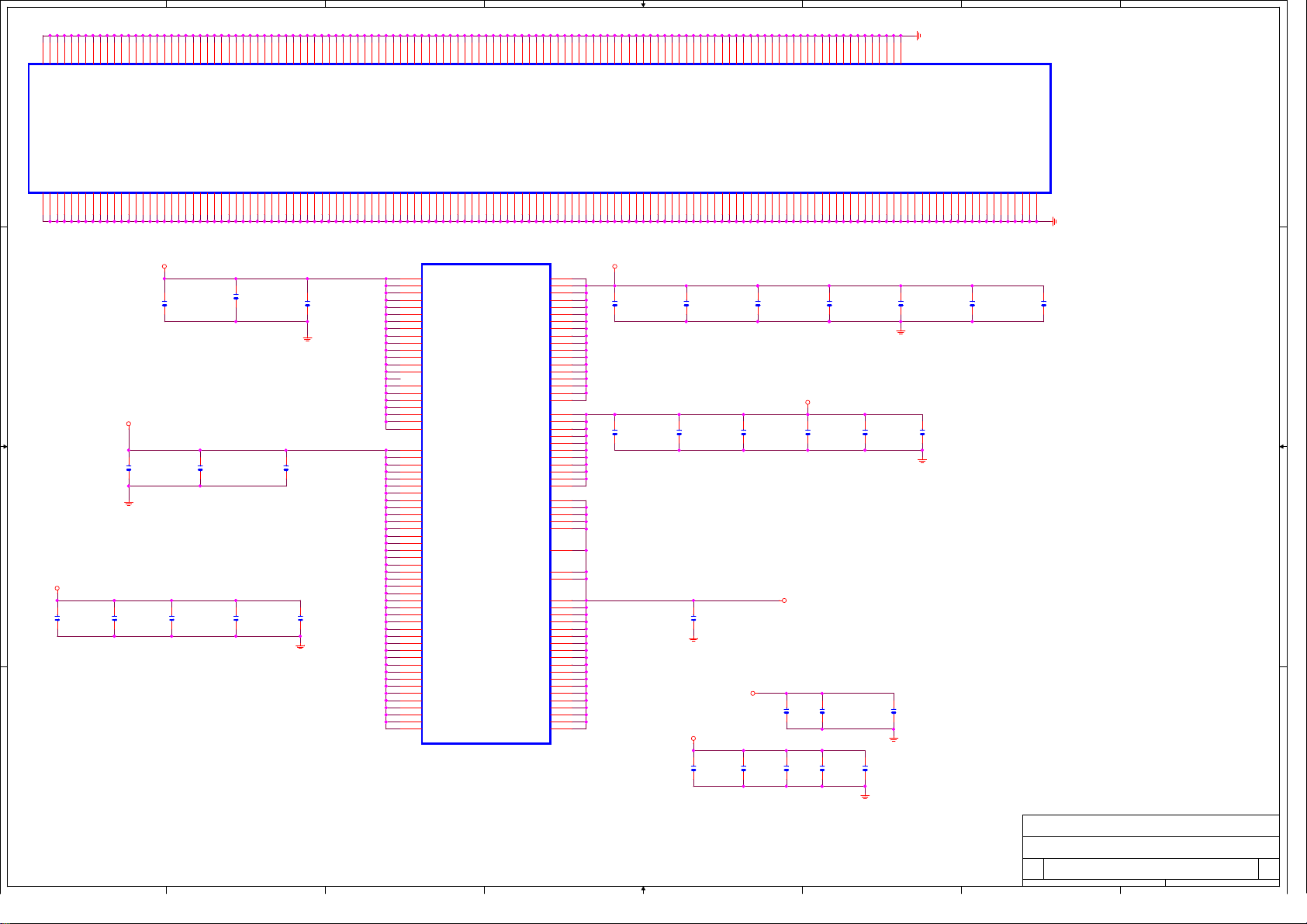

CPU POWER & GND

DDR3 CHANNEL A

DDR3 CHANNEL B

RD890 HT-LINK I/F, PCIE I/F

RD890 SYSTEM I/F, STRAPS

RD890 POWER & GND

RTM880N-793 + ICS9DBL411

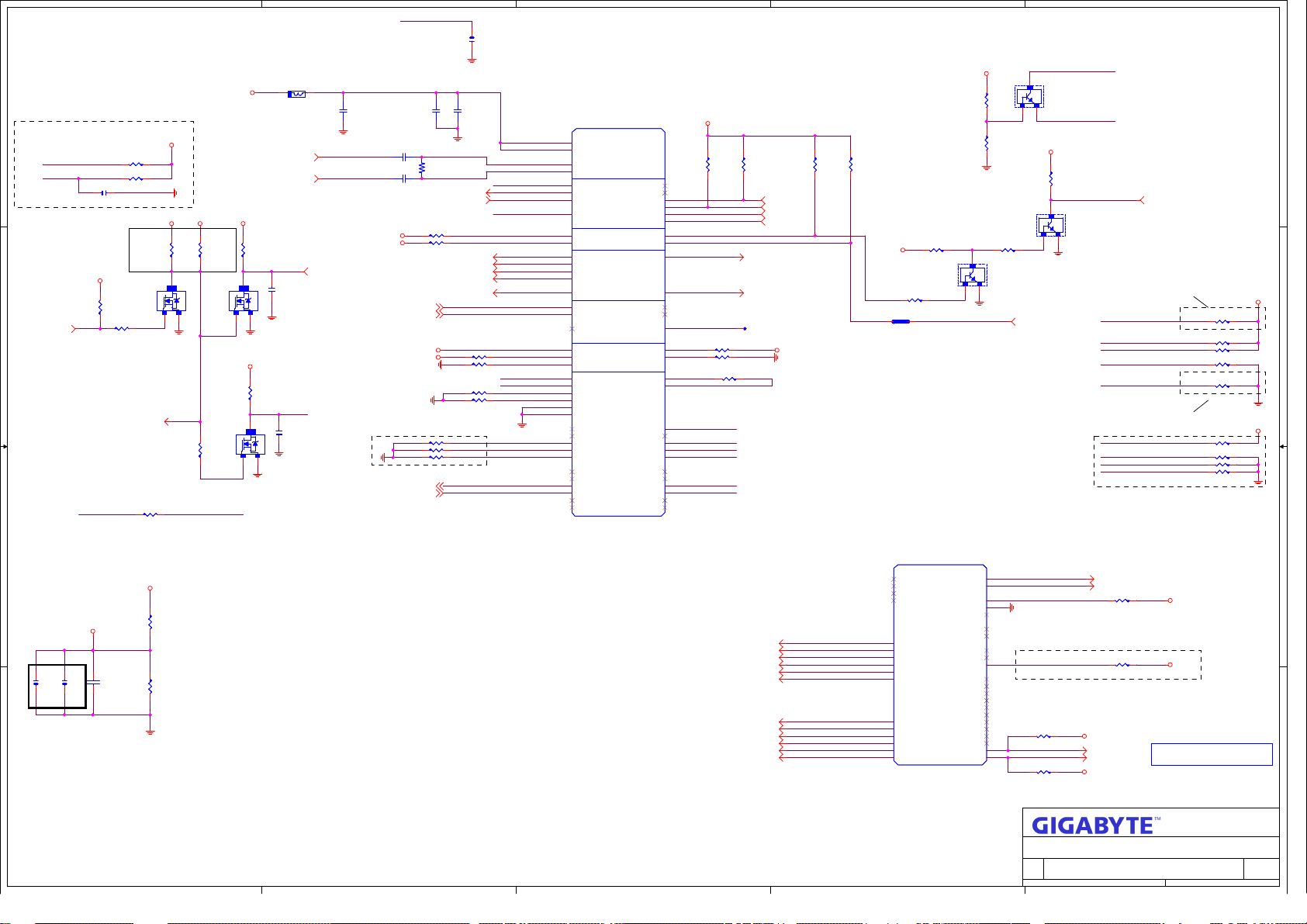

ATI SB850 PCIE/PCI/CPU/LPC

ATI SB850 ACPI/USB/GPIO/AUDIO

ATI SB850 SATA/SPI

ATI SB850 POWER & GND

28

29

30

31

32

33

34

35

36

ATX, F_PANEL. POWER,RESET,CMOS SW, 80 PORT

POWER SECQUENCE, VCC11_DUAL

5V_DUAL, 3V_DUAL, DDR15V, DDRVTT, EUP

VCORE (PWM ISL6324A+6612A x2)

NB/SB POWER, VCC12HT, VDDA25

RTL8111D GBit LAN1

RTL8111D GBIT LAN2

JMB 362 eSATA

JMB 363 2SATA, 1PATA

37 NEC USB 3.0 [UPD720200]

38

TI TSB43AB23 1394A

18

19

20

21

22

23

A A

24

25

PCI EXPRESS x16_1

PCI EXPRESS x16_2, x4

PCI EXPRESS x8_1, SWITCH

PCI EXPRESS x8_2, SWITCH

IT8720 LPC, KB/USB

PCI SLOT, PCI_E x4

FDD, COM, LPT, F_USB

ALC889

5

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

COVER SHEET

COVER SHEET

COVER SHEET

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

1

1 38Thursday, March 25, 2010

1 38Thursday, March 25, 2010

1 38Thursday, March 25, 2010

Page 2

5

Model Name:GA-890FXA-UD7

4

3

2

Circuit or PCB layout change for next version

AM2-->AM3 Different: AE9-->AE7,

H22-->H20. Extra pin:B2 AM3 socket is

938 pins. Only shift 2 pins.

1

Component value change history

D D

2010.01.22

2010.02.26 1.0A DVT BOM Release. PCB:1.0 TPM Remove / Change PCIE SW 10TA1-081440-10R / IO Blinking & RST->0ohm

2010.03.09 2.0A DVT BOM Release. PCB:2.0 Add A Power & EC Function / Change Liner power to OV 20mV/Step

2010.03.25 2.0B PVT BOM Release. PCB:2.01

2010.03.26 2.0B ECN BOM Release. PCB:2.01 Location EU2 add 10HP4-112540-11R 2nd source

2010.03.31 2.0C PVT BOM Release. PCB:2.01 Fix flash BIOS fail Issue PR79,PR80 1K to 330 ohm

2010.04.15 2.0D MP BOM Release. PCB:2.01 Fix OC watchdog issue : R361 300ohm to 8.2K

C C

2010.04.30 Change On/Off Charge IPR9.IPR12 --> 11.3K

VersionDate

0.1 New BOM Release. PCB:0.1

2.0E MP BOM Release. PCB:2.01 Fix SB850 USB fail issue : UR25 374 -> 590ohm2010.04.22

DDR15V offset 1.52V NB offset : 1.145V / Remove SB SATA 25MHz X'TAL

PCIEx16_2 & PCIEx 8_2 GPIO

Change IPR10,IPR11 28K

R63 8.2K

6 Layer, 5mil 60ohm +/- 15% O

Change Items

/ Remove CBC1 realtek Recommend

33K / Q8,Q80 Reset Patch / EU2

R2506 AMD Recommend

33K / PR10 IPR11 --> 33K

P-Code: U98145-0 0.1 Gerber-out

EC FW

-12R

11.3K2.0F MP BOM Release. PCB:2.01

2010.01.22

2010.03.08

2010.03.24

1.0 Gerber out

2.01 Gerber out EC SMBUS change to 0. LED blinking change to GP35.

Modify from GA-790FXTA-UD5 Rev 1.0

R122 change to 0/4, fix RESET bottom can't work issue.

Fix LAN can't work issue. Fix 8X_2/16X_2 switch issue.

Add iPhone charge power circuit, and EC function.2.0 Gerber out

PCIE_16X_1, 8X_1 switch GP20. PCIE_16X_2, 8X_2 switch GP21. Resume well GPIO from IO.

Version: 2.01

ReasonDate Version

Q31 change to TO252

LED Blink change to GP20.

B B

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

BOM & PCB HISTORY

BOM & PCB HISTORY

BOM & PCB HISTORY

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

1

2 38Thursday, April 29, 2010

2 38Thursday, April 29, 2010

2 38Thursday, April 29, 2010

Page 3

5

4

3

2

1

AMD

DDRIII 1333,1600

AM3

D D

Clock Generator

RTM880N-793

+ ICS9DBL411

PCIE SLOT A

16X

PCIE SLOT C

8X

13

HyperTransport

LINK

8X

16X/8X

HyperTransport LINK CPU I/F

2 16X PCIE

6 1X PCIE I/F

18

20

OUT

ATI NB

RD890FX

4,5,6,7

16x16

IN

AM3 SOCKET

1 4X PCIE I/F

PCIE SLOT B

16X/8X

C C

PCIE SLOT D

8X

19

21

1X PCIE INTERFACE

16X/8X

8X

1 4X PCIE I/F WITH SB

128bit

DDRIII 1333,1600

UNBUFFERED

DDR III DIMM1

UNBUFFERED

DDR III DIMM2

DDRIII FIRST LOGICAL DIMM

8,9

DESKTOP AM3

DDR3 MEMORY

POWER

31

UNBUFFERED

DDR III DIMM3

UNBUFFERED

DDR III DIMM4

DDRIII SECOND LOGICAL DIMM

RD890 CORE & PCIE

POWER

SB850 CORE & PCIE

POWER

8,9

8,98,9

32

3230

10,11,12,

PCIE SLOT

4X

19

JM 362 SATA

35

NEC USB3.0

37

GIGABIT LAN

RTL8111D

34

GIGABIT LAN

RTL8111D

33

PCIE SLOT

4X

24

4X

PCIE

ATI SB

SB850

USB2.0

HD AUDIO I/F

SATA II

USB-6 USB-5

USB-7

34

USB-8

B B

34

USB-4

24

USB-9

38

USB-3

24

USB-10 USB-11

38 24 24

USB-2

22

USB-1

22

USB-12

USB-0

38

USB-13

24 24

USB 2.0

38

PCI BUS

AZALIA

ATA 66/100/133

ACPI

LPC I/F

INT RTC

HW MONITOR

14,15,16,17

SATA 3 I/F

1X PCIE INTERFACE

SPI I/F

SPI

Dual-BIOS

ALC889

HD AUDIO CODEC

SATA#0

16

JM 363

2SATA

1PATA

16

25,26

SATA#1

SATA#2

SATA#3

16 16 16 16 16

36

SATA#4 SATA#5

TI TSB43AB23

1394a

PCI SLOT

38

#1

23

ITE LPC SIO IT8720

A A

FLOPPY

5

4

KEYBOARD

LPC BUS

2224

3

HW

MONITOR

SB_SPI_CS ITE_SPI_CS1/2

22

27

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

3 38Monday, May 03, 2010

3 38Monday, May 03, 2010

3 38Monday, May 03, 2010

1

Page 4

5

4

3

2

1

L0_CADIN_L[0..15]

L0_CADIN_H[0..15]

L0_CADOUT_L[0..15]

L0_CADOUT_H[0..15]

D D

L0_CLKIN_H1<10>

L0_CLKIN_L1<10>

L0_CLKIN_H0<10>

L0_CLKIN_L0<10>

L0_CTLIN_L1<10>

L0_CTLIN_H0<10>

L0_CTLIN_L0<10>

C C

L0_CADIN_L[0..15] <10>

L0_CADIN_H[0..15] <10>

L0_CADOUT_L[0..15] <10>

L0_CADOUT_H[0..15] <10>

M2CPUA

M2CPUA

HYPERTRANSPORT

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1 <10>

L0_CLKOUT_L1 <10>

L0_CLKOUT_H0 <10>

L0_CLKOUT_L0 <10>

L0_CTLOUT_H1 <10>L0_CTLIN_H1<10>

L0_CTLOUT_L1 <10>

L0_CTLOUT_H0 <10>

L0_CTLOUT_L0 <10>

CPU_VDD_RUN = VCORE

CPU_VDDA_RUN = VDDA25

VLDT_RUN = VCC12_HT

CPU_VDDIO_SUS = DDR15V

CPU_VDDR = CPU_VDDR12

VLDT_A = VCC12_HT

VLDT_B = HT12B

VCORE

C58 100P/4/NPO/50V/J/XC58 100P/4/NPO/50V/J/X

B B

C59 100P/4/NPO/50V/J/XC59 100P/4/NPO/50V/J/X

C60 100P/4/NPO/50V/J/XC60 100P/4/NPO/50V/J/X

HT_BUS Vcore use

1

1

K3

K1_ICT/XK3K1_ICT/X

K6

K1_ICT/XK6K1_ICT/X

M2CPU

M2CPU

AM2RM/PP/OR/PB/[12KRC-04K812-12R_12KRC-04K812-13R]

AM2RM/PP/OR/PB/[12KRC-04K812-12R_12KRC-04K812-13R]

3

2

K2

K1_ICT/XK2K1_ICT/X

1

K5

K1_ICT/XK5K1_ICT/X

1

4

1

1

K1

K1_ICT/XK1K1_ICT/X

K4

K1_ICT/XK4K1_ICT/X

COUPON1

COUPON2

A A

COUPON3

COUPON4

COUPON1 COUPON/XCOUPON1 COUPON/X

COUPON3 COUPON/XCOUPON3 COUPON/X

COUPON2 COUPON/XCOUPON2 COUPON/X

COUPON4 COUPON/XCOUPON4 COUPON/X

5

21

21

21

21

VCC

VCC

MH3

MH3

2

3

6

8

12

7

9

10

11

MH1

MH1

2

3

6

8

12

7

9

10

11

MH7

MH7

2

3

6

8

12

7

9

10

11

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

S

Date: Sheet of

Date: Sheet of

Date: Sheet of

MH9

MH9

2

3

4

5

1

HOLE_3/X

HOLE_3/X

4

5

1

HOLE_3/X

HOLE_3/X

4

5

1

HOLE_3/X

HOLE_3/X

ize Document Number Rev

Custom

Custom

Custom

6

8

4

5

12

7

1

HOLE_3/X

HOLE_3/X

9

10

11

MH2

MH2

2

3

6

8

4

5

12

7

1

HOLE_3/X

HOLE_3/X

9

10

11

MH5

MH5

2

3

6

8

4

5

12

7

1

HOLE_3/X

HOLE_3/X

9

10

11

COVER SHEET

COVER SHEET

COVER SHEET

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

1

MH8

MH8

MH4

MH4

MH6

MH6

2

3

6

8

4

5

12

7

1

HOLE_3/X

HOLE_3/X

9

10

11

2

3

6

8

4

5

12

7

1

HOLE_3/X

HOLE_3/X

9

10

11

2

3

6

8

4

5

12

7

1

HOLE_3/X

HOLE_3/X

9

10

11

4 38Thursday, March 25, 2010

4 38Thursday, March 25, 2010

4 38Thursday, March 25, 2010

Page 5

5

M2CPUB

M2CPUB

MEMORY INTERFACE A

AG21

AG20

G19

H19

DCLKA3

A11P

DCLKA3<8>

A11N

-DCLKA3<8>

-CSA1<8>

D D

A00P

A00N

MAAA[0..15]<8>

C C

-DQSA[0..8]

DQSA[0..8]

MA_CK[0..8]

DMA[0:8]

B B

-DQSA[0..8] <8>

DQSA[0..8] <8>

DMA[0..8] <8>

-CSA0<8>

MODT_A0<8>

DCLKA0<8>

-DCLKA0<8>

-CSA3<8>

-CSA2<8>

MODT_A2<8>

-SCASA<8>

-SWEA<8>

-SRASA<8>

SBAA2<8> SBAB1<9>

SBAA1<8>

SBAA0<8>

CKEA0<8>

MAAA15

MAAA14

MAAA13

MAAA12

MAAA11

MAAA10

MAAA9

MAAA8

MAAA7

MAAA6

MAAA5

MAAA4

MAAA3

MAAA2

MAAA1

MAAA0

U27

-DCLKA3

U26

-CSA1 -CSB0

AC25

-CSA0

AA24

MODT_A0

AC28

AE20

AE19

G20

G21

DCLKA0

V27

-DCLKA0

W27

AD27

AA25

MODT_A2

AC27

-SCASA

AB25

-SWEA

AB27

-SRASA

AA26

SBAA2

N25

SBAA1

Y27

SBAA0

AA27

CKEA1

L27

CKEA0

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

DQSA7

AD15

-DQSA7

AE15

DQSA6

AG18

-DQSA6

AG19

DQSA5

AG24

-DQSA5

AG25

DQSA4

AG27

-DQSA4

AG28

DQSA3

D29

-DQSA3

C29

DQSA2

C25

-DQSA2

D25

DQSA1

E19

-DQSA1

F19

DQSA0

F15

-DQSA0

G15

DMA7

AF15

DMA6

AF19

DMA5

AJ25

DMA4

AH29

DMA3

B29

DMA2

E24

DMA1

E18

DMA0

H15

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

4

MDA63

MA_DM(8)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MDA62

MDA61

MDA60

MDA59

MDA58

MDA57

MDA56

MDA55

MDA54

MDA53

MDA52

MDA51

MDA50

MDA49

MDA48

MDA47

MDA46

MDA45

MDA44

MDA43

MDA42

MDA41

MDA40

MDA39

MDA38

MDA37

MDA36

MDA35

MDA34

MDA33

MDA32

MDA31

MDA30

MDA29

MDA28

MDA27

MDA26

MDA25

MDA24

MDA23

MDA22

MDA21

MDA20

MDA19

MDA18

MDA17

MDA16

MDA15

MDA14

MDA13

MDA12

MDA11

MDA10

MDA9

MDA8

MDA7

MDA6

MDA5

MDA4

MDA3

MDA2

MDA1

MDA0

DQSA8

-DQSA8

DMA8

MA_CK7

MA_CK6

MA_CK5

MA_CK4

MA_CK3

MA_CK2

MA_CK1

MA_CK0

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

MDA[0..63] <8>

3

B11P

DCLKB3<9>

B11N

-DCLKB3<9>

-CSB1<9>

-CSB0<9>

MODT_B0<9>

DCLKB0<9>

B00P

-DCLKB0<9>

B00N

MAAB[0..15]<9>

-DQSB[0..8]

DQSB[0..8]

MB_CK[0..8]

DMB[0..8]

MODT_B2<9>

-SCASB<9>

-SRASB<9>

-DQSB[0..8] <9>

DQSB[0..8] <9>

MB_CK[0..8] <9>

DMB[0..8] <9>MA_CK[0..8] <8>

-CSB3<9>

-CSB2<9>

-SWEB<9>

SBAB2<9>

SBAB0<9>

CKEB1<9>

CKEB0<9>CKEA1<8>

MAAB15

MAAB14

MAAB13

MAAB12

MAAB11

MAAB10

MAAB9

MAAB8

MAAB7

MAAB6

MAAB5

MAAB4

MAAB3

MAAB2

MAAB1

MAAB0

DCLKB3

-DCLKB3

-CSB1

MODT_B0

DCLKB0

-DCLKB0

MODT_B2

-SCASB

-SWEB

-SRASB

SBAB2

SBAB1

SBAB0

CKEB1

CKEB0

DQSB7

-DQSB7

DQSB6

-DQSB6

DQSB5

-DQSB5

DQSB4

-DQSB4

DQSB3

-DQSB3

DQSB2

-DQSB2

DQSB1

-DQSB1

DQSB0

-DQSB0

DMB7

DMB6

DMB5

DMB4

DMB3

DMB2

DMB1

DMB0

AJ19

AK19

AE30

AC31

AD29

AL19

AL18

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

M31

M29

N28

N29

N30

R29

R28

R31

R30

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A18

A19

U31

U30

C19

D19

N31

P29

P31

T31

T29

A23

B17

B13

2

M2CPUC

M2CPUC

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MEMORY INTERFACE B

MEMORY INTERFACE B

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

MB_DM(8)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MDB63

MDB62

MDB61

MDB60

MDB59

MDB58

MDB57

MDB56

MDB55

MDB54

MDB53

MDB52

MDB51

MDB50

MDB49

MDB48

MDB47

MDB46

MDB45

MDB44

MDB43

MDB42

MDB41

MDB40

MDB39

MDB38

MDB37

MDB36

MDB35

MDB34

MDB33

MDB32

MDB31

MDB30

MDB29

MDB28

MDB27

MDB26

MDB25

MDB24

MDB23

MDB22

MDB21

MDB20

MDB19

MDB18

MDB17

MDB16

MDB15

MDB14

MDB13

MDB12

MDB11

MDB10

MDB9

MDB8

MDB7

MDB6

MDB5

MDB4

MDB3

MDB2

MDB1

MDB0

DQSB8

-DQSB8

DMB8

MB_CK7

MB_CK6

MB_CK5

MB_CK4

MB_CK3

MB_CK2

MB_CK1

MB_CK0

1

MDB[0..63] <9>

MEM CHA

A A

TO DIMMA0 & DIMMA1

CPU

TO DIMMB0 & DIMMB1

A0 A1

5

4

3

CPU

MEM CHB

B0 B1

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

COVER SHEET

COVER SHEET

COVER SHEET

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

1

5 38Thursday, March 25, 2010

5 38Thursday, March 25, 2010

5 38Thursday, March 25, 2010

Page 6

5

2.5V/0.5A

FB1 0/6FB1 0/6

VDDA25

30/6/4A/S

D D

SB600

CPU_PWR / DDR18V

-CPURST

-LDT_STOP

CPU_PG_SB<14>

C C

R26 300/4R26 300/4

R36 300/4R36 300/4

C61 150P/4/NPO/50V/JC61 150P/4/NPO/50V/J

R63 --> R2506

AMD Recommend

DDR15V

R2756

R2756

300/4

300/4

R1 1K/4/1R1 1K/4/1

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

CPU_PG_SB

DDR15V

3VDUAL VCC3

R2506

R2506

8.2K/4

8.2K/4

3

Q309

Q309

D

D

G S

G S

2

-CPU_PG<27>

R6 0/4/XR6 0/4/X

CPUCLK0_H<13>

CPUCLK0_L<13>

VCC3

R2507

R2507

R63

R63

8.2K/4/1

8.2K/4/1

8.2K/4/1/X

8.2K/4/1/X

3

Q310

Q310

D

D

G S

2N7002/SOT23/25pF/5

2N7002/SOT23/25pF/5

Q355

Q355

2N7002/SOT23/25pF/5

2N7002/SOT23/25pF/5

CPU_PWRGD

G S

2

DDR15V

G S

G S

2

1

3

D

D

R2754

R2754

300/4

300/4

CPU_PWRGD

1

1

R84

R84

1K/4/1

1K/4/1 R2727 300/4R2727 300/4

CPUCLK0_H CLKIN_H

PWM_PWRGD <31>

C1752

C1752

0.1u/4/Y5V/16V/Z/X

0.1u/4/Y5V/16V/Z/X

AMD comment for validation.

C1790

C1790

0.1u/4/Y5V/16V/Z/X

0.1u/4/Y5V/16V/Z/X

4

-CPURST

C1798

C1798

100P/4/NPO/50V/J

100P/4/NPO/50V/J

C3

C3

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

3.9n/4/X7R/50V/K

3.9n/4/X7R/50V/K

C1

C1

C2

C2

3.9n/4/X7R/50V/K

3.9n/4/X7R/50V/K

3.3n/4/X7R/50V/K

3.3n/4/X7R/50V/K

C13

C13

R5

169/4/1R5169/4/1

C4

C4

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

CLKIN_LCPUCLK0_L

-LDT_STOP<11,14>

-CPURST<11,14,15>

DG:AM3 1.04

R17 1K/4/1R17 1K/4/1

DDR15V

R19 1K/4/1R19 1K/4/1

DDR15V

CPU_TRST-<15>

CPU_TCK<15>

CPU_TMS<15>

CPU_DBREQ-<15> CPU_DBRDY <15>

COREFB+<31>

COREFB-<31,32>

VTT_SENSE AM3 only, may not use, like AM2

CPU_M_VREF

R2725 300/4R2725 300/4

R2726 300/4R2726 300/4

DDR15V

GNDA<22>

TMPIN2<22,27>

R11 39.2/4/1R11 39.2/4/1

R12 39.2/4/1R12 39.2/4/1

R13 300/4R13 300/4

R14 300/4R14 300/4

3

M2CPUD

M2CPUD

MISC

C10

D10

A8

CPU_PWRGD

-LDT_STOP

-CPURST

CPU_PRESENT_L

*

CPU_TDI CPU_TDO

*

CPU_TRSTCPU_TCK

CPU_TMS

CPU_DBREQ-

CPU_TEST25_H

CPU_TEST25_L

B8

C9

D8

C7

AL3

SIC

AL6

SID

AK6

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

CPU-SK/941AM3/S/GF/[10SC1-A01941-04R_10SC1-A01941-05R]

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

THERMTRIP_L

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

DDR15V

R57

VCC12_HT

R57

300/4

300/4

R2557

R2557

R2555

R2555

1K/4/1

1K/4/1

1K/4/1

1K/4/1

D2

D1

VID3

C1

VID2

E3

VID1

E2

VID0

E1

THERMTRIP_L

AK7

-PROCHOT

AL7

AK10

CPU_DBRDY

B6

AK11

AL11

CPU_PSI-

F1

R53 44.2/4/1R53 44.2/4/1

V8

R54 44.2/4/1R54 44.2/4/1

V7

R55 80.6/4/1R55 80.6/4/1

C11

D11

Route as 80-Ohm differential impedance

Keep trace to resistor less than 1" from CPU pin

CPU_TEST24

AK8

AH8

CPU_TEST22

AJ9

CPU_TEST21

AL8

CPU_TEST20

AJ8

J10

H9

CPU_TEST27

AK9

CPU_TEST26

AK5

G7

D4

VID3 <31>

VID2 <31>

VID1 <31>

VID0 <31>

CPU_TDO <15>CPU_TDI<15>

TP1TP1

LAYOUT: Route trace 50 mils wide and

500 to 750 mils long between these caps.

2

R60

R60

300/4

300/4

R176 1K/4/1R176 1K/4/1

DDR15V

R174 1K/4/1R174 1K/4/1

R190 0/4/SHT/XR190 0/4/SHT/X

3VDUAL

R64

R64

1K/4/1/X

1K/4/1/X

R80

R80

1K/4/1/X

1K/4/1/X

Q10

Q10

-PROCHOT_CPU

Q11

Q11

132

3VDUAL

Q9

Q9

R175 1K/4/1R175 1K/4/1

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

SOT23

SOT23

132

-PROCHOT_CPU <14>

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

THERMTRIP_CPU_L

MMBT2222A/SOT23/600mA/40/X

MMBT2222A/SOT23/600mA/40/X

SOT23

SOT23

THERMTRIP_L

R59

R59

8.2K/4/1

8.2K/4/1

THERMTRIP_CPU_L

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

SOT23

SOT23

132

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

CPU_TEST26

*

CPU_PRESENT_L

CPU_TEST25_H

*

CPU_TEST25_L

CPU_TEST21

CPU_TEST27

CPU_TEST20

CPU_TEST22

CPU_TEST24

1

THERMTRIP_CPU_L <15,30>

R37 300/4/XR37 300/4/X

R49 10K/4/1R49 10K/4/1

R42 510/4/1R42 510/4/1

R43 510/4/1R43 510/4/1

R47 300/4R47 300/4

R2728 300/4R2728 300/4

R2729 300/4R2729 300/4

R2730 300/4R2730 300/4

R2731 300/4R2731 300/4

DDR15V

DDR15V

B B

SC35

SC35

1U/6/X7R/16V/K

1U/6/X7R/16V/K

5

DDR15V

SR19

SR19

15/4/1

15/4/1

SR20

SR20

15/4/1

15/4/1

AM3 only

A10P

A10N

A01P

A01N

DCLKA2<8>

-DCLKA2<8>

MODT_A3<8>

DCLKA1<8>

-DCLKA1<8>

MODT_A1<8>

DCLKA2

-DCLKA2

MODT_A3

DCLKA1

-DCLKA1

MODT_A1

AM3 only

B10P

B10N

B01P

B01N

4

3

DCLKB2<9>

-DCLKB2<9>

MODT_B3<9>

DCLKB1<9>

-DCLKB1<9>

MODT_B1<9>

DCLKB2

-DCLKB2

MODT_B3

DCLKB1

-DCLKB1

MODT_B1

CPUVREF

40 MILS WIDTH

CPU_M_VREF

SBC12

SBC12

1N/4/X7R/50V/K

1N/4/X7R/50V/K

Layout: Place within

500mils of the CPU socket.

A A

12

SBC31

SBC31

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

W26

W25

AE27

AE28

AG31

W31

AF31

L25

L26

L31

L30

U24

V24

Y31

Y30

V31

M2CPUE

M2CPUE

RSVD1

RSVD2

RSVD3

RSVD4

DCLKA2

DCLKA2MODT_A3

DCLKA1

DCLKA1MODT_A1

DCLKB2

DCLKB2MODT_B3

DCLKB1

DCLKB1MODT_B1

2

INTERNAL MISC

INTERNAL MISC

MA_RESETMB_RESET-

RSVD21

RSVD22

M_VDDIO_PWRGD

COREFB_NB+

COREFB_NB-

CORE_TYP_DET

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

MB_EVENT_L

MA_EVENT_L

AM3 only

MA_RESET_L

E20

MB_RESET_L

B19

CPU_ALERT-

AL4

ALERT-

AK4

SA0

AK3

F2

F3

M_VDDIO_PWRGD AM3 Not support PID:40778

G4

G3

CORE_TYPE_DET

G5

AM2: high, AM2R2: low

AD25

AE24

AE25

AJ18

AJ20

C18

C20

AM3 =>DRAM Thermal Event Status

G24

R103 1K/4/1R103 1K/4/1

G25

H25

MB_EVENT_L

V29

MA_EVENT_L

W30

R102 1K/4/1R102 1K/4/1

EVENT pins are for future AM3r2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

MA_RESET_L <8>

MB_RESET_L <9>

R8 1K/4/1R8 1K/4/1

R2448 1K/4/1R2448 1K/4/1

DDR15V

MB_EVENT_L <9>

MA_EVENT_L <8>

DDR15V

COVER SHEET

COVER SHEET

COVER SHEET

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

DDR15V

DDR15V

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

6 38Wednesday, April 14, 2010

6 38Wednesday, April 14, 2010

1

6 38Wednesday, April 14, 2010

Page 7

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCORE_NB

VCORE

VCC12_HT

AA10

AA12

AA14

AA16

AA18

AB11

AC10

AE10

AA8

AB7

AB9

AC4

AC5

AC8

AD2

AD3

AD7

AD9

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

G10

G12

H11

H23

K11

K13

K15

K17

K19

K21

K23

Y17

Y19

VLDT_RUN_B is connected to the VLDT_RUN power

VCORE_NB

supply through the package or on the die. It is only connected

M2CPUF

M2CPUF

VDD1

VDD1

A4

VDD1

A6

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

VDD49

VDD50

H7

VDD51

VDD52

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

VDD150

VDD151

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE11

AE9 Missing pins on package

AF2

AF3

and socket used for

AF8

mechanical keying. =>AM3

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

GND

VCORE

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

R10

R12

R14

R16

R18

R20

U10

U12

U14

U16

U18

U20

W10

W12

W14

W16

W18

W20

VCORE

M2CPUH

M2CPUG

M2CPUG

VDD2

VDD2

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

N8

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22 Missing pins on package

H24

H26

and socket used for

H28

mechanical keying. =>AM3

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

GND

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

L20

L22

M21

M23

N20

N22

P21

P23

R22

T23

U22

V23

W22

Y23

AM3 Only

H20

AE7

GND

B2

M2CPUH

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

NB/RSVD

NP/VSS1

NP/VSS2

VCC12_HT

VDD3

VDD3

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

on the board to decoupling near the CPU package.

M2CPUI

M2CPUI

VDDIO

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

GND

VCC12_HT

VCC12_HT

CPU_VDDR12

VCC12_HT

DDR15V

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

VCORE

SC16

SC16

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

VCORE

SC24

SC24

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

VDDIO

AJ4

VLDT_A1

AJ3

VLDT_A2

AJ2

VLDT_A3

AJ1

VLDT_A4

D12

VDDR_4

C12

VDDR_3

B12

VDDR_2

A12

VDDR_1

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO29

VDDIO9

VDDIO10

VDDIO11

VDDIO12

P24

VDDIO13

P26

VDDIO14

P28

VDDIO15

P30

VDDIO16

T24

VDDIO17

T26

VDDIO18

T28

VDDIO19

T30

VDDIO20

V25

VDDIO21

V26

VDDIO22

V28

VDDIO23

V30

VDDIO24

Y24

VDDIO25

Y26

VDDIO26

Y28

VDDIO27

Y29

VDDIO28

BUTTOM SIDE

SC17

SC17

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

GND

SC25

SC25

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

GND

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDR_9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC18

SC18

SC26

SC26

H6

H5

H2

H1

AG12

AH12

AJ12

AK12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

GND

VCC12_HT

CPU_VDDR12

SC19

SC19

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC27

SC27

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

HT12B

BC795

BC795

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

GND

VCORE

SC20

SC20

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC28

SC28

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

DDR15V

DDR15V

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC11

SC11

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

SC21

SC21

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC29

SC29

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

1021 EMI

VCC12_HT

C1343

C1343

C1344

C1344

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

1U/6/X7R/16V/K

1U/6/X7R/16V/K

GND

SC2

SC2

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

GND

SC10

SC10

SC9

SC9

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

GND

BUTTOM SIDE

SC12

SC12

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

GND

SC22

SC22

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

SC30

SC30

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

C1342

C1342

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

BUTTOM SIDE

SC4

SC4

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

SC7

SC7

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

SC13

SC13

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

SC23

SC23

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

C1345

C1345

0.01u/4/X7R/25V/K

0.01u/4/X7R/25V/K

SC5

SC5

0.01U/4/X7R/25V/K

0.01U/4/X7R/25V/K

SC8

SC8

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

SC14

SC14

0.01U/4/X7R/25V/K

0.01U/4/X7R/25V/K

C1346

C1346

180P/4/NPO/50V/J

180P/4/NPO/50V/J

SC6

SC6

180P/4/NPO/50V/J

180P/4/NPO/50V/J

SC31

SC31

180P/4/NPO/50V/J

180P/4/NPO/50V/J

SC15

SC15

180P/4/NPO/50V/J

180P/4/NPO/50V/J

C1328

C1328

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

GND

DDR15V

C1324

C1324

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

GND

C1329

C1329

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

C1325

C1325

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

C1330

C1330

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

C1337

C1337

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

C1331

C1331

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

C1319

C1319

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

C1332

C1332

180P/4/NPO/50V/J

180P/4/NPO/50V/J

C1333

C1333

180P/4/NPO/50V/J

180P/4/NPO/50V/J

C1316

C1316

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

VCC12_HT

C1334

C1334

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

C1317

C1317

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

GND

C1335

C1335

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

GND

C1318

C1318

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

C1336

C1336

0.22U/6/X7R/16V/K

0.22U/6/X7R/16V/K

C1320

C1320

1N/4/X7R/50V/K

1N/4/X7R/50V/K

C1338

C1338

1N/4/X7R/50V/K

1N/4/X7R/50V/K

C1321

C1321

1N/4/X7R/50V/K

1N/4/X7R/50V/K

C1339

C1339

1N/4/X7R/50V/K

1N/4/X7R/50V/K

C1322

C1322

180P/4/NPO/50V/J

180P/4/NPO/50V/J

C1340

C1340

180P/4/NPO/50V/J

180P/4/NPO/50V/J

C1323

C1323

180P/4/NPO/50V/J

180P/4/NPO/50V/J

C1341

C1341

180P/4/NPO/50V/J

180P/4/NPO/50V/J

BC24

BC20

BC20

100P/4/NPO/50V/J

100P/4/NPO/50V/J

Title

Title

Title

CPU POWER & GND

CPU POWER & GND

CPU POWER & GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

BC23

BC23

100P/4/NPO/50V/J

100P/4/NPO/50V/J

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

BC24

100P/4/NPO/50V/J/X

100P/4/NPO/50V/J/X

BC25

BC25

100P/4/NPO/50V/J/X

100P/4/NPO/50V/J/X

7 38Thursday, March 25, 2010

7 38Thursday, March 25, 2010

7 38Thursday, March 25, 2010

Page 8

8

D D

C C

C275 0.1U/4/X7R/16V/KC275 0.1U/4/X7R/16V/K

VCC3

C277 0.1U/4/X7R/16V/KC277 0.1U/4/X7R/16V/K C278 0.1U/4/X7R/16V/KC278 0.1U/4/X7R/16V/K

B B

A A

SMBDATA<9,13,15,30,31>

MA_RESET_L<6>

DDRVTT

DDR15V DDR15V

VREFDQ_A

SMBCLK

SMBCLK<9,13,15,30,31>

SMBDATA

SBAA2

SBAA2<5>

SBAA1

SBAA1<5>

SBAA0

SBAA0<5>

CKEA1

CKEA1<5>

CKEA0

CKEA0<5>

-CSA1<5>

-CSA0

-CSA0<5>

-DCLKA1<6>

DCLKA1

-DCLKA0

-DCLKA0<5>

DCLKA0 DCLKA2

DCLKA0<5>

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15 MAAA15

MA_RESET_L

-SCASA

-SCASA<5>

-SRASA

-SRASA<5>

-SWEA

-SWEA<5>

7

DDR3_1

DDR3_1

120

VTT

240

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

6

FREE

FREE

FREE

FREE

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DQS0

DQS0*

DQS1

DQS1*

DQS2

DQS2*

DQS3

DQS3*

DQS4

DQS4*

DQS5

DQS5*

DQS6

DQS6*

DQS7

DQS7*

DQS8

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DDR3/240/BU/VA/D

DDR3/240/BU/VA/D

5

48

49

MA_EVENT_L MA_EVENT_L

187

198

79

77

195

68

53

167

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

MA_EVENT_L <6> MA_EVENT_L <6>

MODT_A1

MODT_A0

MA_CK0

MA_CK1

MA_CK2

MA_CK3

MA_CK4

MA_CK5

MA_CK6

MA_CK7

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DQSA8

-DQSA8

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MODT_A1 <6>

MDA[0..63] <5>

DDR15V Decouple

DDR15V

DDRVTT Decouple

DDRVTT

BC118

BC118

4.7U/8/X5R/6.3V/K

4.7U/8/X5R/6.3V/K

DDRVTT

MODT_A[0..3]

-DQSA[0..8]

DQSA[0..8]

DMA[0..8]

MA_CK[0..7]

SMBDATA

SMBCLK

C205

C205

100p/4/NPO/50V/J/X

100p/4/NPO/50V/J/X

DDR15V

R101

R101

15/4/1

15/4/1

R23

R23

15/4/1

15/4/1

DDR15V

R24

R24

15/4/1

15/4/1

R2

15/4/1R215/4/1

BC2

BC2

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

BC3

BC3

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

BC6

BC6

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

BC152

BC152

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

BC7

BC7

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

BC8

BC8

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

BC9

BC9

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

MODT_A[0..3] <5,6>

-DQSA[0..8] <5>

DQSA[0..8] <5>

DMA[0..8] <5>

MA_CK[0..7] <5>

C206

C206

100p/4/NPO/50V/J/X

100p/4/NPO/50V/J/X

Trace min 10/10

VREFDQ_A

Trace min 10/10

VREFCA_A

VCC3

C280 0.1U/4/X7R/16V/KC280 0.1U/4/X7R/16V/KC279 1U/4/X5R/6.3V/KC279 1U/4/X5R/6.3V/K

4

VREFDQ_A

VREFCA_A

C276 0.1U/4/X7R/16V/KC276 0.1U/4/X7R/16V/K

SMBCLK<9,13,15,30,31>

SMBDATA<9,13,15,30,31>

SBAA2<5>

SBAA1<5>

SBAA0<5>

CKEA1<5>

CKEA0<5>

-CSA3<5>

-CSA2<5>

-DCLKA3<5>

DCLKA3<5>DCLKA1<6>

-DCLKA2<6>

DCLKA2<6>

MAAA[0..15]<5>MAAA[0..15]<5>

MA_RESET_L<6>

-SCASA<5>

-SRASA<5>

-SWEA<5>

VCC3

DDRVTT

VREFCA_AVREFCA_A

VREFDQ_A

SMBCLK

SMBDATA

SBAA2

SBAA1

SBAA0

CKEA1

CKEA0

-CSA3

-CSA2

-DCLKA3-DCLKA1

DCLKA3

-DCLKA2

MAAA0

MAAA1

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MA_RESET_L

-SCASA

-SRASA

-SWEA

3

DDR3_3

DDR3_3

120

VTT

240

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

2

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DDR3/240/WH/VA/D

DDR3/240/WH/VA/D

FREE

FREE

FREE

FREE

RSVD

ODT1

ODT0

DQS0

DQS0*

DQS1

DQS1*

DQS2

DQS2*

DQS3

DQS3*

DQS4

DQS4*

DQS5

DQS5*

DQS6

DQS6*

DQS7

DQS7*

DQS8

DQS8*

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

1

48

49

187

198

79

MODT_A3

77

195

68

53

167

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

MODT_A2

MA_CK0

MA_CK1

MA_CK2

MA_CK3

MA_CK4

MA_CK5

MA_CK6

MA_CK7

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DQSA8

-DQSA8

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8DMA8

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40MAAA2

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MODT_A3 <6>

MODT_A2 <5>MODT_A0 <5>

MDA[0..63] <5>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

8

7

6

5

4

3

Date: Sheet of

2

DDR III CHANNEL A

DDR III CHANNEL A

DDR III CHANNEL A

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

GA-890FXA-UD7 2.01

8 38Thursday, March 25, 2010

8 38Thursday, March 25, 2010

8 38Thursday, March 25, 2010

1

Page 9

8

DDRVTT

D D

C C

DDR15V

VCC3

C283 0.1U/4/X7R/16V/KC283 0.1U/4/X7R/16V/K

C285 0.1U/4/X7R/16V/KC285 0.1U/4/X7R/16V/K

SMBCLK<8,13,15,30,31>

DDR15V

MAAB[0..15]<5>

MB_RESET_L<6>

BC11

BC11

22U/8/X5R/6.3V/M

22U/8/X5R/6.3V/M

8

SMBDATA<8,13,15,30,31>

VCC3

SBAB2<5>

SBAB1<5>

SBAB0<5>

CKEB1<5>

CKEB0<5>

-CSB1<5>

-CSB0<5>

-DCLKB1<6>

DCLKB1<6>

-DCLKB0<5>

DCLKB0<5>

-SCASB<5>

-SRASB<5>

-SWEB<5>

B B

A A

120

240

101

104

107

110

113

116

119

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

217

220

223

226

229

232

235

239

170

173

176

179

182

183

186

189

191

194

197

236

VREFCA_A

VREFDQ_A

SMBCLK

118

SMBDATA

238

237

117

SBAB2

SBAB1

190

SBAB0

CKEB1

169

CKEB0

-CSB1

-CSB0

193

-DCLKB1

DCLKB1

-DCLKB0

185

DCLKB0

184

MAAB0

188

MAAB1

181

MAAB2

MAAB3

180

MAAB5

MAAB6

178

MAAB7

MAAB8

177

MAAB9

175

MAAB10

MAAB11

MAAB12

174

MAAB13

196

MAAB14

172

MAAB15

171

MB_RESET_L MDB54

168

-SCASB

-SRASB

192

-SWEB

BC10

BC10

22U/8/X5R/6.3V/M

22U/8/X5R/6.3V/M

7

DDR3_2

DDR3_2

VTT

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDSPD

67

VREFCA

1

VREFDQ

SCL

SDA

SA1

SA0

52

BA2

BA1

71

BA0

CKE1

50

CKE0

76

S1*

S0*

64

CK1/NU*

63

CK1/NU

CK0*

CK0

A0

A1

61

A2

A3

59

A4

58

A5

A6

56

A7

A8

A9

70

A10/AP

55

A11

A12

A13

A14

A15

RESET*

74

CAS*

RAS*

73

WE*

7

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

DQS0*

DQS1*

DQS2*

DQS3*

DQS4*

DQS5*

DQS6*

DQS7*

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DDR3/240/BU/VA/D

DDR3/240/BU/VA/D

6

48

FREE

49

FREE

MB_EVENT_L

187

FREE

198

FREE

79

RSVD

MODT_B1

77

ODT1

MODT_B0

195

ODT0

68

53

167

MB_CK0

39

CB0

MB_CK1

40

CB1

MB_CK2

45

CB2

MB_CK3

46

CB3

MB_CK4

158

CB4

MB_CK5

159

CB5

MB_CK6

164

CB6

MB_CK7

165

CB7

DQSB0

7

DQS0

-DQSB0

6