Page 1

第 1 頁,共 1 頁Technical Information Release Notice

Technical Information Release Notice

Doc Type Schematic Date 2005/11/10 下午 10:12:43

Project Code S94034-0 Customer

Project Name GA-7A8DRL Revision Old N/A New 2.0

Model Name GA-7A8DRL IT Doc No DR05B057

P/N RD Doc No

PCB Rev. 2.0 Check Sum

GA-7A8DRL 2.0A

FINISHED GOOD

P/N Description

Description release GA-7A8DRL MB sch.

Remark

Approved By billy1.chen 2005/11/11 下午 04:40:12 Applicant Ryan.Chen

Research

Management

yuling.cheng

2005/11/11 下午

05:26:05

R

R

T

T

I

I

Effected Class

Validation Manager Project Manager

e

e

g

g

a

a

n

n

a

e

e

s

s

e

e

a

a

r

r

c

c

2

2

h

h

0

0

0

0

M

M

5

5

a

/

/

1

1

1

1

/

/

1

1

1

1

R N M

gfedc gfedcb gfedc

A B C D E F

gfedcb

gfedc

A B

gfedc gfedcb

t

t

n

n

e

e

m

m

gfedc gfedc

gfedc gfedc

2005/11/11http://gwfap/ef2kweb/CHT/Forms/RTC009/RTC009_P.asp

yuling.cheng

Page 2

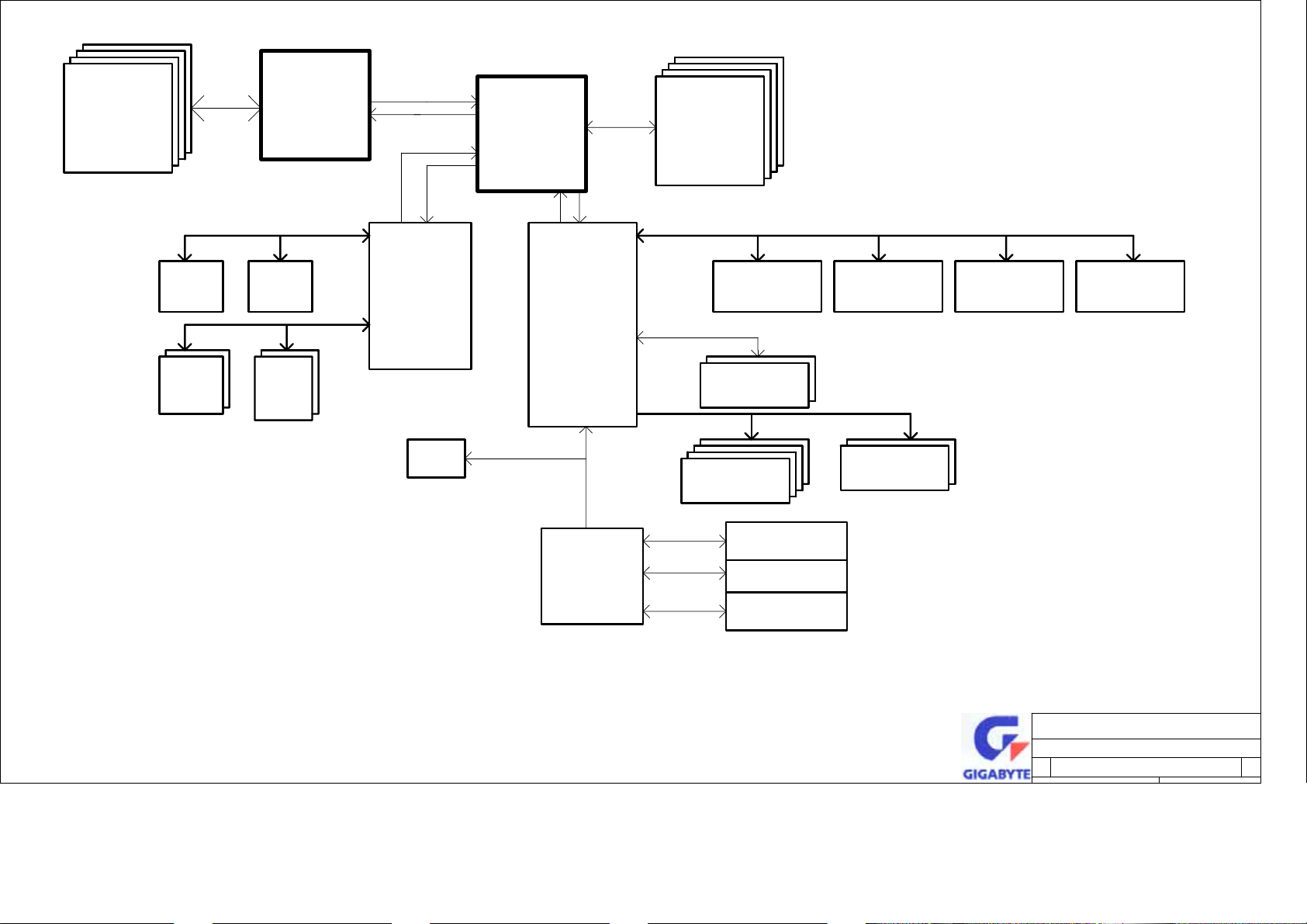

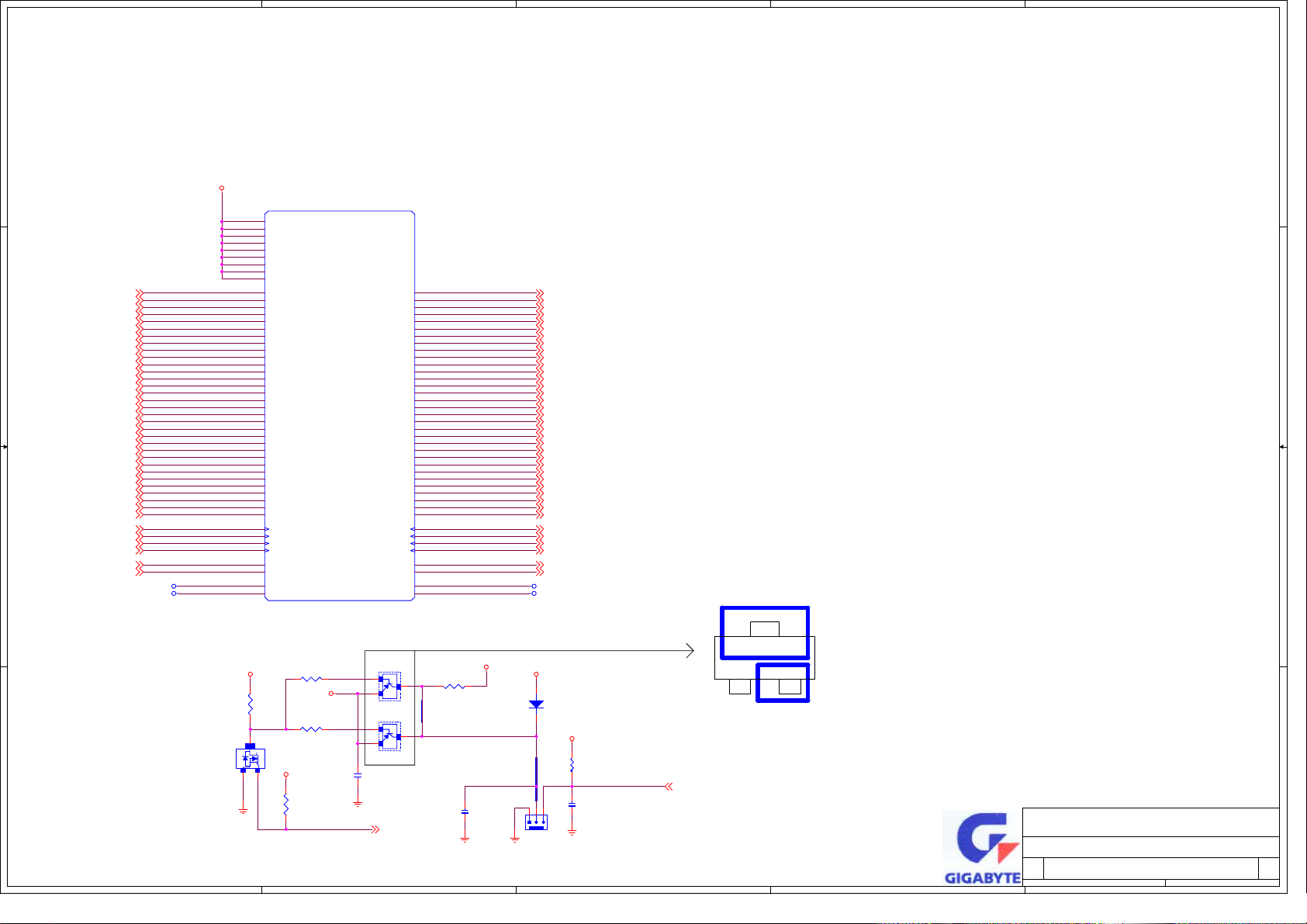

GIGABYTE GA-7A8DRL REFERENCE SCHEMATIC

REVISION:2.0

SHEET 1 COVER SHEET

SHEET 2 BLOCK DIAGRAM

SHEET 3 Power Consumption

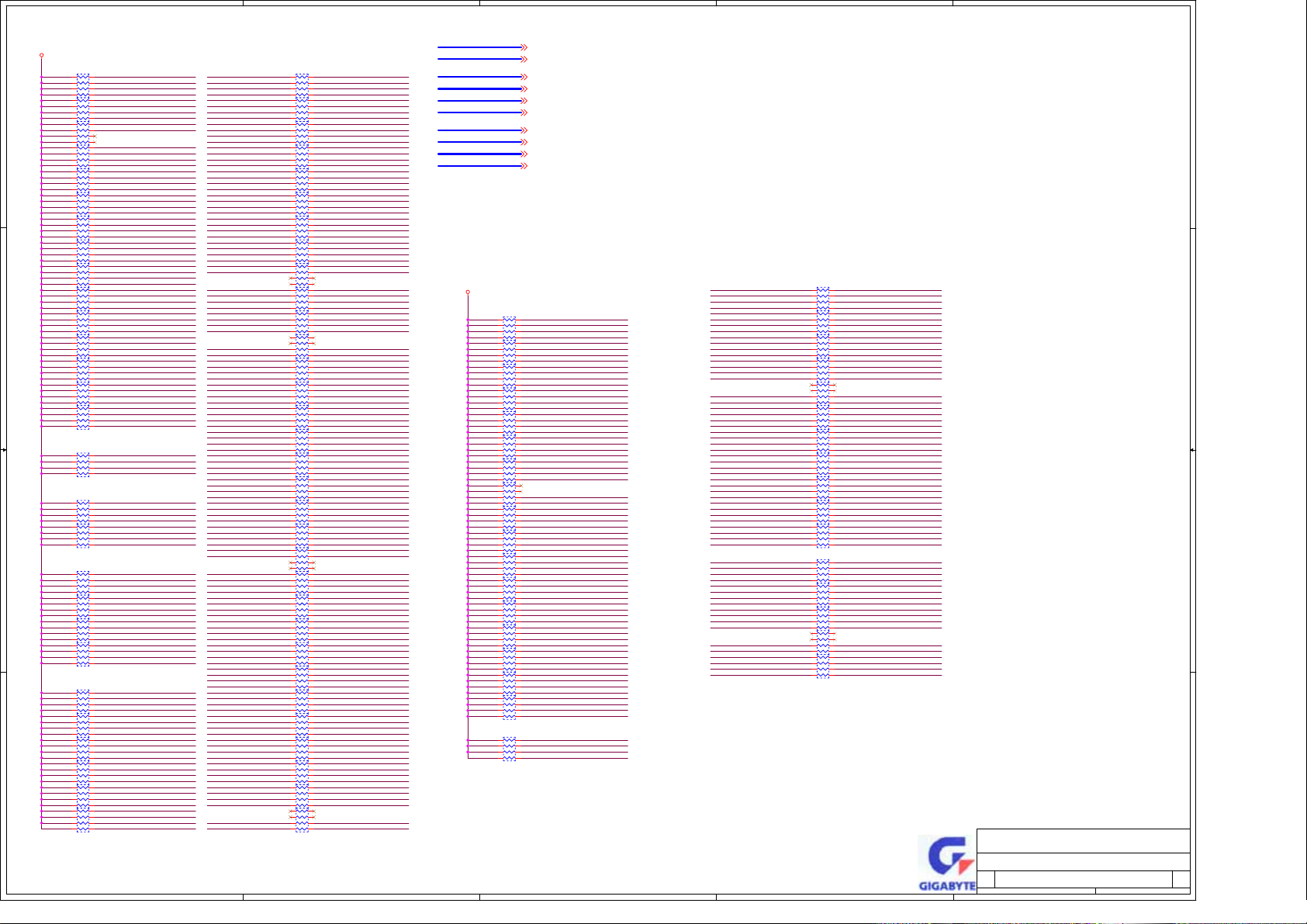

SHEET 4 Opteron P0 LDT0

SHEET 5 Opteron P0 LDT1

SHEET 6 Opteron P0 LDT2

SHEET 7 Opteron P0 Misc

SHEET 8 Opteron P0 Power/Gnd

SHEET 9 Opteron P0 Misc Power 1

SHEET 10 Opteron P0 DDR Interface

SHEET 11 Opteron P0 DDR POWER

SHEET 12 Opteron P0 VTT / VDDIO Decoupling

SHEET 13 Opteron P0 DDR DIMM0

SHEET 14 Opteron P0 DDR DIMM1

SHEET 15 Opteron P0 DDR DIMM2

SHEET 16 Opteron P0 DDR DIMM3

SHEET 17 Opteron P0 DDR Data Termination

SHEET 18 Opteron P0 DDR ADDr/Cmd Ter mi nat ion

SHEET 19 Opteron P0 POWER Decoupling

SHEET 20 Opteron P1 LDT0

SHEET 21 Opteron P1 LDT1

SHEET 22 Opteron P1 LDT2

SHEET 23 Opteron P1 Misc

SHEET 58 FRONT PANEL

SHEET 59 P0 PWM ISL6559CR ( +12V Vin )

SHEET 60 P1 PWM ISL6559CR ( +12V Vin )

SHEET 61 Power Sequencing Circuit

SHEET 62 82545GM_CONTROLLER

SHEET 63 82545GM_ PWR

SHEET 64 82545GM_1.5_2.5_POWER

SHEET 65 Giga_LAN_RJ45

SHEET 66 PCIX-SODIMM

SHEET 67 ATP867-B 4 PORT IDE

SHEET 68 FAN1-2

SHEET 69 BLANK

SHEET 70 KENAI 32/82541GI

SHEET 71 ATI_RAGE_XL

SHEET 72 FRAME_BUFFER_SDRAM

SHEET 73 VGA_CON

SHEET 74 W83791D_HW_MONITOR

SHEET 75 GSMI

SHEET 76 EATX_form factors

SHEET 77 VLDT1.2&VDD1D8V POWER

SHEET 78 PCI-X/PCI MAP

SHEET 79 I2C Routing Map

SHEET 80 Power Routing Map

SHEET 24 P1 DDR POWER SHEET 81 History

SHEET 25 P1 Misc POWER

SHEET 26 Opteron P1 POWER/GND

SHEET 27 Opteron P1 VTT / VDDIO Decoupling

SHEET 28 Opteron P1 DDR Interface

SHEET 29 Opteron P1 DDR DIMM0

SHEET 30 Opteron P1 DDR DIMM1

SHEET 31 Opteron P1 DDR DIMM2

SHEET 32 Opteron P1 DDR DIMM3

SHEET 33 Opteron P1 DDR DDR Data Terminat io n

SHEET 34 Opteron P1 DDR ADDr/Cmd Ter mi nat ion

SHEET 35 Opteron P1 POWER Decoupling

SHEET 36 AMD-8131 Golem LDT

SHEET 37 G0 PCIX Mode And Freq

SHEET 38 AMD-8131 Golem Bridge A

SHEET 39 AMD-8131 Golem Bridge B

SHEET 40 AMD-8131 Golem Decoupling

SHEET 41 Golem PCI-X_B Slot1

SHEET 42 Golem PCI-X_B Slot2

JUMPER SETTING

CLR_CMOS

1-2

CLEAR CMOS

NORMAL2-3

BIOS_WP

WRITE PROTECT

1-2

2-3

NORMAL

SHEET 43 Golem PCI-X_A Slot1

SHEET 44 Golem PCI-X_A Slot2

SHEET 45 AMD-8111 THOR HT & LPC & MII

SHEET 46 AMD-8111 THOR MISC INTE RF ACE

SHEET 47 AMD-8111 THOR POWER & GND

SHEET 48 AMD-8111 THOR CONFIGURATION

SHEET 49 AMD-8111 THOR PCI & EIDE

SHEET 50 PCI SLOT X2

SHEET 51 USB PORT

SHEET 52 ATA-133 EIDE Interface

SHEET 53 ITE LPC SIO

SHEET 54 LPT & COM

SHEET 55 PS2 DEVICE

SHEET 56 BIOS ROM

SHEET 57 CLOCK_GENERATOR

THOR GPIO

GPIO0/ACAV

**

GPIO1/AGPSTOP#

**

GPIO2/BATLOW#

**

GPIO3/C32KHZ

**

GPIO4

**

GPIO5/CLKRUN#

GPIO6/CPUSLEEP#

GPIO7/CPUSTOP#

**

GPIO8

**

GPIO9/FANCON1

**

GPIO10/FANRPM

GPIO11/INTIRQ8#

**

GPIO12/IRQ1

**

GPIO13/IRQ6

**

GPIO14

**

GPIO15/IRQ12

GPIO16

GPIO17

GPIO18/LID

**

GPIO19/PNPIRQ0

GPIO20/PNPIRQ1

GPIO21/PNPIRQ2

GPIO22/SMBALERT0#

**

GPIO23/SLPBTN#

**

GPIO24/SMBALERT1#

GPIO25/SUSPEND#

GPIO26

**

GPIO27

**

GPIO28

GPIO29

**

GPIO30

GPIO31

**

GPIO0 PULL DOWN

GPIO1

GPIO2

GPIO3

GPIO4

FUNCTION

ACAV

GPO1

LPC_PME#

SUSCLK

GPIO PORT

NOT USED

HM_SMI

BIOS_WP#

GPIO PORT

GPIO PORT

SLEEP LED N.C.

BIOS_TBL#

IRQ1

IRQ6

MEMRST TIMING

CLEAR PASSWORD

NMI SW

GPIO PORT

LID

MEMRST TIMING

-OVT

NOT USED

SM BUS ALERT

SLPBTN#

NOT USED

GPO25

DCABLEIDS#

DCABLEIDP#

GPIO PORT

GPIO PORT

GPIO PORT

GPIO PORT

FUNCTION

NOT USED

NOT USED

NOT USED

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

Custom

Date: Sheet

PULL UP/DOWN

PULL UP 3VDUALL

N.C.

PULL UP TO 3VDUAL

N.C.

NC

PULL UP TO VCC3

PULL UP TO VCC3

PULL UP TO VCC3

N.C.

N.C.

PULL UP TO VCC3

PULL UP TO VCC3

PULL UP TO VCC3

PULL DOWN

PULL UP TO VCC3

PULL UP TO VCC3

N.C.

PULL UP 3VDUALL

PULL DOWN

PULL UP TO VCC3

PULL DOWN

PULL UP TO 3VDUAL

PULL UP TO 3VDUAL

PULL UP TO 3VDUAL

PULL UP TO 3VDUAL

PULL UP TO VCC3

PULL UP TO VCC3

N.C.

N.C.

N.C.

N.C.

PULL UP/DOWNLPC FLASH ROM GPIO

PULL DOWNNOT USED

PULL DOWN

PULL DOWNNOT USED

PULL DOWN

COVER SHEET

GA-7A8DRL

2.0

of

181Thursday, November 10, 2005

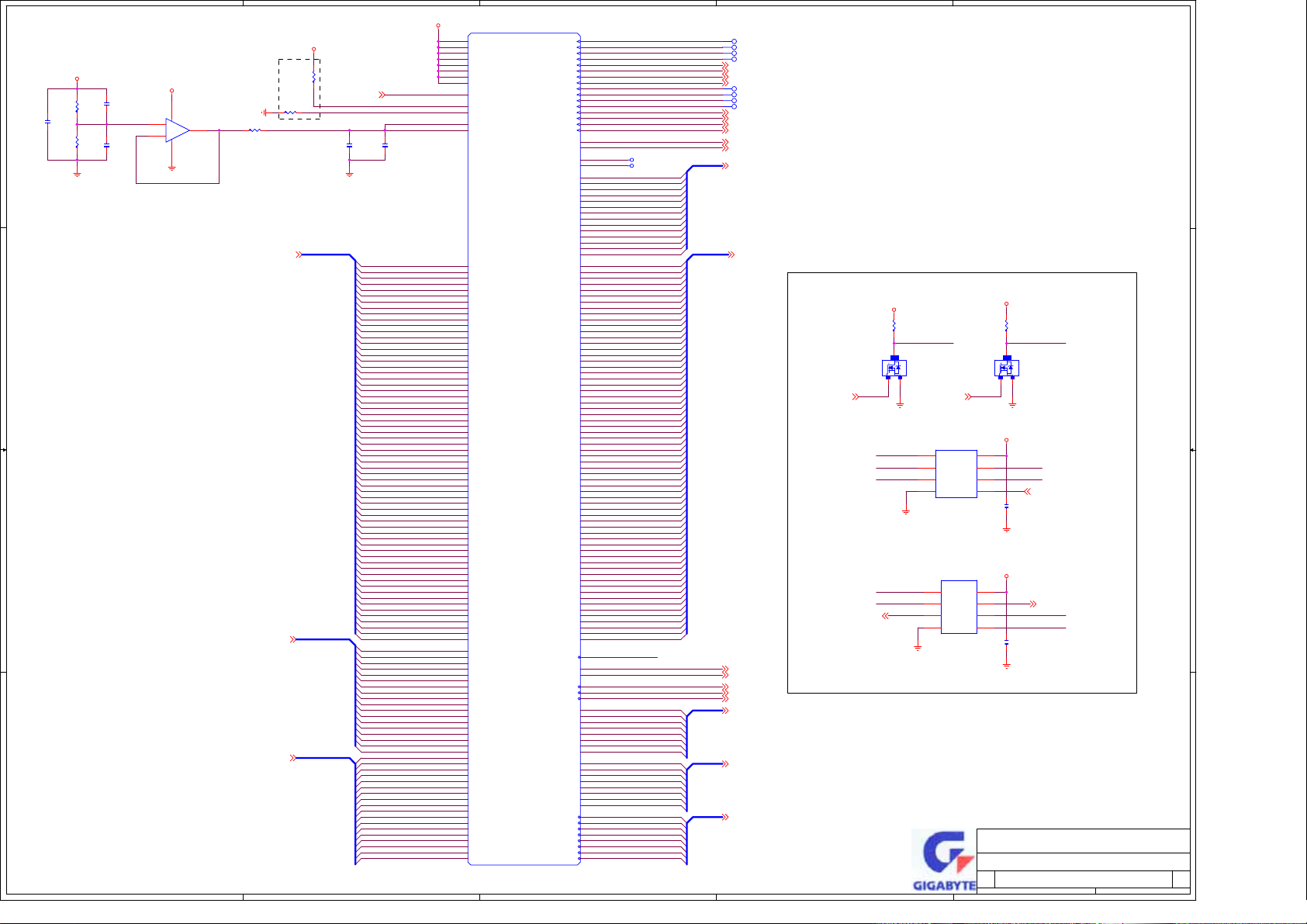

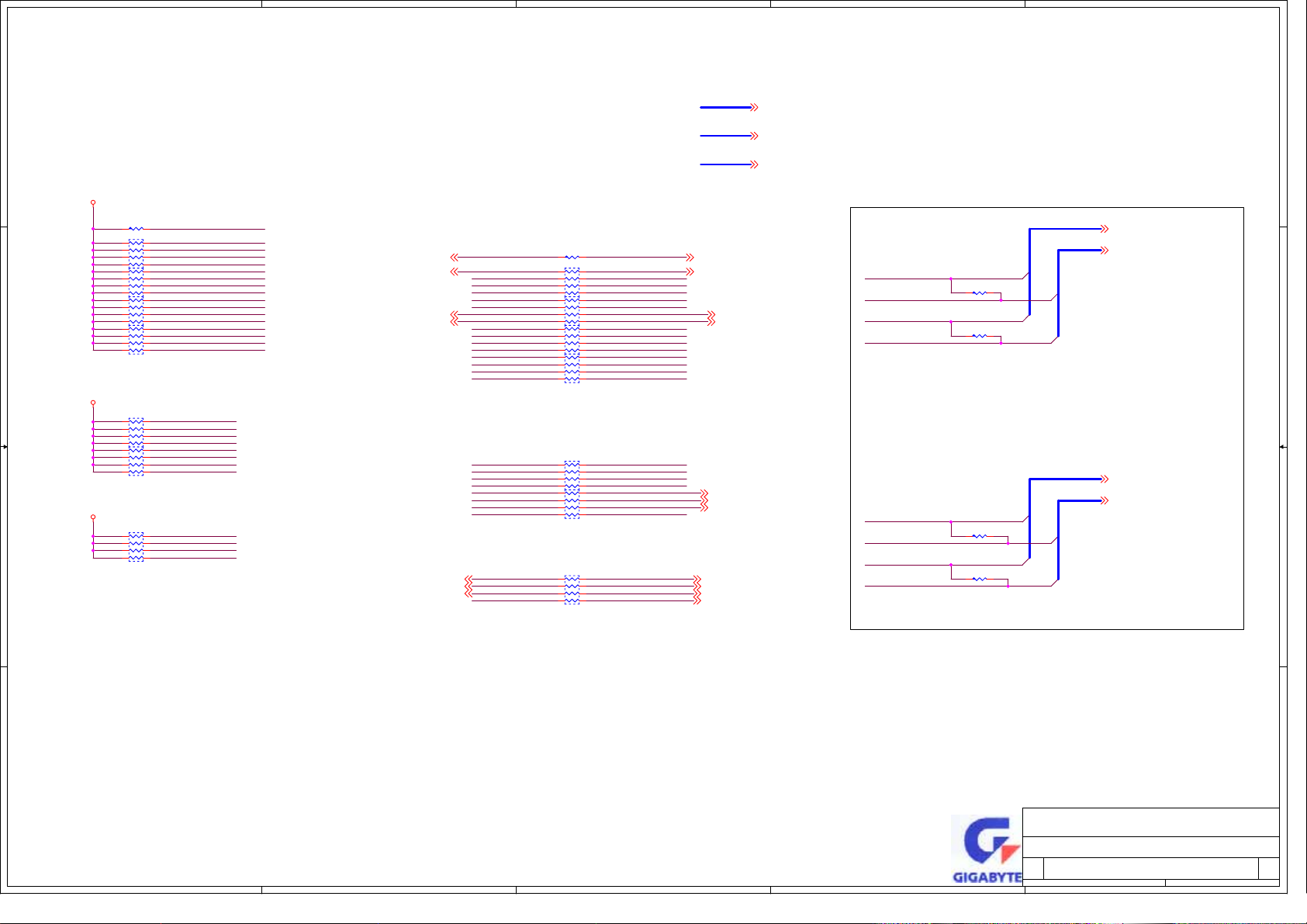

Page 3

Registered

DDR400 SDRAM X4

Sheets 29-32

Opteron 1

Sheets 20-35

Block Diagram

LINK 1 16X16

6.4GB/S

Opteron 0

Sheets 4-19

Registered

DDR400 SDRAM X4

Sheets 13-16

PCI-X

SODIMM

SHEET

66

GigaLAN

Intel

82545GM

Sheet

62-64

channel A

channel B

PCI-X

SLOT X2

SHEET

43-44

PCI-X

Slots x 2

Sheet 41-42

LINK 0 16X16

6.4GB/S

8131

Sheets 36-40

LPC ROM

Sheet 56

8111

Sheets 45-49

LPC

LPC Super

I/O

ITE8712F

Sheet 53

LINK 2 8X8

800MB/S

PCI 32b/33MHz

USB 1.0

PCI VGA

ATI RANGE_XL

VGA X1

SHEET 71-72

Rear USB 1.0 x2

Sheets 51

PCI Slots x 2

Sheets 50

ACARD

ATP867

P-IDE x4

SHEET 67 SHEET 70

EIDE (ATA/100) x2

Sheet 52

Front USB 1.0 x2

Sheets 51

Floppy Disk Drive

Sheet 53

PS2 DEVICE

Sheet 55

LPT X1 &

COM X2

Sheet 54

Intel 82541GI

Giga bit LAN

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

Custom

Date: Sheet

D

BLOCK DIAGRAM

GA-7A8DRL

2.0

of

281Thursday, November 10, 2005

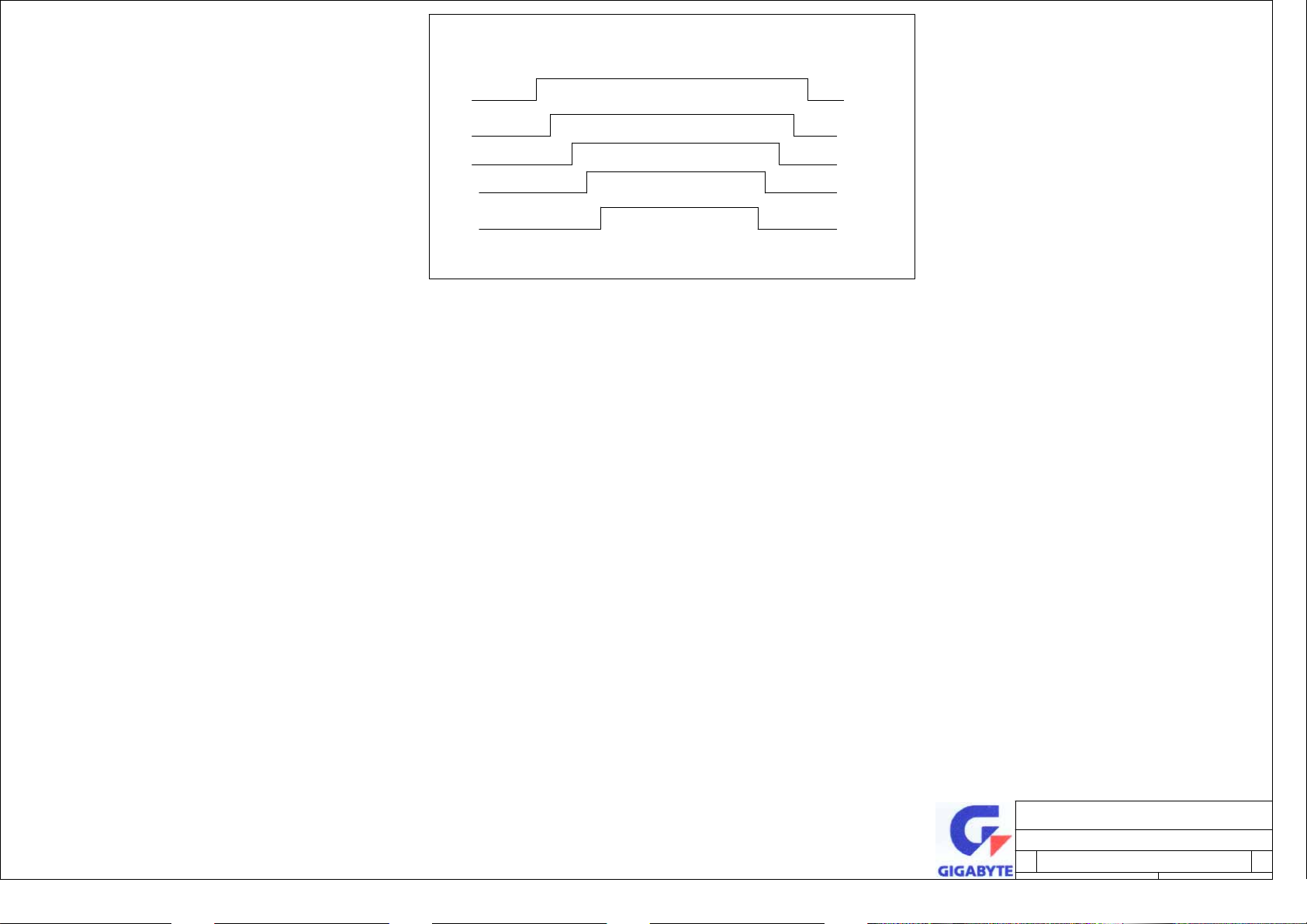

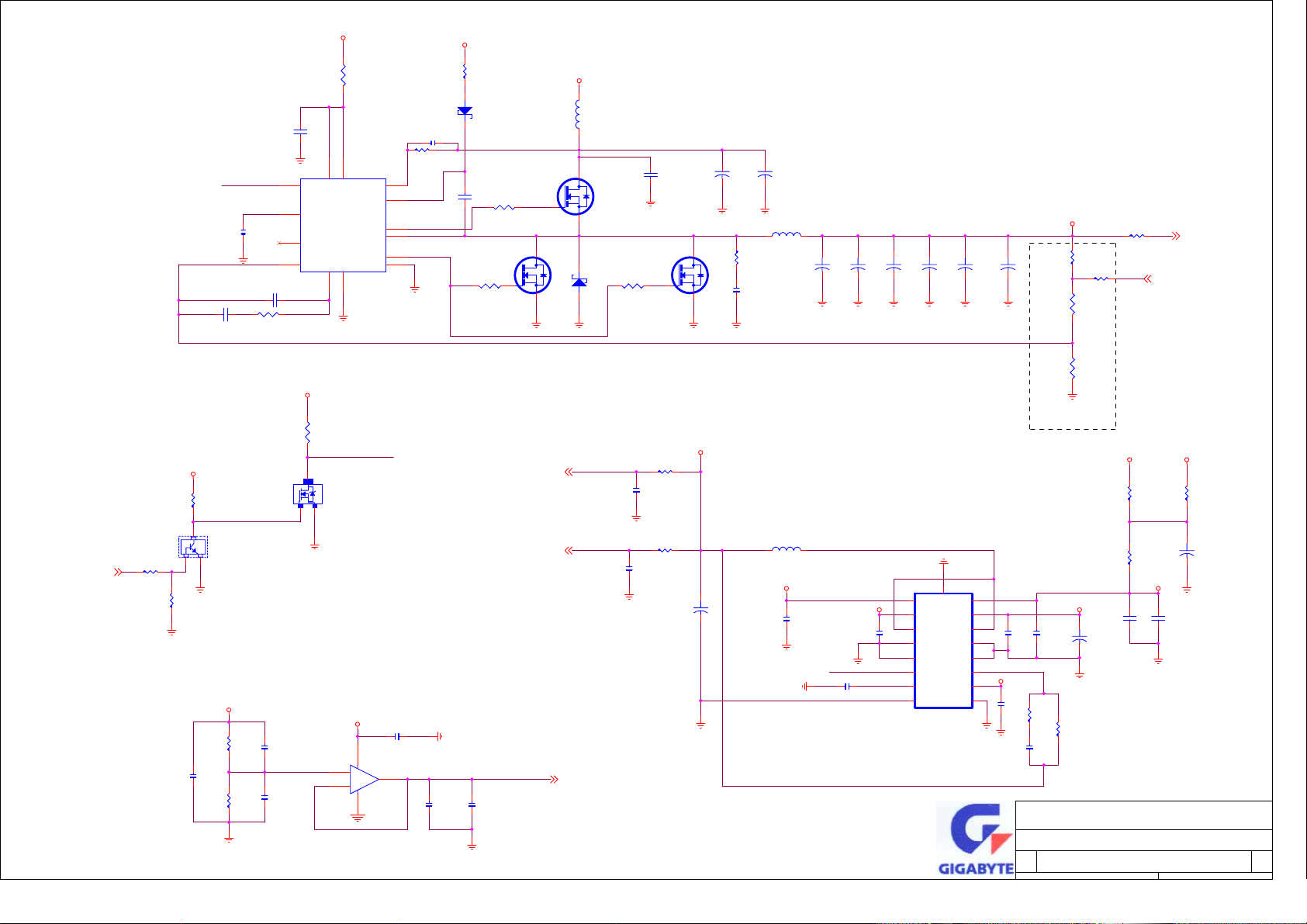

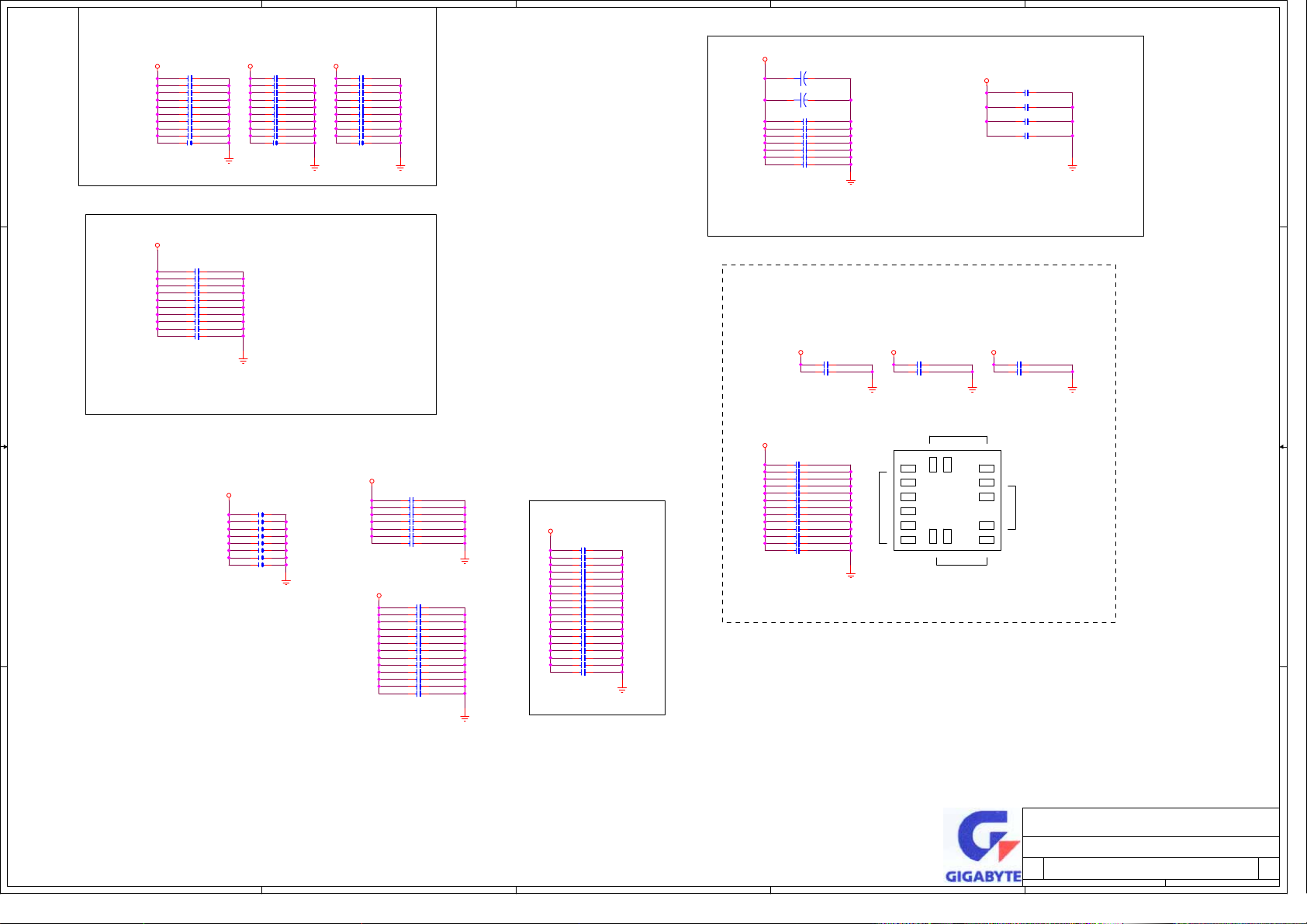

Page 4

AMD - 8131 PCI-X Tunnel

VDD12A : Provides power to A side of the Tunnel.

VDD12B : Provides power to B side of the Tunnel.

VDD18 : 1.8 Volt power plane for the core logic.

VDD18A : Analog 1.8 Volt power plane for the PLLs in the core logic.

VCC3 : 3.3 Volt power plane for PCI I/O.

3VSB : 3.3 Volt auxiliary power plane for PME signal.

VCC3 is required to always be higher than VDD18,VDDA18,VDD12A,VDD12B.

VDD18,VDD18A is required to always be higher VDD12A,VDD12B.

VTT

VDD_2D5V

VDDA_2D5V

(Opteron_PLL)

Vcore

Opteron Power Sequence

Power up

Power down

AMD - 8111 I/O HUB

VDD_IO : 3.3 V supply.

VDD_CORE : 1.8 V supply.

VDD_IOX : 3.3 V supply

VDD_COREX : 1.8 V supply

VDD_LDT : 1.2 V supply

VDD_REF : 5 V supply

VDD_RTC : 3.3 V supply

VDD_USB : 3.3 V supply

VDD_USBA : 1.8 V supply

VDD_IOAL : 3.3 V supply

VDD_COREAL : 1.8 V supply

VLDT

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

Custom

Date: Sheet

Power Sequence

GA-7A8DRL

of

381Thursday, November 10, 2005

2.0

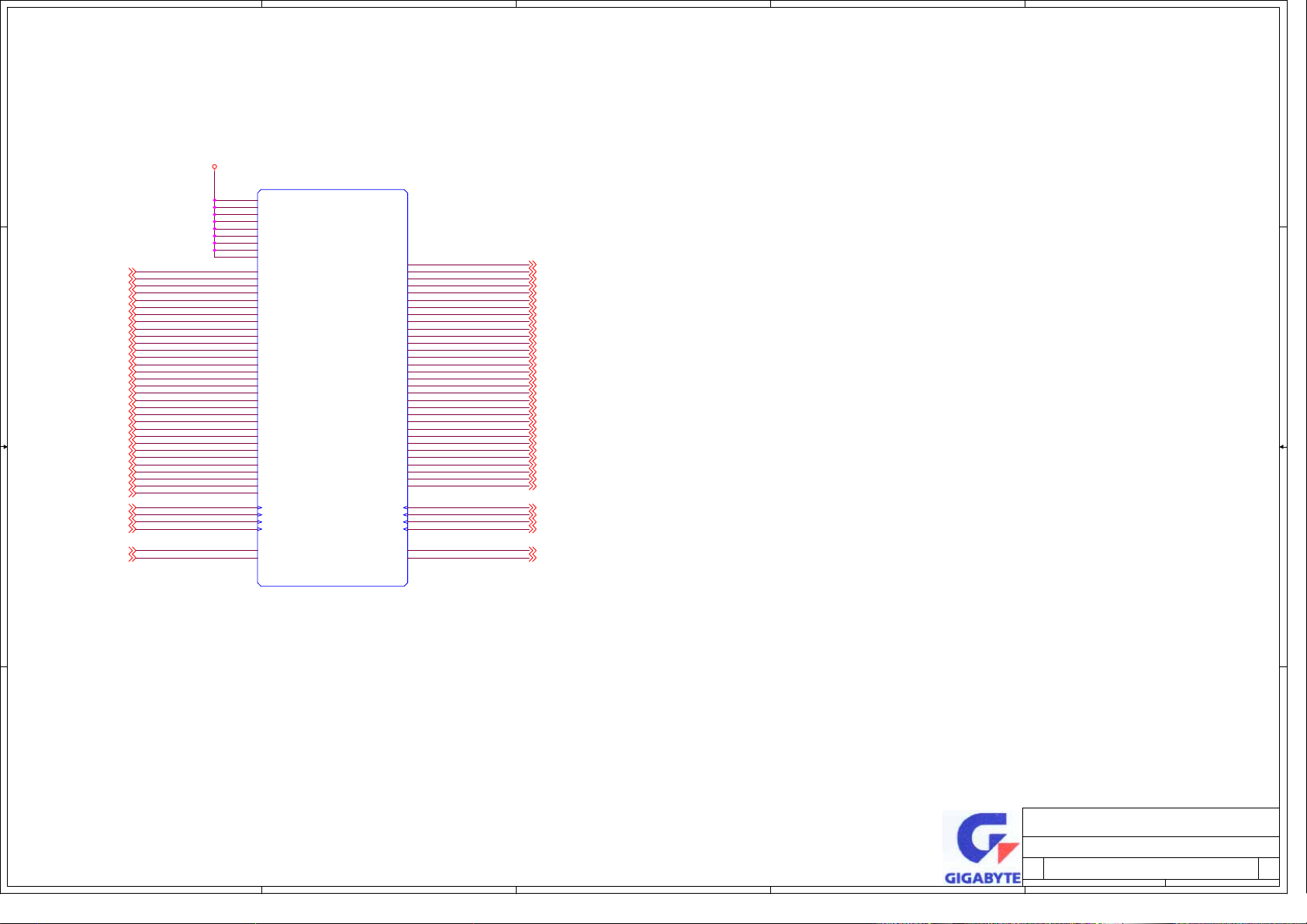

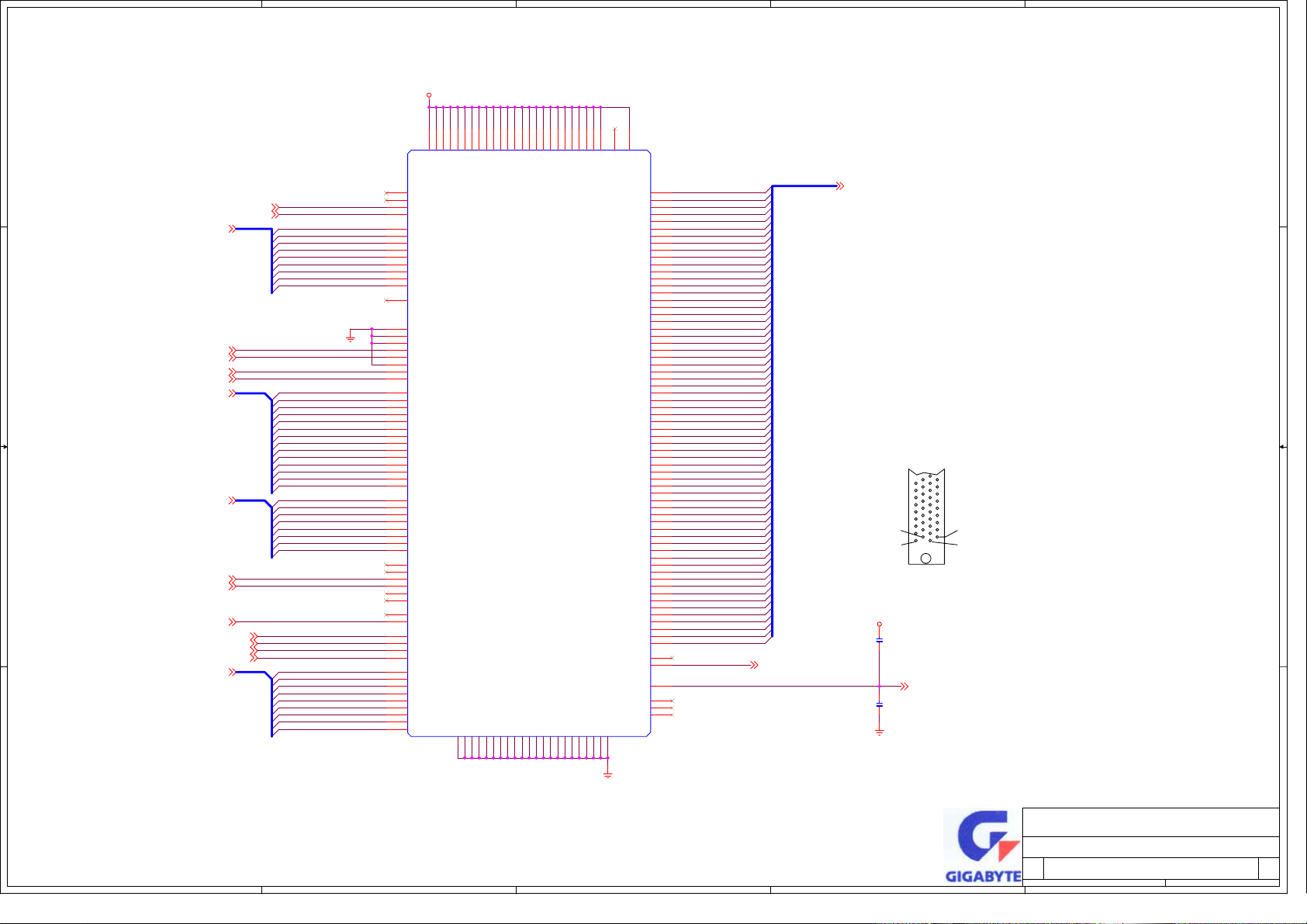

Page 5

5

D D

VLDT_1D2V

U1A

N7

VLDT_0(1)

R7

VLDT_0(2)

U7

VLDT_0(3)

W7

VLDT_0(4)

M8

VLDT_0(5)

P8

VLDT_0(6)

AA7

VLDT_0(7)

V8

VLDT_0(8)

Y8

P0_HTL0_CADIN_H1536

P0_HTL0_CADIN_L1536

P0_HTL0_CADIN_H1436

P0_HTL0_CADIN_L1436

P0_HTL0_CADIN_H1336

P0_HTL0_CADIN_L1336

P0_HTL0_CADIN_H1236

P0_HTL0_CADIN_L1236

P0_HTL0_CADIN_H1136

C C

B B

P0_HTL0_CADIN_L1136

P0_HTL0_CADIN_H1036

P0_HTL0_CADIN_L1036

P0_HTL0_CADIN_H936

P0_HTL0_CADIN_L936

P0_HTL0_CADIN_H836

P0_HTL0_CADIN_L836

P0_HTL0_CADIN_H736

P0_HTL0_CADIN_L736

P0_HTL0_CADIN_H636

P0_HTL0_CADIN_L636

P0_HTL0_CADIN_H536

P0_HTL0_CADIN_L536

P0_HTL0_CADIN_H436

P0_HTL0_CADIN_L436

P0_HTL0_CADIN_H336

P0_HTL0_CADIN_L336

P0_HTL0_CADIN_H236

P0_HTL0_CADIN_L236

P0_HTL0_CADIN_H136

P0_HTL0_CADIN_L136

P0_HTL0_CADIN_H036

P0_HTL0_CADIN_L036

P0_HTL0_CLKIN_H136

P0_HTL0_CLKIN_L136

P0_HTL0_CLKIN_H036

P0_HTL0_CLKIN_L036

P0_HTL0_CTRLIN_H36

P0_HTL0_CTRLIN_L36

P0_HTL0_CADIN_H15

P0_HTL0_CADIN_L15

P0_HTL0_CADIN_H14

P0_HTL0_CADIN_L14

P0_HTL0_CADIN_H13

P0_HTL0_CADIN_L13

P0_HTL0_CADIN_H12

P0_HTL0_CADIN_L12

P0_HTL0_CADIN_H11

P0_HTL0_CADIN_L11

P0_HTL0_CADIN_H10

P0_HTL0_CADIN_L10

P0_HTL0_CADIN_H9

P0_HTL0_CADIN_L9

P0_HTL0_CADIN_H8

P0_HTL0_CADIN_L8

P0_HTL0_CADIN_H7

P0_HTL0_CADIN_L7 P0_HTL0_CADOUT_H6

P0_HTL0_CADIN_H6

P0_HTL0_CADIN_L6

P0_HTL0_CADIN_H5

P0_HTL0_CADIN_L5

P0_HTL0_CADIN_H4

P0_HTL0_CADIN_L4

P0_HTL0_CADIN_H3

P0_HTL0_CADIN_L3

P0_HTL0_CADIN_H2

P0_HTL0_CADIN_L2

P0_HTL0_CADIN_H1

P0_HTL0_CADIN_L1

P0_HTL0_CADIN_H0

P0_HTL0_CADIN_L0

P0_HTL0_CLKIN_H1

P0_HTL0_CLKIN_L1 P0_HTL0_CLKOUT_L1

P0_HTL0_CLKIN_H0

P0_HTL0_CLKIN_L0

P0_HTL0_CTRLIN_H

P0_HTL0_CTRLIN_L

VLDT_0(9)

R5

L0_CADIN_H(15)

T5

L0_CADIN_L(15)

P3

L0_CADIN_H(14)

P4

L0_CADIN_L(14)

N5

L0_CADIN_H(13)

P5

L0_CADIN_L(13)

M3

L0_CADIN_H(12)

M4

L0_CADIN_L(12)

K3

L0_CADIN_H(11)

K4

L0_CADIN_L(11)

J5

L0_CADIN_H(10)

K5

L0_CADIN_L(10)

H3

L0_CADIN_H(9)

H4

L0_CADIN_L(9)

G5

L0_CADIN_H(8)

H5

L0_CADIN_L(8)

R3

L0_CADIN_H(7)

R2

L0_CADIN_L(7)

N1

L0_CADIN_H(6)

P1

L0_CADIN_L(6)

N3

L0_CADIN_H(5)

N2

L0_CADIN_L(5)

L1

L0_CADIN_H(4)

M1

L0_CADIN_L(4)

J1

L0_CADIN_H(3)

K1

L0_CADIN_L(3)

J3

L0_CADIN_H(2)

J2

L0_CADIN_L(2)

G1

L0_CADIN_H(1)

H1

L0_CADIN_L(1)

G3

L0_CADIN_H(0)

G2

L0_CADIN_L(0)

L5

L0_CLKIN_H(1)

M5

L0_CLKIN_L(1)

L3

L0_CLKIN_H(0)

L2

L0_CLKIN_L(0)

R1

L0_CTLIN_H(0)

T1

L0_CTLIN_L(0)

4

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

P0_HTL0_CADOUT_H15

V4

P0_HTL0_CADOUT_L15

V3

P0_HTL0_CADOUT_H14

Y5

P0_HTL0_CADOUT_L14

W5

P0_HTL0_CADOUT_H13

Y4

P0_HTL0_CADOUT_L13

Y3

P0_HTL0_CADOUT_H12

AB5

P0_HTL0_CADOUT_L12

AA5

P0_HTL0_CADOUT_H11

AD5

P0_HTL0_CADOUT_L11

AC5

P0_HTL0_CADOUT_H10

AD4

P0_HTL0_CADOUT_L10

AD3

P0_HTL0_CADOUT_H9

AF5

P0_HTL0_CADOUT_L9

AE5

P0_HTL0_CADOUT_H8

AF4

P0_HTL0_CADOUT_L8

AF3

P0_HTL0_CADOUT_H7

V1

P0_HTL0_CADOUT_L7

U1

W2

P0_HTL0_CADOUT_L6

W3

P0_HTL0_CADOUT_H5

Y1

P0_HTL0_CADOUT_L5

W1

P0_HTL0_CADOUT_H4

AA2

P0_HTL0_CADOUT_L4

AA3

P0_HTL0_CADOUT_H3

AC2

P0_HTL0_CADOUT_L3

AC3

P0_HTL0_CADOUT_H2

AD1

P0_HTL0_CADOUT_L2

AC1

P0_HTL0_CADOUT_H1

AE2

P0_HTL0_CADOUT_L1

AE3

P0_HTL0_CADOUT_H0

AF1

P0_HTL0_CADOUT_L0

AE1

P0_HTL0_CLKOUT_H1

AB4

AB3

P0_HTL0_CLKOUT_H0

AB1

P0_HTL0_CLKOUT_L0

AA1

P0_HTL0_CTRLOUT_H

U2

P0_HTL0_CTRLOUT_L

U3

P0_HTL0_CADOUT_H15 36

P0_HTL0_CADOUT_L15 36

P0_HTL0_CADOUT_H14 36

P0_HTL0_CADOUT_L14 36

P0_HTL0_CADOUT_H13 36

P0_HTL0_CADOUT_L13 36

P0_HTL0_CADOUT_H12 36

P0_HTL0_CADOUT_L12 36

P0_HTL0_CADOUT_H11 36

P0_HTL0_CADOUT_L11 36

P0_HTL0_CADOUT_H10 36

P0_HTL0_CADOUT_L10 36

P0_HTL0_CADOUT_H9 36

P0_HTL0_CADOUT_L9 36

P0_HTL0_CADOUT_H8 36

P0_HTL0_CADOUT_L8 36

P0_HTL0_CADOUT_H7 36

P0_HTL0_CADOUT_L7 36

P0_HTL0_CADOUT_H6 36

P0_HTL0_CADOUT_L6 36

P0_HTL0_CADOUT_H5 36

P0_HTL0_CADOUT_L5 36

P0_HTL0_CADOUT_H4 36

P0_HTL0_CADOUT_L4 36

P0_HTL0_CADOUT_H3 36

P0_HTL0_CADOUT_L3 36

P0_HTL0_CADOUT_H2 36

P0_HTL0_CADOUT_L2 36

P0_HTL0_CADOUT_H1 36

P0_HTL0_CADOUT_L1 36

P0_HTL0_CADOUT_H0 36

P0_HTL0_CADOUT_L0 36

P0_HTL0_CLKOUT_H1 36

P0_HTL0_CLKOUT_L1 36

P0_HTL0_CLKOUT_H0 36

P0_HTL0_CLKOUT_L0 36

P0_HTL0_CTRLOUT_H 36

P0_HTL0_CTRLOUT_L 36

3

2

1

Opteron

TO AMD 8131

A A

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

Opteron P0 LDT Link 0

GA-7A8DRL

1

2.0

of

481Thursday, November 10, 2005

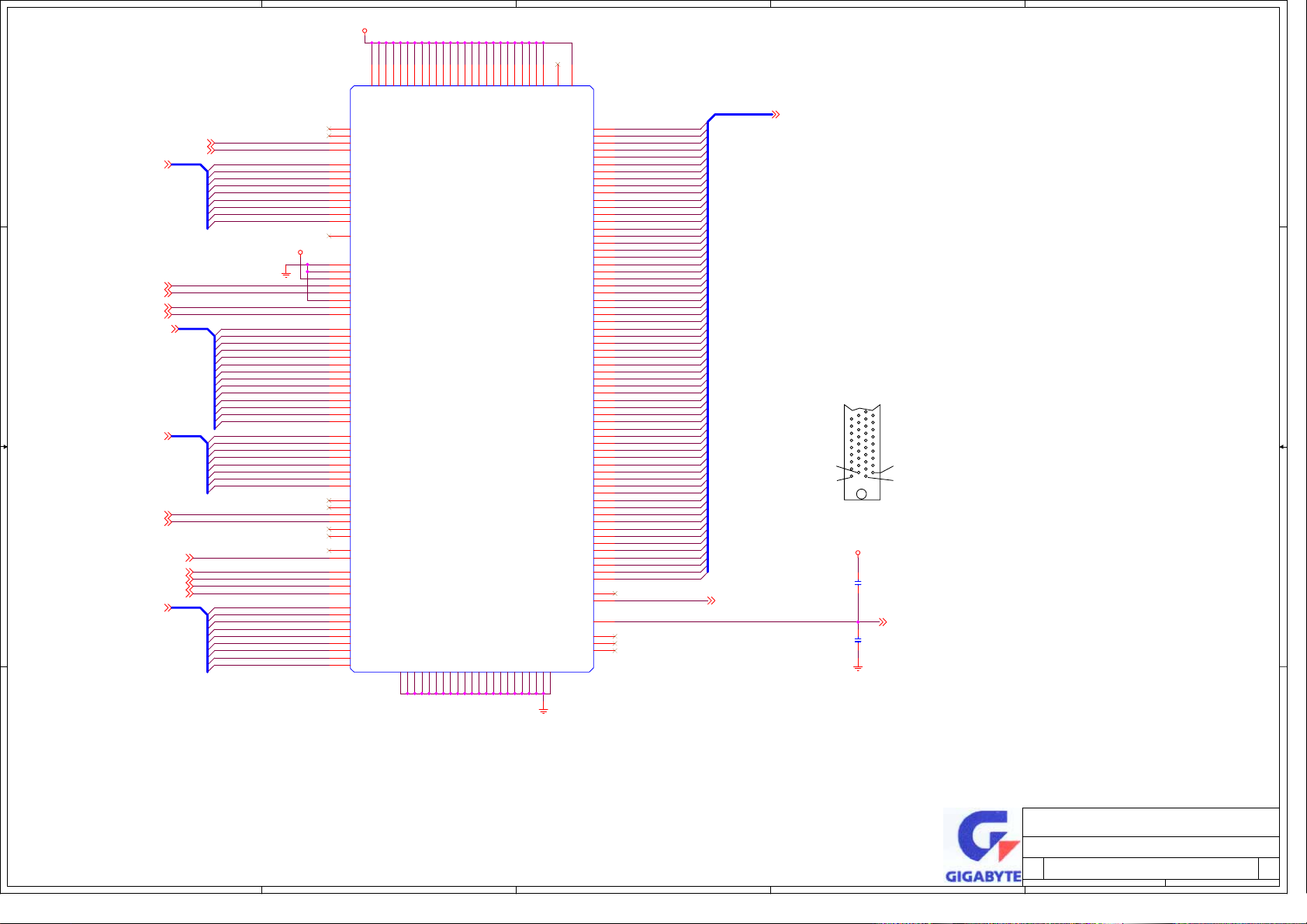

Page 6

5

D D

VLDT_1D2V

U1E

K10

VLDT_1(1)

J11

VLDT_1(2)

H10

VLDT_1(3)

H8

VLDT_1(4)

K14

VLDT_1(5)

J15

VLDT_1(6)

K16

VLDT_1(7)

J16

VLDT_1(8)

J9

P0_HTL1_CADIN_H1521

P0_HTL1_CADIN_L1521

P0_HTL1_CADIN_H1421

P0_HTL1_CADIN_L1421

P0_HTL1_CADIN_H1321

P0_HTL1_CADIN_L1321

C C

B B

P0_HTL1_CADIN_H1221

P0_HTL1_CADIN_L1221

P0_HTL1_CADIN_H1121

P0_HTL1_CADIN_L1121

P0_HTL1_CADIN_H1021

P0_HTL1_CADIN_L1021

P0_HTL1_CADIN_H921

P0_HTL1_CADIN_L921

P0_HTL1_CADIN_H821

P0_HTL1_CADIN_L821

P0_HTL1_CADIN_H721

P0_HTL1_CADIN_L721

P0_HTL1_CADIN_H621

P0_HTL1_CADIN_L621

P0_HTL1_CADIN_H521

P0_HTL1_CADIN_L521

P0_HTL1_CADIN_H421

P0_HTL1_CADIN_L421

P0_HTL1_CADIN_H321

P0_HTL1_CADIN_L321

P0_HTL1_CADIN_H221

P0_HTL1_CADIN_L221

P0_HTL1_CADIN_H121

P0_HTL1_CADIN_L121

P0_HTL1_CADIN_H021

P0_HTL1_CADIN_L021

P0_HTL1_CLKIN_H121

P0_HTL1_CLKIN_L121

P0_HTL1_CLKIN_H021

P0_HTL1_CLKIN_L021

P0_HTL1_CTRLIN_H21

P0_HTL1_CTRLIN_L21

P0_HTL1_CADIN_H15

P0_HTL1_CADIN_L15

P0_HTL1_CADIN_H14

P0_HTL1_CADIN_L14

P0_HTL1_CADIN_H13

P0_HTL1_CADIN_L13

P0_HTL1_CADIN_H12

P0_HTL1_CADIN_L12

P0_HTL1_CADIN_H11

P0_HTL1_CADIN_L11

P0_HTL1_CADIN_H10

P0_HTL1_CADIN_L10

P0_HTL1_CADIN_H9

P0_HTL1_CADIN_L9

P0_HTL1_CADIN_H8

P0_HTL1_CADIN_L8

P0_HTL1_CADIN_H7

P0_HTL1_CADIN_L7

P0_HTL1_CADIN_H6

P0_HTL1_CADIN_L6

P0_HTL1_CADIN_H5

P0_HTL1_CADIN_L5

P0_HTL1_CADIN_H4

P0_HTL1_CADIN_L4

P0_HTL1_CADIN_H3

P0_HTL1_CADIN_L3

P0_HTL1_CADIN_H2

P0_HTL1_CADIN_L2

P0_HTL1_CADIN_H1

P0_HTL1_CADIN_L1

P0_HTL1_CADIN_H0

P0_HTL1_CADIN_L0

P0_HTL1_CLKIN_H1

P0_HTL1_CLKIN_L1

P0_HTL1_CLKIN_H0

P0_HTL1_CLKIN_L0

P0_HTL1_CTRLIN_H

P0_HTL1_CTRLIN_L

TP1 TP2

TP3

E14

E13

C15

D15

E16

E15

C17

D17

C19

D19

E20

E19

C21

D21

E22

E21

C14

B14

A16

A15

C16

B16

A18

A17

A20

A19

C20

B20

A22

A21

C22

B22

E18

E17

C18

B18

A14

A13

C13

D13

VLDT_1(9)

L1_CADIN_H(15)

L1_CADIN_L(15)

L1_CADIN_H(14)

L1_CADIN_L(14)

L1_CADIN_H(13)

L1_CADIN_L(13)

L1_CADIN_H(12)

L1_CADIN_L(12)

L1_CADIN_H(11)

L1_CADIN_L(11)

L1_CADIN_H(10)

L1_CADIN_L(10)

L1_CADIN_H(9)

L1_CADIN_L(9)

L1_CADIN_H(8)

L1_CADIN_L(8)

L1_CADIN_H(7)

L1_CADIN_L(7)

L1_CADIN_H(6)

L1_CADIN_L(6)

L1_CADIN_H(5)

L1_CADIN_L(5)

L1_CADIN_H(4)

L1_CADIN_L(4)

L1_CADIN_H(3)

L1_CADIN_L(3)

L1_CADIN_H(2)

L1_CADIN_L(2)

L1_CADIN_H(1)

L1_CADIN_L(1)

L1_CADIN_H(0)

L1_CADIN_L(0)

L1_CLKIN_H(1)

L1_CLKIN_L(1)

L1_CLKIN_H(0)

L1_CLKIN_L(0)

L1_CTLIN_H(0)

L1_CTLIN_L(0)

L1_RSVD1

L1_RSVD2

Opteron

4

L1_CADOUT_H(15)

L1_CADOUT_L(15)

L1_CADOUT_H(14)

L1_CADOUT_L(14)

L1_CADOUT_H(13)

L1_CADOUT_L(13)

L1_CADOUT_H(12)

L1_CADOUT_L(12)

L1_CADOUT_H(11)

L1_CADOUT_L(11)

L1_CADOUT_H(10)

L1_CADOUT_L(10)

L1_CADOUT_H(9)

L1_CADOUT_L(9)

L1_CADOUT_H(8)

L1_CADOUT_L(8)

L1_CADOUT_H(7)

L1_CADOUT_L(7)

L1_CADOUT_H(6)

L1_CADOUT_L(6)

L1_CADOUT_H(5)

L1_CADOUT_L(5)

L1_CADOUT_H(4)

L1_CADOUT_L(4)

L1_CADOUT_H(3)

L1_CADOUT_L(3)

L1_CADOUT_H(2)

L1_CADOUT_L(2)

L1_CADOUT_H(1)

L1_CADOUT_L(1)

L1_CADOUT_H(0)

L1_CADOUT_L(0)

L1_CLKOUT_H(1)

L1_CLKOUT_L(1)

L1_CLKOUT_H(0)

L1_CLKOUT_L(0)

L1_CTLOUT_H(0)

L1_CTLOUT_L(0)

L1_RSVD3

L1_RSVD4

P0_HTL1_CADOUT_H15

D11

P0_HTL1_CADOUT_L15

C11

P0_HTL1_CADOUT_H14

E9

P0_HTL1_CADOUT_L14

E10

P0_HTL1_CADOUT_H13

D9

P0_HTL1_CADOUT_L13

C9

P0_HTL1_CADOUT_H12

E7

P0_HTL1_CADOUT_L12

E8

P0_HTL1_CADOUT_H11

E5

P0_HTL1_CADOUT_L11

E6

P0_HTL1_CADOUT_H10

D5

P0_HTL1_CADOUT_L10

C5

P0_HTL1_CADOUT_H9

E3

P0_HTL1_CADOUT_L9

E4

P0_HTL1_CADOUT_H8

D3

P0_HTL1_CADOUT_L8

C3

P0_HTL1_CADOUT_H7

A11

P0_HTL1_CADOUT_L7

A12

P0_HTL1_CADOUT_H6

B10

P0_HTL1_CADOUT_L6

C10

P0_HTL1_CADOUT_H5

A9

P0_HTL1_CADOUT_L5

A10

P0_HTL1_CADOUT_H4

B8

P0_HTL1_CADOUT_L4

C8

P0_HTL1_CADOUT_H3

B6

P0_HTL1_CADOUT_L3

C6

P0_HTL1_CADOUT_H2

A5

P0_HTL1_CADOUT_L2

A6

P0_HTL1_CADOUT_H1

B4

P0_HTL1_CADOUT_L1

C4

P0_HTL1_CADOUT_H0

A3

P0_HTL1_CADOUT_L0

A4

P0_HTL1_CLKOUT_H1

D7

P0_HTL1_CLKOUT_L1

C7

P0_HTL1_CLKOUT_H0

A7

P0_HTL1_CLKOUT_L0

A8

P0_HTL1_CTRLOUT_H

B12

P0_HTL1_CTRLOUT_L

C12

E11

E12

P0_HTL1_CADOUT_H15 21

P0_HTL1_CADOUT_L15 21

P0_HTL1_CADOUT_H14 21

P0_HTL1_CADOUT_L14 21

P0_HTL1_CADOUT_H13 21

P0_HTL1_CADOUT_L13 21

P0_HTL1_CADOUT_H12 21

P0_HTL1_CADOUT_L12 21

P0_HTL1_CADOUT_H11 21

P0_HTL1_CADOUT_L11 21

P0_HTL1_CADOUT_H10 21

P0_HTL1_CADOUT_L10 21

P0_HTL1_CADOUT_H9 21

P0_HTL1_CADOUT_L9 21

P0_HTL1_CADOUT_H8 21

P0_HTL1_CADOUT_L8 21

P0_HTL1_CADOUT_H7 21

P0_HTL1_CADOUT_L7 21

P0_HTL1_CADOUT_H6 21

P0_HTL1_CADOUT_L6 21

P0_HTL1_CADOUT_H5 21

P0_HTL1_CADOUT_L5 21

P0_HTL1_CADOUT_H4 21

P0_HTL1_CADOUT_L4 21

P0_HTL1_CADOUT_H3 21

P0_HTL1_CADOUT_L3 21

P0_HTL1_CADOUT_H2 21

P0_HTL1_CADOUT_L2 21

P0_HTL1_CADOUT_H1 21

P0_HTL1_CADOUT_L1 21

P0_HTL1_CADOUT_H0 21

P0_HTL1_CADOUT_L0 21

P0_HTL1_CLKOUT_H1 21

P0_HTL1_CLKOUT_L1 21

P0_HTL1_CLKOUT_H0 21

P0_HTL1_CLKOUT_L0 21

P0_HTL1_CTRLOUT_H 21

P0_HTL1_CTRLOUT_L 21

TP4

3

TO Opteron1

Layout pattern

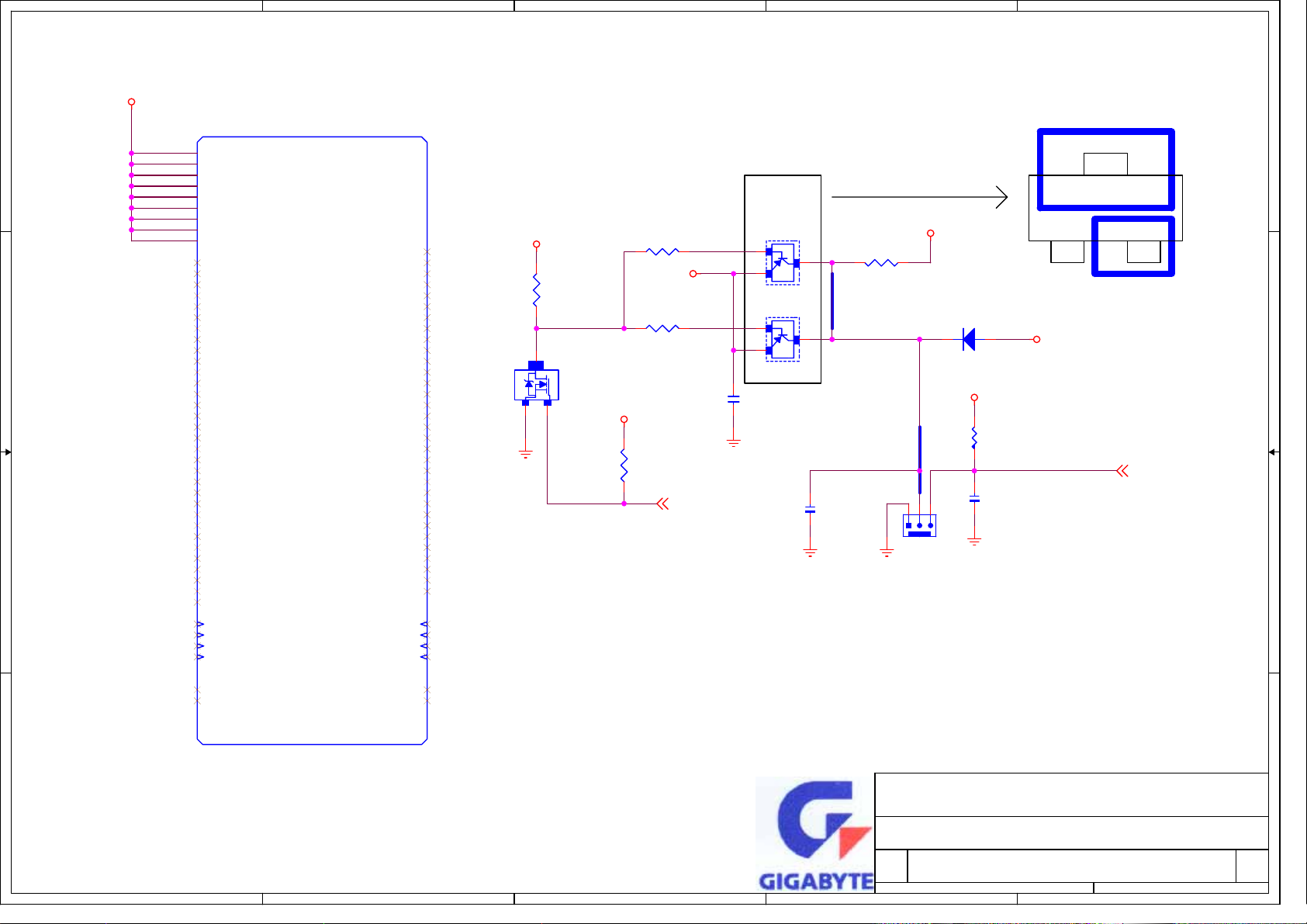

Copper pour(+12V)

2

1

3

+12V

1 2

3

D

A A

5

1

GND

R1022

1K/6

Q136

2N7002/SOT23

GS

2

1 2

1 2

VCC

12

R1020

R1023

1.5K/6

R1024

4.7K/6

1.5K/6

+12V

GND

FANPWM1

2

1

2

1

12

C795

22U/1210/16V

Q134

3

2N2907A

Q135

3

2N2907A

FANPWM1 74

4

0/6/X

R1021

12

V12_CPU_FAN1

Routed trace

width > 40 mils

C16

0.1U/6/16V

GND

+12V

GND

VCC

12

D88

1N5817/X

213

CVS

CPU_FAN1

FAN1x3/W

VCC

R25

8.2K/6

C15

3300P/6/X7R/X

GND

FANIO1

3

FANIO1 74

21

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

Custom

2

Date: Sheet

Opteron P0 LDT Link 1

GA-7A8DRL

1

2.0

of

581Thursday, November 10, 2005

Page 7

Page 8

Page 9

Page 10

Page 11

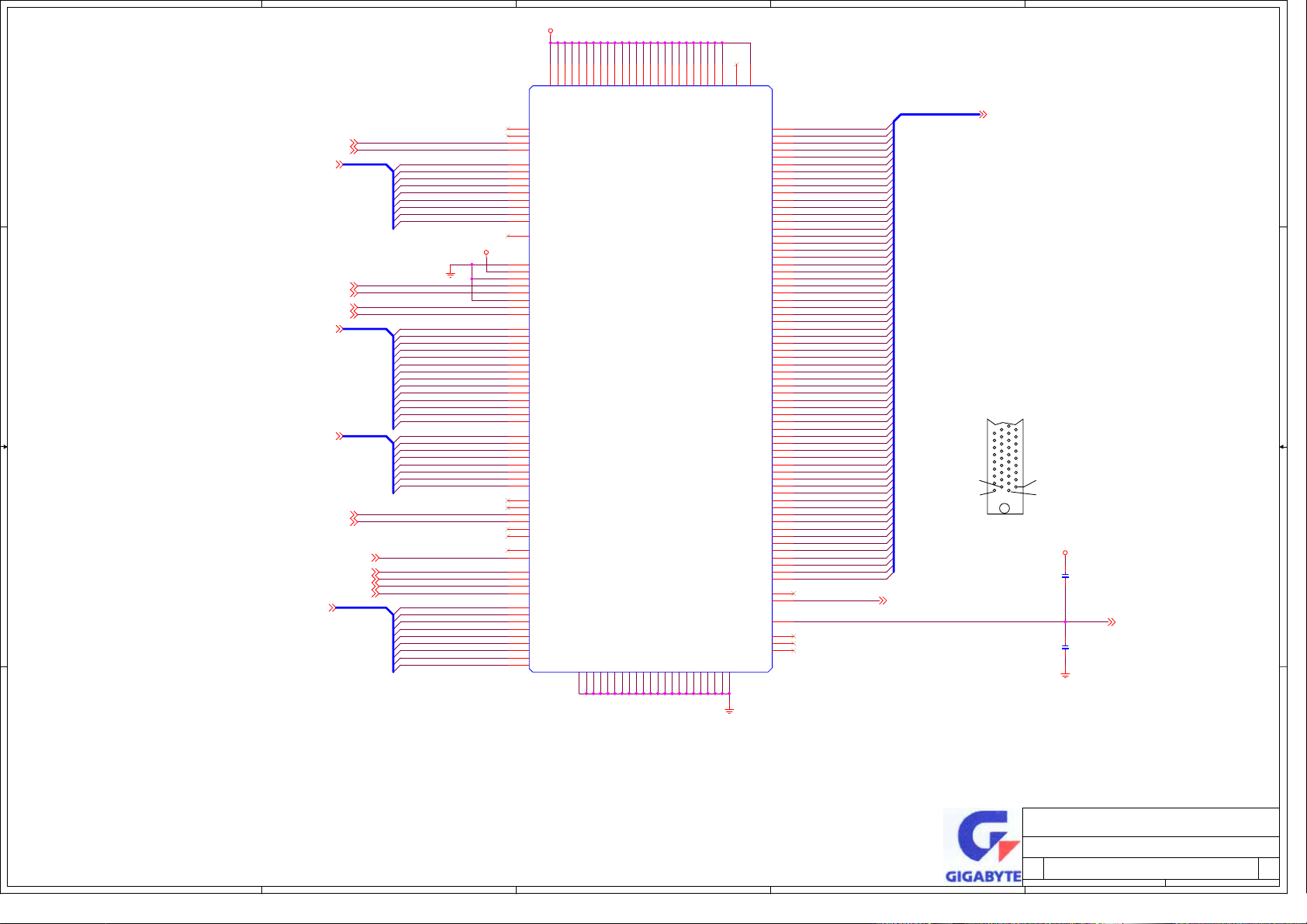

5

P0_VDD_2D5V

P0_VDD_2D5V

R94

C45

100/6/1

4 4

3 3

2 2

1 1

C46

0.1U/6

0.1U/6

V2.5_P0REF

3

C47

0.1U/6

2

GND

5

R97

100/6/1

GND GND

Close to CPU

VCC

84

U8A

+

V1.25_P0 P0_CPU_MEMVREF

1

-

LM2904

P0_MEMDATA[127..64]17

P0_MEMDQS_UPR[17..0]17

P0_MEMDQS_LWR[17..0]17

R93

42.2/6/1

42.2/6/1

R95

GND

R96

0/6

P0_VTT_SENSE11

4

C48

0.01U/6/X

P0_MEMDATA127

P0_MEMDATA126

P0_MEMDATA125

P0_MEMDATA124

P0_MEMDATA123

P0_MEMDATA122

P0_MEMDATA121

P0_MEMDATA120

P0_MEMDATA119

P0_MEMDATA118

P0_MEMDATA117

P0_MEMDATA116

P0_MEMDATA115

P0_MEMDATA114

P0_MEMDATA113

P0_MEMDATA112

P0_MEMDATA111

P0_MEMDATA110

P0_MEMDATA109

P0_MEMDATA108

P0_MEMDATA107

P0_MEMDATA106

P0_MEMDATA105

P0_MEMDATA104

P0_MEMDATA103

P0_MEMDATA102

P0_MEMDATA101

P0_MEMDATA100

P0_MEMDATA99

P0_MEMDATA98

P0_MEMDATA97

P0_MEMDATA96

P0_MEMDATA95

P0_MEMDATA94

P0_MEMDATA93

P0_MEMDATA92

P0_MEMDATA91

P0_MEMDATA90

P0_MEMDATA89

P0_MEMDATA88

P0_MEMDATA87

P0_MEMDATA86

P0_MEMDATA85

P0_MEMDATA84

P0_MEMDATA83

P0_MEMDATA82

P0_MEMDATA81

P0_MEMDATA80

P0_MEMDATA79

P0_MEMDATA78

P0_MEMDATA77

P0_MEMDATA76

P0_MEMDATA75

P0_MEMDATA74

P0_MEMDATA73

P0_MEMDATA72

P0_MEMDATA71

P0_MEMDATA70

P0_MEMDATA69

P0_MEMDATA68

P0_MEMDATA67

P0_MEMDATA66

P0_MEMDATA65

P0_MEMDATA64

P0_MEMDQS_UPR17

P0_MEMDQS_UPR16

P0_MEMDQS_UPR15

P0_MEMDQS_UPR14

P0_MEMDQS_UPR13

P0_MEMDQS_UPR12

P0_MEMDQS_UPR11

P0_MEMDQS_UPR10

P0_MEMDQS_UPR9

P0_MEMDQS_UPR8

P0_MEMDQS_UPR7

P0_MEMDQS_UPR6

P0_MEMDQS_UPR5

P0_MEMDQS_UPR4

P0_MEMDQS_UPR3

P0_MEMDQS_UPR2

P0_MEMDQS_UPR1

P0_MEMDQS_UPR0

P0_MEMDQS_LWR17

P0_MEMDQS_LWR16

P0_MEMDQS_LWR15

P0_MEMDQS_LWR14

P0_MEMDQS_LWR13

P0_MEMDQS_LWR12

P0_MEMDQS_LWR11

P0_MEMDQS_LWR10

P0_MEMDQS_LWR9

P0_MEMDQS_LWR8

P0_MEMDQS_LWR7

P0_MEMDQS_LWR6

P0_MEMDQS_LWR5

P0_MEMDQS_LWR4

P0_MEMDQS_LWR3

P0_MEMDQS_LWR2

P0_MEMDQS_LWR1

P0_MEMDQS_LWR0

4

P0_VTT_SENSE

>25 mils

>25 mils

C49

1000P/6/X

P0_VTT_DDR

AC19

AE19

AE18

AC18

AF19

AF17

AE16

AF22

AG24

AH25

AG26

AH27

AF23

AH24

AF25

AJ26

AG27

AF26

AF28

AE29

AJ29

AH29

AE27

AD26

AD27

AC26

AA26

AA28

AD28

AC27

AB29

AA27

AG25

AF27

AB27

AF24

AG28

AC28

AJ25

AJ30

AD29

AA31

AL25

AL29

AE31

J19

H19

F20

G19

F22

Y27

Y28

V28

U26

Y26

W27

V27

U27

P28

N29

M26

L28

P27

P26

M27

L27

K29

K27

H28

G29

L26

J28

H27

H26

F27

F26

D29

D27

G27

F28

E27

C27

C26

E25

D24

F23

E26

F25

E24

G23

R27

W29

N27

J27

E29

F24

R28

V26

M28

J26

E28

D25

U31

M30

H30

C30

B25

T31

Y29

M29

H29

C29

C25

VTT6

VTT7

VTT4

VTT3

VTT2

VTT1

VTT8

VTT9

VTT_SENSE

MEMZN

MEMZP

MEMVREF0

MEMVREF1

MEMDATA(127)

MEMDATA(126)

MEMDATA(125)

MEMDATA(124)

MEMDATA(123)

MEMDATA(122)

MEMDATA(121)

MEMDATA(120)

MEMDATA(119)

MEMDATA(118)

MEMDATA(117)

MEMDATA(116)

MEMDATA(115)

MEMDATA(114)

MEMDATA(113)

MEMDATA(112)

MEMDATA(111)

MEMDATA(110)

MEMDATA(109)

MEMDATA(108)

MEMDATA(107)

MEMDATA(106)

MEMDATA(105)

MEMDATA(104)

MEMDATA(103)

MEMDATA(102)

MEMDATA(101)

MEMDATA(100)

MEMDATA(99)

MEMDATA(98)

MEMDATA(97)

MEMDATA(96)

MEMDATA(95)

MEMDATA(94)

MEMDATA(93)

MEMDATA(92)

MEMDATA(91)

MEMDATA(90)

MEMDATA(89)

MEMDATA(88)

MEMDATA(87)

MEMDATA(86)

MEMDATA(85)

MEMDATA(84)

MEMDATA(83)

MEMDATA(82)

MEMDATA(81)

MEMDATA(80)

MEMDATA(79)

MEMDATA(78)

MEMDATA(77)

MEMDATA(76)

MEMDATA(75)

MEMDATA(74)

MEMDATA(73)

MEMDATA(72)

MEMDATA(71)

MEMDATA(70)

MEMDATA(69)

MEMDATA(68)

MEMDATA(67)

MEMDATA(66)

MEMDATA(65)

MEMDATA(64)

MEMDQS(35)

MEMDQS(34)

MEMDQS(33)

MEMDQS(32)

MEMDQS(31)

MEMDQS(30)

MEMDQS(29)

MEMDQS(28)

MEMDQS(27)

MEMDQS(26)

MEMDQS(25)

MEMDQS(24)

MEMDQS(23)

MEMDQS(22)

MEMDQS(21)

MEMDQS(20)

MEMDQS(19)

MEMDQS(18)

MEMDQS(17)

MEMDQS(16)

MEMDQS(15)

MEMDQS(14)

MEMDQS(13)

MEMDQS(12)

MEMDQS(11)

MEMDQS(10)

MEMDQS(9)

MEMDQS(8)

MEMDQS(7)

MEMDQS(6)

MEMDQS(5)

MEMDQS(4)

MEMDQS(3)

MEMDQS(2)

MEMDQS(1)

MEMDQS(0)

Opteron

U1B

MEMCLK_UP_H(3)

MEMCLK_UP_L(3)

MEMCLK_UP_H(2)

MEMCLK_UP_L(2)

MEMCLK_UP_H(1)

MEMCLK_UP_L(1)

MEMCLK_UP_H(0)

MEMCLK_UP_L(0)

MEMCLK_LO_H(3)

MEMCLK_LO_L(3)

MEMCLK_LO_H(2)

MEMCLK_LO_L(2)

MEMCLK_LO_H(1)

MEMCLK_LO_L(1)

MEMCLK_LO_H(0)

MEMCLK_LO_L(0)

MEMCHECK(15)

MEMCHECK(14)

MEMCHECK(13)

MEMCHECK(12)

MEMCHECK(11)

MEMCHECK(10)

MEMCKE_UP

MEMCKE_LO

RSVD_MA(15)

RSVD_MA(14)

MEMADD(13)

MEMADD(12)

MEMADD(11)

MEMADD(10)

MEMADD(9)

MEMADD(8)

MEMADD(7)

MEMADD(6)

MEMADD(5)

MEMADD(4)

MEMADD(3)

MEMADD(2)

MEMADD(1)

MEMADD(0)

MEMDATA(63)

MEMDATA(62)

MEMDATA(61)

MEMDATA(60)

MEMDATA(59)

MEMDATA(58)

MEMDATA(57)

MEMDATA(56)

MEMDATA(55)

MEMDATA(54)

MEMDATA(53)

MEMDATA(52)

MEMDATA(51)

MEMDATA(50)

MEMDATA(49)

MEMDATA(48)

MEMDATA(47)

MEMDATA(46)

MEMDATA(45)

MEMDATA(44)

MEMDATA(43)

MEMDATA(42)

MEMDATA(41)

MEMDATA(40)

MEMDATA(39)

MEMDATA(38)

MEMDATA(37)

MEMDATA(36)

MEMDATA(35)

MEMDATA(34)

MEMDATA(33)

MEMDATA(32)

MEMDATA(31)

MEMDATA(30)

MEMDATA(29)

MEMDATA(28)

MEMDATA(27)

MEMDATA(26)

MEMDATA(25)

MEMDATA(24)

MEMDATA(23)

MEMDATA(22)

MEMDATA(21)

MEMDATA(20)

MEMDATA(19)

MEMDATA(18)

MEMDATA(17)

MEMDATA(16)

MEMDATA(15)

MEMDATA(14)

MEMDATA(13)

MEMDATA(12)

MEMDATA(11)

MEMDATA(10)

MEMDATA(9)

MEMDATA(8)

MEMDATA(7)

MEMDATA(6)

MEMDATA(5)

MEMDATA(4)

MEMDATA(3)

MEMDATA(2)

MEMDATA(1)

MEMDATA(0)

MEMRESET_L

MEMBANK(1)

MEMBANK(0)

MEMRAS_L

MEMCAS_L

MEMWE_L

MEMCHECK(9)

MEMCHECK(8)

MEMCHECK(7)

MEMCHECK(6)

MEMCHECK(5)

MEMCHECK(4)

MEMCHECK(3)

MEMCHECK(2)

MEMCHECK(1)

MEMCHECK(0)

MEMCS_L(7)

MEMCS_L(6)

MEMCS_L(5)

MEMCS_L(4)

MEMCS_L(3)

MEMCS_L(2)

MEMCS_L(1)

MEMCS_L(0)

G20

G21

AE21

AE20

L24

L25

R23

T23

H23

J23

AD21

AD20

Y23

AA23

U25

U24

H24

H25

V23

M23

AE23

J24

J25

V24

K23

L23

K25

M25

M24

N25

N23

P23

T25

V25

AJ24

AK25

AK27

AJ27

AL24

AK24

AL26

AL27

AJ28

AK30

AJ31

AG29

AL28

AK28

AH31

AG30

AG31

AF30

AD31

AC30

AF29

AF31

AD30

AC29

AB31

AA29

Y31

W31

AC31

AA30

Y30

V29

P31

M31

L30

L29

P29

N31

L31

K31

J30

J29

G31

F29

J31

H31

F31

F30

D31

C31

B30

C28

E31

E30

A29

B28

B27

A26

C24

A24

A28

A27

A25

B24

G25

W25

W23

Y25

AA25

Y24

U28

T29

P24

P25

T27

R26

R25

R24

V30

U29

R30

P30

V31

U30

R29

R31

AD23

AE25

AD24

AD25

AC24

AC25

AB25

AA24

3

3

P0_MEMCLK_UPR_H3

P0_MEMCLK_UPR_L3

P0_MEMCLK_UPR_H2

P0_MEMCLK_UPR_L2

P0_MEMCLK_UPR_H1

P0_MEMCLK_UPR_L1

P0_MEMCLK_UPR_H0

P0_MEMCLK_UPR_L0

P0_MEMCLK_LWR_H3

P0_MEMCLK_LWR_L3

P0_MEMCLK_LWR_H2

P0_MEMCLK_LWR_L2

P0_MEMCLK_LWR_H1

P0_MEMCLK_LWR_L1

P0_MEMCLK_LWR_H0

P0_MEMCLK_LWR_L0

P0_MEMCKE_UPR

P0_MEMCKE_LWR

TP32

TP33

P0_MEMADD13

P0_MEMADD12

P0_MEMADD11

P0_MEMADD10

P0_MEMADD9

P0_MEMADD8

P0_MEMADD7

P0_MEMADD6

P0_MEMADD5

P0_MEMADD4

P0_MEMADD3

P0_MEMADD2

P0_MEMADD1

P0_MEMADD0

P0_MEMDATA63

P0_MEMDATA62

P0_MEMDATA61

P0_MEMDATA60

P0_MEMDATA59

P0_MEMDATA58

P0_MEMDATA57

P0_MEMDATA56

P0_MEMDATA55

P0_MEMDATA54

P0_MEMDATA53

P0_MEMDATA52

P0_MEMDATA51

P0_MEMDATA50

P0_MEMDATA49

P0_MEMDATA48

P0_MEMDATA47

P0_MEMDATA46

P0_MEMDATA45

P0_MEMDATA44

P0_MEMDATA43

P0_MEMDATA42

P0_MEMDATA41

P0_MEMDATA40

P0_MEMDATA39

P0_MEMDATA38

P0_MEMDATA37

P0_MEMDATA36

P0_MEMDATA35

P0_MEMDATA34

P0_MEMDATA33

P0_MEMDATA32

P0_MEMDATA31

P0_MEMDATA30

P0_MEMDATA29

P0_MEMDATA28

P0_MEMDATA27

P0_MEMDATA26

P0_MEMDATA25

P0_MEMDATA24

P0_MEMDATA23

P0_MEMDATA22

P0_MEMDATA21

P0_MEMDATA20

P0_MEMDATA19

P0_MEMDATA18

P0_MEMDATA17

P0_MEMDATA16

P0_MEMDATA15

P0_MEMDATA14

P0_MEMDATA13

P0_MEMDATA12

P0_MEMDATA11

P0_MEMDATA10

P0_MEMDATA9

P0_MEMDATA8

P0_MEMDATA7

P0_MEMDATA6

P0_MEMDATA5

P0_MEMDATA4

P0_MEMDATA3

P0_MEMDATA2

P0_MEMDATA1

P0_MEMDATA0

P0_MEMRESET_L

P0_MEMBANK1

P0_MEMBANK0

P0_MEMRAS_L

P0_MEMCAS_L

P0_MEMWE_L

P0_MEMCHECK_UPR7

P0_MEMCHECK_UPR6

P0_MEMCHECK_UPR5

P0_MEMCHECK_UPR4

P0_MEMCHECK_UPR3

P0_MEMCHECK_UPR2

P0_MEMCHECK_UPR1

P0_MEMCHECK_UPR0

P0_MEMCHECK_LWR7

P0_MEMCHECK_LWR6

P0_MEMCHECK_LWR5

P0_MEMCHECK_LWR4

P0_MEMCHECK_LWR3

P0_MEMCHECK_LWR2

P0_MEMCHECK_LWR1

P0_MEMCHECK_LWR0

P0_MEMCS_L7

P0_MEMCS_L6

P0_MEMCS_L5

P0_MEMCS_L4

P0_MEMCS_L3

P0_MEMCS_L2

P0_MEMCS_L1

P0_MEMCS_L0

TP125

1

TP126

1

TP127

1

TP128

1

P0_MEMCLK_UPR_H1 16,18

P0_MEMCLK_UPR_L1 16,18

P0_MEMCLK_UPR_H0 14,18

P0_MEMCLK_UPR_L0 14,18

TP129

1

TP130

1

TP131

1

TP132

1

P0_MEMCLK_LWR_H1 15,18

P0_MEMCLK_LWR_L1 15,18

P0_MEMCLK_LWR_H0 13,18

P0_MEMCLK_LWR_L0 13,18

P0_MEMCKE_UPR 18

P0_MEMCKE_LWR 18

P0_MEMADD[13..0] 18

P0_MEMDATA[63..0] 17

P0_MEMBANK1 18

P0_MEMBANK0 18

P0_MEMRAS_L 18

P0_MEMCAS_L 18

P0_MEMWE_L 18

P0_MEMCHECK_UPR[7..0] 17

P0_MEMCHECK_LWR[7..0] 17

P0_MEMCS_L[7..0] 18

2

P0_VDD_2D5V

R217

4.7K/6

GPIO1_MEMRST_2

3

Q66

D

GS

2N7002

2

1

GPIO2_MEMRST46GPIO1_MEMRST46

GND GND

SN74LVC2G08-2.5/DCT/IC8MSOP

GND

GND

U81

1

1A

2

1B

3

2Y

4 5

GND 2A

1

1A

2

1B

3

2Y

4 5

GND 2A

P0_MEMRESET_L

GPIO2_MEMRST_2

P1_MEMRST_AND

SN74LVC2G32-2.5/DCT/IC8MSOP

P0_MEMRST_AND

GPIO1_MEMRST_2

P1_MEMRESET_GPIO29,30,31,32

WORKAROUND:DELAY MEMRESET TIMING BY

GPIO

AMD DOC. ORDER#27510

2

P0_VDD_2D5V

R216

4.7K/6

GPIO2_MEMRST_2

3

Q106

D

GS

2N7002

2

1

P0_VDD_2D5V

8

VCC

P0_MEMRST_AND

7

1Y

GPIO2_MEMRST_2

6

2B

C362

0.1U/6

GND

P0_VDD_2D5V

U80

8

VCC

7

1Y

GPIO1_MEMRST_2

6

2B

P1_MEMRST_AND

C361

0.1U/6

GND

GIGABYTE THCHNOLOGIES , INC.

Title

Opteron P0 DDR Interface

Size Document Number Rev

C

Date: Sheet

1

P1_MEMRESET_L 28

P0_MEMRESET_GPIO 13,14,15,16

GA-7A8DRL

1

2.0

of

10 81Thursday, November 10, 2005

Page 12

+12V

12

R1333

2.2/8

C1381

12

4.7U/12

GND

144

VCC

2

EN

SS

RT

FB

12

R1334

30K/6/1

3

D

1

13

OCSET

VCCCOMP

PVCC

UGATE

PHASE

GND

7

GND

P0_VDD_2D5V_SS

Q162

2N7002

SOT23

VCC

84

5

+

6

-

P0_VDD_2D5V_SS

C13840.01U/6

12

VCC_DUAL

R1296

1K/6

P0_VDD2D5V_VTT_EN_L

Q163

P0_VDD2D5V_VTT_EN61

R1297

10K/6

R1584

5.1K/6

GND

MMBT2222A/SOT23

132

GND

P0_VDD_2D5V

R121

100/6/1

C72

0.1U/6

R123

100/6/1

GND

C1391

0.1U/6

GND

C1383 33P/6

1 2

1 2

C71

0.1U/6

C73

0.1U/6

6

3

1

5

R133620K/6/1

GS

VP0_REF

U127

BOOT

LGATE

PGND

ISL6522CB

U8B

LM2904

C70

0.1U/6

7

2

10

9

8

12

11

C1392 1000P/6

R1351 2K/6

GND

C74

0.01U/6

+12V

R1716

2.2/8

12

1N5817/S

D66

C1382

0.1U/6

1 2

R1335 1/8/B

Q173

NEC2SK3639/TO252

R1338 0/8/B

GND

P0_DIMM_MEMVREF

C75

1000P/6

GND

NEC2SK3638/TO252

Q170

12

12

G

S D

GND

P0_VTT_SENSE10

P0_DIMM_MEMVREF13,14,15,16

+12V

L29

1UH/D/Vertical

VCC25_IN

G

S D

Q188

NEC2SK3639/TO252

1N5817/S

D84

R1711 0/8/B

1 2

GND

P0_VTT_SENSE

20 mils

P0_DIMM_MEMVREF

GND

1000U/6.3V/8X11.5/KZG

P0_DIMM_MEMVREF 13,14,15,16

GND

EC16

390uF/6.3V/PS-CON/8*12.5 12m_Ohm

560uF/4V/PSCON/8*11.5

330U/16V/10*10.5/FPCAP

S D

GND

P0_VTT_DDR

+

GND

12

C1379

GND

R1717

2.2/8

C1679

1000P/6

GND

sense from CAP Gnd pin

C63

0.1U/6

GND

12

C62

0.1U/6

12

C1378

0.1U/6/16V

G

R114

100/6

R116

100/6/X

12

C1380

GND

330U/16V/10*10.5/FPCAP

EC21

L3

3.3UH/3A/SMALL

VCCQ

GND

GND

L30

2.8UH/D/Vertical/MPP

EC23

+

GND

560uF/4V/8*11.5/FPCAP

C64

0.1U/6

GND

P0_VDD2D5V_VTT_EN_L

1000P/6

4700mA @105_Deg / 100Khz

5230mA @105_Deg / 100Khz10m_Ohm

EC25

EC24

+

+

GND

GND

560uF/4V/8*11.5/FPCAP

P0_VDD_2D5V

C65

0.1U/6

C69

GND

560uF/4V/8*11.5/FPCAP

560uF/4V/8*11.5/FPCAP

U10

1

VCC1

2

VDD1

3

VL1

4

PGND1

5

AGND1

6

SD

7

2/VCC

8 9

G-sense AGND3

CM8500AGIT

+

GNDGND

17

GND

PGND2

AGND4

EC146

+

GND GND

560uF/4V/8*11.5/FPCAP

16

VCC2

15

VDD2

14

VL2

13

12

11

FB

10

VCCQ

GND

2.6V/10A

P0_VDD_2D5V

EC147

R138

0/6

+

12

R1337

2.7K/6/1

560uF/4V/8*11.5/FPCAP

12

R1339

1.2K/6/1

GND

NEAR ISL6522

P0_VDD_2D5V

C67

C66

0.1U/6

P0_VDD_2D5V

0.1U/6

C6

GND

1000P/6

Title

Size Document Number Rev

Custom

Date: Sheet

+

0.1U/6

GND

R119

10K/6

R120

470K/6

C68

GIGABYTE THCHNOLOGIES , INC.

Opteron P0 DDR Power

0/6/X

R208

VCC3

EC19

100uF/25V/6*11

R1346

2K/6

P0_VDDIOFB_H 8

R144

0/8

R117

5R1/8

VCCQ

12

12

C1

C3

10U/12

10U/12

GND

GA-7A8DRL

P0_VDDIO_SENSE 8

P0_VDD_2D5V

+

GND

R142

0/8/X

1000U/6.3V/8X11.5/KZG

EC15

of

11 81Thursday, November 10, 2005

2.0

Page 13

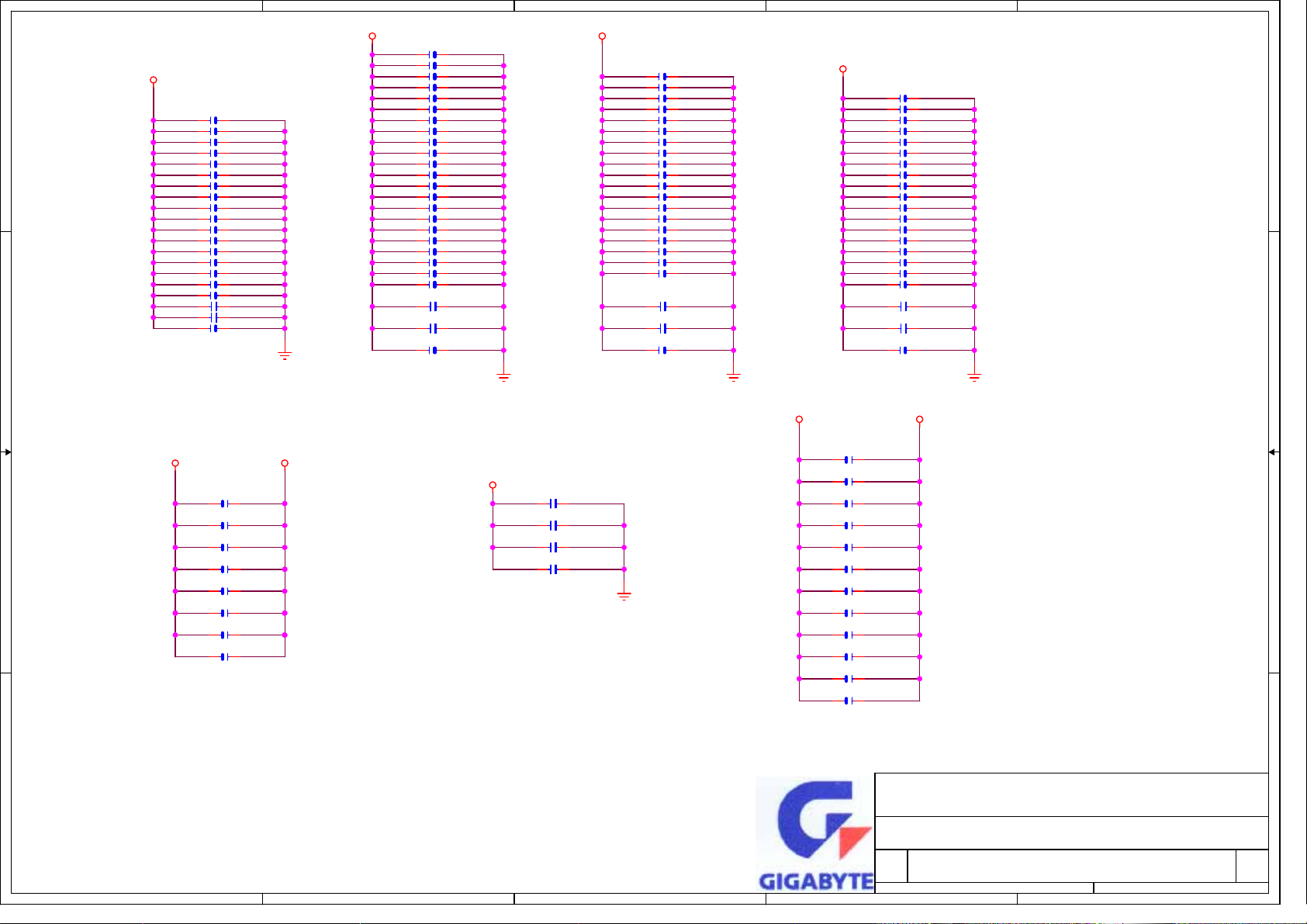

5

P0_VTT_DDR

D D

C C

C436 0.1U/6

C438 0.1U/6

C437 0.1U/6

C439 0.1U/6

C441 0.1U/6

C440 0.1U/6

C442 0.1U/6

C444 0.1U/6

C443 0.1U/6

C450 0.1U/6

C446 0.1U/6

C445 0.1U/6

C447 0.1U/6

C449 0.1U/6

C448 0.1U/6

C453 0.1U/6

C451 0.1U/6

C80 1U/6

C84 1U/6

C1361 10U/12

GND

4

P0_VTT_DDR

C618 0.1U/6

C523 0.1U/6

C521 0.1U/6

C520 0.1U/6/B

C42 0.1U/6/B

C334 0.1U/6/B

C457 0.1U/6

C458 0.1U/6

C459 0.1U/6

C460 0.1U/6

C461 0.1U/6

C462 0.1U/6

C463 0.1U/6

C464 0.1U/6

C465 0.1U/6

C466 0.1U/6

C467 0.1U/6

C541 0.1U/6

C579 0.1U/6

C655 0.1U/6/B

C656 0.1U/6/B

C657 0.1U/6/B

C1362 10U/12

C81 1U/6

C85 1U/6

3

2

P0_VTT_DDR

C660 0.1U/6/B

C658 0.1U/6/B

C659 0.1U/6/B

C668 0.1U/6/B

C667 0.1U/6/B

C664 0.1U/6/B

C669 0.1U/6/B

C661 0.1U/6/B

C670 0.1U/6/B

C662 0.1U/6/B

C671 0.1U/6/B

C665 0.1U/6/B

C666 0.1U/6/B

C663 0.1U/6/B

C672 0.1U/6/B

C673 0.1U/6/B

C674 0.1U/6/B

C676 0.1U/6

C675 0.1U/6/B

C82 1U/6

C86 1U/6

C1363 10U/12

GND GND GND

P0_VTT_DDR

C688 0.1U/6/B

C687 0.1U/6/B

C686 0.1U/6/B

C685 0.1U/6/B

C690 0.1U/6/B

C454 0.1U/6/B

C452 0.1U/6/B

C455 0.1U/6/B

C456 0.1U/6/B

C677 0.1U/6/B

C678 0.1U/6/B

C679 0.1U/6/B

C680 0.1U/6/B

C684 0.1U/6/B

C683 0.1U/6/B

C681 0.1U/6/B

C682 0.1U/6/B

C689 0.1U/6/B

C1364 10U/12

C83 1U/6

C87 1U/6

1

P0_VTT_DDR P0_VDD_2D5V

P0_VTT_DDR P0_VDD_2D5V

P0_VTT_DDR

C225 0.01U/6

C222 0.01U/6

C223 0.01U/6

B B

C224 0.01U/6

C76 0.015uF/6/B

C77 0.015uF/6/B

C78 0.015uF/6

C79 0.015uF/6

C227 0.01U/6

C639 0.01U/6

GND

C877 0.01U/6

C878 0.01U/6

C945 0.01U/6/B

C889 0.01U/6/B

C883 0.01U/6/B

C888 0.01U/6/B

C882 0.01U/6/B

C884 0.01U/6/B

C886 0.01U/6/B

C959 0.01U/6/B

C887 0.01U/6/B

C958 0.01U/6/B

C957 0.01U/6/B

C885 0.01U/6/B

A A

GIGABYTE THCHNOLOGIES , INC.

Title

Opteron P0 VTT/VDDIO Decoupling

Size Document Number Rev

A4

5

4

3

Date: Sheet

2

GA-7A8DRL

of

12 81Thursday, November 10, 2005

1

2.0

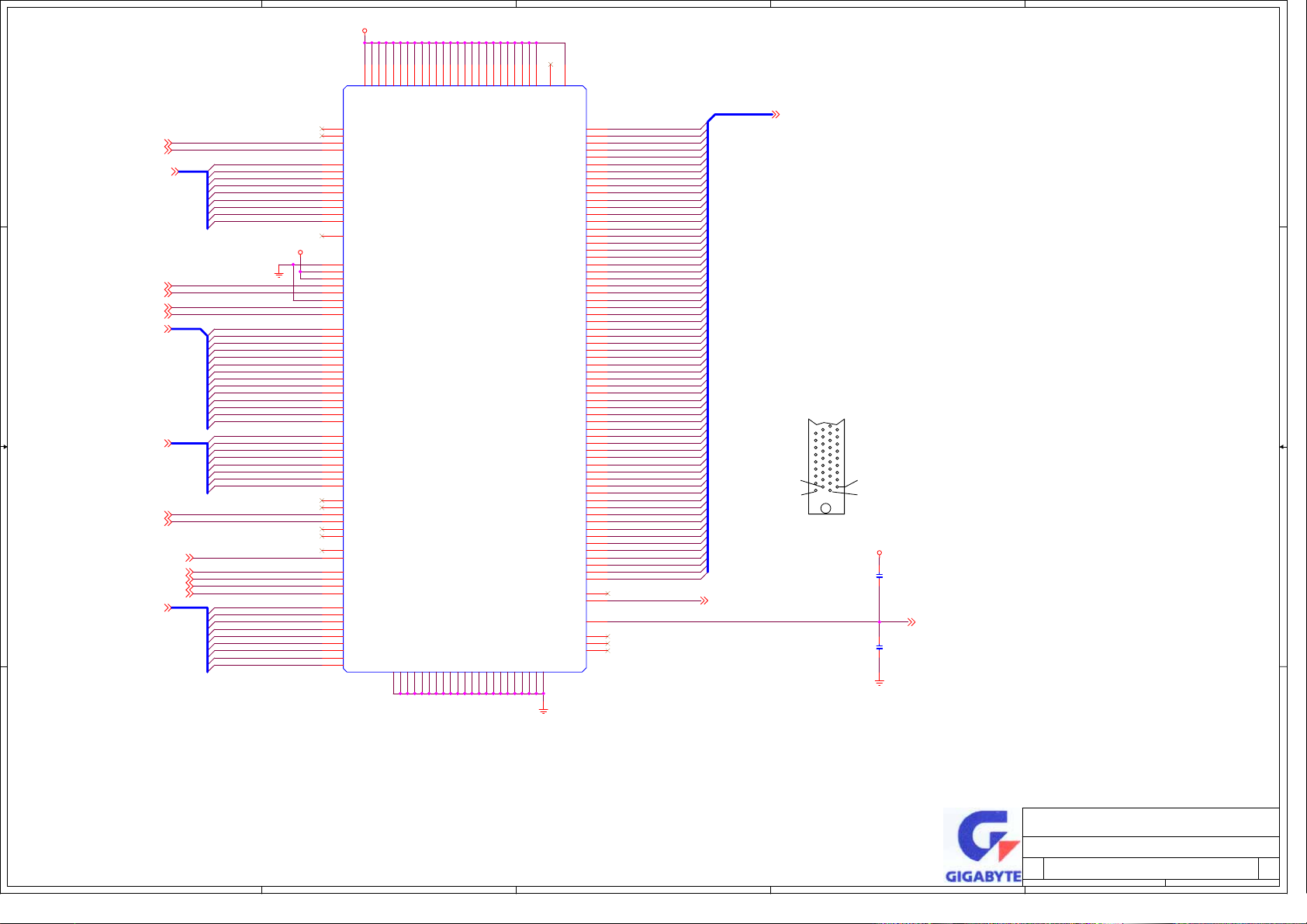

Page 14

5

4

3

2

1

DIMM0

P0_VDD_2D5V

D D

738467085

108

120

148

1688222

30

54627796104

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

163

CS3#

71

P0_SR_MEMCS_L114,18

P0_SR_MEMDQS_LWR[8..0]15,17

C C

P0_SR_MEMBANK114,15,16,18

P0_SR_MEMBANK014,15,16,18

P0_SR_MEMADD[13..0]14,15,16,18

P0_SR_MEMCHECK_LWR[7..0]15,17

B B

P0_MEMCLK_LWR_H010,18

P0_MEMCLK_LWR_L010,18

P0_MEMRESET_GPIO10,14,15,16

P0_SR_MEMCKE_LWR14,15,16,18

P0_SR_MEMCKE_UPR14,15,16,18

P0_SR_MEMCAS_L14,15,16,18

P0_SR_MEMRAS_L14,15,16,18

P0_SR_MEMDQS_LWR[17..9]15,17

P0_SR_MEMCS_L014,18

RCC_SDA14,15,16,29,30,31,32,57,75

RCC_SCL14,15,16,29,30,31,32,57,75

P0_SR_MEMCS_L1

P0_SR_MEMCS_L0

P0_SR_MEMDQS_LWR8

P0_SR_MEMDQS_LWR7

P0_SR_MEMDQS_LWR6

P0_SR_MEMDQS_LWR5

P0_SR_MEMDQS_LWR4

P0_SR_MEMDQS_LWR3

P0_SR_MEMDQS_LWR2

P0_SR_MEMDQS_LWR1

P0_SR_MEMDQS_LWR0

RCC_SDA

RCC_SCL

P0_SR_MEMBANK1

P0_SR_MEMBANK0

P0_SR_MEMADD13

P0_SR_MEMADD12

P0_SR_MEMADD11

P0_SR_MEMADD10

P0_SR_MEMADD9

P0_SR_MEMADD8

P0_SR_MEMADD7

P0_SR_MEMADD6

P0_SR_MEMADD5

P0_SR_MEMADD4

P0_SR_MEMADD3

P0_SR_MEMADD2

P0_SR_MEMADD1

P0_SR_MEMADD0

P0_SR_MEMCHECK_LWR7

P0_SR_MEMCHECK_LWR6

P0_SR_MEMCHECK_LWR5

P0_SR_MEMCHECK_LWR4

P0_SR_MEMCHECK_LWR3

P0_SR_MEMCHECK_LWR2

P0_SR_MEMCHECK_LWR1

P0_SR_MEMCHECK_LWR0

P0_MEMCLK_LWR_H0

P0_MEMCLK_LWR_L0

P0_MEMRESET_GPIO

P0_SR_MEMDQS_LWR17

P0_SR_MEMDQS_LWR16

P0_SR_MEMDQS_LWR15

P0_SR_MEMDQS_LWR14

P0_SR_MEMDQS_LWR13

P0_SR_MEMDQS_LWR12

P0_SR_MEMDQS_LWR11

P0_SR_MEMDQS_LWR10

P0_SR_MEMDQS_LWR9

GND

P0_SR_MEMCKE_LWR

P0_SR_MEMCKE_UPR

P0_SR_MEMCAS_L

P0_SR_MEMRAS_L

158

157

47

86

78

67

56

36

25

14

5

103

183

182

181

91

92

113

52

59

167

115

118

141

27

122

29

125

32

37

130

41

43

48

144

142

135

134

51

49

45

44

16

17

137

138

76

75

173

10

21

111

65

154

140

177

169

159

149

129

119

107

97

CS2#

CS1#

CS0#

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

FETEN

SA2

SA1

SA0

SDA

SCL

BA2

BA1

BA0

A13

A12

A11

A10_AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0

CK0#

CK1

CK1#

CK2

CK2#

NC5

NC1_RESET#

CKE0

CKE1

CAS#

RAS#

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

GND

GND

10011116

GND

GND

GND

GND

GND

GND

GND

124

132

139

145

152

160

143

156

164

172

180

136

VDDQ9

GND

VDDQ10

VDDQ11

GND

GND

VDDQ12

VDDQ13

GND

GND

15

VDDQ14

GND

112

128

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

GND

GND

GND

GND

GND

17618263344250586674818993

VDDQ15

GND

GND

VDDID

184

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

WP

WE#

VREF

NC4

NC2

NC3

P0DIMM0

DDR-DIMM184/ORINGE

P0_SR_MEMDATA63

179

P0_SR_MEMDATA62

178

P0_SR_MEMDATA61

175

P0_SR_MEMDATA60

174

P0_SR_MEMDATA59

88

P0_SR_MEMDATA58

87

P0_SR_MEMDATA57

84

P0_SR_MEMDATA56

83

P0_SR_MEMDATA55

171

P0_SR_MEMDATA54

170

P0_SR_MEMDATA53

166

P0_SR_MEMDATA52

165

P0_SR_MEMDATA51

80

P0_SR_MEMDATA50

79

P0_SR_MEMDATA49

73

P0_SR_MEMDATA48

72

P0_SR_MEMDATA47

162

P0_SR_MEMDATA46

161

P0_SR_MEMDATA45

155

P0_SR_MEMDATA44

153

P0_SR_MEMDATA43

69

P0_SR_MEMDATA42

68

P0_SR_MEMDATA41

64

P0_SR_MEMDATA40

61

P0_SR_MEMDATA39

151

P0_SR_MEMDATA38

150

P0_SR_MEMDATA37

147

P0_SR_MEMDATA36

146

P0_SR_MEMDATA35

60

P0_SR_MEMDATA34

57

P0_SR_MEMDATA33

55

P0_SR_MEMDATA32

53

P0_SR_MEMDATA31

133

P0_SR_MEMDATA30

131

P0_SR_MEMDATA29

127

P0_SR_MEMDATA28

126

P0_SR_MEMDATA27

40

P0_SR_MEMDATA26

39

P0_SR_MEMDATA25

35

P0_SR_MEMDATA24

33

P0_SR_MEMDATA23

123

P0_SR_MEMDATA22

121

P0_SR_MEMDATA21

117

P0_SR_MEMDATA20

114

P0_SR_MEMDATA19

31

P0_SR_MEMDATA18

28

P0_SR_MEMDATA17

24

P0_SR_MEMDATA16

23

P0_SR_MEMDATA15

110

P0_SR_MEMDATA14

109

P0_SR_MEMDATA13

106

P0_SR_MEMDATA12

105

P0_SR_MEMDATA11

20

P0_SR_MEMDATA10

19

P0_SR_MEMDATA9

13

P0_SR_MEMDATA8

12

P0_SR_MEMDATA7

99

P0_SR_MEMDATA6

98

P0_SR_MEMDATA5

95

P0_SR_MEMDATA4

94

P0_SR_MEMDATA3

8

P0_SR_MEMDATA2

6

P0_SR_MEMDATA1

4

P0_SR_MEMDATA0

2

90

P0_SR_MEMWE_L

63

P0_DIMM_MEMVREF

1

102

9

101

P0_SR_MEMWE_L 14,15,16,18

P0_SR_MEMDATA[63..0] 15,17

94

93

P0_VDD_2D5V

C88

0.1U/6

P0_DIMM_MEMVREF 11,14,15,16

C89

0.1U/6

GND

21

A A

smbus addr = 0 0 0

5

4

GND

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

3

2

Date: Sheet

Opteron P0 DIMM 0

Custom

GA-7A8DRL

1

2.0

of

13 81Thursday, November 10, 2005

Page 15

5

DIMM1

P0_VDD_2D5V

4

3

2

1

VDDID

184

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

WP

WE#

VREF

NC4

NC2

NC3

P0DIMM1

DDR-DIMM184/PURPLE

P0_SR_MEMDATA127

179

P0_SR_MEMDATA126

178

P0_SR_MEMDATA125

175

P0_SR_MEMDATA124

174

P0_SR_MEMDATA123

88

P0_SR_MEMDATA122

87

P0_SR_MEMDATA121

84

P0_SR_MEMDATA120

83

P0_SR_MEMDATA119

171

P0_SR_MEMDATA118

170

P0_SR_MEMDATA117

166

P0_SR_MEMDATA116

165

P0_SR_MEMDATA115

80

P0_SR_MEMDATA114

79

P0_SR_MEMDATA113

73

P0_SR_MEMDATA112

72

P0_SR_MEMDATA111

162

P0_SR_MEMDATA110

161

P0_SR_MEMDATA109

155

P0_SR_MEMDATA108

153

P0_SR_MEMDATA107

69

P0_SR_MEMDATA106

68

P0_SR_MEMDATA105

64

P0_SR_MEMDATA104

61

P0_SR_MEMDATA103

151

P0_SR_MEMDATA102

150

P0_SR_MEMDATA101

147

P0_SR_MEMDATA100

146

P0_SR_MEMDATA99

60

P0_SR_MEMDATA98

57

P0_SR_MEMDATA97

55

P0_SR_MEMDATA96

53

P0_SR_MEMDATA95

133

P0_SR_MEMDATA94

131

P0_SR_MEMDATA93

127

P0_SR_MEMDATA92

126

P0_SR_MEMDATA91

40

P0_SR_MEMDATA90

39

P0_SR_MEMDATA89

35

P0_SR_MEMDATA88

33

P0_SR_MEMDATA87

123

P0_SR_MEMDATA86

121

P0_SR_MEMDATA85

117

P0_SR_MEMDATA84

114

P0_SR_MEMDATA83

31

P0_SR_MEMDATA82

28

P0_SR_MEMDATA81

24

P0_SR_MEMDATA80

23

P0_SR_MEMDATA79

110

P0_SR_MEMDATA78

109

P0_SR_MEMDATA77

106

P0_SR_MEMDATA76

105

P0_SR_MEMDATA75

20

P0_SR_MEMDATA74

19

P0_SR_MEMDATA73

13

P0_SR_MEMDATA72

12

P0_SR_MEMDATA71

99

P0_SR_MEMDATA70

98

P0_SR_MEMDATA69

95

P0_SR_MEMDATA68

94

P0_SR_MEMDATA67

8

P0_SR_MEMDATA66

6

P0_SR_MEMDATA65

4

P0_SR_MEMDATA64

2

90

P0_SR_MEMWE_L

63

P0_DIMM_MEMVREF

1

102

9

101

P0_SR_MEMDATA[127..64] 16,17

P0_SR_MEMWE_L 13,15,16,18

94

93

P0_VDD_2D5V

GND

2

1

C90

0.1U/6

P0_DIMM_MEMVREF 11,13,15,16

C91

0.1U/6

738467085

108

120

148

1688222

30

54627796104

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

GND

GND

VDDQ2

GND

GND

GND

GND

GND

124

132

139

145

152

160

D D

P0_SR_MEMCS_L113,18

P0_SR_MEMDQS_UPR[8..0]16,17

C C

P0_SR_MEMCHECK_UPR[7..0]16,17

P0_MEMCLK_UPR_H010,18

P0_MEMCLK_UPR_L010,18

B B

P0_SR_MEMDQS_UPR[17..9]16,17

P0_SR_MEMCS_L013,18

RCC_SDA13,15,16,29,30,31,32,57,75

RCC_SCL13,15,16,29,30,31,32,57,75

P0_SR_MEMBANK113,15,16,18

P0_SR_MEMBANK013,15,16,18

P0_SR_MEMADD[13..0]13,15,16,18

P0_MEMRESET_GPIO10,13,15,16

P0_SR_MEMCKE_LWR13,15,16,18

P0_SR_MEMCKE_UPR13,15,16,18

P0_SR_MEMCAS_L13,15,16,18

P0_SR_MEMRAS_L13,15,16,18

P0_SR_MEMCS_L1

P0_SR_MEMCS_L0

P0_SR_MEMDQS_UPR8

P0_SR_MEMDQS_UPR7

P0_SR_MEMDQS_UPR6

P0_SR_MEMDQS_UPR5

P0_SR_MEMDQS_UPR4

P0_SR_MEMDQS_UPR3

P0_SR_MEMDQS_UPR2

P0_SR_MEMDQS_UPR1

P0_SR_MEMDQS_UPR0

P0_VDD_2D5V

RCC_SDA

RCC_SCL

P0_SR_MEMBANK1

P0_SR_MEMBANK0

P0_SR_MEMCHECK_UPR7

P0_SR_MEMCHECK_UPR6

P0_SR_MEMCHECK_UPR5

P0_SR_MEMCHECK_UPR4

P0_SR_MEMCHECK_UPR3

P0_SR_MEMCHECK_UPR2

P0_SR_MEMCHECK_UPR1

P0_SR_MEMCHECK_UPR0

P0_MEMCLK_UPR_H0

P0_MEMCLK_UPR_L0

P0_SR_MEMDQS_UPR17

P0_SR_MEMDQS_UPR16

P0_SR_MEMDQS_UPR15

P0_SR_MEMDQS_UPR14

P0_SR_MEMDQS_UPR13

P0_SR_MEMDQS_UPR12

P0_SR_MEMDQS_UPR11

P0_SR_MEMDQS_UPR10

P0_SR_MEMDQS_UPR9

GND

P0_SR_MEMADD13

P0_SR_MEMADD12

P0_SR_MEMADD11

P0_SR_MEMADD10

P0_SR_MEMADD9

P0_SR_MEMADD8

P0_SR_MEMADD7

P0_SR_MEMADD6

P0_SR_MEMADD5

P0_SR_MEMADD4

P0_SR_MEMADD3

P0_SR_MEMADD2

P0_SR_MEMADD1

P0_SR_MEMADD0

P0_MEMRESET_GPIO

P0_SR_MEMCKE_LWR

P0_SR_MEMCKE_UPR

P0_SR_MEMCAS_L

P0_SR_MEMRAS_L

163

71

158

157

47

86

78

67

56

36

25

14

5

103

183

182

181

91

92

113

52

59

167

115

118

141

27

122

29

125

32

37

130

41

43

48

144

142

135

134

51

49

45

44

16

17

137

138

76

75

173

10

21

111

65

154

140

177

169

159

149

129

119

107

97

CS3#

CS2#

CS1#

CS0#

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

FETEN

SA2

SA1

SA0

SDA

SCL

BA2

BA1

BA0

A13

A12

A11

A10_AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0

CK0#

CK1

CK1#

CK2

CK2#

NC5

NC1_RESET#

CKE0

CKE1

CAS#

RAS#

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

GND

10011116

143

156

164

172

128

VDDQ8

GND

136

VDDQ9

GND

VDDQ10

VDDQ11

GND

GND

180

VDDQ12

VDDQ13

GND

GND

112

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

GND

GND

GND

GND

GND

17618263344250586674818993

15

VDDQ14

VDDQ15

GND

GND

GND

GND

smbus addr = 0 0 1

A A

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

Opteron P0 DIMM 1

Custom

GA-7A8DRL

1

2.0

of

14 81Thursday, November 10, 2005

Page 16

5

4

DIMM2

P0_VDD_2D5V

3

2

1

VDDID

GND

P0DIMM2

184

DDR-DIMM184/ORINGE

VDDSPD

179

DQ63

178

DQ62

175

DQ61

174

DQ60

88

DQ59

87

DQ58

84

DQ57

83

DQ56

171

DQ55

170

DQ54

166

DQ53

165

DQ52

80

DQ51

79

DQ50

73

DQ49

72

DQ48

162

DQ47

161

DQ46

155

DQ45

153

DQ44

69

DQ43

68

DQ42

64

DQ41

61

DQ40

151

DQ39

150

DQ38

147

DQ37

146

DQ36

60

DQ35

57

DQ34

55

DQ33

53

DQ32

133

DQ31

131

DQ30

127

DQ29

126

DQ28

40

DQ27

39

DQ26

35

DQ25

33

DQ24

123

DQ23

121

DQ22

117

DQ21

114

DQ20

31

DQ19

28

DQ18

24

DQ17

23

DQ16

110

DQ15

109

DQ14

106

DQ13

105

DQ12

20

DQ11

19

DQ10

13

DQ9

12

DQ8

99

DQ7

98

DQ6

95

DQ5

94

DQ4

8

DQ3

6

DQ2

4

DQ1

2

DQ0

90

WP

63

WE#

1

VREF

102

NC4

9

NC2

101

NC3

P0_SR_MEMDATA63

P0_SR_MEMDATA62

P0_SR_MEMDATA61

P0_SR_MEMDATA60

P0_SR_MEMDATA59

P0_SR_MEMDATA58

P0_SR_MEMDATA57

P0_SR_MEMDATA56

P0_SR_MEMDATA55

P0_SR_MEMDATA54

P0_SR_MEMDATA53

P0_SR_MEMDATA52

P0_SR_MEMDATA51

P0_SR_MEMDATA50

P0_SR_MEMDATA49

P0_SR_MEMDATA48

P0_SR_MEMDATA47

P0_SR_MEMDATA46

P0_SR_MEMDATA45

P0_SR_MEMDATA44

P0_SR_MEMDATA43

P0_SR_MEMDATA42

P0_SR_MEMDATA41

P0_SR_MEMDATA40

P0_SR_MEMDATA39

P0_SR_MEMDATA38

P0_SR_MEMDATA37

P0_SR_MEMDATA36

P0_SR_MEMDATA35

P0_SR_MEMDATA34

P0_SR_MEMDATA33

P0_SR_MEMDATA32

P0_SR_MEMDATA31

P0_SR_MEMDATA30

P0_SR_MEMDATA29

P0_SR_MEMDATA28

P0_SR_MEMDATA27

P0_SR_MEMDATA26

P0_SR_MEMDATA25

P0_SR_MEMDATA24

P0_SR_MEMDATA23

P0_SR_MEMDATA22

P0_SR_MEMDATA21

P0_SR_MEMDATA20

P0_SR_MEMDATA19

P0_SR_MEMDATA18

P0_SR_MEMDATA17

P0_SR_MEMDATA16

P0_SR_MEMDATA15

P0_SR_MEMDATA14

P0_SR_MEMDATA13

P0_SR_MEMDATA12

P0_SR_MEMDATA11

P0_SR_MEMDATA10

P0_SR_MEMDATA9

P0_SR_MEMDATA8

P0_SR_MEMDATA7

P0_SR_MEMDATA6

P0_SR_MEMDATA5

P0_SR_MEMDATA4

P0_SR_MEMDATA3

P0_SR_MEMDATA2

P0_SR_MEMDATA1

P0_SR_MEMDATA0

P0_SR_MEMWE_L

P0_DIMM_MEMVREF

P0_SR_MEMWE_L 13,14,16,18

P0_SR_MEMDATA[63..0] 13,17

94

93

2

1

P0_VDD_2D5V

GND

C92

0.1U/6

P0_DIMM_MEMVREF 11,13,14,16

C93

0.1U/6

738467085

108

120

148

1688222

30

54627796104

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

GND

VDDQ3

GND

GND

GND

GND

GND

GND

124

132

139

145

152

160

D D

P0_SR_MEMCS_L316,18

P0_SR_MEMCS_L216,18

P0_SR_MEMDQS_LWR[8..0]13,17

RCC_SDA13,14,16,29,30,31,32,57,75

RCC_SCL13,14,16,29,30,31,32,57,75

P0_SR_MEMBANK113,14,16,18

P0_SR_MEMBANK013,14,16,18

C C

B B

P0_SR_MEMADD[13..0]13,14,16,18

P0_SR_MEMCHECK_LWR[7..0]13,17

P0_MEMCLK_LWR_H110,18

P0_MEMCLK_LWR_L110,18

P0_MEMRESET_GPIO10,13,14,16

P0_SR_MEMCKE_LWR13,14,16,18

P0_SR_MEMCKE_UPR13,14,16,18

P0_SR_MEMCAS_L13,14,16,18

P0_SR_MEMDQS_LWR[17..9]13,17

P0_SR_MEMRAS_L13,14,16,18

P0_SR_MEMCS_L3

P0_SR_MEMCS_L2

P0_SR_MEMDQS_LWR8

P0_SR_MEMDQS_LWR7

P0_SR_MEMDQS_LWR6

P0_SR_MEMDQS_LWR5

P0_SR_MEMDQS_LWR4

P0_SR_MEMDQS_LWR3

P0_SR_MEMDQS_LWR2

P0_SR_MEMDQS_LWR1

P0_SR_MEMDQS_LWR0

GND

RCC_SDA

RCC_SCL

P0_SR_MEMBANK1

P0_SR_MEMBANK0

P0_SR_MEMADD13

P0_SR_MEMADD12

P0_SR_MEMADD11

P0_SR_MEMADD10

P0_SR_MEMADD9

P0_SR_MEMADD8

P0_SR_MEMADD7

P0_SR_MEMADD6

P0_SR_MEMADD5

P0_SR_MEMADD4

P0_SR_MEMADD3

P0_SR_MEMADD2

P0_SR_MEMADD1

P0_SR_MEMADD0

P0_SR_MEMCHECK_LWR7

P0_SR_MEMCHECK_LWR6

P0_SR_MEMCHECK_LWR5

P0_SR_MEMCHECK_LWR4

P0_SR_MEMCHECK_LWR3

P0_SR_MEMCHECK_LWR2

P0_SR_MEMCHECK_LWR1

P0_SR_MEMCHECK_LWR0

P0_MEMCLK_LWR_H1

P0_MEMCLK_LWR_L1

P0_MEMRESET_GPIO

P0_SR_MEMCKE_LWR

P0_SR_MEMCKE_UPR

P0_SR_MEMCAS_L

P0_SR_MEMRAS_L

P0_SR_MEMDQS_LWR17

P0_SR_MEMDQS_LWR16

P0_SR_MEMDQS_LWR15

P0_SR_MEMDQS_LWR14

P0_SR_MEMDQS_LWR13

P0_SR_MEMDQS_LWR12

P0_SR_MEMDQS_LWR11

P0_SR_MEMDQS_LWR10

P0_SR_MEMDQS_LWR9

P0_VDD_2D5V

163

71

158

157

47

86

78

67

56

36

25

14

5

103

183

182

181

91

92

113

52

59

167

115

118

141

27

122

29

125

32

37

130

41

43

48

144

142

135

134

51

49

45

44

16

17

137

138

76

75

173

10

21

111

65

154

140

177

169

159

149

129

119

107

97

CS3#

CS2#

CS1#

CS0#

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

FETEN

SA2

SA1

SA0

SDA

SCL

BA2

BA1

BA0

A13

A12

A11

A10_AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0

CK0#

CK1

CK1#

CK2

CK2#

NC5

NC1_RESET#

CKE0

CKE1

CAS#

RAS#

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

GND

GND

10011116

143

156

164

172

180

136

VDDQ9

GND

VDDQ10

VDDQ11

GND

GND

VDDQ12

VDDQ13

GND

GND

15

VDDQ14

GND

112

128

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

GND

GND

GND

GND

GND

17618263344250586674818993

VDDQ15

GND

GND

A A

5

4

smbus addr = 0 1 0

3

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

2

Date: Sheet

Opteron P0 DIMM 2

Custom

GA-7A8DRL

1

2.0

of

15 81Thursday, November 10, 2005

Page 17

5

DIMM3

P0_VDD_2D5V

4

3

2

1

VDDID

GND

P0DIMM3

184

DDR-DIMM184/PURPLE

VDDSPD

179

DQ63

178

DQ62

175

DQ61

174

DQ60

88

DQ59

87

DQ58

84

DQ57

83

DQ56

171

DQ55

170

DQ54

166

DQ53

165

DQ52

80

DQ51

79

DQ50

73

DQ49

72

DQ48

162

DQ47

161

DQ46

155

DQ45

153

DQ44

69

DQ43

68

DQ42

64

DQ41

61

DQ40

151

DQ39

150

DQ38

147

DQ37

146

DQ36

60

DQ35

57

DQ34

55

DQ33

53

DQ32

133

DQ31

131

DQ30

127

DQ29

126

DQ28

40

DQ27

39

DQ26

35

DQ25

33

DQ24

123

DQ23

121

DQ22

117

DQ21

114

DQ20

31

DQ19

28

DQ18

24

DQ17

23

DQ16

110

DQ15

109

DQ14

106

DQ13

105

DQ12

20

DQ11

19

DQ10

13

DQ9

12

DQ8

99

DQ7

98

DQ6

95

DQ5

94

DQ4

8

DQ3

6

DQ2

4

DQ1

2

DQ0

90

WP

63

WE#

1

VREF

102

NC4

9

NC2

101

NC3

P0_SR_MEMDATA127

P0_SR_MEMDATA126

P0_SR_MEMDATA125

P0_SR_MEMDATA124

P0_SR_MEMDATA123

P0_SR_MEMDATA122

P0_SR_MEMDATA121

P0_SR_MEMDATA120

P0_SR_MEMDATA119

P0_SR_MEMDATA118

P0_SR_MEMDATA117

P0_SR_MEMDATA116

P0_SR_MEMDATA115

P0_SR_MEMDATA114

P0_SR_MEMDATA113

P0_SR_MEMDATA112

P0_SR_MEMDATA111

P0_SR_MEMDATA110

P0_SR_MEMDATA109

P0_SR_MEMDATA108

P0_SR_MEMDATA107

P0_SR_MEMDATA106

P0_SR_MEMDATA105

P0_SR_MEMDATA104

P0_SR_MEMDATA103

P0_SR_MEMDATA102

P0_SR_MEMDATA101

P0_SR_MEMDATA100

P0_SR_MEMDATA99

P0_SR_MEMDATA98

P0_SR_MEMDATA97

P0_SR_MEMDATA96

P0_SR_MEMDATA95

P0_SR_MEMDATA94

P0_SR_MEMDATA93

P0_SR_MEMDATA92

P0_SR_MEMDATA91

P0_SR_MEMDATA90

P0_SR_MEMDATA89

P0_SR_MEMDATA88

P0_SR_MEMDATA87

P0_SR_MEMDATA86

P0_SR_MEMDATA85

P0_SR_MEMDATA84

P0_SR_MEMDATA83

P0_SR_MEMDATA82

P0_SR_MEMDATA81

P0_SR_MEMDATA80

P0_SR_MEMDATA79

P0_SR_MEMDATA78

P0_SR_MEMDATA77

P0_SR_MEMDATA76

P0_SR_MEMDATA75

P0_SR_MEMDATA74

P0_SR_MEMDATA73

P0_SR_MEMDATA72

P0_SR_MEMDATA71

P0_SR_MEMDATA70

P0_SR_MEMDATA69

P0_SR_MEMDATA68

P0_SR_MEMDATA67

P0_SR_MEMDATA66

P0_SR_MEMDATA65

P0_SR_MEMDATA64

P0_SR_MEMWE_L

P0_DIMM_MEMVREF

P0_SR_MEMDATA[127..64] 14,17

P0_SR_MEMWE_L 13,14,15,18

94

93

12

P0_VDD_2D5V

C94

0.1U/6

C95

0.1U/6

GND

P0_DIMM_MEMVREF 11,13,14,15

738467085

108

120

148

1688222

30

54627796104

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

GND

VDDQ3

GND

GND

GND

GND

GND

GND

124

132

139

145

152

160

D D

P0_SR_MEMCS_L315,18

P0_SR_MEMCS_L215,18

P0_SR_MEMDQS_UPR[8..0]14,17

RCC_SDA13,14,15,29,30,31,32,57,75

RCC_SCL13,14,15,29,30,31,32,57,75

P0_SR_MEMBANK113,14,15,18

P0_SR_MEMBANK013,14,15,18

C C

B B

P0_SR_MEMADD[13..0]13,14,15,18

P0_SR_MEMCHECK_UPR[7..0]14,17

P0_MEMCLK_UPR_H110,18

P0_MEMCLK_UPR_L110,18

P0_MEMRESET_GPIO10,13,14,15

P0_SR_MEMCKE_LWR13,14,15,18

P0_SR_MEMCKE_UPR13,14,15,18

P0_SR_MEMCAS_L13,14,15,18

P0_SR_MEMRAS_L13,14,15,18

P0_SR_MEMDQS_UPR[17..9]14,17

P0_SR_MEMCS_L3

P0_SR_MEMCS_L2

P0_SR_MEMDQS_UPR8

P0_SR_MEMDQS_UPR7

P0_SR_MEMDQS_UPR6

P0_SR_MEMDQS_UPR5

P0_SR_MEMDQS_UPR4

P0_SR_MEMDQS_UPR3

P0_SR_MEMDQS_UPR2

P0_SR_MEMDQS_UPR1

P0_SR_MEMDQS_UPR0

P0_VDD_2D5V

RCC_SDA

GND

RCC_SCL

P0_SR_MEMBANK1

P0_SR_MEMBANK0

P0_SR_MEMADD13

P0_SR_MEMADD12

P0_SR_MEMADD11

P0_SR_MEMADD10

P0_SR_MEMADD9

P0_SR_MEMADD8

P0_SR_MEMADD7

P0_SR_MEMADD6

P0_SR_MEMADD5

P0_SR_MEMADD4

P0_SR_MEMADD3

P0_SR_MEMADD2

P0_SR_MEMADD1

P0_SR_MEMADD0

P0_SR_MEMCHECK_UPR7

P0_SR_MEMCHECK_UPR6

P0_SR_MEMCHECK_UPR5

P0_SR_MEMCHECK_UPR4

P0_SR_MEMCHECK_UPR3

P0_SR_MEMCHECK_UPR2

P0_SR_MEMCHECK_UPR1

P0_SR_MEMCHECK_UPR0

P0_MEMCLK_UPR_H1

P0_MEMCLK_UPR_L1

P0_MEMRESET_GPIO

P0_SR_MEMCKE_LWR

P0_SR_MEMCKE_UPR

P0_SR_MEMCAS_L

P0_SR_MEMRAS_L

P0_SR_MEMDQS_UPR17

P0_SR_MEMDQS_UPR16

P0_SR_MEMDQS_UPR15

P0_SR_MEMDQS_UPR14

P0_SR_MEMDQS_UPR13

P0_SR_MEMDQS_UPR12

P0_SR_MEMDQS_UPR11

P0_SR_MEMDQS_UPR10

P0_SR_MEMDQS_UPR9

163

71

158

157

47

86

78

67

56

36

25

14

5

103

183

182

181

91

92

113

52

59

167

115

118

141

27

122

29

125

32

37

130

41

43

48

144

142

135

134

51

49

45

44

16

17

137

138

76

75

173

10

21

111

65

154

140

177

169

159

149

129

119

107

97

CS3#

CS2#

CS1#

CS0#

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

FETEN

SA2

SA1

SA0

SDA

SCL

BA2

BA1

BA0

A13

A12

A11

A10_AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0

CK0#

CK1

CK1#

CK2

CK2#

NC5

NC1_RESET#

CKE0

CKE1

CAS#

RAS#

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

GND

GND

10011116

143

156

164

172

180

136

VDDQ9

GND

VDDQ10

VDDQ11

GND

GND

VDDQ12

VDDQ13

GND

GND

15

VDDQ14

GND

112

128

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

GND

GND

GND

GND

GND

17618263344250586674818993

VDDQ15

GND

GND

smbus addr = 0 1 1

A A

GIGABYTE THCHNOLOGIES , INC.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

Opteron P0 DIMM 3

Custom

GA-7A8DRL

1

2.0

of

16 81Thursday, November 10, 2005

Page 18

5

4

3

2

1

P0_VTT_DDR

1

3

RP2 8P4R/4/47/B

5

7

1

3

RP4 8P4R/4/47/B

5

D D

C C

B B

A A

7

1

3

RP6 8P4R/4/47/B

5

7

1

3

RP8 8P4R/4/47/B

5

7

1

3

RP10 8P4R/4/47/B

5

7

1

3

RP12 8P4R/4/47/B

5

7

1

3

RP14 8P4R/4/47/B

5

7

1

3

RP16 8P4R/4/47/B

5

7

1

3

RP18 8P4R/4/47/B

5

7

1

3

RP20 8P4R/4/47

5

7

1

3

RP23 8P4R/4/47

5

7

1

3

RP27 8P4R/4/47

5

7

1

3

RP31 8P4R/4/47

5

7

1

3

RP35 8P4R/4/47

5

7

1

3

RP39 8P4R/4/47

5

7

1

3

RP46 8P4R/4/47

5

7

1

3

RP53 8P4R/4/47

5

7

1

3

RP57 8P4R/4/47

5

7

1

3

RP64 8P4R/4/47

5

7

1

3

RP68 8P4R/4/47

5

7

1

3

RP72 8P4R/4/47

5

7

1

3

RP76 8P4R/4/47

5

7

1

3

RP82 8P4R/4/47

5

7

1

3

RP85 8P4R/4/47

5

7

1

3

5

RP87 8P4R/4/47

7

1

3

5

RP90 8P4R/4/47

7

1

3

5

RP92 8P4R/4/47

7

1

3

5

RP94 8P4R/4/47

7

P0_SR_MEMDQS_UPR3

2

P0_SR_MEMDQS_UPR12

4