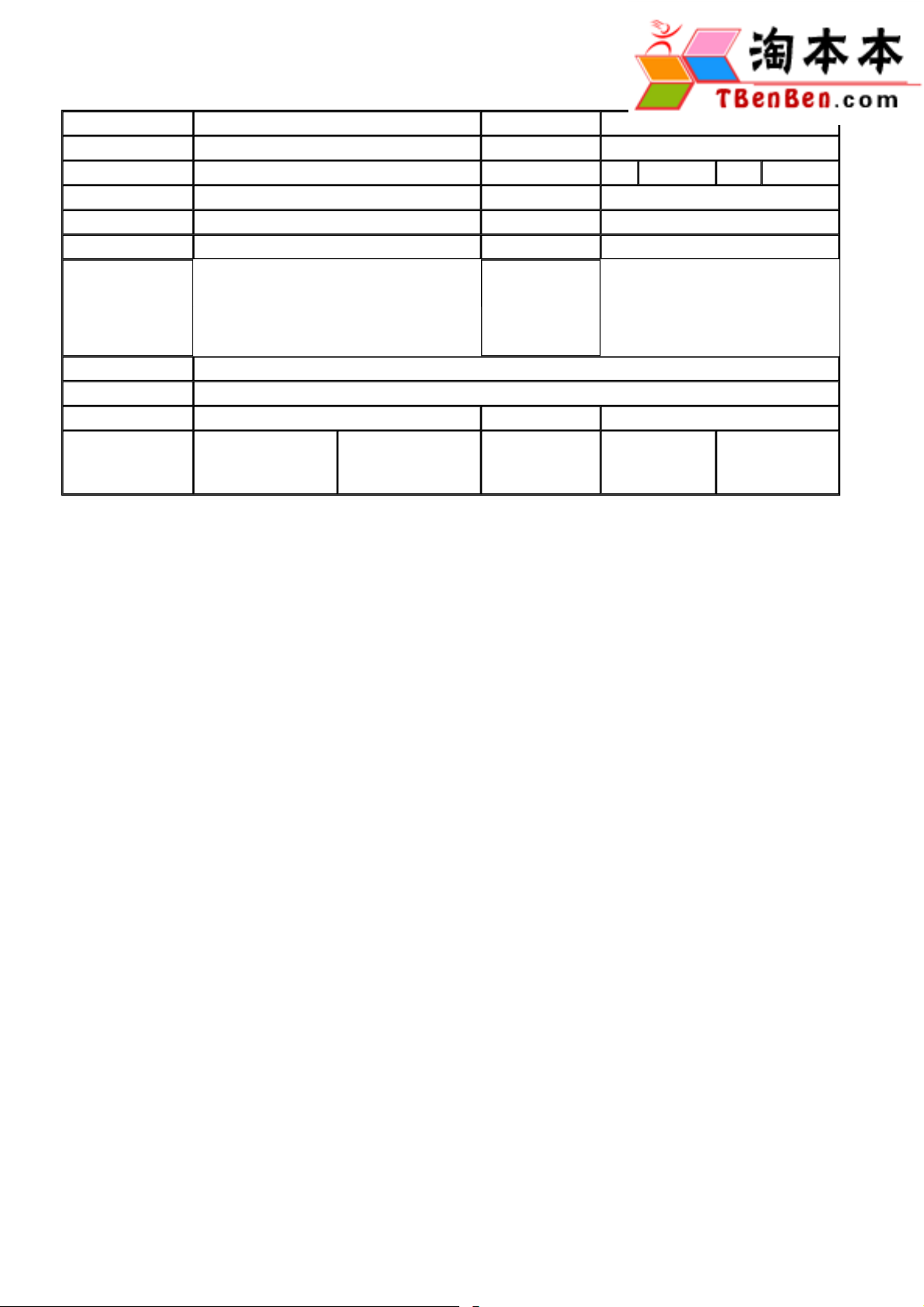

Gigabyte GA-2CEWH-FS REV1.0 Schematic

第 1 頁,共 1 頁Technical Information Release Notice

Technical Information Release Notice

Doc Type Schematic Date 2005/7/5 下午 05:16:32

Project Code S93059-0 Customer FS

Project Name GA-2CEWH-FS Revision Old NA New 1.0

Model Name GA-2CEWH-FS IT Doc No DR057026

P/N RD Doc No

PCB Rev. 1.0 Check Sum

R N M

M/B GA-2CEWH-FS 1.0A

P/N Description

FINISHED GOOD

Description release SCH. for PVT

Remark

Approved By daniel.hou 2005/7/5 下午 08:33:02 Applicant Ryan.Chen

Research

Management

Mimosa.Kao

2005/7/6 上午

08:44:54

Validation Manager Project Manager

Effected Class

gfedc gfedcb gfedc

A B C D E F

gfedc

gfedcb

A B

gfedc gfedcb

gfedc gfedc

gfedc gfedc

I

I

T

T

R

R

e

e

s

s

e

e

a

a

r

r

c

c

h

h

2

2

0

0

M

M

0

0

a

a

5

5

n

n

/

/

7

7

a

a

/

/

g

g

6

6

e

e

m

m

e

e

n

n

t

t

FinePrint - www.fineprint.com 用 列印 可在 訂購

2005/7/6http://10.1.1.15/ef2kweb/CHT/Forms/RTC009/RTC009_P.asp

Mimosa.Kao

GA-2CEWH-FS REV 1.0

1 COVER SHEET

2 BLOCK DIAGRAM

3 PCB STACK UP

4 GPIO LIST

5 CLOCK BLOCK DIAGRAM

6 SMBUS DIAGRAM

7 POWER DELIVERY DIAGRAM

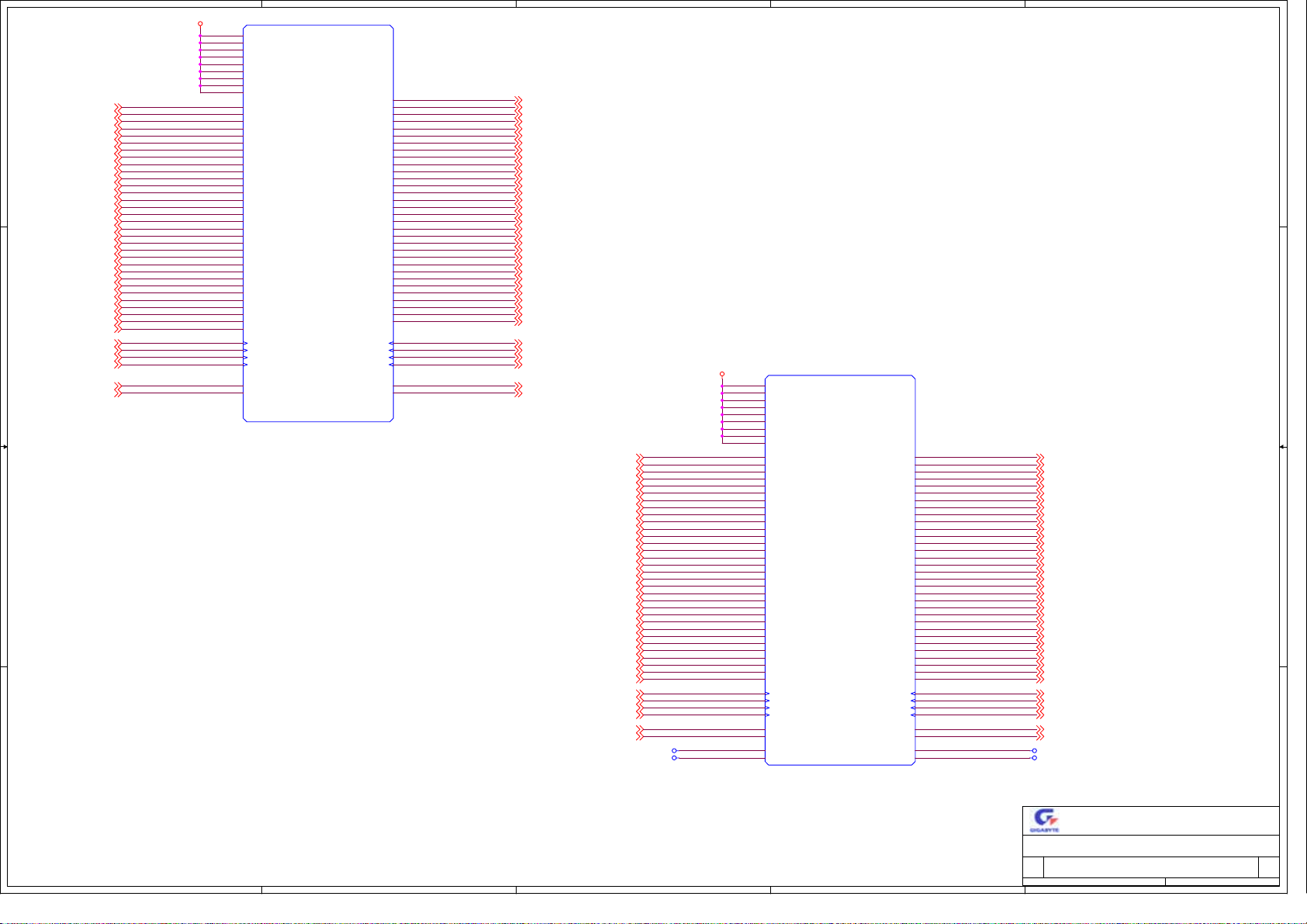

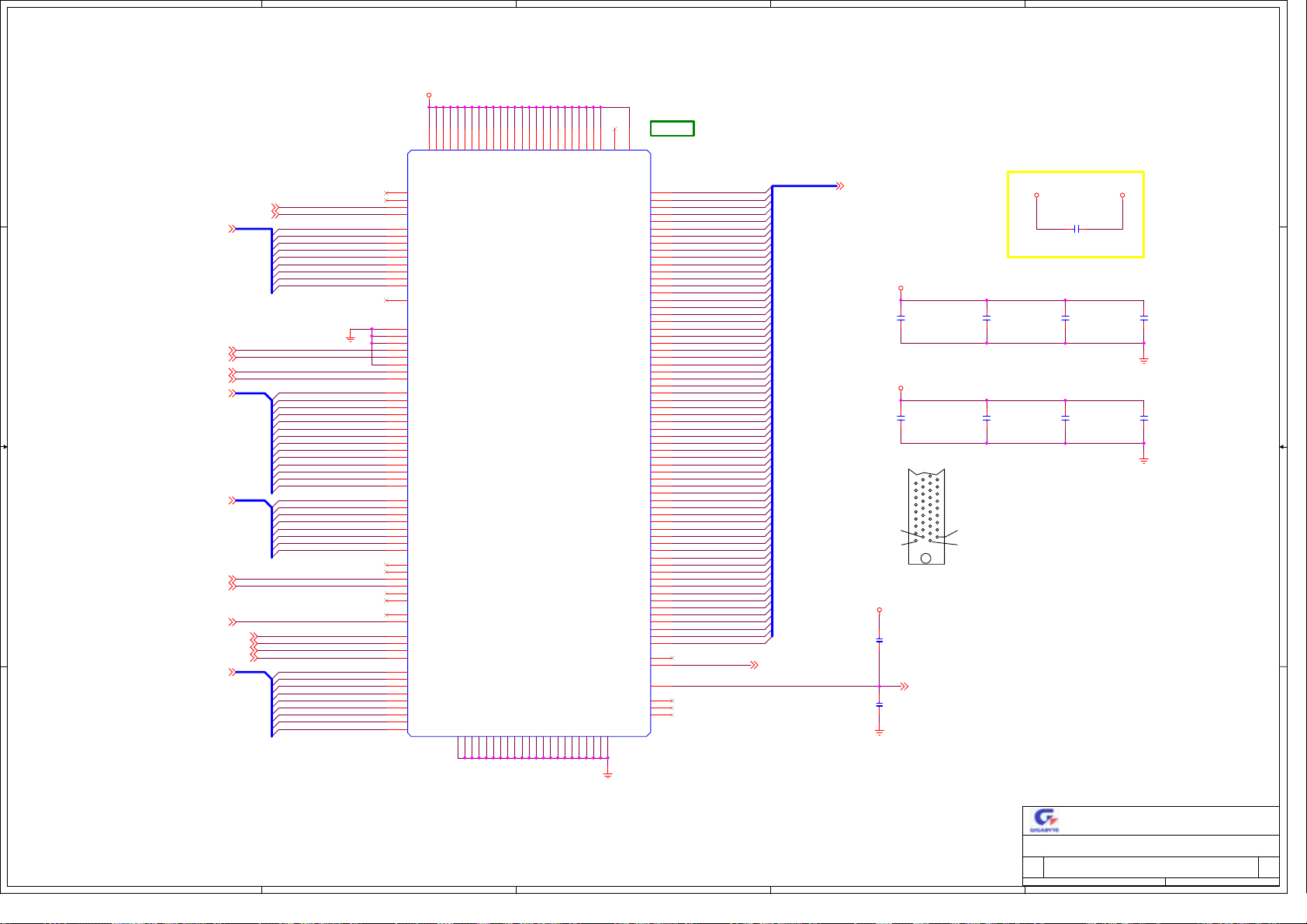

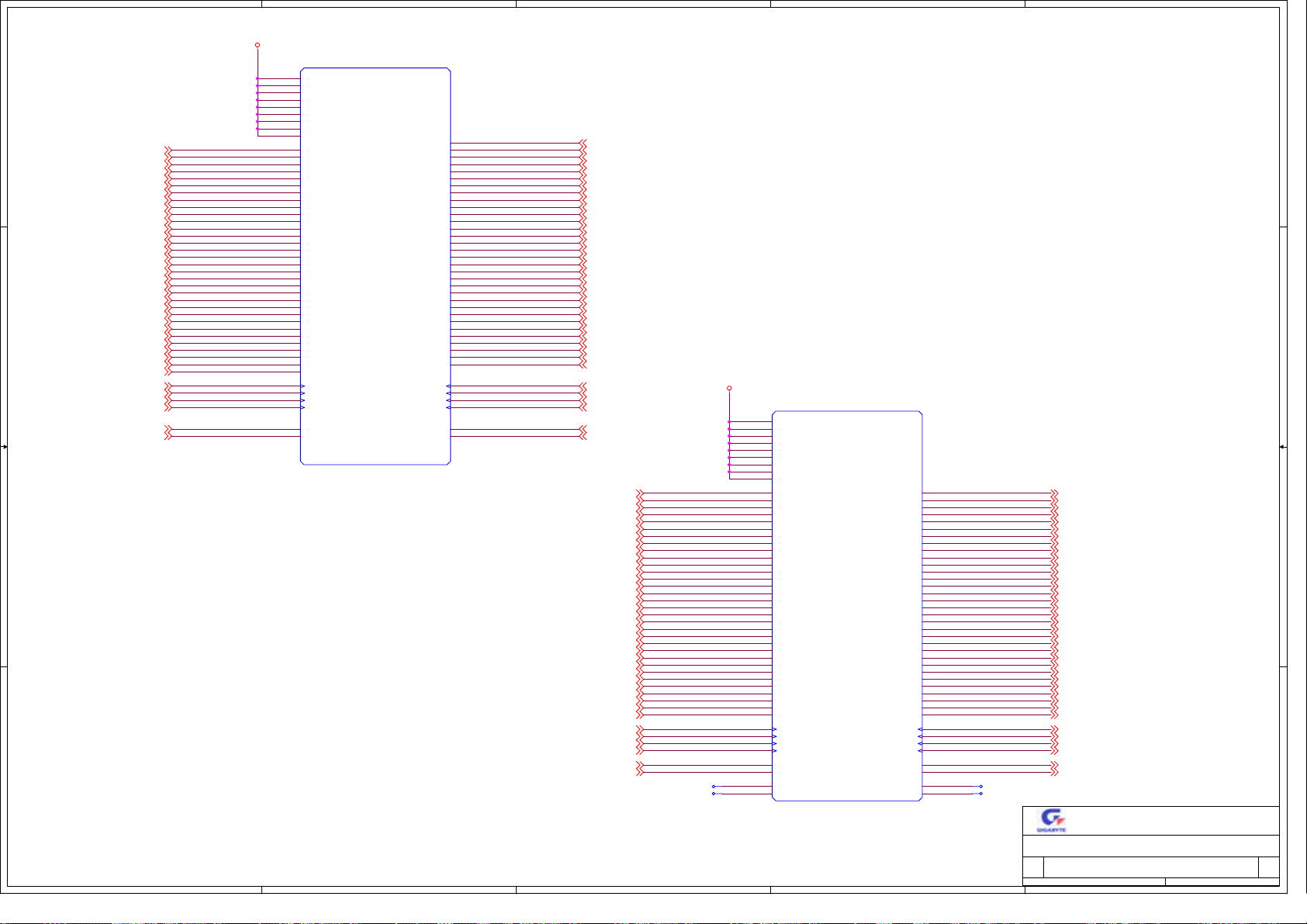

8-9 P0 LDT INTERFACE

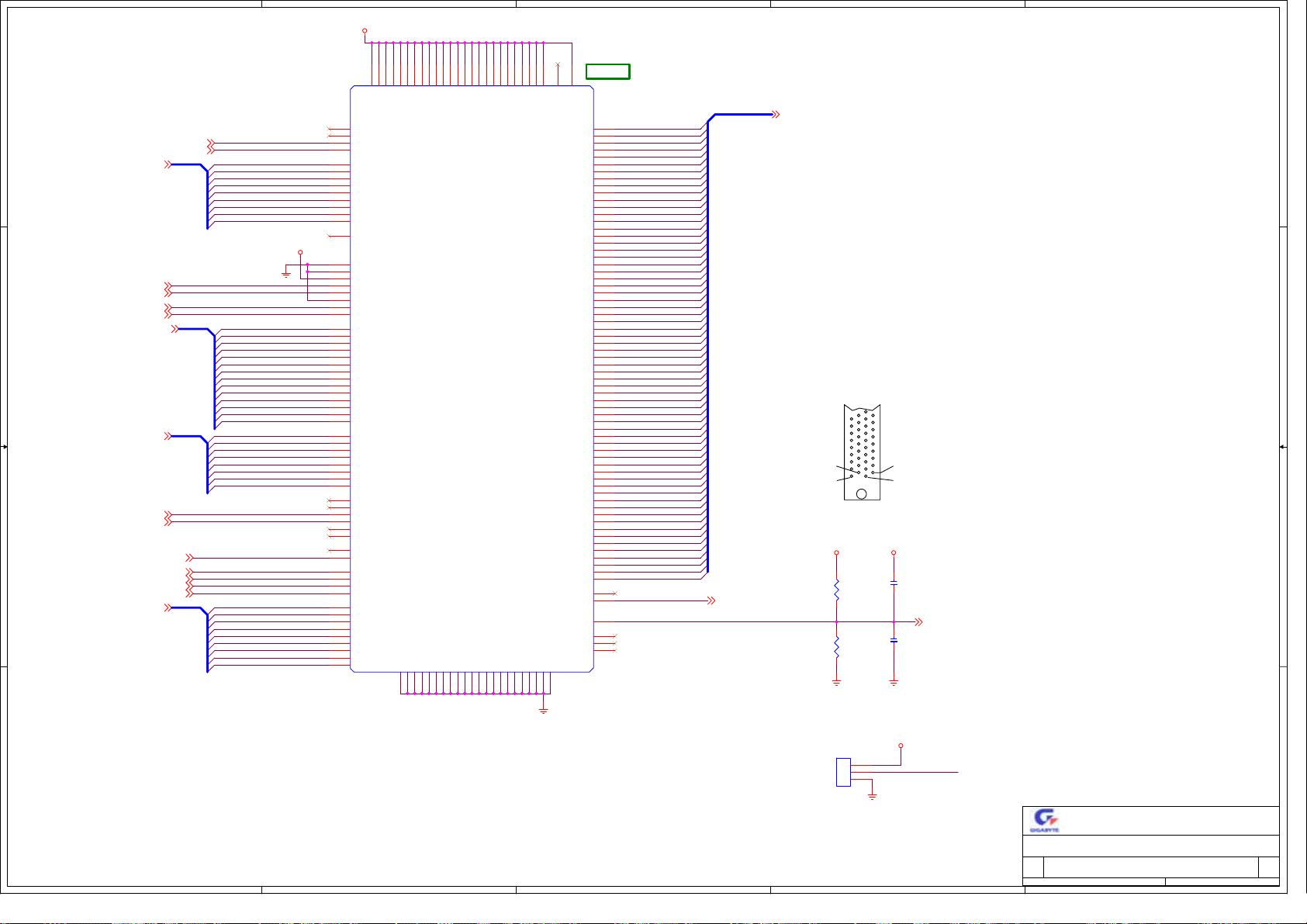

10 P0 MISC

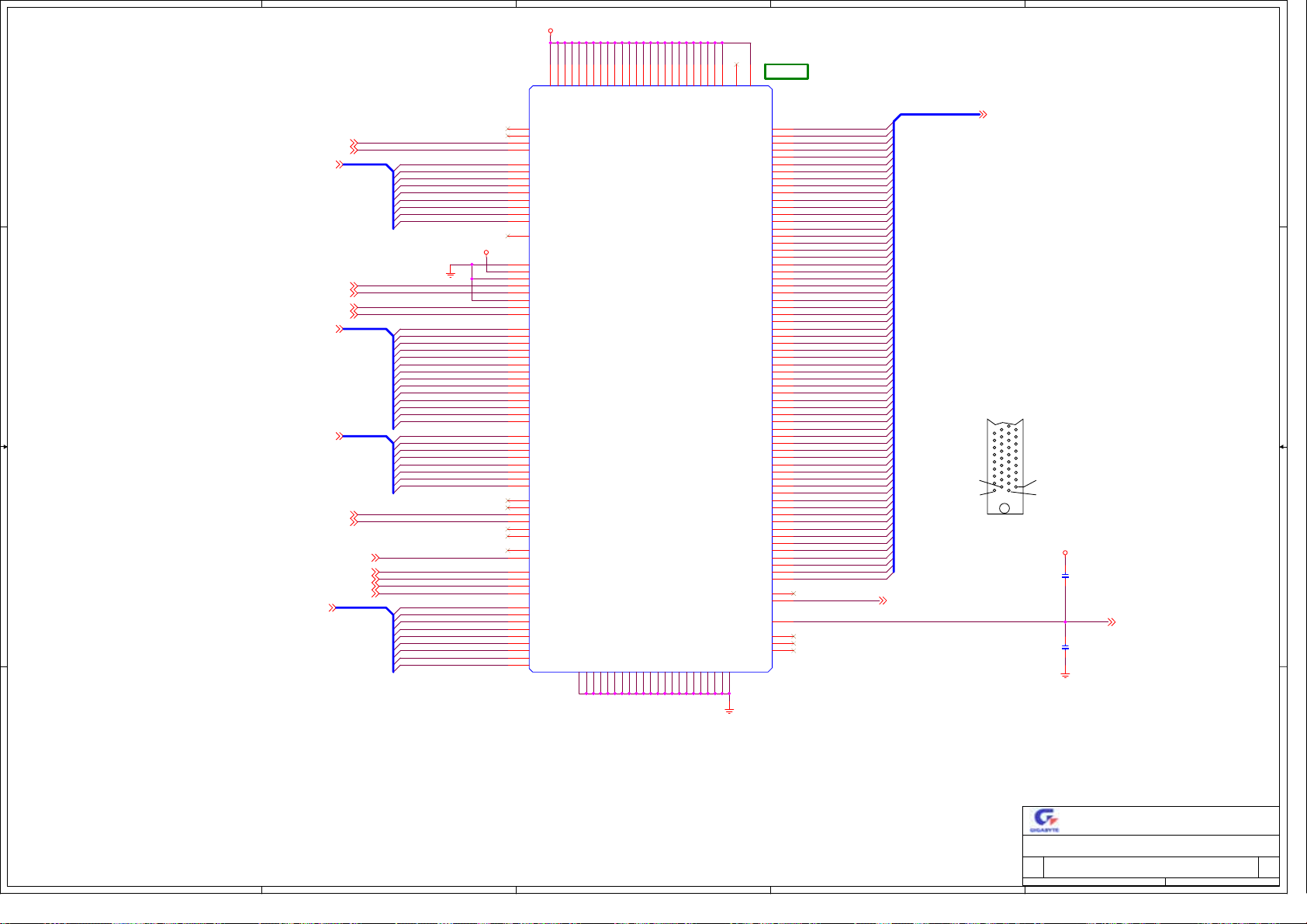

11 P0 POWER/GND

13 P0 DDR INTERFACE

14 P0 DDR VRD

15-18 P0 DDR DIMM 60 PCI SLOT

19-20 P0 DDR TERMINATION

21 P0 POWER DECOUPLING

22-23 P1 LDT INTERFACE

24 P1 MISC

25 P1 POWER/GND

26 P1 MISC POWER

27 P1 DDR INTERFACE

28 P1 DDR VRD

29-32 P1 DDR DIMM

33-34 P1 DDR TERMINATION

35 P1 POWER DECOUPLING

36 CPUCLK ZDB

37 AMD8132 LDT & MISC

38 AMD8132 PCI-X CHA

39 AMD8132 PCI-X CHB

40 AMD8132 DECOUPLING

41 CK804 LDT INTERFACE

42 CK804 PCI-E INTERFACE

43 CK804 PCI & LPC INTERFACE

44 CK804 SATA & IDE & RTC

45 CK804 RGMII & AC97 & USB & BATTERY

46 CK804 DECOUPLING

47 IO4 LDT INTERFACE

48 IO4 PCI-E INTERFACE

49 IO4 PCI & LPC INTERFACE

50 IO4 SATA & IDE

51 IO4 RGMII & AC97 & USB

52 IO4 DECOUPLING

53 BCM5751T GBE

54 B5011U GIGABIT PHY12 P0 MISC POWER

55-56 PCI-X SLOTS

57-59 PCI-E SLOTS

61 IEEE1394 TSB43AB23

62 LPC BIOS FLASH

63 LPC SUPER IO IT8712F-IX

64 AUDIO CODEC ALC850

65 AUDIO CONNECTOR

66 POWER SEQUENCE CIRCUIT

67 USB / USB+RJ45 CONNECTOR

68 ATX & 1394 & LCD & PC2004 CONNECTOR

69 COM & PS2 & FLOPPY & LPT

70 FAN CONTROL

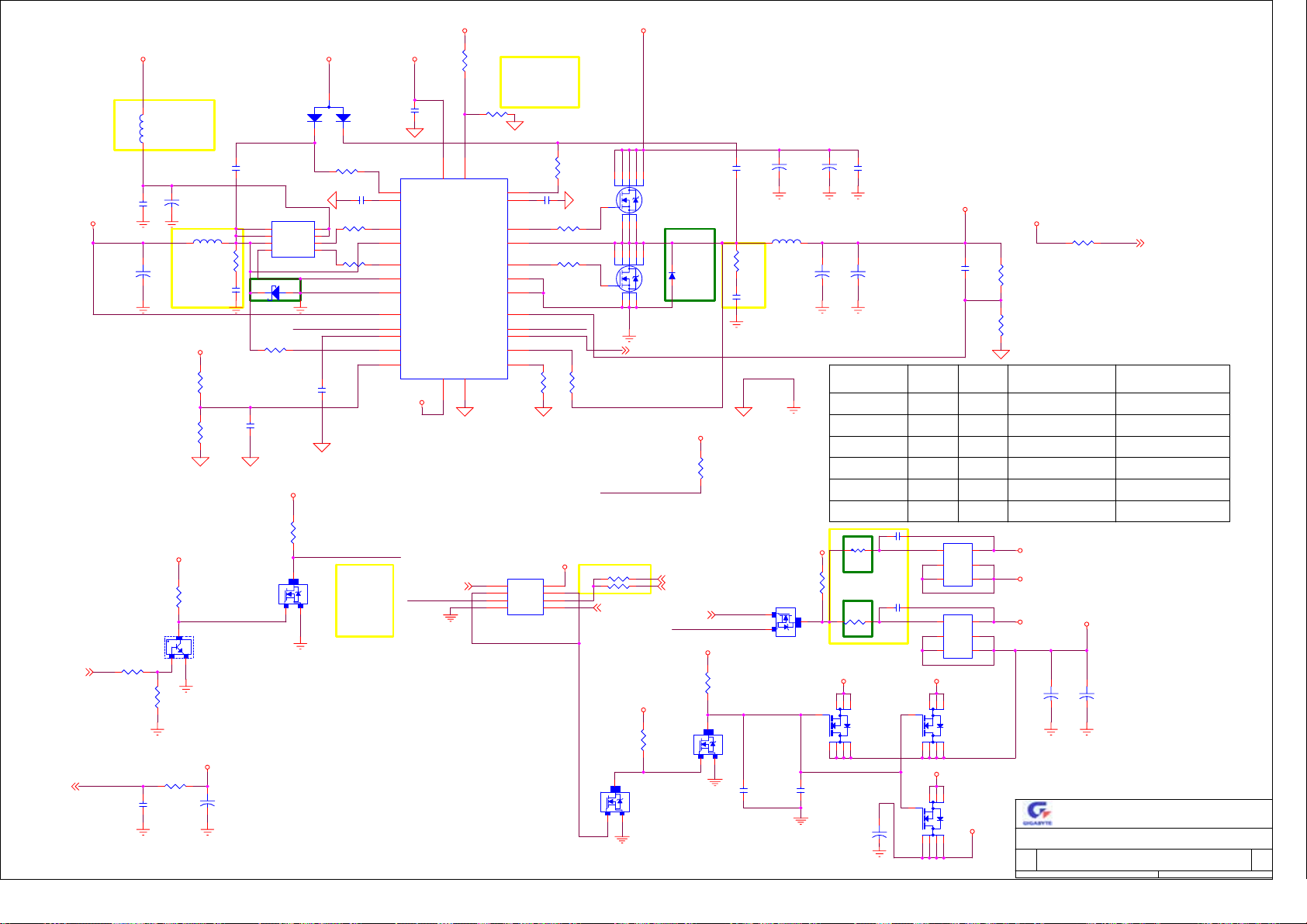

71 P0 VRD

72 P1 VRD

73 CK804 / IO4 VRD

74 P1V2_HT VRD

75 DUAL POWER CIRCUIT

76 FRONT PANEL

77 H/W MONITOR

78 MOUNTING HOLE & COUPON

79 HDT MULTIPROCESSOR CONNECTOR

TABLE OF CONTENTS

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

Cover Sheet

GA-2CEWH-FS

181Monday, July 04, 2005

of

1.0

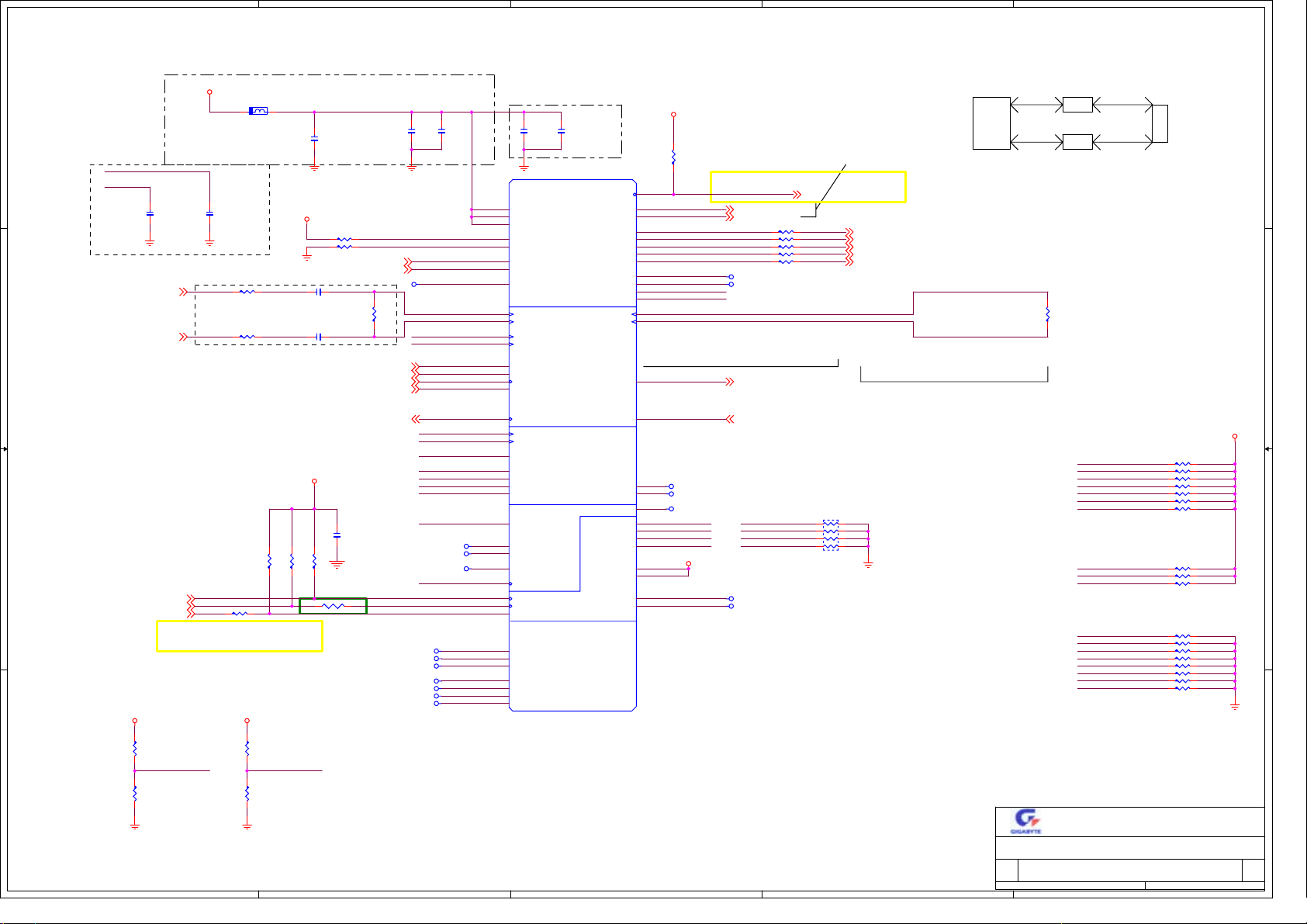

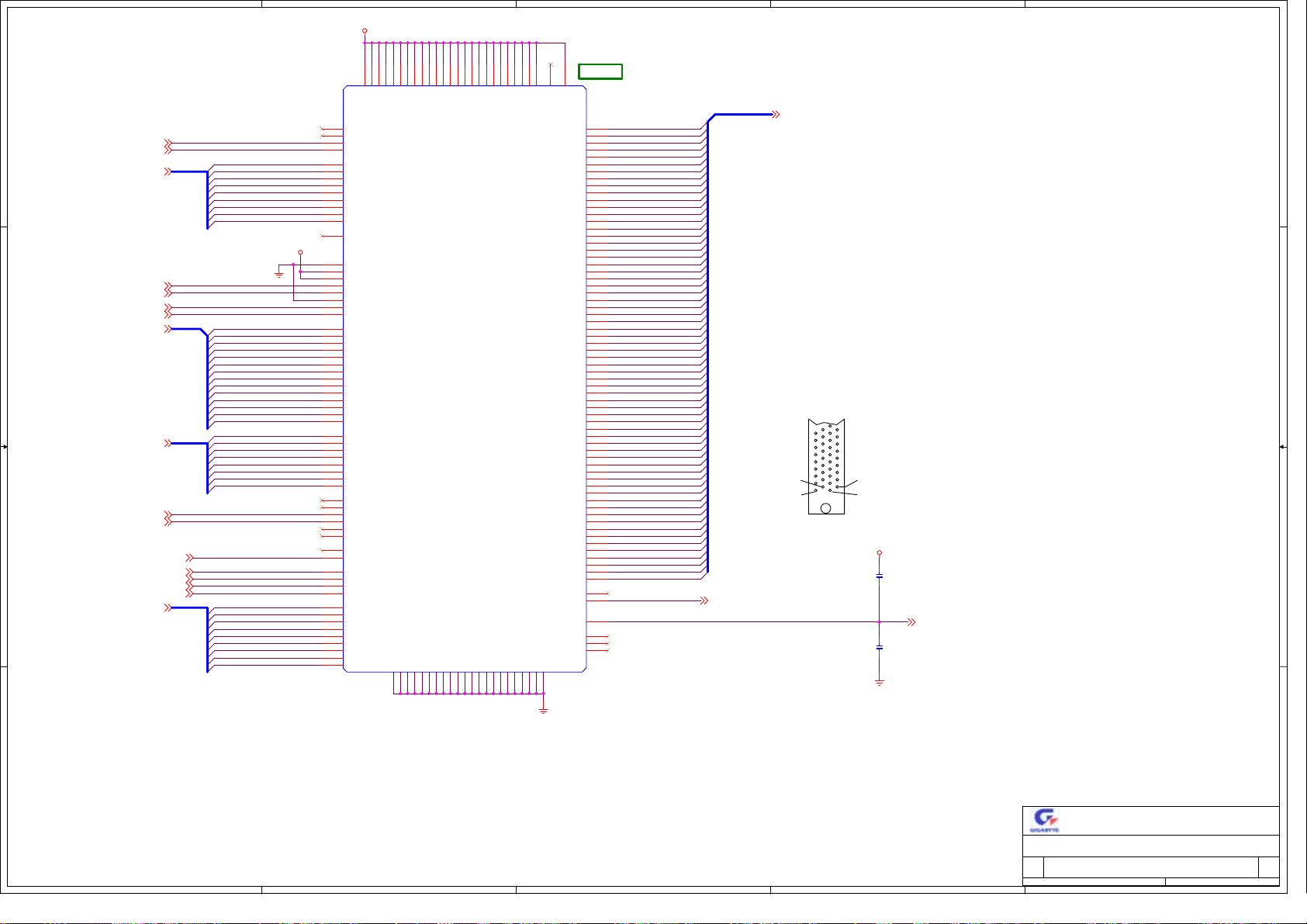

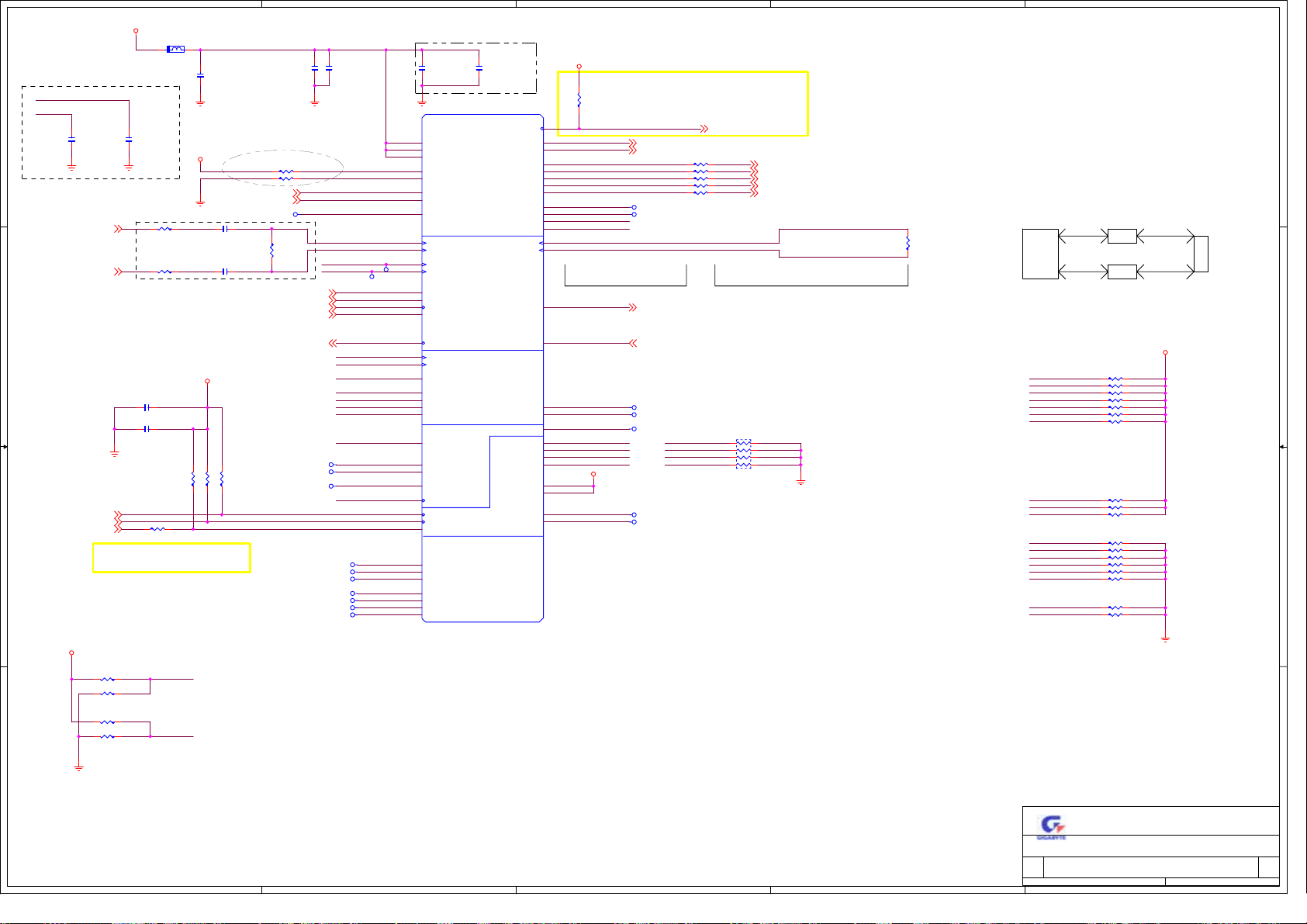

GA-2CEWH-FS SYSTEM BLOCK DIAGRAM

PCIE X16 SLOT #3

PCIE X16 SLOT #4

PCI 33MHz

SLOT #6

400 Mb/s

REAR PANEL

1394 X 1

DDR 400 DIMM Module X 4

PCIE X16 ( 8 GB/S)

PCIE X1 ( 512MB/S)

PCI 32-Bit 33MT/S - 133MB/S

RJ-45

RJ-45

IEEE 1394

TSB43AB23

SYSTEM BIOS

400 Mb/s

FRONT PANEL

1394 X 1

COM 1

Gigabit

PHY

BCM

5751T

LPC

KB / MS

RGMII

PCIE X1 (512MB/S)

For TPM

LPC

IT 8712F

LPC Super I/O

Floppy Connector

nVIDIA

CK804

Opteron 0 Opteron 1

HyperTransport 16X16

ATA-133

HyperTransport 16X16

IDE Connector x2

HyperTransport 16X16

nVIDIA

IO4

AC LINK

AC-97 2.3 COMPATIBLE

SMBus 2.0

LPT PORT

SATA II 3Gb/S

SATA II 3Gb/S

USB 2.0 (480 Mb/S)

ALC 850

8CH AC97

CODEC

EMC6W201

H/W

monitor

SATA

SATA

0/1

2/3

HyperTransport 16X16

FRONT PANEL

USB 2.0 X 2

INTERNAL

USB 2.0 X 2

REAR PANEL

USB 2.0 X 4

REAR AUDIO

PHONE JACK

REAR SPDIF

AMD

8132

DDR(400MT/S - 3.2GB/S)DDR(400MT/S - 3.2GB/S)

PCIE X16 ( 8 GB/S)

SATA II 3Gb/S

SATA II 3Gb/S

CPU0

FAN

CPU1

FAN

Front

FAN

Rear

FAN

FAN1

DDR 400 DIMM Module X 4

PCIE X16 SLOT #5

SATA

4/5

SATA

6/7

PCI-X (133MT/S - 1GB/S)

CH A

PCI-X (133MT/S - 1GB/S)

CH B

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

Block Diagram

SLOT #2

PCI-X 133MHz

GA-2CEWH-FS

PCI-X 133MHz SLOT #1

281Monday, July 04, 2005

1.0

of

5

D D

4

3

2

1

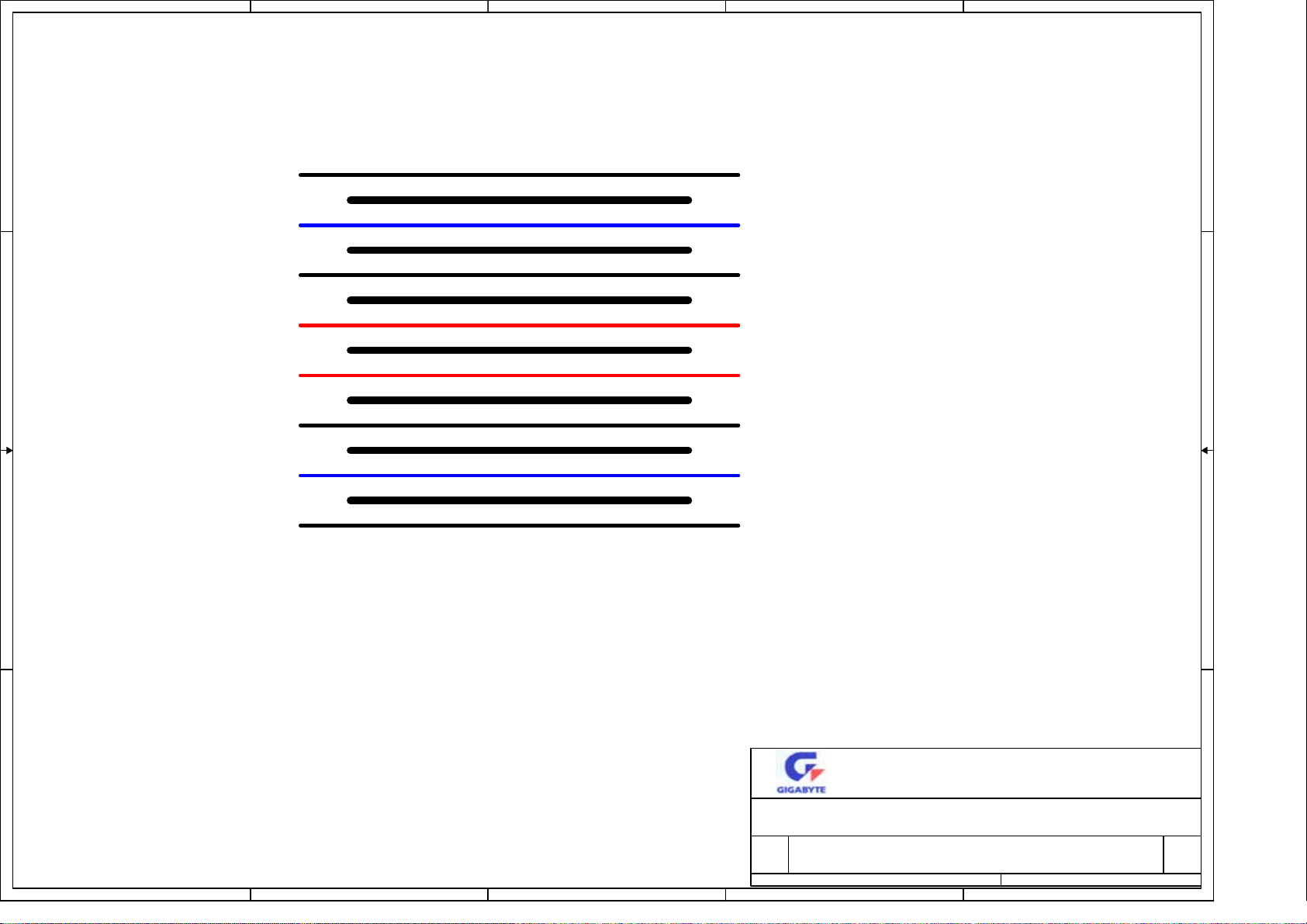

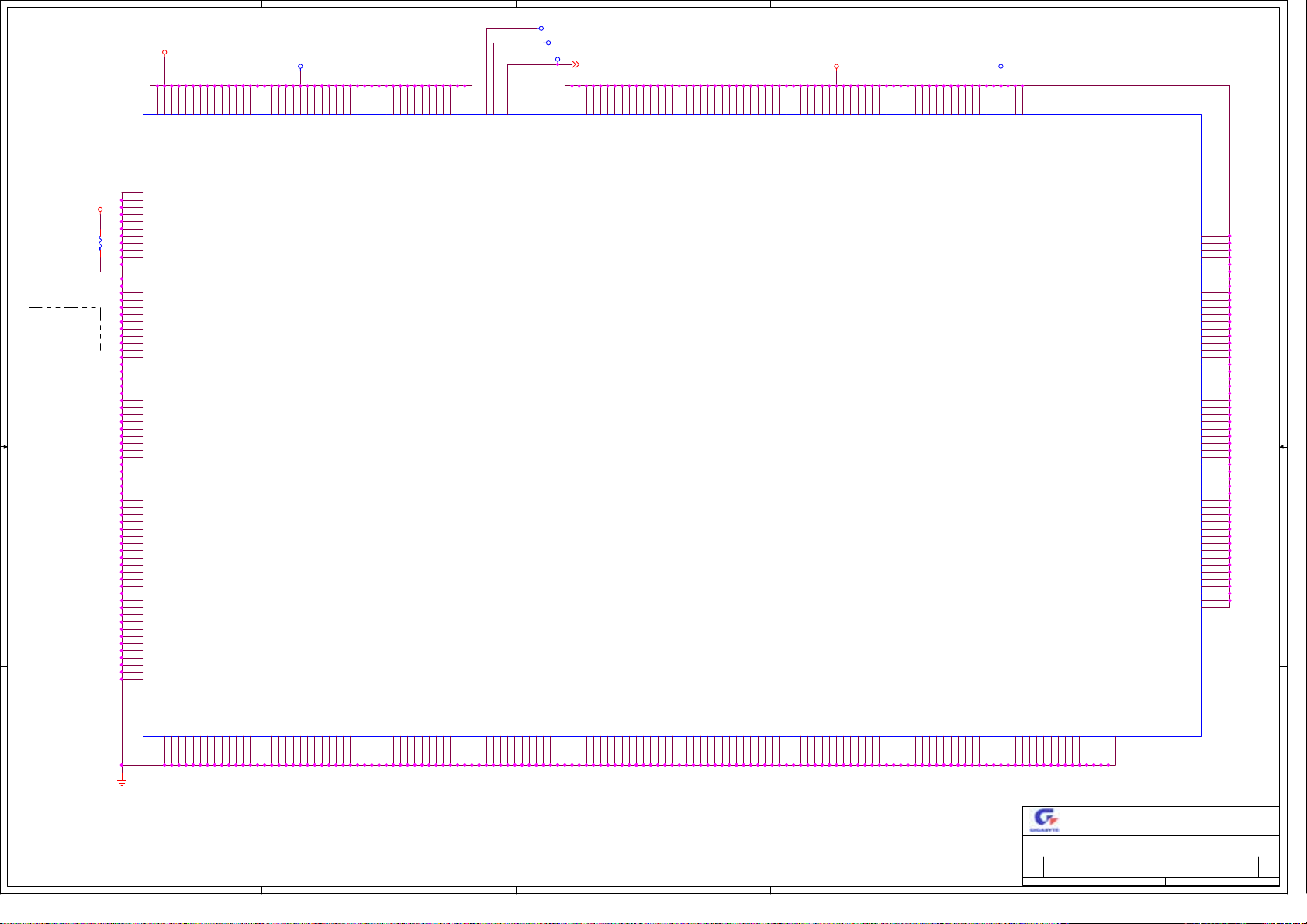

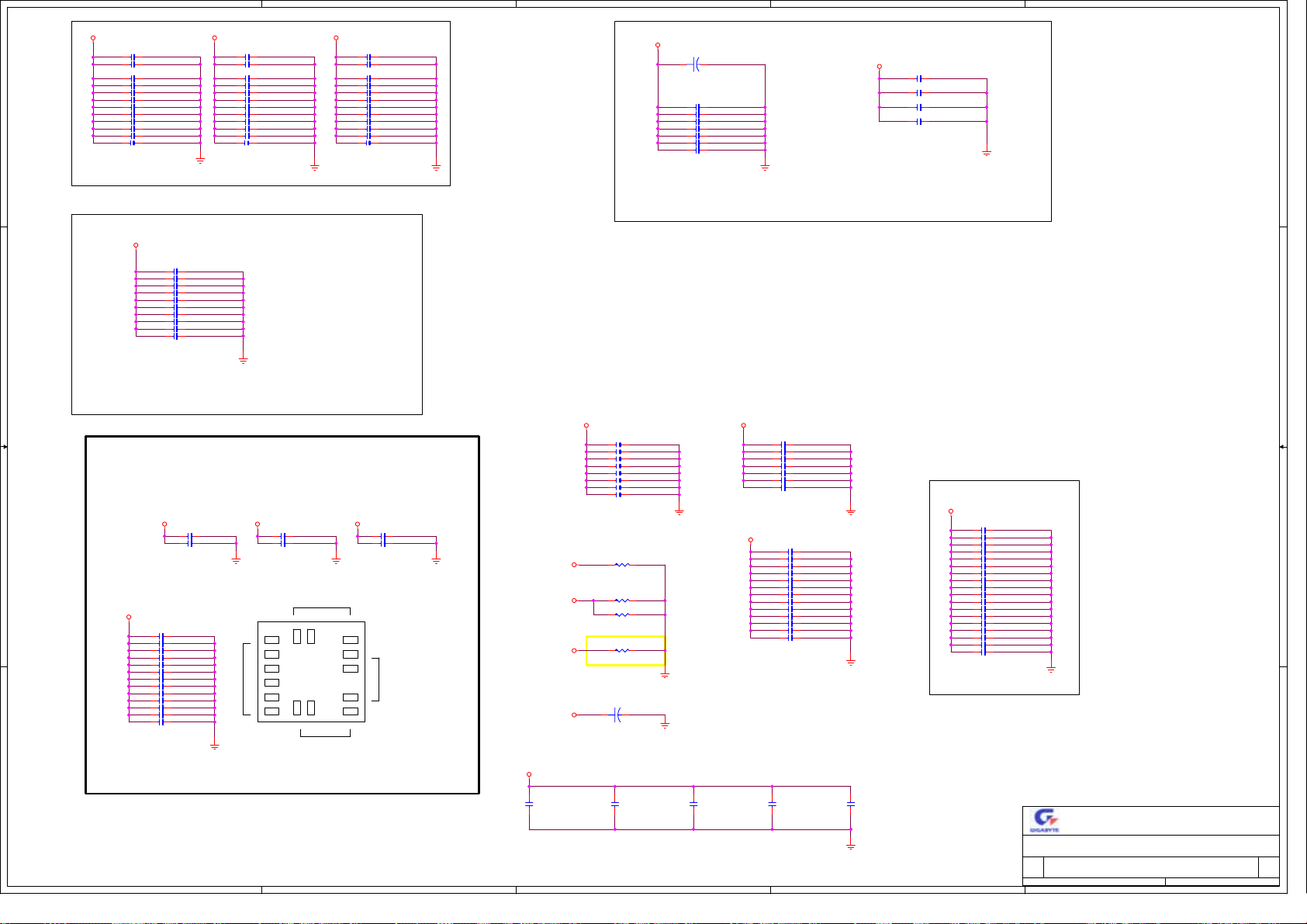

PCB STACK UP

SIGNAL

(4.5-mil)

PREPREG

2116MR

GND

(8-mil)

CORE

SIGNAL

(9.5-mil)

PREPREG

1080+7628

POWER

C C

(6-mil)

CORE

POWER

(9.5-mil)

PREPREG

1080+7628

SIGNAL

(8-mil)

CORE

GND

(4.5-mil)

PREPREG

2116MR

SIGNAL

(0.7-mil/0.5oz Cu Plating)

(1.4-mil / 1.0oz Cu)

(1.4-mil / 1.0oz Cu)

(1.4-mil / 1.0oz Cu)

(1.4-mil /1.0oz Cu)

(1.4-mil / 1.0oz Cu)

(1.4-mil / 1.0oz Cu)

(0.7-mil/0.5oz Cu Plating)

B B

A A

Title

GIGA-BYTE TECHNOLOGY CO., LTD.

PCB STACK UP

Size Document Number Rev

GA-2CEWH-FS

5

4

3

Date: Sheet

2

of

381Monday, July 04, 2005

1

1.0

5

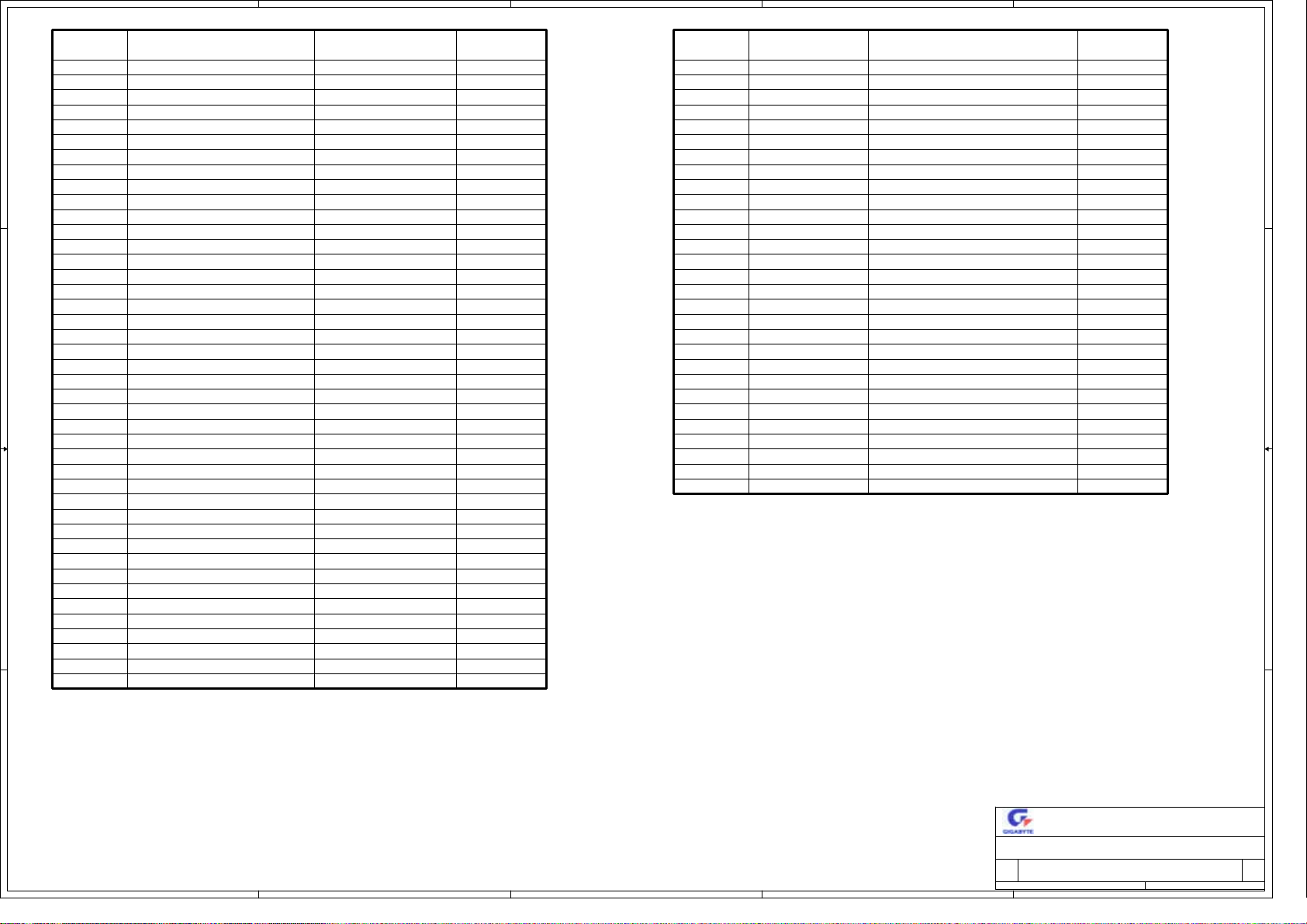

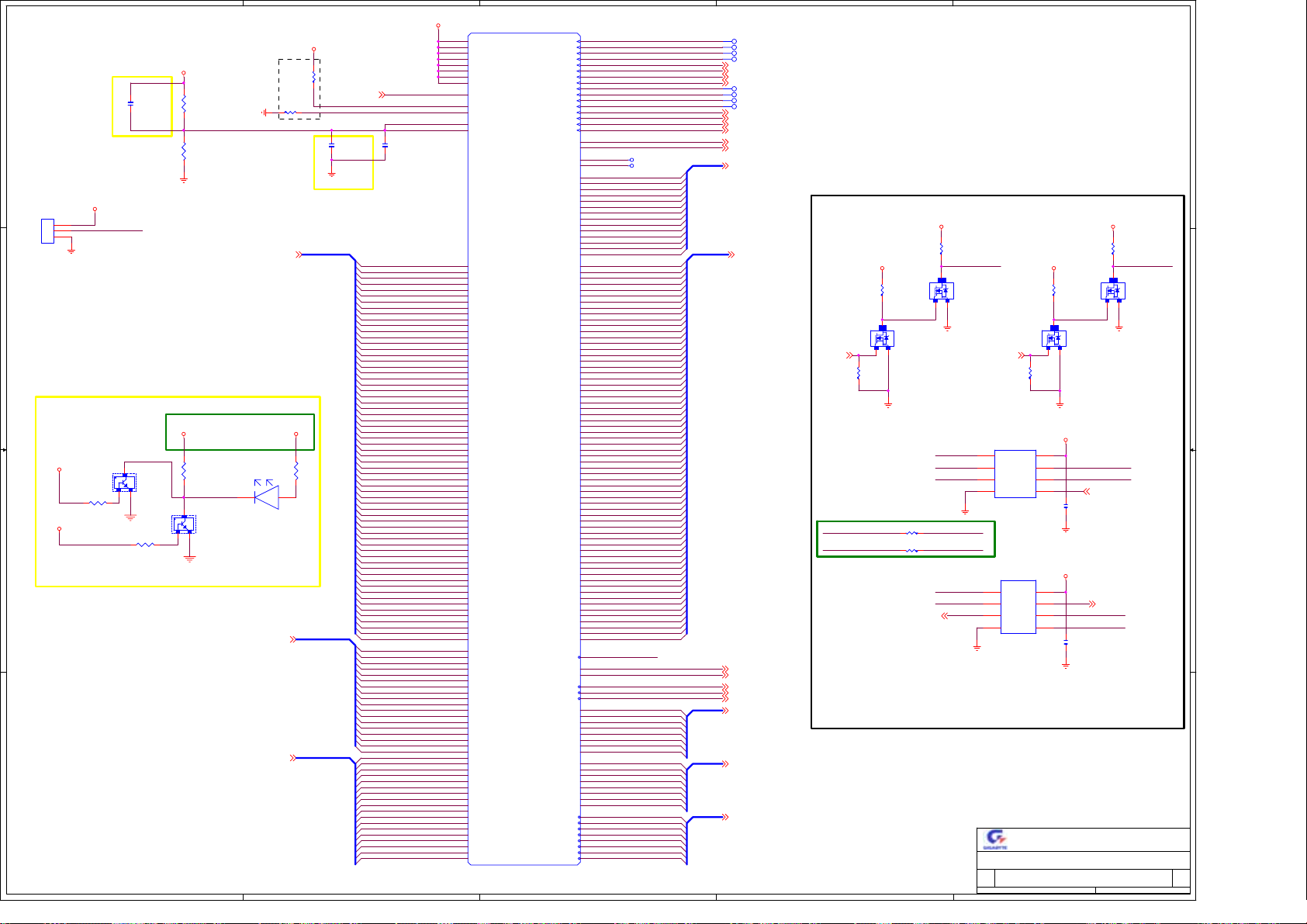

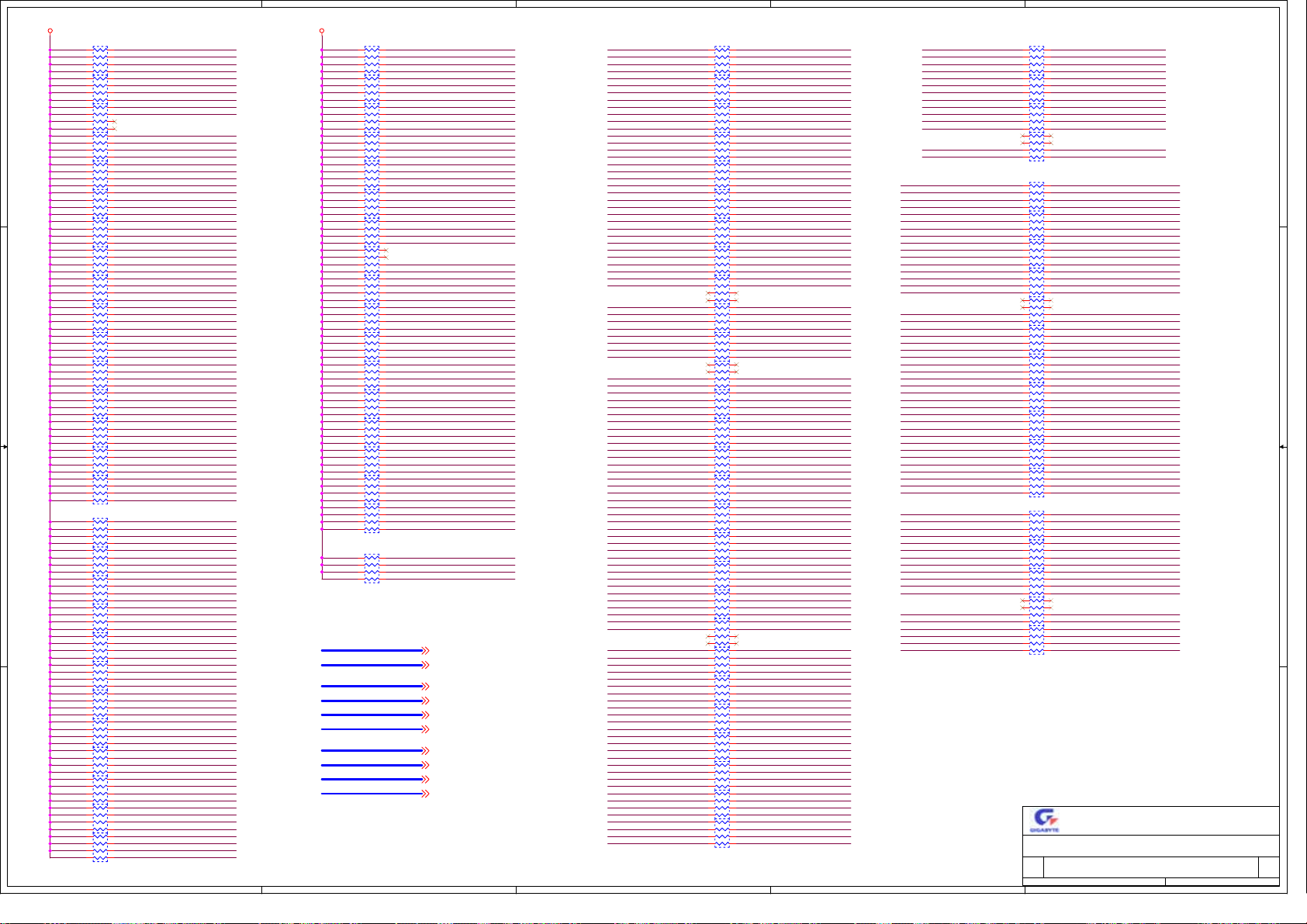

CK804 GPIO LIST

ITEM

FUNCTION

GPIO 1

GPIO 2

GPIO 3

D D

GPIO 4

GPIO 5

GPI0_I

HW_SMALERT#

ENTER_S3#

GPIO_II

GPIO 6

GPIO 7

GPIO 8

GPIO 9

CK804_LIGHT

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

AC_SDATA_IN0

CK804_MSG

GPIO 16

GPIO 17

EXT_NMI#

GPIO 18

C C

GPIO 19

GPIO 20

GPIO 21

SLP_S1S3#

GPIO 22

GPIO 23

GPIO 24

GPIO 25

CISW_PRESENT#

GPIO 26

GPIO 27

CK804_TPM_EN#

GPIO 28

GPIO 29

GPIO 30

SLP_S1-5#

CK804_RI#

GPIO 31

GPIO 32

GPIO 33

B B

GPIO 34

GPIO 35

GPIO 36

CK804_ALERT

8132_PME#

FLASH_WP#

FLASH_TBL#

GPIO 37

GPIO 38

GPIO 39

GPIO 40

GPIO 45

GPIO 46

FP_SLEEP_BTN#

DEFAULT CONDITION

4

POWER RAIL

(OD)PULL-UP

GPI

GPI

GPI

PCI_REQ2#

LID# RESUME(3.3V)

PCI_GNT2# MAIN(3.3V-5V)

PCI_CLKRUN#

HT_REQ#

RGMII_INTR#

AC_SYNC

AC_SDATA_OUT

GPO Low

GPI

PCI_REQ3#

PCI_GNT3#

KBRDRSTIN#

SPLED#

RGMII_PWRDWN

MII_RXER

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

THERMTRIP#

GPO Low

SIO_PME#

EXT_SMI#

GPI

SUSCLK

GPI

GPI

FAN_RPM

FAN_CTL0

FAN_CTL1

PCI_PME#

PCI_PERR#

GPI

A20GATE

PCI_REQ4#

PCI_GNT4#

MAIN(3V3)

MAIN(3.3V)GPI

MAIN(3.3V)

RESUME(3.3V)

RESUME(3.3V)

MAIN(3.3V-5V)

MAIN(3V3)

MAIN(3V3)

RESUME(3.3V)

MAIN(3V3)

MAIN(3V3)

RESUME(3.3V)

MAIN(3V3)

MAIN(3.3V-5V)

MAIN(3.3V-5V)

MAIN(3V3)

MAIN(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)

MAIN(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)

MAIN(3V3)

MAIN(3V3)

MAIN(3V3)

MAIN(3V3)

MAIN(3V3)

RESUME(3V3)

MAIN(3.3V-5V)

MAIN(3V3)

RESUME(3V3)

MAIN(3.3V-5V)

MAIN(3.3V-5V)

3

2

IT8712F GPIO LIST

LAN_DISABLE (OD)PULL-UPGPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO[16..17]

GPIO 20

GPIO 21

GPIO 22

SCRCLK

SCRIO

SCRFET-

SCRRST

CIRTX

N.C

SIO_BEEP

KB_POFF_DIS#

SIO_S1LED#

GPIO 2 5 SIO_SYS_FAN_TACH4 (OD)PUL L- UP MAIN(5V)

GPIO [27..23]

GPIO [35..30]

GPIO 36

GPIO 37

GPIO 40

GPIO 41

GPIO 42

GPIO 43

GPIO 44

GPIO 45

GPIO 46

N.C

N.C

SIO_SYS_FAN_PWM3

SIO_SYS_FAN_TACH3

SIO_S1S3LED

PHY_DISABLE

PS_ON#

SIO_PWRBTN#

SIO_PWRON#

SIO_PSIN

IRRX

GPIO 47

GPIO 50

GPIO 51

GPIO 52

GPIO 53

GPIO 54 RESUME(3V3)

GPIO 55

SIO_SYS_FAN_PWM2

SIO_SYS_FAN_TACH2

SIO_PWRLED-

SIO_PME#

CIRRX

IT8712F GPIOs HAVE INTEGRATED OPEN DRAIN INPUT/OUTPUT BUFFER

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

N.C

N.C

N.C

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

(OD)ICH5 INTERNAL PULL-UP

(OD)NO PULL-UP, CONTROL BY SLP_S#3

N.C

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

N.C

1

POWER RAILITEM DEFAULT CONDITIONFUNCTION

RESUME(3V3)

MAIN(5V)

MAIN(5V)

MAIN(5V)

MAIN(5V)

MAIN(3V3)

MAIN(3V3)(OD)PULL-UP

MAIN(3V3)

MAIN(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(5V)

RESUME(5V)

RESUME(3V3)

RESUME(3V3)

RESUME(3V3)SIO_PWRLED+

MAIN(5V)

MAIN(3V3)

MAIN(3V3)

RESUME(3V3)

RESUME

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

GPIO LIST

GA-2CEWH-FS

1

of

481Monday, July 04, 2005

1.0

5

4

3

2

1

CLOCK BLOCK DIAGRAM

D D

C C

B B

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

CLOCK BLOCK DIAGRAM

GA-2CEWH-FS

1

of

581Monday, July 04, 2005

1.0

5

D D

C C

4

3

2

1

B B

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

SMBUS DIAGRAM

GA-2CEWH-FS

1

of

681Monday, July 04, 2005

1.0

5

4

3

2

1

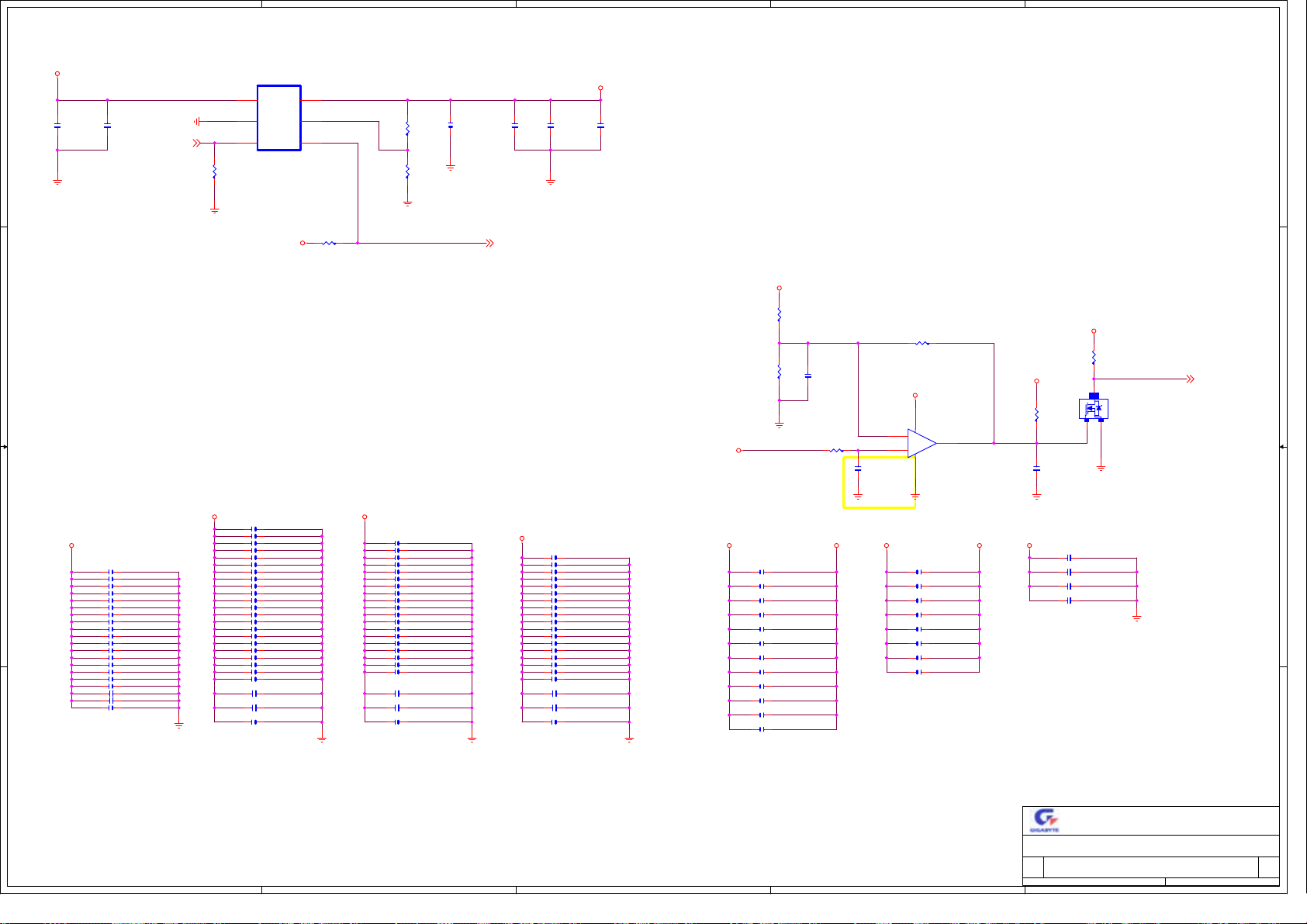

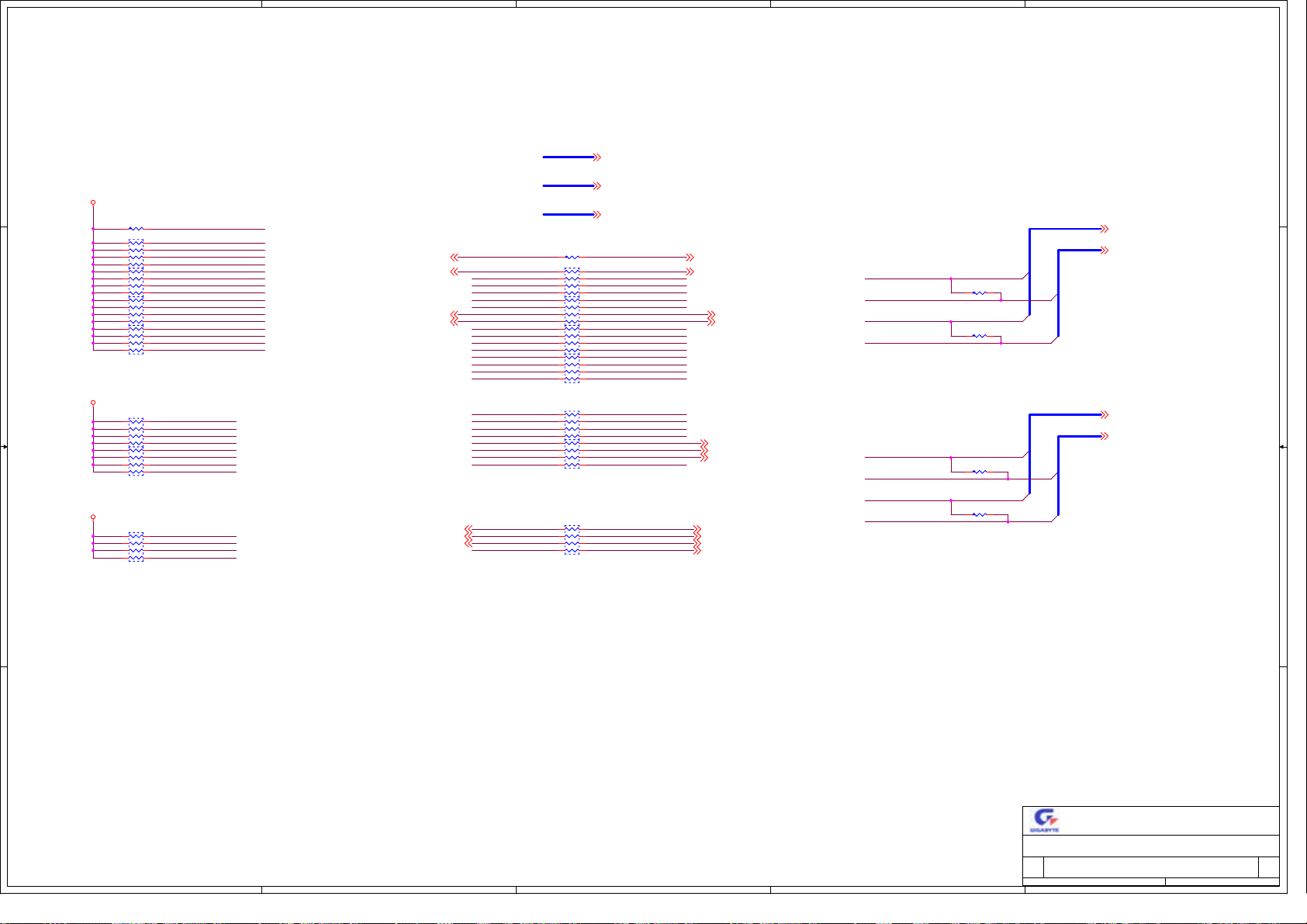

ISL6559CR

D D

4 PHASE

+

ISL6605B

MOSFET DRIVER

P0_VDD_CORE

OPTERON0

X4

ATX CONN 2X4

P12V_CPU_0

4 PHASE

P12V_CPU_1

ISL6559CR

C C

+

ISL6605B

MOSFET DRIVER

X4

P1_VDD_CORE

OPTERON1

ATX CONN 2X12

P12V

P5V

B B

P3V3

P3V3

P5V_STBY

A A

P5V

P-MOSFET +

N-MOSFET

P5V_DUAL P3V3_DUAL

APL1084

NPN

BJT

P1V2_AUX

N12V

5

4

3

BCM5751

3.3V : 230mA Typ

2.5V : 210mA Typ

1.2V : 570mA Typ

2

P2V5_AUX

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

POWER DELIVERY DIAGRAM

GA-2CEWH-FS

1

of

781Monday, July 04, 2005

1.0

5

P0_HTL0_CADIN_H1541

P0_HTL0_CADIN_L1541

D D

P0_HTL0_CADIN_H1441

P0_HTL0_CADIN_L1441

P0_HTL0_CADIN_H1341

P0_HTL0_CADIN_L1341

P0_HTL0_CADIN_H1241

P0_HTL0_CADIN_L1241

P0_HTL0_CADIN_H1141

P0_HTL0_CADIN_L1141

P0_HTL0_CADIN_H1041

P0_HTL0_CADIN_L1041

P0_HTL0_CADIN_H941

P0_HTL0_CADIN_L941

P0_HTL0_CADIN_H841

P0_HTL0_CADIN_L841

P0_HTL0_CADIN_H741

P0_HTL0_CADIN_L741

P0_HTL0_CADIN_H641

P0_HTL0_CADIN_L641

P0_HTL0_CADIN_H541

P0_HTL0_CADIN_L541

P0_HTL0_CADIN_H441

P0_HTL0_CADIN_L441

P0_HTL0_CADIN_H341

P0_HTL0_CADIN_L341

P0_HTL0_CADIN_H241

P0_HTL0_CADIN_L241

P0_HTL0_CADIN_H141

P0_HTL0_CADIN_L141

P0_HTL0_CADIN_H041

P0_HTL0_CADIN_L041

C C

P0_HTL0_CLKIN_H141

P0_HTL0_CLKIN_L141

P0_HTL0_CLKIN_H041

P0_HTL0_CLKIN_L041

P0_HTL0_CTRLIN_H41

P0_HTL0_CTRLIN_L41

B B

A A

P1V2_HT

N7

VLDT_0(1)

R7

VLDT_0(2)

U7

VLDT_0(3)

W7

VLDT_0(4)

M8

VLDT_0(5)

P8

VLDT_0(6)

AA7

VLDT_0(7)

V8

VLDT_0(8)

Y8

P0_HTL0_CADIN_H15

P0_HTL0_CADIN_L15

P0_HTL0_CADIN_H14

P0_HTL0_CADIN_L14

P0_HTL0_CADIN_H13

P0_HTL0_CADIN_L13

P0_HTL0_CADIN_H12

P0_HTL0_CADIN_L12

P0_HTL0_CADIN_H11

P0_HTL0_CADIN_L11

P0_HTL0_CADIN_H10

P0_HTL0_CADIN_L10

P0_HTL0_CADIN_H9

P0_HTL0_CADIN_L9

P0_HTL0_CADIN_H8

P0_HTL0_CADIN_L8

P0_HTL0_CADIN_H7

P0_HTL0_CADIN_L7 P0_HTL0_CADOUT_H6

P0_HTL0_CADIN_H6

P0_HTL0_CADIN_L6

P0_HTL0_CADIN_H5

P0_HTL0_CADIN_L5

P0_HTL0_CADIN_H4

P0_HTL0_CADIN_L4

P0_HTL0_CADIN_H3

P0_HTL0_CADIN_L3

P0_HTL0_CADIN_H2

P0_HTL0_CADIN_L2

P0_HTL0_CADIN_H1

P0_HTL0_CADIN_L1

P0_HTL0_CADIN_H0

P0_HTL0_CADIN_L0

P0_HTL0_CLKIN_H1

P0_HTL0_CLKIN_L1 P0_HTL0_CLKOUT_L1

P0_HTL0_CLKIN_H0

P0_HTL0_CLKIN_L0

P0_HTL0_CTRLIN_H

P0_HTL0_CTRLIN_L

VLDT_0(9)

R5

L0_CADIN_H(15)

T5

L0_CADIN_L(15)

P3

L0_CADIN_H(14)

P4

L0_CADIN_L(14)

N5

L0_CADIN_H(13)

P5

L0_CADIN_L(13)

M3

L0_CADIN_H(12)

M4

L0_CADIN_L(12)

K3

L0_CADIN_H(11)

K4

L0_CADIN_L(11)

J5

L0_CADIN_H(10)

K5

L0_CADIN_L(10)

H3

L0_CADIN_H(9)

H4

L0_CADIN_L(9)

G5

L0_CADIN_H(8)

H5

L0_CADIN_L(8)

R3

L0_CADIN_H(7)

R2

L0_CADIN_L(7)

N1

L0_CADIN_H(6)

P1

L0_CADIN_L(6)

N3

L0_CADIN_H(5)

N2

L0_CADIN_L(5)

L1

L0_CADIN_H(4)

M1

L0_CADIN_L(4)

J1

L0_CADIN_H(3)

K1

L0_CADIN_L(3)

J3

L0_CADIN_H(2)

J2

L0_CADIN_L(2)

G1

L0_CADIN_H(1)

H1

L0_CADIN_L(1)

G3

L0_CADIN_H(0)

G2

L0_CADIN_L(0)

L5

L0_CLKIN_H(1)

M5

L0_CLKIN_L(1)

L3

L0_CLKIN_H(0)

L2

L0_CLKIN_L(0)

R1

L0_CTLIN_H(0)

T1

L0_CTLIN_L(0)

Opteron

CPU0A

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

4

To CK804

P0_HTL0_CADOUT_H15

V4

P0_HTL0_CADOUT_L15

V3

P0_HTL0_CADOUT_H14

Y5

P0_HTL0_CADOUT_L14

W5

P0_HTL0_CADOUT_H13

Y4

P0_HTL0_CADOUT_L13

Y3

P0_HTL0_CADOUT_H12

AB5

P0_HTL0_CADOUT_L12

AA5

P0_HTL0_CADOUT_H11

AD5

P0_HTL0_CADOUT_L11

AC5

P0_HTL0_CADOUT_H10

AD4

P0_HTL0_CADOUT_L10

AD3

P0_HTL0_CADOUT_H9

AF5

P0_HTL0_CADOUT_L9

AE5

P0_HTL0_CADOUT_H8

AF4

P0_HTL0_CADOUT_L8

AF3

P0_HTL0_CADOUT_H7

V1

P0_HTL0_CADOUT_L7

U1

W2

P0_HTL0_CADOUT_L6

W3

P0_HTL0_CADOUT_H5

Y1

P0_HTL0_CADOUT_L5

W1

P0_HTL0_CADOUT_H4

AA2

P0_HTL0_CADOUT_L4

AA3

P0_HTL0_CADOUT_H3

AC2

P0_HTL0_CADOUT_L3

AC3

P0_HTL0_CADOUT_H2

AD1

P0_HTL0_CADOUT_L2

AC1

P0_HTL0_CADOUT_H1

AE2

P0_HTL0_CADOUT_L1

AE3

P0_HTL0_CADOUT_H0

AF1

P0_HTL0_CADOUT_L0

AE1

P0_HTL0_CLKOUT_H1

AB4

AB3

P0_HTL0_CLKOUT_H0

AB1

P0_HTL0_CLKOUT_L0

AA1

P0_HTL0_CTRLOUT_H

U2

P0_HTL0_CTRLOUT_L

U3

P0_HTL0_CADOUT_H15 41

P0_HTL0_CADOUT_L15 41

P0_HTL0_CADOUT_H14 41

P0_HTL0_CADOUT_L14 41

P0_HTL0_CADOUT_H13 41

P0_HTL0_CADOUT_L13 41

P0_HTL0_CADOUT_H12 41

P0_HTL0_CADOUT_L12 41

P0_HTL0_CADOUT_H11 41

P0_HTL0_CADOUT_L11 41

P0_HTL0_CADOUT_H10 41

P0_HTL0_CADOUT_L10 41

P0_HTL0_CADOUT_H9 41

P0_HTL0_CADOUT_L9 41

P0_HTL0_CADOUT_H8 41

P0_HTL0_CADOUT_L8 41

P0_HTL0_CADOUT_H7 41

P0_HTL0_CADOUT_L7 41

P0_HTL0_CADOUT_H6 41

P0_HTL0_CADOUT_L6 41

P0_HTL0_CADOUT_H5 41

P0_HTL0_CADOUT_L5 41

P0_HTL0_CADOUT_H4 41

P0_HTL0_CADOUT_L4 41

P0_HTL0_CADOUT_H3 41

P0_HTL0_CADOUT_L3 41

P0_HTL0_CADOUT_H2 41

P0_HTL0_CADOUT_L2 41

P0_HTL0_CADOUT_H1 41

P0_HTL0_CADOUT_L1 41

P0_HTL0_CADOUT_H0 41

P0_HTL0_CADOUT_L0 41

P0_HTL0_CLKOUT_H1 41

P0_HTL0_CLKOUT_L1 41

P0_HTL0_CLKOUT_H0 41

P0_HTL0_CLKOUT_L0 41

P0_HTL0_CTRLOUT_H 41

P0_HTL0_CTRLOUT_L 41

P0_HTL1_CADIN_H1522

P0_HTL1_CADIN_L1522

P0_HTL1_CADIN_H1422

P0_HTL1_CADIN_L1422

P0_HTL1_CADIN_L1322

P0_HTL1_CADIN_H1222

P0_HTL1_CADIN_L1222

P0_HTL1_CADIN_H1122

P0_HTL1_CADIN_L1122

P0_HTL1_CADIN_H1022

P0_HTL1_CADIN_L1022

P0_HTL1_CADIN_H922

P0_HTL1_CADIN_L922

P0_HTL1_CADIN_H822

P0_HTL1_CADIN_L822

P0_HTL1_CADIN_H722

P0_HTL1_CADIN_L722

P0_HTL1_CADIN_H622

P0_HTL1_CADIN_L622

P0_HTL1_CADIN_H522

P0_HTL1_CADIN_L522

P0_HTL1_CADIN_H422

P0_HTL1_CADIN_L422

P0_HTL1_CADIN_H322

P0_HTL1_CADIN_L322

P0_HTL1_CADIN_H222

P0_HTL1_CADIN_L222

P0_HTL1_CADIN_H122

P0_HTL1_CADIN_L122

P0_HTL1_CADIN_H022

P0_HTL1_CADIN_L022

P0_HTL1_CLKIN_H122

P0_HTL1_CLKIN_L122

P0_HTL1_CLKIN_H022

P0_HTL1_CLKIN_L022

P0_HTL1_CTRLIN_H22

P0_HTL1_CTRLIN_L22

3

P1V2_HT

P0_HTL1_CADIN_H15

P0_HTL1_CADIN_L15

P0_HTL1_CADIN_H14

P0_HTL1_CADIN_L14

P0_HTL1_CADIN_H13

P0_HTL1_CADIN_L13

P0_HTL1_CADIN_H12

P0_HTL1_CADIN_L12

P0_HTL1_CADIN_H11

P0_HTL1_CADIN_L11

P0_HTL1_CADIN_H10

P0_HTL1_CADIN_L10

P0_HTL1_CADIN_H9

P0_HTL1_CADIN_L9

P0_HTL1_CADIN_H8

P0_HTL1_CADIN_L8

P0_HTL1_CADIN_H7

P0_HTL1_CADIN_L7

P0_HTL1_CADIN_H6

P0_HTL1_CADIN_L6

P0_HTL1_CADIN_H5

P0_HTL1_CADIN_L5

P0_HTL1_CADIN_H4

P0_HTL1_CADIN_L4

P0_HTL1_CADIN_H3

P0_HTL1_CADIN_L3

P0_HTL1_CADIN_H2

P0_HTL1_CADIN_L2

P0_HTL1_CADIN_H1

P0_HTL1_CADIN_L1

P0_HTL1_CADIN_H0

P0_HTL1_CADIN_L0

P0_HTL1_CLKIN_H1

P0_HTL1_CLKIN_L1

P0_HTL1_CLKIN_H0

P0_HTL1_CLKIN_L0

P0_HTL1_CTRLIN_H

P0_HTL1_CTRLIN_L

TP1 TP2

TP3

K10

J11

H10

H8

K14

J15

K16

J16

J9

E14

E13

C15

D15

E16

E15

C17

D17

C19

D19

E20

E19

C21

D21

E22

E21

C14

B14

A16

A15

C16

B16

A18

A17

A20

A19

C20

B20

A22

A21

C22

B22

E18

E17

C18

B18

A14

A13

C13

D13

CPU0E

VLDT_1(1)

VLDT_1(2)

VLDT_1(3)

VLDT_1(4)

VLDT_1(5)

VLDT_1(6)

VLDT_1(7)

VLDT_1(8)

VLDT_1(9)

L1_CADIN_H(15)

L1_CADIN_L(15)

L1_CADIN_H(14)

L1_CADIN_L(14)

L1_CADIN_H(13)

L1_CADIN_L(13)

L1_CADIN_H(12)

L1_CADIN_L(12)

L1_CADIN_H(11)

L1_CADIN_L(11)

L1_CADIN_H(10)

L1_CADIN_L(10)

L1_CADIN_H(9)

L1_CADIN_L(9)

L1_CADIN_H(8)

L1_CADIN_L(8)

L1_CADIN_H(7)

L1_CADIN_L(7)

L1_CADIN_H(6)

L1_CADIN_L(6)

L1_CADIN_H(5)

L1_CADIN_L(5)

L1_CADIN_H(4)

L1_CADIN_L(4)

L1_CADIN_H(3)

L1_CADIN_L(3)

L1_CADIN_H(2)

L1_CADIN_L(2)

L1_CADIN_H(1)

L1_CADIN_L(1)

L1_CADIN_H(0)

L1_CADIN_L(0)

L1_CLKIN_H(1)

L1_CLKIN_L(1)

L1_CLKIN_H(0)

L1_CLKIN_L(0)

L1_CTLIN_H(0)

L1_CTLIN_L(0)

L1_RSVD1

L1_RSVD2

Opteron

2

L1_CADOUT_H(15)

L1_CADOUT_L(15)

L1_CADOUT_H(14)

L1_CADOUT_L(14)

L1_CADOUT_H(13)

L1_CADOUT_L(13)

L1_CADOUT_H(12)

L1_CADOUT_L(12)

L1_CADOUT_H(11)

L1_CADOUT_L(11)

L1_CADOUT_H(10)

L1_CADOUT_L(10)

L1_CADOUT_H(9)

L1_CADOUT_L(9)

L1_CADOUT_H(8)

L1_CADOUT_L(8)

L1_CADOUT_H(7)

L1_CADOUT_L(7)

L1_CADOUT_H(6)

L1_CADOUT_L(6)

L1_CADOUT_H(5)

L1_CADOUT_L(5)

L1_CADOUT_H(4)

L1_CADOUT_L(4)

L1_CADOUT_H(3)

L1_CADOUT_L(3)

L1_CADOUT_H(2)

L1_CADOUT_L(2)

L1_CADOUT_H(1)

L1_CADOUT_L(1)

L1_CADOUT_H(0)

L1_CADOUT_L(0)

L1_CLKOUT_H(1)

L1_CLKOUT_L(1)

L1_CLKOUT_H(0)

L1_CLKOUT_L(0)

L1_CTLOUT_H(0)

L1_CTLOUT_L(0)

L1_RSVD3

L1_RSVD4

To Opteron1

P0_HTL1_CADOUT_H15

D11

P0_HTL1_CADOUT_L15

C11

P0_HTL1_CADOUT_H14

E9

P0_HTL1_CADOUT_L14

E10

P0_HTL1_CADOUT_H13

D9

P0_HTL1_CADOUT_L13

C9

P0_HTL1_CADOUT_H12

E7

P0_HTL1_CADOUT_L12

E8

P0_HTL1_CADOUT_H11

E5

P0_HTL1_CADOUT_L11

E6

P0_HTL1_CADOUT_H10

D5

P0_HTL1_CADOUT_L10

C5

P0_HTL1_CADOUT_H9

E3

P0_HTL1_CADOUT_L9

E4

P0_HTL1_CADOUT_H8

D3

P0_HTL1_CADOUT_L8

C3

P0_HTL1_CADOUT_H7

A11

P0_HTL1_CADOUT_L7

A12

P0_HTL1_CADOUT_H6

B10

P0_HTL1_CADOUT_L6

C10

P0_HTL1_CADOUT_H5

A9

P0_HTL1_CADOUT_L5

A10

P0_HTL1_CADOUT_H4

B8

P0_HTL1_CADOUT_L4

C8

P0_HTL1_CADOUT_H3

B6

P0_HTL1_CADOUT_L3

C6

P0_HTL1_CADOUT_H2

A5

P0_HTL1_CADOUT_L2

A6

P0_HTL1_CADOUT_H1

B4

P0_HTL1_CADOUT_L1

C4

P0_HTL1_CADOUT_H0

A3

P0_HTL1_CADOUT_L0

A4

P0_HTL1_CLKOUT_H1

D7

P0_HTL1_CLKOUT_L1

C7

P0_HTL1_CLKOUT_H0

A7

P0_HTL1_CLKOUT_L0

A8

P0_HTL1_CTRLOUT_H

B12

P0_HTL1_CTRLOUT_L

C12

E11

E12

P0_HTL1_CADOUT_H15 22

P0_HTL1_CADOUT_L15 22

P0_HTL1_CADOUT_H14 22

P0_HTL1_CADOUT_L14 22

P0_HTL1_CADOUT_H13 22P0_HTL1_CADIN_H1322

P0_HTL1_CADOUT_L13 22

P0_HTL1_CADOUT_H12 22

P0_HTL1_CADOUT_L12 22

P0_HTL1_CADOUT_H11 22

P0_HTL1_CADOUT_L11 22

P0_HTL1_CADOUT_H10 22

P0_HTL1_CADOUT_L10 22

P0_HTL1_CADOUT_H9 22

P0_HTL1_CADOUT_L9 22

P0_HTL1_CADOUT_H8 22

P0_HTL1_CADOUT_L8 22

P0_HTL1_CADOUT_H7 22

P0_HTL1_CADOUT_L7 22

P0_HTL1_CADOUT_H6 22

P0_HTL1_CADOUT_L6 22

P0_HTL1_CADOUT_H5 22

P0_HTL1_CADOUT_L5 22

P0_HTL1_CADOUT_H4 22

P0_HTL1_CADOUT_L4 22

P0_HTL1_CADOUT_H3 22

P0_HTL1_CADOUT_L3 22

P0_HTL1_CADOUT_H2 22

P0_HTL1_CADOUT_L2 22

P0_HTL1_CADOUT_H1 22

P0_HTL1_CADOUT_L1 22

P0_HTL1_CADOUT_H0 22

P0_HTL1_CADOUT_L0 22

P0_HTL1_CLKOUT_H1 22

P0_HTL1_CLKOUT_L1 22

P0_HTL1_CLKOUT_H0 22

P0_HTL1_CLKOUT_L0 22

P0_HTL1_CTRLOUT_H 22

P0_HTL1_CTRLOUT_L 22

TP4

1

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 LDT Link0 & Link1

GA-2CEWH-FS

1

881Monday, July 04, 2005

of

1.0

5

4

3

2

1

D D

P0_HTL2_CADIN_H[15..0]37

P0_HTL2_CADIN_L[15..0]37

P0_HTL2_CADIN_H1537

P0_HTL2_CADIN_L1537

P0_HTL2_CADIN_H1437

P0_HTL2_CADIN_L1437

P0_HTL2_CADIN_H1337

P0_HTL2_CADIN_L1337

P0_HTL2_CADIN_H1237

P0_HTL2_CADIN_L1237

P0_HTL2_CADIN_H1137

P0_HTL2_CADIN_L1137

P0_HTL2_CADIN_H1037

P0_HTL2_CADIN_L1037

P0_HTL2_CADIN_H937

P0_HTL2_CADIN_L937

P0_HTL2_CADIN_H837

P0_HTL2_CADIN_L837

P0_HTL2_CADIN_H737

C C

B B

P0_HTL2_CADIN_L737

P0_HTL2_CADIN_H637

P0_HTL2_CADIN_L637

P0_HTL2_CADIN_L537

P0_HTL2_CADIN_L437

P0_HTL2_CADIN_H337

P0_HTL2_CADIN_L337

P0_HTL2_CADIN_H237

P0_HTL2_CADIN_L237

P0_HTL2_CADIN_H137

P0_HTL2_CADIN_L137

P0_HTL2_CADIN_H037

P0_HTL2_CADIN_L037

P0_HTL2_CLKIN_H137

P0_HTL2_CLKIN_L137

P0_HTL2_CLKIN_H037

P0_HTL2_CLKIN_L037

P0_HTL2_CTRLIN_H37

P0_HTL2_CTRLIN_L37

P0_HTL2_CADIN_H15

P0_HTL2_CADIN_L15

P0_HTL2_CADIN_H14

P0_HTL2_CADIN_L14

P0_HTL2_CADIN_H13

P0_HTL2_CADIN_L13

P0_HTL2_CADIN_H12

P0_HTL2_CADIN_L12

P0_HTL2_CADIN_H11

P0_HTL2_CADIN_L11

P0_HTL2_CADIN_H10

P0_HTL2_CADIN_L10

P0_HTL2_CADIN_H9

P0_HTL2_CADIN_L9

P0_HTL2_CADIN_H8

P0_HTL2_CADIN_L8

P0_HTL2_CADIN_H7

P0_HTL2_CADIN_L7

P0_HTL2_CADIN_H6

P0_HTL2_CADIN_L6

P0_HTL2_CADIN_H5

P0_HTL2_CADIN_L5

P0_HTL2_CADIN_H4

P0_HTL2_CADIN_L4

P0_HTL2_CADIN_H3

P0_HTL2_CADIN_L3

P0_HTL2_CADIN_H2

P0_HTL2_CADIN_L2

P0_HTL2_CADIN_H1

P0_HTL2_CADIN_L1

P0_HTL2_CADIN_H0

P0_HTL2_CADIN_L0

P0_HTL2_CLKIN_H1

P0_HTL2_CLKIN_L1

P0_HTL2_CLKIN_H0

P0_HTL2_CLKIN_L0

P0_HTL2_CTRLIN_H

P0_HTL2_CTRLIN_L

TP5

TP7

P1V2_HT

AB10

AC11

AD10

AD8

AB14

AC15

AB16

AC16

AC9

AG11

AG12

AJ10

AH10

AG9

AG10

AJ8

AH8

AJ6

AH6

AG5

AG6

AJ4

AH4

AG3

AG4

AJ11

AK11

AL9

AL10

AJ9

AK9

AL7

AL8

AL5

AL6

AJ5

AK5

AL3

AL4

AJ3

AK3

AG7

AG8

AJ7

AK7

AL11

AL12

AJ12

AH12

VLDT_2(1)

VLDT_2(2)

VLDT_2(3)

VLDT_2(4)

VLDT_2(5)

VLDT_2(6)

VLDT_2(7)

VLDT_2(8)

VLDT_2(9)

L2_CADIN_H(15)

L2_CADIN_L(15)

L2_CADIN_H(14)

L2_CADIN_L(14)

L2_CADIN_H(13)

L2_CADIN_L(13)

L2_CADIN_H(12)

L2_CADIN_L(12)

L2_CADIN_H(11)

L2_CADIN_L(11)

L2_CADIN_H(10)

L2_CADIN_L(10)

L2_CADIN_H(9)

L2_CADIN_L(9)

L2_CADIN_H(8)

L2_CADIN_L(8)

L2_CADIN_H(7)

L2_CADIN_L(7)

L2_CADIN_H(6)

L2_CADIN_L(6)

L2_CADIN_H(5)

L2_CADIN_L(5)

L2_CADIN_H(4)

L2_CADIN_L(4)

L2_CADIN_H(3)

L2_CADIN_L(3)

L2_CADIN_H(2)

L2_CADIN_L(2)

L2_CADIN_H(1)

L2_CADIN_L(1)

L2_CADIN_H(0)

L2_CADIN_L(0)

L2_CLKIN_H(1)

L2_CLKIN_L(1)

L2_CLKIN_H(0)

L2_CLKIN_L(0)

L2_CTLIN_H(0)

L2_CTLIN_L(0)

L2_RSVD1

L2_RSVD2

Opteron

CPU0F

L2_CADOUT_H(15)

L2_CADOUT_L(15)

L2_CADOUT_H(14)

L2_CADOUT_L(14)

L2_CADOUT_H(13)

L2_CADOUT_L(13)

L2_CADOUT_H(12)

L2_CADOUT_L(12)

L2_CADOUT_H(11)

L2_CADOUT_L(11)

L2_CADOUT_H(10)

L2_CADOUT_L(10)

L2_CADOUT_H(9)

L2_CADOUT_L(9)

L2_CADOUT_H(8)

L2_CADOUT_L(8)

L2_CADOUT_H(7)

L2_CADOUT_L(7)

L2_CADOUT_H(6)

L2_CADOUT_L(6)

L2_CADOUT_H(5)

L2_CADOUT_L(5)

L2_CADOUT_H(4)

L2_CADOUT_L(4)

L2_CADOUT_H(3)

L2_CADOUT_L(3)

L2_CADOUT_H(2)

L2_CADOUT_L(2)

L2_CADOUT_H(1)

L2_CADOUT_L(1)

L2_CADOUT_H(0)

L2_CADOUT_L(0)

L2_CLKOUT_H(1)

L2_CLKOUT_L(1)

L2_CLKOUT_H(0)

L2_CLKOUT_L(0)

L2_CTLOUT_H(0)

L2_CTLOUT_L(0)

L2_RSVD3

L2_RSVD4

TO AMD-8132

P0_HTL2_CADOUT_H15

AH14

P0_HTL2_CADOUT_L15

AJ14

P0_HTL2_CADOUT_H14

AG16

P0_HTL2_CADOUT_L14

AG15

P0_HTL2_CADOUT_H13

AH16

P0_HTL2_CADOUT_L13

AJ16

P0_HTL2_CADOUT_H12

AG18

P0_HTL2_CADOUT_L12

AG17

P0_HTL2_CADOUT_H11

AG20

P0_HTL2_CADOUT_L11

AG19

P0_HTL2_CADOUT_H10

AH20

P0_HTL2_CADOUT_L10

AJ20

P0_HTL2_CADOUT_H9

AG22

P0_HTL2_CADOUT_L9

AG21

P0_HTL2_CADOUT_H8

AH22

P0_HTL2_CADOUT_L8

AJ22

P0_HTL2_CADOUT_H7

AL14

P0_HTL2_CADOUT_L7

AL13

P0_HTL2_CADOUT_H6

AK15

P0_HTL2_CADOUT_L6

AJ15

P0_HTL2_CADOUT_H5

AL16

P0_HTL2_CADOUT_L5

AL15

P0_HTL2_CADOUT_H4

AK17

P0_HTL2_CADOUT_L4

AJ17

P0_HTL2_CADOUT_H3

AK19

P0_HTL2_CADOUT_L3

AJ19

P0_HTL2_CADOUT_H2

AL20

P0_HTL2_CADOUT_L2

AL19

P0_HTL2_CADOUT_H1

AK21

P0_HTL2_CADOUT_L1

AJ21

P0_HTL2_CADOUT_H0

AL22

P0_HTL2_CADOUT_L0

AL21

P0_HTL2_CLKOUT_H1

AH18

P0_HTL2_CLKOUT_L1

AJ18

P0_HTL2_CLKOUT_H0

AL18

P0_HTL2_CLKOUT_L0

AL17

P0_HTL2_CTRLOUT_H

AK13

P0_HTL2_CTRLOUT_L

AJ13

AG13

AG14

P0_HTL2_CADOUT_H[15..0] 37

P0_HTL2_CADOUT_L[15..0] 37

P0_HTL2_CADOUT_H15 37

P0_HTL2_CADOUT_L15 37

P0_HTL2_CADOUT_H14 37

P0_HTL2_CADOUT_L14 37

P0_HTL2_CADOUT_H13 37

P0_HTL2_CADOUT_L13 37

P0_HTL2_CADOUT_H12 37

P0_HTL2_CADOUT_L12 37

P0_HTL2_CADOUT_H11 37

P0_HTL2_CADOUT_L11 37

P0_HTL2_CADOUT_H10 37

P0_HTL2_CADOUT_L10 37

P0_HTL2_CADOUT_H9 37

P0_HTL2_CADOUT_L9 37

P0_HTL2_CADOUT_H8 37

P0_HTL2_CADOUT_L8 37

P0_HTL2_CADOUT_H7 37

P0_HTL2_CADOUT_L7 37

P0_HTL2_CADOUT_H6 37

P0_HTL2_CADOUT_L6 37

P0_HTL2_CADOUT_H5 37P0_HTL2_CADIN_H537

P0_HTL2_CADOUT_L5 37

P0_HTL2_CADOUT_H4 37P0_HTL2_CADIN_H437

P0_HTL2_CADOUT_L4 37

P0_HTL2_CADOUT_H3 37

P0_HTL2_CADOUT_L3 37

P0_HTL2_CADOUT_H2 37

P0_HTL2_CADOUT_L2 37

P0_HTL2_CADOUT_H1 37

P0_HTL2_CADOUT_L1 37

P0_HTL2_CADOUT_H0 37

P0_HTL2_CADOUT_L0 37

P0_HTL2_CLKOUT_H1 37

P0_HTL2_CLKOUT_L1 37

P0_HTL2_CLKOUT_H0 37

P0_HTL2_CLKOUT_L0 37

P0_HTL2_CTRLOUT_H 37

P0_HTL2_CTRLOUT_L 37

TP6

TP8

LDT 0

LDT 1

MEMORY

LDT 2

POWER SUPPLIES OF OPTERON

POWER PLANE TYPICAL

VTT

VDDIO

2.8A 850mA

VDDA

VDD

VLDT

A A

5

4

MAX

S0 state S3 state

200mA

200mA

2.9A

33mA

60A

(2.4G, 1.4 V _ 1 . 3 5 V_VID, 85.3W)

1.5A

(3 16X16 HT running at 1.6GT/s)

Title

Size Document Number Rev

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 LDT Link2

GA-2CEWH-FS

1

981Monday, July 04, 2005

of

1.0

5

4

3

2

1

Trace 50 mils width , 500 ~ 700 mils long , Short as possible

G16

H16

G14

H14

AE6

AE7

AD7

AF7

AE10

AE11

AF11

AE13

AE12

AF13

AF15

AE14

G12

AG1

AH2

AA6

AC6

C1

D2

C2

E1

D1

L7

L6

K7

J7

T3

T4

L8

K8

J6

F12

H9

AJ2

N6

Placed just

outside

keepout

C3

1000P/6/X/50V

VDDA1

VDDA2

VDDA3

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORESENSE_H

CLKIN_H

CLKIN_L

NC_G14

NC_H14

TMS

TCK

TRST_L

TDI

DBREQ_L

NC_AE10

NC_AE11

NC_AF11

NC_AE13

NC_AE12

NC_T3

NC_T4

NC_AF13

NC_L8

NC_K8

NC_AF15

NC_AE14

RESET_L

LDTSTOP_L

PWROK

NC

NC

NC

NC

NC

NC

NC

C4

1000P/6/X/50V

CPU0C

Opteron

THERMTRIP_L

THERMDA

THERMDC

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

NC_H13

NC_G6

NC_F7

NC_H12

FBCLKOUT_H

FBCLKOUT_L

TDO

DBRDY

NC_V5

NC_U5

NC_H7

NC_T7

NC_W6

NC_R6

NC_U6

VTT

VTT

RSVD_SMBUSC

RSVD_SMBUSD

P0_VDD_2D5V

R1

W/S = 10 /10 mils ( Routed the as differential signals )

680

O.D

signal

AE15

P0_THERMDA

AJ1

P0_THERMDC

AH1

P0_VID4_R

G9

P0_VID3_R

F9

P0_VID2_R

G10

P0_VID1_R

H11

P0_VID0_R

G11

P0_NC_H13

H13

P0_NC_G6

G6

P0_NC_F7

F7

P0_NC_H12

H12

P0_FBCLKOUT_PIN_H

G18

P0_FBCLKOUT_PIN_L

H18

P0_THERMTRIP#

L < 0.5 " , Routed 5/5/5

SR_P0_TDO

AE8

SR_P0_DBRDY

G8

V5

TP12

U5

TP13

H7

TP14

P0_NC_T7 P0_NC_T7

T7

W6

P0_NC_R6

R6

P0_NC_U6

U6

P0_VTT_DDR

F21

AF18

AF9

AE9

P0_THERMDA 77

P0_THERMDC 77

R15 560

R16 560

R17 560

R18 560

R19 560

TP9

TP11

SR_P0_TDO 79

P0_NC_W6P0_NC_W6

P0_NC_U6

P0_NC_R6

TP18

TP19

P0_THERMTRIP# 41

P0_VID4 71

P0_VID3 71

P0_VID2 71

P0_VID1 71

P0_VID0 71

Place in windows

RN1 680/8P4R

1

2

3

4

5

6

7

8

GND

CPU

For break out only route 5/5/5

then route 20/8/5/8/20 for

1000 mils to resistor

SR_P0_FBCLKOUT_PIN_H

SR_P0_FBCLKOUT_PIN_L

L<1" Routed 20/8/5/8/20

P0_VDDA_2D5V

FB1

D D

P0_L0_REF1

P0_L0_REF0

C6

1000P/6/X/50V

Place together but not

critical to be close P0

C C

B B

GND GND

CPU0_CPUCLK36

CPU0_CPUCLK#36

Place these parts

near socket window

as possible

P0_CPU_RST#79

P0_HT_STOP#79

P0_CPU_PWRGD79

33mA

C7

1000P/6/X/50V

R4

0

R7

0

R1189 0

FB30/8

P1V2_HT

GND

C8 3900P/6/X/50V

DC Blocking

Caps

C9 3900P/6/X/50V

P0_VDD_2D5V

R20 680/X

R21 680/X

P0_VDDA

C5

4.7U/1206/X/10V

GND GND GND

R2 43.2/1%

R3 43.2/1%

P0_COREFB_P71

P0_COREFB_N71

169/1%

SR_P0_TMS79

SR_P0_TCK79

SR_P0_TRST_L79

SR_P0_TDI79

SR_P0_DBREQ_L79 SR_P0_DBRDY 79

C10

0.01U/6/X/50V

R22 680/X

R1310 0/6

Delete R1190

P1V2_HT P1V2_HT

R34

49.9/1%

SCANIN_L SCANIN_H

A A

R36

49.9/1%/X

R35

49.9/1%/X

R37

49.9/1%

0.22U/6/X/16V

C1

TP10

R5

3300P/6/X/50V

C2

P0_L0_REF1

P0_L0_REF0

P0_COREFB_P

P0_COREFB_N

P0_CORESENSE_H

Trace Length

< 0.5 "

P0_CPUCLK_TER_H

P0_CPUCLK_TER_L

P0_NC_G14

P0_NC_H14

SR_P0_TMS

SR_P0_TCK

SR_P0_TRST_L

SR_P0_TDI

SR_P0_DBREQ_L

P0_NC_AE10

P0_NC_AE11

P0_NC_AF11

P0_NC_AE13

P0_NC_AE12

SCANIN_H

SCANIN_L

P0_NC_AF13

TP15

TP16

TP17

P0_NC_AE14

P0_CPU_RST#

CPU0_HT_STOP#

CPU0_PWRGD

TP20

TP21

TP22

TP23

TP24

TP25

TP26

Length L1=L2

Length L3=L4

L1

L2

R6

80.6/1%

L3

R

L4

R

SR_P0_TDO

SR_P0_DBRDY

SR_P0_TMS

SR_P0_TCK

SR_P0_TRST_L

SR_P0_TDI

SR_P0_DBREQ_L

P0_NC_AE14

P0_NC_AF13

P0_NC_G14

P0_NC_H14

P0_NC_AF11

P0_NC_AE10

P0_NC_AE11

P0_NC_AE12

P0_NC_AE13

P0_NC_F7

P0_NC_H12

Strapping

R

R8 1K/X

R9 1K/X

R10 1K/X

R11 1K/X

R12 1K/X

R13 1K/X

R14 1K/X

R23 680

R24 680

R25 820

R26 820

R27 680

R28 680

R29 680

R30 680

R31 680

R32 680

R33 680

P0_VDD_2D5V

GND

GNDGND

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 MISC

GA-2CEWH-FS

1

of

10 81Monday, July 04, 2005

1.0

5

P0_VDD_2D5V

4

TP27

TP28

TP30 TP31

TP29

P0_VDDIO_SENSE 14

3

2

P0_VDD_CORE

1

L19

W21

AA21

J21

M22

P22

T22

V22

Y22

AB22

AJ23

AA19

C23

E23

K26

T26

AE28

G26

N26

W26

AE26

AG23

K20

D28

K28

T28

AB28

AH28

AH26

G28

N28

W28

AB26

AB20

L21

N21

R21

U21

H22

D26

K22

A23

U23

AL23

AC21

AD22

AB23

AC23

VDDIO47

VDDIO48

AF20

VDDIOFB_L

VDDIOFB_H

VDDIO_SENSE

D D

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

F17

VSS6

P19

AB13

AC22

AD13

AA10

AC10

AK10

N30

T13

AB2

AF2

AK2

AH3

V13

AC4

AB7

AD6

AK6

F14

Y13

AA8

AF8

G17

AB9

AD9

D10

N10

R10

U10

B11

H15

K11

VSS7

VSS8

F1

VSS9

F2

VSS10

K2

VSS11

P2

VSS12

VSS92

V2

VSS13

VSS14

VSS15

VSS16

B3

VSS17

VSS18

G4

VSS19

L4

VSS20

R4

VSS21

VSS93

W4

VSS22

VSS23

F5

VSS24

D6

VSS25

H6

VSS26

M7

VSS27

VSS28

Y6

VSS29

VSS30

J17

VSS94

VSS31

B7

VSS32

VSS33

P7

VSS34

V7

VSS35

Y7

VSS36

M6

VSS37

VSS95

N8

VSS38

R8

VSS39

U8

VSS40

W8

VSS41

VSS42

VSS43

F8

VSS44

VSS45

K9

VSS46

VSS96

M9

VSS47

P9

VSS48

VSS49

VSS50

Y9

VSS51

VSS52

VSS53

VSS54

J10

VSS55

VSS97

L10

VSS56

VSS57

VSS58

VSS59

T6

VSS60

VSS61

VSS62

VSS63

VSS64

L14

VSS98

VSS65

J8

VSS66

VSS67

P3V3_DUAL

R42

4.7K

Lo : P0 present

Hi : P0 absent

C C

B B

V6

AD12H2AA4

VDD117

VDD1

VDD118

T18

VDD2

V18

VDD3

Y18

VDD4

K12

VDD5

F19

N19

VDD7

VDD119

R19

VDD8

U19

VDD9

W19

VDD10

VDD11

D20

AE4

VDD12

M20

VDD13

VDD14

P20

VDD15

T20

VDD16

V20

VDD17

Y20

VDD18

AK20

VDD19

B21

AH21

AK4B5AH5K6P6T8AB6

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

AF6M2F6D8G7

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

AB8

AK8B9K18L9N9R9T2U9W9

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

AA9

VDD44

AB18

VDD45

AH9

VDD46

W13

VDD47

M10

VDD48

P10

VDD49

T10

VDD50

V10Y2Y10

VDD51

VDD52

AB12

VDD53

VDD54

AF10

VDD55

F11

VDD56

L11

N11

VDD57

R11

VDD58

VDD59

U11

VDD60

W11

VDD61

AA11

VDD62

AD2

VDD63

CPU0D

Opteron

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD95

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

D12

M12

P12

T12

V12

Y12

AC13

AK12

B13

L13

D4

N13

R13

U13

AA13

AH13

J13

M14

P14

T14

J4

V14

Y14

AD14

AF14

F15

L15

N15

R15

U15

W15

N4

AA15

D16

F18

M16

P16

T16

V16

Y16

AD16

AK16

U4

B17

L17

N17

R17

U17

W17

AA17

AH17

M18

P18

VSS68

VSS69

VSS70

VSS71

VSS99

VSS72

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS101

VSS90

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS100

VSS81

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS182

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS183

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS184

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS185

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS186

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS187

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS188

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS189

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS190

VSS181

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS1

VSS2

VSS3

VSS4

VSS203

VSS202

VSS91

VSS5

VSS200

VSS201

M11

P11

T11

V11

N14

Y11

AA12

N16

AF12

F13

G15

F10

AD15

K13

U14

M13

AB11

AD11

AH11

G13

J12

N12

R12

U12

R14

W12

W14

AA14

AC14

AH15

AK14

B15

K15

M15

B23

P15

T15

V15

Y15

AB15

D14

J14

H17

G24

L16

R16

U16

W18

AA16

AC17

AF16

F16

K17

N24

M17

P17

T17

V17

Y17

AB17

AD17

D18

J18

W24

L18

N18

R18

U18

W10

AA18

AE17

AK18

B19

G30

K19

M19

T19

V19

Y19

AB19

AH19

J20

L20

W30

N20

R20

U20

W20

AA20

AC20

AF21

K21

M21

AB24

P21

T21

V21

Y21

AB21

D22

G22

L22

N22

B26

R22

U22

W22

AA22

AE22

AK22

J22

AE24

AK26

B29

AK23

K24

T24

AE30

AK29

D30

K30

T30

AB30

AH30

AH7V9L12

AC12T9AG2E2P13

W16

D23

AH23

A A

GND

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 Power / GND

GA-2CEWH-FS

1

11 81Monday, July 04, 2005

of

1.0

5

4

3

2

1

P5V

Q133

R46

110/1%

R49

100/1%

P0_VDDA_2D5V

C13

10U/1206/X/6.3V

0.01U/6/X/50V

GND

P0_VDDA_2D5V_PG 66

1

D D

C11

2.2U/8/Y/25V

GND

C12

0.1U/6/X/16V

P0_VDDA_2D5V_EN66

GND

2

3 4

R48

1K

GND

AME8824AEEY/SOT23-6

VIN

VOUT

GND

EN PG

P3V3

6

5

ADJ

GND

R52

P0_VDDA_2D5V_PG

2.5V/300 mA

C14

C15

0.1U/6/X/16V

GND

P0_VDDA_2D5V

C16

1U/6/X/16V

4.7K

P5V_DUAL

R53

3.9K/1%

GND

R56

1K/1%

0.9V

C19

0.1U/6/X/16V

R58 0

R54 1M/X

P5V_DUAL

U11A

84

3

+

1

2

-

C1528

0.1U/6/X/16V/X

GND

P0_VTT_DDR P0_VTT_DDR

LM393

set 0.9V

GND

P0_VDD_2D5V

C39 0.01U/6/X/50V

C50 0.01U/6/X/50V/B

C61 0.01U/6/X/50V

C72 0.01U/6/X/50V/B

C82 0.01U/6/X/50V

C92 0.01U/6/X/50V

C102 0.01U/6/X/50V/B

P5V_DUAL

C C

P0_VTT_DDR

P0_VTT_DDR

C21 0.1U/6/X/16V

P0_VTT_DDR P0_VTT_DDR P0_VDD_2D5V

B B

C34 0.1U/6/X/16V/B

C41 0.1U/6/X/16V/B

C45 0.1U/6/X/16V

C52 0.1U/6/X/16V/B

C56 0.1U/6/X/16V/B

C63 0.1U/6/X/16V/B

C67 0.1U/6/X/16V

C73 0.1U/6/X/16V

C77 0.1U/6/X/16V

C83 0.1U/6/X/16V/B

C87 0.1U/6/X/16V/B

C93 0.1U/6/X/16V

C103 0.1U/6/X/16V/B

C107 0.1U/6/X/16V

C113 0.1U/6/X/16V/B

C116 0.1U/6/X/16V

C118 1U/6/X/16V

C122 1U/6/X/16V/B

C22 0.1U/6/X/16V

C23 0.1U/6/X/16V

C25 0.1U/6/X/16V

C27 0.1U/6/X/16V

C31 0.1U/6/X/16V/B

C35 0.1U/6/X/16V

C42 0.1U/6/X/16V/B

C46 0.1U/6/X/16V/B

C53 0.1U/6/X/16V/B

C57 0.1U/6/X/16V/B

C64 0.1U/6/X/16V

C68 0.1U/6/X/16V

C74 0.1U/6/X/16V/B

C78 0.1U/6/X/16V

C84 0.1U/6/X/16V

C88 0.1U/6/X/16V

C94 0.1U/6/X/16V

C98 0.1U/6/X/16V/BC97 0.1U/6/X/16V/B

C104 0.1U/6/X/16V/B

C108 0.1U/6/X/16V/B

C114 0.1U/6/X/16V/B

C119 1U/6/X/16V/B

C125 1U/6/X/16V

C129 10U/1206/X/6.3V

GND

GND

P0_VTT_DDR

C24 0.1U/6/X/16V

C26 0.1U/6/X/16V/B

C28 0.1U/6/X/16V

C32 0.1U/6/X/16V

C36 0.1U/6/X/16V/B

C43 0.1U/6/X/16V/B

C47 0.1U/6/X/16V/B

C54 0.1U/6/X/16V

C58 0.1U/6/X/16V

C65 0.1U/6/X/16V

C69 0.1U/6/X/16V

C75 0.1U/6/X/16V/B

C79 0.1U/6/X/16V/B

C85 0.1U/6/X/16V/B

C89 0.1U/6/X/16V/B

C95 0.1U/6/X/16V

C99 0.1U/6/X/16V

C105 0.1U/6/X/16V/B

C109 0.1U/6/X/16V/B

C120 1U/6/X/16V

C126 1U/6/X/16V/B

C130 10U/1206/X/6.3V

GND

P0_VTT_DDR

C29 0.1U/6/X/16V/B

C33 0.1U/6/X/16V/B

C37 0.1U/6/X/16V

C44 0.1U/6/X/16V/B

C48 0.1U/6/X/16V/B

C55 0.1U/6/X/16V

C59 0.1U/6/X/16V

C66 0.1U/6/X/16V

C70 0.1U/6/X/16V/B

C76 0.1U/6/X/16V

C80 0.1U/6/X/16V/B

C86 0.1U/6/X/16V/B

C90 0.1U/6/X/16V/B

C96 0.1U/6/X/16V

C100 0.1U/6/X/16V/B

C106 0.1U/6/X/16V/B

C110 0.1U/6/X/16V C112 0.01U/6/X/50V/B

C115 0.1U/6/X/16V

C121 1U/6/X/16V

C127 1U/6/X/16VC124 10U/1206/X/6.3V/B

C131 10U/1206/X/6.3V/B

GND

P0_VTT_DDR

C38 0.01U/6/X/50V

C49 0.01U/6/X/50V/B

C60 0.01U/6/X/50V/B

C71 0.01U/6/X/50V/B

C81 0.01U/6/X/50V

C91 0.01U/6/X/50V

C101 0.01U/6/X/50V

C111 0.01U/6/X/50V/B

C117 0.01U/6/X/50V/B

C123 0.01U/6/X/50V

C128 0.01U/6/X/50V

C132 0.01U/6/X/50V/B

R57

4.7K

C20

0.1U/6/X/16V

GND

C30 0.015u/6/X/50V

C40 0.015u/6/X/50V/B

C51 0.015u/6/X/50V

C62 0.015u/6/X/50V

P3V3_DUAL

R55

4.7K

3

D

GS

2

1

GND

P0_VTT_DDR_PG

Q2

2N7002

GND

P0_VTT_DDR_PG 66

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 MISC Power & VTT/ VDDIO Decoupling

GA-2CEWH-FS

1

12 81Monday, July 04, 2005

of

1.0

5

P0_VDD_2D5V

P0_VDD_2D5V

C1507

P0_MEMVREF

0.1U/6/X/16V

0221

4 4

Place close to CPU0

P0_VDD_2D5V

J1

1

2

3

PIN1X3

GND

3 3

GND

R60

100/1%

R62

100/1%

Close to CPU

P0_MEMDATA[127..64]19

GND

P0_MEMVREF

R59

42.2/1%

42.2/1%

R61

P3V3_DUALP3V3_DUAL

P0_VDD_2D5V

Q135

ECB

MMBT2222A

SOT23

R1267

10K

R1266

P0_VTT_DDR

2 2

10K

R1264

10K

DDR0_PWR_LED_C

Q136

MMBT2222A

SOT23

ECB

P0_DDRLED

LED/AMBER/SMD

R1265

220

12

12

P0_MEMDQS_UPR[17..0]19

P0_MEMDQS_LWR[17..0]19

1 1

5

GND

P0_VTT_SENSE14

C133

0.1U/6/X/16V

4

0221

P0_MEMDATA127

P0_MEMDATA126

P0_MEMDATA125

P0_MEMDATA124

P0_MEMDATA123

P0_MEMDATA122

P0_MEMDATA121

P0_MEMDATA120

P0_MEMDATA119

P0_MEMDATA118

P0_MEMDATA117

P0_MEMDATA116

P0_MEMDATA115

P0_MEMDATA114

P0_MEMDATA113

P0_MEMDATA112

P0_MEMDATA111

P0_MEMDATA110

P0_MEMDATA109

P0_MEMDATA108

P0_MEMDATA107

P0_MEMDATA106

P0_MEMDATA105

P0_MEMDATA104

P0_MEMDATA103

P0_MEMDATA102

P0_MEMDATA101

P0_MEMDATA100

P0_MEMDATA99

P0_MEMDATA98

P0_MEMDATA97

P0_MEMDATA96

P0_MEMDATA95

P0_MEMDATA94

P0_MEMDATA93

P0_MEMDATA92

P0_MEMDATA91

P0_MEMDATA90

P0_MEMDATA89

P0_MEMDATA88

P0_MEMDATA87

P0_MEMDATA86

P0_MEMDATA85

P0_MEMDATA84

P0_MEMDATA83

P0_MEMDATA82

P0_MEMDATA81

P0_MEMDATA80

P0_MEMDATA79

P0_MEMDATA78

P0_MEMDATA77

P0_MEMDATA76

P0_MEMDATA75

P0_MEMDATA74

P0_MEMDATA73

P0_MEMDATA72

P0_MEMDATA71

P0_MEMDATA70

P0_MEMDATA69

P0_MEMDATA68

P0_MEMDATA67

P0_MEMDATA66

P0_MEMDATA65

P0_MEMDATA64

P0_MEMDQS_UPR17

P0_MEMDQS_UPR16

P0_MEMDQS_UPR15

P0_MEMDQS_UPR14

P0_MEMDQS_UPR13

P0_MEMDQS_UPR12

P0_MEMDQS_UPR11

P0_MEMDQS_UPR10

P0_MEMDQS_UPR9

P0_MEMDQS_UPR8

P0_MEMDQS_UPR7

P0_MEMDQS_UPR6

P0_MEMDQS_UPR5

P0_MEMDQS_UPR4

P0_MEMDQS_UPR3

P0_MEMDQS_UPR2

P0_MEMDQS_UPR1

P0_MEMDQS_UPR0

P0_MEMDQS_LWR17

P0_MEMDQS_LWR16

P0_MEMDQS_LWR15

P0_MEMDQS_LWR14

P0_MEMDQS_LWR13

P0_MEMDQS_LWR12

P0_MEMDQS_LWR11

P0_MEMDQS_LWR10

P0_MEMDQS_LWR9

P0_MEMDQS_LWR8

P0_MEMDQS_LWR7

P0_MEMDQS_LWR6

P0_MEMDQS_LWR5

P0_MEMDQS_LWR4

P0_MEMDQS_LWR3

P0_MEMDQS_LWR2

P0_MEMDQS_LWR1

P0_MEMDQS_LWR0

4

P0_VTT_SENSE

>25 mils

>25 mils

C134

1000P/6/X/50V/X

P0_VTT_DDR

AG24

AG26

AG27

AG25

AG28

AC19

AE19

AE18

AC18

AF19

AF17

AE16

AF22

AH25

AH27

AF23

AH24

AF25

AJ26

AF26

AF28

AE29

AJ29

AH29

AE27

AD26

AD27

AC26

AA26

AA28

AD28

AC27

AB29

AA27

AF27

AB27

AF24

AC28

AJ25

AJ30

AD29

AA31

AL25

AL29

AE31

H19

F20

G19

F22

Y27

Y28

V28

U26

Y26

W27

V27

U27

P28

N29

M26

P27

P26

M27

K29

K27

H28

G29

H27

H26

F27

F26

D29

D27

G27

F28

E27

C27

C26

E25

D24

F23

E26

F25

E24

G23

R27

W29

N27

E29

F24

R28

V26

M28

E28

D25

U31

M30

H30

C30

B25

T31

Y29

M29

H29

C29

C25

J19

L28

L27

L26

J28

J27

J26

VTT6

VTT7

VTT4

VTT3

VTT2

VTT1

VTT8

VTT9

VTT_SENSE

MEMZN

MEMZP

MEMVREF0

MEMVREF1

MEMDATA(127)

MEMDATA(126)

MEMDATA(125)

MEMDATA(124)

MEMDATA(123)

MEMDATA(122)

MEMDATA(121)

MEMDATA(120)

MEMDATA(119)

MEMDATA(118)

MEMDATA(117)

MEMDATA(116)

MEMDATA(115)

MEMDATA(114)

MEMDATA(113)

MEMDATA(112)

MEMDATA(111)

MEMDATA(110)

MEMDATA(109)

MEMDATA(108)

MEMDATA(107)

MEMDATA(106)

MEMDATA(105)

MEMDATA(104)

MEMDATA(103)

MEMDATA(102)

MEMDATA(101)

MEMDATA(100)

MEMDATA(99)

MEMDATA(98)

MEMDATA(97)

MEMDATA(96)

MEMDATA(95)

MEMDATA(94)

MEMDATA(93)

MEMDATA(92)

MEMDATA(91)

MEMDATA(90)

MEMDATA(89)

MEMDATA(88)

MEMDATA(87)

MEMDATA(86)

MEMDATA(85)

MEMDATA(84)

MEMDATA(83)

MEMDATA(82)

MEMDATA(81)

MEMDATA(80)

MEMDATA(79)

MEMDATA(78)

MEMDATA(77)

MEMDATA(76)

MEMDATA(75)

MEMDATA(74)

MEMDATA(73)

MEMDATA(72)

MEMDATA(71)

MEMDATA(70)

MEMDATA(69)

MEMDATA(68)

MEMDATA(67)

MEMDATA(66)

MEMDATA(65)

MEMDATA(64)

MEMDQS(35)

MEMDQS(34)

MEMDQS(33)

MEMDQS(32)

MEMDQS(31)

MEMDQS(30)

MEMDQS(29)

MEMDQS(28)

MEMDQS(27)

MEMDQS(26)

MEMDQS(25)

MEMDQS(24)

MEMDQS(23)

MEMDQS(22)

MEMDQS(21)

MEMDQS(20)

MEMDQS(19)

MEMDQS(18)

MEMDQS(17)

MEMDQS(16)

MEMDQS(15)

MEMDQS(14)

MEMDQS(13)

MEMDQS(12)

MEMDQS(11)

MEMDQS(10)

MEMDQS(9)

MEMDQS(8)

MEMDQS(7)

MEMDQS(6)

MEMDQS(5)

MEMDQS(4)

MEMDQS(3)

MEMDQS(2)

MEMDQS(1)

MEMDQS(0)

Opteron

CPU0B

MEMCLK_UP_H(3)

MEMCLK_UP_L(3)

MEMCLK_UP_H(2)

MEMCLK_UP_L(2)

MEMCLK_UP_H(1)

MEMCLK_UP_L(1)

MEMCLK_UP_H(0)

MEMCLK_UP_L(0)

MEMCLK_LO_H(3)

MEMCLK_LO_L(3)

MEMCLK_LO_H(2)

MEMCLK_LO_L(2)

MEMCLK_LO_H(1)

MEMCLK_LO_L(1)

MEMCLK_LO_H(0)

MEMCLK_LO_L(0)

MEMCHECK(15)

MEMCHECK(14)

MEMCHECK(13)

MEMCHECK(12)

MEMCHECK(11)

MEMCHECK(10)

MEMCKE_UP

MEMCKE_LO

RSVD_MA(15)

RSVD_MA(14)

MEMADD(13)

MEMADD(12)

MEMADD(11)

MEMADD(10)

MEMADD(9)

MEMADD(8)

MEMADD(7)

MEMADD(6)

MEMADD(5)

MEMADD(4)

MEMADD(3)

MEMADD(2)

MEMADD(1)

MEMADD(0)

MEMDATA(63)

MEMDATA(62)

MEMDATA(61)

MEMDATA(60)

MEMDATA(59)

MEMDATA(58)

MEMDATA(57)

MEMDATA(56)

MEMDATA(55)

MEMDATA(54)

MEMDATA(53)

MEMDATA(52)

MEMDATA(51)

MEMDATA(50)

MEMDATA(49)

MEMDATA(48)

MEMDATA(47)

MEMDATA(46)

MEMDATA(45)

MEMDATA(44)

MEMDATA(43)

MEMDATA(42)

MEMDATA(41)

MEMDATA(40)

MEMDATA(39)

MEMDATA(38)

MEMDATA(37)

MEMDATA(36)

MEMDATA(35)

MEMDATA(34)

MEMDATA(33)

MEMDATA(32)

MEMDATA(31)

MEMDATA(30)

MEMDATA(29)

MEMDATA(28)

MEMDATA(27)

MEMDATA(26)

MEMDATA(25)

MEMDATA(24)

MEMDATA(23)

MEMDATA(22)

MEMDATA(21)

MEMDATA(20)

MEMDATA(19)

MEMDATA(18)

MEMDATA(17)

MEMDATA(16)

MEMDATA(15)

MEMDATA(14)

MEMDATA(13)

MEMDATA(12)

MEMDATA(11)

MEMDATA(10)

MEMDATA(9)

MEMDATA(8)

MEMDATA(7)

MEMDATA(6)

MEMDATA(5)

MEMDATA(4)

MEMDATA(3)

MEMDATA(2)

MEMDATA(1)

MEMDATA(0)

MEMRESET_L

MEMBANK(1)

MEMBANK(0)

MEMRAS_L

MEMCAS_L

MEMWE_L

MEMCHECK(9)

MEMCHECK(8)

MEMCHECK(7)

MEMCHECK(6)

MEMCHECK(5)

MEMCHECK(4)

MEMCHECK(3)

MEMCHECK(2)

MEMCHECK(1)

MEMCHECK(0)

MEMCS_L(7)

MEMCS_L(6)

MEMCS_L(5)

MEMCS_L(4)

MEMCS_L(3)

MEMCS_L(2)

MEMCS_L(1)

MEMCS_L(0)

G20

G21

AE21

AE20

L24

L25

R23

T23

H23

J23

AD21

AD20

Y23

AA23

U25

U24

H24

H25

V23

M23

AE23

J24

J25

V24

K23

L23

K25

M25

M24

N25

N23

P23

T25

V25

AJ24

AK25

AK27

AJ27

AL24

AK24

AL26

AL27

AJ28

AK30

AJ31

AG29

AL28

AK28

AH31

AG30

AG31

AF30

AD31

AC30

AF29

AF31

AD30

AC29

AB31

AA29

Y31

W31

AC31

AA30

Y30

V29

P31

M31

L30

L29

P29

N31

L31

K31

J30

J29

G31

F29

J31

H31

F31

F30

D31

C31

B30

C28

E31

E30

A29

B28

B27

A26

C24

A24

A28

A27

A25

B24

G25

W25

W23

Y25

AA25

Y24

U28

T29

P24

P25

T27

R26

R25

R24

V30

U29

R30

P30

V31

U30

R29

R31

AD23

AE25

AD24

AD25

AC24

AC25

AB25

AA24

3

3

P0_MEMCLK_UPR_H3

P0_MEMCLK_UPR_L3

P0_MEMCLK_UPR_H2

P0_MEMCLK_UPR_L2

P0_MEMCLK_UPR_H1

P0_MEMCLK_UPR_L1

P0_MEMCLK_UPR_H0

P0_MEMCLK_UPR_L0

P0_MEMCLK_LWR_H3

P0_MEMCLK_LWR_L3

P0_MEMCLK_LWR_H2

P0_MEMCLK_LWR_L2

P0_MEMCLK_LWR_H1

P0_MEMCLK_LWR_L1

P0_MEMCLK_LWR_H0

P0_MEMCLK_LWR_L0

P0_MEMCKE_UPR

P0_MEMCKE_LWR

TP40

TP41

P0_MEMADD13

P0_MEMADD12

P0_MEMADD11

P0_MEMADD10

P0_MEMADD9

P0_MEMADD8

P0_MEMADD7

P0_MEMADD6

P0_MEMADD5

P0_MEMADD4

P0_MEMADD3

P0_MEMADD2

P0_MEMADD1

P0_MEMADD0

P0_MEMDATA63

P0_MEMDATA62

P0_MEMDATA61

P0_MEMDATA60

P0_MEMDATA59

P0_MEMDATA58

P0_MEMDATA57

P0_MEMDATA56

P0_MEMDATA55

P0_MEMDATA54

P0_MEMDATA53

P0_MEMDATA52

P0_MEMDATA51

P0_MEMDATA50

P0_MEMDATA49

P0_MEMDATA48

P0_MEMDATA47

P0_MEMDATA46

P0_MEMDATA45

P0_MEMDATA44

P0_MEMDATA43

P0_MEMDATA42

P0_MEMDATA41

P0_MEMDATA40

P0_MEMDATA39

P0_MEMDATA38

P0_MEMDATA37

P0_MEMDATA36

P0_MEMDATA35

P0_MEMDATA34

P0_MEMDATA33

P0_MEMDATA32

P0_MEMDATA31

P0_MEMDATA30

P0_MEMDATA29

P0_MEMDATA28

P0_MEMDATA27

P0_MEMDATA26

P0_MEMDATA25

P0_MEMDATA24

P0_MEMDATA23

P0_MEMDATA22

P0_MEMDATA21

P0_MEMDATA20

P0_MEMDATA19

P0_MEMDATA18

P0_MEMDATA17

P0_MEMDATA16

P0_MEMDATA15

P0_MEMDATA14

P0_MEMDATA13

P0_MEMDATA12

P0_MEMDATA11

P0_MEMDATA10

P0_MEMDATA9

P0_MEMDATA8

P0_MEMDATA7

P0_MEMDATA6

P0_MEMDATA5

P0_MEMDATA4

P0_MEMDATA3

P0_MEMDATA2

P0_MEMDATA1

P0_MEMDATA0

P0_MEMRESET_L

P0_MEMBANK1

P0_MEMBANK0

P0_MEMRAS_L

P0_MEMCAS_L

P0_MEMWE_L

P0_MEMCHECK_UPR7

P0_MEMCHECK_UPR6

P0_MEMCHECK_UPR5

P0_MEMCHECK_UPR4

P0_MEMCHECK_UPR3

P0_MEMCHECK_UPR2

P0_MEMCHECK_UPR1

P0_MEMCHECK_UPR0

P0_MEMCHECK_LWR7

P0_MEMCHECK_LWR6

P0_MEMCHECK_LWR5

P0_MEMCHECK_LWR4

P0_MEMCHECK_LWR3

P0_MEMCHECK_LWR2

P0_MEMCHECK_LWR1

P0_MEMCHECK_LWR0

P0_MEMCS_L7

P0_MEMCS_L6

P0_MEMCS_L5

P0_MEMCS_L4

P0_MEMCS_L3

P0_MEMCS_L2

P0_MEMCS_L1

P0_MEMCS_L0

TP32

1

TP33

1

TP34

1

TP35

1

P0_MEMCLK_UPR_H1 18,20

P0_MEMCLK_UPR_L1 18,20

P0_MEMCLK_UPR_H0 16,20

P0_MEMCLK_UPR_L0 16,20

TP36

1

TP37

1

TP38

1

TP39

1

P0_MEMCLK_LWR_H1 17,20

P0_MEMCLK_LWR_L1 17,20

P0_MEMCLK_LWR_H0 15,20

P0_MEMCLK_LWR_L0 15,20

P0_MEMCKE_UPR 20

P0_MEMCKE_LWR 20

P0_MEMADD[13..0] 20

P0_MEMDATA[63..0] 19

P0_MEMBANK1 20

P0_MEMBANK0 20

P0_MEMRAS_L 20

P0_MEMCAS_L 20

P0_MEMWE_L 20

P0_MEMCHECK_UPR[7..0] 19

P0_MEMCHECK_LWR[7..0] 19

P0_MEMCS_L[7..0] 20

2

P0_VDD_2D5V

R63

P3V3_DUAL P3V3_DUAL

R1160

4.7K

3

Q119

D

GS

2N7002

2

1

R1162

100K

GND GND

4.7K

GPIO1_MEMRST#

3

Q3

D

GS

2N7002

2

1

GND GND

SN74LVC2G08-2.5/DCT/IC8VSSOP

R1296 0/X

R1297 0/X

P0_MEMRESET_L

GPIO2_MEMRST#

P1_MEMRST_AND

P0_MEMRESET_GPIOP0_MEMRESET_L

P1_MEMRESET_GPIOP1_MEMRESET_L

GND

1

2

3

4 5

SN74LVC2G32-2.5/DCT/IC8VSSOP

P0_MEMRST_AND

GPIO1_MEMRST#

P1_MEMRESET_GPIO29,30,31,32

GND

WORKAROUND:DELAY MEMRESET TIMING BY GPIO

AMD DOC. ORDER#27510

Title

Size Document Number Rev

2

Date: Sheet

1

P0_VDD_2D5V

3

D

R1161

4.7K

GS

2

Q120

2N7002

P0_MEMRST_AND

GPIO2_MEMRST#

P1_MEMRESET_L 27

C135

0.1U/6/X/16V

P0_MEMRESET_GPIO 15,16,17,18

GPIO1_MEMRST#

P1_MEMRST_AND

C136

0.1U/6/X/16V

GPIO_II45GPIO_I45

U12

1A

VCC

1B

1Y

2Y

2B

GND 2A

U13

1

1A

VCC

2

1B

1Y

3

2Y

2B

4 5

GND 2A

3

D

GS

2

R1163

100K

P0_VDD_2D5V

8

7

6

P0_VDD_2D5V

8

7

6

GPIO2_MEMRSTGPIO1_MEMRST

1

GND

GND

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 DDR I/F

GA-2CEWH-FS

1

R64

4.7K

GPIO2_MEMRST#

Q4

2N7002

1

13 81Monday, July 04, 2005

of

1.0

P5V

VIN12_P0

P0_DDR_MAIN

L28

1UH/7A/T3026/DIP

C138

560uF/4V/8*11.5/PSA

12

C143

EC3

P0_VTT_DDR_MAIN

1U/6/X/16V

L2

1.5uH/5A/T3026/DIP

EC4

+

P5V_DUAL

10K/B

R87

5.1K/B

R84 100

C148

0.1U/6/X/16V

1000P/6/X/50V/B

P0_DDR_MAIN

R85

1K/B

P0_VDD2D5V_VTT_EN_L

Q9

ECB

P0_VTT_DDR

820U/2.5V/8*11.5/PSA

P0_VDD2D5V_VTT_EN66

P0_VTT_SENSE13

R86

P0_VTT_SENSE

20 mils

0.1U/6/X/16V/B

R72

5.1/B

C146

R79

10K/1%

R82

10K/1%

0.01U/6/X/50V/X

MMBT2222A/B

SOT23

EC10

+

1000U/6.3V/8X11.5/KZG

Q6

FDS6900S

7

6

5

IC8SO

D43

1N5817/B

R78 6.2K/1%/B

P0_DDR_OCSET2

C1454

D1

S1D2

D1

S1D2

S1D2

G1

G2S2

12

P5V_DUAL

R83

10K/B

3

D

GS

2

1

P0_VDD_2D5V_SS

Q8

2N7002/B

SOT23

P5V P5V

23

17

24

25

27

26

20

19

21

16

22

18

4.7U/8/X/6.3V

BOOT2

SOFT2

UGATE2

PHASE2

LGATE2

PGND2

GND

VSEN2

EN2

PG2/REF

ISEN2

OCSET2

P5V

C137

D1

BAT54A/B

0/B

R68

C141

0.01U/6/X/50V/B/X

0/B

1

R69

2

8

34

0/B

R74

P0_VDD_2D5V_SS

P0_MEMVREF_VRD

C1453

4.7U/8/X/6.3V/B

Tsoft=(1.5V* Csoft)/5uA=3uS

Tsoft= time from EN assertion to PGOOD assertion

Time of P0_VDD_2D5V reach 2.5V=Trise=0.6*Tsoft=1.8uS

R65

0

0/X

R66

U14

14

28

VIN

BOOT1

VCC

SOFT1

UGATE1

PHASE1

LGATE1

PGND1

GND

VSEN1

EN1

PG1

ISEN1

OCSET1

GND

DDR

1

13

Vout= 0.9V*(R1+R2)/R2=2.598V

Delete R1196

SLP_S5#28,45,51,66,75,76

P0_PSPGD_S3S5

1

2 3

4 5

SN74LVC2G08-2.5/DCT/IC8VSSOP

Delete R1062

ISL6539CAZ

6

12

0.01U/6/X/50V/B

C142

5

4

2

3

9

10

P0_VDD_2D5V_SS

8

P0_MEM_PG

15

7

11

U89

A1

VCC

B1 Y2

B2Y1

GND A2

R70

R75

R80

75K/B

P3V3_DUAL

8

67

R67

0/B

Q5

G

0

0/6/B

Q7

G

R81

2K/1%/B

0221

R1181 0

R1182 0/X

SLP_S3# 28,45,63,66,68

P0_PSPGD_S3

GS

D1

S1 D2

D1

S1 D2

P0_MEM_PG

P3V3_DUAL

D

D

G

S

D3

D4

D5

HAT2168H

S2

S3

D3

D4

D5

HAT2165H

S2

S3

P0_MEM_PG 66

P0_MEM_PG 66

PS_PWRGD_3V3 28,66,68,74

R1056

1K

Q100

2N7002

Del Q129

D42

1N5820/B

P3V3

SLP_S5#28,45,51,66,75,76

P0_PSPGD_S3S5

P12V_CPU0

GS

R1165

4.7K/B

D

D

G

S

R1055

7.5K

2N7002

Q99

12

C139

EC1

0.1U/6/X/16V/B

330U/16V/10*12.5/FPCAP

2UH/30A/WM50GA/DIP

L3

R73

5.1/B

C147

1000P/6/X/50V/B

P5V_DUAL

R1053

Q94

GS

G

D

S

2N7002

C1465

0.33U/8/X7R/25V

330U/16V/10*12.5/FPCAP

EC6

+

560uF/4V/8*11.5/PSA

0221

10K

D

P0_DDR_MAIN

4

C1446

4.7U/8/X/6.3V/X

12

C140

EC2

1U/8/Y/25V/B

EC7

+

560uF/4V/8*11.5/PSA

PS_PWRGD_3V3

0

0

0

0

1

1

C1508 0.1U/6/X/16V

C1509

R1246

0/6

3

1

Q96

AP4880GM

67825

EC5

820U/2.5V/8*11.5/PSA

390uF/6.3V/PS-CON/8*12.5 12m_Ohm

560uF/4V/PSCON/8*11.5

SLP_S3#

0

0

1

P0_DDR_MAIN

SLP_S5#

P0_VDD_2D5V

C144

R76

8.87K/1%

0.01U/6/X/50V/B

R77

4.7K/1%

H/W off, No AC power,

0No Power

S4 or S5 state

1

1

00

R13140/6

+

0

1

FDC642P/PMOS/TSOP-6

FDC642P/PMOS/TSOP-6

0.1U/6/X/16V

P0_DDR_MAIN

1

4

67825

P0_VTT_DDR_MAIN

1

4

67825

3 4

GS

2

D

D

1

D

D

Q122

3 4

GS

2

D

D

1

D

D

Q95

3

Q97

AP4880GM

3

Q123

AP4880GM

P0_VTT_DDR

1

1

5

6

5

6

P1V25_DUAL

P0_VTT_DDR

P2V5_DUAL

Title

Size Document Number Rev

Date: Sheet

4700mA @105_Deg / 100Khz

5230mA @105_Deg / 100Khz10m_Ohm

2K

R71

P0_VDDIO_SENSE 11

2.6V/20A

System Status

S3 state

Power up,wake up P5V_DUA L

Entering S4, S5

Entering S3

H/W on

P0_VDD_2D5V

EC9

EC8

+

560uF/4V/8*11.5/PSA

560uF/4V/8*11.5/PSA

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 DDR Power

DDR VRD INPUT POWER

P5V_DUAL

No Power

P5V_DUAL

P5V

+

GA-2CEWH-FS

14 81Monday, July 04, 2005

1.0

of

5

4

3

2

1

DIMM0

P0_VDD_2D5V

D D

738467085

108

120

148

1688222

30

54627796104

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

163

CS3#

71

P0_SR_MEMCS_L116,20

P0_SR_MEMDQS_LWR[8..0]17,19

C C

P0_SR_MEMBANK116,17,18,20

P0_SR_MEMBANK016,17,18,20

P0_SR_MEMADD[13..0]16,17,18,20

P0_SR_MEMCHECK_LWR[7..0]17,19

B B

P0_MEMCLK_LWR_H013,20

P0_MEMCLK_LWR_L013,20

P0_MEMRESET_GPIO13,16,17,18

P0_SR_MEMDQS_LWR[17..9]17,19

P0_SR_MEMCS_L016,20

SMB_MEM_SDA16,17,18,29,30,31,32,45

SMB_MEM_SCL16,17,18,29,30,31,32,45

P0_SR_MEMCKE_LWR16,17,18,20

P0_SR_MEMCKE_UPR16,17,18,20

P0_SR_MEMCAS_L16,17,18,20

P0_SR_MEMRAS_L16,17,18,20

P0_SR_MEMCS_L1

P0_SR_MEMCS_L0

P0_SR_MEMDQS_LWR8

P0_SR_MEMDQS_LWR7

P0_SR_MEMDQS_LWR6

P0_SR_MEMDQS_LWR5

P0_SR_MEMDQS_LWR4

P0_SR_MEMDQS_LWR3

P0_SR_MEMDQS_LWR2

P0_SR_MEMDQS_LWR1

P0_SR_MEMDQS_LWR0

GND

P0_SR_MEMBANK1

P0_SR_MEMBANK0

P0_SR_MEMADD13

P0_SR_MEMADD12

P0_SR_MEMADD11

P0_SR_MEMADD10

P0_SR_MEMADD9

P0_SR_MEMADD8

P0_SR_MEMADD7

P0_SR_MEMADD6

P0_SR_MEMADD5

P0_SR_MEMADD4

P0_SR_MEMADD3

P0_SR_MEMADD2

P0_SR_MEMADD1

P0_SR_MEMADD0

P0_SR_MEMCHECK_LWR7

P0_SR_MEMCHECK_LWR6

P0_SR_MEMCHECK_LWR5

P0_SR_MEMCHECK_LWR4

P0_SR_MEMCHECK_LWR3

P0_SR_MEMCHECK_LWR2

P0_SR_MEMCHECK_LWR1

P0_SR_MEMCHECK_LWR0

P0_MEMCLK_LWR_H0

P0_MEMCLK_LWR_L0

P0_MEMRESET_GPIO

P0_SR_MEMCKE_LWR

P0_SR_MEMCKE_UPR

P0_SR_MEMCAS_L

P0_SR_MEMRAS_L

P0_SR_MEMDQS_LWR17

P0_SR_MEMDQS_LWR16

P0_SR_MEMDQS_LWR15

P0_SR_MEMDQS_LWR14

P0_SR_MEMDQS_LWR13

P0_SR_MEMDQS_LWR12

P0_SR_MEMDQS_LWR11

P0_SR_MEMDQS_LWR10

P0_SR_MEMDQS_LWR9

158

157

47

86

78

67

56

36

25

14

5

103

183

182

181

91

92

113

52

59

167

115

118

141

27

122

29

125

32

37

130

41

43

48

144

142

135

134

51

49

45

44

16

17

137

138

76

75

173

10

21

111

65

154

140

177

169

159

149

129

119

107

97

CS2#

CS1#

CS0#

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

FETEN

SA2

SA1

SA0

SDA

SCL

BA2

BA1

BA0

A13

A12

A11

A10_AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0

CK0#

CK1

CK1#

CK2

CK2#

NC5

NC1_RESET#

CKE0

CKE1

CAS#

RAS#

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

GND

GND

10011116

GND

GND

GND

GND

GND

GND

GND

124

132

139

145

152

160

143

156

164

172

180

136

VDDQ9

GND

VDDQ10

VDDQ11

GND

GND

VDDQ12

VDDQ13

GND

GND

15

VDDQ14

GND

112

128

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

GND

GND

GND

GND

GND

17618263344250586674818993

VDDQ15

GND

GND

VDDID

184

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15