Gigabyte F85226 Schematics

F85226F

F85226F

LPC to ISA Bridge

Release Date: August, 2004

Revision: V0.23P

k

F

Finte

Feature Integration Technology Inc.

F85226

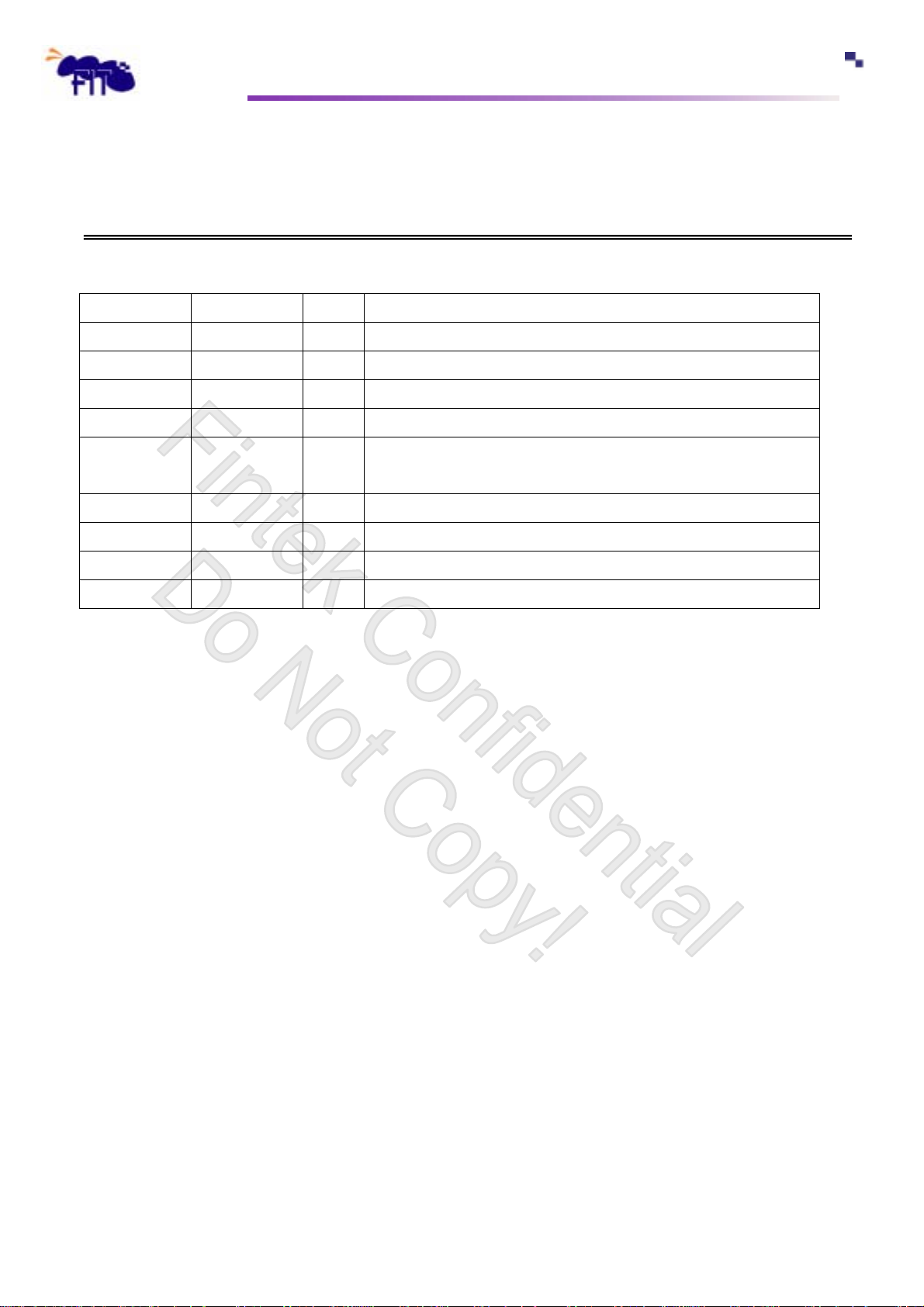

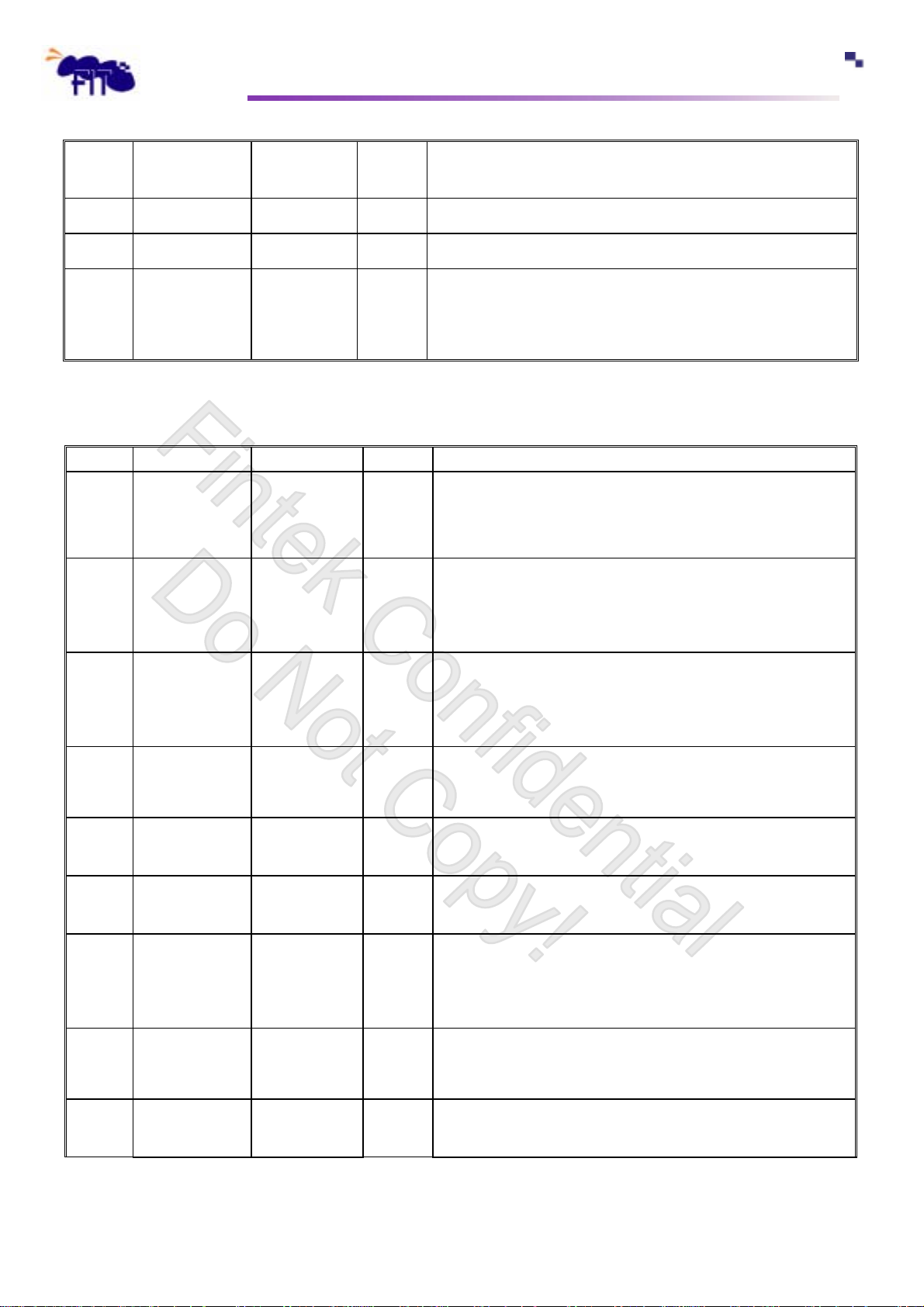

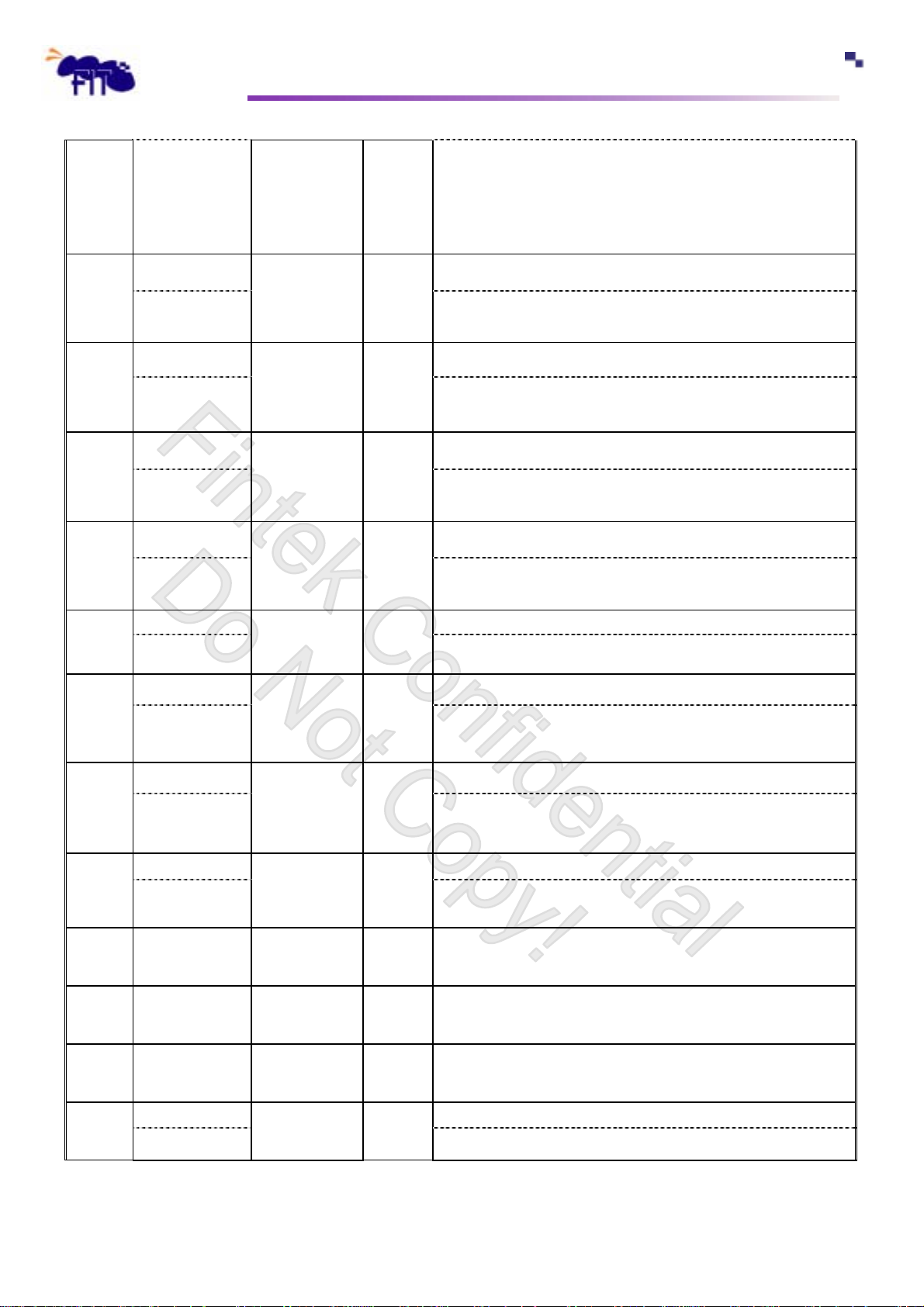

F85226F Datasheet Revision History

Version Date Page Revision History

0.10P 2003/12/18 Original version (Non Register Description)

0.20P 2003/12/23 Added register and application circuit

0.21P 2003/12/29 3 Removed PCI5v Item of pin descriptions

5 Revised the type description of pin 92 from INts to O24

0.22P 2004/5/30 1 Revised features : Fully ISA bridge support except bus

4 Revised ROMCS#/ROM_EN pin’s description

master (By conditions)

- Revised register descriptions

0.23P 2004/8/17 37 Update application circuit

Please note that all data and specifications are subject to change without notice. All the trade marks of products and

companies mentioned in this data sheet belong to their respective owners.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Customers using or selling these products for use

in such applications do so at their own risk and agree to fully indemnify Fintek for any damages resulting from such

improper use or sales.

F85226F

I

k

F

Finte

Feature Integration Technology Inc.

F85226

Table of Contents

1. General Description.............................................................................................................. 1

2. Features ............................................................................................................................... 1

3. Key Specifications ................................................................................................................ 1

4. Block Diagram ...................................................................................................................... 2

5. Pin Configuration .................................................................................................................. 3

6. Pin Descriptions.................................................................................................................... 3

6.1 Power Pin .......................................................................................................................4

6.2 Power on strapping signal .............................................................................................. 4

6.3 LPC interface.................................................................................................................. 4

6.4 ISA interface ...................................................................................................................5

7. Function Description........................................................................................................... 10

7.1 LPC interface: ............................................................................................................... 10

7.2 Serialized Interrupt........................................................................................................ 13

7.3 LPC DMA...................................................................................................................... 14

8. Registers Description ......................................................................................................... 15

8.1 Entry Key. ..................................................................................................................... 15

8.2 Configuration and Control Register – Index 03h ........................................................... 15

8.3 GPIO1 Function Select Register – Index 04h ............................................................... 16

8.4 GPIO2 Function Select Register – Index 05h ............................................................... 17

8.5 System Clock Register – Index 06h.............................................................................. 17

8.6 System Power down Register – Index 10h ................................................................... 18

8.7 GPIO Port Define Register (Low byte)– Index 11h ....................................................... 18

8.8 GPIO Port Define Register (High byte)– Index 12h ...................................................... 19

8.9 Address Decoder Register (I) – Index 013h.................................................................. 19

8.10 Address Decoder Register (II) – Index 014h............................................................... 20

8.11 GPIO Input Control Register – Index 15h.................................................................... 20

8.12 GPIO Output Data Register – Index 16h..................................................................... 21

8.13 GPIO1x Input Register – Index 17h ............................................................................ 21

8.14 GPIO2 Input Control Register – Index 18h ................................................................. 22

8.15 GPIO2 Output Data Register – Index 19h................................................................... 22

8.16 GPIO2 Input Register – Index 1Ah ............................................................................. 23

8.17 LED & IRQIN Control Register – Index 1Bh ............................................................... 23

8.18 Master Setting Register – Index 1Ch .......................................................................... 23

8.19 Master Setting Register – Index 1Dh .......................................................................... 24

8.20 Refresh Address Register (Low Byte) – Index 1Eh..................................................... 24

F85226F

II

k

F

Finte

8.21 Refresh Address Register (High Byte) – Index 1Fh .................................................... 24

8.22 Address1 Decode Mask Register – Index 20h............................................................ 24

8.23 Address1 Decode Register (Low Byte) – Index 21h ................................................... 24

8.24 Address1 Decode Register (High Byte) – Index 22h .................................................. 25

8.25 Address2 Decode Mask Register – Index 23h............................................................ 25

8.26 Address2 Decode Register (Low Byte) – Index 24h ................................................... 25

8.27 Address2 Decode Register (High Byte) – Index 25h .................................................. 25

8.28 ROM1 Decoder Mask Low Byte Register – Index 0x28.............................................. 26

8.29 ROM Decoder Mask (High Byte) Register – Index 0x29............................................. 26

8.30 ROM Decoder Address (Low Byte) Register – Index 0x2A......................................... 26

8.31 ROM Decoder Address (High Byte) Register – Index 0x2B........................................ 26

8.32 ROM2 Decoder Mask Low Byte Register – Index 0x2C ............................................. 27

8.33 ROM2 Decoder Mask (High Byte) Register – Index 0x2D .......................................... 27

Feature Integration Technology Inc.

F85226

8.34 ROM2 Decoder Address (Low Byte) Register – Index 0x2E....................................... 27

8.35 ROM2 Decoder Address (High Byte) Register – Index 0x2F ...................................... 27

8.36 ADDR3 Decoder Mask High Byte Register – Index 0x30 ........................................... 28

8.37 ADDR3 Decoder Address Low Byte Register – Index 0x31........................................ 28

8.38 ADDR3 Decoder Address High Byte Register – Index 0x32....................................... 28

8.39 ADDR4 Decoder Mask High Byte Register – Index 0x33 ........................................... 28

8.40 ADDR4 Decoder Address Low Byte Register – Index 0x34........................................ 29

8.41 ADDR4 Decoder Address High Byte Register – Index 0x35....................................... 29

8.42 KBC Decoder Mask Register – Index 0x36 ................................................................ 29

8.43 KBC Decoder Address Low Byte Register – Index 0x37 ............................................ 30

8.44 KBC Decoder Address High Byte Register – Index 0x38............................................ 30

8.45 MC Decoder Mask Register – Index 0x39 .................................................................. 30

8.46 MC Decoder Address Low Byte Register – Index 0x3A.............................................. 30

8.47 MC Decoder Address High Byte Register – Index 0x3B ............................................. 31

8.48 RTC Decoder Mask Register – Index 0x3C................................................................ 31

8.49 RTC Decoder Address Low Byte Register – Index 0x3D............................................ 31

8.50 RTC Decoder Address High Byte Register – Index 0x3E ........................................... 31

8.51 IOH Decoder Mask Register – Index 0x3F ................................................................. 32

8.52 IOH Decoder Address Low Byte Register – Index 0x40 ............................................. 32

8.53 IOH Decoder Address High Byte Register – Index 0x41............................................. 32

8.54 Edge Detector Status Register – Index 0x50 .............................................................. 32

8.55 IRQ Wakeup Register (I) – Index 0x51 ....................................................................... 33

8.56 IRQ Wakeup Register (II) – Index 0x52 ...................................................................... 33

8.57 CHIPID (1) Register – Index 5Ah................................................................................ 33

F85226F

III

k

F

Finte

8.58 CHIPID (2) Register – Index 5Bh................................................................................ 33

8.59 VERSION Register – Index 5Ch ................................................................................. 34

8.60 VENDOR ID (1) Register – Index 5Dh........................................................................ 34

8.61 VENDOR ID (2) Register – Index 5Eh ........................................................................ 34

9. Electrical characteristic.......................................................................................................34

9.1 Absolute Maximum Ratings .......................................................................................... 34

9.2 DC Characteristics........................................................................................................ 35

10. Package specification ...................................................................................................... 36

11. Application Circuit ............................................................................................................ 37

Feature Integration Technology Inc.

F85226

F85226F

IV

k

F

Finte

Feature Integration Technology Inc.

F85226

1. General Description

The F85226F is a LPC to ISA Bridge IC for new generation chipset which is no support for ISA bus

and slots. However the demand of ISA devices still exists. Therefore LPC to ISA Bridge IC is necessary to

be used for new chipset system. The F85226F is the best selection even though there is the PCI to ISA

Bridge for supporting ISA device, because the issue of package size is critical for layout requirement.

Follows the point at these issues, the F85226F is optimal solution for the non-ISA chipset, the package of

F85226F will be the best chosen for economic solution and save the layout size of Motherboard.

The F85226F absolutely meets LPC spec. 1.1 and supports fully ISA interface. Provides multi-ISA

compatible slots without buffering and supports ISA parallel IRQ transfer to serial IRQ by IRQ Serialier. The

F85226F also provides programmable general purpose I/O pins for user. It is completely LPC to ISA bridge

specialized chip.

2. Features

Meets LPC spec. 1.1

Supports LDRQ#(LPC DMA), SERIRQ(Serial IRQ)

Fully ISA bridge support except bus master(By conditions)

Supports 8/16bit I/O and memory R/W

All software transparent

All ISA signals can be isolate

ISA parallel IRQ transfer to serial IRQ by IRQ Serialier

Supports multi-slots without buffering

Supports the PCI clock to divide by 3 or 4 for ISA bus

Supports to generate two 14.318MHz buffer out from one 14.318MHz in

4 sets of address decoder supported

Supports programmable general purpose I/O pins

Powered by 3Vcc (Signal 5V tolerance)

128pin PQFP package

3. Key Specifications

Supply Voltage 3.0v to 3.6v

Operating Supply current 4mA typ.

F85226F

1

k

F

Finte

Feature Integration Technology Inc.

F85226

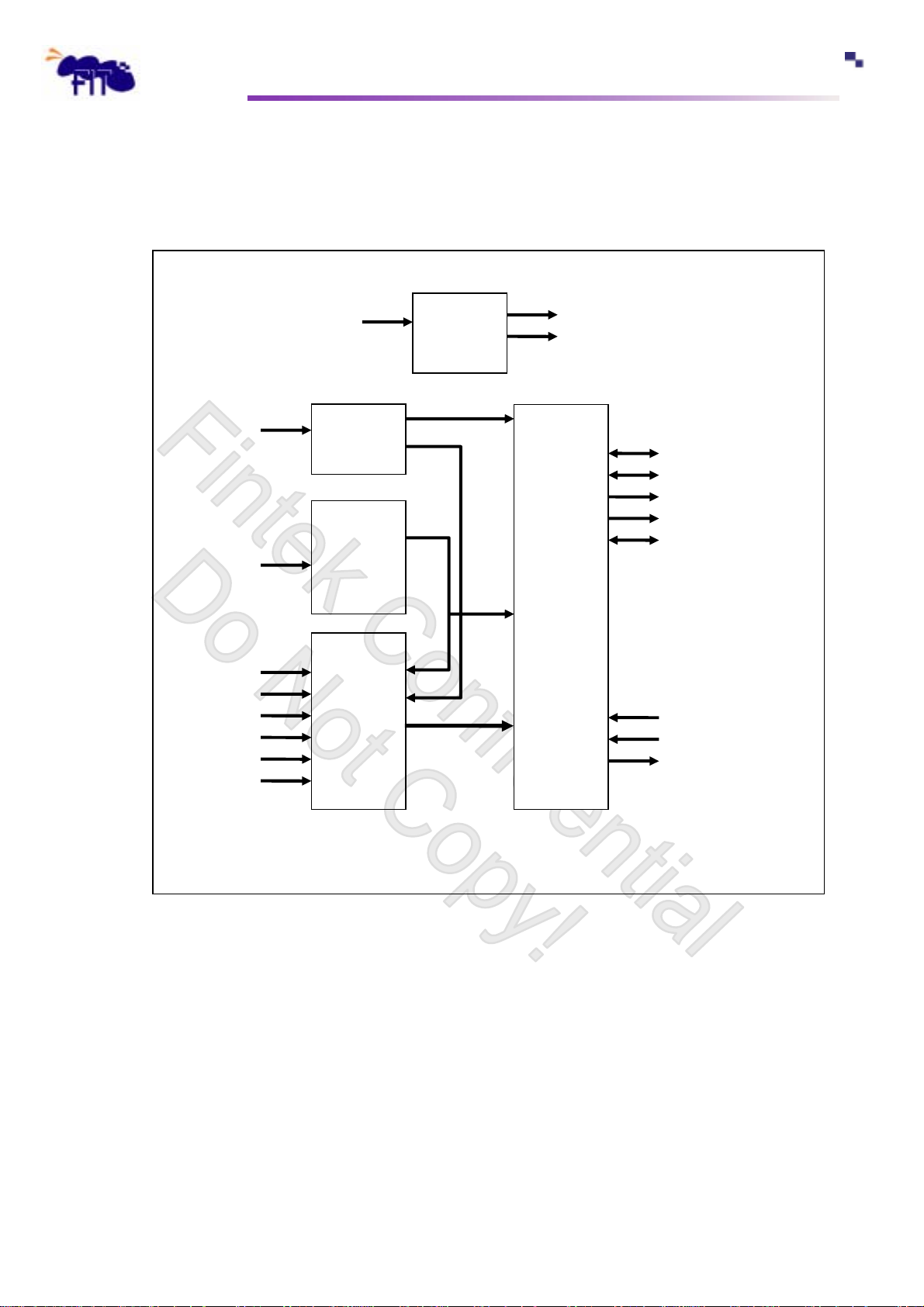

4. Block Diagram

14.318M

3.3V

PWRDN#

Power

Supply

Signal

Power

Down

Control

CLK

GEN./BUF

.

14MOUT1

14MOUT2

ISA

Interface

SA [19:0]

SD [15:0]

AEN

BALE

IOCHRDY

…………………

PCIRST#

LFRAM#

LDRQ#

PCICLK

SERIRQ

LAD [3:0]

LPC

Interface

IRQ [3:7,9:12,14,15]

DRQ [0:3,5:7]

DACK [0:3,5:7]

F85226F

2

k

F

Finte

Feature Integration Technology Inc.

F85226

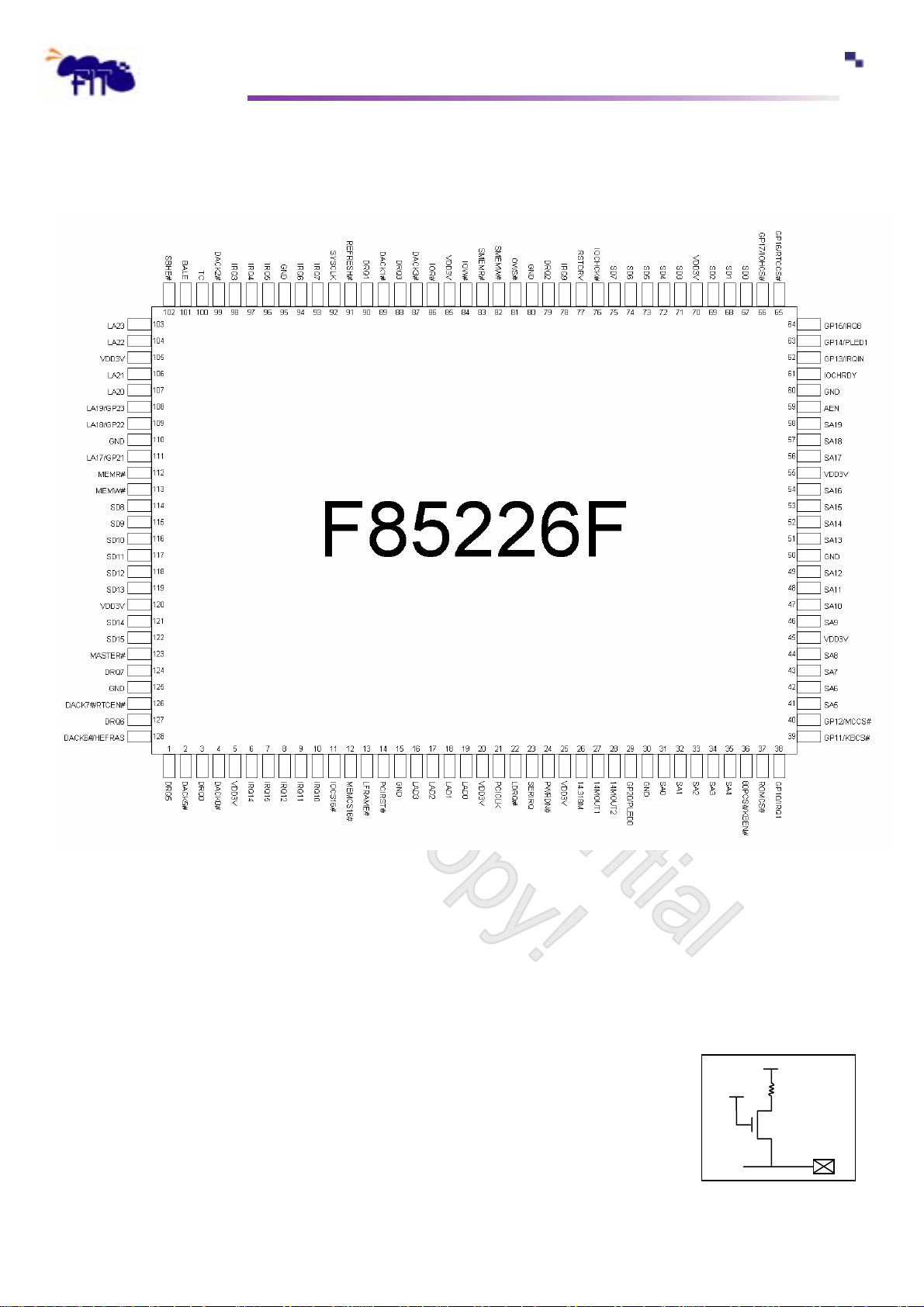

5. Pin Configuration

6. Pin Descriptions

I/O

- TTL level bi-directional pin and Schmitt trigger with 24 mA source-sink capability.

24ts

I/OD

24ts_u100k

I/O

24ts_u100k

O

24_u100k

O

- Output pin with 24 mA source-sink capability.

24

O

- Output pin with 20 mA source-sink capability.

20

F85226F

- TTL level input pin and Schmitt trigger, Open-drain output with 24 mA sink capability, internal pull-up

100KΩ connected with 3.3V to protect electric leakage.

- TTL level input pin and Schmitt trigger, Output pin with 24 mA sink capability, internal pull-up 100KΩ

connected with 3.3V to protect electric leakage.

- Output pin with 24 mA source-sink capability, internal pull-up 100KΩ

connected with 3.3V to protect electric leakage.

3

3.3V

100K

k

F

Finte

Feature Integration Technology Inc.

F85226

IN

- TTL level input pin.

t

IN

- TTL level input pin and schmitt trigger.

ts

P - Power.

6.1 Power Pin

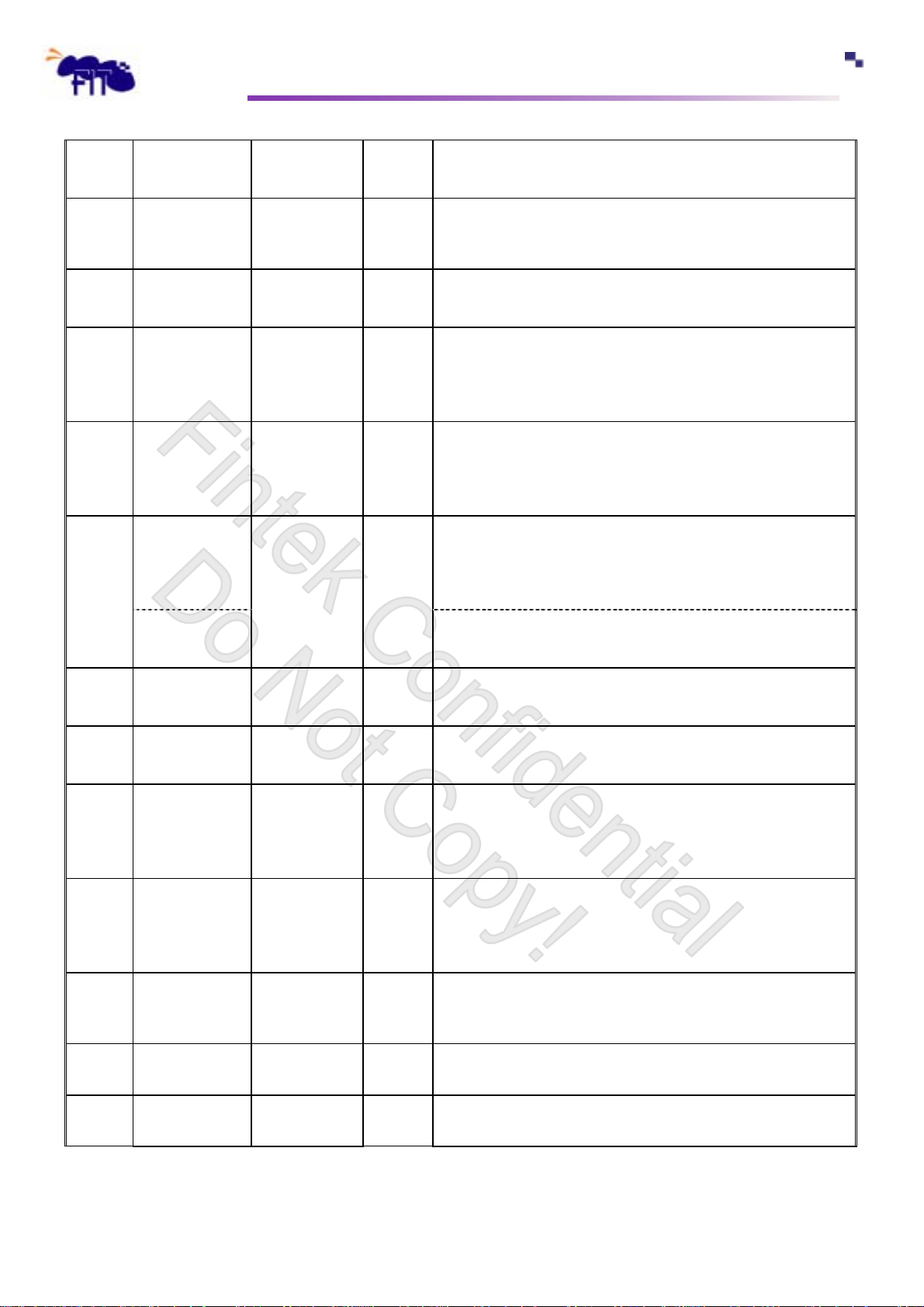

Pin No. Pin Name Type Description

5, 20, 25, 45, 55, 70, 85, 105, 120 VDD3V P Standard Power Supply Voltage Input with 3.3V.

15, 30, 50, 60, 80, 95, 110, 125 GND P Ground.

6.2 Power on strapping signal

Pin No Pin Name Ty pe PWR Description

36 80PCS#/KBEN#

37

126 DACK7#/RTCEN#

128 DACK6#/HEFRAS

2 DACK5#/EN_GP2X

ROMCS#/ROM_EN

I/OD

24ts_u100k

(5V-tolerance)

I/O

24ts

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

Power-on strapping with external pulled-down resistor 10k will

enable K/B and mouse functions. When it is set, pin 38, 39 and 40

will execute IRQ1, KBCS# and MCCS# signals.

Power-on strapping without internal resister, need external

pulled-up resistor to enable CR03h (BIOS_ROM_EN bit) If there is

a boot-ROM (BIOS). Else if without boot-ROM, please use external

pulled-down 10K resister to disable this BIOS_ROM_EN.

Power-on strapping with external pulled-down 10k resistor will

enable RTC functions. When it is set, pin 64 and 65 will do IRQ8

and RTCCS# signals.

Set this function will change the port that is used to access

configuration registers. Default setting is 4Eh, but by power-on

strapping with a external pulled-down 10k resister change to 2Eh.

Power-on strapping with external pulled-down 10k resistor. Then it

will disable LA [19:17] function and pin108~pin111, pin29 use as

GPIO2X function.

6.3 LPC interface

Pin No. Pin Name Type PWR Description

16-19 LAD[3:0]

13 LFRAME#

21 PCICLK

I/O

IN

IN

24ts

ts

t

VDD3v

VDD3v

VDD3v

F85226F

Multiplexed command, address bi-directional data and cycle status.

Through the LPC bus between a host and a peripheral.

Low pulse indicates start of a new cycle or termination of broken

cycle.

PCI clock used for the LPC bus. Same 33MHz clock as PCI clock

on the host. Same clock phase with typical PCI skew.

4

k

F

Finte

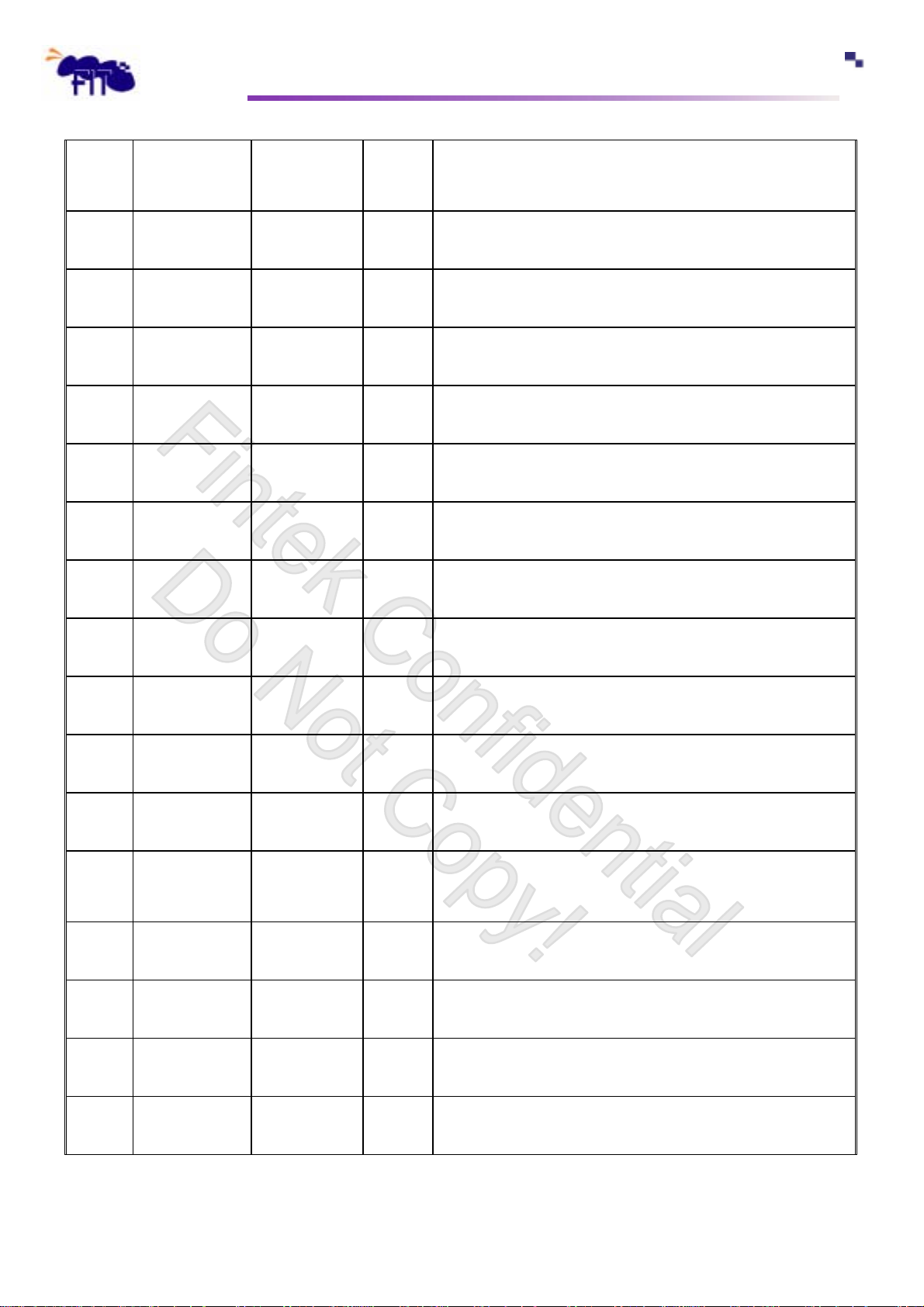

14 PCIRST#

23 SERIRQ I/O

22 LDRQ# O24

24

6.4 ISA interface

Pin No. Pin Name Type PWR Description

58-56

PWRDN#

SA[19:17]

I/O

24ts_u100k

(5V-tolerance)

IN

IN

ts

24ts

ts

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

PCI system reset used for the LPC bus. The Reset signal line can

be connected to PCIRST# signal on the host.

Serial IRQ Input/Output.

Encoded DMA Request signal.

Power Down. The signal is active low according to CR 44 Bit 7and

wake-up enable by hardware setting. There are eight different

power-down states (Power down Mode 3).

System Address Bus. These are the upper addresses that define

the ISA’s byte address space (up to 1 M byte). The SA [19:17] are

at tri-states during PCIRST#.

Feature Integration Technology Inc.

F85226

54-51

49-46

44-41

35-31

122-121

119-114

75-71

69-67

59 AEN

86 IOR#

84 IOW#

61 IOCHRDY

92 SYSCLK O24 VDD3v

SA[16:0]

SD[15:0]

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

O

24

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts

(5V-tolerance)

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

System Address Bus. These define the ISA’s byte address space

(up to 128K byte). The SD [16:0] are at tri-states during PCIRST#.

System Data Bus. These provide 16-bit data for devices to reside

on the ISA Bus. The SD [15:0] are at tri-states during PCIRST#.

Address Enable. AEN is asserted during DMA cycles, driven high

during F85226F initiated refresh cycles, driven low upon

PCIRST#.

I/O Read. IOR# is asserted to request an ISA I/O slave to drive

data onto the data bus.

I/O Write. IOW# is asserted to request an ISA I/O slave to accept

data from the data bus.

I/O Channel Ready. IOCHDRY asserted indicates that an ISA

slave requires additional wait states. When the F85226F is an ISA

slave, IOCHRDY is an output indicating additional wait states are

required.

ISA System Clock. SYSCLK offers the reference clock to the ISA

bus. The frequency is generated from dividing PCICLK by 3 or 4

(select by CR06 bit7).

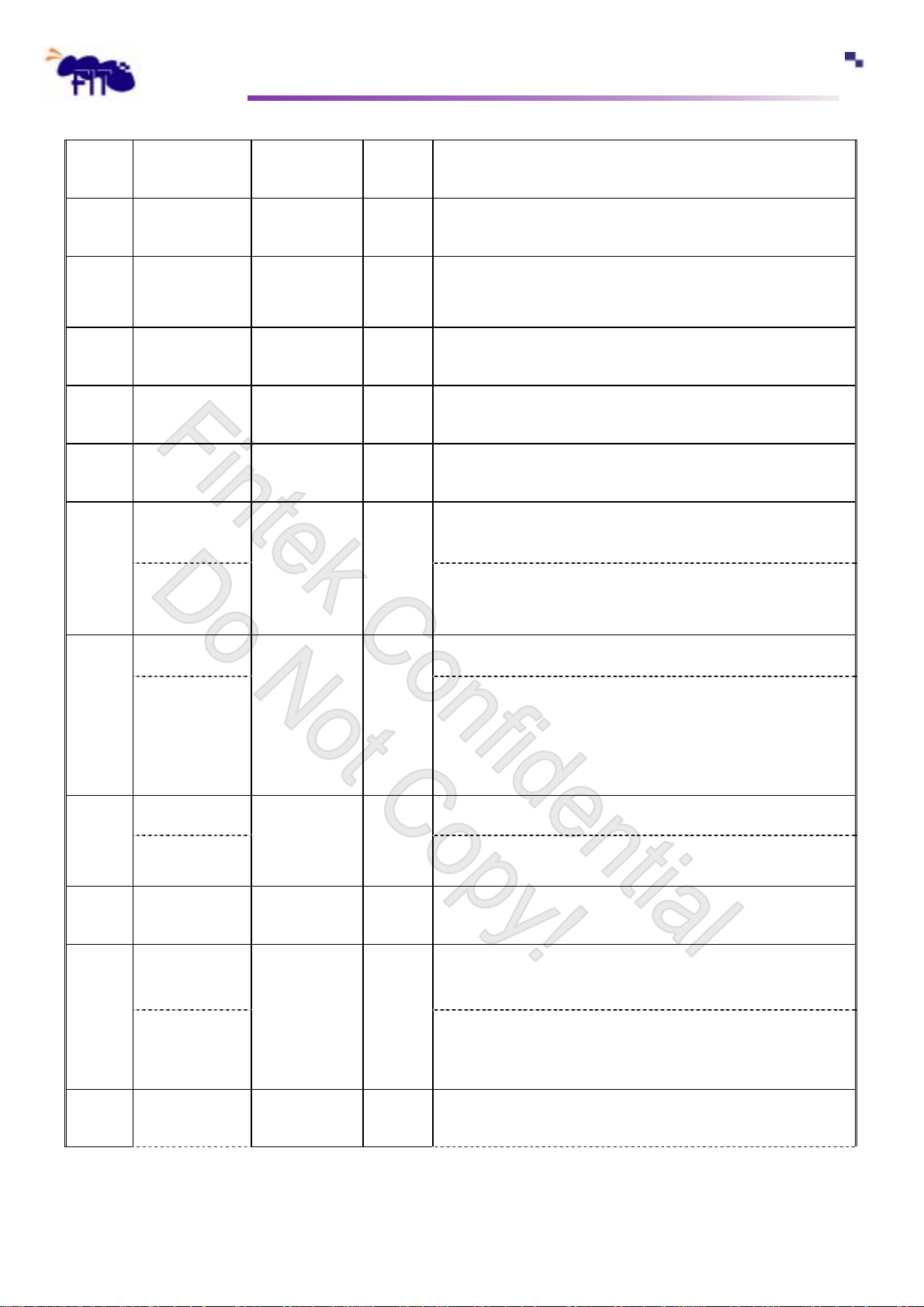

77 RSTDRV O

24

VDD3v

F85226F

Reset Drive. RSTDRV asserted indicates to reset devices that

reside on the ISA Bus while the PCIRST# has been asserted.

5

k

F

Finte

11 IOCS16#

12 MEMCS16#

76 IOCHCK#

81 OWS#

103-104

106-107

108-109

111

LA[23:20]

LA[19:17]

GP23, GP22,

GP21

I/O

24ts

(5V-tolerance)

I/O

24ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

16-bit I/O Chip Select. IOCS16# is asserted by 16-bit ISA I/O

devices to indicate that they support 16-bit I/O bus cycles.

Memory Chip Select 16. MEMCS16# is asserted by 16-bit ISA

memory devices to indicate that the memory slave supports 16-bit

accesses.

I/O Channel Check. Asserted by an ISA device indicating an error

condition.

Zero Wait States. An ISA slave asserts ZEROWS# after its

address and command signals have been decoded to indicate

that the current cycle can be executed as an ISA zero wait state

cycle. ZEROWS# has no effect during 16-bit I/O cycles.

Unlatched Address. The LA [23:20] address lines are

bi-directional. These address lines allow accesses to physical

memory on the ISA Bus up to 16 Mbytes. LA [23:20] are outputs

when the F85226F owns the ISA Bus.

Unlatched Address. The LA [19:17] address lines are

bi-directional. These address lines allow accesses to physical

memory on the ISA Bus up to 16 Mbytes. LA [19:17] are outputs

when the F85226F owns the ISA Bus.

General purpose I/O pin.

Feature Integration Technology Inc.

F85226

82 SMEMW#

83 SMEMR#

91 REFRESH#

101 BALE

102 SBHE#

112 MEMR#

113 MEMW#

O

24

(5V-tolerance)

O

24

(5V-tolerance)

O

24_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

Standard (system) Memory Write. SMEMW# is asserted for

memory write accesses below 1MB.

Standard (system) Memory Read. SMEMR# is asserted for

memory read accesses below 1 MB.

Refresh Cycle indicator. REFRESH# asserted indicates that a

refresh cycle is in progress, or ISA master requests F85226F to

generate a refresh cycle. The signal is at tri-stated upon

PCIRST#.

Bus Address Latch Enable. BALE asserted indicates when the

address (SA[19:0], LA[23:17]) and SBHE# are valid. The LA

[23:17] address lines are latched on the trailing edge of BALE.

BALE is driven by low upon PCIRST#.

System Byte High Enable. SBHE# asserted indicates that

SD[15:8] will be used to transfer a byte. SBHE# is at an unknown

state upon PCIRST#.

Memory Read. MEMR# asserted indicates the current ISA bus

cycle is a memory read.

Memory Write. MEMW# asserted indicates the current ISA bus

cycle is a memory write.

F85226F

6

k

F

Finte

123 MASTER#

98 IRQ3

97 IRQ4

96 IRQ5

94 IRQ6

93 IRQ7

78 IRQ9

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

The MASTER# input asserted indicates an ISA bus master is

VDD3v

VDD3v Parallel Interrupt Requested Input 3.

VDD3v Parallel Interrupt Requested Input 4.

VDD3v Parallel Interrupt Requested Input 5.

VDD3v Parallel Interrupt Requested Input 6.

VDD3v Parallel Interrupt Requested Input 7.

VDD3v Parallel Interrupt Requested Input 9.

driving the ISA bus. This signal is executed with DREQ line by an

ISA master to gain control of the ISA Bus.

Feature Integration Technology Inc.

F85226

10 IRQ10

9 IRQ11

8 IRQ12

6 IRQ14

7 IRQ15

3 DRQ0

90 DRQ1

79 DRQ2

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

VDD3v Parallel Interrupt Requested Input 10.

VDD3v Parallel Interrupt Requested Input 11.

VDD3v Parallel Interrupt Requested Input 12.

VDD3v Parallel Interrupt Requested Input 14.

VDD3v Parallel Interrupt Requested Input 15.

DMA Request input 0. The DREQ asserted indicates that either a

VDD3v

VDD3v DMA Request input 1.

VDD3v DMA Request input 2.

slave DMA device is requesting DMA services or an ISA bus

master is requesting to use the ISA bus.

IN

88 DRQ3

1 DRQ5

F85226F

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

VDD3v DMA Request input 3.

VDD3v DMA Request input 5.

7

k

F

Finte

127 DRQ6

124 DRQ7

4 DACK0#

89 DACK1#

99 DACK2#

87 DACK3#

IN

ts

(5V-tolerance)

IN

ts

(5V-tolerance)

O

24

(5V-tolerance)

O

24

(5V-tolerance)

O

24

(5V-tolerance)

O

24

(5V-tolerance)

VDD3v DMA Request input 6.

VDD3v DMA Request input 7.

DMA Acknowledge channel 0. The DACK# outputs asserted

VDD3v

VDD3v DMA Acknowledge channel 1.

VDD3v DMA Acknowledge channel 2.

VDD3v DMA Acknowledge channel 3.

indicates that either a DMA channel or an ISA bus master has

been granted the ISA bus.

Feature Integration Technology Inc.

F85226

DACK5# DMA Acknowledge channel 5.

2

EN_GP2X

DACK6# DMA Acknowledge channel 6.

128

HERFRA

DACK7# DMA Acknowledge channel 7.

126

RTCEN#

100 TC

80PCS#

36

KBEN#

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

I/O

24ts_u100k

(5V-tolerance)

O

24

(5V-tolerance)

I/OD

24ts_u100k

(5V-tolerance)

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

During power-on strapping with external pulled-down 10k resistor.

Then it will disable LA [19:17] function and pin108~pin111, pin29

use as GPIO2X function.

During power-on reset, this pin is pulled-up internally(Select

4Eh) ,and is defined as HEFRAS which provides the power-on

value for CR3 bit4 .A 10k ohm is recommended if intends to pull

down .(Select 2Eh)

RTC Function Enable. The pin applies a pull-down resistor (4.7K

ohm) to enable RTC functions (RTCCS#, and IRQ8)

Terminal Count. TC signals the final data transfer of a DMA

transfer.

80h PORT Chip Select.(Default)

Only decode IO address port 80h and must apply with IOW#.

K/B Functions Enable. During power-on reset this pin is weak

pulled-up internally. The pin applied a pull-down resistor (10K

ohm) to enable K/B functions. (IRQ1,KBCS#,and MCCS#)

I/O

37

ROMCS#

24ts

(5V-tolerance)

VDD3v

F85226F

ROMCS#, this pin enable positive decoder of BIOS address

range.

8

k

F

Finte

ROM_EN

GPIO0 General purpose I/O pin 0.

38

IRQ1

GPIO1 General purpose I/O pin 1.

39

KBCS#

GPIO2 General purpose I/O pin 2.

40

MCCS#

I/O

24ts

(5V-tolerance)

I/O

24t

(5V-tolerance)

I/O

24ts

(5V-tolerance)

VDD3v

VDD3v

VDD3v

Power-on strapping with internal pulled-up resistor will enable

CR03h (BIOS_ROM_EN, BIOS_WR_EN bit). If there is a

boot-ROM (BIOS), else if without boot-ROM, please use external

pulled-down 10K resister to disable this ROM_EN and WR_EN.

Parallel Interrupt Requested Input 1. This pin is used for specific

K/B functions.

Decode address 60h and 64h to generate chip selected signal.

Enable by KBEN# power-on setting.

Decode address 62h and 66h to generate chip selected signal.

Enable by KBEN# power-on setting.

Feature Integration Technology Inc.

F85226

GPIO3 General purpose I/O pin 3.

62

IRQIN

GPIO4 General purpose I/O pin 4.

63

PLED

GPIO5 General purpose I/O pin 5.

64

IRQ8

GPIO6 General purpose I/O pin 6.

65

RTCCS#

GPIO7 General purpose I/O pin 7.

66

IOHCS#

26 14.318M

I/O

24ts

(5V-tolerance)

I/O

24ts

(5V-tolerance)

I/O

24ts

(5V-tolerance)

I/O

24ts

(5V-tolerance)

I/O

24ts

(5V-tolerance)

IN

ts

(5V-tolerance)

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v

VDD3v 14.318 MHz Clock Input.

It is programmable to transfer parallel IRQ input to serial IRQ,

Enable by KBEN# power-on setting.

Power LED output, the signal is at low state after system reset.

Parallel Interrupt Requested Input 8. This interrupt request is used

for specific RTC functions. Enable by RTCEN# power-on setting.

Decode address 70h and 71h to generate chip selected signal.

Enable by RTCEN# power-on setting.

Decode SA [15-11] all are at “0” state initially and setting by CR04

Bit 6.

O

27 14MOUT 1

28 14MOUT 2

GP20 General purpose I/O pin.

29

PLED

F85226F

20

O

20

I/O

24ts

(5V-tolerance)

VDD3v 14.318 MHz Buffer Output 1.

VDD3v 14.318 MHz Buffer Output 2.

VDD3v

Power LED output, the signal is at low state after system reset.

9

Loading...

Loading...