Gigabyte F81218 Schematics

F81218D

F81218D

ISA/LPC to 6 UART Datasheet

Release Date: January, 2004

Version: V0.27P

F81218D Jan, 2004

V0.27P

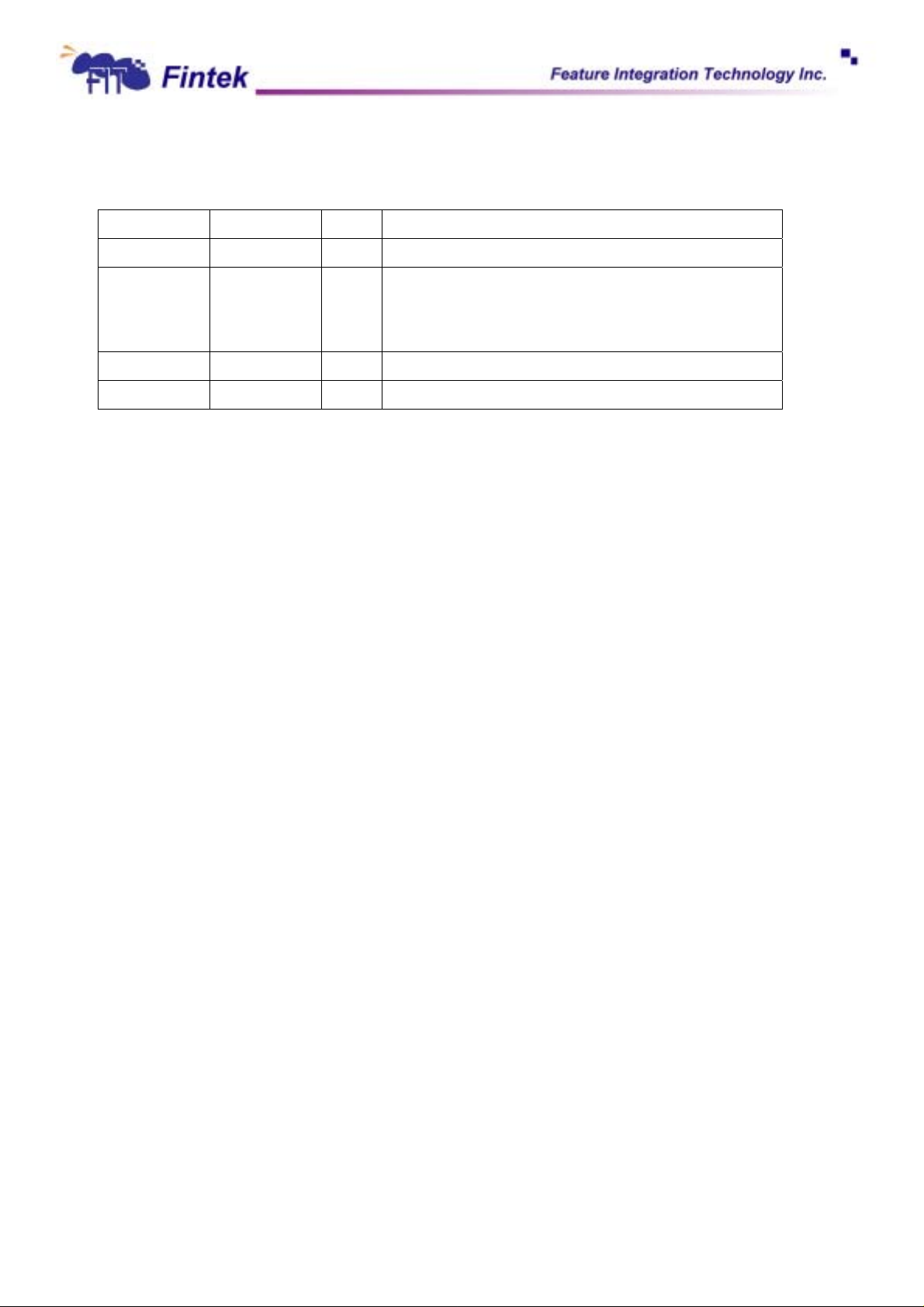

F81218D Datasheet Revision History

Version Date Page Revision History

0.24P 2003/7/10 25 Revised index 25h to index 26h

0.25P 2003/07/31 17 Updated WDT enable timer as power-on setting

48MHz clock input : 5 sec

0.26P 2003/09/16 Updated application circuit

0.27P 2004/01/07 56 Revised the pin naming, between Pin91 to Pin96

F81218D

24MHz clock input : 10 sec

Please note that all data and specifications are subject to change without notice. All the trade marks of products and

companies mentioned in this data sheet belon g to their respective owners.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to re sult in p ersonal injury. Customers using or selling these products for use

in such applications do so at their own risk and agree to fully indemnify Fintek for any damages resulting from such

improper use or sales.

F81218D Jan, 2004

V0.27P

F81218D

Ta ble of Content

1. General Description......................................................................................................................................... 1

2. Feature List ...................................................................................................................................................... 1

3. Pin Configuration............................................................................................................................................. 2

4. Pin Description................................................................................................................................................. 3

4.1 ISA/LPC Interface ................................................................................................................................. 3

4.2 UART Interface...................................................................................................................................... 5

4.3 GPIO pins............................................................................................................................................. 10

4.4 Power ................................................................................................................................................... 10

5. Functional Description................................................................................................................................... 11

5.1 LPC Interface.................................................................................................................................... 11

5.2 UART................................................................................................................................................ 12

5.2.1 UART Port Register.................................................................................................................. 12

5.3 IR Function....................................................................................................................................... 17

5.4 Watch Dog Timer Function............................................................................................................... 17

5.4.1 Watchdog Port Register......................................................................................................... 17

5.5 Serial IRQ......................................................................................................................................... 18

5.5.1 Start Frame................................................................................................................................ 18

5.5.2 IRQ/Data Frame........................................................................................................................ 18

5.5.3 Stop Frame................................................................................................................................ 19

6. Register Description................................................................................................................................... 20

6.1 Global Control Register.................................................................................................................... 23

6.1.1 Software Reset Register – index 02h........................................................................................23

6.1.2 Logic Device Select Register – index 07h................................................................................ 24

6.1.3 Device ID Register– index 20h, 21h......................................................................................... 24

6.1.4 Device Reversion Register– index 22h..................................................................................... 24

6.1.5 Vendor ID Register– index 23h, 24h......................................................................................... 24

6.1.6 Clock Source Select Register – index 25h................................................................................ 25

6.1.7 GPIO Function Select Register ( ISA Interface Only ) – index 26h......................................... 25

6.1.8 Test Mode Register – index 2Fh ............................................................................................... 25

6.2 UART 1 Device Control Register (LDN 0).........................................................................................26

6.2.1 Device Enable Register – index 30h.................................................................................. 26

F81218D Jan, 2004

V0.27P

F81218D

6.2.2 I/O Port Select Register – index 60h.................................................................................. 26

6.2.3 I/O Port Select Register – index 61h.................................................................................. 26

6.2.4 IRQ Channel Select Register – index 70h ............................................................................. 26

6.2.5 UART 1 Clock Select Register – index F0h..........................................................................27

6.2.6 IR1 Control Register – index F1h..........................................................................................28

6.3 UART 2 Device Control Register (LDN 1).........................................................................................28

6.3.1 Device Enable Register – index 30h.................................................................................. 28

6.3.2 I/O Port Select Register – index 60h.................................................................................. 28

6.3.3 I/O Port Select Register – index 61h.................................................................................. 29

6.3.4 IRQ Channel Select Register – index 70h ............................................................................. 29

6.3.5 UART 2 Clock Select Register – index F0h..........................................................................30

6.3.6 IR 2 Control Register – index F1h.........................................................................................30

6.4 UART 3 Device Control Register (LDN 2).........................................................................................31

6.4.1 Device Enable Register – index 30h.................................................................................. 31

6.4.2 I/O Port Select Register – index 60h.................................................................................. 31

6.4.3 I/O Port Select Register – index 61h.................................................................................. 31

6.4.4 IRQ Channel Select Register – index 70h ............................................................................. 31

6.4.5 UART 3 Clock Select Register – index F0h..........................................................................32

6.5 UART 4 Device Control Register (LDN 3).........................................................................................32

6.5.1 Device Enable Register – index 30h.................................................................................. 32

6.5.2 I/O Port Select Register – index 60h.................................................................................. 33

6.5.3 I/O Port Select Register – index 61h.................................................................................. 33

6.5.4 IRQ Channel Select Register – index 70h ............................................................................. 33

6.5.6 UART 4 Clock Select Register – index F0h..........................................................................34

6.6 UART 5 Device Control Register (LDN 4).........................................................................................34

6.6.1 Device Enable Register – index 30h.................................................................................. 34

6.6.2 I/O Port Select Register – index 60h.................................................................................. 34

6.6.3 I/O Port Select Register – index 61h.................................................................................. 34

6.6.5 IRQ Channel Select Register – index 70h ............................................................................. 35

6.6.6 UART 5 Clock Select Register – index F0h..........................................................................35

6.7 UART 6 Device Control Register (LDN 5).........................................................................................36

6.7.1 Device Enable Register – index 30h.................................................................................. 36

6.7.2 I/O Port Select Register – index 60h.................................................................................. 36

6.7.3 I/O Port Select Register – index 61h.................................................................................. 36

6.7.4 IRQ Channel Select Register – index 70h ............................................................................. 36

6.7.5 UART 6 Clock Select Register – index F0h..........................................................................37

6.8 Address Decoder 0 Device Control Register (LDN 6)........................................................................ 37

F81218D Jan, 2004

V0.27P

F81218D

6.8.1 Device Enable Register – index 30h.................................................................................. 37

6.8.2 Address Decoder Select Register 0– index 60h................................................................. 38

6.8.3 Address Decoder Select Register 1– index 61h................................................................. 38

6.8.4 Address Mask Register – index 62h .................................................................................. 38

6.8.5 IRQIN0 Channel Select Register (Only for LPC) – index 70h ......................................... 38

6.9 Address Decoder 1 Device Control Register (LDN 7)........................................................................ 39

6.9.1 Device Enable Register – index 30h.................................................................................. 39

6.9.2 Address Decoder Select Register 0 – index 60h................................................................ 39

6.9.3 Address Decoder Select Register 1 – index 61h................................................................ 39

6.9.4 Address Mask Register – index 62h .................................................................................. 40

6.9.5 IRQIN1 Channel Select Register (Only for LPC) – index 70h ......................................... 40

6.10 Watch Dog Timer Device Control Register (LDN 8)........................................................................ 41

6.10.1 Device Enable Register – index 30h.................................................................................. 41

6.10.2 I/O Port Select Register – index 60h.................................................................................. 41

6.10.3 I/O Port Select Register – index 61h.................................................................................. 41

6.10.4 IRQ Channel Select Register – index 70h ......................................................................... 41

6.10.5 Timer Status and Control Register – index F0h................................................................. 42

6.10.6 Timer Count Number Register – index F1h.......................................................................42

6.11 GPIO and PME Device Control Register (LDN 9)............................................................................ 43

6.11.1 GPIO Port 2 Control Register – index F0h........................................................................ 43

6.11.2 GPIO Port 1 Control Register – index F1h........................................................................ 43

6.11.3 GPIO Port 2 Output Data Control Register – index F2h................................................... 44

6.11.4 GPIO Port 1 Output Data Register – index F3h ................................................................ 45

6.11.5 PME Event 1 Control Register – index F4h ...................................................................... 45

6.11.6 PME Event 2 Control Register – index F5h ...................................................................... 46

6.11.7 PME Event 3 Control Register – index F6h ...................................................................... 47

6.11.8 GPIO Port 2 Input Status Register – index F7h................................................................. 47

6.11.9 GPIO Port 1 Input Status Register – index F8h................................................................. 47

6.11.10 PME Real Time Status Register – index F9h..................................................................... 48

6.11.11 PME Edge Status 1 Register – index FAh ......................................................................... 48

6.11.12 PME Edge Status 2 Register – index FBh......................................................................... 49

6.11.13 PME Edge Status 3 Register – index FCh......................................................................... 49

7. Electron Characteristic................................................................................................................................ 51

7.1 Absolute Maximum Ratings ............................................................................................................. 51

7.2 DC Characteristics............................................................................................................................... 51

8. Ordering Information..................................................................................................................................52

9. Package Dimensions ................................................................................................................................... 53

F81218D Jan, 2004

V0.27P

F81218D

10. Application Circuit....................................................................................................................................... 54

F81218D Jan, 2004

V0.27P

F81218D

1. General Description

The F81218D mainly provides 4 pure UART and 2 SIR+UART ports through ISA or

LPC interface which cab be selected by hardware setting. Each UART includes 16-byte

send/receive FIFO, a programmable baud rate generator, co mplete modem control cap ability

and an interrupt system. When using ISA interface mode, total 6 IRQ can be used, and each

one supports sharing function. 2 address decoder pins are provided for ISA mode as well.

When in LPC interface mode, some pins such as DATA pins, IOR, IOW, address decoder,

ISA address A0-A3 can be simple LPC to ISA transferring bridge pins. And some other pins

can be set to be GPIO pins.

No matter in ISA or LPC mode, one watch dog timer is provided for system controlling

and the time interval can be programmed by register or hardware power on setting pin.

This IC needs one clock 24/48MHz input, and default is 24MHz. Powered by 3.3V voltage,

the F81218D is in 100pin LQFP package (14mm x 14mm).

2. Feature List

Supports LPC or ISA interface (1 hardware setting pin to define LPC or ISA I/F )

In LPC mode, also provides simple LPC to ISA bridge

Totally provides 6 UART (16550 asynchronous) ports

4 pure UART ports

2 SIR+ UART ports

Provides 6 IRQ and each one can be shared

2 address decoder for ISA/LPC interface

1 watch dog timer with WDTOUT# signal

1 frequency input 24/48MHz

Powered by 3Vcc

100-LQFP(14mm x 14mm)

Jan, 2004

-1-

V0.27P

3. Pin Configuration

F81218D

Jan, 2004

-2-

V0.27P

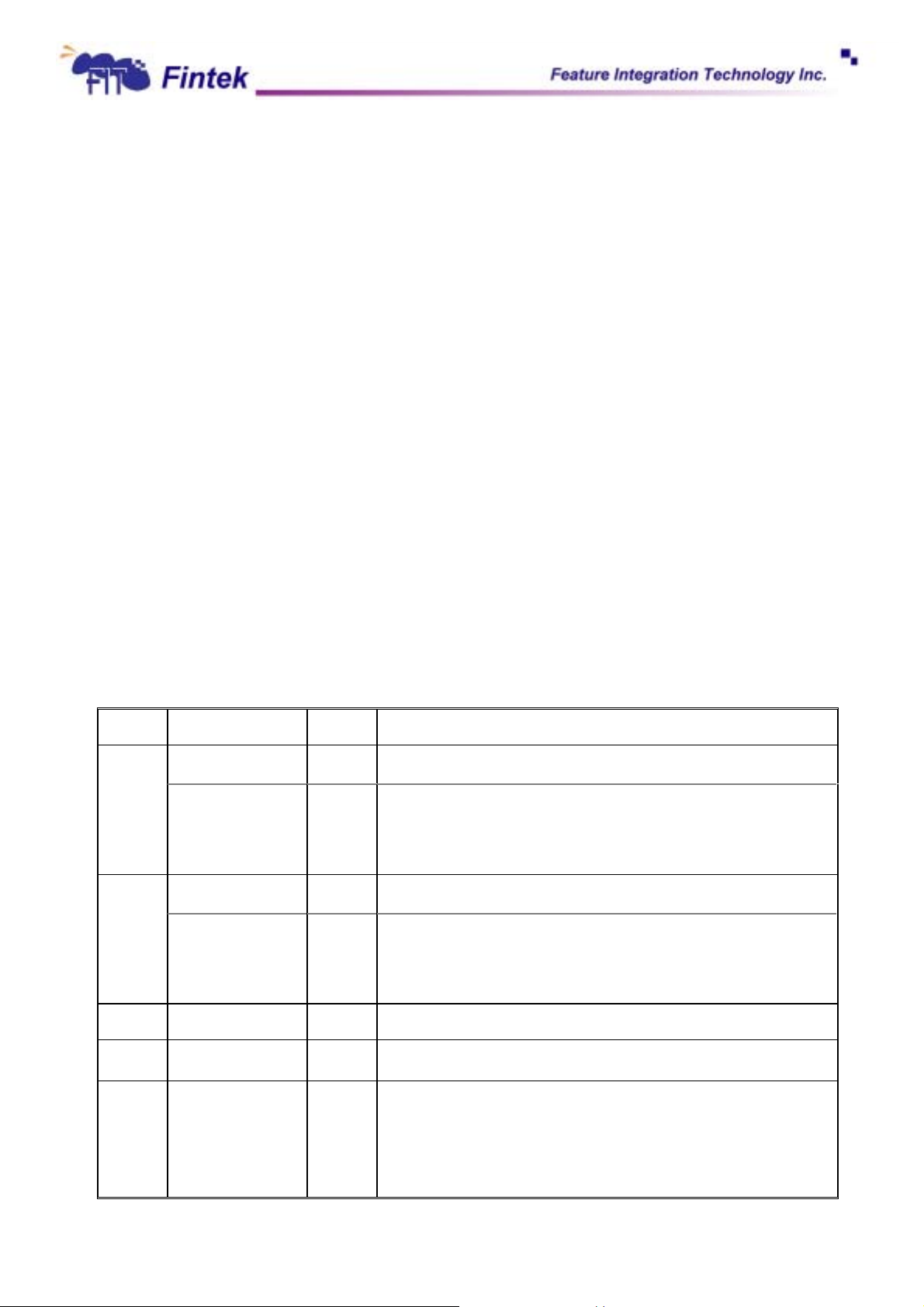

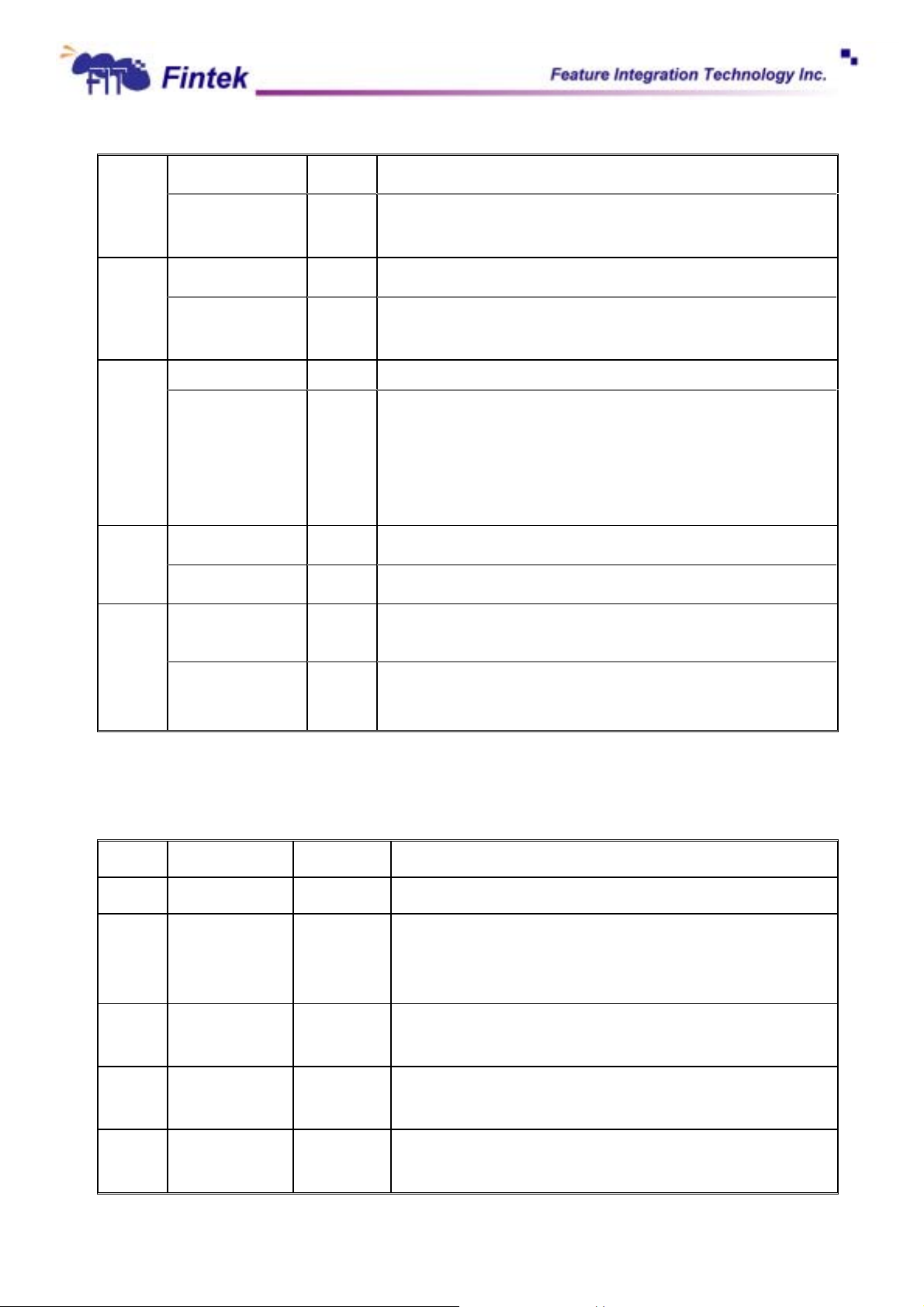

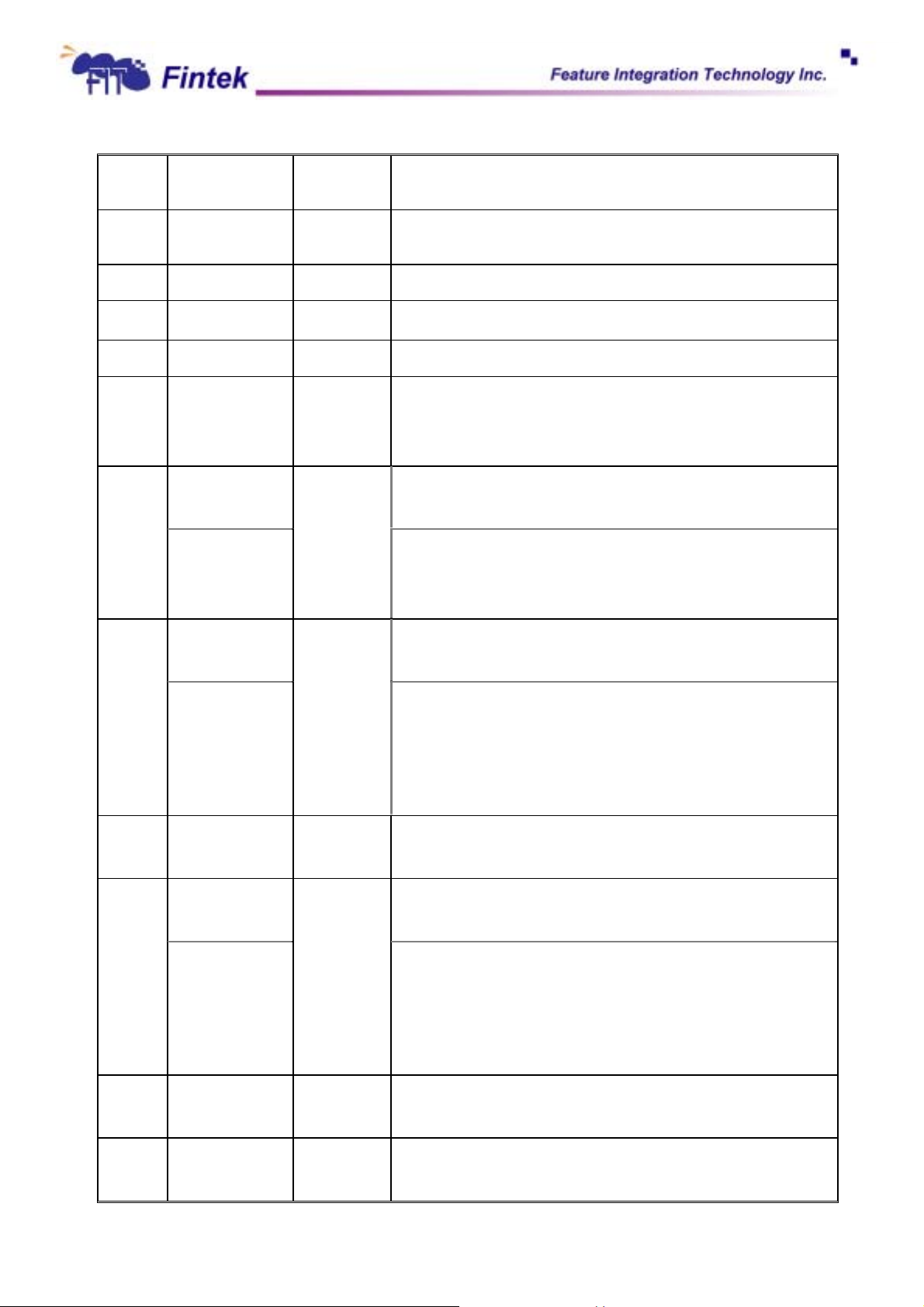

4. Pin Description

F81218D

I/O

8t5V-d100

- TTL level bi-directional pin with 8 mA source-sink capability, 5V tolerance, pull-down

100K ohms

I/O

- TTL level bi-directional pin with 12 mA source-sink capability

12t

I/OD

12

- TTL level bi-directional pin, Open-drain outpu with 12 mA sink capability

PCI5V - bi-direction pin, slew rate control, 5V tolerance.

OUT

OD

IN

IN

IN

IN

- Output pin with 12 mA source-sink capability

12

- Open-drain output pin with 12 mA sink capability

12

- TTL level input pin

t

- TTL level input pin and 5V tolerance.

t5V

- TTL level input pin and schmitt trigger

ts

ts5V

- TTL level input pin and Schmitt trigger, 5V tolerance.

P - Power

4.1 ISA/LPC Interface

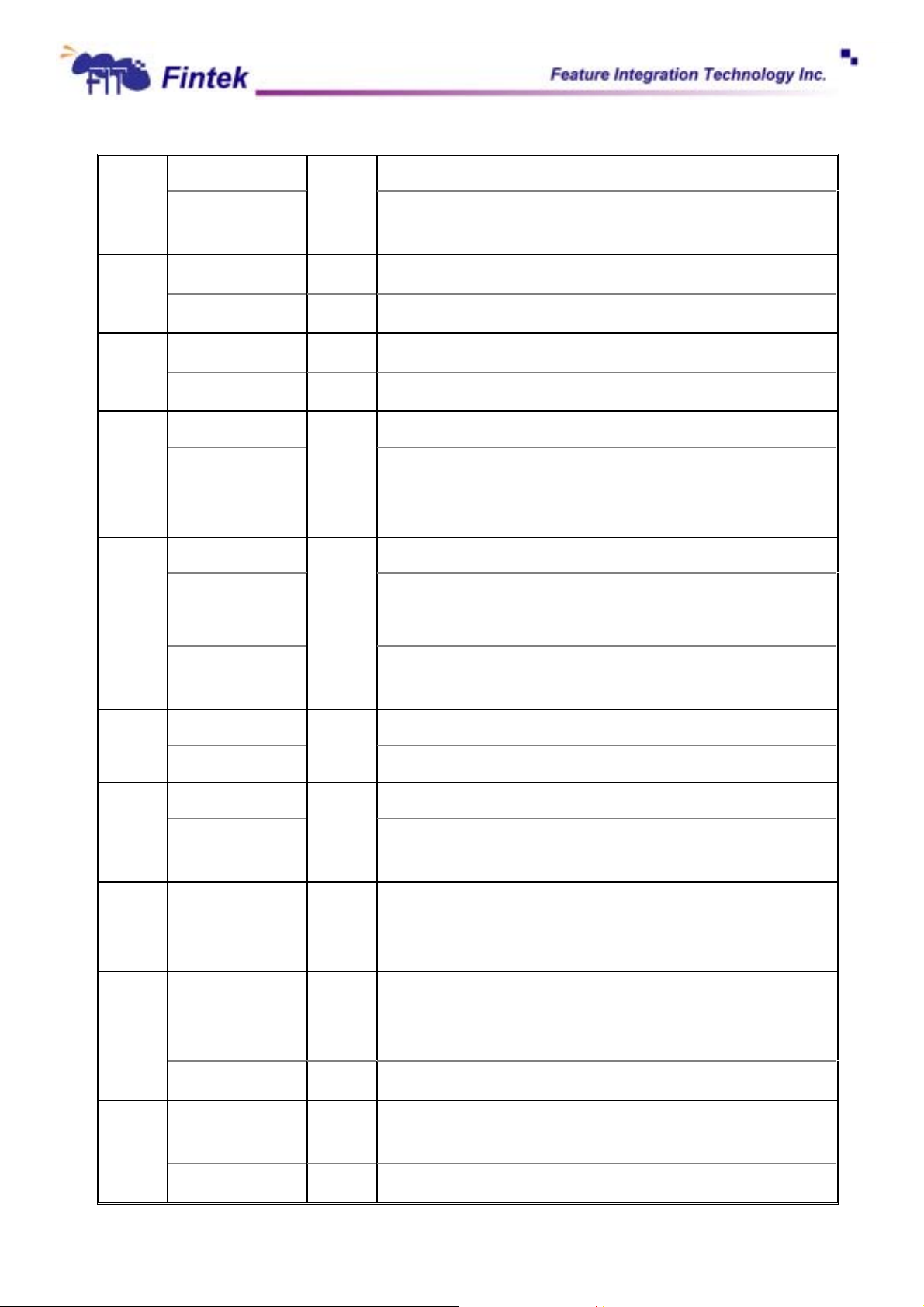

Pin No. Pin Name Ty pe Description

99

ISA_IRQA O12

IRQIN0 IN

Default is ISA IRQ output

When in LPC mode (pin 39 PS_LPC =1), the pin becomes LPC

t5V

to ISA IRQ input. About IRQ index setting please refer to pin84

and pin86.

100

ISA_IRQB O

IRQIN1 IN

12

t5V

Default is ISA IRQ output,

When in LPC mode (pin 39 PS_LPC =1), the pin becomes LPC

to ISA IRQ input. About IRQ index setting please refer to pin74

and pin76.

1 PCIRST# INts System PCI reset active low.

2 PME# OD12 Generated PME event.

3 WDT_OUT# OD12 Watch dog timer output. When pin 50 power on setting

PS_WDT=0(default), Watch Dog timer time interval setting is

programmed by register. Once power on setting PS_WDT=1,

watch dog timer time interval will be fixed to 10 sec.

Jan, 2004

-3-

V0.27P

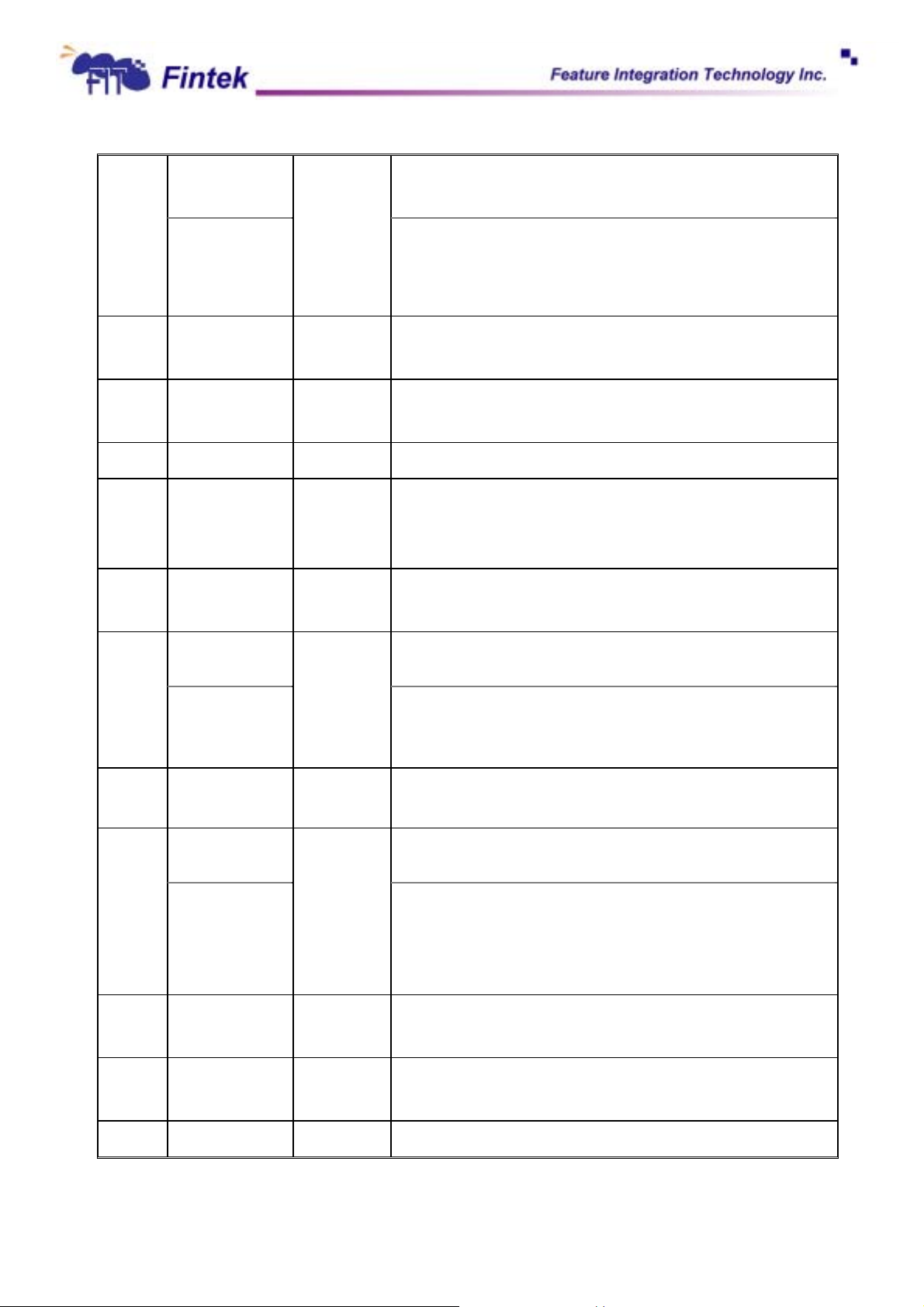

F81218D

4~7

ISA_A[3:0] ISA address bus bit 0-3.

LPC_A[3:0]

PCI5V

When in LPC mode, these pins become LPC to ISA address

output.

ISA_IOR IN

LPC_IOR

ISA_IOW IN

LPC_IOW

ISA_A[10:7] ISA address bus bits 7-10. 11~14

LPC_LAD[3:0]

OD

OD

PCI

t5V

t5V

CPU I/O read signal. 8

When in LPC mode, these pin becomes LPC to ISA IOR output.

12

CPU I/O write signal. 9

When in LPC mode, these pin becomes LPC to ISA IOW output.

12

5V

When in LPC mode, these signal lines communicate address,

control, and data information over the LPC bus between a host

and a peripheral.

ISA_A6 ISA address bus bit 6 15

LPC_PCICLK

IN

ts5V

In LPC mode, this pin acts as PCI clock input.

ISA_A5 ISA address bus bit 5 16

LPC_LFRAME#

IN

ts5V

In LPC mode, indicates start of a new cycle or termination of a

broken cycle.

ISA_A4 ISA address bus bit 4. 17

LPC_SERIRQ

ISA_D[7:0] ISA data bus bits 0-7 19~26

LPC_D[7:0]

PCI5V

In LPC mode, Serial IRQ input/Output.

PCI5V

When in LPC mode, the pins become LPC to ISA data bus bits

0-7.

27 CLKIN INt System clock input. According to the input frequency 24MHz or

48MHz, it is selectable through register. Default is 24MHz

input.

45

ISA_IRQE O12 Default is ISA IRQ output, can act as GPIO function by

programming register. About IRQ index setting please refer to

pin67.

44

GP15

IN

t5V

ISA_IRQF O12 Default is ISA IRQ output, can be GPIO by programming

When in LPC mode, this pin acts as GPIO function

register. About IRQ index setting please refer to pin33.

GP16

IN

t5V

Jan, 2004

When in LPC mode, this pin acts as GPIO function

-4-

V0.27P

F81218D

60

59

92~96

91

ISA_IRQC O12

LPC_GP26

IN

t5V

ISA_IRQD O12

GP27

ISA_A[15:11]

LPC_GP24

IN

t5V

IN

t

I/OD

LPC_GP23

LPC_GP22

LPC_GP21

LPC_GP20

ISA_CS#

IN

t

GP25 I/OD

Default is ISA IRQ output

When in LPC mode (pin 39 PS_LPC =1), the pin becomes GPIO.

About IRQ index setting please refer to pin52

Default is ISA IRQ output

When in LPC mode (pin 39 PS_LPC =1), the pin becomes GPIO.

About IRQ index setting please refer to pin41.

ISA address bus bits 11-15.

In LPC mode, these pins are all GPIO pins.

12

ISA chip select pin.

In LPC mode (pin 39 PS_LPC =1), this pin is GPIO.

12

4.2 UART Interface

Pin No. Pin Name Type Description

28 CTS6# IN

29 DSR6# IN

30 RTS6# I/O

ADD_DEC[1:0]# OUT12 ISA address decoder, 98,97

LPC_DEC[1:0]# OD

t5V

t5V

8t5V-d100

When in LPC mode (pin 39 PS_LPC =1), the pin becomes LPC

12

to ISA address decod er.

Clear To Send is the modem control input.

Data Set Ready. An active low signal indicates the modem or

data set is ready to establish a communication link and transfer

data to the UART.

UART 6 Request To Send. An active low signal informs the

modem or data set that the controller is ready to send data.

31 DTR6# I/O

UART 6 Data Terminal Ready. An active low signal informs

8t5V-d100

the modem or data set that controller is ready to communicate.

32 SIN6 IN

Serial Input. Used to receive serial data through the

t5V

communication link.

Jan, 2004

-5-

V0.27P

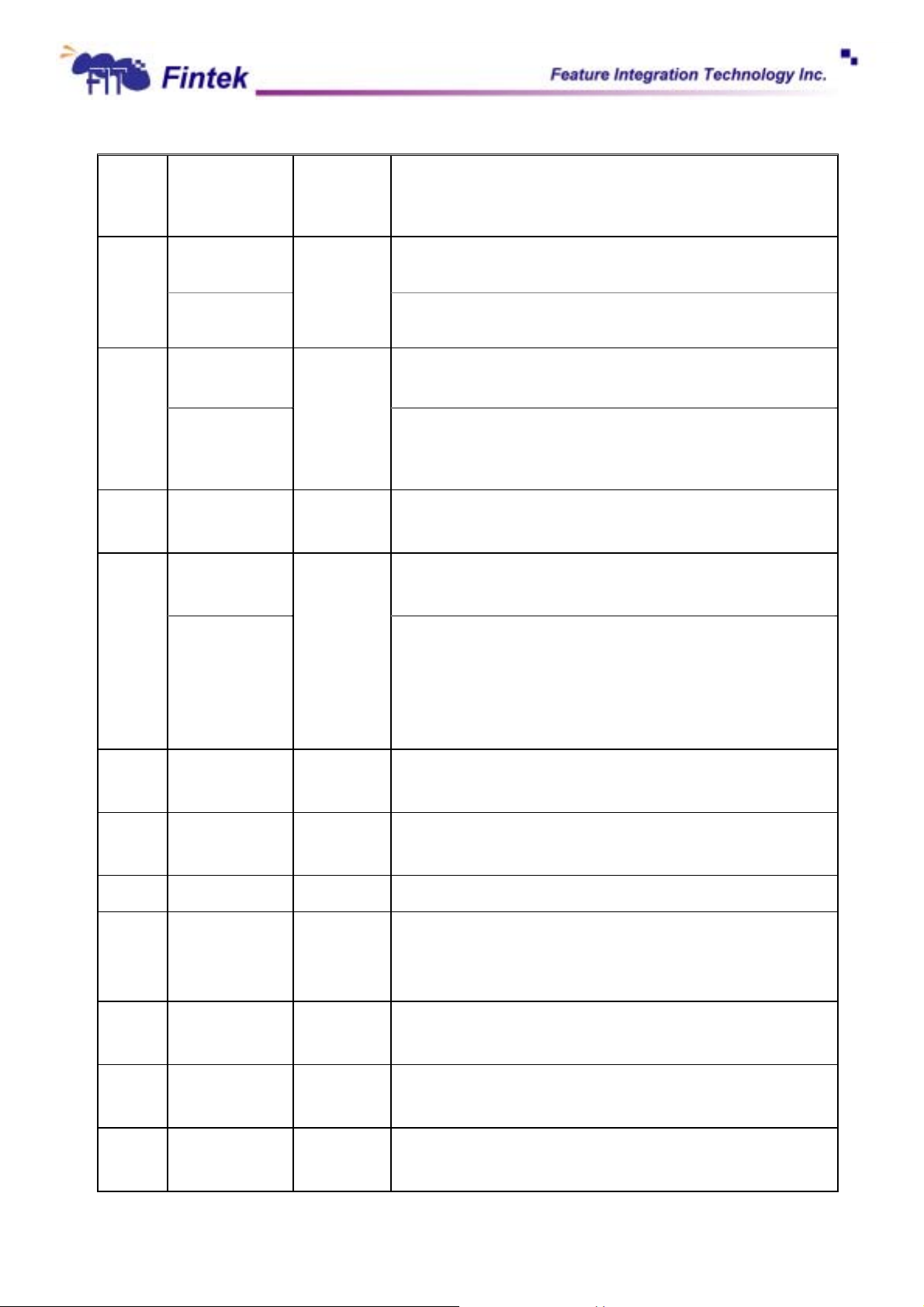

F81218D

33

SOUT6 UART 6 Serial Output. Used to transmit serial data out to the

I/O

PS_238_IRQF

34 DCD6# IN

35 RI6# IN

36 CTS4# IN

37 DSR4# IN

38 RTS4# I/O

8t5V-d100

communication link.

Power setting pin to define the IRQF index.

Default PS_238_IRQF = 0, IRQF index is programmed by

register. If PS_238_IRQF = 1, setting IRQF index to 0x238

Data Carrier Detect. An active low signal indicates the

t5V

modem or data set has detected a data carrie r.

Ring Indicator. An active low signal indicates that a ring

t5V

signal is being received from the modem or data set.

Clear To Send is the modem control input.

t5V

Data Set Ready. An active low signal indicates the modem or

t5V

data set is ready to establish a communication link and transfer

data to the UART.

UART 4 Request To Send. An active low signal informs the

8t5V-d100

modem or data set that the controller is ready to send data.

39

DTR4# UART 4 Data Terminal Ready. An active low signal informs

I/O

PS_LPC

40 SIN4 IN

41

SOUT4 UART 4 Serial Output. Used to transmit serial data out to the

I/O

PS_2E8_IRQD

42 DCD4# IN

43 RI4# IN

8t5V-d100

the modem or data set that controller is ready to communicate.

Power on setting pin to define the ISA or LPC interface.

Default PS_LPC=0, ISA interface.

When PS_LPC=1, transfer to LPC interface.

Serial Input. Used to receive serial data through the

t5V

communication link.

8t5V-d100

communication link.

Power setting pin to define the IRQD index.

Default PS_2E8_IRQD = 0, IRQF index is programmed by

register.

If PS_2E8_IRQD = 1, setting IRQF index to 0x2E8.

Data Carrier Detect. An active low signal indicates the

t5V

modem or data set has detected a data carrie r.

Ring Indicator. An active low signal indicates that a ring

t5V

signal is being received from the modem or data set.

47 CTS3# IN

Jan, 2004

Clear To Send is the modem control input.

t5V

-6-

V0.27P

F81218D

48 DSR3# IN

49

RTS3# UART 3 Request To Send. An active low signal informs the

I/O

PS_CONF_KE

Y0

50

DTR3# UART 3 Data Terminal Ready. An active low signal informs

I/O

PS_WDT

51 SIN3 IN

52

SOUT3 UART 3 Serial Output. Used to transmit serial data out to the

I/O

Data Set Ready. An active low signal indicates the modem or

t5V

data set is ready to establish a communication link and transfer

data to the UART.

8t5V-d100

modem or data set that the controller is ready to send data.

Power on configuration setting pin. As for detail description,

please refer to register description.

8t5V-d100

the modem or data set that controller is ready to communicate.

Power on setting pin to enable the watch dog timer.

Default PS_WDT=0, WDT time programmed by register.

When PS_WDT=1, WDT time is defined as 10 sec.

Serial Input. Used to receive serial data through the

t5V

communication link.

8t5V-d100

communication link.

PS_3E8_IRQC

53 DCD3# IN

54 RI3# IN

62 CTS5# IN

63 DSR5# IN

64 RTS5# I/O

65 DTR5# I/O

Power setting pin to define the IRQC index.

Default PS_3E8_IRQC = 0, IRQF index is programmed by

register.

If PS_3E8_IRQC = 1, setting IRQC index to 0x3E8.

Data Carrier Detect. An active low signal indicates the

t5V

modem or data set has detected a data carrie r.

Ring Indicator. An active low signal indicates that a ring

t5V

signal is being received from the modem or data set.

Clear To Send is the modem control input.

t5V

Data Set Ready. An active low signal indicates the modem or

t5V

data set is ready to establish a communication link and transfer

data to the UART.

UART 5 Request To Send. An active low signal informs the

8t5V-d100

modem or data set that the controller is ready to send data.

UART 5 Data Terminal Ready. An active low signal informs

8t5V-d100

the modem or data set that controller is ready to communicate.

66 SIN5 IN

Serial Input. Used to receive serial data through the

t5V

communication link.

Jan, 2004

-7-

V0.27P

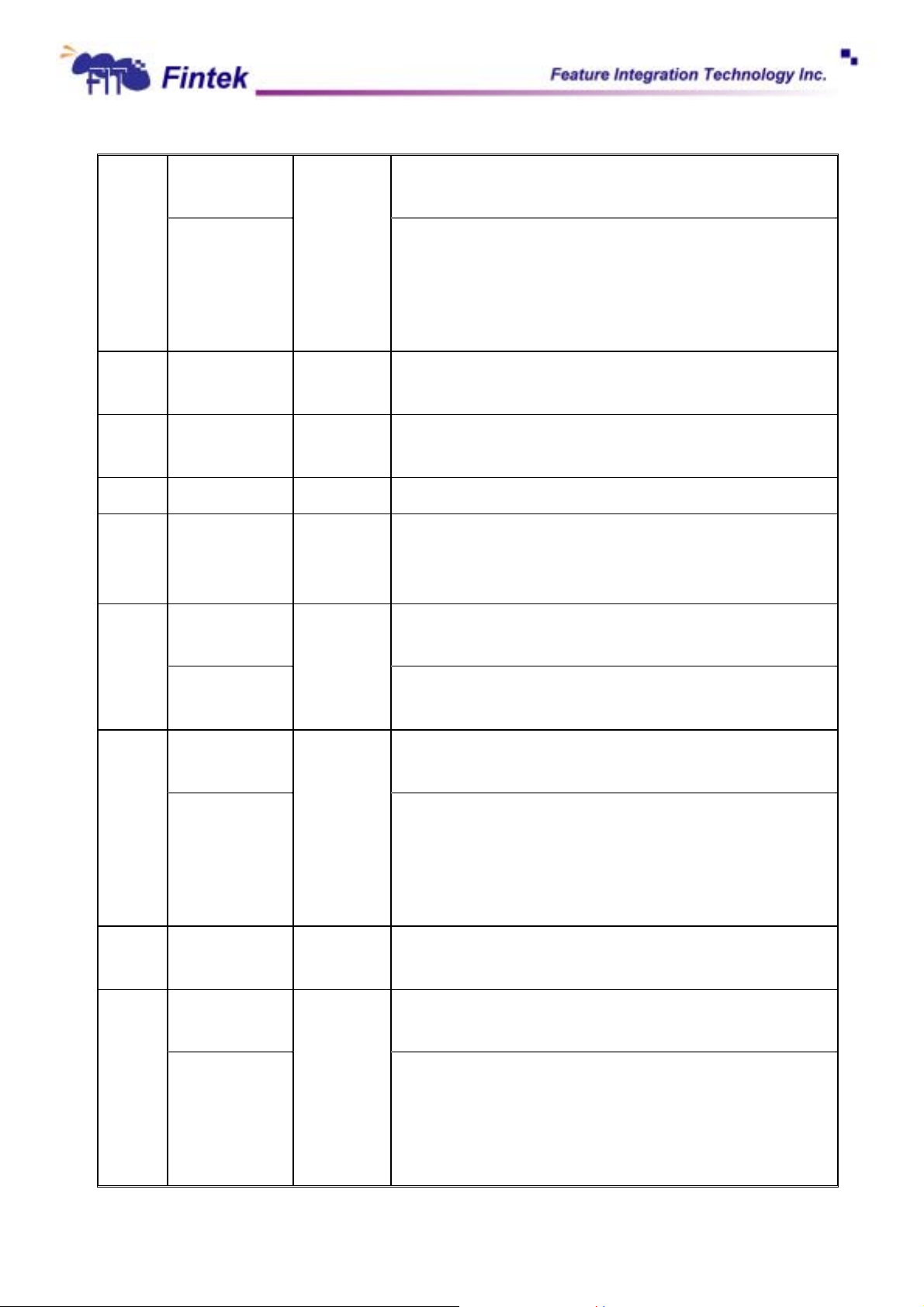

F81218D

67

SOUT5 UART 5 Serial Output. Used to transmit serial data out to the

I/O

PS_338_IRQE

69 DCD5# IN

70 RI5# IN

71 CTS2# IN

72 DSR2# IN

73

RTS2# UART 2 Request To Send. An active low signal informs the

I/O

8t5V-d100

communication link.

Power setting pin to define the IRQE index.

Default PS_338_IRQE = 0, IRQF index is programmed by

register.

If PS_338_IRQE = 1, setting IRQF index to 0x338.

Data Carrier Detect. An active low signal indicates the

t5V

modem or data set has detected a data carrie r.

Ring Indicator. An active low signal indicates that a ring

t5V

signal is being received from the modem or data set.

Clear To Send is the modem control input.

t5V

Data Set Ready. An active low signal indicates the modem or

t5V

data set is ready to establish a communication link and transfer

data to the UART.

8t5V-d100

modem or data set that the controller is ready to send data.

PS_CONF_KE

Y1

74

DTR2# UART 2 Data Terminal Ready. An active low signal informs

I/O

PS_2E0_IRQB

75 SIN2 IN

76

SOUT2 UART 2 Serial Output. Used to transmit serial data out to the

I/O

PS_2F8_IRQB

Power on configuration setting pin. As for detail description,

please refer to register description.

8t5V-d100

the modem or data set that controller is ready to communicate.

Power setting pin to define the IRQB index.

Default PS_2E0_IRQB = 0, IRQB index is programmed by

register.

If PS_2E0_IRQB = 1, setting IRQB index to 0x2E0.

Serial Input. Used to receive serial data through the

t5V

communication link.

8t5V-d100

communication link.

Power setting pin to define the IRQB index.

Default PS_2F8_IRQB = 0, IRQB index is programmed by

register.

If PS_2F8_IRQB = 1, setting IRQB index to 0x2F8.

Jan, 2004

-8-

V0.27P

F81218D

77 DCD2# IN

Data Carrier Detect. An active low signal indicates the

t5V

modem or data set has detected a data carrie r.

78 RI2# IN

Ring Indicator. An active low signal indicates that a ring

t5V

signal is being received from the modem or data set.

79 IRRX2 IN

Infrared Receiver input.

ts5V

80 IRTX2 OUT12 Infrared Transmitter Output.

81 CTS1# IN

82 DSR1# IN

Clear To Send is the modem control input.

t5V

Data Set Ready. An active low signal indicates the modem or

t5V

data set is ready to establish a communication link and transfer

data to the UART.

83

RTS1# UART 1 Request To Send. An active low signal informs the

I/O

8t5V-d100

modem or data set that the controller is ready to send data.

PS_CONF_2E

Power on configuration setting. Default PS_CONF_2E = 0,

setting the configuration to 0x4E. If PS_CONF_2E =1, setting

the configuration to 0x2E.

84

DTR1# UART 1 Data Terminal Ready. An active low signal informs

I/O

PS_3E0_IRQA

85 SIN1 IN

86

SOUT1 UART 1 Serial Output. Used to transmit serial data out to the

I/O

PS_3F8_IRQA

8t5V-d100

the modem or data set that controller is ready to communicate.

Power setting pin to define the IRQA index.

Default PS_3E0_IRQA = 0, IRQB index is programmed by

register.

If PS_3E0_IRQA = 1, setting IRQA index to 0x3E0.

Serial Input. Used to receive serial data through the

t5T

communication link.

8t5T-d100

communication link.

Power setting pin to define the IRQA index.

Default PS_3F8_IRQA = 0, IRQA index is programmed by

register.

If PS_3F8_IRQA = 1, setting IRQA index to 0x3F8.

87 DCD1# IN

Data Carrier Detect. An active low signal indicates the

t5T

modem or data set has detected a data carrie r.

88 RI1# IN

Ring Indicator. An active low signal indicates that a ring

t5T

signal is being received from the modem or data set.

Jan, 2004

-9-

V0.27P

F81218D

89 IRRX1 IN

90 IRTX1 OUT12 Infrared Transmitter Output.

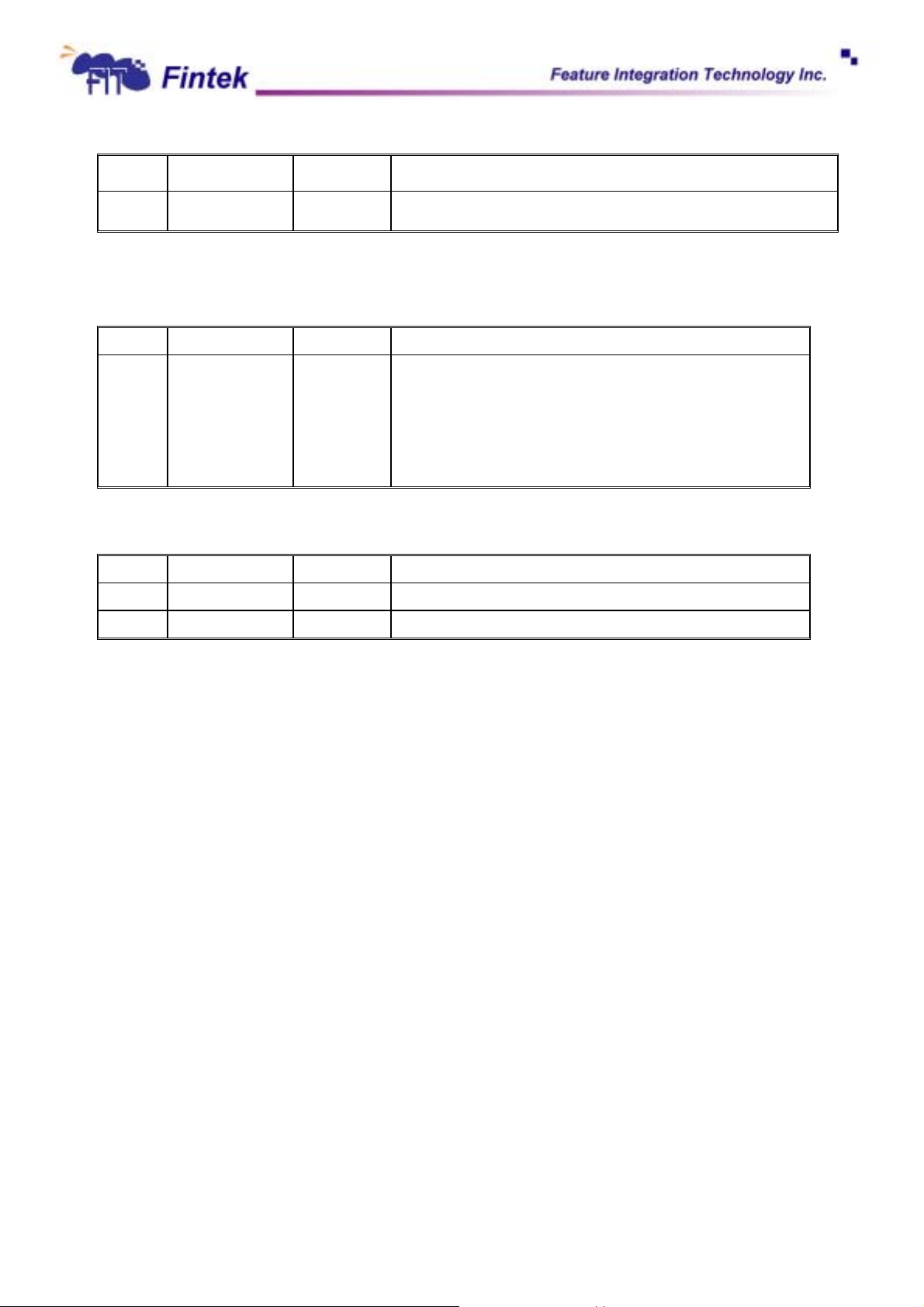

4.3 GPIO pins

Pin No. Pin Name Type Description

46,

55~58

4.4 Power

Pin No. Pin Name Type Description

18,68 VCC P 3.3V power supply.

GPIO14

GPIO13

GPIO12

GPIO11

GPIO10

Infrared Receiver input.

ts5T

I/OD

General purpose input/output pins.

12t

10,61 GND P Ground.

Jan, 2004

-10-

V0.27P

F81218D

5. Functional Description

The F81218D totally provides 6 UART ports through ISA or LPC interface which can be

selected by hardware setting. Among 6 UART ports, two ports can support serial infrared

communication. Besides, each UART includes 16-byte send/receive FIFO, a

programmable baud rate generator, completed modem control capability and interrupt

system. When using ISA interface mode, total 6 IRQ can be used, and each one supports

sharing function (IRQ sharing). 2 address decoder pins are provided for ISA mode as well.

When in LPC interface mode, some pins such as DATA pins, IOR, IOW, 2 address decoder,

ISA address A0-A3 can be simple LPC to ISA transferring bridge pins. And some other pins

can be set to be GPIO pins.

No matter in ISA or LPC mode, one watch dog timer is provided for system controlling

and the time interval can be programmed by register or hardware power on setting pin.

This IC needs one clock 24/48MHz input, and default is 24MHz. Powered by 3.3V voltage, the

F81218D is in 100pin LQFP

5.1 LPC Interface

The F81218D can support LPC interface serving as a bus interface between host

(chipset) and peripheral (I/O chip) by hardware trapping. This interface provides much less

pins and more efficient transmission. Data transfer on the LPC bus is serialized over a 4 bit

bus. The general characteristics of the interface implemented in F81218D are listed as

below:

One control line, namely LPC_FRAME#, which is used by the host to start or stop

transfers. No peripherals drive this signal.

The LPC_LAD[3:0] bus, which communicates information serially. The information

conveyed is cycle type, cycle direction, chip selection, address, data, and wait states.

PCIRST# is an active low reset signal.

An additional 33 MHz PCI clock is needed in the F81218D for synchronization.

Interrupt requests are issued through LPC_SERIRQ.

Power management events are issued through PME#.

Jan, 2004

-11-

V0.27P

F81218D

5.2 UART

A Universal Asynchronous Receiver/Transmitter (UART) is used to implement serial

communication. The F81218D incorporates six fully function UART compatible with NS16550D.

The UART ports perform serial to parallel conversion on receiving characters and parallel to

serial conversion on transmitting characters. The controllable characteristics of the data

transmission are baud rate, number of information bits per character, type of parity checking,

number of stop bits and breaking the transmission. The serial format is a start bit, followed by

five to eight data bits, a parity bit(if programmable), and one, one and half, or two stop bits. The

UART also includes completed modem control capability and interrupt system that may be

software trailed to the computing time required to handle the communication link. The UART

also has a FIFO mode to reduce the number of interrupts presented to the CPU. In the UART,

there is 16-byte FIFO for both receive and transmit mode.

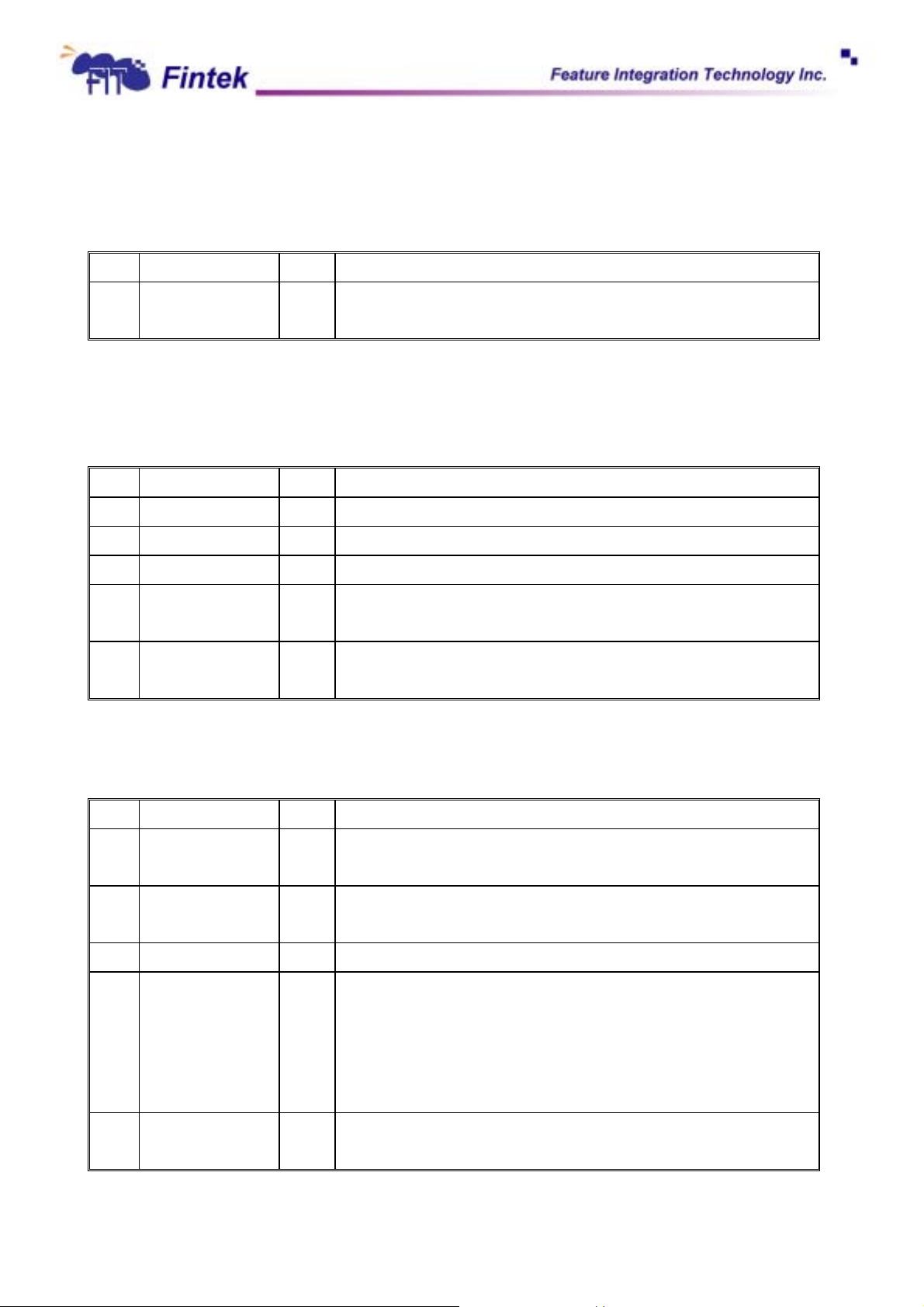

5.2.1 UART Port Register

5.2.1.1 Receiver Buffer Register – Base + 0

Power-on default [7:0] = 0x00h.

Bit Name R/W Description

7:0 RBR[7:0] R The data received .

Read only when LCR[7] is 0

5.2.1.2 Transmitter Holding Register – Base + 0

Power-on default [7:0] = 0x00h.

Bit Name R/W Description

7:0 THR[7:0] W Data to be transmitted.

Write only when LCR[7] is 0

5.2.1.3 Divisor Latch ( LS ) – Base + 0

Power-on default [7:0] = 0x01h.

Bit Name R/W Description

7:0 DLL[7:0] R/W Baud generator divisor low byte.

Access only when LCR[7] is 1.

Jan, 2004

-12-

V0.27P

F81218D

5.2.1.4 Divisor Latch ( MS ) – Base + 1

Power-on default [7:0] = 0x00h.

Bit Name R/W Description

7:0 DLM[7:0] R/W Baud generator divisor high byte.

Access only when LCR[7] is 1.

5.2.1.5 Interrupt Enable Register – Base + 1

Power-on default [7:0] = 0x00h.

Bit Name R/W Description

7:4 Reserved R/W Return 0 when read. Access only when LCR[7] is 0

3 EDSSI R/W Enable Modem Status Interrupt. Access only when LCR[7] is 0.

2 ELSI R/W Enable Line Status Error Interrupt. Access only when LCR[7] is 0.

1 ETBFI R/W Enable Transmitter Holding Register Empty Interrupt. Access only

when LCR[7] is 0.

0 ERBFI R/W Enable Received Data Available Interrupt. Access o nly whe n LCR[7]

is 0

5.2.1.6 Interrupt Identification Register – Base + 2

Power-on default [7:0] = 0x01h.

Bit Name R/W Description

7 FIFO_EN R 0 : FIFO is disabled

1 : FIFO is enabled.

6 FIFO_EN R 0 : FIFO is disabled.

1 : FIFO is enabled.

5:4 Reserved R Return 0 when read.

3:1 IRQ_ID[2:0] R 000 : Interrupt is caused by Modem Status

001 : Interrupt is caused by Transmitter Holding Register Empty

010 : Interrupt is caused by Received Data Available.

110 : Interrupt is caused by Character Timeout

011 : Interrupt is caused by Line Status..

0 IRQ_PENDN R 1 : Interrupt is not pending.

0 : Interrupt is pending.

Jan, 2004

-13-

V0.27P

Loading...

Loading...