Gigabyte F71882 Schematics

F71882

F71882

Super Hardware Monitor + LPC I/O

Release Date: Nov., 2006

Version: V0.24P

Nov., 2006

V0.24P

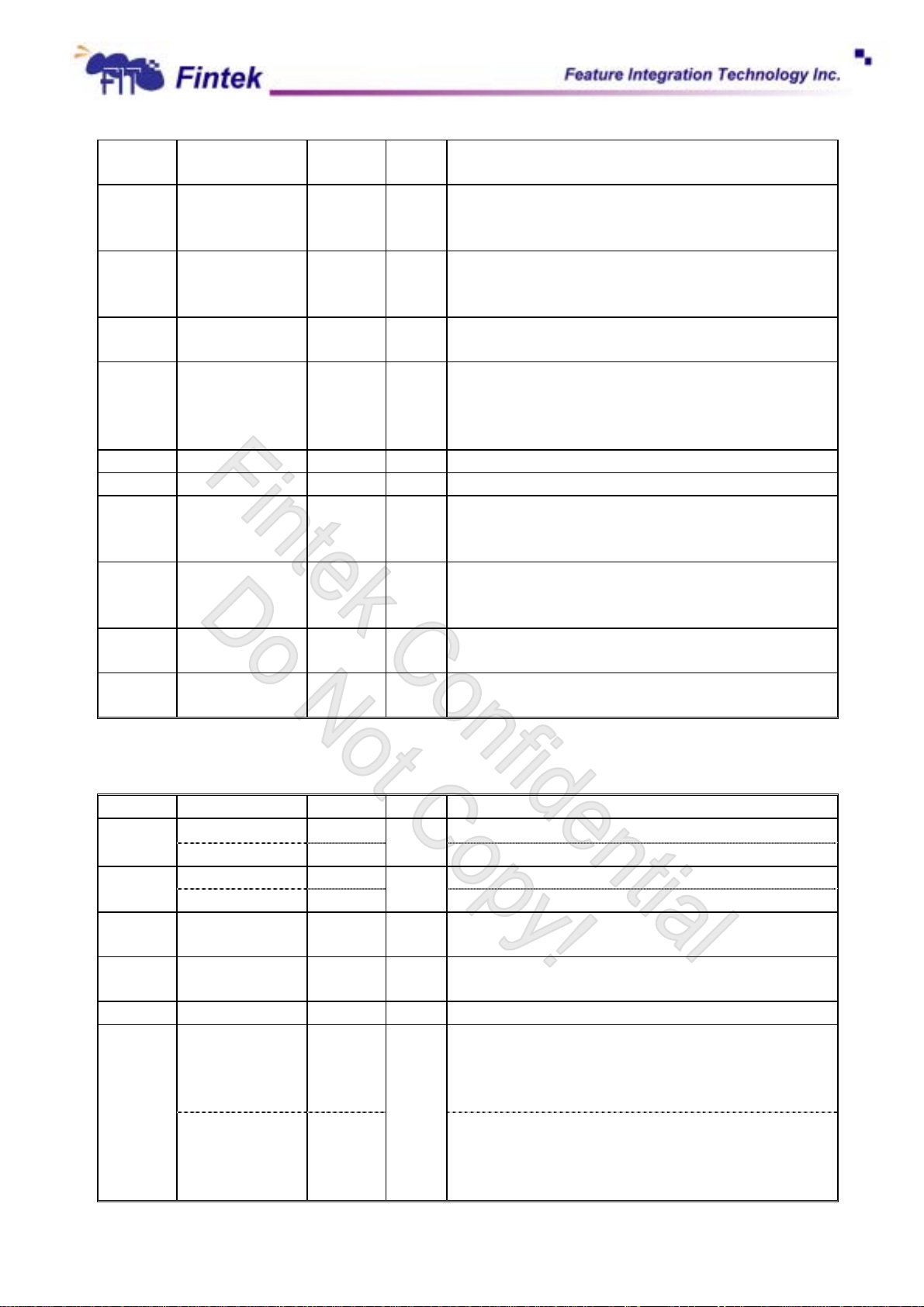

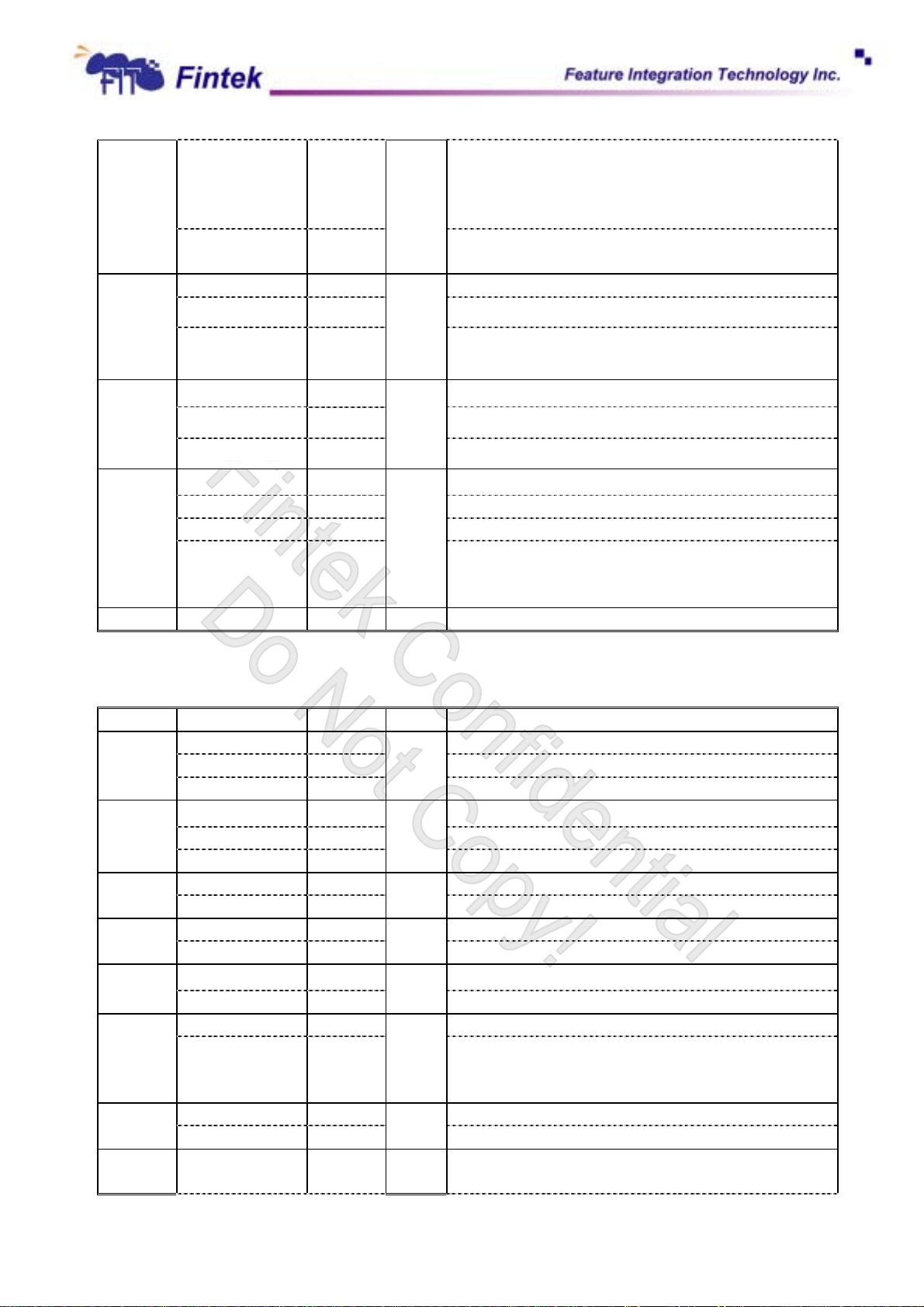

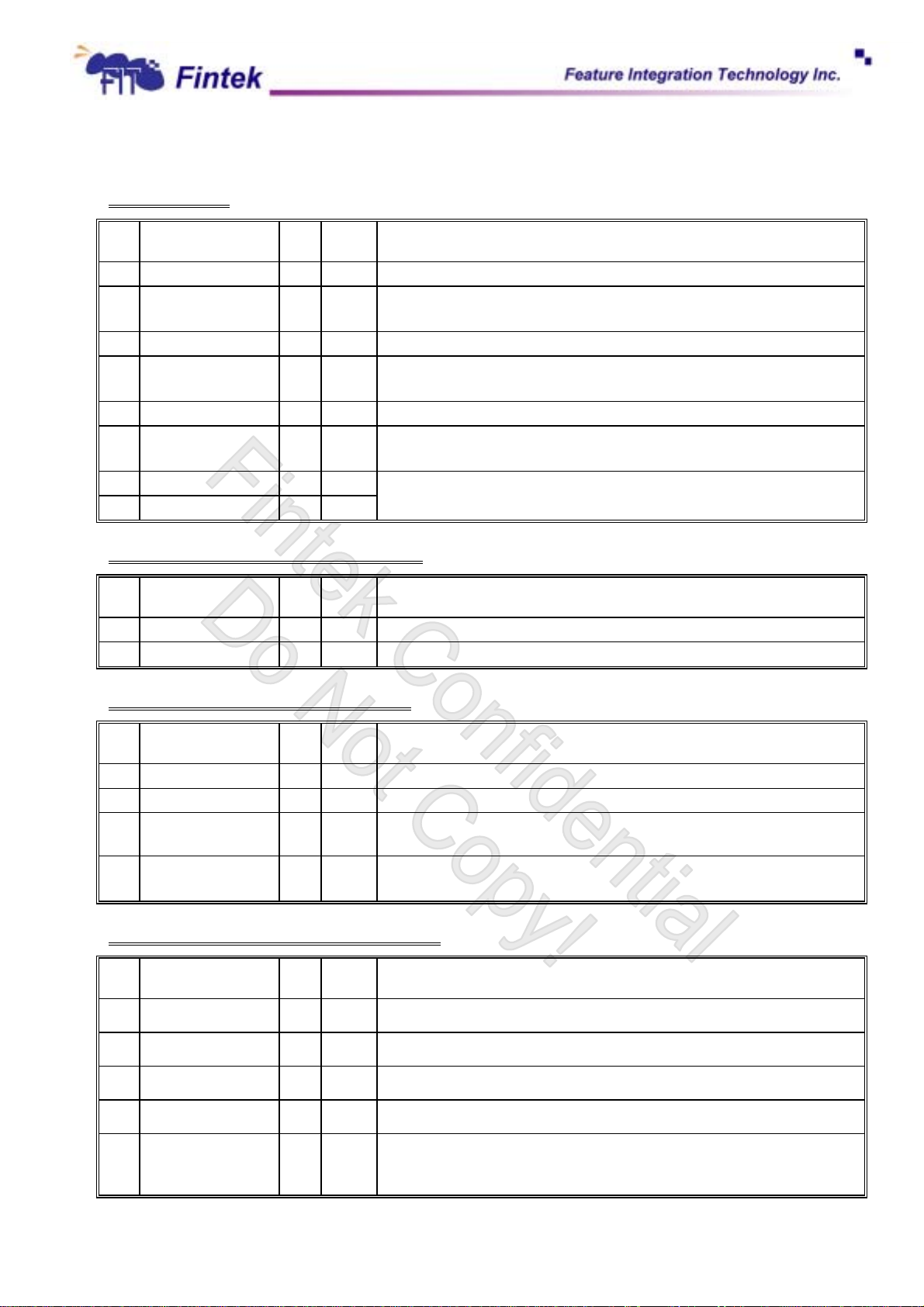

F71882 Datasheet Revision History

Version Date Page Revision History

0.20P 2005/10/14 - Release Version

0.21P 2005/12/08 8 Added New SPI Function of Pin1

13 Added New SPI Function Description of Power on

50 Added F1 Register Description of SPI Device Config.

53 Modified ROM Address Select Register Index 27h Bit5

103 Added Output Voltage Control Register 3 Index 09h

105 Added SPI Timeout Register Index F1h

106 Added SPI Status Register Index F3h Bit 6-5 Description.

107 Added SPI Memory Mapping Register Index F7h

0.21P 2005/12/14 - Updated the schematics

0.22P 2005/12/19 10 Added description of Pin 26

11 Modified Pin 77 that GPIO23 be the default function

12 Added SST/PECI Function on Pin 57/58

47 Multi Function Select 4 Register Index 2Ch bit3 default is 1

56 Multi Function Select 4 Register Index 2Ch bit3 default is 1

111 ACPI Control Register Index F5h bit 5 be set 0

0.23P 2006/1/19 - Added ALERT# function on Pin 64

- Added FAN60_100 power on strap pin on Pin 121

- Added WDTRST# function on Pin56

- Updated register description

- Updated application circuits

0.24P 2006/11/23 59 Modified the description of Wakeup Control Register 2Dh

F71882

Strapping Option (Pin1 & Pin5)

Registers.

Description.

Description.

Description.

bit 7(SPI_CS1_EN)

Please note that all data and specifications are subject to change without notice. All the trade marks of products

and companies mentioned in this data sheet belong to their respective owners.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Customers using or selling these products for

use in such applications do so at their own risk and agree to fully indemnify Fintek for any damages resulting from

such improper use or sales.

Nov., 2006

V0.24P

F71882

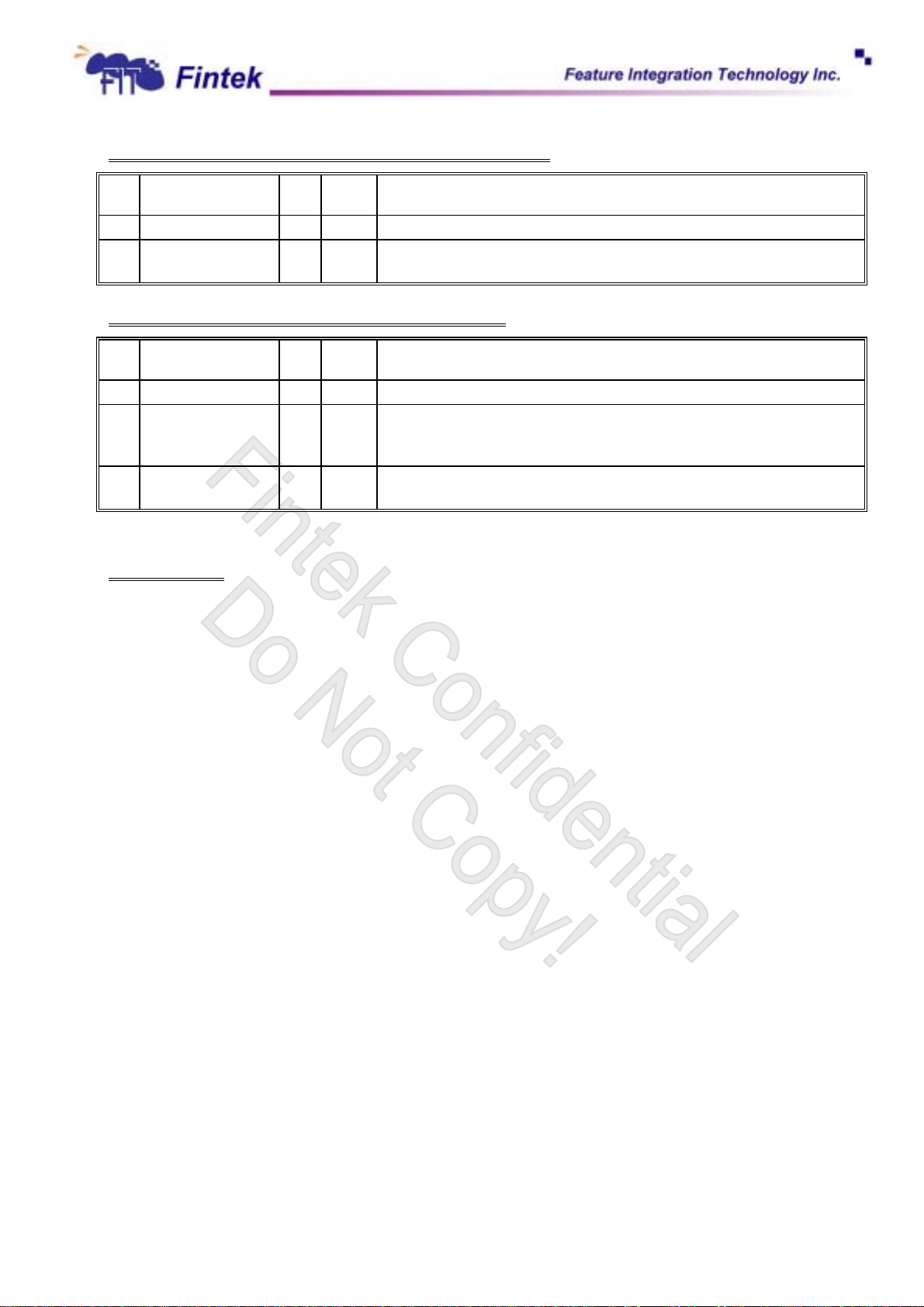

Table of Content

1. General Description........................................................................................................................1

2. Feature List .....................................................................................................................................1

3. Key Specification............................................................................................................................4

4. Block Diagram................................................................................................................................4

5. Pin Configuration............................................................................................................................5

6. Pin Description................................................................................................................................5

6.1 Power Pin....................................................................................................................................6

6.2 LPC Interface..............................................................................................................................6

6.3 FDC.............................................................................................................................................6

6.4 UART and SIR............................................................................................................................7

6.5 Parallel Port.................................................................................................................................9

6.6 Hardware Monitor.....................................................................................................................10

6.7 ACPI Function Pins ..................................................................................................................11

6.8 VID Controller..........................................................................................................................12

6.9 KBC Function...........................................................................................................................13

7. Function Description.....................................................................................................................14

7.1 Power on Strapping Option.......................................................................................................14

7.2 FDC...........................................................................................................................................14

7.3 UART........................................................................................................................................29

7.4 Parallel Port...............................................................................................................................32

7.5 Hardware Monitor.....................................................................................................................36

7.6 Keyboard Controller .................................................................................................................45

7.7 SPI Interface..............................................................................................................................46

7.8 ACPI Function..........................................................................................................................47

7.9 AMDSI and Intel SST PECI Function......................................................................................49

8. Register Description......................................................................................................................51

8.1 Global Control Registers...........................................................................................................55

8.2 FDC Registers (CR00)..............................................................................................................60

8.3 UART1 Registers (CR01).........................................................................................................63

8.4 UART 2 Registers (CR02)........................................................................................................64

8.5 Parallel Port Registers (CR03)..................................................................................................66

8.6 Hardware Monitor Registers (CR04)........................................................................................68

8.6.2.1 HW Monitor Config. Register Index 01h.....................................................................69

Nov., 2006

V0.24P

F71882

8.6.2.2 BEEP OVT ALERTConfig. Register Index 02h............................................................69

8.6.2.3 Case Open Config. Register Index 03h..........................................................................69

8.6.2.4 PECI AMDSI Select Register Index 0Ah......................................................................70

8.6.2.5 PECI CPU Select Register Index 0Bh (MEAS_TYPE == 2’b01)..............................70

8.6.2.6 AMDSI Version Register Index 0Bh (MEAS_TYPE ==2’b10).................................70

8.6.2.7 TCC Temp. Register Index 0Ch (MEAS_TYPE == 2’b01).......................................70

8.6.2.8 AMDSI Node ID Register Index 0Ch (MEAS_TYPE ==2’b10)...............................70

8.6.2.9 SST Address Register Index 0Dh ..................................................................................70

8.6.2.10 VID Divide Register Index 0Eh...................................................................................71

8.6.2.11 Configuration Register Index 0Fh................................................................................71

8.6.2.12 Voltage1 PME# Enable Register Index 10h.................................................................72

8.6.2.13 Voltage1 Interrupt Status Register Index 11h ..............................................................72

8.6.2.14 Voltage1 Exceeds Real Time Status Register 1 Index 12h ..........................................72

8.6.2.15 Voltage1 BEEP Enable Register Index 13h.................................................................72

8.6.2.16 Voltage reading and limit Index 20h- 4Fh ....................................................................72

8.6.2.17 Temperature PME# Enable Register Index 60h...........................................................73

8.6.2.18 Temperature Interrupt Status Register Index 61h ........................................................73

8.6.2.19 Temperature Real Time Status Register Index 62h......................................................74

8.6.2.20 Temperature BEEP Enable Register Index 63h...........................................................75

8.6.2.21 OVT Output Enable Register 1 Index 66h...................................................................75

8.6.2.22 Temperature Sensor Type Register Index 6Bh ............................................................75

8.6.2.23 TEMP1 Limit Hystersis Select Register -- Index 6Ch.....................................................76

8.6.2.24 TEMP2 and TEMP3 Limit Hystersis Select Register -- Index 6Dh................................76

8.6.2.25 DIODE OPEN Status Register -- Index 6Fh....................................................................76

8.6.2.26 Temperature Filter Select Register -- Index 8Eh .............................................................77

8.6.2.27 FAN PME# Enable Register

Index 90h.......................................................................78

8.6.2.28 FAN Interrupt Status Register Index 91h.....................................................................78

8.6.2.29 FAN Real Time Status Register

Index 92h..................................................................79

8.6.2.30 FAN BEEP# Enable Register Index 93h .....................................................................79

8.6.2.31 Fan Type Select Register -- Index 94h.............................................................................79

8.6.2.32 Fan mode Select Register -- Index 96h............................................................................80

8.6.2.33 Auto Fan1 and Fan2 Boundary Hystersis Select Register -- Index 98h..........................81

8.6.2.34 Auto Fan3 and Fan4 Boundary Hystersis Select Register -- Index 99h..........................82

8.6.2.35 Auto Fan3 and Fan4 Boundary Hystersis Select Register -- Index 9Bh..........................82

8.6.2.36 FAN1 and FAN2 START UP DUTY-CYCLE/VOLTAGE

Index 9Ch........................82

8.6.2.37 FAN3 and FAN4 START UP DUTY-CYCLE/VOLTAGE Index 9Dh........................83

8.6.2.38 Fan Fault Time Register -- Index 9Fh..............................................................................83

Nov., 2006

V0.24P

F71882

8.6.2.39 VT1 BOUNDARY 1 TEMPERATURE – Index A6h......................................................84

8.6.2.40 VT1 BOUNDARY 2 TEMPERATURE – Index A7........................................................84

8.6.2.41 VT1 BOUNDARY 3 TEMPERATURE – Index A8h......................................................85

8.6.2.42 VT1 BOUNDARY 4 TEMPERATURE – Index A9........................................................85

8.6.2.43 FAN1 SEGMENT 1 SPEED COUNT – Index AAh ....................................................85

8.6.2.44 FAN1 SEGMENT 2 SPEED COUNT – Index ABh.....................................................86

8.6.2.45 FAN1 SEGMENT 3 SPEED COUNT – Index ACh...................................................86

8.6.2.46 FAN1 SEGMENT 4 SPEED COUNT – Index ADh ..................................................86

8.6.2.47 FAN1 SEGMENT 5 SPEED COUNT – Index AEh...................................................86

8.6.2.48 FAN1 Temperature Mapping Select – Index AFh.......................................................86

8.6.2.49 VT2 BOUNDARY 1 TEMPERATURE – Index B6h......................................................88

8.6.2.50 VT2 BOUNDARY 2 TEMPERATURE – Index B7........................................................88

8.6.2.51 VT2 BOUNDARY 3 TEMPERATURE – Index B8h......................................................88

8.6.2.52 VT2 BOUNDARY 4 TEMPERATURE – Index B9........................................................88

8.6.2.53 FAN2 SEGMENT 1 SPEED COUNT – Index BAh ....................................................89

8.6.2.54 FAN2 SEGMENT 2 SPEED COUNT – Index BBh.....................................................89

8.6.2.55 FAN2 SEGMENT 3 SPEED COUNT – Index BCh...................................................89

8.6.2.56 FAN2 SEGMENT 4 SPEED COUNT – Index BDh ..................................................89

8.6.2.57 FAN2 SEGMENT 5 SPEED COUNT – Index BEh...................................................90

8.6.2.58 FAN2 Temperature Mapping Select – Index BFh.......................................................90

8.6.2.59 VT3 BOUNDARY 1 TEMPERATURE – Index C6h......................................................91

8.6.2.60 VT3 BOUNDARY 2 TEMPERATURE – Index C7........................................................91

8.6.2.61 VT3 BOUNDARY 3 TEMPERATURE – Index C8h......................................................92

8.6.2.62 VT3 BOUNDARY 4 TEMPERATURE – Index C9........................................................92

8.6.2.63 FAN3 SEGMENT 1 SPEED COUNT – Index CAh ....................................................92

8.6.2.64 FAN3 SEGMENT 2 SPEED COUNT – Index CBh.....................................................93

8.6.2.65 FAN3 SEGMENT 3 SPEED COUNT – Index CCh...................................................93

8.6.2.66 FAN3 SEGMENT 4 SPEED COUNT – Index CDh ..................................................93

8.6.2.67 FAN3 SEGMENT 5 SPEED COUNT – Index CEh...................................................93

8.6.2.68 FAN3 Temperature Mapping Select – Index CFh.......................................................93

8.6.2.69 VT4 BOUNDARY 1 TEMPERATURE – Index D6h .....................................................95

8.6.2.70 VT4 BOUNDARY 2 TEMPERATURE – Index D7 .......................................................95

8.6.2.71 VT4 BOUNDARY 3 TEMPERATURE – Index D8h .....................................................95

8.6.2.72 VT4 BOUNDARY 4 TEMPERATURE – Index D9 .......................................................95

8.6.2.73 FAN4 SEGMENT 1 SPEED COUNT – Index DAh ....................................................96

8.6.2.74 FAN4 SEGMENT 2 SPEED COUNT – Index DBh ....................................................96

8.6.2.75 FAN4 SEGMENT 3 SPEED COUNT – Index DCh ..................................................96

Nov., 2006

V0.24P

F71882

8.6.2.76 FAN4 SEGMENT 4 SPEED COUNT – Index DDh ..................................................96

8.6.2.77 FAN4 SEGMENT 5 SPEED COUNT – Index DEh...................................................97

8.6.2.78 FAN4 Temperature Mapping Select – Index DFh ......................................................97

8.7 KBC Registers (CR05) .............................................................................................................98

8.8 GPIO Registers (CR06) ..........................................................................................................100

8.9 VID Registers (CR07).............................................................................................................107

8.10 SPI Registers (CR08)..............................................................................................................111

8.11 PME and ACPI Registers (CR0A)..........................................................................................115

9. Electron Characteristic................................................................................................................118

9.1 Absolute Maximum Ratings...................................................................................................118

9.2 DC Characteristics..................................................................................................................118

9.3 DC Characteristics Continued.................................................................................................118

10. Ordering Information..................................................................................................................119

11. Package Dimensions...................................................................................................................120

12. Application Circuit......................................................................................................................121

Nov., 2006

V0.24P

F71882

1. General Description

The F71882 is the featured IO chip for PC system. Equipped with one IEEE 1284

parallel port, two UART ports, KBC, Serial Peripheral Interface (SPI), SIR and one FDC. The

F71882 integrated with hardware monitor, 9 sets of voltage sensor, 4 sets of creative

auto-controlling fans and 4 temperature sensor pins for the accurate dual current type temp.

measurement for CPU thermal diode or external transistors 2N3906.

The F71882 provides flexible features for multi-directional application. For instance,

supports 6/12 pins CPU VID controlling for VRM9.0/10.0/11* and CPU VID OTF (On The Fly),

provides 32 GPIO pins (multi-pin), IRQ sharing function also designed in UART feature for

particular usage and accurate current mode H/W monitor will be worth in measurement of

temperature, provides 3 modes fan speed control mechanism included Manual Mode/Speed

Mode/Temperature Mode for users’ selection Additionally, provides easy voltage sensor input

(VSI) function for sensing Vcore voltage, then output (VSO) the offset voltage for over/under

voltage change use.

of over-clocking or under-clocking. This function provides a pin by external trigger signal to

improve the CPU’s performance by voltage offset automatically when system is going to run

over-clocking or under-clocking. Due to achieve this action, suggest F75133S Loading Gauge

chip can be the part which detects system/CPU loading to decide when issues the

over-clocking/under-clocking signal for system executing. Briefly, user can gain more features

on motherboard by these two parts which improve performance and efficiency.

bridge function and back up function. Others, the F71882 supports newest AMDSI and Intel

PECI/SST interfaces for temperature use. These features as above description will help you

more and improve product value. Finally, the F71882 is powered by 3.3V voltage, with the

LPC interface in the package of 128-PQFP.

Further, the F71882 supports an automatic/dynamic over-voltage function for application

The F71882 also integrated SPI interface. The SPI interface is for BIOS usage including

2. Feature List

General Functions

¾ Comply with LPC Spec. 1.0

¾ Support DPM (Device Power Management), ACPI

¾ 6/12 VID pins for VRM9.0/10.0/11.0* and CPU VID OTF (On The Fly)

¾ Easy voltage sensor I/O (VSI/VSO) for Vcore change use.

¾ Support automatic and dynamic voltage change function

(2 Turbo pins Turbo1# and Turbo2# for VID usage)

¾ Provides one FDC, two UARTs, KBC and Parallel Port

Nov., 2006

-1V0.24P

F71882

¾ H/W monitor functions

¾ SPI interface for BIOS usage

¾ Support AMD SID/SIC interface and Intel SST/PECI interface

¾ 32 GPIO Pins for flexible application

¾ 24/48 MHz clock input

¾ Packaged in 128-PQFP and powered by 3.3VCC

FDC

¾ Compatible with IBM PC AT disk drive systems

¾ Variable write pre-compensation with track selectable capability

¾ Support vertical recording format

¾ DMA enable logic

¾ 16-byte data FIFOs

¾ Support floppy disk drives and tape drives

¾ Detects all overrun and under run conditions

¾ Built-in address mark detection circuit to simplify the read electronics

¾ Completely compatible with industry standard 82077

¾ 360K/720K/1.2M/1.44M/2.88M format; 250K, 300K, 500K, 1M, 2M bps data transfer rate

UART

¾ Two high-speed 16C550 compatible UART with 16-byte FIFOs

¾ Fully programmable serial-interface characteristics

¾ Baud rate up to 115.2K

¾ Support IRQ sharing

Infrared

¾ Support IrDA version 1.0 SIR protocol with maximum baud rate up to 115.2K bps

Parallel Port

¾ One PS/2 compatible bi-directional parallel port

¾ Support Enhanced Parallel Port (EPP)

¾ Support Extended Capabilities Port (ECP)

¾ Enhanced printer port back-drive current protection

− Compatible with IEEE 1284 specification

− Compatible with IEEE 1284 specification

Keyboard Controller

¾ 8042 based with optional F/W from AMIKKEYTM-2, with 2K bytes of programmable

ROM, and 256 bytes of RAM

¾ Asynchronous Access to Two Data Registers and One status Register

Nov., 2006

-2V0.24P

F71882

¾ Software compatibility with the 8042

¾ Support PS/2 mouse

¾ Support both interrupt and polling modes

¾ Fast Gate A20 and Hardware Keyboard Reset

¾ 6 MHz, 8 MHz, 12 MHz, or 16 MHz operating frequency

Hardware Monitor Functions

¾ 3 dual current type (±3℃) thermal inputs for CPU thermal diode and 2N3906 transistors

¾ Temperature range -20℃~145 (One is from ℃ -20~127 , ℃ others are from 0~ 145℃)

¾ 9 sets voltage monitoring (6 external and 3 internal powers)

¾ High limit signal (SMI#) for Vcore level

¾ 4 fan speed monitoring inputs

¾ 4 fan speed PWM/DC control outputs(support 3 wire and 4 wire fans)

¾ Issue PME# and OVT# hardware signals output

¾ Case intrusion detection circuit

¾ WATCHDOG# comparison of all monitored values

¾

Support AMDSI interface

Serial Peripheral Interface Compatible

¾ Support SPI bridge function for BIOS use

¾ Support Back Up BIOS function

Integrate AMD SI Interface

Integrate Intel PECI/SST Interface

Package

¾ 128-pin PQFP Green Package

Noted: Patented TW207103 TW207104 TW220442 US6788131 B1 TWI235231 TW237183 TWI263778

Nov., 2006

-3-

V0.24P

r

F71882

3. Key Specification

Supply Voltage 3.0V to 3.6V

Operating Supply Current ----- mA typ.

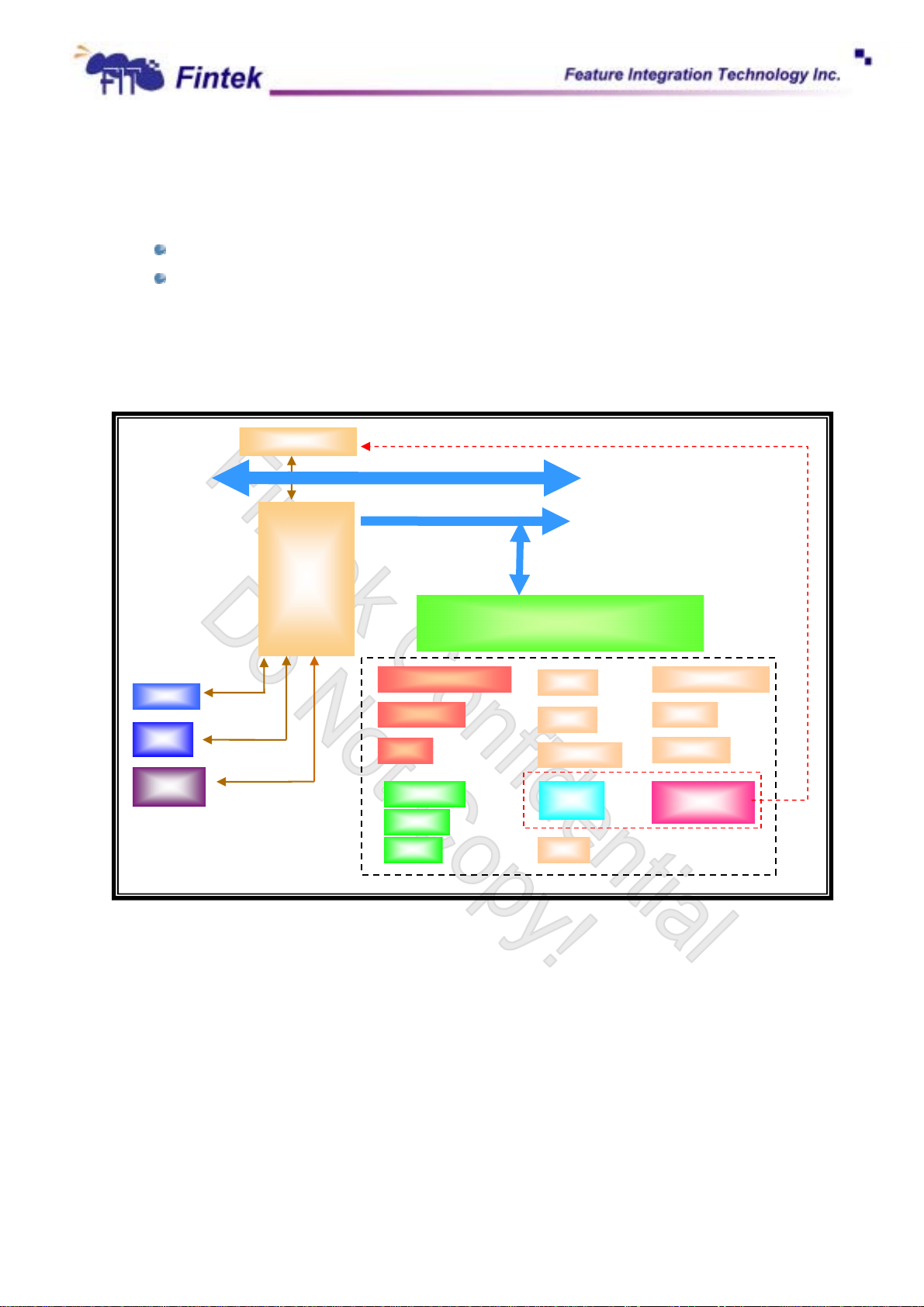

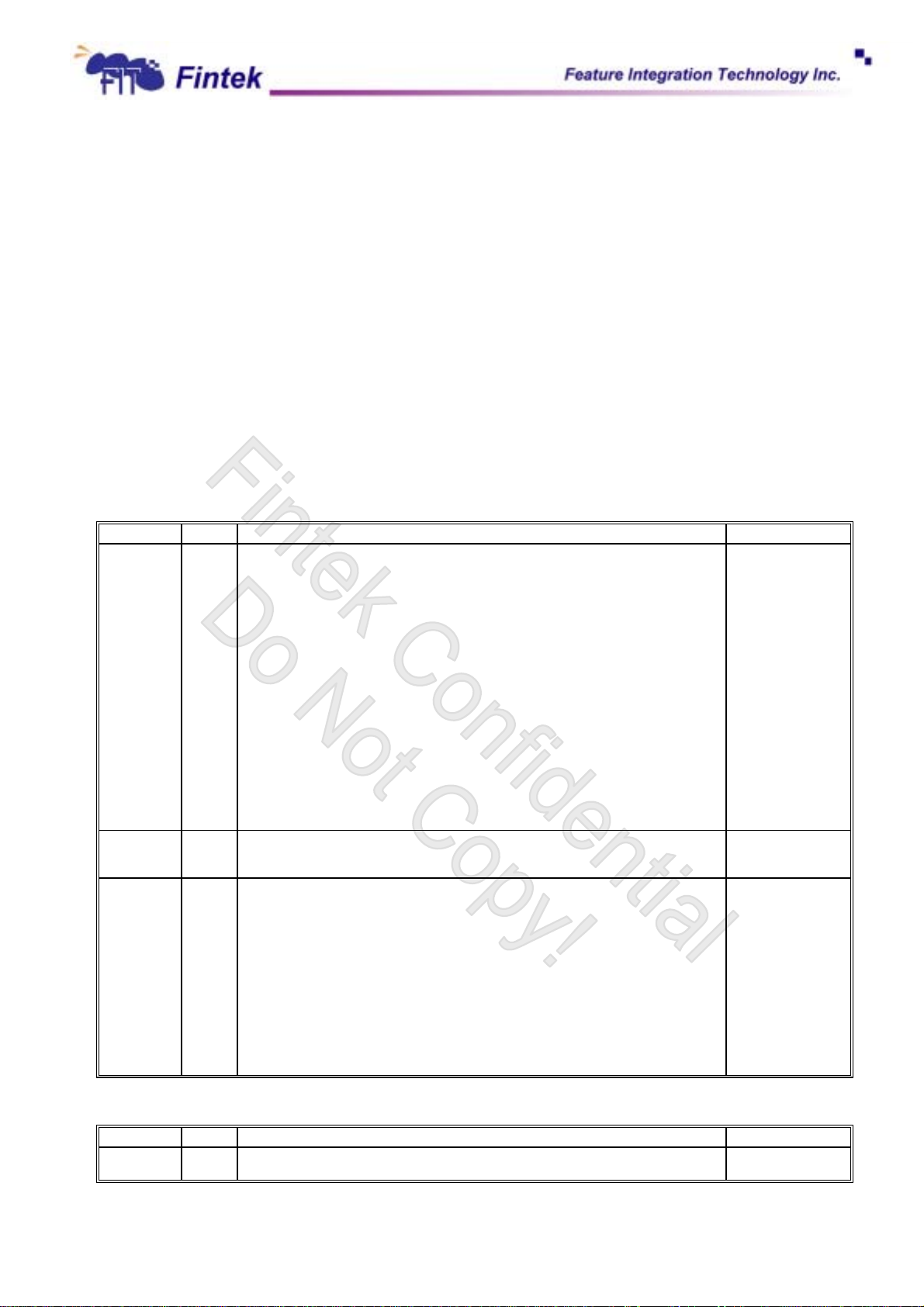

4. Block Diagram

CPU

Chipset

(NB+SB)

Super H/W Monitor + I/O

F71882

IDE

USB

AC’97

Temperature

Voltage

Fan

AMDSI

A PECI

SST

KBC

IrDA

Parallel

ACPI

SPI

LED(GPIO)

COM

Floppy

VID

Controlle

Nov., 2006

-4V0.24P

F71882

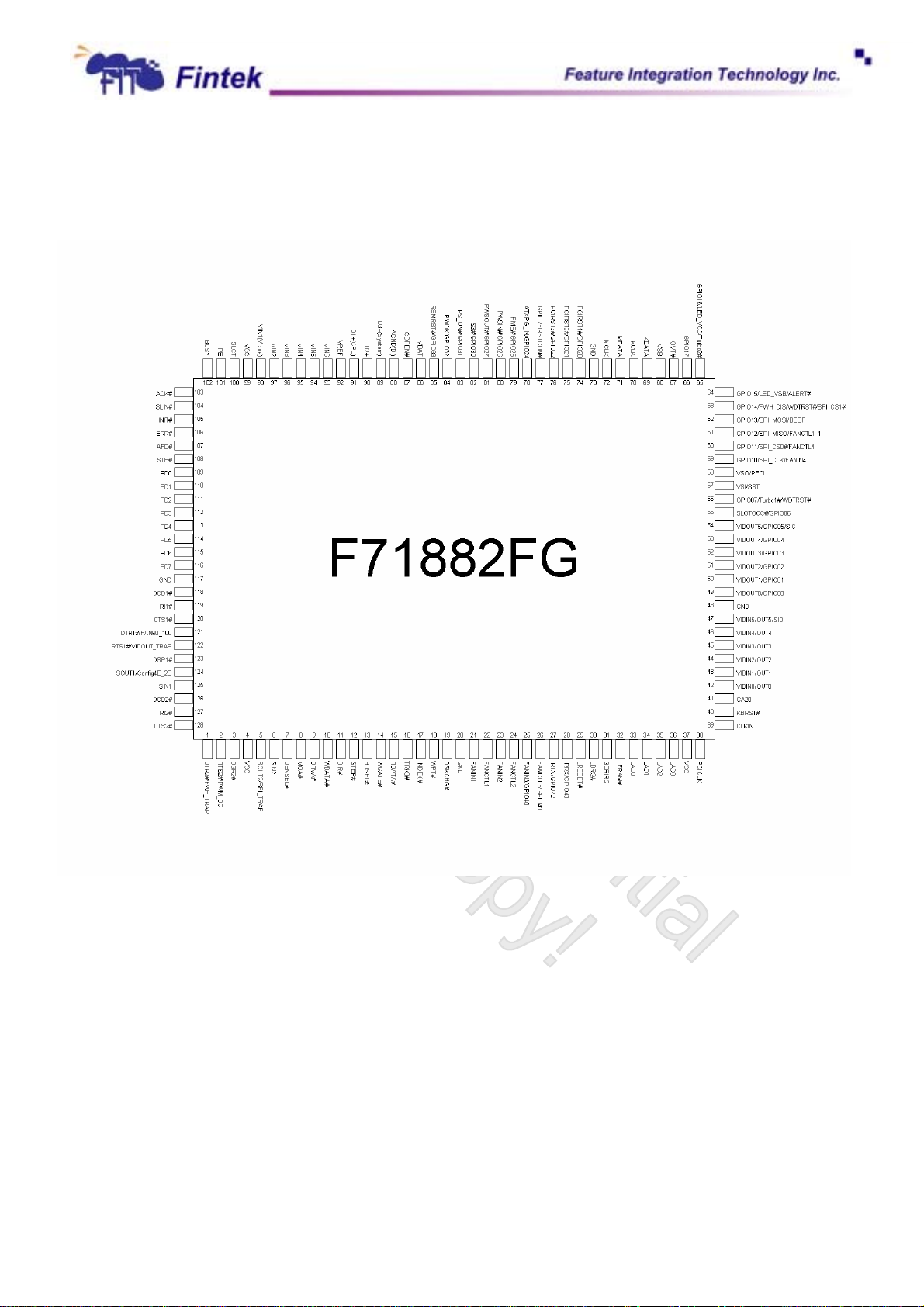

5. Pin Configuration

6. Pin Description

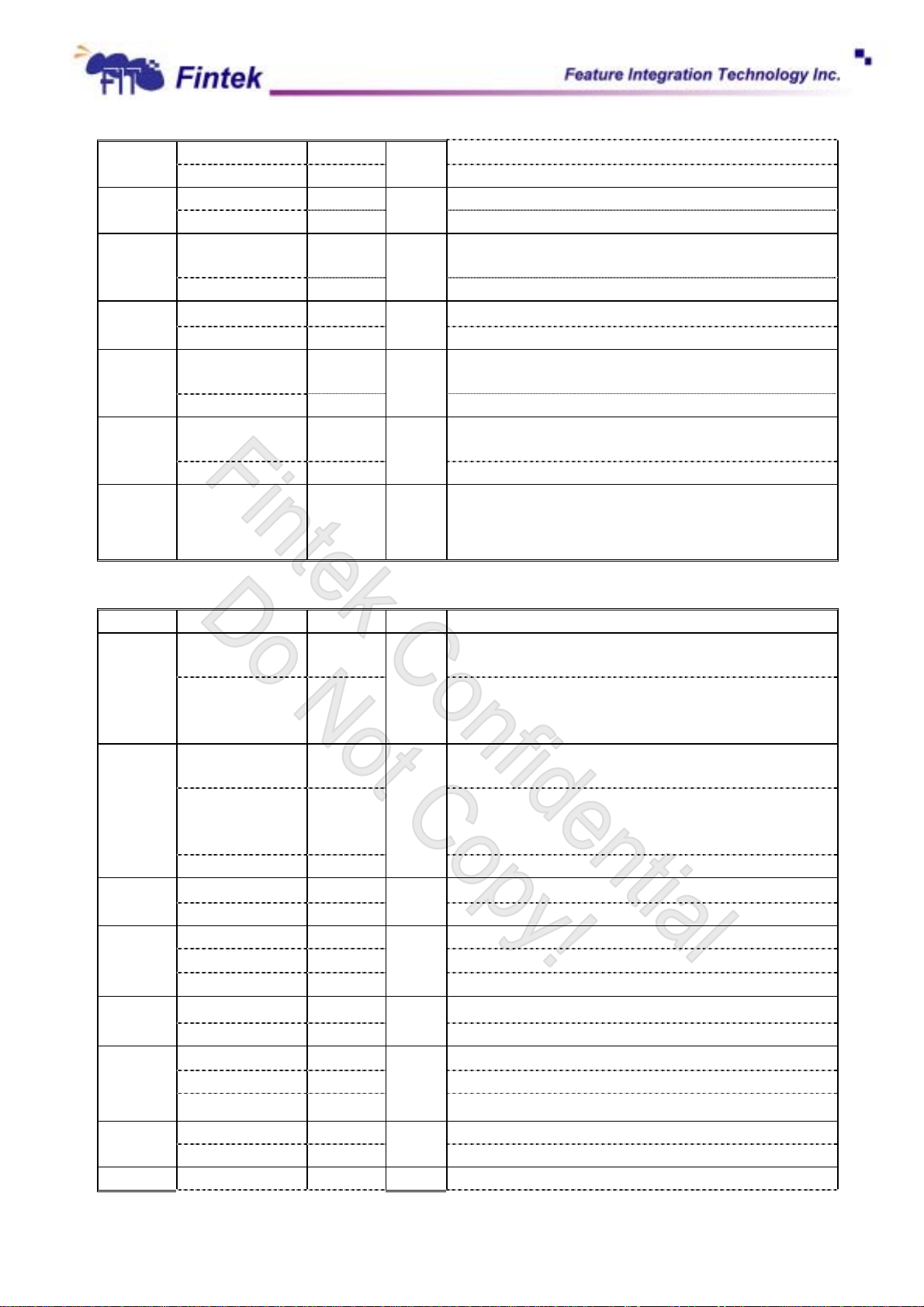

I/O

- TTL level bi-directional pin with 12 mA source-sink cap ability.

12t

I/OOD

I/OD

16t5v

OD

16-u10-5v

I/OD

12ts5v

ILv/O

D8-S1

ILv/OD

- TTL level bi-directional pin, can select to OD or OUT by register, with 12 mA

12t

source-sink capability.

- TTL level bi-directional pin,Open-drain output with 16 mA source-sink capability, 5V

tolerance.

- Open-drain output pin with 16 mA sink capability, pull-up 10k ohms, 5V tolerance.

- TTL level bi-directional pin and schmitt trigger, Open-drain output with 12 mA sink

capability, 5V tolerance.

- Low level bi-directional pin (VIH Æ 0.9V, VIL Æ 0.6V.). Output with 8mA drive and

1mA sink capability.

- Low level bi-directional pin (VIH Æ 0.9V, VIL Æ 0.6V.). Output with 12mA sink

12

Nov., 2006

-5V0.24P

F71882

O

O

O

O30

AOUT - Output pin(Analog).

OD

OD

OD24

IN

INts

IN

AIN - Input pin(Analog).

P - Power.

8-u47-5v

8

12

12

12-5v

t5v

- TTL level input pin and schmitt trigger, 5V tolerance.

ts5v

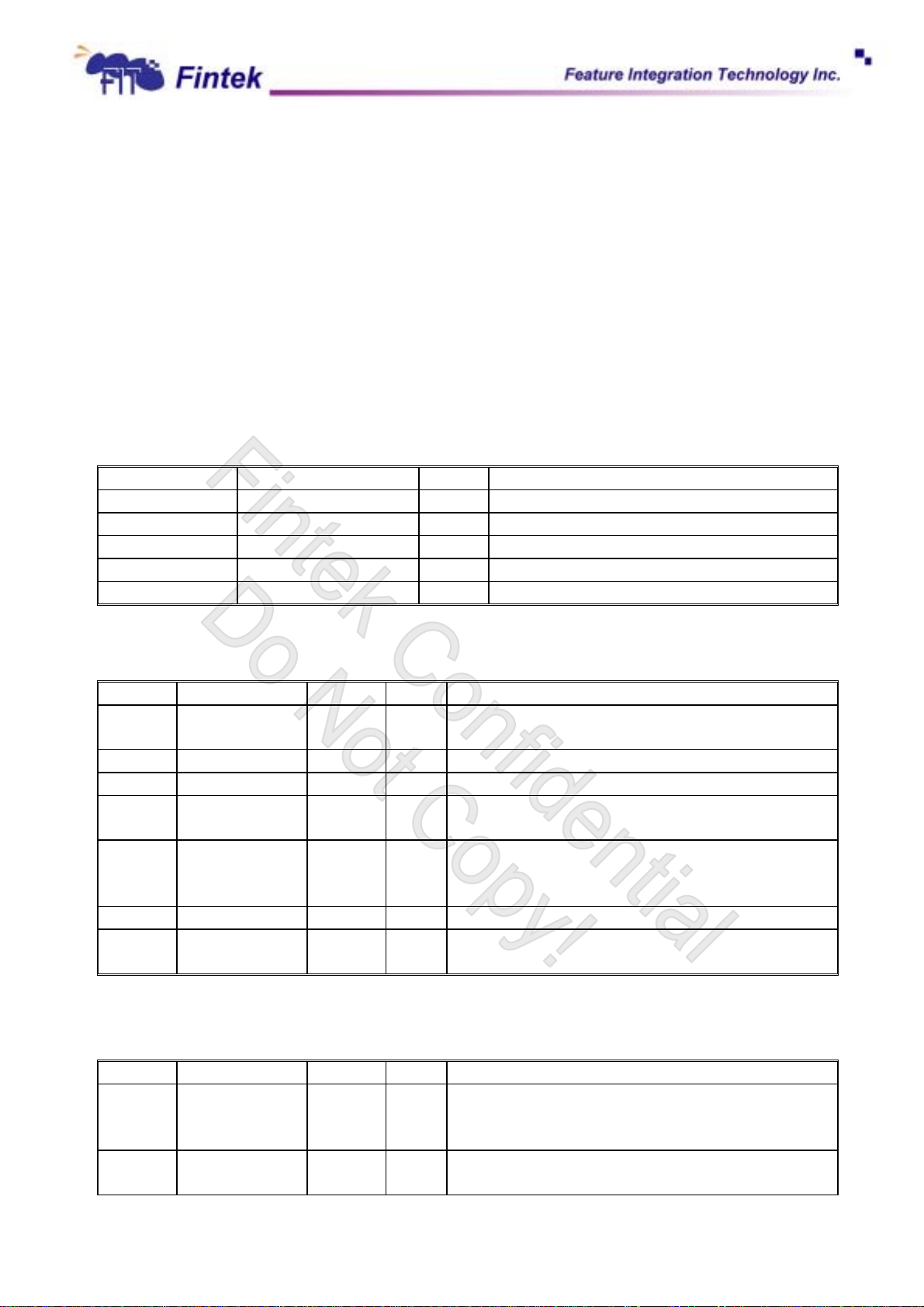

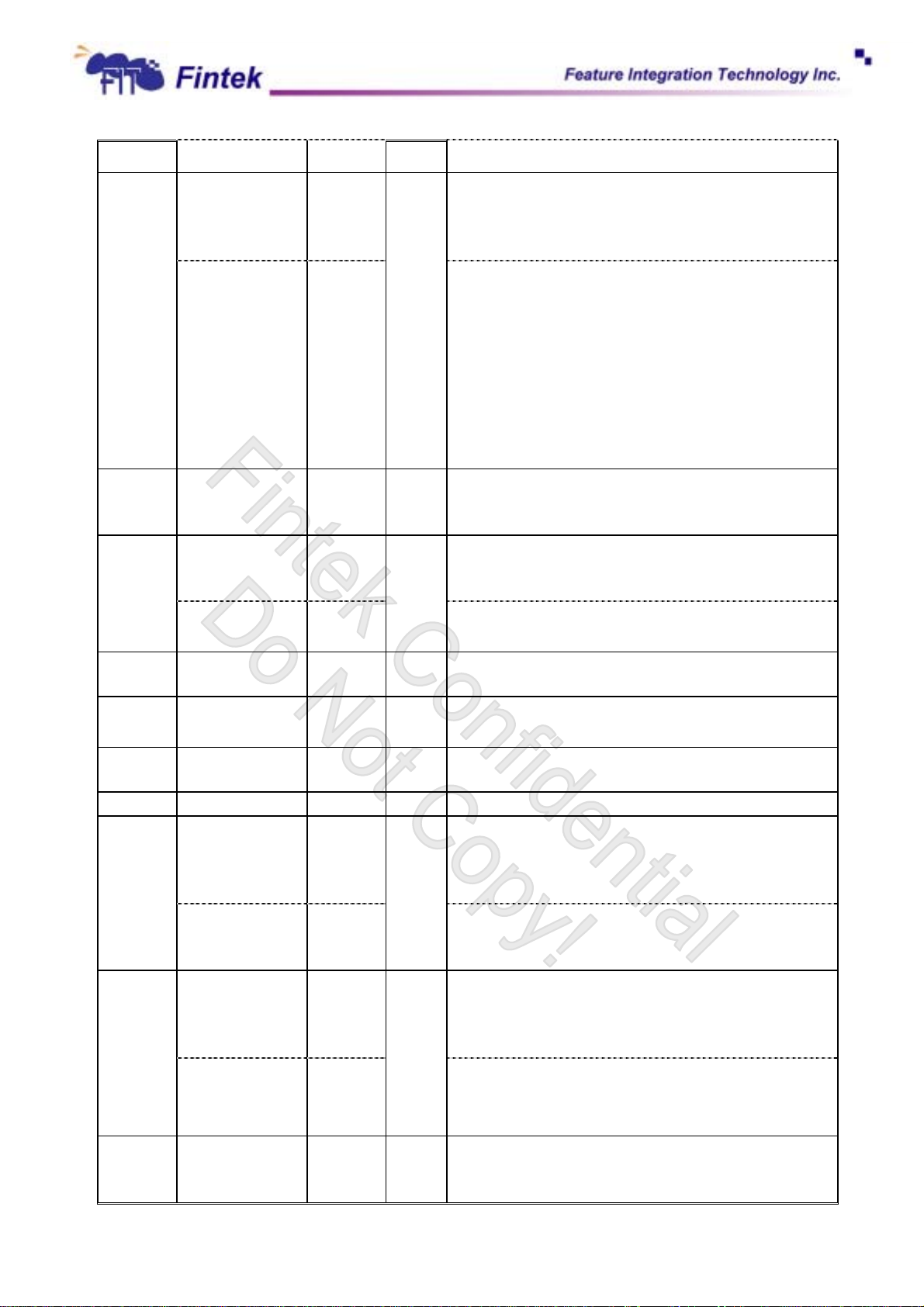

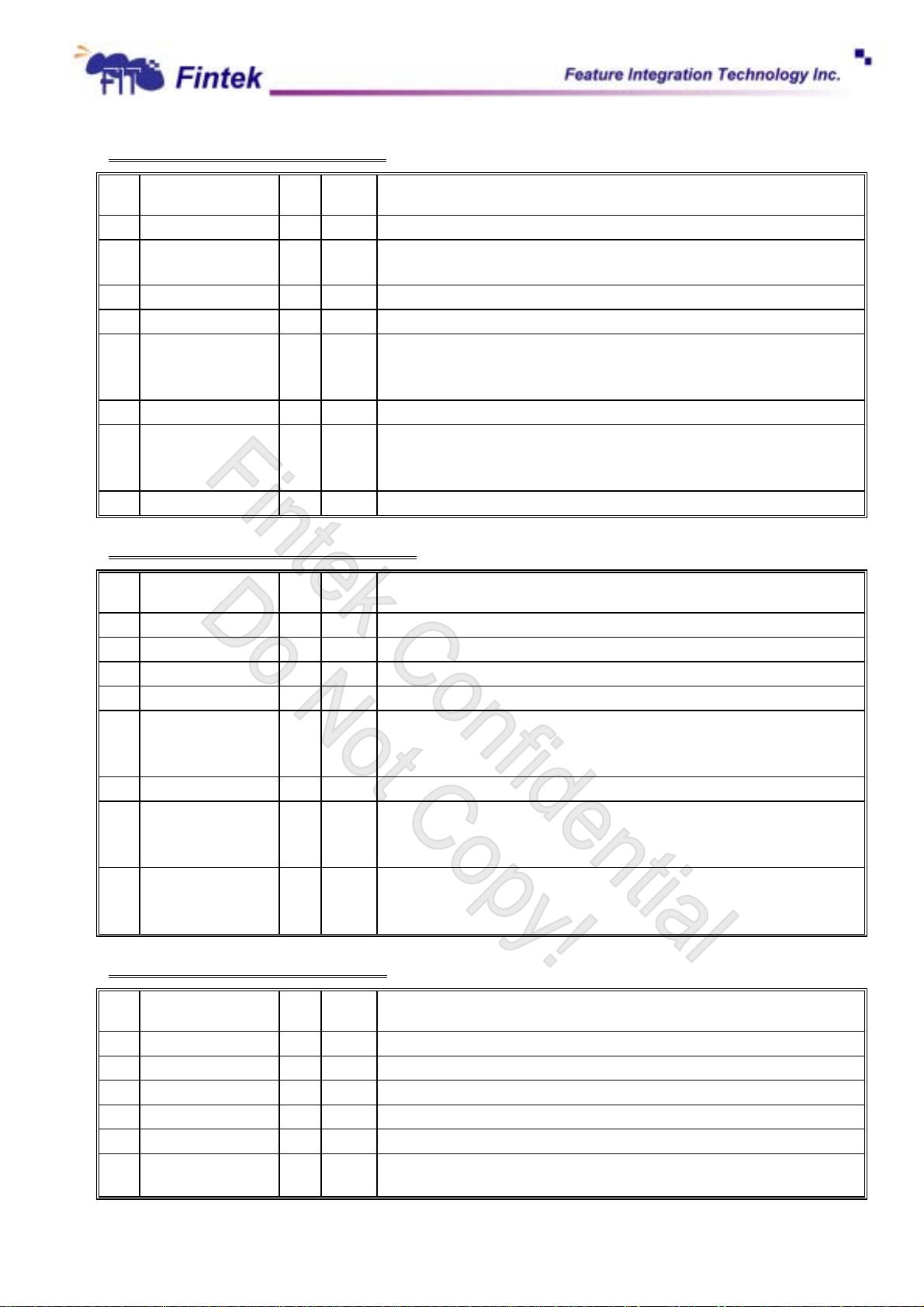

6.1 Power Pin

Pin No. Pin Name Type Description

4,37,99 VCC P Power supply voltage input with 3.3V

68 VSB P Stand-by power supply voltage input 3.3V

86 VBAT P Battery voltage input

88 AGND(D-) P Analog GND

20, 48, 73, 117 GND P Digital GND

capability.

- Open-drain pin with 8 mA source-sink capability, pull-up 47k ohms, 5V tolerance.

- Output pin with 8 mA source-sink capability.

- Output pin with 12 mA source-sink capability.

- Output pin with 30 mA source-sink capability.

- Open-drain output pin with 12 mA sink capability.

- Open-drain output pin with 12 mA sink capability, 5V tolerance.

- Open-drain output pin with 24 mA sink capability.

- TTL level input pin,5V tolerance.

- TTL level input pin and schmitt trigger.

6.2 LPC Interface

Pin No. Pin Name Type PWR Description

29 LRESET# IN

30 LDRQ# O12 VCC Encoded DMA Request signal.

31 SERIRQ I/O

32 LFRAM# INts VCC Indicates start of a new cycle or termination of a

36-33 LAD[3:0] I/O

38 PCICLK INts VCC 33MHz PCI clock input.

39 CLKIN INts VCC System clock input. According to the input frequency

VCC Reset signal. It can connect to PCIRST# signal on the

ts5v

host.

VCC Serial IRQ input/Output.

12t

broken cycle.

VCC These signal lines communicate address, control, and

12t

data information over the LPC bus between a host and

a peripheral.

24/48MHz.

6.3 FDC

Pin No. Pin Name Type PWR Description

7

8

DENSEL#

OD24 VCC Motor A On. When set to 0, this pin enables disk drive

MOA#

OD24 VCC Drive Density Select.

Set to 1 - High data rate.(500Kbps, 1Mbps)

Set to 0 – Low data rate. (250Kbps, 300Kbps)

0. This is an open drain output.

Nov., 2006

-6-

V0.24P

e

l

o

e

F71882

9 DRVA# OD24 VCC Drive Select A. When set to 0, this pin enables disk

drive A. This is an open drain output.

10 WDATA# OD24 VCC Write data. This logic low open drain writes

pre-compensation serial data to the selected FDD. An

open drain output.

11 DIR# OD24 VCC Direction of the head step motor. An open drain output.

Logic 1 = outward motion

Logic 0 = inward motion

12 STEP# OD24 VCC Step output pulses. This active low open drain output

produces a pulse to move the head to another track.

13 HDSEL# OD24 VCC Head select. This open drain output determines which

disk drive head is active.

14 WGATE# OD24 VCC Write enable. An open drain output.

15 RDATA# IN

16 TRK0# IN

17 INDEX# IN

VCC The read data input signal from the FDD.

ts5v

VCC Track 0. This Schmitt-triggered input from the disk

ts5v

VCC This Schmitt-triggered input from the disk drive is

ts5v

18 WPT# IN

19 DSKCHG# IN

VCC Write protected. This active low Schmitt input from the

ts5v

VCC Diskette change. This signal is active low at power on

ts5v

Logic 1 = side 0

Logic 0 = side 1

drive is active low when the head is positioned over

the outermost track.

active low when the head is positioned over the

beginning of a track marked by an index hole.

disk drive indicates that the diskette is write-protected.

and whenever the diskette is removed.

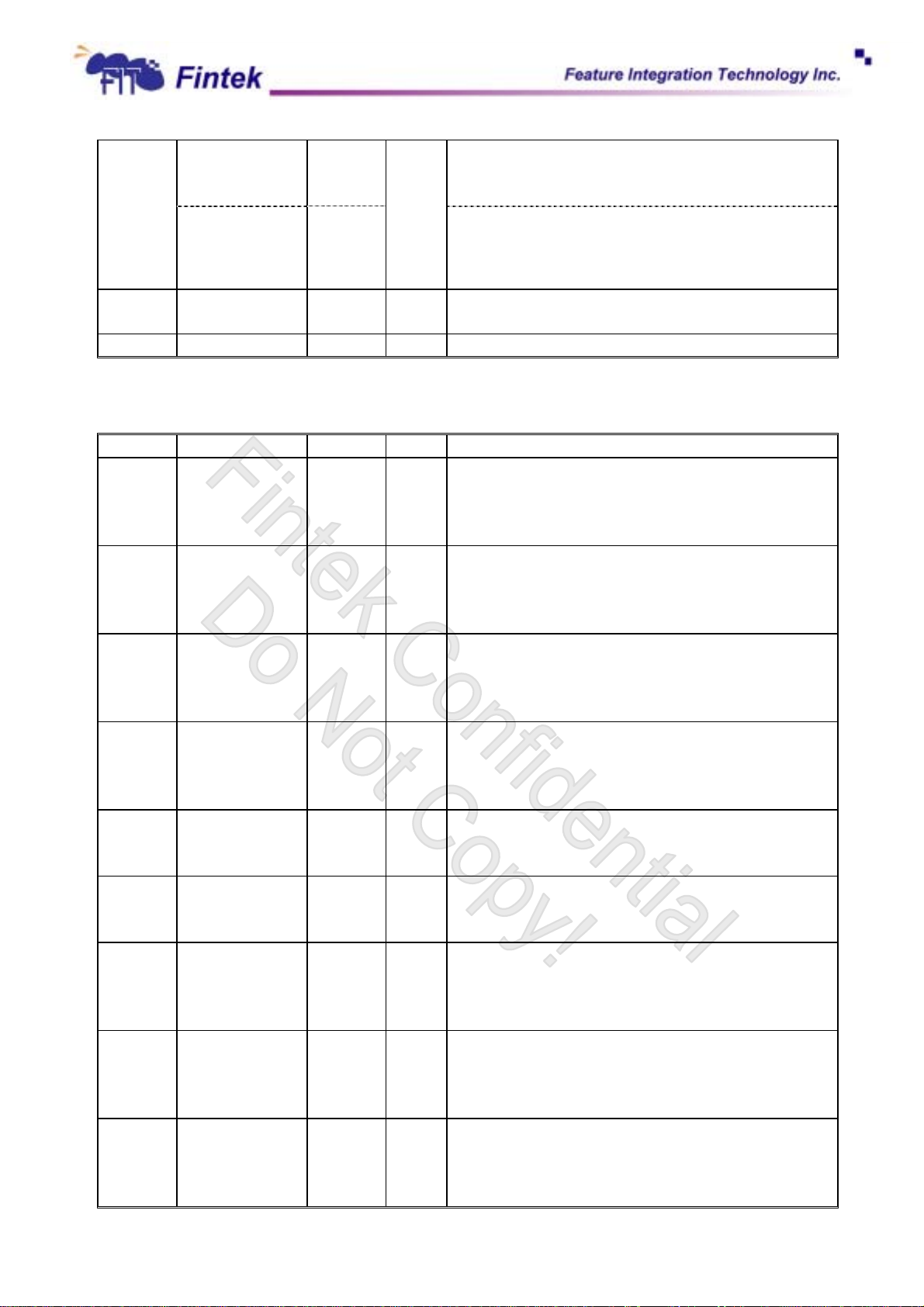

6.4 UART and SIR

Pin No. Pin Name Type PWR Description

IRTX O12 Infrared Transmitter Output. 27

GPIO42 I/OOD

IRRX INts Infrared Receiver input. 28

GPIO43 I/OOD

118 DCD1# IN

119 RI1# IN

120 CTS1# IN

121

DTR1#

O

FAN60_100 IN

VCC Data Carrier Detect. An active low signal indicates th

t5v

VCC Ring Indicator. An active low signal indicates that a ring

t5v

VCC Clear To Send is the modem control input.

t5v

8-u47,5v

t5v

VCC

12t

General Purpose IO

VSB

12t

General Purpose IO.

modem or data set has detected a data carrier.

signal is being received from the modem or data set.

VCC

UART 1 Data Terminal Ready. An active low signa

informs the modem or data set that controller is ready t

communicate. Internal 47k ohms pulled high and disabl

after power on strapping.

Power on strapping pin:

1(Default): (Internal pull high)

Power on fan speed default duty is 60%.(PWM)

0: (External pull down)

Nov., 2006

-7-

V0.24P

s

o

e

e

a

t

h

e

e

g

A

l

o

e

s

o

e

e

a

F71882

Power on fan speed default duty is 100%.(PWM)

122

RTS1#

O

VIDOUT_TRAP IN

123 DSR1# IN

124

SOUT1

Config4E_2E IN

125 SIN1 IN

126 DCD2# IN

O

VCC

UART 1 Request To Send. An active low signal inform

8-u47,5v

the modem or data set that the controller is ready t

send data. Internal 47k ohms pulled high and disabl

after power on strapping.

t5v

VCC Data Set Ready. An active low signal indicates th

t5v

Power on strapping pin:

1(Default) :

1. VIDIN[5-0]/OUT[5-0] pins will be VIDIN function.

2. VIDOUT[5-0]/GPIO0[5-0] pins will be VIDOUT function

0 :

1. VIDIN[5-0]/OUT[5-0] pins will be VIDIN[5-0]/OUT[5-0]

function.(In-Out on the same pins)

2. VIDOUT[5-0]/GPIO0[5-0] pins will be GPIO0 function.

modem or data set is ready to establish

communication link and transfer data to the UART.

VCC

UART 1 Serial Output. Used to transmit serial data ou

8-u47,5v

to the communication link. Internal 47k ohms pulled hig

and disable after power on strapping.

t5v

Power on strapping: 1(Default)Configuration register:4E

0 Configuration register:2E

VCC Serial Input. Used to receive serial data through th

t5v

communication link.

VCC Data Carrier Detect. An active low signal indicates th

t5v

modem or data set has detected a data carrier.

127 RI2#

IN

128 CTS2# IN

1

DTR2#

O

FWH_TRAP IN

2

RTS2#

O

HPWM_DC IN

3 DSR2# IN

t5v

VCC Ring Indicator. An active low signal indicates that a rin

signal is being received from the modem or data set.

VCC Clear To Send is the modem control input.

t5v

VCC

U

8-u47,5v

RT 2 Data Terminal Ready. An active low signa

informs the modem or data set that controller is ready t

communicate. Internal 47k ohms pulled high and disabl

after power on strapping.

t5v

Power on strapping :

1(Default): SPI as a backup BIOS

0 : SPI as a primary BIOS

VCC

UART 2 Request To Send. An active low signal inform

8-u47,5v

the modem or data set that the controller is ready t

send data. Internal 47k ohms pulled high and disabl

after power on strapping.

t5v

Power on strapping :

1 (Default): Fan control method will be PWM Mode

0 Drive :Fan control method will be Linear Mode

VCC Data Set Ready. An active low signal indicates th

t5v

modem or data set is ready to establish

communication link and transfer data to the UART.

Nov., 2006

-8-

V0.24P

t

d

e

F71882

5

SOUT2

O

8-u47,5v

VCC

UART 2 Serial Output. Used to transmit serial data ou

to the communication link. Internal 47k ohms pulle

high and disable after power on strapping.

IN

SPI_TRAP

t5v

Power on strapping:

1(Default) : SPI function disable

0 : SPI function enable

6 SIN2 IN

66 GPIO17 I/OOD

t5v

VCC Serial Input. Used to receive serial data through th

communication link.

VSB General Purpose IO

12t

6.5 Parallel Port

Pin No. Pin Name Type PWR Description

100 SLCT IN

101 PE IN

102 BUSY IN

103 ACK# IN

104 SLIN# OD

105 INIT#

106 ERR#

107 AFD# OD

108 STB# OD

VCC An active high input on this pin indicates that the

ts5v

printer is selected. Refer to the description of the

parallel port for definition of this pin in ECP and EPP

mode.

VCC An active high input on this pin indicates that the

ts5v

printer has detected the end of the paper. Refer to the

description of the parallel port for the definition of this

pin in ECP and EPP mode.

VCC An active high input indicates that the printer is not

ts5v

ready to receive data. Refer to the description of the

parallel port for definition of this pin in ECP and EPP

mode.

VCC An active low input on this pin indicates that the printer

ts5v

has received data and is ready to accept more data.

Refer to the description of the parallel port for the

definition of this pin in ECP and EPP mode.

VCC Output line for detection of printer selection. Refer to

12-5v

the description of the parallel port for the definition of

this pin in ECP and EPP mode.

OD

VCC Output line for the printer initialization. Refer to the

12-5v

description of the parallel port for the definition of this

pin in ECP and EPP mode.

IN

ts5v

VCC An active low input on this pin indicates that the printer

has encountered an error condition. Refer to the

description of the parallel port for the definition of this

pin in ECP and EPP mode.

VCC An active low output from this pin causes the printer to

12-5v

auto feed a line after a line is printed. Refer to the

description of the parallel port for the definition of this

pin in ECP and EPP mode.

VCC An active low output is used to latch the parallel data

12-5v

into the printer. Refer to the description of the parallel

port for the definition of this pin in ECP and EPP mode.

Nov., 2006

-9V0.24P

F71882

109

I/O

PD0

VCC Parallel port data bus bit 0. Refer to the description of

12ts5v

the parallel port for the definition of this pin in ECP and

EPP mode.

110

111

112

113

114

115

116

I/O

PD1

I/O

PD2

I/O

PD3

I/O

PD4

I/O

PD5

I/O

PD6

I/O

PD7

VCC Parallel port data bus bit 1.

12ts5v

VCC Parallel port data bus bit 2.

12ts5v

VCC Parallel port data bus bit 3.

12ts5v

VCC Parallel port data bus bit 4.

12ts5v

VCC Parallel port data bus bit 5.

12ts5v

VCC Parallel port data bus bit 6.

12ts5v

VCC Parallel port data bus bit 7.

12ts5v

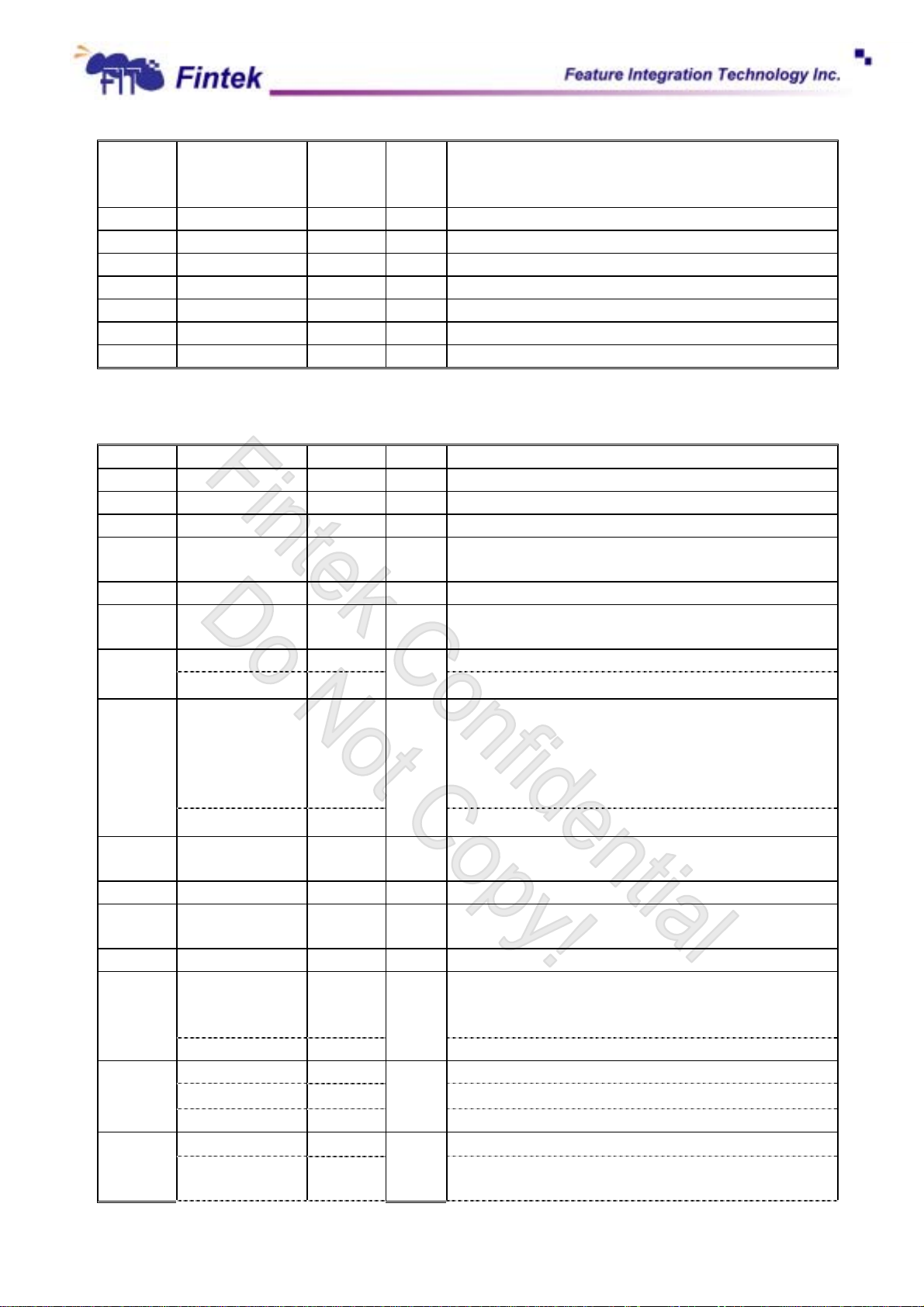

6.6 Hardware Monitor

Pin No. Pin Name Type PWR Description

93-97 VIN6~VIN2 AIN VCC Voltage Input 2 ~ 6.

98 Vcore(VIN1) AIN VCC Voltage Input for Vcore.

21 FANIN1 IN

22 FAN_CTL1 OD

23 FANIN2 IN

24 FAN_CTL2 OD

26

89 D3+(System) AIN VCC Thermal diode/transistor temperature sensor input for

90 D2+ AIN VCC Thermal diode/transistor temperature sensor input.

91 D1+(CPU) AIN VCC CPU thermal diode/transistor temperature sensor

92 VREF AOUT

79

59

ts5v

12-5v

AOUT

ts5v

12-5v

AOUT

FANIN3 IN

ts5v

GPIO40 I/OOD

FAN_CTL3*

OD

12-5V

AOUT

GPIO41 I/OOD

PME#

OD

12-5v

GPIO25 I/OOD

GPIO10 I/OOD

SPI_SLK O12 Serial clock output pin for SPI device.

FANIN4 IN

ts5v

GPIO11 I/OOD

SPI_CS0# O12

VCC Fan 1 tachometer input.

VCC Fan 1 control output. This pin provides PWM

duty-cycle output or a voltage output.

VCC Fan 2 tachometer input.

VCC Fan 2 control output. This pin provides PWM

duty-cycle output or a voltage output.

12t

VCC

VCC

Fan 3 speed input. 25

General purpose IO.

Fan 3 control output. This pin provides PWM

duty-cycle output or a voltage output.

*This pin default function is FANCTL (PWM signal

output), please take care the application if user want to

implement GPIO function.

12t

General purpose IO.

system use.

input. This pin is for CPU use.

VCC Voltage sensor output.

VSB

Generated PME event. It supports the PCI PME#

interface. This signal allows the peripheral to request

the system to wake up from the S3 state.

12t

General purpose IO.

VSB

12t

General purpose IO. 60

VSB

12t

General Purpose IO.

Fan 4 tachometer input

Function A: When using firmware hub BIOS for

primary BIOS and SPI BIOS for second BIOS, please

Nov., 2006

-10V0.24P

F71882

connect this pin to SPI BIOS chip select pin.

Function B: When using two SPI Flashes for primary

and back up BIOS, please connect this pin to primary

BIOS chip select pin.

FANCTL4 OD

AOUT

61

GPIO12 I/OOD

SPI_MISO IN

FANCTL1_1 OD

62

GPIO13 I/OOD

SPI_MOSI O12

BEEP OD24

63

GPIO14 I/OOD

FWH_DIS O12 Firmware hub disable

WDTRST# OD

SPI_CS1# O

67 OVT# OD

12-5v

General purpose IO.

VSB

12t

t5v

12-5v

General purpose IO.

VSB

12t

General purpose IO.

VSB

12t

Watch dog timer signal output.

12-5v

12

VSB Over temperature signal output.

12-5v

Fan 4 control output. This pin provides PWM

duty-cycle output or a voltage output.

SPI master in/slave out pin.

Fan 1 control output. This pin provides PWM

duty-cycle open drain output for Intel 4-pin Fan.

SPI master out/slave in pin.

Beep pin.

When using two SPI Flashes for primary and back up

BIOS, please connect this pin to back up BIOS chip

select pin.

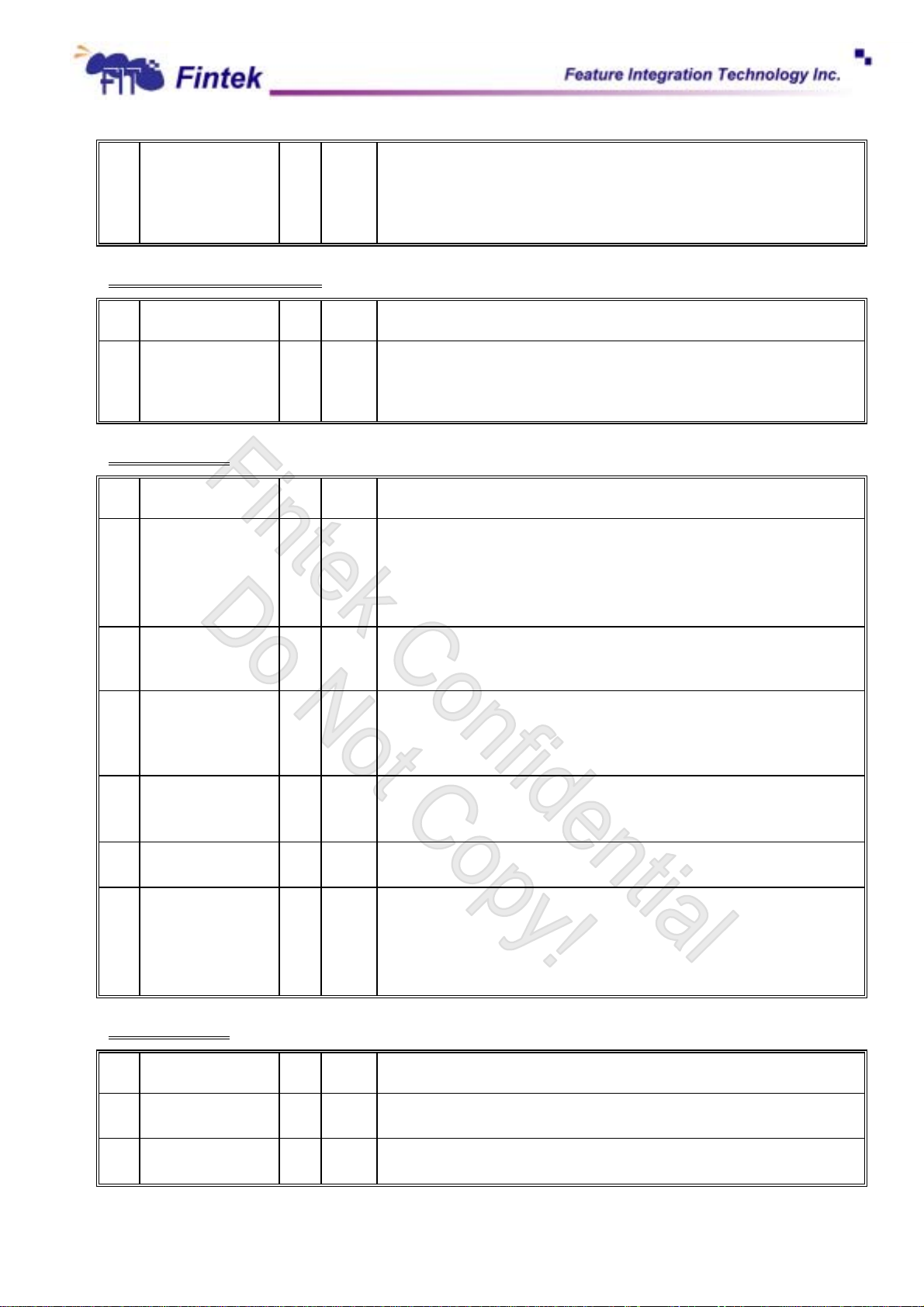

6.7 ACPI Function Pins

Pin No. Pin Name Type PWR Description

64

GPIO15 I/OOD

LED_VSB OD12 Power LED for VSB.

ALERT# OD

65

GPIO16 I/OOD

LED_VCC OD12 Power LED for VCC.

Turbo2# IN

PCIRST1# OD12 It is a output buffer of RSTCON# and LRESET#. 74

GPIO20 I/OOD

PCIRST2# O12 It is a output buffer of RSTCON# and LRESET#. 75

GPIO21 I/OOD

PCIRST3# O12 It is a output buffer of RSTCON# and LRESET#. 76

GPIO22 I/OOD

GPIO23 I/OOD12 General purpose IO. (Default) 77

RSTCON#

OD

ATXPG_IN AIN ATX Power Good input. 78

GPIO24 I/OOD

84 PWROK OD12 VSB PWROK function, It is power good signal of VCC,

General purpose IO.

VSB

12t

12

General purpose IO.

VSB

12t

ts5v

Alert a signal when temperature over limit setting.

VID Turbo 2 enable control pin. (Patent Issue)

VSB

12

General purpose IO.

VSB

12

General purpose IO.

VSB

12

General purpose IO.

VSB

12

RESET Connect# with 50ms debouce function, it

connects to reset button, and also other reset source

on the motherboard.

VSB

12t

General purpose IO.

which is delayed 400ms (default) as VCC arrives at

Nov., 2006

-11V0.24P

F71882

2.8V.

GPIO32 I/OOD

PWSIN# IN

GPIO26 I/OOD

81

PWSOUT#

OD12 Panel Switch Output. This pin is low active and pulse

GPIO27 I/OOD

S3# IN

GPIO30 I/OOD

83

PSON#

OD

GPIO31 I/OOD

85

RSMRST#

OD12 Resume Reset# function, It is power good signal of

GPIO33 I/OOD

87 COPEN# IN

General purpose IO.

12t

VSB Main power switch button input. 80

ts5v

General purpose IO.

12t

VSB

output. It is power on request output#.

12t

ts5v

12-5v

VSB

12t

VSB Power supply on-off control output. Connect to ATX

General purpose IO.

S3# Input is Main power on-off switch input. 82

General purpose IO.

power supply PS_ON# signal.

General purpose IO.

12t

VBAT

VSB, which is delayed 66ms as VSB arrives at 2.3V.

12t

VBAT Case Open Detection #. This pin is connected to a

ts5v

General purpose IO.

specially designed low power CMOS flip-flop backed

by the battery for case open state preservation during

power loss.

6.8 VID Controller

Pin No. Pin Name Type PWR Description

46-42

VIDIN[4:0]

OUT[4:0] O

IN

12

ts5v

VCC

CPU VID input pins.

Special level input VIHÆ 0.9, VIL Æ 0.6

CPU VID output pins.

(These is for VID in-out function at the same pin)

(Power On Trapping by pin 122)

47

VIDIN5

IN

ts5v

VCC

CPU VID input pins.

Special level input VIHÆ 0.9, VIL Æ 0.6

OUT5 O12 CPU VID output pins.

(These is for VID in-out function at the same pin)

(Power On Trapping by pin 122)

54

56

SID I

VIDOUT[4:0] OD12 CPU VID output pins. 53-49

GPIO[4:0] I/OOD

VIDOUT5 OD12 CPU VID output pins.

GPIO5 I/OOD

SIC OD

SLOTOCC# IN

GPIO06 I/OOD

GPIO07 I/OOD

Turbo1# IN

WDTRST# OD

VSI AIN Easy voltage sensor input for Vcore change use. 57

SST I

/OD12

Lv

AMDSI interface data input.

VSB

12t

General purpose pin. (Power On Trapping by pin 122)

VSB

General purpose pin. (Power On Trapping by pin 122)

12t

12

ts5v

ts5v

12-5v

VSB

12t

General purpose pin.

VSB

12t

VID Turbo 1 enable control pin. (Patent Issue)

AMDSI interface clock output.

CPU SLOTOCC# input. 55

General purpose pin.

Watch dog timer signal output.

VSB

Lv/OD8-S1

Intel SST hardware monitor interface.

58 VSO AOUT VSB Easy voltage sensor output for Vcore change use.

Nov., 2006

-12V0.24P

F71882

PECI ILv/O

Intel PECI hardware monitor interface.

D8-S1

6.9 KBC Function

Pin No. Pin Name Type PWR Description

40 KBRST#

41 GA20

69 KDATA I/OD

70 KCLK I/OD

71 MDAT I/OD

72 MCLK I/OD

D

16-u10,5V

D

16-u10,5V

VCC Keyboard reset. This pin is high after system reset.

Internal pull high 3.3V with 10k ohms. (KBC P20)

VCC Gate A20 output. This pin is high after system reset.

Internal pull high 3.3V with 10k ohms. (KBC P21)

VSB Keyboard Data.

16t,5V

VSB Keyboard Clock.

16t,5V

VSB PS2 Mouse Data.

16t,5V

VSB PS2 Mouse Clock.

16t,5V

Nov., 2006

-13V0.24P

F71882

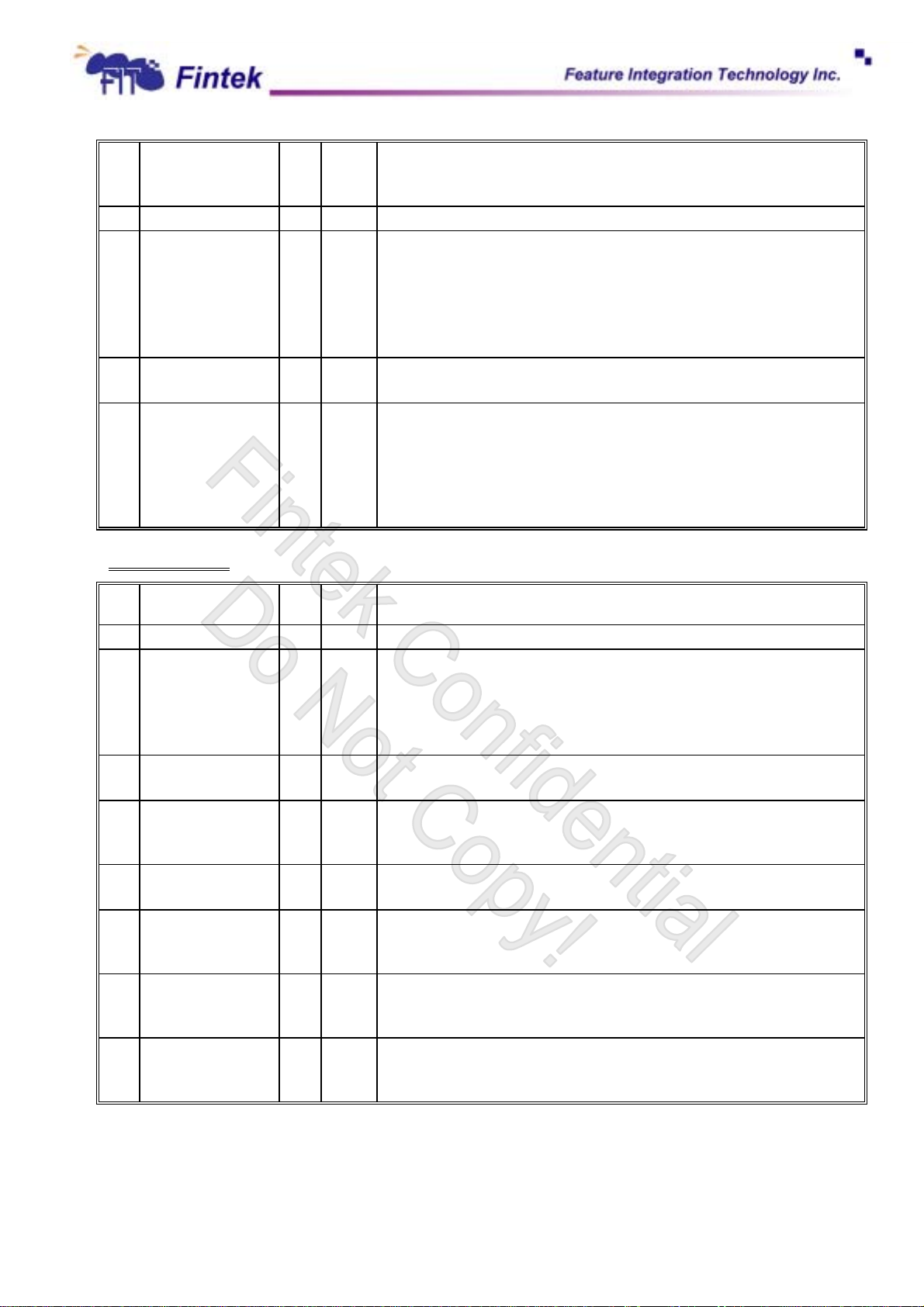

7. Function Description

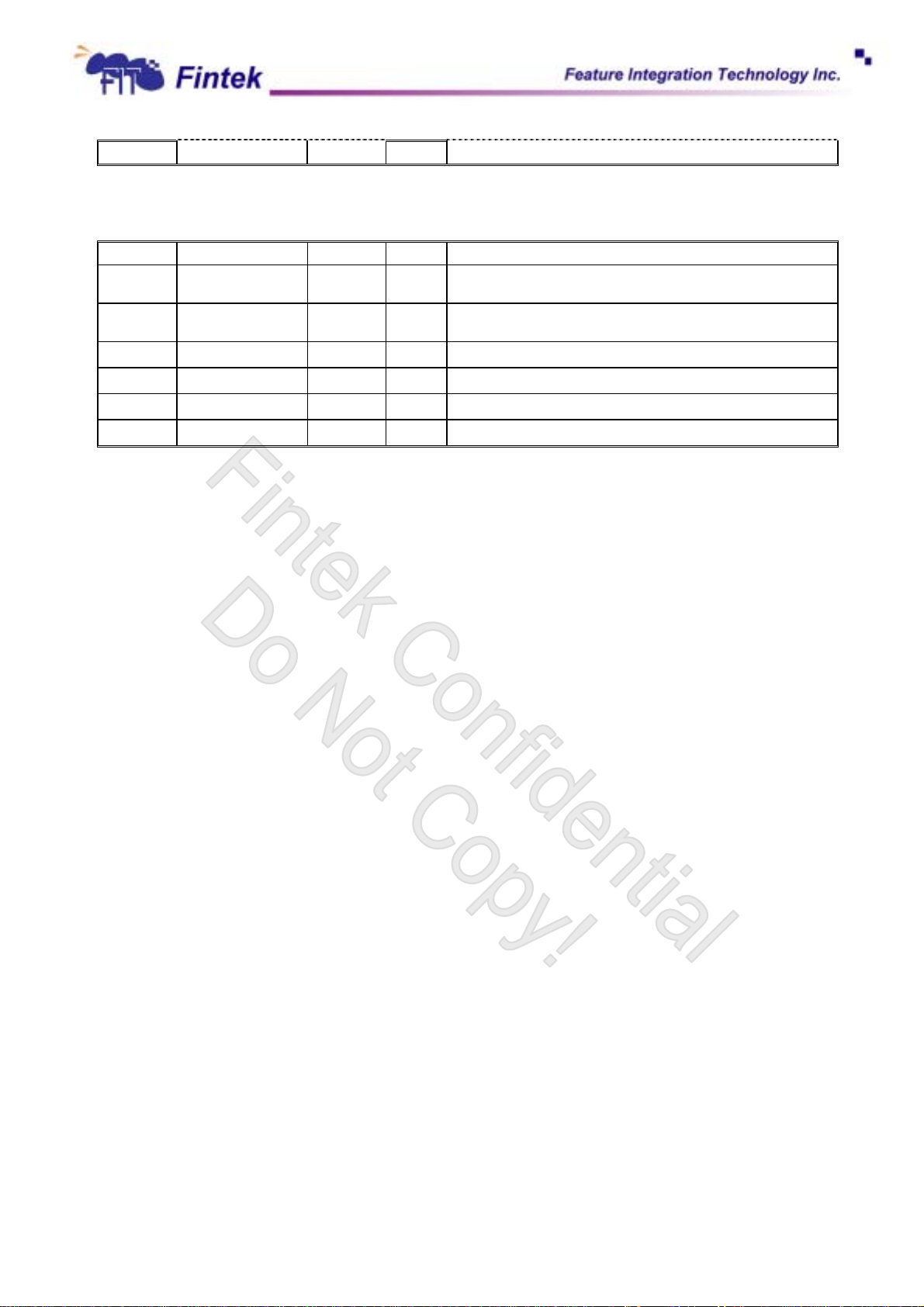

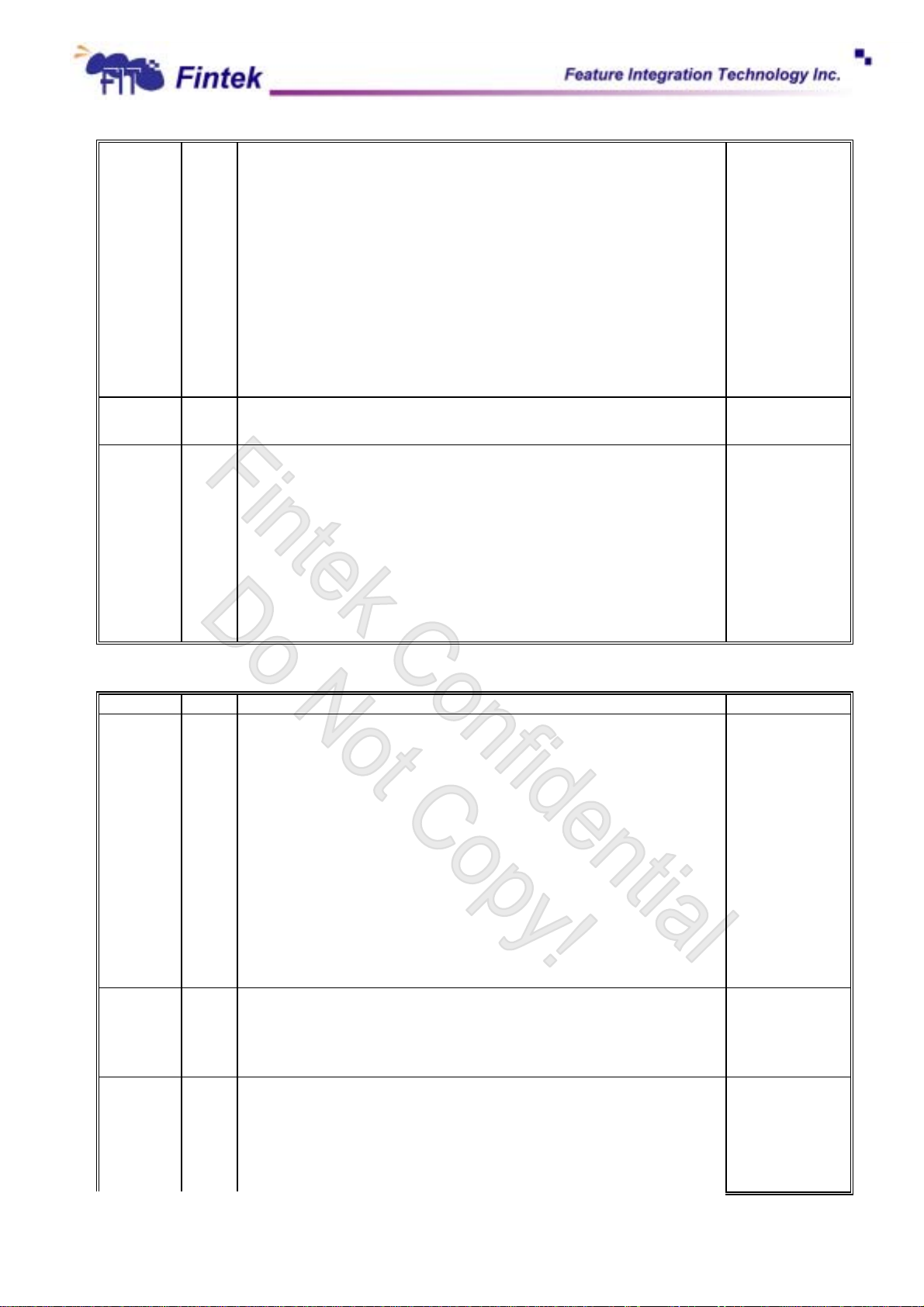

7.1 Power on Strapping Option

The F71882 provides four pins for power on hardware strapping to select functions. There is

a form to describe how to set the functions you want.

Pin No. Symbol Value Description

1 SPI as a backup BIOS (Default) 1 FWH_TRAP

0 SPI as a primary BIOS

1 Fan control mode: PWM mode. ( Default) 2 HPWM_DC

0 Fan control mode: Linear mode.

1 SPI function disable (Default) 5 SPI_TRAP

0 SPI function enable

1 Power on Fan speed default duty is 60%(PWM)(Default) 121 FAN60_100

0 Power on Fan speed default duty is 100%(PWM)

1 6 pins VIDIN and 6 pins VIDOUT (Default) 122 VIDOUT

0 VIDIN/OUT on 6 pins , Original VIDOUT pins will be GPIO

pins.

1 Configuration Register I/O port is 4E/4F. (Default) 124 Config4E_2E

0 Configuration Register I/O port is 2E/2F.

7.2 FDC

The Floppy Disk Controller provides the interface between a host processor and one

floppy disk drives. It integrates a controller and a digital data separator with write

pre-compensation, data rate selection logic, microprocessor interface, and a set of registers.

The FDC supports data transfer rates of 250 Kbps, 300 Kbps, 500 Kbps, and 1 Mbps. It

operates in PC/AT mode and supports 3-mode type drives.

The FDC configuration is handled by software and a set of Configuration registers.

Status, Data, and Control registers facilitate the interface between the host microprocessor

and the disk drive, providing information about the condition and/or state of the FDC. These

configuration registers can select the data rate, enable interrupts, drives, and DMA modes,

and indicate errors in the data or operation of the FDC/FDD. The controller manages data

transfers using a set of data transfer and control commands. These commands are handled in

three phases: Command, Execution, and Result. Not all commands utilize all these three

phases.

The below content is about the FDC device register descriptions. All the registers are for

software porting reference.

Nov., 2006

-14V0.24P

F71882

Status Register A (PS/2 mode) Base + 0

Bit Name R/W Default Description

7 INTPEND R 0 This bit indicates the state of the interrupt output.

6 DRV2_N R - 0: a second drive has been installed.

1: a second drive has not been installed.

5 STEP R 0 This bit indicates the complement of STEP# disk interface output.

4 TRK0_N R - This bit indicates the state of TRK0# disk interface input.

3 HDSEL R 0 This bit indicates the complement of HDSEL# disk interface output.

0: side 0.

1: side 1.

2 INDEX_N R - This bit indicates the state of INDEX# disk interface input.

1 WPT_N R - This bit indicates the state of WPT# disk interface input.

0 DIR R 0 This bit indicates the complement of DIR# disk interface output.

Status Register A (Model 30 mode) Base + 0

Bit Name R/W Default Description

0: disk is write-protected.

1: disk is not write-protected.

7 INTPEND R 0 This bit indicates the state of the interrupt output.

6 DRQ R 0 This bit indicates the state of the DRQ signal.

5 STEP_FF R 0 This bit indicates the complement of latched STEP# disk interface output.

4 TRK0 R - This bit indicates the complement of TRK0# disk interface input.

3 HDSEL_N R 1 This bit indicates the state of HDSEL# disk interface output.

0: side 0.

1: side 1.

2 INDEX R - This bit indicates the complement of INDEX# disk interface input.

1 WPT R - This bit indicates the complement of WPT# disk interface input.

0: disk is write-protected.

1: disk is not write-protected.

0 DIR_N R 1 This bit indicates the state of DIR# disk interface output.

0: head moves in inward direction.

1: head moves in outward direction.

Status Register B (PS/2 Mode) Base + 1

Bit Name R/W Default Description

7-6 Reserved R 11 Reserved. Return 11b when read.

5 DR0 R 0 Drive select 0. This bit reflects the bit 0 of Digital Output Register.

4 WDATA R 0 This bit changes state at every rising edge of WDATA#.

3 RDATA R 0 This bit changes state at every rising edge of RDATA#.

2 WGATE R 0 This bit indicates the complement of WGATE# disk interface output.

1 MOTEN1 R 0 This bit indicates the complement of MOB# disk interface output. Not support

in this design.

Nov., 2006

-15V0.24P

F71882

0 MOTEN0 R 0 This bit indicates the complement of MOA# disk interface output.

Status Register B (Model 30 Mode) Base + 1

Bit Name R/W Default Description

7 DRV2_N R - 0: a second drive has been installed.

1: a second drive has not been installed.

6 DSB_N R 1 This bit indicates the state of DRVB# disk interface output. Not support in this

design.

5 DSA_N R 1 This bit indicates the state of DRVA# disk interface output.

4 WDATA_FF R 0 This bit is latched at the rising edge of WDATA# and is cleared by a read from

the Digital Input Register.

3 RDATA_FF R 0 This bit is latched at the rising edge of RDATA# and is cleared by a read form

2 WGATE_FF R 0 This bit is latched at the falling edge of WGATE# and is cleared by a read from

1 DSD_N R 1 This bit indicates the complement of DRVD# disk interface output. Not support

0 DSC_N R 1 This bit indicates the complement of DRVC# disk interface output. Not support

the Digital Input Register.

the Digital Input Register.

in this design.

in this design.

Digital Output Register Base + 2

Bit Name R/W Default Description

7 MOTEN3 R 0 Motor enable 3. Not support in this design.

6 MOTEN2 R 0 Motor enable 2. Not support in this design.

5 MOTEN1 R/W 0 Motor enable 1. Used to control MOB#. MOB# is not support in this design.

4 MOTEN0 R/W 0 Motor enable 0. Used to control MOA#.

3 DAMEN R/W 0 DMA enable. This bit has two mode of operation.

PC-AT and Model 30 mode: write 1 will enable DMA and IRQ, write 0 will

disable DMA and IRQ.

PS/2 mode: This bit is reserved. DMA and IRQ are always enabled in PS/2

mode.

2 RESET R 0 Write 0 to this bit will reset the controller. I will remain in reset condition until a 1

is written.

1 DSD_N R 1 This bit indicates the complement of DRVD# disk interface output. Not support

in this design.

0 DSC_N R 1 This bit indicates the complement of DRVC# disk interface output. Not support

in this design.

Tape Drive Register Base + 3

Bit Name R/W Default Description

7-6 Reserved R 00 Reserved. Return 00b when read.

5-4 TYPEID R 11 Reserved in normal function, return 11b when read.

If 3 mode FDD function is enabled. These bits indicate the drive type ID.

Nov., 2006

-16V0.24P

F71882

3-2 Reserved R 11 Reserved. Return 11b when read in normal function.

Return 00b when read in 3 mode FDD function.

1-0 TAPESEL R/W 0 These bits assign a logical drive number to be a tape drive.

Main Status Register Base + 4

Bit Name R/W Default Description

7 RQM R 0 Request for Master indicates that the controller is ready to send or receive data

from the uP through the FIFO.

6 DIO R 0 Data I/O (direction):

0: the controller is expecting a byte to be written to the Data Register.

1: the controller is expecting a byte to be read from the Data Register.

5 NON_DMA R 0 Non DMA Mode:

4 FDC_BUSY R 0 This bit indicate that a read or write command is in process.

3 DRV3_BUSY R 0 FDD number 3 is in seek or calibration condition. FDD number 3 is not support

2 DRV2_BUSY R 0 FDD number 2 is in seek or calibration condition. FDD number 2 is not support

1 DRV1_BUSY R 0 FDD number 1 is in seek or calibration condition. FDD number 1 is not support

0 DRV0_BUSY R 0 FDD number 0 is in seek or calibration condition.

0: the controller is in DAM mode.

1: the controller is interrupt or software polling mode.

in this design.

in this design.

in this design.

Data Rate Select Register Base + 4

Bit Name R/W Default Description

7 SOFTRST W 0 A 1 written to this bit will software reset the controller. Auto clear after reset.

6 PWRDOWN W 0 A 1 to this bit will put the controller into low power mode which will turn off the

5 Reserved - - Return 0 when read.

4-2 PRECOMP W 000 Select the value of write precompensation:

oscillator and data separator circuits.

250K-1Mbps 2Mbps

000: default delays default delays

001: 41.67ns 20.8ns

010: 83.34ns 41.17ns

011: 125.00ns 62.5ns

100: 166.67ns 83.3ns

101: 208.33ns 104.2ns

110: 250.00ns 125.00ns

111: 0.00ns (disabled) 0.00ns (disabled)

The default value of corresponding data rate:

250Kbps: 125ns

300Kbps: 125ns

500Kbps: 125ns

1Mbps: 41.67ns

2Mbps: 20.8ns

Nov., 2006

-17V0.24P

F71882

1-0 DRATE W 10 Data rate select:

MFM FM

00: 500Kbps 250Kbps

01: 300Kbps 150Kbps

10: 250Kbps 125Kbps

11: 1Mbps illegal

Data (FIFO) Register Base + 5

Bit Name R/W Default Description

7-0 DATA R/W 00h The FIFO is used to transfer all commands, data and status between controller

and the system. The Data Register consists of four status registers in a stack

with only one register presented to the data bus at a time. The FIFO is default

Status Registers 0

disabled and could be enabled via the CONFIGURE command.

Bit Name R/W Default Description

7-6 IC R - Interrupt code :

5 SE R - Seek end.

4 EC R - Equipment check.

3 NR R - Not ready.

2 HD R - Head address.

1-0 DS R - Drive select.

00: Normal termination of command.

01: Abnormal termination of command.

10: Invalid command.

11: Abnormal termination caused by poling.

Set when a SEEK or RECALIBRATE or a READ or WRITE with implied seek

command is completed.

0: No error

1: When a fault signal is received form the FDD or the TRK0# signal fails to

occur after 77 step pulses.

0: Drive is ready

1: Drive is not ready.

The current head address.

00: Drive A selected.

01: Drive B selected.

10: Drive C selected.

11: Drive D selected.

Status Registers 1

Bit Name R/W Default Description

7 EN R - End of Track.

Set when the FDC tries to access a sector beyond the final sector of a cylinder.

6 DE R - Data Error.

The FDC detect a CRC error in either the ID field or the data field of a sector.

Nov., 2006

-18V0.24P

F71882

4 OR R - Overrun/Underrun.

Set when the FDC is not serviced by the host system within a certain time

interval during data transfer.

3 Reserved - - Unused. This bit is always “0”

2 ND R - No Data.

Set when the following conditions occurred:

1. The specified sector is not found during any read command.

2. The ID field cannot be read without errors during a READ ID command.

3. The proper sector sequence cannot be found during a READ TRACK

command.

1 NW R - No Writable

Set when WPT# is active during execution of write commands.

0 MA R - Missing Address Mark.

Set when the following conditions occurred:

1. Cannot detect an ID address mark at the specified track after

encountering the index pulse form the INDEX# pin twice.

2. Cannot detect a data address mark or a deleted data address mark on the

specified track.

Status Registers 2

Bit Name R/W Default Description

7 Reserved - - Unused. This bit is always “0”.

6 CM R - Control Mark.

5 DD R - Data Error in Data Field.

4 WC R - Wrong Cylinder.

3 SE R - Scan Equal.

2 SN R - Scan Not Satisfied.

1 BC R - Bad Cylinder.

0 MD R - Missing Data Address Mark.

Set when following conditions occurred:

1. Encounters a deleted data address mark during a READ DATA command.

2. Encounters a data address mark during a READ DELETED DATA

command.

The FDC detects a CRC error in the data field.

Set when the track address from the sector ID field is different from the track

address maintained inside the FDC.

Set if the equal condition is satisfied during execution of the SCAN command.

Set when the FDC cannot find a sector on the track which meets the desired

condition during any scan command.

The track address from the sector ID field is different from the track address

maintained inside the FDC and is equal to FFh which indicates a bad track.

Set when the FDC cannot detect a data address mark or a deleted data

address mark.

Nov., 2006

-19V0.24P

F71882

Status Registers 3

Bit Name R/W Default Description

7 Reserved - - Unused. This bit is always “0”.

6 WP R - Write Protect.

5 Reserved R - Unused. This bit is always “1”.

4 T0 R - Track 0.

3 Reserved. R - Unused. This bit is always “1”.

2 HD R - Head Address.

1 DS1 R -

0 DS0 R -

Digital Input Register (PC-AT Mode) Base + 7

Indicates the status of WPT# pin.

Indicates the status of the TRK0# pin.

Indicates the status of the HDSEL# pin.

Drive Select.

These two bits indicate the DS1, DS0 bits in the command phase.

Bit Name R/W Default Description

7 DSKCHG R - This bit indicates the complement of DSKCHG# disk interface input.

6-0 Reserved R - Reserved.

Digital Input Register (PS/2 Mode) Base + 7

Bit Name R/W Default Description

7 DSKCHG R - This bit indicates the complement of DSKCHG# disk interface input.

6-3 Reserved - - Reserved.

2-1 DRATE R 10 These bits indicate the status of the DRATE programmed through the Data

Rate Select Register or Configuration Control Register.

0 HIGHDEN_N R 1 0: 1Mbps or 500Kbps data rate is chosen.

1: 300Kbps or 250Kbps data rate is chosen.

Digital Input Register (Model 30 Mode) Base + 7

Bit Name R/W Default Description

7 DSKCHG_N R - This bit indicates the state of DSKCHG# disk interface input.

6-4 Reserved - - Reserved.

3 DMAEN R 0 This bit reflects the DMA bit in Digital Output Register.

2 NOPRE R 0 This bit reflects the NOPRE bit in Configuration Control Register.

1-0 DRATE R 10 These bits indicate the status of DRATE programmed through the Data Rate

Select Register or Configuration Control Register.

Nov., 2006

-20V0.24P

F71882

Configuration Control Register (PC-AT and PS/2 Mode) Base + 7

Bit Name R/W Default Description

7-2 Reserved - - Reserved.

1-0 DRATE W 10 These bit determine the data rate of the floppy controller. See DRATE bits in

Data Rate Select Register.

Configuration Control Register (Model 30 Mode) Base + 7

Bit Name R/W Default Description

7-3 Reserved - - Reserved.

2 NOPRE W 0 This bit could be programmed through Configuration Control Register and be

1-0 DRATE W 10 These bit determine the data rate of the floppy controller. See DRATE bits in

read through the bit 2 in Digital Input Register in Model 30 Mode. But it has no

functionality.

Data Rate Select Register.

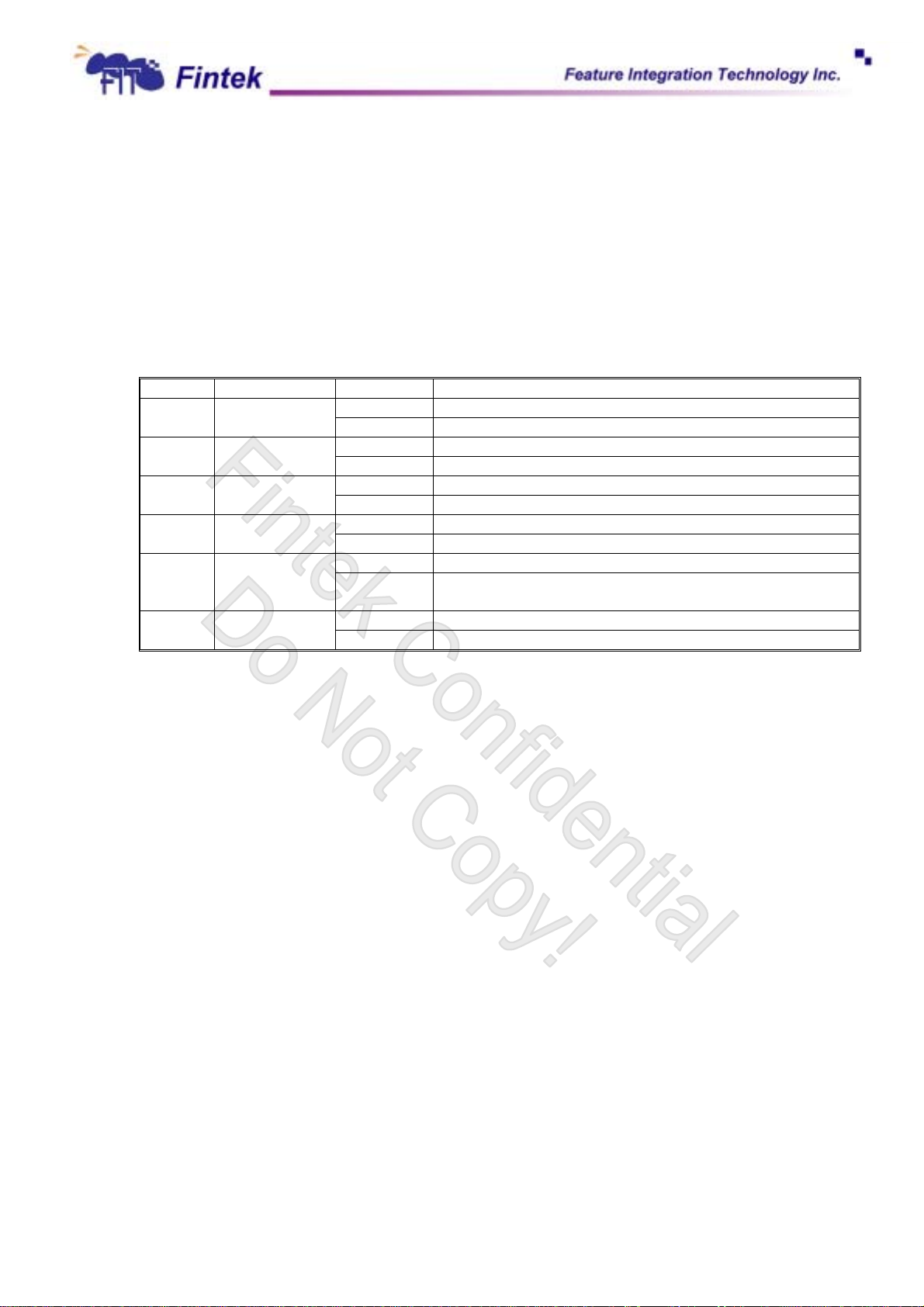

FDC Commands

Terminology:

C Cylinder Number 0 -256

D Data Pattern

DIR Step Direction

0: step out

1: step in

DS0 Drive Select 0

DS1 Drive Select 1

DTL Data Length

EC Enable Count

EOT End of Track

EFIFO Enable FIFO

0: FIFO is enabled.

1: FIFO is disabled.

EIS Enable Implied Seek

FIFOTHR FIFO Threshold

GAP Alters Gap Length

GPL Gap Length

H/HDS Head Address

HLT Head Load Time

HUT Head Unload Time

LOCK Lock EFIFO, FIFOTHR, PTRTRK bits.

Prevent these bits from being affected by software reset.

MFM MFM or FM mode

0: FM

1: MFM

MT Multi-Track

N Sector Size Code. All values up to 07h are allowable.

00: 128 bytes

01: 256 bytes

.. ..

07 16 Kbytes

Nov., 2006

-21V0.24P

F71882

NCN New Cylinder Number

ND Non-DMA Mode

OW Overwritten

PCN Present Cylinder Number

POLL Polling disa ble

0: polling is enabled.

1: polling is disabled.

PRETRK Precompensation Start Track Number

R Sector address

RCN Relative Cylinder Number

SC Sector per Cylinder

SK Skip deleted data address mark

SRT Step Rate Time

ST0 Status Register 0

ST1 Status Register 1

ST2 Status Register 2

ST3 Status Register 3

WGATE Write Gate alters timing of WE.

Read Data

Phase R/W D7 D6 D5 D4 D3 D2 D1 D0 Remark

Command W MT MFM SK 0 0 1 1 0 Command code

W 0 0 0 0 0 HDS DS1 DS0

W ----------------------------- C ---------------------------

W ----------------------------- H ---------------------------

W ----------------------------- R ---------------------------

Sector ID

information prior to

command

execution

Execution Data transfer

Result R ---------------------------- ST0 --------------------------

Read Deleted Data

Phase R/W D7 D6 D5 D4 D3 D2 D1 D0 Remark

Command W MT MFM SK 0 1 1 0 0 Command code

W ------------------------------ N ---------------------------

W ---------------------------- EOT --------------------------

W ---------------------------- GPL --------------------------

W ---------------------------- DTL --------------------------

R ----------------------------- ST1 --------------------------

R ---------------------------- ST2 --------------------------

R ----------------------------- C ---------------------------

R ----------------------------- H ---------------------------

R ----------------------------- R ---------------------------

R ----------------------------- N ---------------------------

between the FDD

and system

Status information

after command

execution.

Sector ID

information after

command

execution.

Nov., 2006

-22V0.24P

F71882

W 0 0 0 0 0 HDS DS1 DS0

W ----------------------------- C ---------------------------

W ----------------------------- H ---------------------------

W ----------------------------- R ---------------------------

W ------------------------------ N ---------------------------

W ---------------------------- EOT --------------------------

W ---------------------------- GPL --------------------------

W ---------------------------- DTL --------------------------

Execution Data transfer

Result R ---------------------------- ST0 --------------------------

R ----------------------------- ST1 --------------------------

R ---------------------------- ST2 --------------------------

R ----------------------------- C ---------------------------

R ----------------------------- H ---------------------------

R ----------------------------- R ---------------------------

R ----------------------------- N ---------------------------

Sector ID

information prior to

command

execution

between the FDD

and system

Status information

after command

execution.

Sector ID

information after

command

execution.

Read A Track

Phase R/W D7 D6 D5 D4 D3 D2 D1 D0 Remark

Command W 0 MFM 0 0 0 0 1 0 Command code

W 0 0 0 0 0 HDS DS1 DS0

W ----------------------------- C ---------------------------

W ----------------------------- H ---------------------------

W ----------------------------- R ---------------------------

W ------------------------------ N ---------------------------

W ---------------------------- EOT --------------------------

W ---------------------------- GPL --------------------------

W ---------------------------- DTL --------------------------

Execution Data transfer

Result R ---------------------------- ST0 --------------------------

R ----------------------------- ST1 --------------------------

R ---------------------------- ST2 --------------------------

Sector ID

information prior to

command

execution

between the FDD

and system. FDD

reads contents of

all cylinders from

index hole to EOT.

Status information

after command

execution.

R ----------------------------- C --------------------------- Sector ID

Nov., 2006

-23-

information after

V0.24P

F71882

R ----------------------------- H ---------------------------

R ----------------------------- R ---------------------------

R ----------------------------- N ---------------------------

Read ID

Phase R/W D7 D6 D5 D4 D3 D2 D1 D0 Remark

Command W 0 MFM 0 0 1 0 1 0 Command code

W 0 0 0 0 0 HDS DS1 DS0

Execution The first correct ID

Result R ---------------------------- ST0 --------------------------

R ----------------------------- ST1 --------------------------

R ---------------------------- ST2 --------------------------

command

execution.

information on the

cylinder is stored in

Data Register.

Status information

after command

execution.

R ----------------------------- C ---------------------------

R ----------------------------- H ---------------------------

R ----------------------------- R ---------------------------

R ----------------------------- N ---------------------------

Verify

Phase R/W D7 D6 D5 D4 D3 D2 D1 D0 Remark

Command W MT MFM SK 1 0 1 1 0 Command code

W EC 0 0 0 0 HDS DS1 DS0

W ----------------------------- C ---------------------------

W ----------------------------- H ---------------------------

W ----------------------------- R ---------------------------

W ------------------------------ N ---------------------------

W ---------------------------- EOT --------------------------

W ---------------------------- GPL --------------------------

W -------------------------- DTL/SC ------------------------

Execution No data transfer

Result R ---------------------------- ST0 --------------------------

R ----------------------------- ST1 --------------------------

R ---------------------------- ST2 --------------------------

Disk status after

the command has

been completed.

Sector ID

information prior to

command

execution

Status information

after command

execution.

R ----------------------------- C ---------------------------

R ----------------------------- H ---------------------------

Nov., 2006

-24-

Sector ID

information after

command

V0.24P

Loading...

Loading...