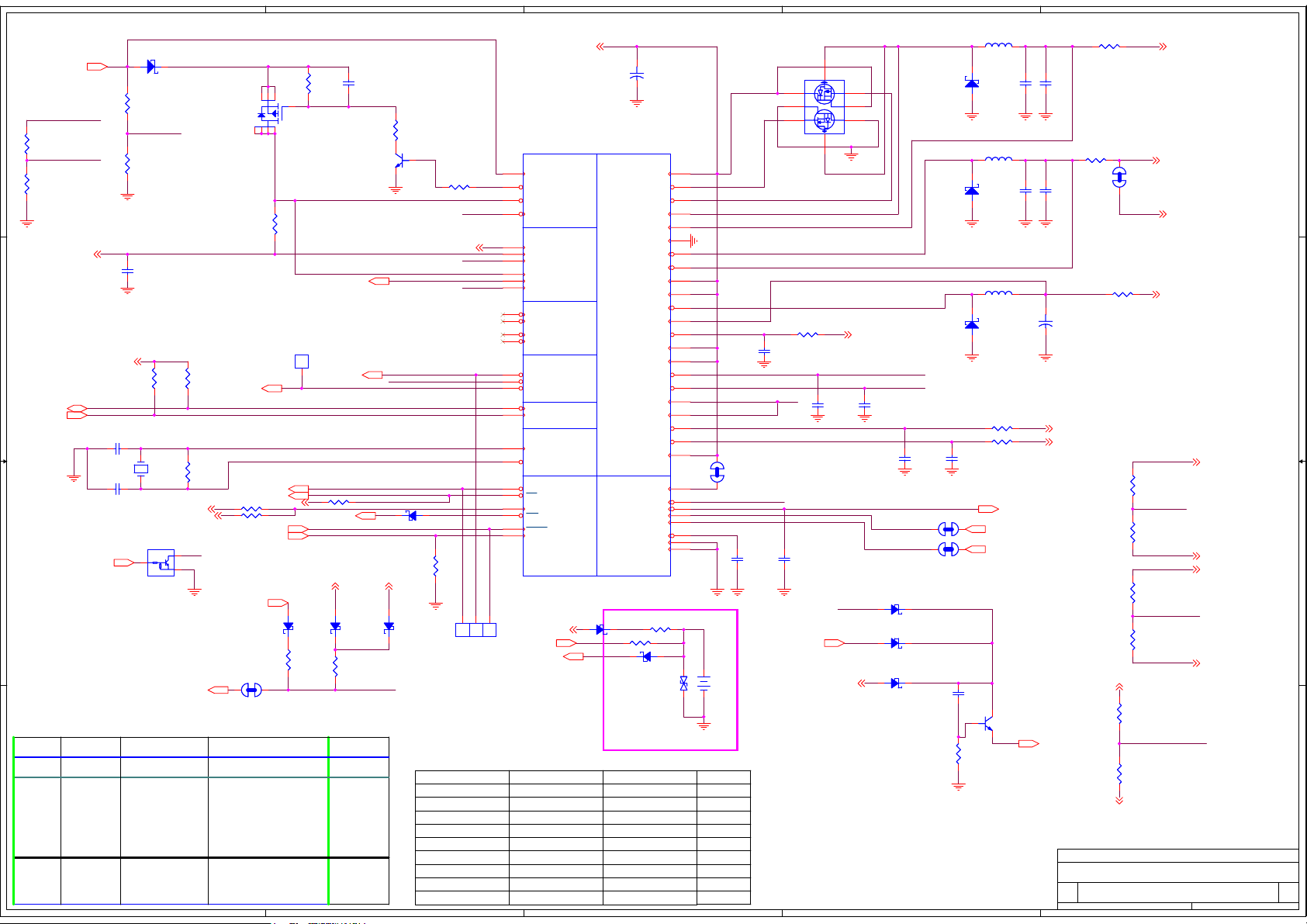

Gigabyte Einstein_MB rev.1.1 Schematics

5

TH1TH1

TH2TH2

1

1

GND GND

TH6TH6

D D

C C

TH5TH5

1

1

TH3TH3

TH7TH7

TH4TH4

1

1

GNDGND

1

FD1

FD1

Fiducial

Fiducial

NM

NM

FD2

FD2

Fiducial

Fiducial

1

1

NM

NM

CASE1

CASE1

SHIELDING

SHIELDING

NM

NM

4

FD4

FD3

FD3

Fiducial

Fiducial

1

1

1

1

GND GND GND

NM

NM

1

CASE2

CASE2

SHIELDING

SHIELDING

NM

NM

FD4

Fiducial

Fiducial

1

1

1

1

1

NM

NM

CASE3

CASE3

SHIELDING

SHIELDING

NM

NM

1

FD5

FD5

Fiducial

Fiducial

NM

NM

1

3

FD6

FD6

Fiducial

Fiducial

1

1

1

1

NM

NM

2

1

B B

A A

GIGABYTE Communication

Einstein Main Board

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Wednesday, January 18, 2006

Date: Sheet of

Wednesday, January 18, 2006

Date: Sheet of

5

4

3

2

Wednesday, January 18, 2006

1

of

1

1

1

1.1

1.1

1.1

21

21

21

5

FFRXD<10>

FFTXD<10>

FFCTS<10>

FFRTS<10>

BT_RXD<17>

BT_TXD<17>

BT_CTS<17>

BT_RTS<17>

D D

C C

B B

VCC_BATT<4,5,8,10> VCC_1V8<3,4,5,7,8,11,12,15,20>

GND

A A

SDIO_CLK<13>

SDIO_CMD<13>

SDIO_DAT0<13>

SDIO_DAT1<13>

SDIO_DAT2<13>

SDIO_DAT3<13>

DSC_STRB<8>

CIF_MCLK<8,12>

CIF_FV<8,12>

CIF_LV<8,12>

CIF_PCLK<8,12>

GPRS_ON<10>

UBL_ON<18>

GPRS_RST<10>

WKUP_GPRS<10>

AC97_BITCLK<7>

AC97_SDATA_IN_0<7>

AC97_SDATA_OUT<7>

AC97_SYNC<7>

AC97_nRESET<7>

IR_RXD<13>

IR_TXD<13>

SCL<8,11,14>

SDA<8,11,14>

BT_EN<17>

GPRS_OFF<10>

PWM2<18>

AC97_INT<7>

nRESET<5,16,19>

nRESET_OUT<18>

PWR_EN<5>

nBATT_FAULT<5>

nVCC_FAULT<5>

SYS_EN<5>

PWR_SCL<5>

PWR_SDA<5>

R203

R203

N.M

N.M

BOOTSELBOOTSEL

R204

R204

10K

10K

TP202TP202

TP203TP203

TP204TP204

R203 R204 (JUMP)

1

1

1

CIF_DD6

CIF_DD0

KP_MKOUT7

CIF_DD1 CIF_DD2

CIF_DD3

CIF_DD2

CIF_DD7

TP219TP219

1

BOOTSEL

TP201TP201

TP_13

1

TP_14

TP_15

TP_16

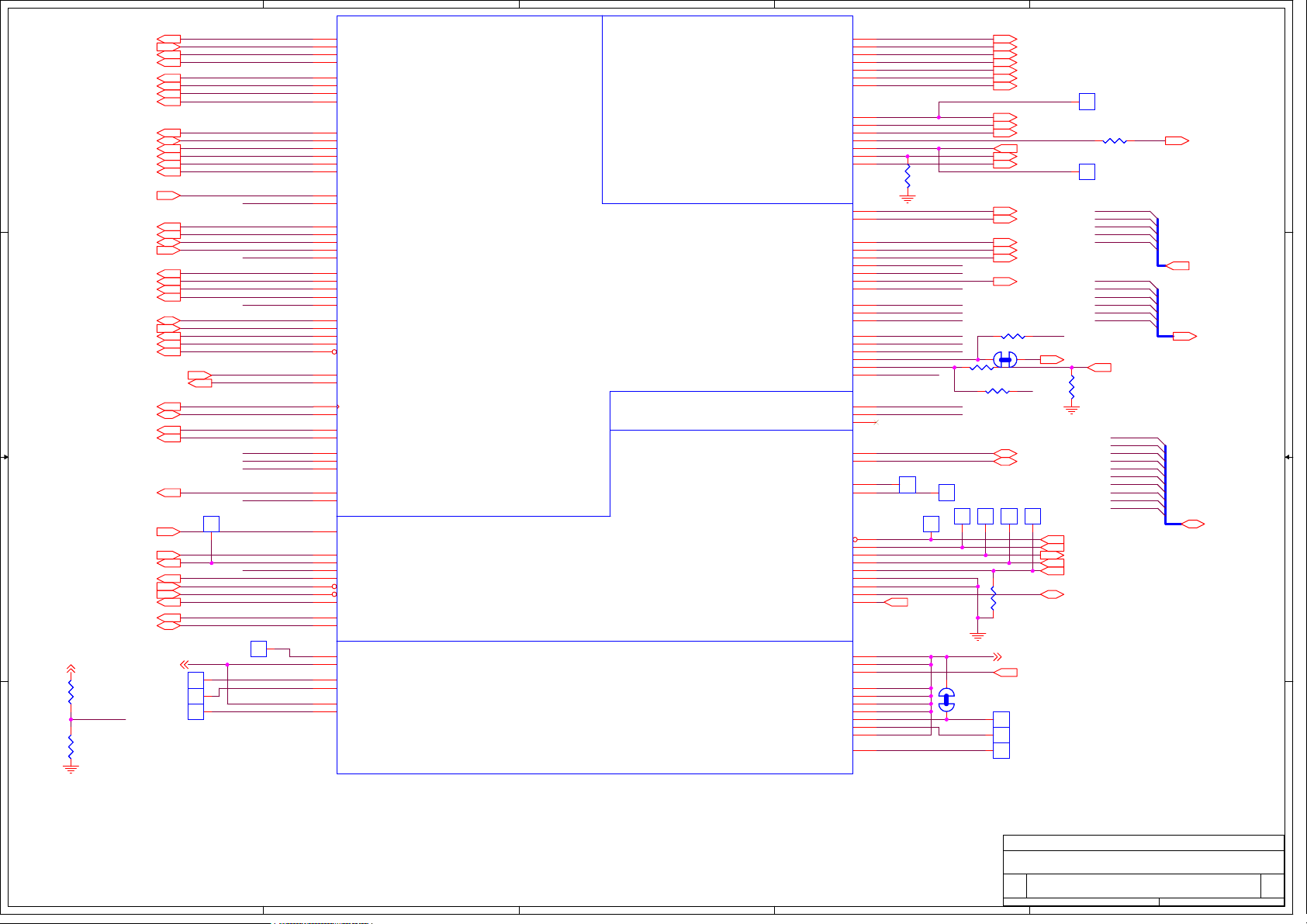

U201A

U201A

F2

FF_RXD/GPIO34/USB_nOE2/KP_MKIN3/SSPCLK3

D4

FF_TXD/GPIO39/KP_MKIN4/SSPSFRM3 USB_VPO2

E3

FF_CTS/GPIO35/KP_MKOUT6 USB_RCV2/SSPTXD3

D5

FF_RTS/GPIO41/KP_MKOUT7/USB_HPWR2/SSPRXD3

A4

BT_RXD/GPIO42/ICP_RXD/CIF_MCLK

B4

BT_TXD/GPIO43/ICP_TXD/CIF_FV

D3

BT_CTS/GPIO44/CIF_LV

F1

BT_RTS/GPIO45/AC97_SYSCLK/CIF_PCLK SSPSYSCLK3

F3

MMCLK/GPIO32/MSSCLK

G1

MMCMD/GPIO112/MSINS

G2

MMDATA0/GPIO92/MSBS

E5

MMDATA1/GPIO109/MSSDIO

F4

MMDATA2/GPIO110/MMCCS0

F5

MMDATA3/GPIO111/MMCCS1

E6

PWM_OUT0/GPIO16/KP_MKIN5

G3

PWM_OUT1/GPIO17/KP_MKIN6/CIF_DD6

H1

SSPSCLK/GPIO23/CIF_MCLK

H2

SSPSFRM/GPIO24/CIF_FV

F6

SSPTXD/GPIO25/CIF_LV

H3

SSPRXD/GPIO26/CIF_PCLK

H4

SSPEXTCLK/GPIO27/SSPSYSCLK/SSPSCLKEN/CIF_DD[0]

G4

SSPSCLK2/GPIO36/USB_VMO2/FFDCD/KP_MKIN7

G5

SSPSFRM2/GPIO37/USB_HPEN2/FFDSR/KP_MKIN3

H5

SSPTXD2/GPIO38/FFRI/USB_VM2 PWM_OUT1

J3

SSPRXD2/GPIO40/KP_MKOUT6/FFDTR/USB_VP2

F7

SSPEXTCLK2/GPIO22/SSPSCLK2EN SPSSYSCLK2/KP_MKOUT7

K1

AC97_BITCLK/GP28/I2S_BITCLK/SSPSFRM

K2

AC97_SDATA_IN_0/GPIO29/I2S_DATA_IN/SSPCLK

G6

AC97_SDATA_OUT/GPIO30/I2S_SDATA_OUT/USN_nOE3

J4

AC97_SYNC/GPIO31/I2S_SYNC/USB_VPO3

K4

AC97_nRESET/GPIO113/I2S_SYSCLK/USB_VM3

H6

ICP_RXD/GPIO46/STD_RXD/PWM_OUT2

K5

ICP_TXD/GPIO47/STD_TXD CIF_DD0/PWM_OUT3

E2

SCL/GPIO117

B1

SDA/GPIO118

B3

USBHPWR0/GPIO88/SSPRXD2

A3

USBHPEN0/GPIO89/AC97_SYSCLK/SSPTXD2

C5

UVS0/GPIO114/CIFDD-[1] AC97_BITCLK/UVS0

B5

nUVS1/GPIO115/DREQ0/nUVS1 CIF_DD3/PWM_OUT1 MREQ

C4

nUVS2/GPIO116/CIF_DD2 AVAL0/AC97_SDATA_IN_0/MBGNT U_DET

J6

EXT_SYNC0/GPIO11/EXT_SYCN0 48_MHz/CHOUT0/PWM_OUT2 USB_RCV3

L3

EXT_SYNC2/GPIO12/EXT_SYNC1 48_MHz/CHOUT1 CIF_DD7/PWM_OUT3

D15

CLK_OUT/HZ_CLK/CHOUT1/USB_VP3/GPIO10

A16

nRESET

B19

nRESET_OUT

B18

BOOT_SEL

B16

PWR_EN

C18

nBATT_FAULT

C17

nVCC_FAULT

D17

SYS_EN/GPIO2

C16

PWR_SCL/GPIO3

B15

PWR_SDA/GPIO4

W9

RFU

W10

F_VPP

W12

RFU

W13

RFU

W15

NF_WP

W16

RFU

4

Function

Function

VCC_IO

VCC_IO

Reserved Function

Reserved Function

3

BB_OB_DAT0/GPIO81/SSPTXD3CIF_DD0

BB_OB_DAT1/GPIO48/PCMCIA_nPOE/CIF_DD5

BB_OB_DAT2/GPIO50/PCMCIA_nPIOR/CIF_DD3

BB_OB_DAT3/GPIO51/PCMCIA_nPLOW/CIF_DD2

BB_OB_STB/GPIO53/CIF_MCLK USB_VM2/FFRXD SSPSYSCLK

VCC_BB

VCC_BB

KP_DKIN2/GPIO95/AC97_RESET_n/CID_DD4/KP_MKIN6

VCC_USIM

VCC_USIM

VCC_REG

VCC_REG

BB_OB_CLK/GPIO52/SSPSCLK3/CIF_DD4

BB_OB_WAIT/GPIO54/PCMCIA_nPCE2/CIF_PCLK

BB_IB_DATA0/GPIO82/SSPRXD3/CIF_DD5

BB_IB_DATA1/GPIO55/PCMCIA_nPREG/CIF_DD1

BB_IB_DATA2/GPIO56/PCMCIA_nPWAIT/USB_VOM3

BB_IB_DATA3/GPIO57/PCMCIA_NIOIS16/SSPTXD

KP_DKIN0/GPIO93/CIFDD6/AC97_SDATA_OUT

KP_DKIN3/GPIO96/DVAL1/MBREQ KP_MKOUT6

KP_DKIN4/GPIO97/DREQ1 KP_MKIN3/MBGNT

KP_DKIN5/GPIO98/CIF_DD0/AC97_SYSCLK/KP_MKIN4

KP_DKIN6/GPIO99/AC97_SDATA_IN_1/KP_MKIN5

KP_MKOUT1/GPIO104/CIF_DD2/PCMCIA_PSKTSEL

KP_MKOUT2/GPIO105/CIF_DD1/PCMCIA_nPCE2

UCLK/GPIO91/KP_MKIN6 USB_RCV3/CIF_DD5

BB_IB_CLK/GPIO83/SSPSFRM3

BB_IB_STB/GPIO84/SSPSCLK3/CIF_FV

BB_IB_WAIT/GPIO85/PCMCIA_nPCE1/CIF_LV

KP_DKIN1/GPIO94/CIF_DD5/AC97_SYNC

KP_MIKIN2/GPIO102/PCMCIA_nPCE1

KP_MKOUT0/GPIO103/CIF_DD3

KP_MKOUT3/GPIO106/CIF_DD9

KP_MKOUT4/GPIO107/CIF_DD8

KP_MKOUT5/GPIO108/CIF_DD7/CHOUT0

URST/GPIO90/KP_MKIN5 USB_VP3/CIF_DD4

USBHPWR/GPIO119

USBHPEN/GPIO120

KP_MIKIN0/GPIO100

KP_MIKIN1/GPIO101

UIO

USBC_P

USBC_N

USBH_P[1]

USBH_N[1]

nTRST

TDO

TMS

TCK

TESTCLK

TEST

GPIO0

nGP_RST/GPIO1

D_VCC

RFU

NF_RST

RFU

RFU

F_VCC

F_VCC

RFU

RFU

D_VCC

RFU

2

K15

L18

K17

J15

K18

K19

K20

N19

L16

M18

L17

M19

M20

L15

100K

100K

R212

R212

GND

B2

C3

G19

F16

G20

KP_MKOUT6

F17

KP_MKIN3

F15

G18

KP_MKIN5

G17

KP_MKIN0

G16

KP_MKIN1

H18

KP_MKIN2

H19

KP_MKOUT0

J20

KP_MKOUT1

H17

KP_MKOUT2

J18

GPIO_106

H16

GPIO_107

J17

KP_MKOUT5

J16

CIF_DD4

A7

CIF_DD5

C7

B6

D2

C2

TP212TP212

A6

1

A5

C14

B14

TDI

D14

C13

E14

A13

B13

A15

D16

Y6

Y7

Y8

Y10

Y11

Y12

Y13

Y14

Y15

Y16

Y18

U201_Y14

U201_Y15

U201_Y18

GPRS_INT <10>

TP214TP214

TP213TP213

1

1

TP215TP215

SJ201SJ201

2 1

R210 0RR210 0R

1

GND

USB_EN <13>

WLAN_nPOE <21>

WLAN_nPIOR <21>

WLAN_nPIOW <21>

WLAN_PWREN <21>

SD_CD <13>

WLAN_nPCE2 <21>

BT_WKUP <17>

WLAN_nPREG <21>

WLAN_nPWAIT <21>

BT_INT <17>

DBL_ON <16>

WLAN_nPCE1 <21>

ETH_INT <19>

DSC_PWR <8>

TRI_LED1 <18>

TRI_LED2 <18>

VB_ON <19>

AC97_SYSCLK <7>

R208 N.MR208 N.M

CIF_DD9

SJ202SJ202

21

R209 N.MR209 N.M

CIF_DD8

USB_OTG_P <13>

USB_OTG_N <13>

TP216TP216

TP218TP218

TP217TP217

1

1

1

R205

R205

2.2K

2.2K

VCC_1V8 <3,4,5,7,8,11,12,15,20>

nRESET_OUT <18>

1

TP205TP205

1

TP206TP206

1

TP207TP207

TP209TP209

1

R2070RR207

TP210TP210

1

KP_MKIN0

KP_MKIN1

KP_MKIN2

KP_MKIN3

KP_MKIN5

KP_MKOUT0

KP_MKOUT1

KP_MKOUT2

KP_MKOUT5

KP_MKOUT6

KP_MKOUT7

keepact <12>

R211

R211

100K

100K

GND

nTRST <19>

TDI <19>

TDO <19>

TMS <19>

TCK <19>

nPMIC_INT <5>

REMOVE nTRST

1

JUMP

0R

MOD_ON_STATE<19>

CIF_DD0

CIF_DD1

CIF_DD3

CIF_DD4

CIF_DD5

CIF_DD6

CIF_DD7

CIF_DD8

CIF_DD9

WLAN_nIOIS16 <21>

KP_MKIN[7:0] <16,18>

KP_MKOUT[7:0] <16,18>

CIF_DD[9:0] <8,12>

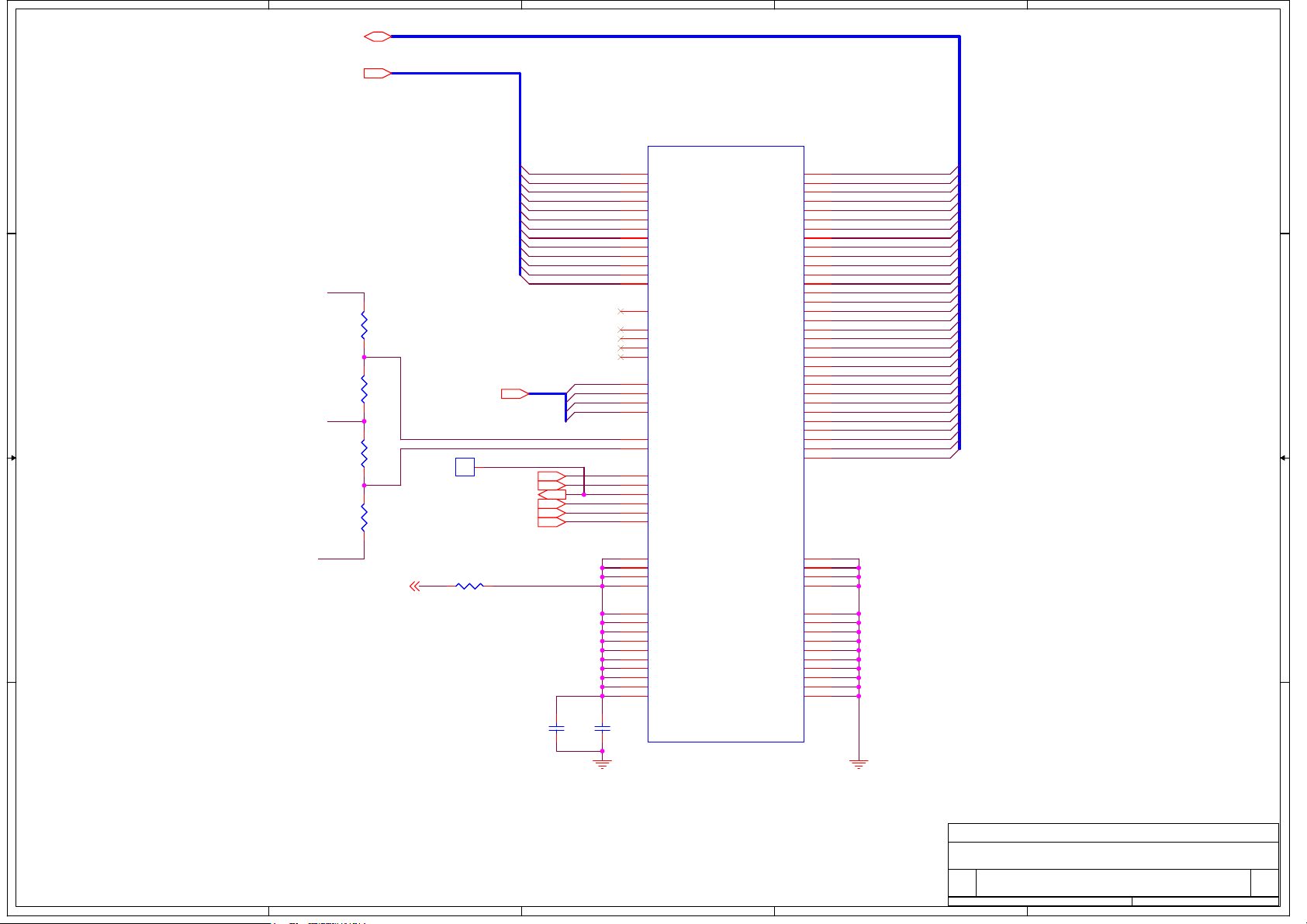

GIGABYTE Communication

Einstein Main Board

Title

Title

Title

Bulverde_GPIO PVT

Bulverde_GPIO PVT

Bulverde_GPIO PVT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

221Wednesday, January 18, 2006

221Wednesday, January 18, 2006

221Wednesday, January 18, 2006

1

1.1

1.1

1.1

5

4

3

2

1

EVT2

GPIO15 -->HP_DECT

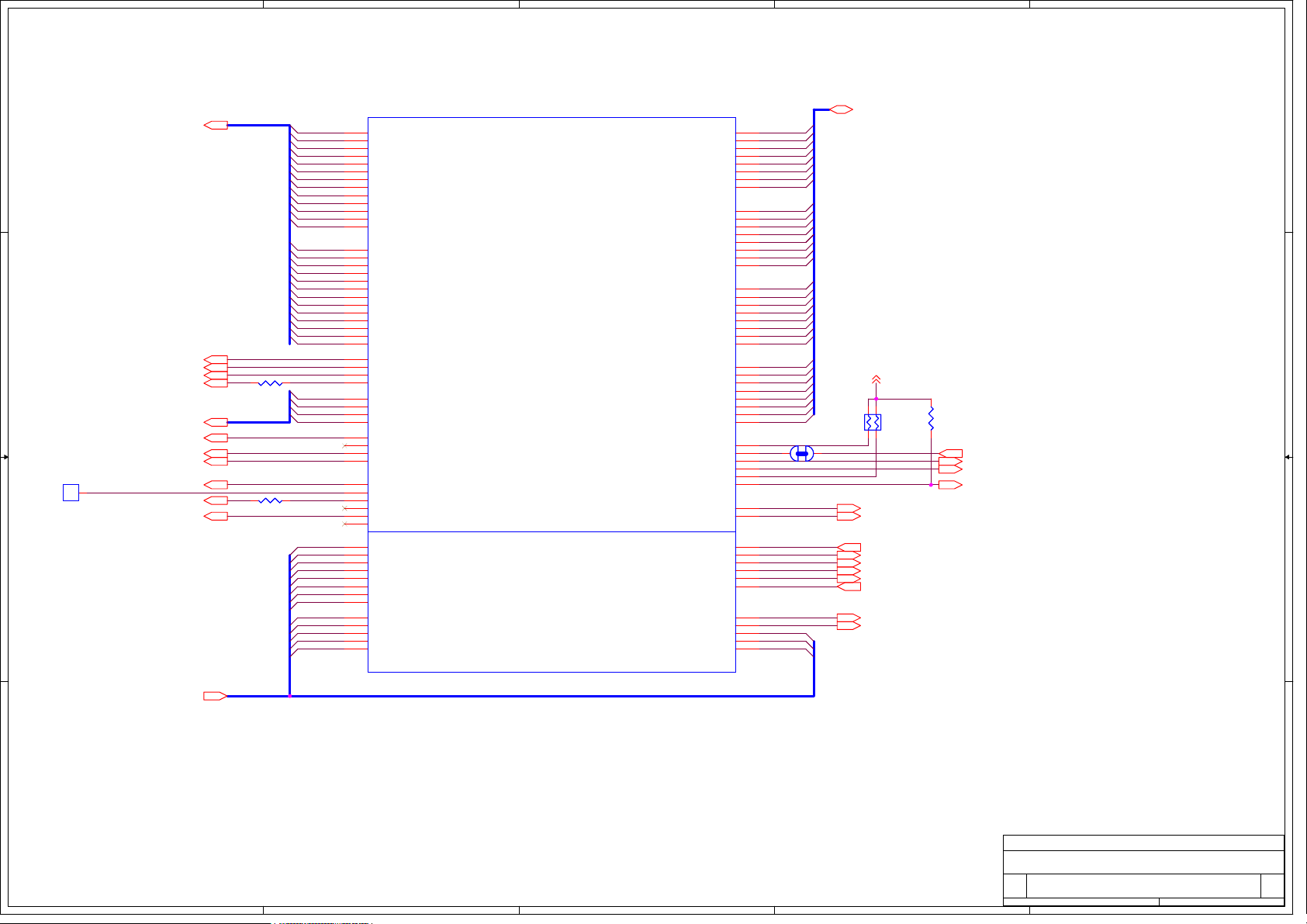

U201B

U201B

MEMORY INTERFACE

D D

GPIO20 available

GPIO78

GPIO79

C C

TP301TP301

TP301

1

B B

MA[25:0]<6,19,20>

nOE<19,20>

nWE<6,20>

nSDRAS<6>

nSDCAS<6>

DQM[3:0]<6,19>

nSDCS0<6>

TV_nRESET<12>

STRB-INTEN<8>

SDCKE<6>

SDCLK1<6>

RDnWR<19,20>

R302

R302

24R

24R

R301

R301

24R

24R

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15

MA16

MA17

MA18

MA19

MA20

MA21

MA22

MA23

MA24

MA25

U201_U20

DQM0

DQM1

DQM2

DQM3

U201_P19

L_DD0

L_DD1

L_DD2

L_DD3

L_DD4

L_DD5

L_DD6

L_DD7

L_DD8

L_DD9

L_DD10

L_DD11

L_DD12

W3

MA0

Y3

MA1

T8

MA2

P6

MA3

R7

MA4

W8

MA5

N5

MA6

R6

MA7

T7

MA8

P5

MA9

P4

MA10

W7

MA11

T6

MA12

U6

MA13

V6

MA14

R5

MA15

T5

MA16

W6

MA17

P2

MA18

R4

MA19

T4

MA20

W5

MA21

Y4

MA22

W4

MA23

W2

MA24

V2

MA25

W19

nOE

W20

nWE

Y19

nSDRAS

U20

nSDCAS

W18

DQM0

P17

DQM1

T17

DQM2

W17

DQM3

V18

nSDCS0

R17

nSDCS1

T20

GPIO20/nSDCS2/DREQ0/MBREQ

R18

GPIO21/nSDCS3/DVAL0/MBGNT

T18

SDCKE

V20

SDCLK0

P19

SDCLK1

T19

SDCLK2

M4

RDnWR

V19

SDCLK3

D7

L_DD0/GP58

D8

L_DD1/GP59

F8

L_DD2/GP60

A8

L_DD3/GP61

E8

L_DD4/GP62

C8

L_DD5/GP63

C9

L_DD6/GP64

A9

L_DD7/GP65

E9

L_DD8/GP66

F10

L_DD9/GP67

D10

D10

C10

L_DD11/GP69

B10

L_DD12/GP70

MEMORY INTERFACE

nCS1/GPIO15/PCMCIA_nPCE1

nCS3/GPIO79/PCMCIA_PSKTSEL/PWM_OUT2

VCC_MEM

VCC_MEM

L_DD17/GPIO87/PCMCIA_nPCE[2] SSPTXD2/USB_P3_1 SSPSFRM2

L_DD16/GPIO86/SSPRXD2 PCMCIA_nPCE[1]/USB_P3_5

VCC_LCD

VCC_LCD

nCS2/GPIO78/PCMCIA_nPCE2

nCS4/GPIO80/DREQ1/MBREQ PWM_OUT3

nCS5/GPIO33/DVAL1/MBGNT

L_VSYNC/GPIO14/SSPSFRM2

L_CS/GPIO19/SSPCLK2

L_PCLK_WR/GPIO76

L_LCLK_A0/GPIO75

L_FCLK_RD/GPIO74

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

nCS0

RDY/GPIO18

nPWE/GPIO49

L_BIAS/GPIO77

L_DD15/GP73

L_DD14/GP72

L_DD13/GP71

MD0

U17

MD1

M17

MD2

P16

MD3

V15

MD4

M16

MD5

M15

MD6

T14

MD7

V13

MD8

R14

MD9

T12

MD10

T11

MD11

R10

MD12

R9

MD13

R8

MD14

M6

MD15

N6

MD16

N17

MD17

N16

MD18

T16

MD19

U15

MD20

W14

MD21

N15

MD22

R15

MD23

P15

MD24

U13

MD25

R12

MD26

R11

MD27

T10

MD28

T9

MD29

L6

MD30

L5

MD31

M5

W1

V1

V4

P3

P1

T3

M2

M1

B12

F14

D13

D12

C12

E13

D11

C11

F12

E11

A10

SJ301SJ301

IR_STDN change to GPIO79

L_DD15

L_DD14

L_DD13

TP302

21

MD[31:0] <6,19,20>

VCC_1V8<2,4,5,7,8,11,12,15,20>

1

2

3

4

RDY <19>

nPWE <19,20>

L_SSPSFRM <18>

L_SSPCLK <18>

WLAN_RESET <21>

L_PCLK <18>

L_LCLK <18>

L_FCLK <18>

L_SSPTXD <18>

DSC_RESET <8>

Rn301

Rn301

100k 0404

100k 0404

R303

R303

100K

100K

HP_DECT <15>

nCS2 <20>

WLAN_1V8_PSKTSEL <20>

nCS5_ETH <19>

L_DD[17:0]<18>

A A

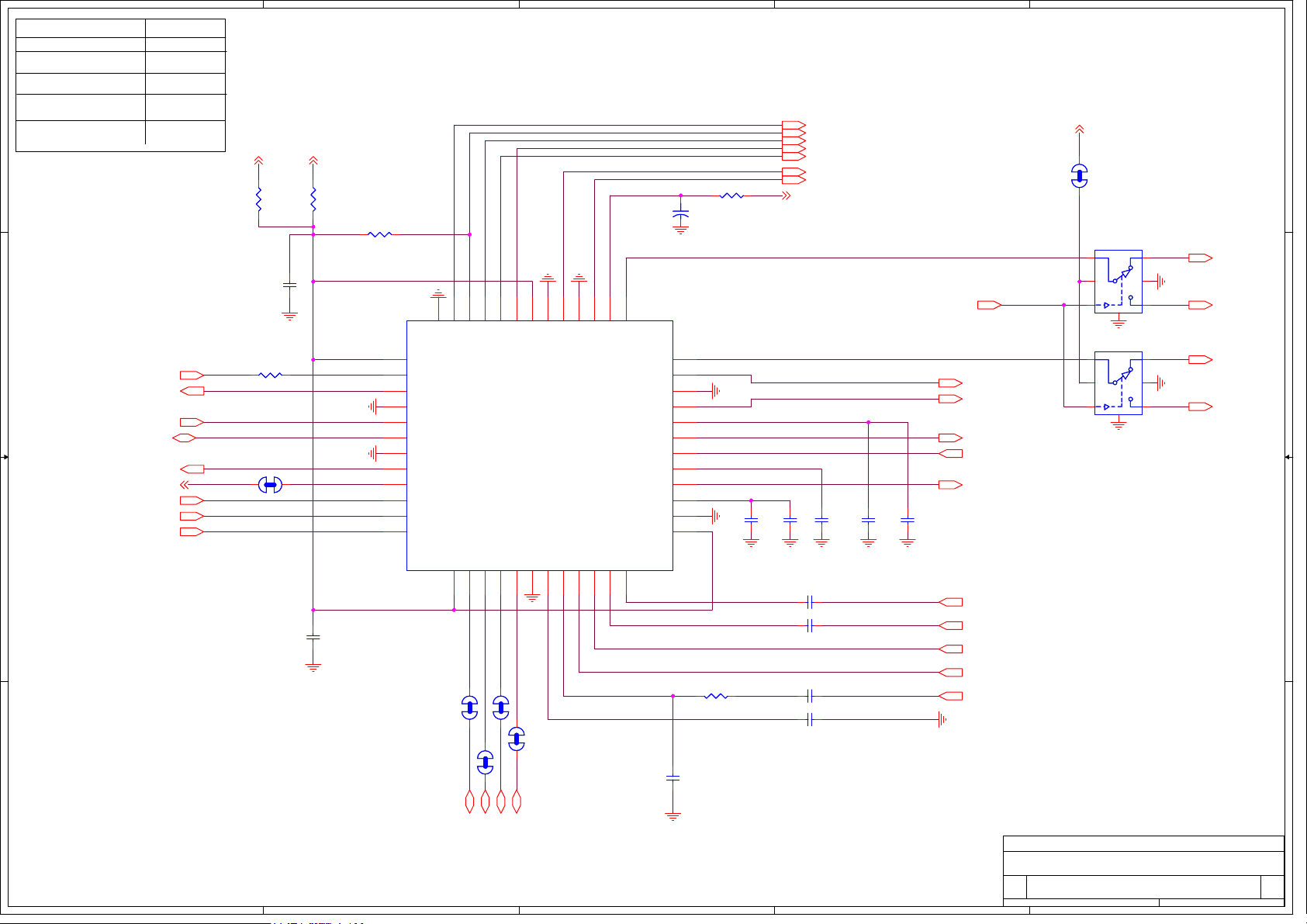

GIGABYTE Communication

Einstein Main Board

Title

Title

Title

Bulverde_Memory PVT

Bulverde_Memory PVT

Bulverde_Memory PVT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

321Wednesday, January 18, 2006

321Wednesday, January 18, 2006

321Wednesday, January 18, 2006

1

1.1

1.1

1.1

5

8

4

3

2

1

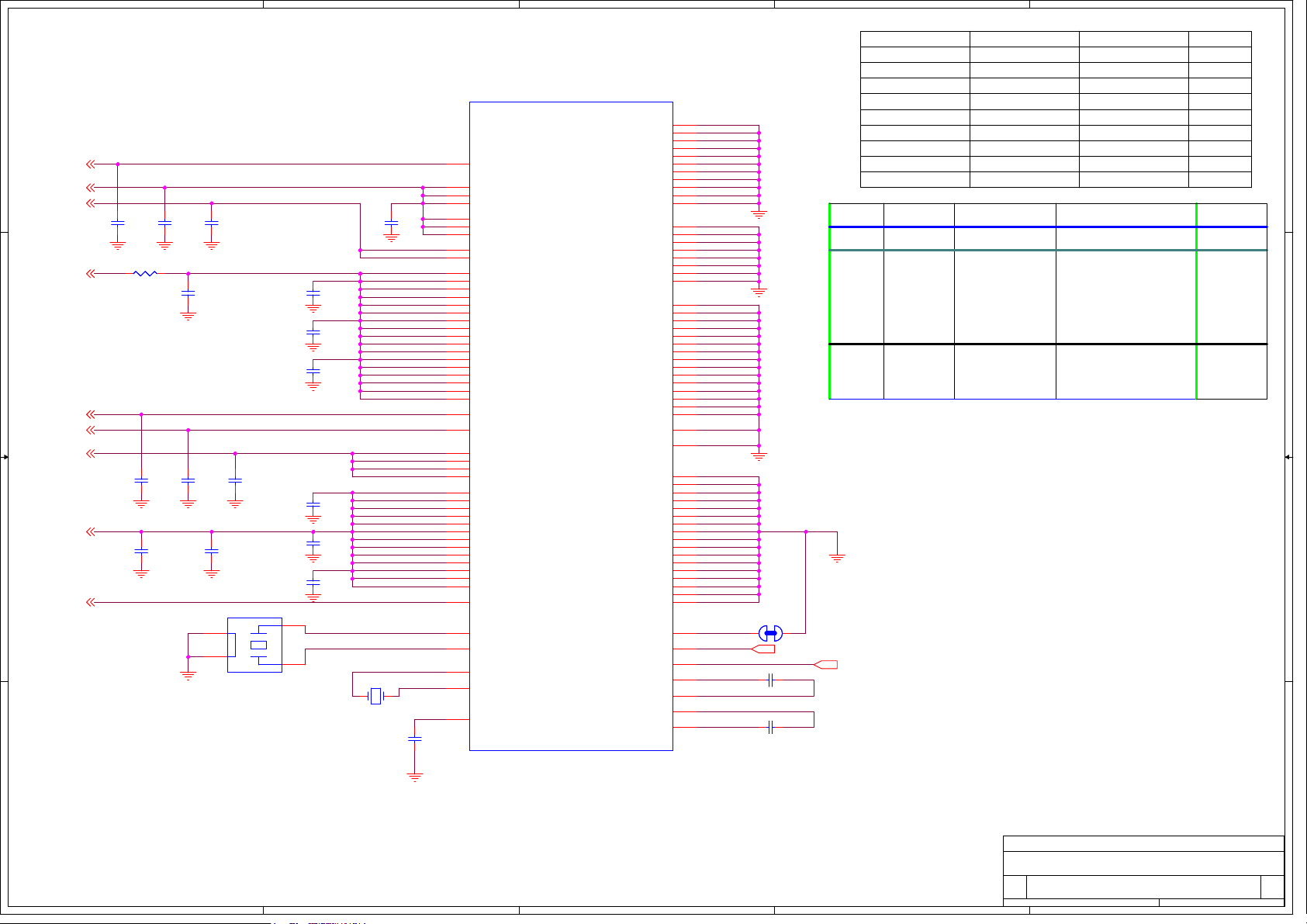

REGULATOR NAME

IOREG VCC_IO

DCUD

DCD

U201C

U201C

D D

VCC_BATT<2,5,8,10>

VCC_IO13,14,15,16>

VCC_3P0<5,8,12,18>

C402

C402

100nF

100nF

,11,12,15,20>

C C

,13,14,15,16>

B B

,13,14,15,16>

A A

VCC_1V8

VCC_IO

VCC_PLL<5>

VCC_SRAM<5>

VCC_CORE<5>

VCC_IO

GND

R401 0RR401 0R

GND

C409

C409

100nF

100nF

C414

C414

100nF

100nF

C401

C401

100nF

100nF

C408

C408

100nF

100nF

GNDGND

C404

C404

100nF

100nF

GND

C410

C410

100nF

100nF

GNDGND GND

C419

C419

100nF

100nF

GND

4

2

GND

13MHZ

13MHZ

VCC_MEM

C411

C411

100nF

100nF

X401

X401

C403

C403

100nF

100nF

GND

C405

C405

100nF

100nF

GND

C406

C406

100nF

100nF

GND

C407

C407

100nF

100nF

GND

C412

C412

100nF

100nF

GND

C413

C413

100nF

100nF

GND

C415

C415

100nF

100nF

GND

3

1

13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT13MOUT

13MIN

X402

X402

32.786KHZ

32.786KHZ

VCC_MEM

U201_D20

GND

32KIN32KIN32KIN32KIN32KIN32KIN32KIN32KIN

32KOUT

C418

C418

100nF

100nF

E17

VCC_BATT

H20

VCC_IO

J1

VCC_IO

L1

VCC_IO

A1

VCC_USB

A2

VCC_USB

D1

VCC_USB

A11

VCC_LCD

B8

VCC_LCD

N1

VCC_MEM

T2

VCC_MEM

V5

VCC_MEM

V7

VCC_MEM

V8

VCC_MEM

V9

VCC_MEM

V10

VCC_MEM

V11

VCC_MEM

V12

VCC_MEM

V14

VCC_MEM

V16

VCC_MEM

V17

VCC_MEM

Y20

VCC_MEM

R19

VCC_MEM

N20

VCC_MEM

P20

VCC_MEM

R1

VCC_MEM

L20

VCC_BB

F18

VCC_PLL

M3

VCC_SRAM

N3

VCC_SRAM

R3

VCC_SRAM

U3

VCC_SRAM

A12

VCC_CORE

B7

VCC_CORE

B9

VCC_CORE

B11

VCC_CORE

E1

VCC_CORE

J19

VCC_CORE

K3

VCC_CORE

L19

VCC_CORE

R2

VCC_CORE

R20

VCC_CORE

T13

VCC_CORE

T15

VCC_CORE

U1

VCC_CORE

C6

VCC_USIM

E19

PXTAL_IN

E20

PXTAL_OUT

B17

TXTAL_IN

A17

TXTAL_OUT

D20

PER_OUT

PCGAPBVM22B0

PCGAPBVM22B0

VCC_GND

VCC_GND

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

VSS_CORE

CLK_PIO/GPIO9/HZ_CLK/CHOUT0

CLK_EXT/GPIO13

PWR_CAP0/GPIO5

PWR_CAP1/GPIO6

PWR_CAP2/GPIO7

PWR_CAP3/GPIO8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_IO

VSS_IO

VSS_IO

VSS_IO

VSS_IO

VSS_IO

VSS_IO

VSS_IO

VSS_MEM

VSS_MEM

VSS_MEM

VCC_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_MEM

VSS_BB

VSS_PLL

CLKREQ

Y9

Y17

W11

Y5

D19

C15

C20

B20

A20

A19

A18

D6

D9

E4

E12

F20

G15

J2

L2

U19

Y2

N2

N18

P18

T1

U5

U7

U8

U9

U10

U11

U12

U14

U16

K16

F19

R13

R16

U2

U4

U18

V3

Y1

C1

E7

E10

F9

F11

F13

H15

J5

K6

N4

E15

A14

L4

C19

D18

E18

E16

U201_E15

PWR_CAP0

PWR_CAP1

PWR_CAP2

PWR_CAP3

GND

GND

GND

SJ401SJ401

HALL_SENSOR <16>

C416

C416

100nF

100nF

C417

C417

100nF

100nF

Enable

None

SYS_EN

SYS_EN

SYS_EN

SYS_EN

SYS_EN

SYS_EN

PWR_EN

PWR_EN

PWR_EN

GND

21

WLAN_INT <21>

Cancel 13M_OUT

D2REG

D1REG

DCDE

LPREG

D3REG

DC_DC

POWER

DOMAIN

VCC_BATT

VCC_IO

VCC_LCD

VCC_MEM

VCC_BB

VCC_USIM

VCC_USB

VCC_PLL

VCC_SRAM

VCC_CORE

VOLTAGE SUPPLY

VCC_MEM

VCC_CORE

VCC_PLL

VCC_SRAM

VCC_LCD

VCC_BATT

VOLTAGE

LEVEL

V3.0

V3.3

V3.0

V1.8,2.5,3.0

V3.3

V2.5,3.0,3.3

V1.8

V1.8,2.5,3.0,3.3

V1.8,3.0

V3.3

V3.0

V1.3

V1.1

Variable V 0.85-V1.3

OUTPUT VOLTAGE

3.3V

1.8V

0.9-1.5V ADJUST

1.3V

1.1V

V3.3

3.3V

Initial 2.5V config to 2.8V

1.8V

Tolerance

+_25%

+_10%

+20,-5(@1.8V) Otherwise +_10%

+20,-5(@1.8V) Otherwise +_10%

+20,-5(@1.8V) Otherwise +_10%

+20,-5(@1.8V) Otherwise +_10%

+_10%

+_10%

+_10%

+_10%

1.8V

CURRENT

150mA

500mA

500mA

150mA

150mA

2000mA(max)

150mA (5mA@ECO)

150mA

500mA

5mA@3.75V

15mA@3.3V

6mA@3.3V

127mA@3.3V

4mA@3.3V

0.3mA@3.0V

15mA@3.3V

23mA@1.3V

14mA@1.1V

310mA@1.3V

GIGABYTE Communication

Einstein Main Board

Title

Title

Title

Bulverde_Power PVT

Bulverde_Power PVT

Bulverde_Power PVT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet of

421Wednesday, January 18, 2006

421Wednesday, January 18, 2006

421Wednesday, January 18, 2006

of

1

of

1.1

1.1

1.1

5

4

3

2

1

CHGVINCHGVINCHGVINCHGVINCHGVINCHGVIN

D501

D501

USBC_VBUS<13>

R510

R510

10K 1%

10K 1%

R508

R508

10K 1%

10K 1%

PWR_SDA<2>

PWR_SCL<2>

None

SYS_EN

SYS_EN

SYS_EN

SYS_EN

SYS_EN

SYS_EN

PWR_EN

PWR_EN

PWR_EN

NTCSW

BATTEMPBATTEMP

BATT+<8,9,11,14,17,18,19,21>

GND

keepact<2>

POWER

DOMAIN

VCC_BATT

VCC_IO

VCC_LCD

VCC_MEM

VCC_BB

VCC_USIM

VCC_USB

VCC_PLL

VCC_SRAM

VCC_CORE

D D

GND

C C

B B

Enable

A A

2 1

MBRM120LT1

MBRM120LT1

R529

R529

127K 1%

127K 1%

R530

R530

24K 1%

24K 1%

GND

C506

C506

100nF

100nF

GND

VCC_BATT<2,4,8,10>

C509

C509

20pF

20pF

C513

C513

20pF

20pF

<4,7,10,11,13,14,15,16>

Q505

Q505

1

PDTC114EE(N.M.)

PDTC114EE(N.M.)

VOLTAGE

LEVEL

V3.0

V3.3

V3.3

V1.8

V1.8,2.5,3.0,3.3

V1.8,3.0

V3.3

V1.3

V1.1

Variable V 0.85-V1.3

5

ADIN3

R512

R512

4.7K

4.7K

X501

X501

32.786KHZ

32.786KHZ

R1

R1

R2

R2

V3.0

V1.8,2.5,3.0

V2.5,3.0,3.3

VCC_BATT<2,4,8,10>

U501_KEEPACT

3

2

CHG_LED<18>

V3.0

Q501.1Q501.1

Q501

Q501

SI7411DN

SI7411DN

D

Rsense

0.12R 1206 1%

0.12R 1206 1%

EVT2

ADD NET

ACCESSARY_TYPE

R509

R509

4.7K

4.7K

GPOOD1<21>

PMICXIN

PMICXOUT

R516

R516

10M

10M

R517 47KR517 47K

R535 N.M.R535 N.M.

VCC_IO

GND

USBC_VBUS<13>

SJ504

SJ504

short jump

short jump

Tolerance

+_25%

+_10%

+20,-5(@1.8V) Otherwise +_10%

+20,-5(@1.8V) Otherwise +_10%

+20,-5(@1.8V) Otherwise +_10%

+20,-5(@1.8V) Otherwise +_10%

+_10%

+_10%

+_10%

+_10%

R5011KR501

C501

C501

1K

1uF 0603

S

R504

R504

2

3

4

G

786

5 1

1uF 0603

16V

CHGTR.G

909 mA for fast charge

change VCC_BATT --> Vcc_IO

ACCESSARY_TYPE<13>

TP504TP504

1

nBATT_FAULT<2>

nVCC_FAULT<2>

nPMIC_INT<2>

POWER_ON<18,19>

USBC_VBUS<13>

21

R513 47KR513 47K

VCC_BATT<2,4,8,10>

21

H-->GPOOD0 L-->LED OFF;

L-->GPOOD0 H-->LED ON;

Charger IN -->GPOOD0 H-->LED ON

D509

D509

1SS400 EMD2

1SS400 EMD2

R520

R520

200K

200K

U501_KEEPACT

nRESET<2,16,19>

VCC_LCD<7,17,19,21> VCC_IO

<4,7,10,11,13,14,15,16>

21

D505

D505

N.M

N.M

R522

R522

300K(N.M.)

300K(N.M.)

GPOOD0

5mA@3.75V

15mA@3.3V

6mA@3.3V

127mA@3.3V

4mA@3.3V

0.3mA@3.0V

15mA@3.3V

23mA@1.3V

14mA@1.1V

310mA@1.3V

R503

R503

100R

100R

Q504

Q504

CHGTR.B

1

BC846BW

BC846BW

2 3

GND

GPOOD0

GPOOD1

D512

D512

1SS400 EMD2

1SS400 EMD2

21

D510

D510

1SS400 EMD2(N.M.)

1SS400 EMD2(N.M.)

REGULATOR NAME

4

U501

U501

11

CHGCURCHGCURCHGCURCHGCUR

CHGCURCHGCUR

21

GND

R5192KR519

R5060RR506

CHGDRV

0R

NTCSW

VCC_IO<4,7,10,11,13,14,15,16>

BATTEMP

ADIN3

2K

1

1

TP502TP502

TP501TP501

12

13

14

24

15

16

17

18

19

20

21

22

23

52

2

1

6

7

9

10

53

54

5

56

8

55

<4,7,10,11,13,14,15,16>

1

GPRS_VBACK<9>

TP503TP503

CHGVIN

CHGDRV

CHGCUR

NTCSW

AVDD

BATVOLT

BATTEMP

ADCIN1

ADCIN2

ADCIN3

TSMY

TSPY

TSMX

TSPX

GPO0

GPOOD0

GPOOD1

SDA

SCL

OSC32I

OSC32O

PWRROK

IRQ

KEEPACT

RST

ONKEY

EXTON

VOLTAGE SUPPLY

IOREG VCC_IO

DCUD

DCD

D2REG

D1REG

DCDE

LPREG

D3REG

XC9216A18CMR

CHARGER

CHARGER

ADC

ADC

TOUCH SCREEN

TOUCH SCREEN

GPO

GPO

I2C

I2C

OSCILLATOR

OSCILLATOR

POWER ON

POWER ON

INTERRUPT

INTERRUPT

PCF50606HN/13B/N2

PCF50606HN/13B/N2

2 1

VCC_IO

nRESET<2,16,19>

N.M.

N.M.

BACKUP BATTERY

VCC_1V8

VCC_CORE

VCC_PLL

VCC_SRAM

VCC_LCD

VCC_BATT

VCC_2P5

VCC_SDRAM 1.8V

12

+

C502

+

C502

47uF 6.3V 6TPC47MB

47uF 6.3V 6TPC47MB

GND

DCDEVIN

DCDEND

DCDEPD

DCDELX

DCDEFB

DCUDMOD

DCUDLX

DCUDFB

DCUDVIN

DCDVIN

DCDLX

DCDFB

IOVDD

REGULATOR

REGULATOR

IOVIN

BASIC

BASIC

D3VIN

D3VDD

D2VDD

D2VIN

D1VIN

D1VDD

LPVDD

LPVIN

VBAT

VBACK

VINT

PWREN1

PWREN2

REFC

REFGND

VSS

VBACK

R532 N.M.R532 N.M.

D511

D511

N.M.

N.M.

R5210RR521

21

D513

D513

OUTPUT VOLTAGE

3.3V

1.8V

0.9-1.5V ADJUST

1.3V

1.1V

3.3V

3.3V

2.5V

3

51

50

49

47

48

25

45

46

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

27

26

4

3

28

29

57

0R

GND

IOVDDIOVDDIOVDDIOVDDIOVDDIOVDD

PMIC_REFC

U502_VBACK

2

.

.

T501

T501

1

GND

DCDEND

DCDEPDDCDEPDDCDEPDDCDEPD

GND

U501_D1D2

D1VDD

LPVDD

SJ505

SJ505

short jump

short jump

2 1

U501_4U501_4U501_4U501_4U501_4U501_4U501_4U501_4U501_4U501_4

U501_3U501_3

GND

21

U502U502

ML614R-TT33

MLVS0402M04

MLVS0402M04

C514

C514

100nF

100nF

VBACK

CURRENT

150mA

500mA

500mA

150mA

150mA

2000mA(max)

150mA (5mA@ECO)

150mA

500mA

C507

C507

470nF

470nF

GNDGND

DCDFB

DCDLX

USBC_VBUS<13>

C515

C515

470nF

470nF

1

2

3

Q2(N)

Q2(N)

FDC6020C

FDC6020C

7

U504

U504

Q1(P)

Q1(P)

D1

S1

G1

S2

S1

G2

S2

D2

8

R5110RR511

0R

C510

C510

470nF

470nF

BATT+<8,9,11,14,17,18,19,21>

6

5

4

GND

VCC_IO <4,7,10,11,13,14,15,16>

PWR_EN-->PWREN2;

SYS_EN-->PWREN1

VBACK

GNDGND

C508

C508

470nF

470nF

D506

D506

2 1

1SS400 EMD2

1SS400 EMD2

D507

D507

2 1

1SS400 EMD2

1SS400 EMD2

D508

D508

2 1

1SS400 EMD2

1SS400 EMD2

DCDELXDCDELX

MBRM120LT1

MBRM120LT1

DCDEFB

DCUDLX

D503

D503

PMEG2005AEA

PMEG2005AEA

D504

D504

PMEG2005AEA

PMEG2005AEA

D3VDD

D2VDD

C511

C511

470nF

470nF

GND GND

SJ507

SJ507

SJ506

SJ506

short jump

short jump

short jump

short jump

2

D502

D502

GND

L501

L501

10uH DB318C

10uH DB318C

C503

C503

10uF 0805

10uF 0805

2 1

GND GNDGND

L502

L502

10uH 7E03LG

10uH 7E03LG

C504

C504

10uF 0805

10uF 0805

2 1

GND

L503

L503

10uH 7E03LG

10uH 7E03LG

2 1

GND

R5140RR514

0R

R5150RR515

0R

C512

C512

470nF

470nF

PMIC_FIRQ

21

SYS_EN <2>

21

PWR_EN <2>

C516

C516

1UF 0603

1UF 0603

31

Q502

Q502

2

2SC5585

2SC5585

R531

R531

220K

220K

R502

R502

0R 0603

0R 0603

C520

C520

10uF 0805

10uF 0805

R5050RR505

21

0R

C519

C519

10uF 0805

10uF 0805

GND GND

DCUDFB

GND

Config D2VDD 2.5V-->3.0V

for LCD interface and

LCD vcc

R523&R524 Slect VCCSRAM

12

+

C505

+

C505

47uF 6.3V 6TPC47MB

47uF 6.3V 6TPC47MB

VCC_SRAM <4>

VCC_BATT <2,4,8,10>

BATT+<8,9,11,14,17,18,19,21>

PMIC_FIRQ

VCC_1V8<2,3,4,7,8,11,12,15,20>

GIGABYTE Communication

Einstein Main Board

Title

Title

Title

Power Manager IC PVT

Power Manager IC PVT

Power Manager IC PVT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCC_LCD <7,17,19,21>BATT+<8,9,11,14,17,18,19,21>

VCC_1V8 <2,3,4,7,8,11,12,15,20>

SJ501

SJ501

short jump

short jump

VCC_SDRAM <6>

R507

R507

VCC_CORE <4>

0 ohm 0603

0 ohm 0603

R5250RR525

0R

R525 R526 (JUMP)

D3VDDD3VDD

R526

R526

N.M

N.M

R5270RR527

0R

R527 R528 (JUMP)

D2VDDD2VDD

R528

R528

N.M

N.M

V1.8

R5340RR534

0R

U501_D1D2

R533

R533

N.M

N.M

1

VCC_3P0 <4,8,12,18>

VCC_PLL <4>

VCC_PLL <4>

VCC_1V8 <2,3,4,7,8,11,12,15,20>

521Wednesday, January 18, 2006

521Wednesday, January 18, 2006

521Wednesday, January 18, 2006

1.1

1.1

1.1

5

MD[31:0]<3,19,20>

MA[25:0]<3,19,20>

4

3

2

1

D D

MA10

MA11

MA12

MA13

MA14 MD4

MA15

MA16

MA17

SDCLK1<3>

SDCKE<3>

nWE<3,20>

U601.VDDU601.VDD

MA18

MA19

MA20

MA21

MA22

DQM0

DQM1

DQM2

DQM3

U601_J7

U601_H8

R602 R604--> 256Mb;

R603 R605--> 512Mb

MA22

R602

R602

N.M

N.M

C C

B B

R602 R603 (JUMP)

R604 R605 (JUMP)

MA23

MA24MA24

R6030RR603

0R

R604

R604

N.M

N.M

R6050RR605

0R

VCC_SDRAM<5>

TP601TP601

DQM[3:0]<3,19>

1

nSDCS0<3>

nSDCAS<3>

nSDRAS<3>

R6010RR601

0R

LAYOUT with samsung 256k [K4M56323PE-M(E)G/F1L] size 11mm X 13mm

LAYOUT with MICRON 256k [MT48H8M32LFF5-8] size 8mm X 11mm

LAYOUT with infenion 512k [K4M51323PE-M(E)G/F1L ] size 11mm X 13mm

U601

U601

MD0

G8

A0

G9

A1

F7

A2

F3

A3

G1

A4

G2

A5

G3

A6

H1

A7

H2

A8

J3

A9

G7

A10

H9

A11

H3

A12

E3

NC

K2

NC

K3

NC

E7

NC

H7

NC

K9

DQM_0

K1

DQM_1

F8

DQM_2

F2

DQM_3

J7

BA_0

H8

BA_1

J1

CLK

J2

CKE

J8

nCS

K8

nWE

K7

nCAS

J9

nRAS

A7

VDD_0

L7

VDD_1

R7

VDD_2

F9

VDD_3

E1

VDDQ_0

L1

VDDQ_1

B2

VDDQ_2

P2

VDDQ_3

B7

VDDQ_4

P7

VDDQ_5

C9

VDDQ_6

D9

VDDQ_7

M9

VDDQ_8

N9

VDDQ_9

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VSS_0

VSS_1

VSS_2

VSS_3

VSSQ_0

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

VSSQ_9

R8

MD1

N7

MD2

R9

MD3

N8

P9

MD5

M8

MD6

M7

MD7

L8

MD8

L2

MD9

M3

MD10

M2

MD11

P1

MD12

N2

MD13

R1

MD14

N3

MD15

R2

MD16

E8

MD17

D7

MD18

D8

MD19

B9

MD20

C8

MD21

A9

MD22

C7

MD23

A8

MD24

A2

MD25

C3

MD26

A1

MD27

C2

MD28

B1

MD29

D2

MD30

D3

MD31

E2

A3

F1

L3

R3

C1

D1

M1

N1

B3

P3

B8

P8

E9

L9

C602

C602

100nF

100nF

A A

5

4

C601

C601

100nF

100nF

K4S51323PF

K4S51323PF

3

GNDGND

GIGABYTE Communication

Einstein Main Board

Title

Title

Title

Mobile SDRAM PVT

Mobile SDRAM PVT

Mobile SDRAM PVT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

of

Date: Sheet of

Date: Sheet of

2

Date: Sheet

621Wednesday, January 18, 2006

621Wednesday, January 18, 2006

621Wednesday, January 18, 2006

1

1.1

1.1

1.1

5

AC97_SYSCLK<2>

SPEAKER_PATH

AC97_SDATA_OUT<2>

AC97_BITCLK<2>

AC97_SDATA_IN_0<2>

VCC_1V8<2,3,4,5,8,11,12,15,20>

AC97_SYNC<2>

AC97_nRESET<2>

SEND_END<15>

AC97

3.3V

200mA

1.1mA

0.56mA

0.005mA

0.0005mA

R705

R705

VCC_BATT

<2,4,8,10>

N.M.

N.M.

4.7uF 0603

4.7uF 0603

R704

R704

SJ701SJ701

C702

C702

R7010RR701

GND

Bead

Bead

VCC_IO<4,5,10,11,13,14,15,16>

0R

MCLKAMCLKAMCLKAMCLKAMCLKAMCLKAMCLKA

9713CoreVDD

21

VCC_IO

MAX

IDLE MODE(AC-LINK

RUNNING )

STANDBY MODE(READY

TO PLAY )

LOWER POWER

STANDBY

D D

OFF

MODE

C C

B B

INTERFACE

SEND_END use Auxiliary ADC input

HP_DEC use GPIO function

L: headphone plug in

H: no plug in

A A

5

C701

C701

4.7uF 0603

4.7uF 0603

GND

R703 NMR703 NM

AC97_VCCAC97_VCC

GND

GND

4

GND

49

U701

U701

1

thermal pad

DBVDD

2

MCLKA

3

MCLKB/GPIO6/(ADA/MASK)

4

DGND1

5

SDATAOUT

6

BITCLK

7

DGND2

8

SDATAIN

9

DCVDD

10

SYNC

11

RESETB/GPIO7

12

WIPER/AUX4/GPIO8

SJ702SJ702

4

GND GND

U701_SPKVDD

46

GPIO4/ADA/MASK/PCMDAC

GPIO3/PENDOWN/PCMFRM

X-_C

Y+_C

21

SJ703SJ703

TS_X-<18>

TS_Y+<18>

44

45

42

43

AGND2

HPVDD

GPIO2/IRQ

GPIO1/PCMCLK

WM9713L

WM9713L

GND

U701_19

Y-_C

21

SJ704SJ704

21

SJ705SJ705

TS_Y- <18>

41

HPR

U701_20

40

HPGND

38

39

HPL

SPKVDD

MIC2B/COMP2/AUX2

MIC2A/COMP1/AUX1

48

47

GPIO5/SPDIF/PCMADC

TPVDD13X+14Y+15X-16Y-17TPGND18PCBEEP19MONOIN20MIC121MICCM22LINEL23LINER

X+_C

21

TS_X+<18>

37

OUT3

24

3

SPKR

SPKL

SPKGND

OUT4

CAP2

MONO

MICBIAS

VREF

AGND

AVDD

3

12

+

+

GND

36

35

34

33

32

31

30

29

28

27

26

25

U701_LINER

U701_LINEL

R715 7.5KR715 7.5K

C713

C713

10nF

10nF

GND

R702 0RR702 0R

C714

C714

47uF 6.3V 6TPC47MB

47uF 6.3V 6TPC47MB

CODEC_OUT3

CODEC_SPKRCODEC_SPKRCODEC_SPKRCODEC_SPKRCODEC_SPKR

GND

U701_32U701_32U701_32U701_32U701_32U701_32U701_32U701_32

U701_MIC2AU701_MIC2A

U701_27

C706

C706

GND

4.7uF 0603

4.7uF 0603

CODEC_PCMADC <17>

CODEC_PCMDAC <17>

CODEC_PCMFRAM <17>

CODEC_PCMCLK <17>

AC97_INT <2>

HPOUTR <15>

HPOUTL_RECEIVER_P <15,18>

VCC_LCD <5,17,19,21>

C705

C705

C707

C707

1uF 0603

1uF 0603

100nF

100nF

GNDGND GNDGND

GND

C708 1uF 0603C708 1uF 0603

C709 1uF 0603C709 1uF 0603

C711 1uF 0603C711 1uF 0603

C710 100nFC710 100nF

C703

C703

4.7uF 0603

4.7uF 0603

2

SPEAKER_PATH

C704

C704

100nF

100nF

2

SPKL <8>

OUT4 <8>

RECEIVER_N <18>

MIC2B <15>

MIC_BIAS <15>

LINER <10>

LINEL <10>

MICCM <15>

MIC1 <15>

TV_AUDIO <11>

GND

1

VCC_IO<4,5,10,11,13,14,15,16>

21

SJ706SJ706

SW701

SW701

SW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCCSW701_VCC

PI3A3159ZCEX

PI3A3159ZCEX

4

COM

5

VCC

6

IN

SW702

SW702

PI3A3159ZCEX

PI3A3159ZCEX

4

COM

5

VCC

6

IN

SPEAKER_PATH=HIGH ----> GPRS

SPEAKER_PATH=LOW ----> SPEAKER_UB

GND

GND

3

NC

2

GND

GND

1

NO

GND

7

3

NC

2

GND

GND

1

NO

GND

7

OUT3 <18>

MICIN <10>

SPKR <18>

MICIP <10>

LS -UB: SPKL-OUT4

LS_DSC:SPKR-OUT3 & GPRS

RECEIVER : HPL-MONO_OUT

MIC:MIC1-MICCM

HP:HPOUTR-HPOUTL

HPMIC:MIC2B-MICCM

GPRSout:LINER LINEL

GPRSin:SPKR-OUT3

BT:PCM

TV:MONOIN

GIGABYTE Communication

Einstein Main Board

Title

Title

Title

Audio CodecPVT

Audio CodecPVT

Audio CodecPVT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

721Wednesday, January 18, 2006

721Wednesday, January 18, 2006

721Wednesday, January 18, 2006

of

of

1

of

1.1

1.1

1.1

Loading...

Loading...