Page 1

TITLE

5

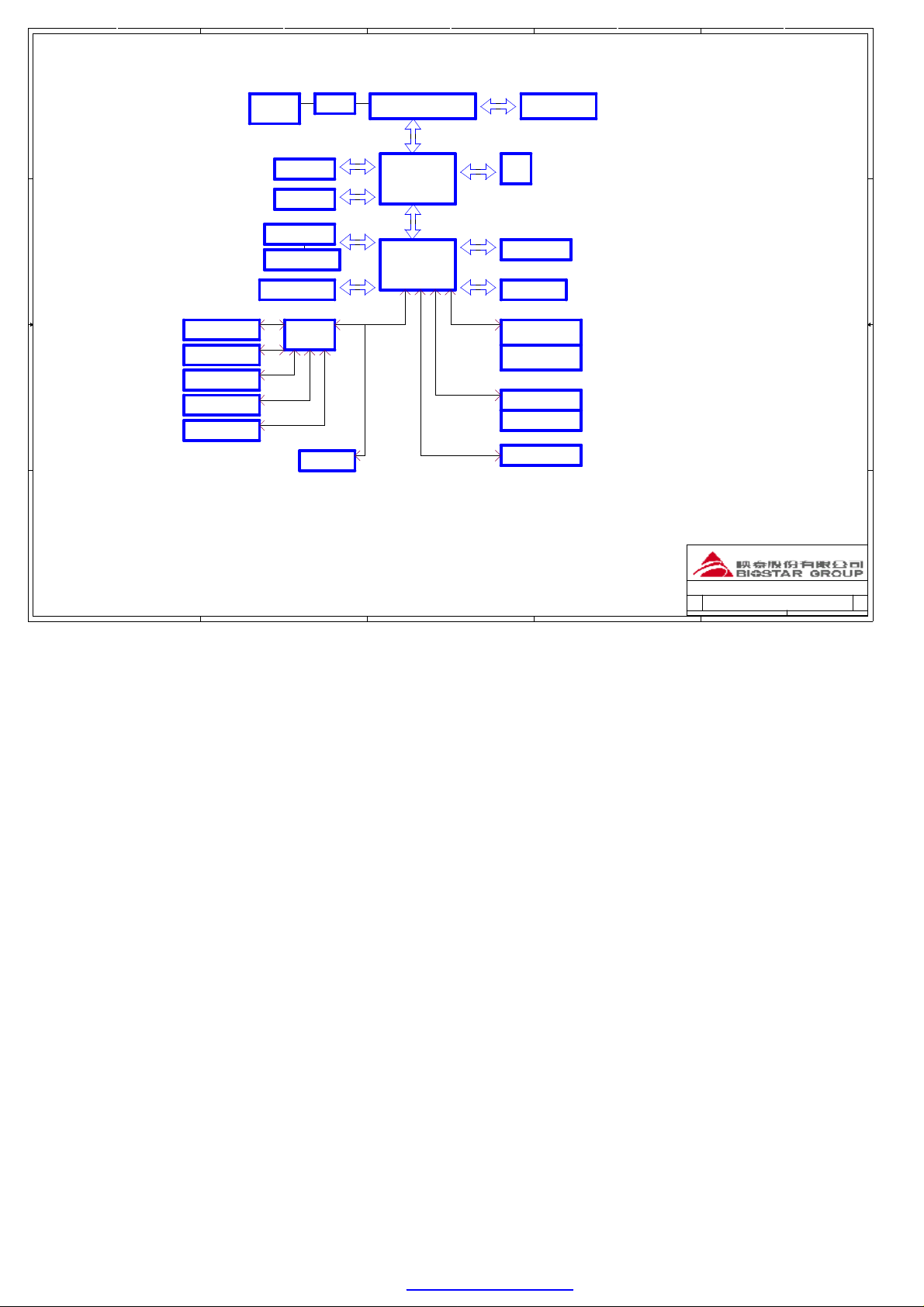

COVER SHEET

BLOCK DIAGRAM

RESET&CLK MAP

SPEC&CHANGE LIST

D D

PROCESSOR M2 940

DDR ADD/CTL/VTT TERMINATI

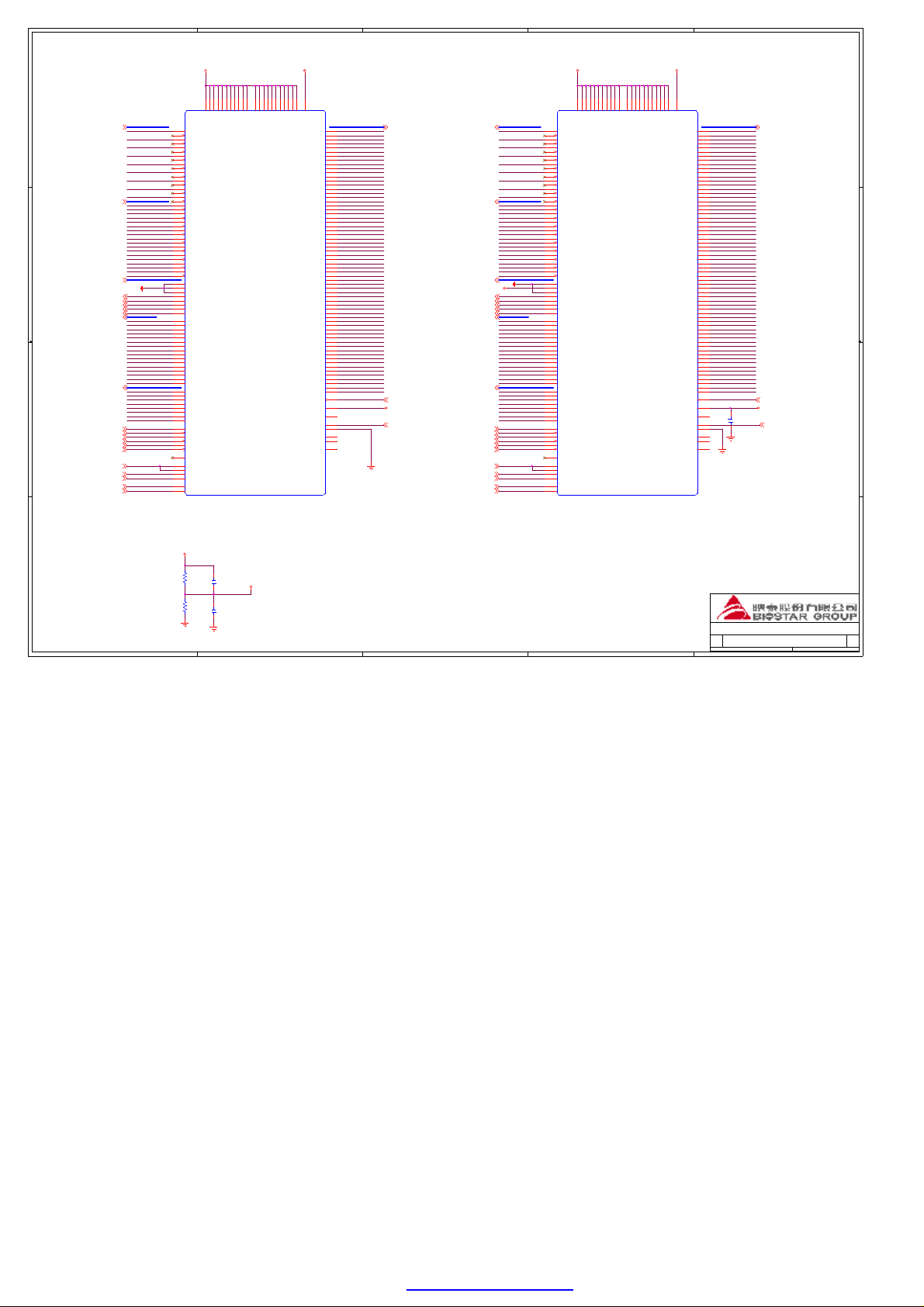

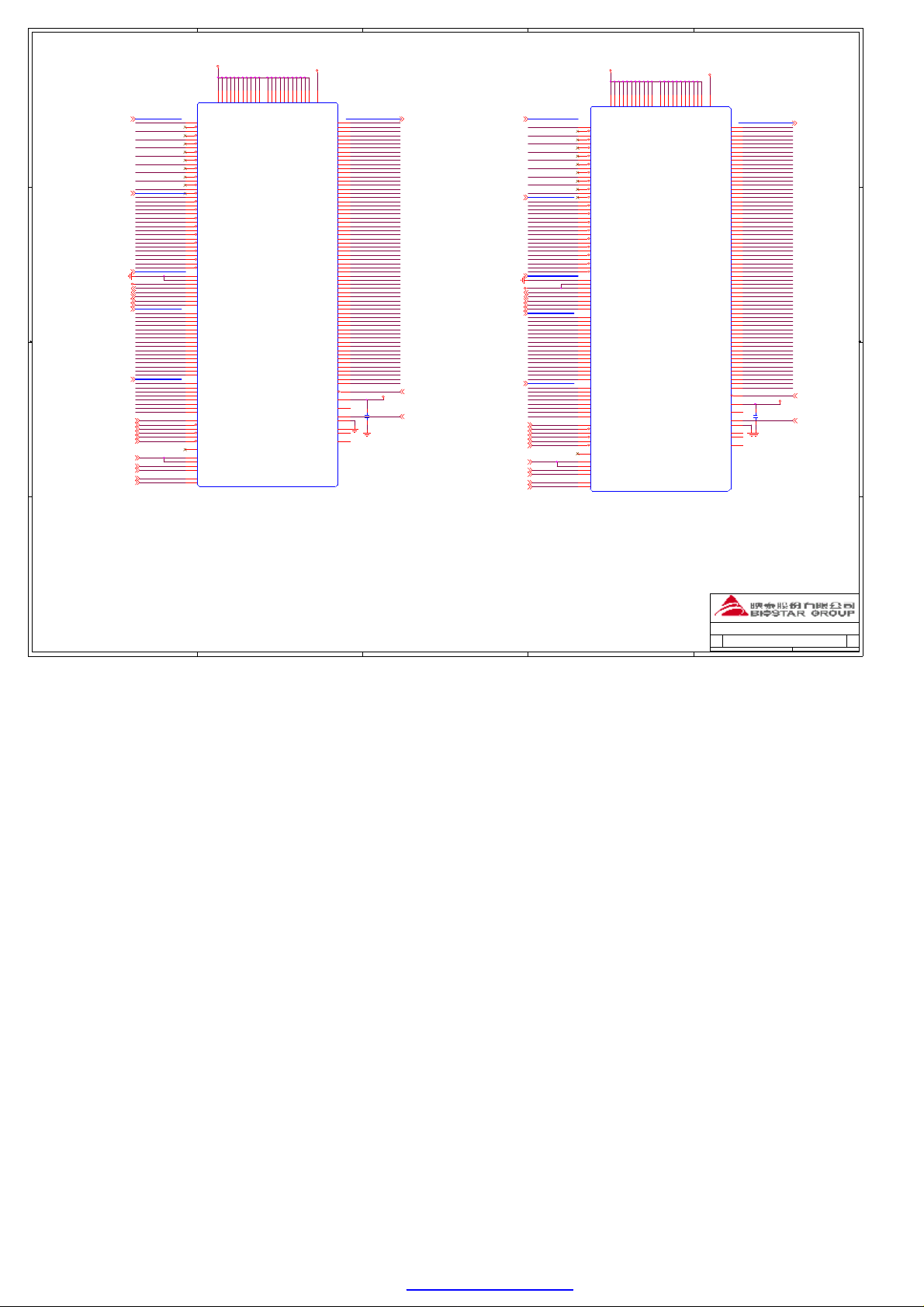

DDR 1&2

4

SHEET

3

2

1

1

2

3

4

5,6,7,8,9

10

11

CRU51-M2

DDR 3&4 12

NORTH BRIDGE(C51)

SOURTH BRIDGE(MCP51)

PCI 1&2

FRONT PANEL HEADER

PCI EXPRESS X16 & X1

C C

IDE CONN

POWER CONN & FAN CONTROL

FLOOPY / KB / MOUSE / CMOS

VGA CONN & TV OUT

USB DEVICE

SERIAL & PARALLEL

AUDIO CODEC

AUDIO CONN

VCORE POWER SUPPLY

MEM_VREG/MEM_VTT

B B

LPC SUPER IO(IT8712/8716)

FLASH ROM & H/W MON

POWER SEQUENCING

LAN 10/100

OVER VOLTAGE

C51 CORE

13,14,15

16,17,18,19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

VER:1.3

A A

Title

COVER SHEET

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

CRU51-M2

1

1.3

1 39Friday, July 07, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

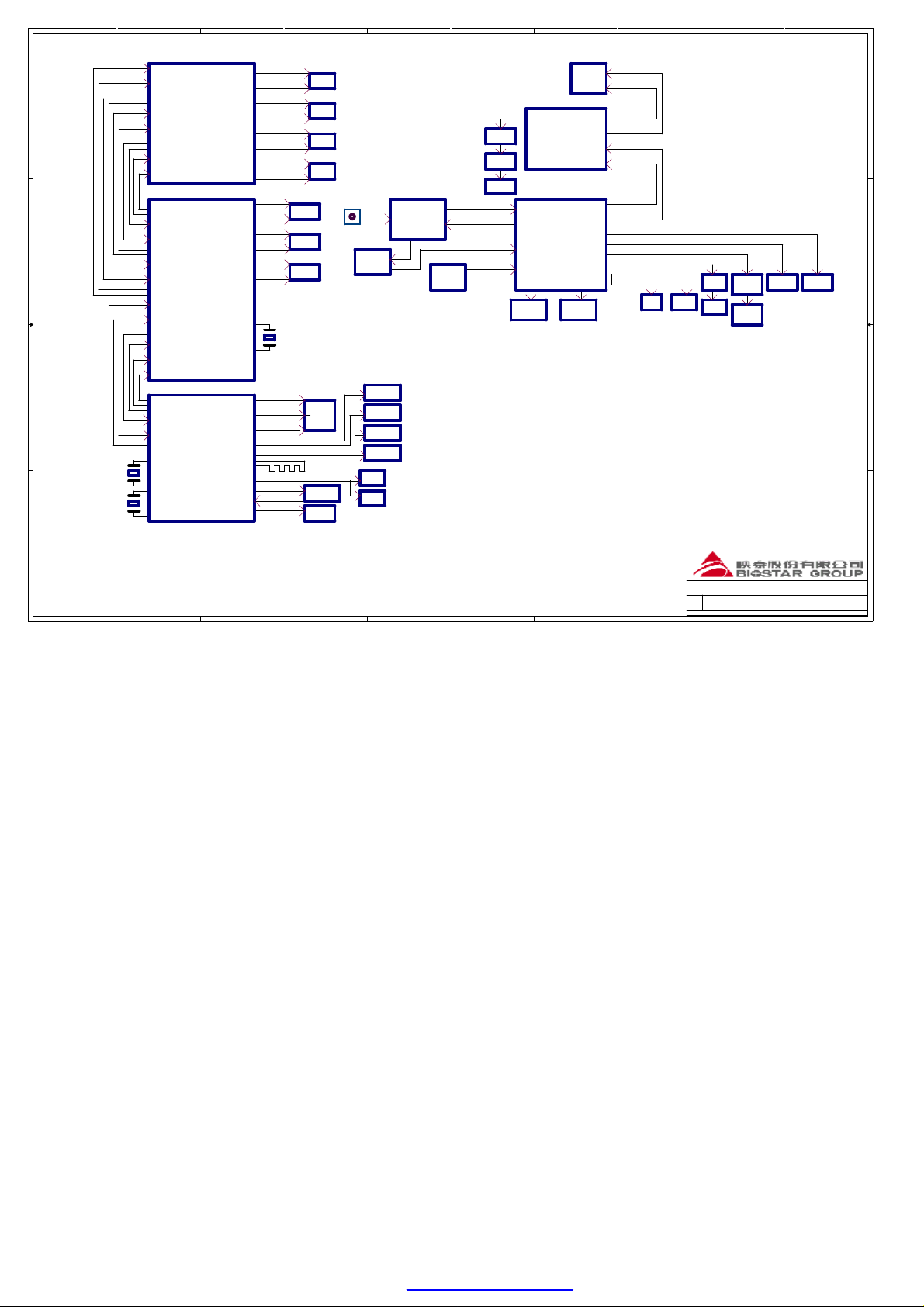

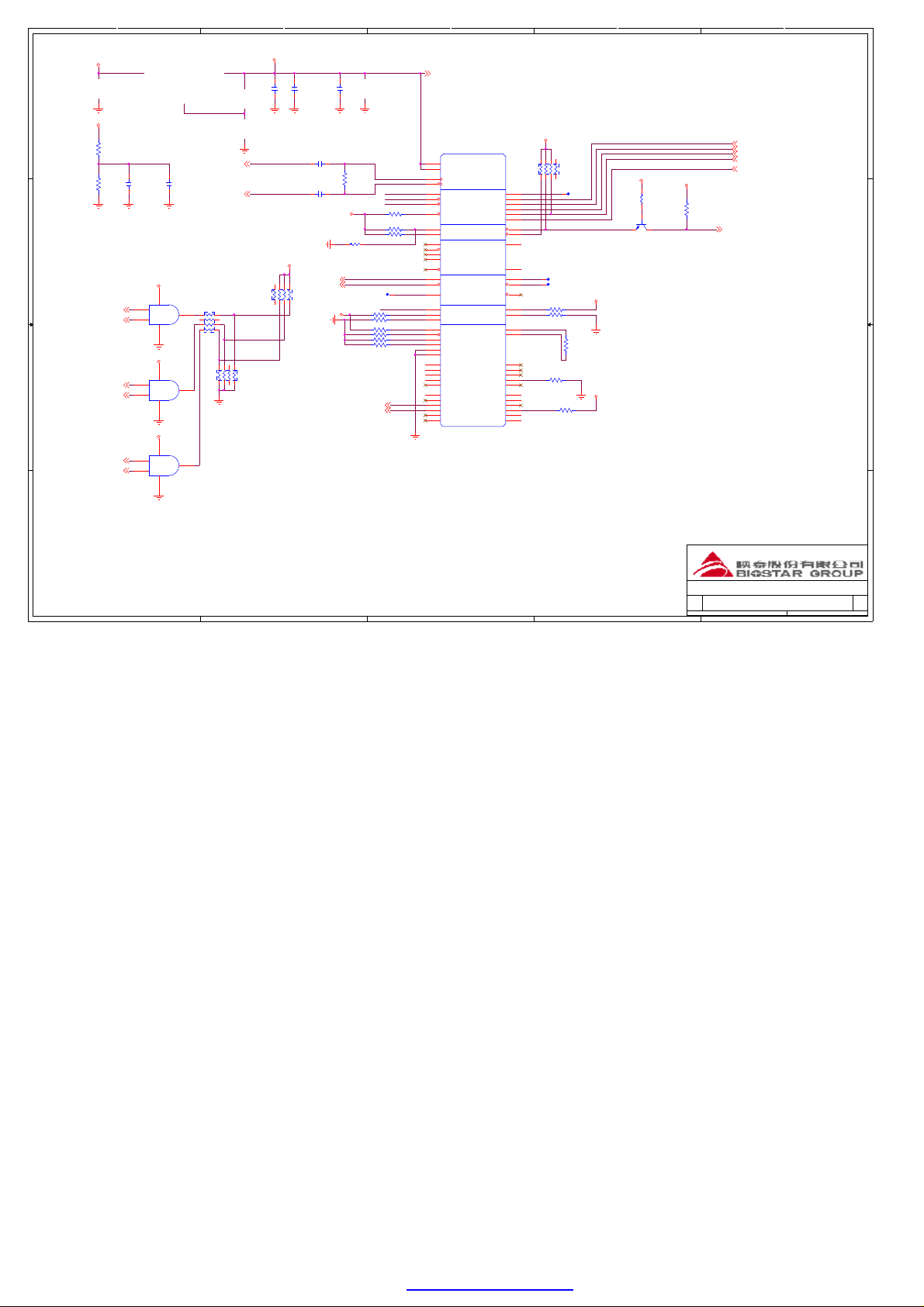

Page 2

5

4

3

2

1

D D

POWER

SUPPLY

CONN

VREG

PEX X16 (1)

PEX X1 (2)

PRIMARY IDE

C C

SECONDARY IDE

SATA CONN(X2)

SIOFLOPPY CONN

IT8712/8716

PS2/KBRD CONN

AMD M2 SOCKET 940

ATA 133

INTEGRATED SATA 1/2

LPC BUS 33MHZ

M2

HT 16X16 1GHZ

NFORCE

CRUSH 51G

468BGA

HT 8X8 800MHZ

NFORCE

MCP 51G

508BGA

MEMORY DDR2

VGA

CONN

DDR DIMM(4)

128-BIT 400/533/667/800 MHZ

PCI 33MHZ

PCI SLOT (2)

AC97

AUDIO CODEC

USB2.0 (X8)

DOUBLE STACK

USB2 PORTS 3-2

LAN RJ45

BACK PANEL CONNUSB2 PORTS 5-4

PARALLEL CONN

B B

SERIAL CONN

H/W MON

RGMII

4MB FLASH

A A

USB2 PORTS 1-0FRONT PANEL HDR

USB2 PORTS 7-6

MII/RGMII

Title

SYSTEM BLOCK

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

CRU51-M2

1

1.3

2 39Friday, July 07, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

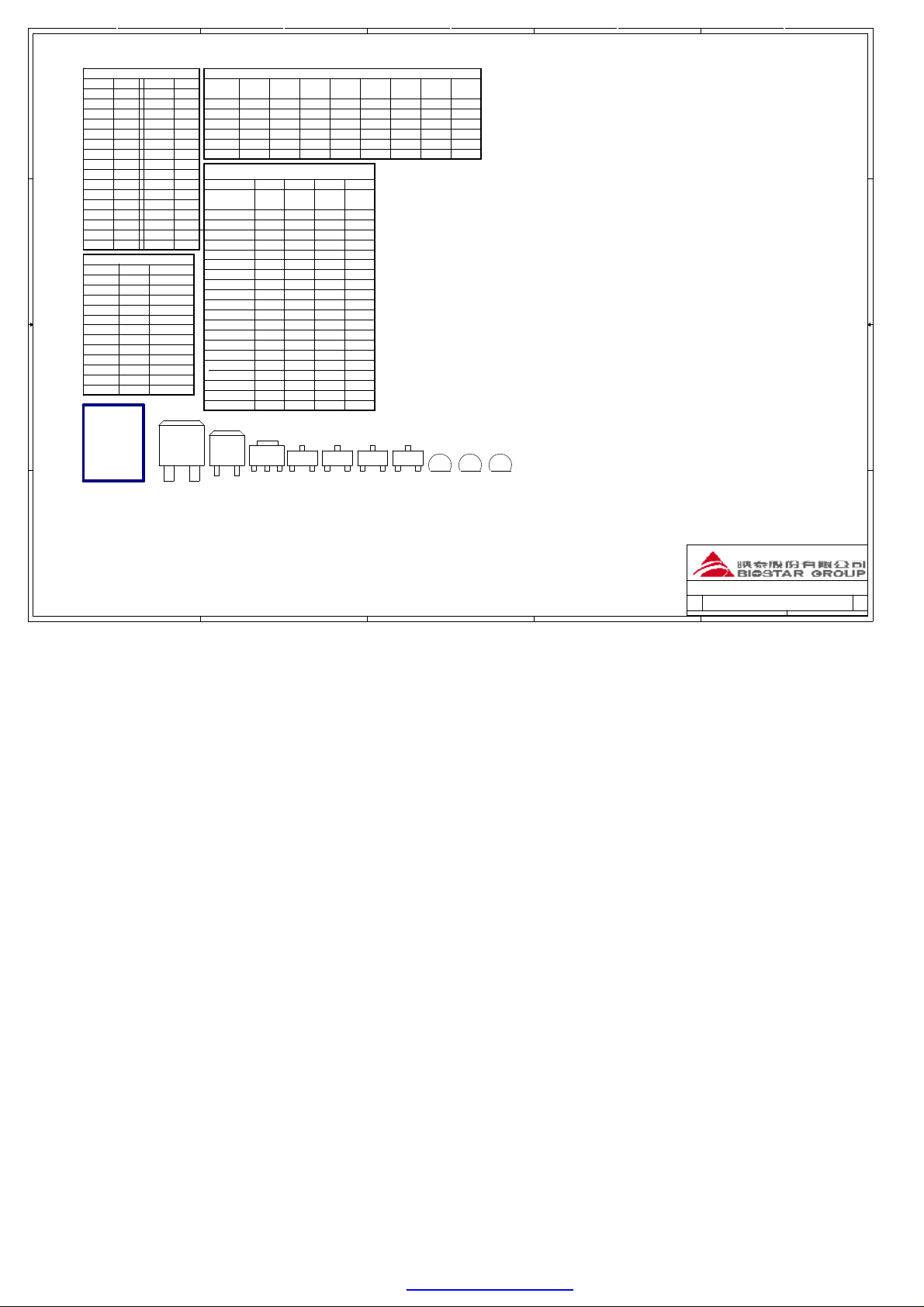

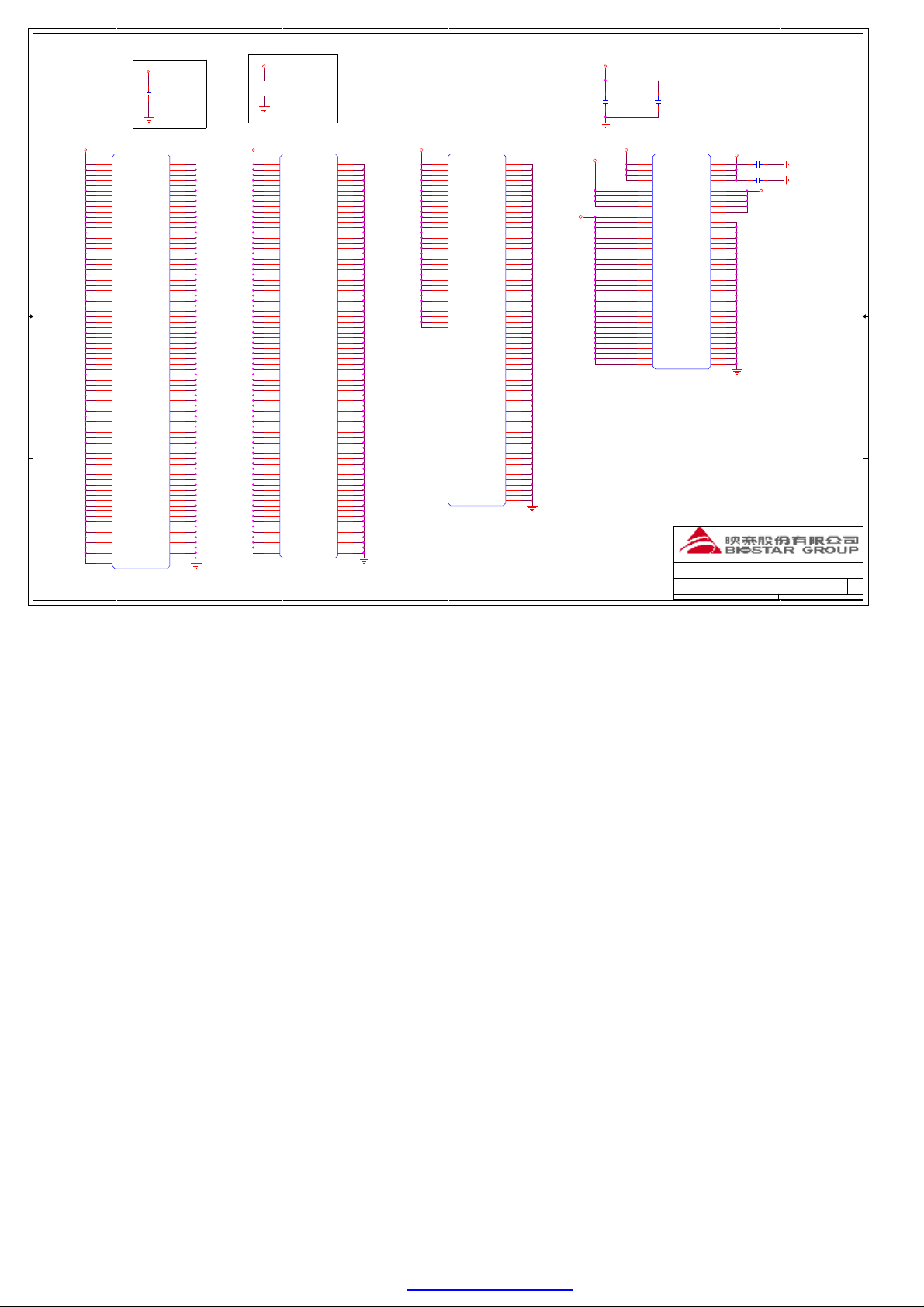

Page 3

5

M2 940 CPU

D D

CRUSH 51

C C

B B

MCP 51

32.0 KHZ

25 MHZ

HT_CPU_TXCLK0

HT_CPU_TXCLK0*

HT_CPU_RXCLK0

HT_CPU_RXCLK0*

HT_CPU_TXCLK1

HT_CPU_TXCLK1*

HT_CPU_RXCLK1

HT_CPU_RXCLK1*

CPUCLK_IN*

CPUCLK_IN

CLKOUT_200MHZ

CLKOUT_200MHZ*

HT_CPU_RXCLK1*

HT_CPU_RXCLK1

HT_CPU_TXCLK1*

HT_CPU_TXCLK1

HT_CPU_RXCLK0*

HT_CPU_RXCLK0

HT_CPU_TXCLK0*

HT_CPU_TXCLK0

HT_MCP_TXCLK0

HT_MCP_TXCLK0*

HT_MCP_RXCLK0

HT_MCP_RXCLK0*

CLKIN_25MHZ

CLKIN_200MHZ*

CLKIN_200MHZ

MCPCLK_OUT

MCPCLK_OUT*

25MHZ_CLKOUT

HT_MCP_RXCLK0*

HT_MCP_RXCLK0

HT_MCP_RXCLK0*

HT_MCP_RXCLK0

RTC_XTAL

XTAL_IN

XTAL_OUT

MEMORY_A1_CLK[2:0]

MEMORY_A1_CLK[2:0]*

MEMORY_B1_CLK[2:0]

MEMORY_B1_CLK[2:0]*

MEMORY_A2_CLK[2:0]

MEMORY_A2_CLK[2:0]*

MEMORY_B2_CLK[2:0]

MEMORY_B2_CLK[2:0]*

PE0_REFCLK

PE0_REFCLK*

PE1_REFCLK

PE1_REFCLK*

PE2_REFCLK

PE2_REFCLK*

XTAL_IN

XTAL_OUT

BUF_SIO

SUSCLK

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK_FB

LPC_CLK1

AC_97CLK

AC_BITCLK

BUF_25MHZ

4

CHANNEL A1 0-63

CHANNEL B1 64-127

CHANNEL A2 0-63

CHANNEL B2 64-127

PEX X16

PEX X1

PEX X1

/NI

CLOCK

DISTRIBUTION

27 MHZ (TV OUT ONLY)

14MHZ OR 24MHZ

32KHZ

33MHZ

33MHZ

33MHZ

AC97/AZALIA LINK

AC97 CODEC

LAN PHY

DIMM 0

DIMM 1

DIMM 2

/NI

DIMM 3

/NI

SIO

PWR SWTCH

PWR CONN

PWR GOOD

FLASH

S-IO

PS ON

PCI SLOT2

PCI SLOT1

PCI SLOT 3

/NI

PCI SLOT4

/NI

8712/8716

PWR

BUTTON*

PS ON

3

RESET MAP

PWRBT

ON*

SLP_S3*

CIRCUIT

PEX X16

PEX X1

PEX X1

/NI

PWRBTN*

SLP_S3*

POWER_GOOD

PWRGD_SB

PWR BUTTON

SLP S3*

PWRGD

PWRGD_SB

GPIO_AUX*

LAN_PHY

RESET*

CRUSH 51

PE_RESET*

MCP 51

M2 SKT 939

CPU RST*

CPU PWRGD

HT CPU PWRGD

HT CPU RST*

HT MCP PWRGD

HT MCP RST*

HT MCP RST*

HT MCP PWRGD

PCI RST0*

PCI RST1*

PCI RST2*

PCI RST3*

LPC_RST*PWRGD SB

AC_RESET*

AUDIO_PHY

RESET*

2

CPU_RST*

CPU_PWRGD

HT_CPU_PWRGD

HT_CPU_RST*

HT_MCP_PWRGD

HT_MCP_RST*

HT_MCP_RST*

HT_MCP_PWRGD

PCIRST_SLOT1*

PCIRST_SLOT2*

PCIRST_SLOT3-4*

PCIRST_IDE*

LPCRST_FLASH*

LPCRST_SIO*

SIO FLASH

PRI IDE

SEC IDE

PCI SLOT 3

/NI

PCI SLOT4

/NI

1

PCI SLOT2 PCI SLOT1

A A

Title

RESET&CLOCK MAP

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

CRU51-M2

1

1.3

3 39Friday, July 07, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

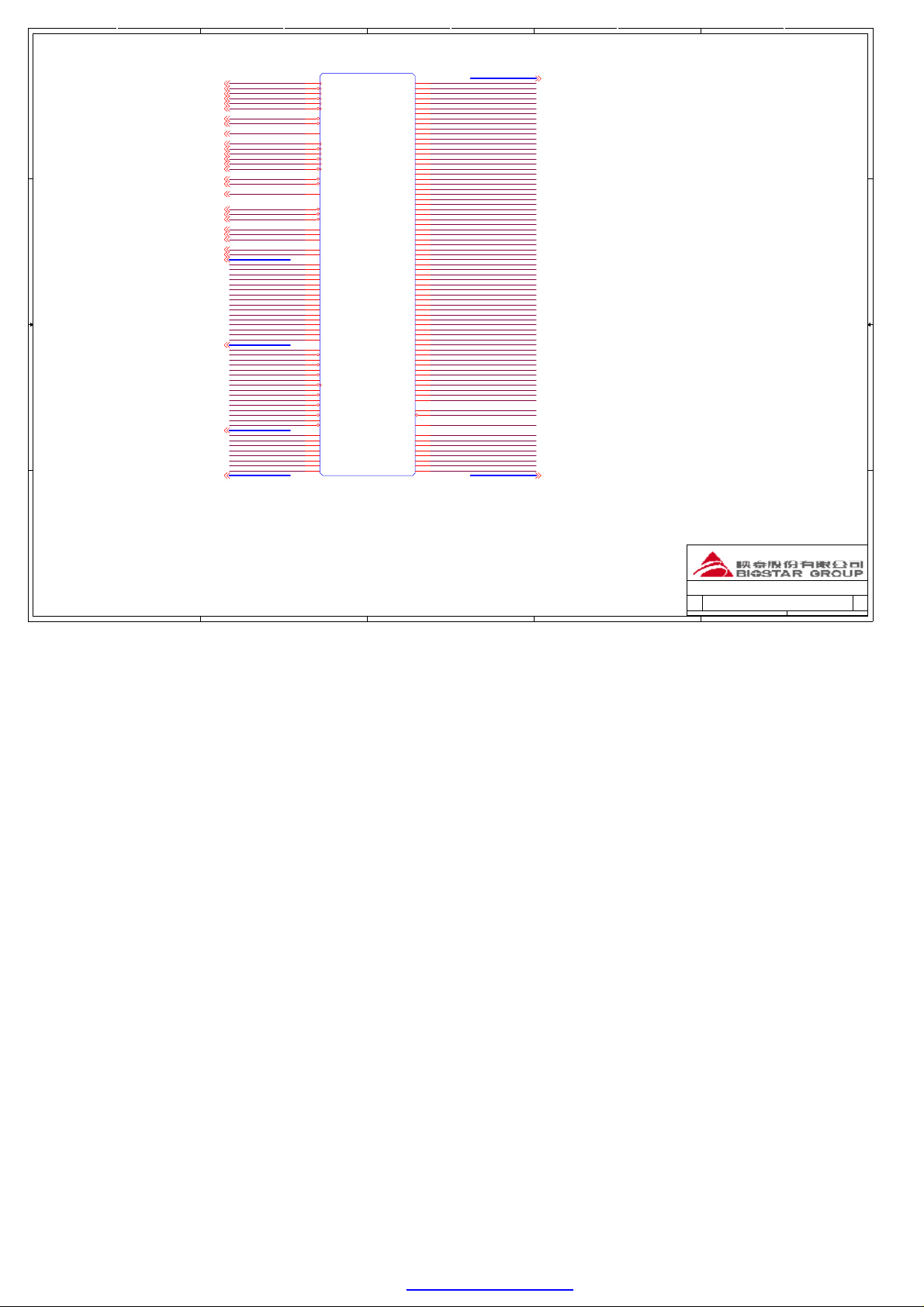

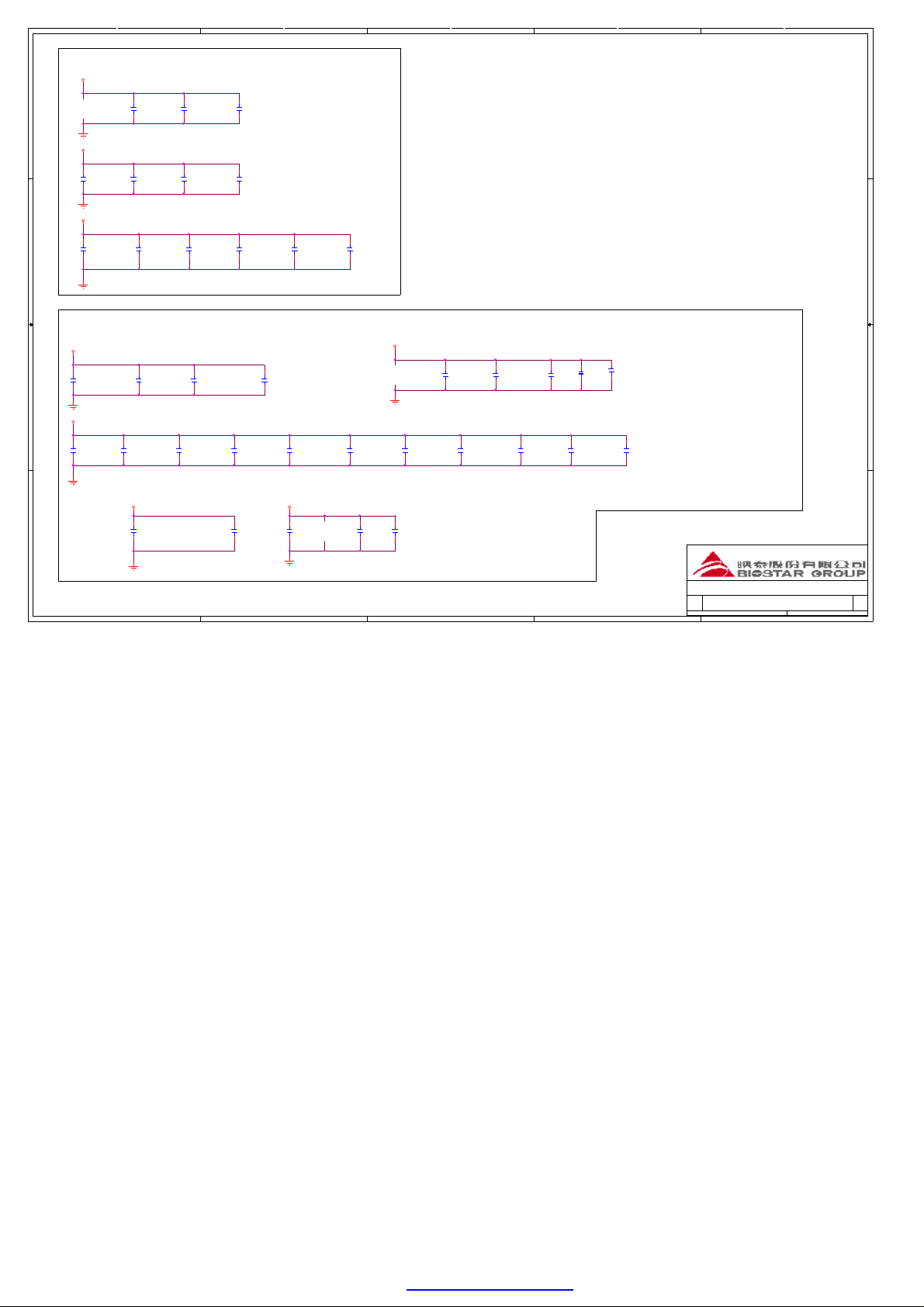

Page 4

5

4

3

2

1

CPU VID TABLE

VDD

VID [4..0]

D D

C C

B B

0X00000

0X00010

0X00011

0X00100

0X00101

0X00110

0X00111

0X01000

0X01001

0X01010 1.300V

0X01011

0X01100

0X01101

0X01110

0X01111

SMBUS ADDRESS MAP

DEVICE

SLOT

DIMM 0

DIMM 1

DIMM 2

DIMM 3

SIO

PCI SLOT 1 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

22U/25DE 5*7 mm

100U/16DE

220U/10DE

470U/16DE

1000U/10DE

1500U/16DE

3300U/25DE

VID [4..0]

0X10000

1.550V

0X10001

1.525V

1.500V

0X10010

0X10011

1.475V

0X10100

1.450V

0X10101

1.425V

1.400V

0X10110

1.375V

0X10111

1.350V

0X11000

0X11001

1.325V

0X11010

1.275V

0X11011

1.250V

0X11100

1.225V

1.200V

0X11110

0X11111

1.175V

SMBUS # ADDRESS

0

0

0

1

1

1

1

ADDC BUS

BDDC BUS

6.3*11 mm

6.3*11 mm

8*11 mm

8*14 mm

10*25 mm

10*25 mm

1010 000 = 0X500

1010 001 = 0X51

1010 010 = 0X52

1010 011 = 0X53

0101 101 = 0X2D

ARP

ARP

ARP

ARP

?

?

G

PCI INTERRUPT/IDSEL MAP

VDD

BACK PANEL

1.150V

SLOT

1.125V0X00001

1

1.100V

2

1.075V

3

1.050V

4

1.025V

5

1.000V

0.975V

PCI DEVICE MAP

0.950V

0.925V

DEVICE

0.900V

MCP51

0.875V

0.850V

MAC /MAC

0.825V0X11101

PCI-PCI BRIDGE

0.800V

SATA1

OFF

SATA0

IDE

MODEM CODEC

AUDIO CODEC

USB 2.0

USB 1.1

SHAPE TRIM

LDT

SMBUS2

LEGACY SLAVE

LPC

LOGICAL PCI BUS

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

PCI SLOT 5

D

D

G

TO-263

TO-252

20N03

PHB55N03

TM3055TL-S

90N02

PHD55N03

PCI BUS#

01

01

01

01

01

016

S

DEVICE#

0X05

0X06

0X07

0X08

0X09

0X0A

PCI BUS# FUNCTION

MCP51

LOGICAL

PCI BUS 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

O

I

O

A

SOT-223

AMS1117

IDSEL PIN

22

24

IDSEL PIN

0X01-0X0F

- -

0

XA

0

X9

0

X8

0

X8

0

X6

X4

1

X4

0

X2

1

X2

0

X1

2

X0

0

X1

1

?

?

X1

0

?

?

A

R E

C

G

SOT-23

SOT-23

2N7002

SI2303S

SI2301S

PCI SLOT

INTA*

P_INTY*

P_INTW*

D

DEVICE ID

- -

0X56/57

0X005C

0X0055

0X0054

0X0053

0X0058

0X0059

0X005B

0X005A

0X005F

0X005E

0X0052

0X00D3

0X0050/51

?

S

PCI SLOT

PCI SLOT

INTB*

INTC*

P_INTZ*

P_INTW*

P_INTX*

P_INTY*

C

B

A

SOT-23

BAT54CKLM431 2N2222ALM431

2N3904

2N3906

BAT54S 78L05-DS2N2097A

MMBT2907A

2N2222A

PCI SLOT

INTD*

P_INTX*

P_INTZ*

KA

O

I

G

TO-92SOT-23

LM432

CRU51-M9

1. CPU --- AMD Socket 939(3-Phase Power)

REQ/GNT

2. CHIPSET --- NF C51G IGP + NF MCP51

3. MEMORY ---Dual Channel DDR SDRAM X 2 (Max. 2GB)

1/1

4. SLOTS --- PEX X16 (x1),PEX X1 (x1),PCI (x2)

2/2

5. CODEC --- Realtek ALC655 5.1 Channel Audio

6. LAN PHY --- RTL8201

7. LPC/SIO --- IT8712F

8. SATA -- INTEGRATED(x2)

9. PCB Size --- 24.4cmx24.4cm, 4-Layer

CHANGE LIST

1.Q37 2N7002 CHANGE 2N3904 FOR POWER_SB TIMING

2.ADD C398 10U/10V FOR POWER_SB TIMING

3.PHY RST FOR S3 WAKE CAN WORK R134,C187 /NI, R136 0

4.DEL VID[0..5] TO MCP51.IT8712

5.ADD C45 1U/10V , R16 10K--> 100K FOR +2.6V

6.ADD U5,R83,R82(22) R84,R81(0)/NI FOR ON BOARD VGA PLUG INTO THE MONITOR CAN'T BOOT UP

7.ADD HEATSINK FOR S/B

8.R262.R264 20K --> 56K FOR KBRST,A20GATE BECOMING 3.3V

9.DEL R217,R222 SLEEPBTNJ CHANGE FROM S/B EXSMI PIN. R206 MOVE NEAR S/B

10.ADD OV-->R222,R281,R282,R283 /NI,R217

11.ADD LED-->D14,D15,D16,D17,R64,R66,R67,R74,R108,R149, SW-->PWRSW1,RSTSW2,R62,R63

12.DEL CT31,PWRGD,C3,C4,C6,C7,C13,CT5,CT19,C209,C210,C230,C211,C212,C213,C227,C228,C229,C17(BOM)

13.AR19 0 /NI FOR AUDIO CLK TO 24Mhz

14.ADD FOR EMI BC92,AR23,AL8,FB24

15.FOR EMI C9,C10,C12,C14-->47P

C8,C193,C196,AC32,C331-->104P

C395,C394,C393,C392,C391,C390,C389,C388,C383C387,C382,C386,C381,C385,C378,C384,C380-->100P

C116,C119,C123-->33P

AR22-->0

C343-->103P

C342-->102P

C336-->10P H1,H2-->COMMOM CHOKE

16.DEL BOM FOR EMI FB6 /NI

5.CHANGE HEATSINK FOR N/B TO SHORT

B

EC

B

C

E

TO-92

TO-92

HSD882-D

A A

Title

SPEC&CHANGE LIST

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

CRU51-M2

1

1.3

4 39Friday, July 07, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 5

5

CPU1A

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

HYPERTRANSPORT

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

HTCPU_UPCLK113

HTCPU_UPCLK1_13

HTCPU_UPCLK013

HTCPU_UPCLK0_13

D D

HTCPU_UPCNTL_13

C C

HTCPU_UP[15..0]13

HTCPU_UP_[15..0]13 HTCPU_DWN_[15..0] 13

B B

HTCPU_UPCLK1

HTCPU_UPCLK1_

HTCPU_UPCLK0

HTCPU_UPCLK0_

R34 49.9 1%

+1.2V_HT

R35 49.9 1%

HTCPU_UPCNTL

HTCPU_UPCNTL_

HTCPU_UP15

HTCPU_UP_15

HTCPU_UP14

HTCPU_UP_14

HTCPU_UP13

HTCPU_UP_13

HTCPU_UP12

HTCPU_UP_12

HTCPU_UP11

HTCPU_UP_11

HTCPU_UP10

HTCPU_UP_10

HTCPU_UP9

HTCPU_UP_9

HTCPU_UP8

HTCPU_UP_8

HTCPU_UP7

HTCPU_UP_7

HTCPU_UP6

HTCPU_UP_6

HTCPU_UP5

HTCPU_UP_5

HTCPU_UP4

HTCPU_UP_4

HTCPU_UP3

HTCPU_UP_3

HTCPU_UP2

HTCPU_UP_2

HTCPU_UP1

HTCPU_UP_1 HTCPU_DWN_1

HTCPU_UP0

HTCPU_UP_0

HTCPU_UP[15..0]

HTCPU_UP_[15..0] HTCPU_DWN_[15..0]

HTCPU_DWNCLK1

AD5

HTCPU_DWNCLK1_

AD4

HTCPU_DWNCLK0

AD1

HTCPU_DWNCLK0_

AC1

Y6

W6

HTCPU_DWNCNTL

W2

HTCPU_DWNCNTL_

W3

HTCPU_DWN15

Y5

HTCPU_DWN_15

Y4

HTCPU_DWN14

AB6

HTCPU_DWN_14

AA6

HTCPU_DWN13

AB5

HTCPU_DWN_13

AB4

HTCPU_DWN12

AD6

HTCPU_DWN_12

AC6

HTCPU_DWN11

AF6

HTCPU_DWN_11

AE6

HTCPU_DWN10

AF5

HTCPU_DWN_10

AF4

HTCPU_DWN9

AH6

HTCPU_DWN_9

AG6

HTCPU_DWN8

AH5

HTCPU_DWN_8

AH4

HTCPU_DWN7

Y1

HTCPU_DWN_7

W1

HTCPU_DWN6

AA2

HTCPU_DWN_6

AA3

HTCPU_DWN5

AB1

HTCPU_DWN_5

AA1

HTCPU_DWN4

AC2

HTCPU_DWN_4

AC3

HTCPU_DWN3

AE2

HTCPU_DWN_3

AE3

HTCPU_DWN2

AF1

HTCPU_DWN_2

AE1

HTCPU_DWN1

AG2

AG3

HTCPU_DWN0

AH1

HTCPU_DWN_0

AG1

HTCPU_DWN[15..0]

4

HTCPU_DWNCLK1 13

HTCPU_DWNCLK1_ 13

HTCPU_DWNCLK0 13

HTCPU_DWNCLK0_ 13

HTCPU_DWNCNTL 13HTCPU_UPCNTL13

HTCPU_DWNCNTL_ 13

HTCPU_DWN[15..0] 13

3

CPU1B

MEMORY INTERFACE A

MEM_MA0_CLK_H210,11

MEM_MA0_CLK_L210,11

MEM_MA0_CLK_H110,11

MEM_MA0_CLK_L110,11

MEM_MA0_CLK_H010,11

MEM_MA0_CLK_L010,11

MEM_MA0_CS_L110,11

MEM_MA0_CS_L010,11

MEM_MA0_ODT010,11

MEM_MA1_CLK_H210,11

MEM_MA1_CLK_L210,11

MEM_MA1_CLK_H110,11

MEM_MA1_CLK_L110,11

MEM_MA1_CLK_H010,11

MEM_MA1_CLK_L010,11

MEM_MA1_CS_L110,11

MEM_MA1_CS_L010,11

MEM_MA1_ODT010,11

MEM_MA_CAS_L10,11

MEM_MA_WE_L10,11

MEM_MA_RAS_L10,11

MEM_MA_BANK210,11

MEM_MA_BANK110,11

MEM_MA_BANK010,11

MEM_MA_CKE110,11

MEM_MA_CKE010,11

MEM_MA_ADD[15..0]10,11

MEM_MA_DQS_H[8..0]11

MEM_MA_DQS_L[8..0]11

MEM_MA_DM[8..0]11

MEM_MA_ADD[15..0]

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0 MEM_MA_DM8

MEM_MA_DQS_L[8..0]

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DM[8..0]

AG21

AG20

G19

H19

U27

U26

AC25

AA24

AC28

AE20

AE19

G20

G21

W27

AD27

AA25

AC27

AB25

AB27

AA26

N25

AA27

M25

M27

N24

AC26

N26

N27

R24

R25

R26

R27

U25

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

G15

AF15

AF19

AJ25

AH29

H15

V27

Y27

L27

P25

Y25

P27

T25

T27

E19

F19

F15

B29

E24

E18

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

2

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

MEM_MA_DATA[0..63]

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

J25

MEM_MA_CHECK[7..0]

MEM_MA_CHECK7

K25

MEM_MA_CHECK6

J26

MEM_MA_CHECK5

G28

MEM_MA_CHECK4

G27

MEM_MA_CHECK3

L24

MEM_MA_CHECK2

K27

MEM_MA_CHECK1

H29

MEM_MA_CHECK0

H27

1

MEM_MA_DATA[0..63] 11

MEM_MA_CHECK[7..0] 11

A A

Title

M2 HT

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

CRU51-M2

1

1.3

5 39Friday, July 07, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 6

5

4

3

2

1

CPU1C

MEMORY INTERFACE B

AC31

AD29

AD31

AC29

AC30

AH17

AJ19

AK19

A18

A19

U31

U30

AE30

AL19

AL18

C19

D19

W29

W28

AE29

AB31

AB29

N31

AA31

AA28

M31

M29

N28

N29

AE31

N30

P29

AA29

P31

R29

R28

R31

R30

T31

T29

U29

U28

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AJ23

AK29

C30

A23

B17

B13

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MEM_MB0_CLK_H210,12

MEM_MB0_CLK_L210,12

MEM_MB0_CLK_H110,12

MEM_MB0_CLK_L110,12

D D

C C

B B

MEM_MB0_CLK_H010,12

MEM_MB0_CLK_L010,12

MEM_MB0_CS_L110,12

MEM_MB0_CS_L010,12

MEM_MB0_ODT010,12

MEM_MB1_CLK_H210,12

MEM_MB1_CLK_L210,12

MEM_MB1_CLK_H110,12

MEM_MB1_CLK_L110,12

MEM_MB1_CLK_H010,12

MEM_MB1_CLK_L010,12

MEM_MB1_CS_L110,12

MEM_MB1_CS_L010,12

MEM_MB1_ODT010,12

MEM_MB_CAS_L10,12

MEM_MB_WE_L10,12

MEM_MB_RAS_L10,12

MEM_MB_BANK210,12

MEM_MB_BANK110,12

MEM_MB_BANK010,12

MEM_MB_CKE110,12

MEM_MB_CKE010,12

MEM_MB_ADD[15..0]10,12

MEM_MB_DQS_H[8..0]12

MEM_MB_DQS_L[8..0]12

MEM_MB_ADD[15..0]

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_L[8..0]

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DM8

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DATA[0..63]

MEM_MB_CHECK[7..0]MEM_MB_DM[8..0]

MEM_MB_DATA[0..63] 12

MEM_MB_CHECK[7..0] 12MEM_MB_DM[8..0]12

A A

Title

M2 CNTL/STRAPS

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

CRU51-M2

1

1.3

6 39Friday, July 07, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 7

5

+5V

D D

C C

B B

+1.8V_SUS

HTCPU_RST_13

MCP51_PWRGD18,35

HTCPU_PWRGD13

MCP51_PWRGD18,35

HTCPU_STOP_13

MCP51_PWRGD18,35

BR1

16.9 1%

CPU_M_VREFF

1 2

12

12

BR2

BC1

16.9 1%

1UF 10V Y5V

+5V_STBY

U1A

SN74ACT08

1

2

+5V_STBY

U1B

SN74ACT08

4

5

+5V_STBY

U1C

SN74ACT08

9

10

147

147

147

12

BC3

0.1UF 25V Y5V

CPU_VDDA_ADJ

3

6

8

RN2

1 2

3 4

5 6

7 8

100 8P4R

CPU_CLK13

CPU_CLK_13

123456

78

+2.5V

CPU_CLK

CPU_CLK*

HTCPU_RST_R

HTCPU_PWRGDR

HTCPU_STOP_R

RN3

56 8P4R

4

12

12

C28

C21

100UF 6.3V D TAN /NI

1UF 16V 0805 Y5V

ROUTE AS DIF 5/5/5/20

LAYOUT: PLACE 169 OHM WITHIN

600mils OF CPU

AND TRACE TO AC CAPS LESS

THAN 1250mil

C30

12

3900P 50V X7R

C29

12

3900P 50V X7R

+1.8V_SUS

R56 300

+1.8V_SUS

CPU_CORE_FB31

CPU_CORE_FB_31

RN4

330 8P4R

1 2

3 4

5 6

7 8

+1.8V_SUS

12

C34

1UF 16V 0805 Y5V

R28

169 1%

1 2

R53 1K 1%1 2

R54 300 /NI

1 2

R55 300 /NI1 2

CPU_SIC

CPU_CORE_FB

CPU_CORE_FB-

TP_VDDIOSENSE1 TP /NI

CPU_M_VREFF

R50 39.2 1%1 2

R59 39.2 1%

1 2

R27 510

1 2

R26 5101 2

R23 300

1 2

R24 3001 2

CPU_THERMDC33,34

CPU_THERMDA33

3

2P5V_PWR 13,14,15,38

CPU1D

MISC

C10

VDDA1

D10

VDDA2

A8

CLKIN_H

B8

C9

D8

C7

AL3

AL6

AK6

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

PSI_L

D2

D1

C1

E3

E2

E1

AK7

AL7

AK10

TDO

B6

AK11

AL11

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

HTCPU_PWRGDR

HTCPU_STOP_R

HTCPU_RST_R VID3

2

+1.8V_SUS

RN15

330 8P4R

1 2

3 4

5 6

7 8

TP /NI

VID1

VID4

VID2

VID1

VID0

CPU_THERMTRIP

TP /NI

TP_VDDIOFB1

TP_VDDIOFB_1

TP /NI

R32 44.2 1%

12

R31 44.2 1%12

FBCLKOUT

FBCLKOUT*

R25

80.6 1%

8/5/8/20

1 2

LAYOUT: ROUTE 80 OHM DIFF IMPEDENCE

LAYOUT: PLACE WITHIN 1 INCH OF CPU

R58 300

1 2

R51 300

1 2

+1.2V_HT

+1.8V_SUS

+1.8V_SUS

Q11

2N3904 SOT23

R21

1K 1%

+3.3V_DUAL

12

R17

10K 1%

K8_VID4 31

K8_VID3 31

K8_VID2 31

K8_VID1 31

K8_VID0 31

CPU_THERMTRIP_ 16

1

A A

Title

M2 DDR MEM 0-63

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

CRU51-M2

1

1.3

7 39Tuesday, December 26, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 8

5

4

3

2

1

+V_CPU

ADD FOR EMI

PLACE NEAR C80

BC2

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD150

VDD151

5

CPU1F

1UF 10V Y5V

VDD1

A3

VSS1

A7

VSS2

A9

VSS3

A11

VSS4

AA4

VSS5

AA5

VSS6

AA7

VSS7

AA9

VSS8

AA11

VSS9

AA13

VSS10

AA15

VSS11

AA17

VSS12

AA19

VSS13

AA21

VSS14

AA23

VSS15

AB2

VSS16

AB3

VSS17

AB8

VSS18

AB10

VSS19

AB12

VSS20

AB14

VSS21

AB16

VSS22

AB18

VSS23

AB20

VSS24

AB22

VSS25

AC7

VSS26

AC9

VSS27

AC11

VSS28

AC13

VSS29

AC15

VSS30

AC17

VSS31

AC19

VSS32

AC21

VSS33

AC23

VSS34

AD8

VSS35

AD10

VSS36

AD12

VSS37

AD14

VSS38

AD16

VSS39

AD20

VSS40

AD22

VSS41

AD24

VSS42

AE4

VSS43

AE5

VSS44

AE9

VSS45

AE11

VSS46

AF2

VSS47

AF3

VSS48

AF8

VSS49

AF10

VSS50

AF12

VSS51

AF14

VSS52

AF16

VSS53

AF18

VSS54

AF20

VSS55

AF22

VSS56

AF24

VSS57

AF26

VSS58

AF28

VSS59

AG10

VSS61

AG11

VSS62

AH14

VSS63

AH16

VSS64

AH18

VSS65

AH20

VSS66

AH22

VSS67

AH24

VSS68

AH26

VSS69

AH28

VSS70

AH30

VSS71

AK2

VSS72

AK14

VSS73

AK16

VSS74

AK18

VSS75

Y14

VSS240

Y16

VSS241

D D

+V_CPU +V_CPU

A4

A6

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

AC8

AC10

AD2

C C

B B

A A

AD3

AD7

AD9

AE10

AF7

AF9

AG4

AG5

AG7

AH2

AH3

B3

B5

B7

C2

C4

C6

C8

D3

D5

D7

D9

E4

E6

E8

E10

F5

F7

F9

F11

G6

G8

G10

G12

H7

H11

H23

J8

J12

J14

J16

J18

J20

J22

J24

K7

K9

K11

K13

K15

K17

K19

K21

K23

L4

L5

L8

L10

L12

Y17

Y19

+1.8V_SUS

PLACE AT CPU SOCKET SOLDER SIDE

CPU1G

VDD2

L14

L16

L18

M2

M3

M7

M9

M11

M13

M15

M17

M19

N8

N10

N12

N14

N16

N18

P7

P9

P11

P13

P15

P17

P19

R4

R5

R8

R10

R12

R14

R16

R18

R20

T2

T3

T7

T9

T11

T13

T15

T17

T19

T21

U8

U10

U12

U14

U16

U18

U20

V9

V11

V13

V15

V17

V19

V21

W4

W5

W8

W10

W12

W14

W16

W18

W20

Y2

Y3

Y7

Y9

Y11

Y13

Y15

Y21

4

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

+V_CPU

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

CPU1H

VDD3

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

AA20

VDD1

AA22

VDD2

AB13

VDD3

AB15

VDD4

AB17

VDD5

AB19

VDD6

AB21

VDD7

AB23

VDD8

AC12

VDD9

AC14

VDD10

AC16

VDD11

AC18

VDD12

AC20

VDD13

AC22

VDD14

AD11

VDD15

AD23

VDD16

AE12

VDD17

AF11

VDD18

L20

VDD19

L22

VDD20

M21

VDD21

M23

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

W22

VDD31

Y23

VDD32

3

+1.8V_SUS

+1.2V_HT

+0.9V_SUS

C101

1UF 16V 0805 Y5V

1 2

+1.2V_HT

2

C107

1UF 16V 0805 Y5V

1 2

CPU1I

VDDIO

AJ4

VLDT_A1

AJ3

VLDT_A2

AJ2

VLDT_A3

AJ1

VLDT_A4

D12

VTT1

C12

VTT2

B12

VTT3

A12

VTT4

AB24

VDDIO1

AB26

VDDIO2

AB28

VDDIO3

AB30

VDDIO4

AC24

VDDIO5

AD26

VDDIO6

AD28

VDDIO7

AD30

VDDIO8

AF30

VDDIO29

M24

VDDIO9

M26

VDDIO10

M28

VDDIO11

M30

VDDIO12

P24

VDDIO13

P26

VDDIO14

P28

VDDIO15

P30

VDDIO16

T24

VDDIO17

T26

VDDIO18

T28

VDDIO19

T30

VDDIO20

V25

VDDIO21

V26

VDDIO22

V28

VDDIO23

V30

VDDIO24

Y24

VDDIO25

Y26

VDDIO26

Y28

VDDIO27

Y29

VDDIO28

Title

Size Document Number Rev

Custom

Date: Sheet of

+1.2V_HT_CPU

1 2

H6

VLDT_B1

H5

VLDT_B2

H2

VLDT_B3

H1

VLDT_B4

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VTT5

VTT6

VTT7

VTT8

VTT9

1 2

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

M2 DDR MEM 64-127

+0.9V_SUS

CRU51-M2

1UF 16V 0805 Y5VC43

1UF 16V 0805 Y5VC44

8 39Friday, July 07, 2006

1

1.3

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 9

5

DECOUPLING BETWEEN PROCESSOR AND DIMMS

PLACE AS CLOSE TO PROCESSOR AS

POSSIBLE

+1.8V_SUS

C67

0.1UF 25V Y5V

C22

1UF 10V Y5V /NI

12

12

D D

+0.9V_SUS

12

+0.9V_SUS

12

C C

C12

1UF 16V 0805 Y5V /NI

C19

1UF 16V 0805 Y5V /NI

12

C111

1UF 10V Y5V /NI

12

BC14

10UF 10V 0805 Y5V

12

C125

1UF 16V 0805 Y5V

12

C25

0.1UF 25V Y5V

12

BC11

1UF 16V 0805 Y5V

12

C20

1UF 16V 0805 Y5V /NI

12

C45

1UF 16V 0805 Y5V

4

1UF 10V Y5V /NI

12

C35

1UF 10V Y5V

12

C108

3

2

1

12

BC25

1UF 16V 0805 Y5V

12

C75

0.1UF 25V Y5V

+1.8V_SUS

12

12

BC8

1UF 16V 0805 Y5V

C53

0.1UF 25V Y5V

12

BC6

10UF 10V 0805 Y5V

12

3

BC19

1UF 16V 0805 Y5V

12

BC20

1UF 16V 0805 Y5V

12

BC36

1UF 10V Y5V

12

C132

1UF 16V 0805 Y5V

C282

0.1UF 25V Y5V

12

BC7

1UF 16V 0805 Y5V

12

BC26

10UF 10V 0805 Y5V

12

2

BC4

1UF 10V Y5V

Title

M2 PWR/GND

Size Document Number Rev

Custom

Date: Sheet of

CRU51-M2

1

9 39Friday, July 07, 2006

1.3

+V_CPU

12

BC24

+V_CPU

1UF 16V 0805 Y5V

12

BC18

1UF 16V 0805 Y5V

B B

A A

PLACE BOTTOM SIDE DECOUPLING

12

BC5

1UF 16V 0805 Y5V

+1.8V_SUS

5

12

BC32

1UF 16V 0805 Y5V

12

C23

1UF 10V Y5V

12

12

BC31

1UF 16V 0805 Y5V

BC9

1UF 16V 0805 Y5V

12

BC15

1UF 16V 0805 Y5V

12

C14

1UF 10V Y5V

12

BC13

1UF 16V 0805 Y5V

+0.9V_SUS

12

12

4

BC10

1UF 16V 0805 Y5V

C82

0.1UF 25V Y5V

PDF created with pdfFactory Pro trial version www.pdffactory.com

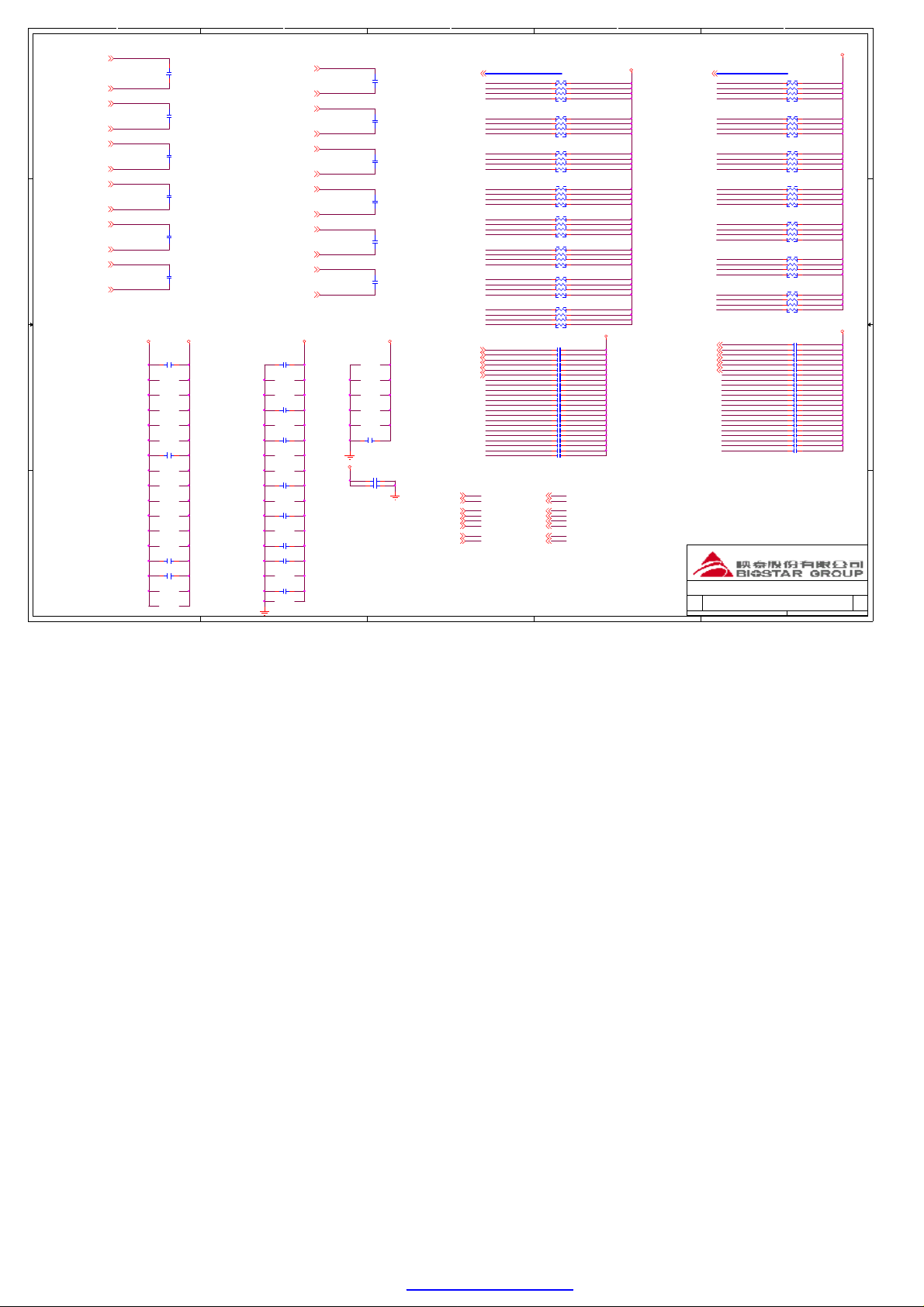

Page 10

5

MEM_MA0_CLK_H25,11

MEM_MA0_CLK_L25,11

MEM_MA0_CLK_H15,11

D D

MEM_MA0_CLK_L15,11

MEM_MA0_CLK_H05,11

MEM_MA0_CLK_L05,11

MEM_MB0_CLK_H26,12

MEM_MB0_CLK_L26,12

MEM_MB0_CLK_H16,12

MEM_MB0_CLK_L16,12

C C

MEM_MB0_CLK_H06,12

MEM_MB0_CLK_L06,12

LAYOUT: FRONT SIDE PLACE ALTERNATING GND AND 1.8V

ALONG 0.9V VTT FILL

B B

A A

5

12

C116

1.5P 50V NPO 0402

C24

1.5P 50V NPO 0402

BC23

1.5P 50V NPO 0402

C109

1.5P 50V NPO 0402

C26

1.5P 50V NPO 0402

C74

1.5P 50V NPO 0402

+0.9V_SUS

C52 0.1UF 25V Y5V1 2

C85 0.1UF 25V Y5V

1 2

C117 0.1UF 25V Y5V1 2

4

MEM_MA1_CLK_H25,11

MEM_MA1_CLK_L25,11

MEM_MA1_CLK_H15,11

MEM_MA1_CLK_L15,11

MEM_MA1_CLK_H05,11

MEM_MA1_CLK_L05,11

MEM_MB1_CLK_H26,12

MEM_MB1_CLK_L26,12

MEM_MB1_CLK_H16,12

MEM_MB1_CLK_L16,12

MEM_MB1_CLK_H06,12

MEM_MB1_CLK_L06,12

+0.9V_SUS+1.8V_SUS

C126 0.1UF 25V Y5V1 2

C118 0.1UF 25V Y5V

1 2

C100 0.1UF 25V Y5V

1 2

C99 1UF 10V Y5V1 2

C105 0.1UF 25V Y5V1 2

C112 0.1UF 25V Y5V1 2

C130 0.1UF 25V Y5V

1 2

C60 0.1UF 25V Y5V

1 2

4

C115

C31

BC30

C113

C33

C79

+0.9V_SUS

1 2

+1.8V_SUS

C114 1UF 10V Y5V

1 2

C55 1UF 16V 0805 Y5V1 2

1.5P 50V NPO 0402

1.5P 50V NPO 0402

1.5P 50V NPO 0402

1.5P 50V NPO 0402

1.5P 50V NPO 0402

1.5P 50V NPO 0402

3

MEM_MA_ADD[15..0]5,11 MEM_MB_ADD[15..0]6,12

MEM_MA_BANK05,11

MEM_MA_BANK15,11

MEM_MA_BANK25,11

MEM_MA_CAS_L5,11

MEM_MA_WE_L5,11

MEM_MA_RAS_L5,11

MEM_MA_CKE05,11

MEM_MA_CKE15,11 MEM_MB_CKE16,12

MEM_MA0_CS_L05,11

MEM_MA0_CS_L15,11

MEM_MA1_CS_L05,11

MEM_MA1_CS_L15,11

MEM_MA0_ODT05,11

MEM_MA1_ODT05,11

MEM_MA_ADD[15..0]

MEM_MA_ADD9

MEM_MB_BANK2

MEM_MA_ADD12

MEM_MB_ADD12

MEM_MB_ADD4 MEM_MB_ADD14

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MB_ADD2

MEM_MA_ADD0

MEM_MB_BANK1

MEM_MB_ADD10

MEM_MB_BANK0

MEM_MB_ADD3

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MA_ADD4

MEM_MA1_ODT0

MEM_MA0_CS_L1

MEM_MA0_ODT0

MEM_MB_CAS_L

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MB_ADD15

MEM_MA_ADD11

MEM_MA0_CS_L0

MEM_MA_CAS_L

MEM_MB0_ODT0

MEM_MB1_CS_L1

MEM_MA_BANK0

MEM_MA_RAS_L

MEM_MB1_CS_L0

MEM_MB0_CS_L0

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MB_CKE06,12

MEM_MB0_CS_L06,12

MEM_MB0_CS_L16,12

MEM_MB1_CS_L16,12

MEM_MB1_CS_L06,12

MEM_MB0_ODT06,12

MEM_MB1_ODT06,12

3

RN8 47 8P4R

78

56

34

12

RN1247 8P4R

78

56

34

12

RN1347 8P4R

78

56

34

12

RN1147 8P4R

78

56

34

12

RN1847 8P4R

78

56

34

12

RN7 47 8P4R

78

56

34

12

RN1747 8P4R

78

56

34

12

RN1647 8P4R

78

56

34

12

22P 50V NPO 0402BC43

22P 50V NPO 0402BC44

22P 50V NPO 0402BC22

22P 50V NPO 0402BC47

22P 50V NPO 0402BC46

22P 50V NPO 0402BC41

22P 50V NPO 0402BC40

22P 50V NPO 0402BC39

22P 50V NPO 0402BC37

22P 50V NPO 0402BC38

22P 50V NPO 0402BC34

22P 50V NPO 0402BC35

22P 50V NPO 0402BC33

22P 50V NPO 0402BC29

22P 50V NPO 0402BC28

22P 50V NPO 0402BC42

22P 50V NPO 0402BC27

22P 50V NPO 0402BC21C32 0.1UF 25V Y5V

22P 50V NPO 0402BC48

22P 50V NPO 0402BC16

22P 50V NPO 0402BC17C128 0.1UF 25V Y5V1 2

2

+0.9V_SUS

+1.8V_SUS

2

1

+0.9V_SUS

MEM_MB_ADD[15..0]

MEM_MA_BANK2

MEM_MA_ADD6

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MB_ADD9

MEM_MB_ADD11

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MA_ADD5

MEM_MB_ADD1

MEM_MA_ADD3

MEM_MB_RAS_L

MEM_MB_ADD0

MEM_MA_ADD10

MEM_MA_BANK1

MEM_MB_WE_L

MEM_MA_WE_L

MEM_MA1_CS_L0

MEM_MA_ADD13

MEM_MB_CKE0

MEM_MA_ADD14

MEM_MB_CKE1

MEM_MA_CKE1

MEM_MB_ADD13

MEM_MA1_CS_L1

MEM_MB0_CS_L1

MEM_MB1_ODT0

MEM_MB_BANK06,12

MEM_MB_BANK16,12

MEM_MB_BANK26,12

MEM_MB_CAS_L6,12

MEM_MB_WE_L6,12

MEM_MB_RAS_L6,12

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

Title

DDR ADD/CTL/VTT TERMINATI

Size Document Number Rev

Custom

Date: Sheet of

CRU51-M2

1

RN6 47 8P4R

78

56

34

12

RN9 47 8P4R

78

56

34

12

RN1047 8P4R

78

56

34

12

RN1447 8P4R

78

56

34

12

RN1947 8P4R

78

56

34

12

RN5 47 8P4R

78

56

34

12

RN2147 8P4R

78

56

34

12

22P 50V NPO 0402C94

22P 50V NPO 0402C90

22P 50V NPO 0402C63

22P 50V NPO 0402C103

22P 50V NPO 0402C10222P 50V NPO 0402BC45

22P 50V NPO 0402C96

22P 50V NPO 0402C88

22P 50V NPO 0402C81

22P 50V NPO 0402C83

22P 50V NPO 0402C77

22P 50V NPO 0402C76

22P 50V NPO 0402C73

22P 50V NPO 0402C72

22P 50V NPO 0402C69

22P 50V NPO 0402C68

22P 50V NPO 0402C65

22P 50V NPO 0402C92

22P 50V NPO 0402C66

22P 50V NPO 0402C61

22P 50V NPO 0402C110

22P 50V NPO 0402C59

22P 50V NPO 0402C57

+1.8V_SUS

10 39Friday, July 07, 2006

1.3

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 11

5

4

3

2

1

175

VDDQ1

181

191

VDDQ2

VDDQ3

194515662727578

VDDQ4

VDDQ5

VDDQ6

VDDQ7

+3.3V

DIMMA1

238

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDSPD

ERR_OUT_L

PAR_IN

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

WE_L

VREF

TEST

ODT0

ODT1

NC1

MEM_MA_DATA[0..63]

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

73

1

102

195

77

55

68

19

MEM_MA_DATA[0..63]5

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17MEM_MA_ADD15

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_WE_L5,10 MEM_MA_WE_L5,10

MEM_M_VREF

MEM_MA0_ODT05,10

MEM_MA_DQS_H[8..0]5

MEM_MA_DQS_L[8..0]5

MEM_MA_ADD[15..0]5,10

MEM_MA_CHECK[7..0]5

MEM_MA_DM[8..0]

MEM_MA_DM[8..0]5 MEM_MA_DATA[0..63]5

MEM_MA_DM8

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_H8

MEM_MA_DQS_L8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3 MEM_MA_DATA34

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_L[8..0]

+3.3V

SMB_MEM_SCL12,18

SMB_MEM_SDA12,18

MEM_MA_BANK25,10

MEM_MA_BANK15,10

MEM_MA_BANK05,10

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK[7..0]

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA1_CLK_H05,10

MEM_MA1_CLK_L05,10

MEM_MA1_CLK_H15,10

MEM_MA1_CLK_L15,10

MEM_MA1_CLK_H25,10

MEM_MA1_CLK_L25,10

MEM_MA_CKE1

MEM_MA_CKE15,10

MEM_MA_RAS_L5,10

MEM_MA_CAS_L5,10

MEM_MA1_CS_L05,10

MEM_MA1_CS_L15,10

+1.8V_SUS +3.3V

DIMMA2

172

178

184

187

189

1975359646769170

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

DDR2-240 pin-W

VDD11

VDDQ1

175

VDDQ2

181

191

VDDQ3

VDDQ4

194515662727578

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

238

VDDQ11

ERR_OUT_L

VDDSPD

PAR_IN

DIMMA2

236

DQ63

235

DQ62

230

DQ61

229

DQ60

117

DQ59

116

DQ58

111

DQ57

110

DQ56

227

DQ55

226

DQ54

218

DQ53

217

DQ52

108

DQ51

107

DQ50

99

DQ49

98

DQ48

215

DQ47

214

DQ46

209

DQ45

208

DQ44

96

DQ43

95

DQ42

90

DQ41

89

DQ40

206

DQ39

205

DQ38

200

DQ37

199

DQ36

87

DQ35

86

DQ34

81

DQ33

80

DQ32

159

DQ31

158

DQ30

153

DQ29

152

DQ28

40

DQ27

39

DQ26

34

DQ25

33

DQ24

150

DQ23

149

DQ22

144

DQ21

143

DQ20

31

DQ19

30

DQ18

25

DQ17

24

DQ16

141

DQ15

140

DQ14

132

DQ13

131

DQ12

22

DQ11

21

DQ10

13

DQ9

12

DQ8

129

DQ7

128

DQ6

123

DQ5

122

DQ4

10

DQ3

9

DQ2

4

DQ1

3

DQ0

73

WE_L

1

VREF

102

TEST

195

ODT0

77

ODT1

55

68

19

NC1

MEM_MA_DATA[0..63]

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

12

C15

0.1UF 25V Y5V

PLACE NEAR DIMM SOCKETS

MEM_M_VREF

MEM_MA1_ODT05,10

+1.8V_SUS

DIMMA1

172

178

184

187

189

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

DDR2-240 pin

VDD1

VDD2

VDD3

1975359646769170

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

D D

MEM_MA_DQS_H[8..0]5

C C

MEM_MA_DQS_L[8..0]5

MEM_MA_ADD[15..0]5,10

MEM_MA_CHECK[7..0]5

B B

MEM_MA_DM[8..0]

MEM_MA_DM[8..0]5

MEM_MA_DM8

164

165

MEM_MA_DM7

232

233

MEM_MA_DM6

223

224

MEM_MA_DM5

211

212

MEM_MA_DM4

202

203

MEM_MA_DM3

155

156

MEM_MA_DM2

146

147

MEM_MA_DM1

134

135

MEM_MA_DM0

125

MEM_MA_DQS_H[8..0]

126

MEM_MA_DQS_H8

46

MEM_MA_DQS_L8

45

MEM_MA_DQS_H7

114

MEM_MA_DQS_L7

113

MEM_MA_DQS_H6

105

MEM_MA_DQS_L6

104

MEM_MA_DQS_H5

93

MEM_MA_DQS_L5

92

MEM_MA_DQS_H4

84

MEM_MA_DQS_L4

83

MEM_MA_DQS_H3

37

MEM_MA_DQS_L3

36

MEM_MA_DQS_H2

28

MEM_MA_DQS_L2

27

MEM_MA_DQS_H1

16

MEM_MA_DQS_L1

15

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_L[8..0]

SMB_MEM_SCL12,18

SMB_MEM_SDA12,18

MEM_MA_BANK25,10

MEM_MA_BANK15,10

MEM_MA_BANK05,10

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA0_CLK_H05,10

MEM_MA0_CLK_L05,10

MEM_MA0_CLK_H15,10

MEM_MA0_CLK_L15,10

MEM_MA0_CLK_H25,10

MEM_MA0_CLK_L25,10

MEM_MA_CKE0

MEM_MA_CKE05,10

MEM_MA_RAS_L5,10

MEM_MA_CAS_L5,10

MEM_MA0_CS_L05,10

MEM_MA0_CS_L15,10

MEM_MA_CHECK[7..0]

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

+1.8V_SUS

R20

A A

5

150 1%

1 2

R18

150 1%

1 2

12

C18

1UF 10V Y5V

MEM_M_VREF

12

C10

0.1UF 25V Y5V /NI

PLACE NEAR DIMM SOCKETS

Title

DDR DIMM0&1

Size Document Number Rev

C

4

3

2

Date: Sheet of

CRU51-M2

1

11 39Friday, July 07, 2006

1.3

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 12

5

4

3

2

1

+1.8V_SUS

DIMMB1

DIMMB1

172

178

184

187

189

1975359646769170

175

181

191

194515662727578

D D

MEM_MB_DQS_H[8..0]6

C C

B B

MEM_MB_DQS_L[8..0]6

MEM_MB_ADD[15..0]6,10

MEM_MB_CHECK[7..0]6

MEM_MB_DM[8..0]

MEM_MB_DM[8..0]6

MEM_MB_DM8

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_L[8..0]

+3.3V

SMB_MEM_SCL11,18

SMB_MEM_SDA11,18

MEM_MB_BANK26,10

MEM_MB_BANK16,10

MEM_MB_BANK06,10

MEM_MB_ADD[15..0]

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK[7..0]

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB0_CLK_H06,10

MEM_MB0_CLK_L06,10

MEM_MB0_CLK_H16,10

MEM_MB0_CLK_L16,10

MEM_MB0_CLK_H26,10

MEM_MB0_CLK_L26,10

MEM_MB_CKE06,10

MEM_MB_RAS_L6,10

MEM_MB_CAS_L6,10

MEM_MB0_CS_L06,10

MEM_MB0_CS_L16,10

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

7

DQS0_H

6

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

DDR2-240 pin

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDDQ1

238

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

ERR_OUT_L

MEM_MB_DATA[0..63]

VDDSPD

236

DQ63

235

DQ62

230

DQ61

229

DQ60

117

DQ59

116

DQ58

111

DQ57

110

DQ56

227

DQ55

226

DQ54

218

DQ53

217

DQ52

108

DQ51

107

DQ50

99

DQ49

98

DQ48

215

DQ47

214

DQ46

209

DQ45

208

DQ44

96

DQ43

95

DQ42

90

DQ41

89

DQ40

206

DQ39

205

DQ38

200

DQ37

199

DQ36

87

DQ35

86

DQ34

81

DQ33

80

DQ32

159

DQ31

158

DQ30

153

DQ29

152

DQ28

40

DQ27

39

DQ26

34

DQ25

33

DQ24

150

DQ23

149

DQ22

144

DQ21

143

DQ20

31

DQ19

30

DQ18

25

DQ17

24

DQ16

141

DQ15

140

DQ14

132

DQ13

131

DQ12

22

DQ11

21

DQ10

13

DQ9

12

DQ8

129

DQ7

128

DQ6

123

DQ5

122

DQ4

10

DQ3

9

DQ2

4

DQ1

3

DQ0

73

WE_L

1

VREF

102

TEST

195

ODT0

77

ODT1

55

68

PAR_IN

19

NC1

MEM_MB_DATA[0..63]6

MEM_MB_DATA63

MEM_MB_DATA62 MEM_MB_DATA63

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11MEM_MB_ADD9

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1