Page 1

5

4

3

2

1

B450 AORUS M

26

PAGE

D D

01

02

03

04

05

06

07

08

C C

09

10

11

12

13

TITLE

COVER SHEET

BOM & PCB MODIFY HISTORY

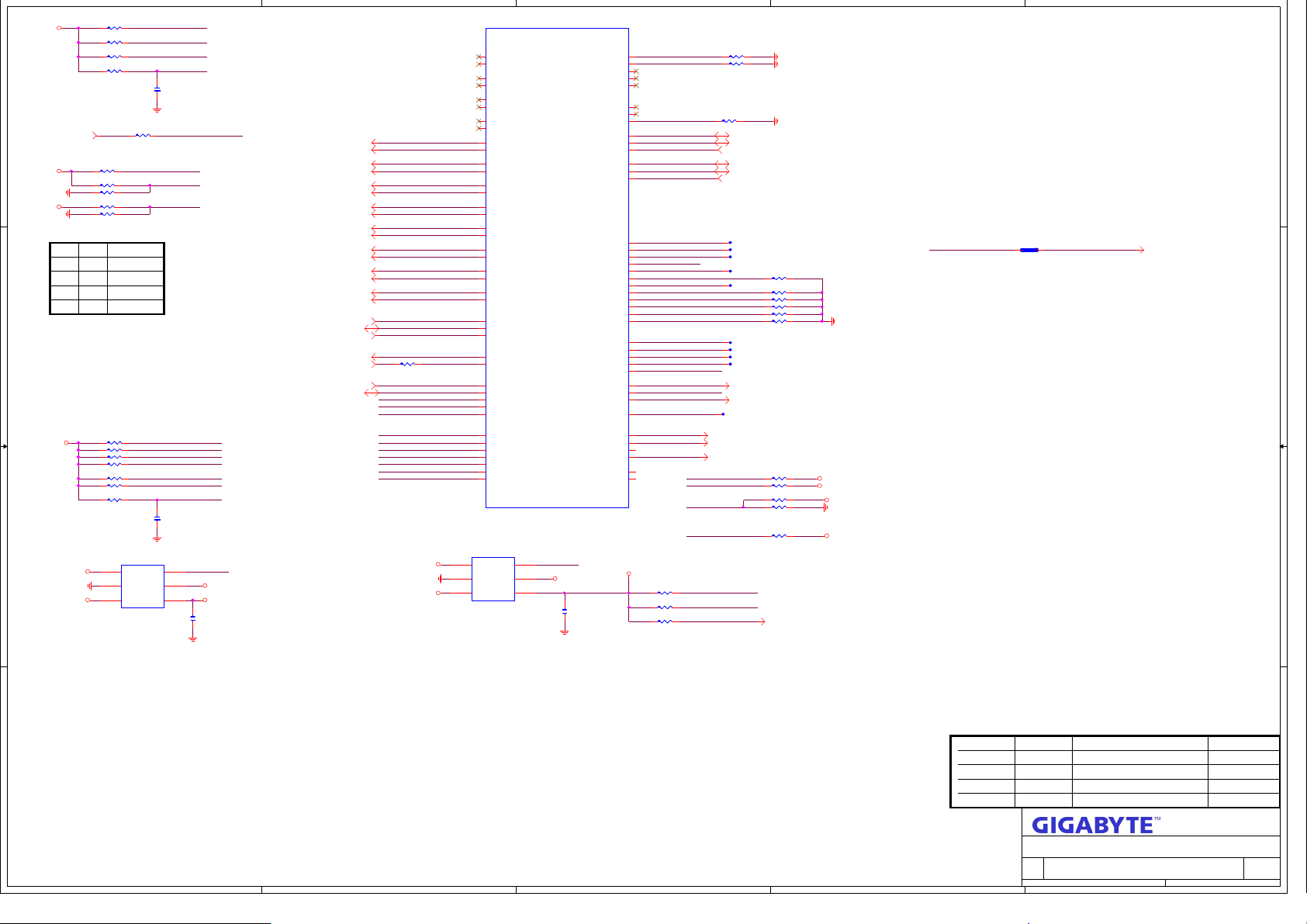

BLOCK DIAGRAM

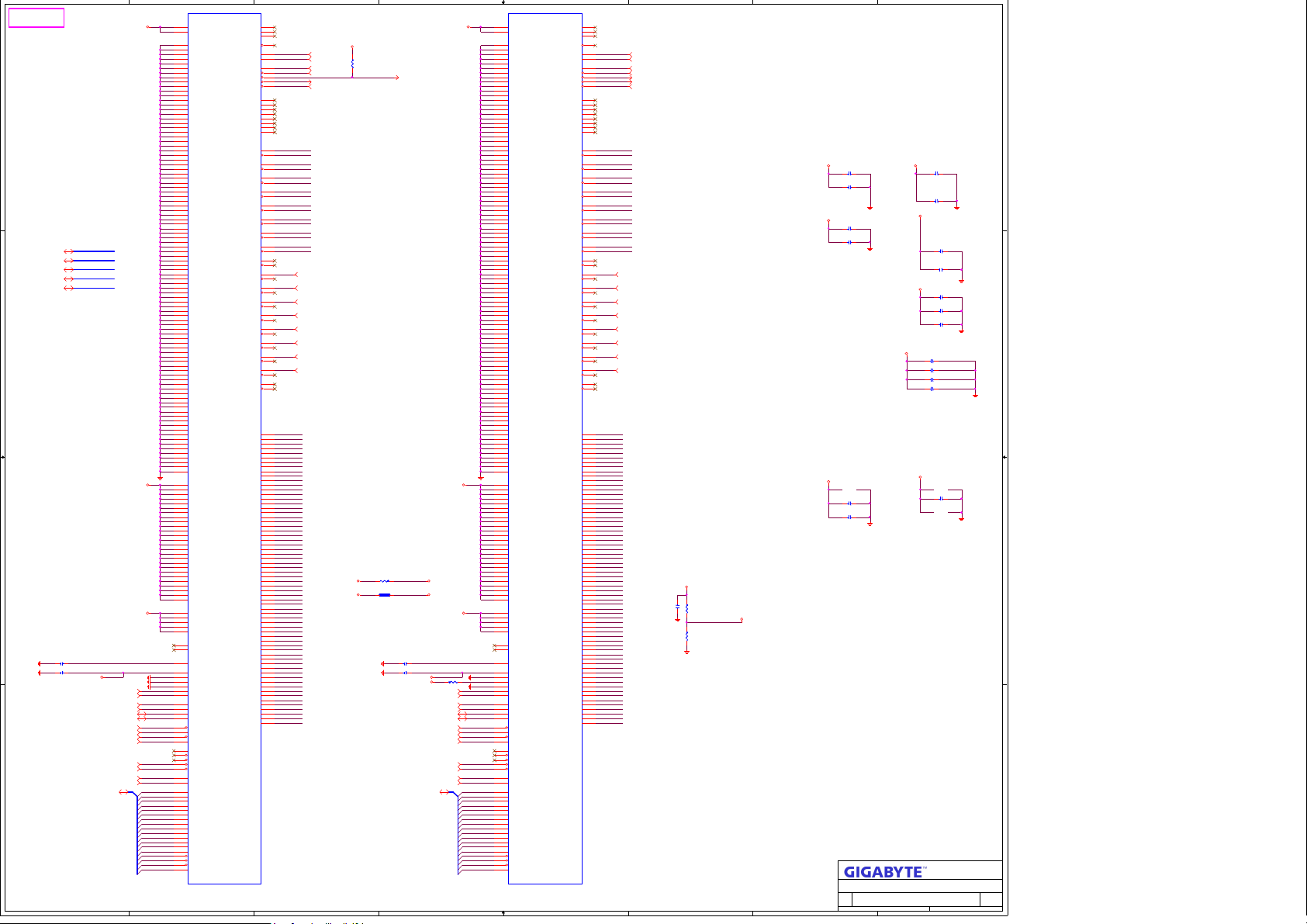

CPU DDR4 MEMORY

CPU CONTROL

CPU GFX, GPP, SB, GND

CPU ACPI/GPIO/USB/AUDIO

CPU POWER & GND

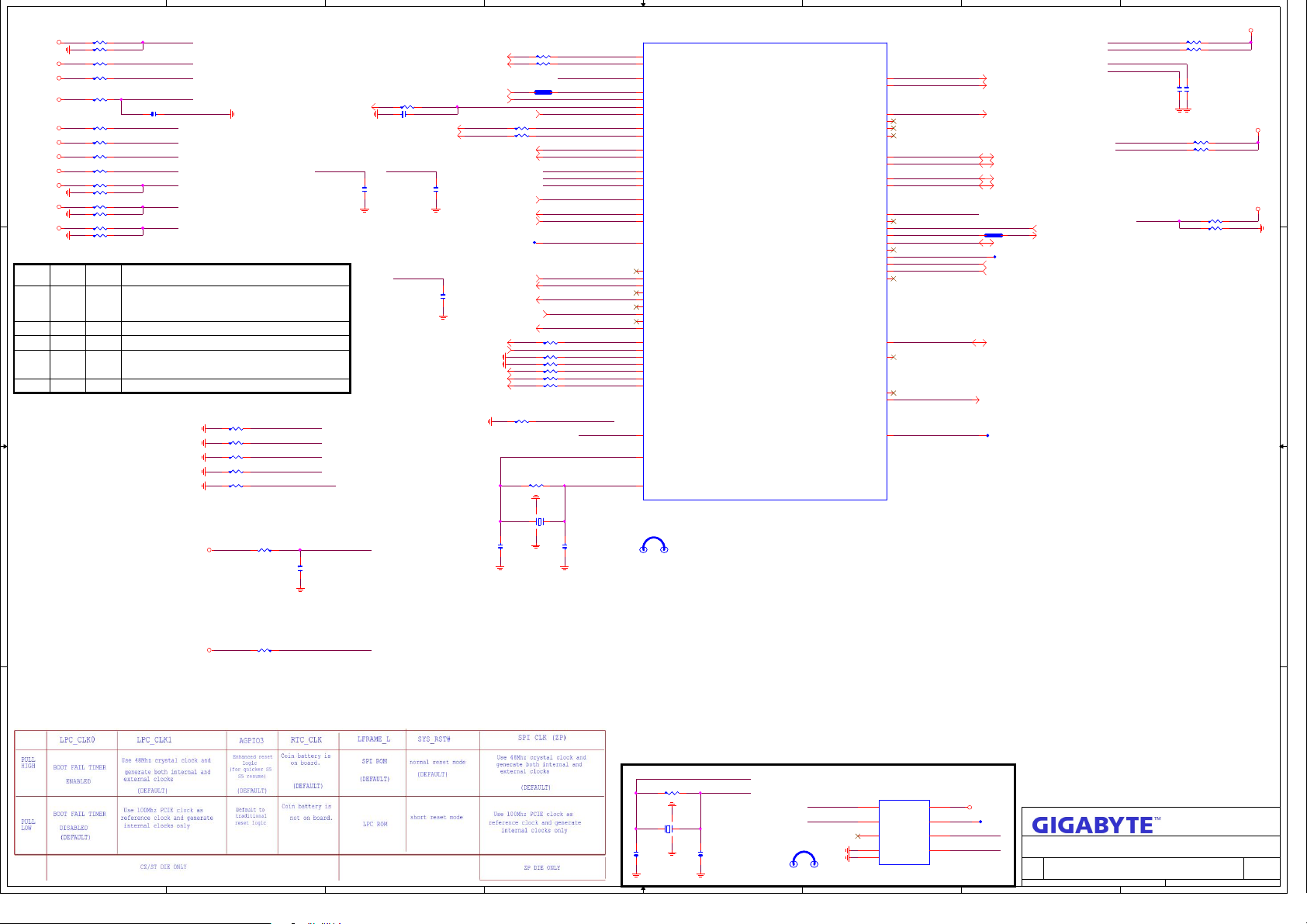

CPU CLK/SPI/USB

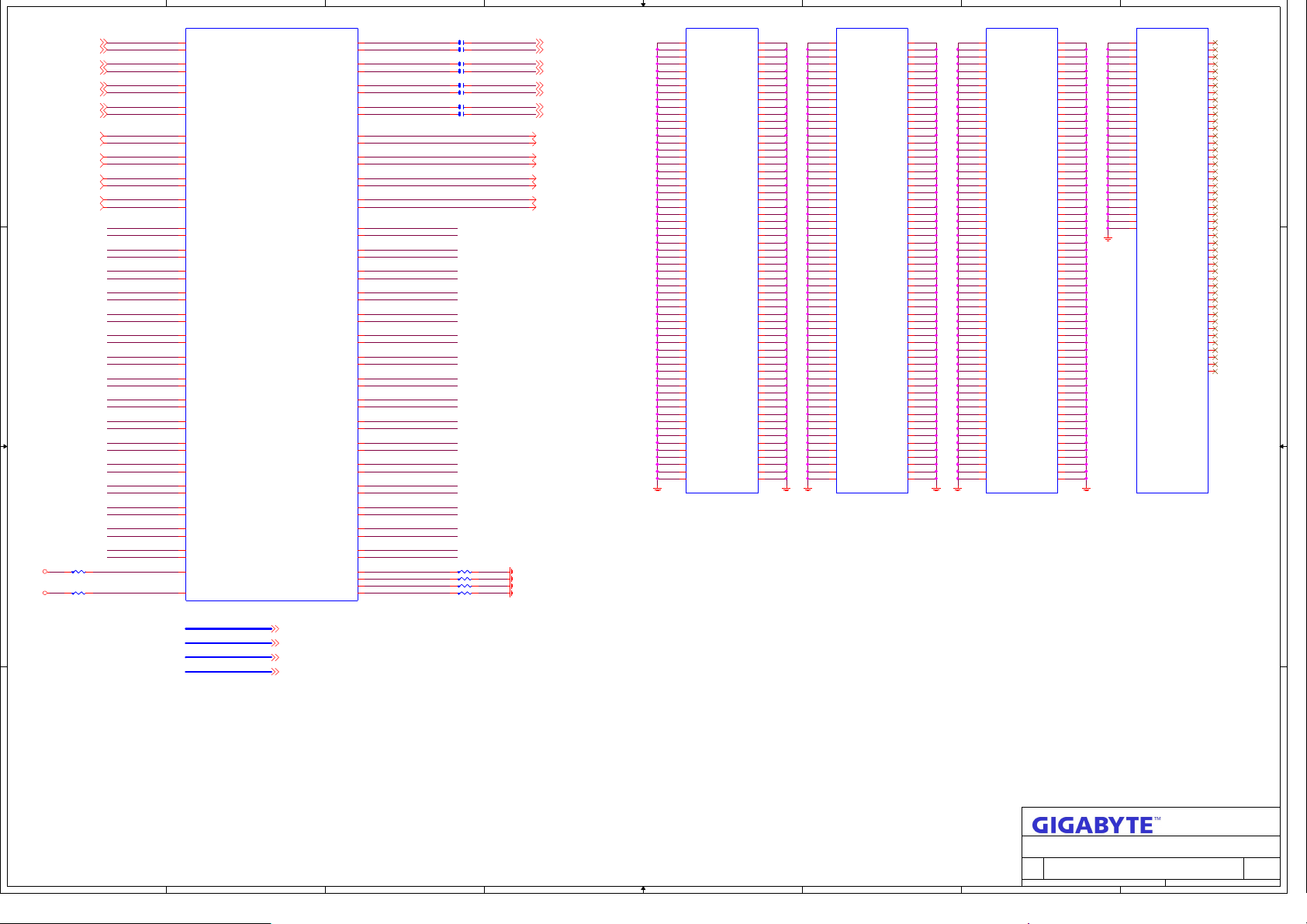

DDR4 CHANNEL A

DDR4 CHANNEL B

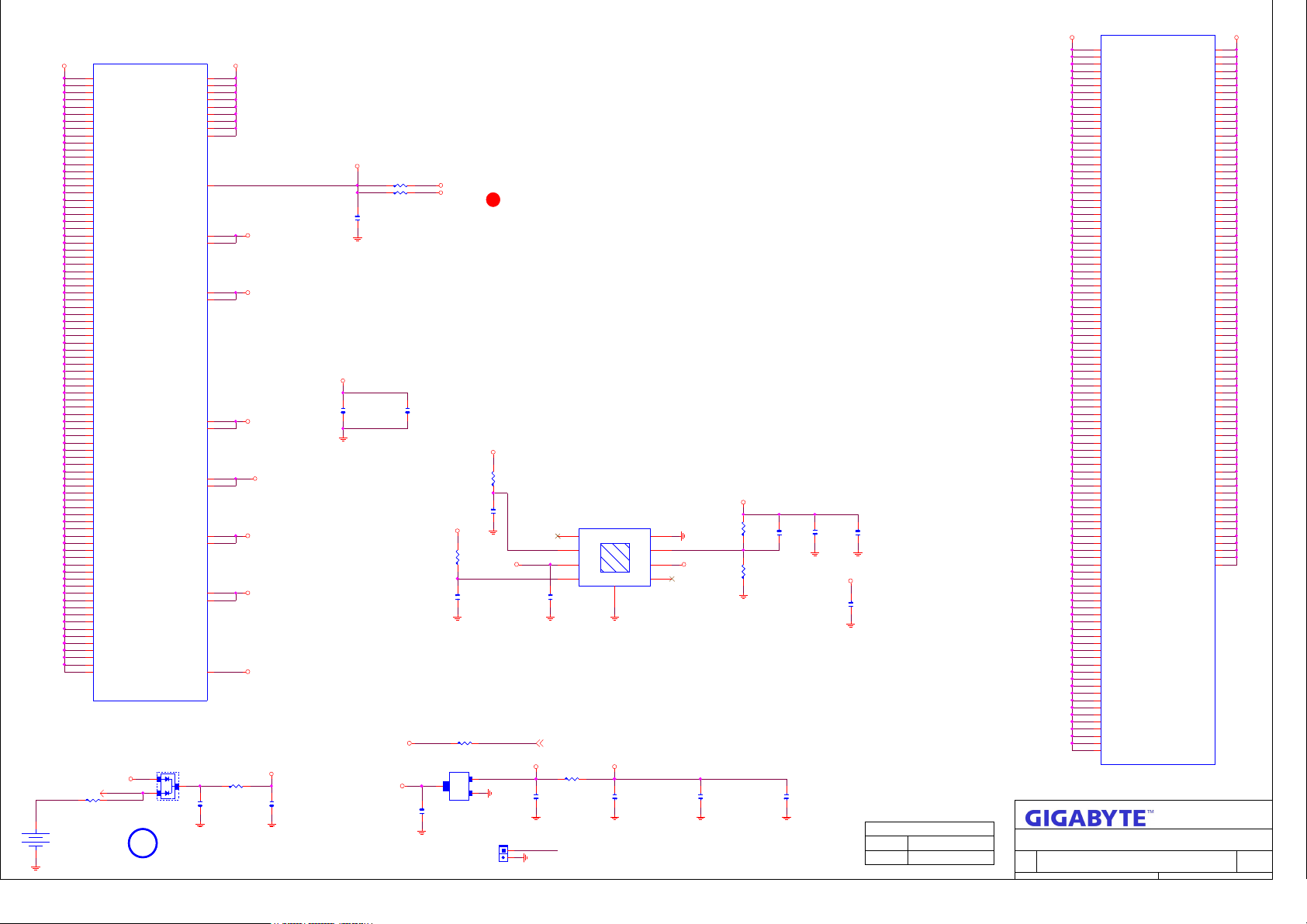

PM CLK/GPIO/FAN

PM USB

Revision : 1.05

27

28

29

30

31

32

33

34

35

36

TITLEPAGE

VCORE MOS , VCORE_SOC MOS

ATX , F_PANEL

VPP_MEM , VDDCR_SOC_S5 , PM_1V05 , PM_2V5

5VDUAL , 3VDUAL , VDDIO_MEM , DDRVTT

REALTK RTL8118

FAN, LPT, COM

RTD2168

M.2 , SWITCH

PCIEx4 , PCIEx1

CPU SMD CAP BOTTOM

CPU SMD CAP TOP

EC8792 FOR DUAL BIOS37

14

15

16

B B

17

18

19

20

21

22

23

A A

24

25

PM UMI/GPP/SATA

PM POWER & GND

PCI EXPRESS x16

HDMI , DVI

IT8686CX , TPM

F_USB30 , R_USB30 , F_USB20

A_VDD1V8 / A_VDDPS5

ALC892 CODEC

AUDIO JACK

AUDIO LED

POWER SEQUENCE , A_VDDP

PWM SL95712

5

2015.12.30--B.L

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

COVER SHEET

COVER SHEET

COVER SHEET

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

1

1 38Tuesday, November 12, 2019

1 38Tuesday, November 12, 2019

1 38Tuesday, November 12, 2019

Page 2

5

4

3

2

1

Model Name:B450 AORUS M

Component value change history

D D

2017.11.01 10C BOM Release. PCB: 1.01 1. update B33006 RoHS LOGO & 小版本修改 , other

2018.01.17 11A E-BOM Release. PCB:1.11 1. rename DR25

2018.06.14 10A P-BOM Release. PCB:1.0 1. SEQU ENCE CHANGE (PC34 NA, SQR2 8.2K-->39K , SQC1-->2.2u)

2018.08.20 10G P-BOM Release. PCB:1.01

2019.05.21 10H P-BOM Release. PCB:1.01 UPDATE NEW EC FW V684.BIN

C C

2019.11.12 1. Vcore choke Footprint 自動插件修改10L P-BOM PCB:1.05

Change ItemDate

not change

2. PCB cheange to Rev1.11

3. SIO OR15 NA , OR7 上件

2. PCB cheange to Rev1.0

3. F_PANNEL (ADD MPD-)

4. M2 SOCKET SMBUS NA

5. DR38 20.5K-->18.7K

1. Vcore SENSE 位置

2. C125 10u change to 22u

3. VINA0 change to APU_PWRGD(for summit / Pinnacle

不上DIMM時,僅亮CPU DEBUD LED,應改為亮DDR DEB UG

LED)

4.BRN1 change to 1K

Reason

Version: 1.05

P-Code: U98126-0

Circuit or PCB layout change for next version

ReasonDate Change Item

1. Add USB 3.1 2nd re-driver.

2. Fix VDDCR_SOC_S5 power issue.

3. PWM/DRIVER change to 12V.

4. LAN, R_USB30_1 signal swap.

5. CPU side 0603 10u change to 0805 22u.

6. Add POS CAP 470U DEC3.

7. Debug port turn to left.

8. KB/MS EMI CAP change to 0402.

9. Update PWM choke (P/N not done).

10. Update PWM OV (current dac)

B B

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

BOM & PCB HISTORY

BOM & PCB HISTORY

BOM & PCB HISTORY

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

1

2 38Wednesday, November 20, 2019

2 38Wednesday, November 20, 2019

2 38Wednesday, November 20, 2019

Page 3

5

4

3

2

1

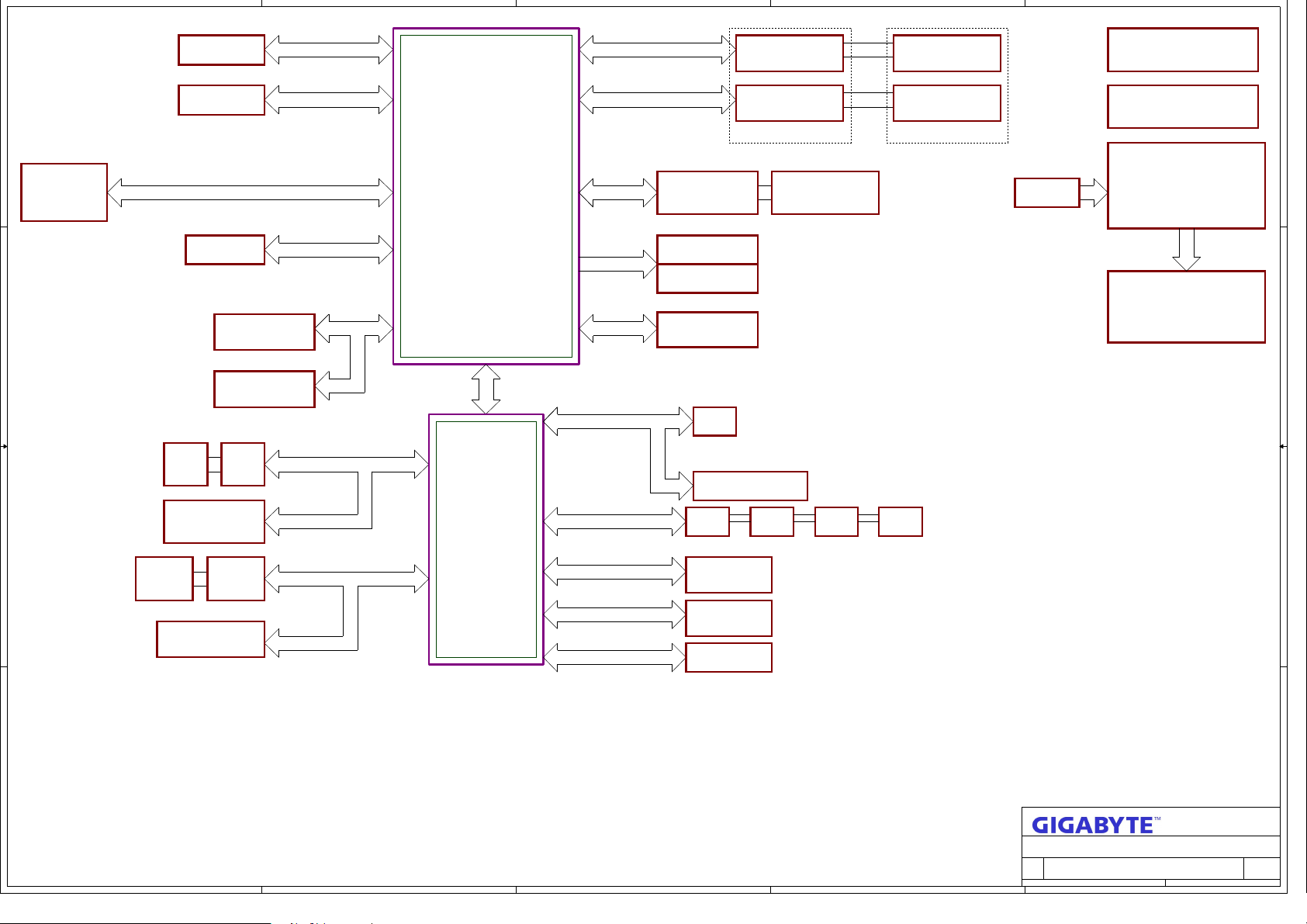

HDMI

17

DP0

AMD AM4

1 X16 o r X8 P CIE+ VIDEO I/F

DVI-D

D D

17 29

DP1

1 X4 P CIE I /F W ITH

AZALIA

SATA III

LPC I /F

UNGANGE D MODE 64BIT

DDR4 2133/2400/2666

UNGANGE D MODE 64BIT

DDR4 2133/2400/2666

UNBUFFERED

DDR4 DIMM4

UNBUFFERED

DDR4 DIMM3

DDR4 FIRST LOGICAL DIMM

UNBUFFERED

10

9 9

DDR4 DIMM2

UNBUFFERED

DDR4 DIMM1

DDR4 SECON D LOGICAL DIMM

10

INT R TC

PCIE SLOT X16

C C

16

SPI BIOS

9

PCIE0~15

SPI I/F

GPP0~3PCIE GEN3 M.2x4

33

SWITCH

33

USB31 GEN1 (0~1)

USB-1

19

SATA PORT * 2

SATA#4/5

USB-0

19

USB20-10/11

19

B B

USB31-1

USB31-0

30

USB31 GEN2 (0~1)

30

USB20-0/5

30

HW M ONITOR

ACPI

USB3.1 GEN1 x4

I/O HUB

Promontory

PCIE GEN2 x6

USB2.0 x10

USB3.1 GEN2 x2

USB3.0 GEN1 x2

SATA Express x 2

or SAT A G EN3 x2

SATA GEN3 x2

X4 PCIE GEN3

12,13,14,15

HD AUDIO I/F

4,5,6,7,8,9

SATA_EXPRESS/S ATA GEN3

SATA GEN3

GPP0

GPP1

GPP4~GPP7

USB31 Gen1

LPC

R_USB30_1

Port 0 / Port 1 Port 2 / Port 3

ITE LPC SIO IT8686

TPM Header

ALC892

HD AUDIO CODEC

21,22,23

R_USB30_2

19

18

18

SATA#0

14

SWITCH

SATA#1 / M.2

14,33

SATA#1SATA#0

14

GIGABIT LAN

RTL8118G

PCIE SLOT x1

PCIEX1

PCIE SLOT x4

PCIEX4

14

30

34

34

48MHz

19

9

SATA#3SATA#2

14

14

VCORE /VCORE_SOC

IR35201+ IR3555 4+ 2PHASE

VDDIO_MEM : RT8120

DDRVTT : NCT3103S

DDRVPP : RT8068A

CLK From AM4

GFX_CLK : PCIEX16

GPP_CLK(0~3)

0: PCIEX8

1: M.2

2: Promontory

3: n/a

CLK Buffer (Promontory )

GPP_CLK0~7

0 : LAN

1/2 : PCIEx1_1,PCIEx1_2 SLOT

4: PCIEX4 SLOT

3,5,6,7 : n/a

26,27

28

9

12

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

1

3 38Tuesday, November 12, 2019

3 38Tuesday, November 12, 2019

3 38Tuesday, November 12, 2019

Page 4

5

AM4A

MAAA0

AM4A

AA32

MAAA[0..13]<10>

D D

MA_DM[0..7]<10> MB_DM[0..7]<11>

C C

MA_CLKH0<10>

MA_CLKL0<10>

MA_CLKH1<10>

MA_CLKL1<10>

MA_CLKH2<10>

MA_CLKL2<10>

MA_CLKH3<10>

MA_CLKL3<10>

MA_RST-<10>

MA_EVENT-<10>

MA0_CKE0<10>

MA0_CKE1<10>

MA1_CKE0<10>

MA1_CKE1<10>

MODT_A0<10>

MODT_A1<10>

MODT_A2<10>

B B

MODT_A3<10>

MA0_CS0-<10>

MA0_CS1-<10>

MA1_CS0-<10>

MA1_CS1-<10>

MAAA17<10> MAAB17<11>

MAAA16<10>

MAAA15<10>

MAAA14<10> MAAB14<11>

MA_ALERT-<10> MB_ALERT-<11>

MA_PAROUT<10> MB_PAROUT<11>

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MA_ACT-

MA_ACT-<10>

MA_BG0

MA_BG0<10>

MA_BG1

MA_BG1<10>

MA_BA0

MA_BA0<10>

MA_BA1

MA_BA1<10>

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

★

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

MA_CLKH0

MA_CLKL0

MA_CLKH1

MA_CLKL1

MA_CLKH2 MB_CLKH2

MA_CLKL2

MA_CLKH3

MA_CLKL3

MA_RSTMA_ENENT-

MA0_CKE0

MA0_CKE1

MA1_CKE0

MA1_CKE1

MODT_A0

MODT_A1

MODT_A2

MA0_CS0MA0_CS1MA1_CS0MA1_CS1-

MAAA17 MAAB17

MAAA16

MAAA15

MAAA14

MA_ALERT- MB_ALERTMA_PAROUT MB_PAROUT

MA_ADD[0]

T32

MA_ADD[1]

T35

MA_ADD[2]

T31

MA_ADD[3]

R30

MA_ADD[4]

R33

MA_ADD[5]

R32

MA_ADD[6]

P34

MA_ADD[7]

P30

MA_ADD[8]

P31

MA_ADD[9]

AA36

MA_ADD[10]

P33

MA_ADD[11]

N35

MA_ADD[12]

AE32

MA_ADD[13]

M35

MA_ACT_L

N31

MA_BG[0]

N32

MA_BG[1]

AA35

MA_BANK[0]

AA33

MA_BANK[1]

K19

MA_DM[0]

J23

MA_DM[1]

G26

MA_DM[2]

H30

MA_DM[3]

AJ31

MA_DM[4]

AM31

MA_DM[5]

AL29

MA_DM[6]

AL26

MA_DM[7]

G34

MA_DM[8]

H19

MA_DQS_H[0]

G19

MA_DQS_L[0]

F23

MA_DQS_H[1]

G23

MA_DQS_L[1]

F27

MA_DQS_H[2]

F26

MA_DQS_L[2]

F30

MA_DQS_H[3]

E30

MA_DQS_L[3]

AJ33

MA_DQS_H[4]

AJ34

MA_DQS_L[4]

AN32

MA_DQS_H[5]

AN33

MA_DQS_L[5]

AP29

MA_DQS_H[6]

AN29

MA_DQS_L[6]

AP26

MA_DQS_H[7]

AN26

MA_DQS_L[7]

H34

MA_DQS_H[8]

H33

MA_DQS_L[8]

T34

MA_CLK_H[0]

U34

MA_CLK_L[0]

U33

MA_CLK_H[1]

V33

MA_CLK_L[1]

V35

MA_CLK_H[2]

V36

MA_CLK_L[2]

V32

MA_CLK_H[3]

W32

MA_CLK_L[3]

L33

MA_RESET_L

W35

MA_EVENT_L

M32

MA0_CKE[0]

M30

MA0_CKE[1]

M33

MA1_CKE[0]

L34

MA1_CKE[1]

AD35

MA0_ODT[0]

AF31

MA0_ODT[1]

AD33

MA1_ODT[0]

AF34

MA1_ODT[1]

AC33

MA0_CS_L[0]

AE35

MA0_CS_L[1]

AC34

MA1_CS_L[0]

AE34

MA1_CS_L[1]

AF33

MA_ADD_17

AB34

MA_RAS_L_ADD[16]

AD32

MA_CAS_L_ADD[15]

AB35

MA_WE_L_ADD[14]

N34

MA_ALERT_L

Y33

MA_PAROUT

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

MEMORY A

MEMORY A

AM4 REV 0.92

AM4 REV 0.92

PART 1 OF 12

PART 1 OF 12

MA_ZVDDIO_MEM_S3

MA_DATA[0]

MA_DATA[1]

MA_DATA[2]

MA_DATA[3]

MA_DATA[4]

MA_DATA[5]

MA_DATA[6]

MA_DATA[7]

MA_DATA[8]

MA_DATA[9]

MA_DATA[10]

MA_DATA[11]

MA_DATA[12]

MA_DATA[13]

MA_DATA[14]

MA_DATA[15]

MA_DATA[16]

MA_DATA[17]

MA_DATA[18]

MA_DATA[19]

MA_DATA[20]

MA_DATA[21]

MA_DATA[22]

MA_DATA[23]

MA_DATA[24]

MA_DATA[25]

MA_DATA[26]

MA_DATA[27]

MA_DATA[28]

MA_DATA[29]

MA_DATA[30]

MA_DATA[31]

MA_DATA[32]

MA_DATA[33]

MA_DATA[34]

MA_DATA[35]

MA_DATA[36]

MA_DATA[37]

MA_DATA[38]

MA_DATA[39]

MA_DATA[40]

MA_DATA[41]

MA_DATA[42]

MA_DATA[43]

MA_DATA[44]

MA_DATA[45]

MA_DATA[46]

MA_DATA[47]

MA_DATA[48]

MA_DATA[49]

MA_DATA[50]

MA_DATA[51]

MA_DATA[52]

MA_DATA[53]

MA_DATA[54]

MA_DATA[55]

MA_DATA[56]

MA_DATA[57]

MA_DATA[58]

MA_DATA[59]

MA_DATA[60]

MA_DATA[61]

MA_DATA[62]

MA_DATA[63]

MA_CHECK[0]

MA_CHECK[1]

MA_CHECK[2]

MA_CHECK[3]

MA_CHECK[4]

MA_CHECK[5]

MA_CHECK[6]

MA_CHECK[7]

MA_ZVSS

4

MDA[0..63] <10>

MDA0

E18

MDA1MAAA1

J18

MDA2

J20

MDA3

H21

MDA4

H18

MDA5

F18

MDA6

G20

MDA7

F20

MDA8

H22

MDA9

G22

MDA10

E24

MDA11

J24

MDA12

F21

MDA13

J21

MDA14

H24

MDA15

F24

MDA16

J26

MDA17

J27

MDA18

G28

MDA19

H28

MDA20

H25

MDA21

G25

MDA22

E28

MDA23

H27

MDA24

F29

MDA25

J30

MDA26

H31

MDA27

F32

MDA28

J29

MDA29

G29

MDA30

E31

MDA31

G31

MDA32

AH34

MDA33

AJ30

MDA34

AK30

MDA35

AL34

MDA36

AH31

MDA37

AH32

MDA38

AK33

MDA39

AK32

MDA40

AM34

MDA41

AM33

MDA42

AP31

MDA43

AR33

MDA44

AL32

MDA45

AL31

MDA46

AP34

MDA47

AP32

MDA48

AR31

MDA49

AK29

MDA50

AM28

MDA51

AL28

MDA52

AM30

MDA53

AN30

MDA54

AP28

MDA55

AR28

MDA56

AK27

MDA57

AK26

MDA58

AP25

MDA59

AR25

MDA60

AN27

MDA61

AM27

MDA62

AL25

MDA63

AM25

F33

G32

K31

K32

E33

E34

J32

J33

MA_ZVDDIO MB_ZVDDIO

Y34

AJ37

AR23 39.2/4/1AR23 39.2/4/1

AR48 40.2/4/1/XAR48 40.2/4/1/X

VDDIO_MEM VDDIO_MEM

Place within 1" of APU.

3

MAAB0

MAAB[0..13]<11>

★

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

MB_ACT-

MB_ACT-<11>

MB_BG0

MB_BG0<11>

MB_BG1

MB_BG1<11>

MB_BA0

MB_BA0<11>

MB_BA1

MB_BA1<11>

MB_DM0

MB_DM1

★

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

DQSB0

-DQSB0

DQSB1

-DQSB1

DQSB2

-DQSB2

DQSB3

-DQSB3

DQSB4

-DQSB4

DQSB5

-DQSB5

DQSB6

-DQSB6

DQSB7

-DQSB7

★

MB_CLKH0<11>

MB_CLKL0<11>

MB_CLKH1<11>

MB_CLKL1<11>

MB_CLKH2<11>

MB_CLKL2<11>

MB_CLKH3<11>

MB_CLKL3<11>

MB_CLKH0

MB_CLKL0

MB_CLKH1

MB_CLKL1

MB_CLKL2

MB_CLKH3

MB_CLKL3

MB_RST-<11>

MB_EVENT-<11>

MB0_CKE0<11>

MB0_CKE1<11>

MB1_CKE0<11>

MB1_CKE1<11>

MODT_B0<11>

MODT_B1<11>

MODT_B2<11>

MODT_B3<11>

MB0_CS0-<11>

MB0_CS1-<11>

MB1_CS0-<11>

MB1_CS1-<11>

MB_RSTMB_EVENT-

MB0_CKE0

MB0_CKE1

MB1_CKE0

MB1_CKE1

MODT_B0

MODT_B1

MODT_B2

MODT_B3MODT_A3

MB0_CS0MB0_CS1MB1_CS0MB1_CS1-

MAAB16

MAAB16<11>

MAAB15

MAAB15<11>

MAAB14

2

AM4I

AM4I

AC36

MB_ADD[0]

U36

MB_ADD[1]

U37

MB_ADD[2]

T38

MB_ADD[3]

T37

MB_ADD[4]

R39

MB_ADD[5]

R36

MB_ADD[6]

P39

MB_ADD[7]

R38

MB_ADD[8]

P36

MB_ADD[9]

AC39

MB_ADD[10]

P37

MB_ADD[11]

N38

MB_ADD[12]

AG38

MB_ADD[13]

M38

MB_ACT_L

M36

MB_BG[0]

M39

MB_BG[1]

AD38

MB_BANK[0]

AC37

MB_BANK[1]

C21

MB_DM[0]

D26

MB_DM[1]

A32

MB_DM[2]

D37

MB_DM[3]

AL38

MB_DM[4]

AR39

MB_DM[5]

AT35

MB_DM[6]

AW29

MB_DM[7]

F39

MB_DM[8]

B22

MB_DQS_H[0]

A22

MB_DQS_L[0]

C27

MB_DQS_H[1]

B27

MB_DQS_L[1]

C33

MB_DQS_H[2]

C32

MB_DQS_L[2]

B37

MB_DQS_H[3]

A37

MB_DQS_L[3]

AM37

MB_DQS_H[4]

AM36

MB_DQS_L[4]

AT38

MB_DQS_H[5]

AT39

MB_DQS_L[5]

AU34

MB_DQS_H[6]

AV34

MB_DQS_L[6]

AU28

MB_DQS_H[7]

AU29

MB_DQS_L[7]

G38

MB_DQS_H[8]

G37

MB_DQS_L[8]

U39

MB_CLK_H[0]

V39

MB_CLK_L[0]

V38

MB_CLK_H[1]

W38

MB_CLK_L[1]

W37

MB_CLK_H[2]

Y37

MB_CLK_L[2]

Y39

MB_CLK_H[3]

AA39

MB_CLK_L[3]

K35

MB_RESET_L

AA38

MB_EVENT_L

L37

MB0_CKE[0]

K37

MB0_CKE[1]

L39

MB1_CKE[0]

L36

MB1_CKE[1]

AF39

MB0_ODT[0]

AH36

MB0_ODT[1]

AF37

MB1_ODT[0]

AH38

MB1_ODT[1]

AE37

MB0_CS_L[0]

AG39

MB0_CS_L[1]

AE38

MB1_CS_L[0]

AG36

MB1_CS_L[1]

AH37

MB_ADD_17

AD36

MB_RAS_L_ADD[16]

AF36

MB_CAS_L_ADD[15]

AD39

MB_WE_L_ADD[14]

N37

MB_ALERT_L

AB38

MB_PAROUT

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

MEMORY B

MEMORY B

AM4 REV 0.92

AM4 REV 0.92

PART 9 OF 12

PART 9 OF 12

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_CHECK[0]

MB_CHECK[1]

MB_CHECK[2]

MB_CHECK[3]

MB_CHECK[4]

MB_CHECK[5]

MB_CHECK[6]

MB_CHECK[7]

MB_ZVDDIO_MEM_S3

MB_ZVSS

MDB0

D20

MDB1

B21

MDB2

B24

MDB3

C24

MDB4

A20

MDB5

C20

MDB6

A23

MDB7

C23

MDB8

A26

MDB9

C26

MDB10

A29

MDB11

C29

MDB12

A25

MDB13

B25

MDB14

A28

MDB15

B28

MDB16

A31

MDB17

B31

MDB18

B34

MDB19

C35

MDB20

B30

MDB21

C30

MDB22

B33

MDB23

A34

MDB24

B36

MDB25

E36

MDB26

C39

MDB27

D38

MDB28

A35

MDB29

C36

MDB30

B38

MDB31

C38

MDB32

AK39

MDB33

AL37

MDB34

AN36

MDB35

AN39

MDB36

AK38

MDB37

AK36

MDB38

AM39

MDB39

AN38

MDB40

AR36

MDB41

AR37

MDB42

AU37

MDB43

AV37

MDB44

AP37

MDB45

AP38

MDB46

AT36

MDB47

AU38

MDB48

AW35

MDB49

AU35

MDB50

AW32

MDB51

AU32

MDB52

AV36

MDB53

AW36

MDB54

AW33

MDB55

AV33

MDB56

AW30

MDB57

AV30

MDB58

AW27

MDB59

AW26

MDB60

AV31

MDB61

AU31

MDB62

AV28

MDB63

AV27

F38

F36

H39

J39

E37

E39

H36

H37

Y36

MB_ZVSSMA_ZVSS

AJ39

Place within 1" of APU.

1

MDB[0..63] <11>

MEM CHB

AR27 39.2/4/1AR27 39.2/4/1

AR49 40.2/4/1/XAR49 40.2/4/1/X

B0 B1

MEM CHA

AM4

MODT_A[0..3]<10>

MDA[0..63]<10>

MAAA[0..16]<10>

A A

DQSA[0..7]<10>

-DQSA[0..7]<10>

MODT_A[0..3]

MDA[0..63]

MAAA[0..16]

DQSA[0..7]

-DQSA[0..7]

AM4

MODT_B[0..3]<11>

MDB[0..63]<11>

MAAB[0..16]<11>

DQSB[0..7]<11>

-DQSB[0..7]<11>

MODT_B[0..3]

MDB[0..63]

MAAB[0..16]

DQSB[0..7]

-DQSB[0..7]

A0 A1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

AM3RM/SC/BL/MB/[12KRC-04K813-11R]

5

4

AM3RM/SC/BL/MB/[12KRC-04K813-11R]

3

2

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

APU DDR4

APU DDR4

APU DDR4

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

1

4 38Tuesday, November 12, 2019

4 38Tuesday, November 12, 2019

4 38Tuesday, November 12, 2019

Page 5

5

A_VDD1V8

AR39 1K/4/1AR39 1K/4/1

AR40 1K/4/1AR40 1K/4/1

AR34 300/4AR34 300/4

AR33 300/4AR33 300/4

100P/4/NPO/50V/J

100P/4/NPO/50V/J

D D

APU_PWRGD_R<31>

A_VDD1V8

A_VDD1V8

AR50 1K/4/1AR50 1K/4/1

AR41 1K/4/1/XAR41 1K/4/1/X

AR43 1K/4/1/XAR43 1K/4/1/X

AR44 1K/4/1/XAR44 1K/4/1/X

AR45 1K/4/1/XAR45 1K/4/1/X

SVC SVD

0

0

1

0

1

0

1 1

C C

HDTP_PWR

B B

AR72 1K/4/1AR72 1K/4/1

AR107 1K/4/1/XAR107 1K/4/1/X

AR70 1K/4/1AR70 1K/4/1

AR71 1K/4/1AR71 1K/4/1

AR108 1K/4/1/XAR108 1K/4/1/X

AR67 1K/4/1AR67 1K/4/1

100P/4/NPO/50V/J/X

100P/4/NPO/50V/J/X

A_VDD18S5

A_VDD1V8 HDTP_PWR

74LVC1G3157GW/SOT363

74LVC1G3157GW/SOT363

AC25

AC25

AR38 0/4AR38 0/4

Boot voltage

1.1

1.0

0.9

0.8

AC33

AC33

A_Q6

A_Q6

1

IN(H)

SEL

2

GND

VCC

3

IN(L)

OUT

APU_SIC

APU_SID

APU_PWRGD

APURSTL

APU_SVT

APU_SVC

APU_SVD

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_DBRDY

APU_DBREQ-

APU_TRST-

6

5

4

APU_PWRGD

CORETYPE1

3VDUAL

ABC25

ABC25

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

DVI

HDMI

DP1_TXP0<17>

DP1_TXN0<17>

DP1_TXP1<17>

DP1_TXN1<17>

DP1_TXP2<17>

DP1_TXN2<17>

DP1_TXP3<17>

DP1_TXN3<17>

DP0_TXP0<17>

DP0_TXN0<17>

DP0_TXP1<17>

DP0_TXN1<17>

DP0_TXP2<17>

DP0_TXN2<17>

DP0_TXP3<17>

DP0_TXN3<17>

APU_SVC<24>

APU_SVD<24>

APU_SVT<24>

APU_PWRGD<24>

APURST-<26>

APU_SIC<18>

APU_SID<18>

4

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

APU_SVC

APU_SVD

APU_SVT

APU_PWRGD

AR52 22/4AR52 22/4

APU_SIC

APU_SID

APU_ALERTAPU_PROCHOTTHERMTRIP-

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRSTAPU_DBRDY

APU_DBREQ-

VCC3

A_VDD1V8

B6

B7

A7

A8

C8

C9

B9

B10

D4

D5

D7

D8

F8

G8

E9

F9

D2

C2

C3

B3

B4

A4

C5

C6

D17

C17

A17

E16

APURSTL

B16

B18

C18

D16

H15

A19

A14

C14

C15

B15

B13

E13

D14

A_Q4

A_Q4

1

IN(H)

2

GND

3

IN(L)

74LVC1G3157GW/SOT363

74LVC1G3157GW/SOT363

AM4C

AM4C

DISPLAY/SVI2/JTAG/TEST

DISPLAY/SVI2/JTAG/TEST

DP2_TXP[0]

DP2_TXN[0]

DP2_TXP[1]

DP2_TXN[1]

DP2_TXP[2]

DP2_TXN[2]

DP2_TXP[3]

DP2_TXN[3]

DP1_TXP[0]

DP1_TXN[0]

DP1_TXP[1]

DP1_TXN[1]

DP1_TXP[2]

DP1_TXN[2]

DP1_TXP[3]

DP1_TXN[3]

DP0_TXP[0]

DP0_TXN[0]

DP0_TXP[1]

DP0_TXN[1]

DP0_TXP[2]

DP0_TXN[2]

DP0_TXP[3]

DP0_TXN[3]

SVC

SVD

SVT

PWROK

RESET_L

SIC

SID

ALERT_L

PROCHOT_L

THERMTRIP_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

AM4 REV 0.92

AM4 REV 0.92

PART 3 OF 12

VCC

SEL

OUT

6

5

4

PART 3 OF 12

CORETYPE1

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

VDDIO_MEM_S3_SENSE

3VDUAL

ABC24

ABC24

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP2_AUXP

DP2_AUXN

DP2_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

TEST47

TEST10

TEST14

TEST15

TEST16

TEST17

TEST11

TEST19

TEST18

TEST28_H

TEST28_L

TEST31

TEST40

DP_STEREOSYNC

CORETYPE[0]

CORETYPE[1]

TEST41

VDDCR_CPU_SENSE

VDDCR_SOC_SENSE

VSS_SENSE_A

VDDP_SENSE

VSS_SENSE_B

3

Placed within 1500 mils from APU

DP_ZVSS

F12

DP_A_ZVSS

E12

G13

H13

H12

A10

A11

DP2_HPD

E10

DP1_AUXP

F11

DP1_AUXN

G11

DP1_HPD

D10

DP0_AUXP

G10

DP0_AUXN

H10

DP0_HPD

H9

APU_TEST4

L23

TEST4

APU_TEST5

M22

TEST5

APU_TEST6

D13

TEST6

APU_TEST47

P28

APU_TEST10

AB4

APU_TEST14

C12

APU_TEST15

B12

APU_TEST16

C11

APU_TEST17

D11

APU_TEST11

A13

APU_TEST19

H16

APU_TEST18

G16

APU_TEST28_H

E6

APU_TEST28_L

E7

APU_TEST31

AA30

APU_TEST40

W30

APU_STESYNC

K14

AM4R1

AL8

AM4R1

CORETYPE0

AM24

CORETYPE1

AN9

APU_TEST41

A16

F14

E15

G14

F15

AL22

AM23

APU_STESYNC: high=>HDMI, low=>NO HDMI

A_VDD1V8_O

AR51 1K/4/1AR51 1K/4/1

AR61 1K/4/1AR61 1K/4/1

AR32 1K/4/1AR32 1K/4/1

AR29 2K/4/1AR29 2K/4/1

AR26 150/4/1AR26 150/4/1

AR46 100K/4/1AR46 100K/4/1

DP1_AUXP <17>

DP1_AUXN <17>

DP1_HPD <17>

DP0_AUXP <17>

DP0_AUXN <17>

DP0_HPD <17>

TP1TP1

TP2TP2

TP3TP3

TP5TP5

TP6TP6

TP8TP8

TP9TP9

TP13TP13

TP14TP14

AM4R1 <23,27>

CORETYPE1 <20,23,31>

TP15TP15

COREFB+ <24>

VNB_FB+ <24>

COREFB- <24>

CORETYPE0

CORETYPE1

APU_STESYNC

AM4R1

APU_ALERT-

THERMTRIP-

APU_PROCHOT-

AR1 1K/4/1/XAR1 1K/4/1/X

AR2 1K/4/1/XAR2 1K/4/1/X

AR3 1K/4/1/XAR3 1K/4/1/X

AR5 1K/4/1/XAR5 1K/4/1/X

AR62 1K/4/1AR62 1K/4/1

AR20 1K/4/1AR20 1K/4/1

AR30 1K/4/1AR30 1K/4/1

AR13 1K/4/1AR13 1K/4/1AR73 1K/4/1AR73 1K/4/1

AR22 1K/4/1AR22 1K/4/1

AR21 1K/4/1/XAR21 1K/4/1/X

AR117 8.2K/4/1AR117 8.2K/4/1

APU_PROCHOT- <24>

A_VDD18S5

3VDUAL

A_VDD1V8

3VDUAL

2

THERMTRIP- THERMTRIPO

AR36 0/4/SHT/XAR36 0/4/SHT/X

1

THERMTRIPO <18>

AM4 CPU CoreType

CORETYPE 1 CORETYPE 0

0 BR

A A

0 ST

1 ZP

1 RV 1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Family / Model Numbers

Family 15 h / Models 60 h- 6 Fh

0

Reserved

1

Family 17 h / Models 00 h- 0 Fh

0

Family 17 h / Models 10 h- 1 Fh

CPU CONTROL

CPU CONTROL

CPU CONTROL

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

1

AM4 APU TYPE

TYPE 0

TYPE 1

TYPE 2

TYPE 3

5 38Tuesday, November 12, 2019

5 38Tuesday, November 12, 2019

5 38Tuesday, November 12, 2019

Page 6

8

AM4B

AM4B

AE8

A_RX0P<14>

A_RX0N<14>

A_RX1P<14>

A_RX1N<14>

A_RX2P<14>

A_RX2N<14>

A_RX3P<14>

D D

C C

B B

A_VDDP

A_VDDP

A_RX3N<14>

PCIE1X0_IP<32>

PCIE1X0_IN<32>

PCIE1X1_IP<32>

PCIE1X1_IN<32>

PCIE1X2_IP<32>

PCIE1X2_IN<32>

PCIE1X3_IP<32>

PCIE1X3_IN<32>

AR25 196/4/1AR25 196/4/1

AR28 1K/4/1AR28 1K/4/1

EXP_A_RXP0

EXP_A_RXN0

EXP_A_RXP1

EXP_A_RXN1

EXP_A_RXP2

EXP_A_RXN2

EXP_A_RXP3

EXP_A_RXN3

EXP_A_RXP4

EXP_A_RXN4

EXP_A_RXP5

EXP_A_RXN5

EXP_A_RXP6

EXP_A_RXN6

EXP_A_RXP7

EXP_A_RXN7

EXP_A_RXP8

EXP_A_RXN8

EXP_A_RXP9

EXP_A_RXN9

EXP_A_RXP10

EXP_A_RXN10

EXP_A_RXP11

EXP_A_RXN11

EXP_A_RXP12

EXP_A_RXN12

EXP_A_RXP13

EXP_A_RXN13

EXP_A_RXP14

EXP_A_RXN14

EXP_A_RXP15

P_VZDD

SATA_VZDD

AD8

AB8

AA8

AR9

AM9

AM10

AR10

AP10

AP11

AN11

AV7

Y6

Y7

W4

W5

AT9

F6

F5

G5

G4

H7

H6

J6

J5

K8

K7

K5

K4

L7

L6

M6

M5

N8

N7

N5

N4

P7

P6

R6

R5

T8

T7

T4

T5

U7

U6

V6

V5

W8

P_HUB_RXP[0]

P_HUB_RXN[0]

P_HUB_RXP[1]

P_HUB_RXN[1]

P_HUB_RXP[2]

P_HUB_RXN[2]

P_HUB_RXP[3]

P_HUB_RXN[3]

P_GPP_RXP[0]

P_GPP_RXN[0]

P_GPP_RXP[1]

P_GPP_RXN[1]

P_GPP_RXP[2]/SATA_RX0P

P_GPP_RXN[2]/SATA_RX0N

P_GPP_RXP[3]/SATA_RX1P

P_GPP_RXN[3]/SATA_RX1N

P_GFX_RXP[0]

P_GFX_RXN[0]

P_GFX_RXP[1]

P_GFX_RXN[1]

P_GFX_RXP[2]

P_GFX_RXN[2]

P_GFX_RXP[3]

P_GFX_RXN[3]

P_GFX_RXP[4]

P_GFX_RXN[4]

P_GFX_RXP[5]

P_GFX_RXN[5]

P_GFX_RXP[6]

P_GFX_RXN[6]

P_GFX_RXP[7]

P_GFX_RXN[7]

P_GFX_RXP[8]

P_GFX_RXN[8]

P_GFX_RXP[9]

P_GFX_RXN[9]

P_GFX_RXP[10]

P_GFX_RXN[10]

P_GFX_RXP[11]

P_GFX_RXN[11]

P_GFX_RXP[12]

P_GFX_RXN[12]

P_GFX_RXP[13]

P_GFX_RXN[13]

P_GFX_RXP[14]

P_GFX_RXN[14]

P_GFX_RXP[15]

P_GFX_RXN[15]

P_ZVDDP

SATA_ZVDDP

Within 1500mil from APU

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

EXP_A_RXP[0..15]

EXP_A_RXN[0..15]

EXP_A_TX P[0..15]

EXP_A_TX N[0..15]

7

PCIE

PCIE

AM4 REV 0.92

AM4 REV 0.92

PART 2 OF 12

PART 2 OF 12

P_HUB_TXP[0]

P_HUB_TXN[0]

P_HUB_TXP[1]

P_HUB_TXN[1]

P_HUB_TXP[2]

P_HUB_TXN[2]

P_HUB_TXP[3]

P_HUB_TXN[3]

P_GPP_TXP[0]

P_GPP_TXN[0]

P_GPP_TXP[1]

P_GPP_TXN[1]

P_GPP_TXP[2]/SATA_TX0P

P_GPP_TXN[2]/SATA_TX0N

P_GPP_TXP[3]/SATA_TX1P

P_GPP_TXN[3]/SATA_TX1N

P_GFX_TXP[0]

P_GFX_TXN[0]

P_GFX_TXP[1]

P_GFX_TXN[1]

P_GFX_TXP[2]

P_GFX_TXN[2]

P_GFX_TXP[3]

P_GFX_TXN[3]

P_GFX_TXP[4]

P_GFX_TXN[4]

P_GFX_TXP[5]

P_GFX_TXN[5]

P_GFX_TXP[6]

P_GFX_TXN[6]

P_GFX_TXP[7]

P_GFX_TXN[7]

P_GFX_TXP[8]

P_GFX_TXN[8]

P_GFX_TXP[9]

P_GFX_TXN[9]

P_GFX_TXP[10]

P_GFX_TXN[10]

P_GFX_TXP[11]

P_GFX_TXN[11]

P_GFX_TXP[12]

P_GFX_TXN[12]

P_GFX_TXP[13]

P_GFX_TXN[13]

P_GFX_TXP[14]

P_GFX_TXN[14]

P_GFX_TXP[15]

P_GFX_TXN[15]

P_ZVSS

P0A_ZVSS

P0B_ZVSS

SATA_ZVSS

EXP_A_RXP[0..15] <16>

EXP_A_RXN[0..15] <16>

EXP_A_TX P[0..15] <16>

EXP_A_TX N[0..15] <16>

AE4

AE5

AA5

AB5

AC6

AC7

AD5

AD6

AT12

AR12

AP13

AR13

AL13

AM13

AN14

AP14

D1

E1

E3

F3

F2

G2

G1

H1

H3

J3

J2

K2

K1

L1

L3

M3

M2

N2

N1

P1

P3

R3

R2

T2

T1

U1

U3

V3

V2

W2

W1

Y1

W7

V8

AT8

AV6

6

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

A_TX2P_C

A_TX2N_C

A_TX3P_C

A_TX3N_C

EXP_A_TX P0

EXP_A_TX N0

EXP_A_TX P1

EXP_A_TX N1

EXP_A_TX P2

EXP_A_TX N2

EXP_A_TX P3

EXP_A_TX N3

EXP_A_TX P4

EXP_A_TX N4

EXP_A_TX P5

EXP_A_TX N5

EXP_A_TX P6

EXP_A_TX N6

EXP_A_TX P7

EXP_A_TX N7

EXP_A_TX P8

EXP_A_TX N8

EXP_A_TX P9

EXP_A_TX N9

EXP_A_TX P10

EXP_A_TX N10

EXP_A_TX P11

EXP_A_TX N11

EXP_A_TX P12

EXP_A_TX N12

EXP_A_TX P13

EXP_A_TX N13

EXP_A_TX P14

EXP_A_TX N14

EXP_A_TX P15

EXP_A_TX N15EXP_A_RXN15

P_ZVSS

P0A_ZVSS

P0B_ZVSS

SATA_ZVS S

AC1 0.22U/4/X7R/16V/KAC1 0.22U/4/X7R/16V/K

AC2 0.22U/4/X7R/16V/KAC2 0.22U/4/X7R/16V/K

AC3 0.22U/4/X7R/16V/KAC3 0.22U/4/X7R/16V/K

AC4 0.22U/4/X7R/16V/KAC4 0.22U/4/X7R/16V/K

AC5 0.22U/4/X7R/16V/KAC5 0.22U/4/X7R/16V/K

AC6 0.22U/4/X7R/16V/KAC6 0.22U/4/X7R/16V/K

AC7 0.22U/4/X7R/16V/KAC7 0.22U/4/X7R/16V/K

AC8 0.22U/4/X7R/16V/KAC8 0.22U/4/X7R/16V/K

PLACE THESE CA P CLOSE TO APU.

AR24 196/4/1AR24 196/4/1

AR6 200/4/1/XAR6 200/4/1/X

AR7 200/4/1/XAR7 200/4/1/X

AR4 1K/4/1AR4 1K/4/1

Within 1500mil from APU

5

A_TX0P <14>

A_TX0N <14>

A_TX1P <14>

A_TX1N <14>

A_TX2P <14>

A_TX2N <14>

A_TX3P <14>

A_TX3N <14>

PCIE1X0_OP <32>

PCIE1X0_ON <32>

PCIE1X1_OP <32>

PCIE1X1_ON <32>

PCIE1X2_OP <32>

PCIE1X2_ON <32>

PCIE1X3_OP <32>

PCIE1X3_ON <32>

AM4G

AM4G

J15

VSS

L29

VSS

AJ11

VSS

A3

VSS

A6

VSS

A9

VSS

A12

VSS

A15

VSS

A18

VSS

A21

VSS

A24

VSS

A27

VSS

A30

VSS

A33

VSS

A36

VSS

B19

VSS

B23

VSS

B26

VSS

B29

VSS

B32

VSS

B35

VSS

C1

VSS

C22

VSS

C25

VSS

C28

VSS

C31

VSS

C34

VSS

C37

VSS

D6

VSS

D9

VSS

D12

VSS

D15

VSS

D18

VSS

D19

VSS

D21

VSS

D22

VSS

D23

VSS

D24

VSS

D25

VSS

D27

VSS

D29

VSS

D30

VSS

D31

VSS

D32

VSS

D33

VSS

D34

VSS

D35

VSS

D36

VSS

D39

VSS

E4

VSS

E5

VSS

E8

VSS

E11

VSS

E14

VSS

E17

VSS

E20

VSS

E21

VSS

E23

VSS

E26

VSS

E27

VSS

E29

VSS

E32

VSS

AM4 REV 0.92

AM4 REV 0.92

PART 7 OF 12

PART 7 OF 12

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

4

GND

GND

E35

VSS

E38

VSS

F1

VSS

F4

VSS

F17

VSS

F19

VSS

F22

VSS

F25

VSS

F28

VSS

F31

VSS

F34

VSS

F35

VSS

F37

VSS

G7

VSS

G21

VSS

G24

VSS

G27

VSS

G30

VSS

G33

VSS

G35

VSS

G36

VSS

G39

VSS

H4

VSS

H5

VSS

H8

VSS

H11

VSS

H14

VSS

H17

VSS

H20

VSS

H23

VSS

H26

VSS

H29

VSS

H32

VSS

H35

VSS

H38

VSS

J1

VSS

J4

VSS

J8

VSS

J9

VSS

J11

VSS

J13

VSS

J17

VSS

J19

VSS

J22

VSS

J25

VSS

J28

VSS

J31

VSS

J34

VSS

J35

VSS

J37

VSS

K10

VSS

K12

VSS

K18

VSS

K20

VSS

K21

VSS

K22

VSS

K23

VSS

K26

VSS

K27

VSS

K28

VSS

K29

VSS

K30

VSS

AF28

AF30

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AG25

AG27

AG28

AG29

AG30

AG31

AG32

AH10

AH12

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH29

AH30

AH33

AJ13

AJ23

AJ25

AJ26

AJ27

AJ28

AJ29

AJ32

AJ35

AJ36

AJ38

AK10

AK12

AK14

AK22

AK25

AK28

AK31

AK35

AK37

AL11

AL24

AL27

AG1

AG4

AG8

AG9

AJ5

AJ8

AJ9

AK1

AK4

AL9

3

AM4J

AM4J

GND

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM4 REV 0.92

AM4 REV 0.92

PART 10 OF 12

PART 10 OF 12

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

2

AM4H

AM4H

GND

AL30

VSS

AL33

VSS

AL35

VSS

AL36

VSS

AL39

VSS

AM5

VSS

AM11

VSS

AM14

VSS

AM26

VSS

AM29

VSS

AM32

VSS

AM35

VSS

AM38

VSS

AN1

VSS

AN4

VSS

AN22

VSS

AN25

VSS

AN28

VSS

AN31

VSS

AN34

VSS

AN35

VSS

AN37

VSS

AP6

VSS

AP24

VSS

AP27

VSS

AP30

VSS

AP33

VSS

AP35

VSS

AP36

VSS

AP39

VSS

AR5

VSS

AR8

VSS

AR11

VSS

AR14

VSS

AR17

VSS

AR23

VSS

AR26

VSS

AR27

VSS

AR29

VSS

AR30

VSS

AR32

VSS

AR34

VSS

AR35

VSS

AR38

VSS

AT1

VSS

AT7

VSS

AT10

VSS

AT13

VSS

AT16

VSS

AT22

VSS

AT26

VSS

AT27

VSS

AT28

VSS

AT29

VSS

AT31

VSS

AT32

VSS

AT33

VSS

AT34

VSS

AT37

VSS

AU18

VSS

AU21

VSS

AU24

VSS

K33

L11

L13

L15

L17

L19

L21

L25

L27

L28

L30

L31

M10

M12

M14

M16

M18

M20

M24

M26

M27

M28

N11

N13

N15

N17

N19

N21

N23

N25

N27

N29

P10

P12

R11

R13

R27

R29

T10

T12

T28

T30

U11

GND

VSS

L4

VSS

L5

VSS

L8

VSS

L9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M1

VSS

M4

VSS

M8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P4

VSS

P5

VSS

P8

VSS

VSS

VSS

R1

VSS

R4

VSS

R8

VSS

R9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U4

VSS

U5

VSS

U8

VSS

U9

VSS

VSS

AM4 REV 0.92

AM4 REV 0.92

PART 8 OF 12

PART 8 OF 12

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

U13

VSS

U27

VSS

U29

VSS

U31

VSS

V1

VSS

V4

VSS

V7

VSS

V10

VSS

V12

VSS

V28

VSS

V30

VSS

W9

VSS

W11

VSS

W13

VSS

W27

VSS

W29

VSS

W31

VSS

Y5

VSS

Y8

VSS

Y10

VSS

Y12

VSS

Y28

VSS

Y30

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA9

VSS

AA11

VSS

AA13

VSS

VSS

AA27

VSS

AA31

VSS

AA29

AB7

VSS

AB10

VSS

AB12

VSS

AB28

VSS

AB30

VSS

AC5

VSS

AC8

VSS

AC9

VSS

AC11

VSS

AC13

VSS

AC27

VSS

AC29

VSS

AC31

VSS

AD1

VSS

AD4

VSS

AD10

VSS

AD12

VSS

AD28

VSS

AD30

VSS

AE7

VSS

AE9

VSS

AE11

VSS

AE13

VSS

AE27

VSS

AE29

VSS

AE31

VSS

AF5

VSS

AF8

VSS

AF10

VSS

AF12

VSS

AM4K

AM4K

AU26

VSS

AU27

VSS

AU30

VSS

AU33

VSS

AU36

VSS

AU39

VSS

AV2

VSS

AV17

VSS

AV20

VSS

AV23

VSS

AV26

VSS

AV29

VSS

AV32

VSS

AV35

VSS

AV38

VSS

AW4

VSS

AW7

VSS

AW10

VSS

AW13

VSS

AW16

VSS

AW19

VSS

AW22

VSS

AW25

VSS

AW28

VSS

AW31

VSS

AW34

VSS

AW37

VSS

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

GND & RSVD

GND & RSVD

AM4 REV 0.92

AM4 REV 0.92

PART 11 OF 12

PART 11 OF 12

1

AM12

RSVD

AT25

RSVD

AR15

RSVD

AP15

RSVD

AN12

RSVD

AN15

RSVD

AT30

RSVD

AW24

RSVD

AR24

RSVD

A5

RSVD

AD3

RSVD

AB2

RSVD

AH2

RSVD

AL16

RSVD

AL17

RSVD

AL18

RSVD

AL19

RSVD

AL20

RSVD

AL21

RSVD

AM16

RSVD

AM17

RSVD

AM21

RSVD

AN16

RSVD

AN17

RSVD

AN21

RSVD

AP16

RSVD

AP17

RSVD

AP21

RSVD

AR16

RSVD

AR18

RSVD

AR19

RSVD

AR20

RSVD

AR21

RSVD

AT19

RSVD

D28

RSVD

E19

RSVD

E22

RSVD

E25

RSVD

G17

RSVD

J36

RSVD

J38

RSVD

K34

RSVD

K38

RSVD

R35

RSVD

AB37

RSVD

AH35

RSVD

AK34

RSVD

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

8

7

6

5

4

3

Date: Sheet of

2

AM4 PCIE LINK

AM4 PCIE LINK

AM4 PCIE LINK

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

6 38Tuesday, November 12, 2019

6 38Tuesday, November 12, 2019

6 38Tuesday, November 12, 2019

1

Page 7

8

7

6

5

4

3

2

1

VCC3

AR95 8.2K/4AR95 8.2K/4

3VDUAL

AR96 1K/4/1/XAR96 1K/4/1/X

AR103 8.2K/4/XAR103 8.2K/4/X

3VDUAL

AR120 8.2K/4/AAR120 8.2K/4/A

VCC3

AR104 8.2K/4AR104 8.2K/4

3VDUAL

D D

3VDUAL

3VDUAL

3VDUAL

3VDUAL

3VDUAL

3VDUAL

3VDUAL

AR112 1K/4/1/XAR112 1K/4/1/X

AR111 8.2K/4/1A R111 8.2K/4/1

AR110 1K/4/1/XAR110 1K/4/1/X

AR109 1K/4/1/XAR109 1K/4/1/X

AR74 1K/4/1/XAR74 1K/4/1/X

AR75 15K/4/1AR75 15K/4/1

AR76 1K/4/1/XAR76 1K/4/1/X

AR77 15K/4/1AR77 15K/4/1

AR78 1K/4/1/XAR78 1K/4/1/X

AR79 15K/4/1AR79 15K/4/1

Internal Debug Only

TEST0

TEST1

TEST2

0 0

0

0

0

TMS

TMS

1

1

X

0

1

C C

0

1

1

B B

SYS_RSTL

PCIE_RST-

PCIE_RST-

PCIE_WAKE-

ABC43 10P/4/NPO/50V/J/XABC43 10P/4/NPO/50V/J/X

S0A3_GPIO

LPCPME-

SLP_S3-

SLP_S5-

A_TEST0

10P/4/NPO/50V/J

A_TEST1

10P/4/NPO/50V/J

A_TEST2

Description

FCH TAP accessible from APU when TAPEN is asserted

FCH JTAG pins overloaded for multiple functions, in this

configuration the FCH JTAG are used as non-J TAG pins

Reserve

Reserve

FCH JTAG multi-function pins are configured as JTAG

pins, in this configuration the FCH TAP can be

accessed from FCH JTAG pins

Use on JTAG only, Yuba JTAG enable.

A_AZRSTL

A_AZBCLK

A_AZSYNC

A_AZSOUT

AZ_SDATA_IN0

ABC21

ABC21

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

A_VDD18S5

AR118 1K/4/1AR118 1K/4/1

AR123 1K/4/1AR123 1K/4/1

AR124 1K/4/1AR124 1K/4/1

AR125 1K/4/1AR125 1K/4/1

AR126 1K/4/1/XAR126 1K/4/1/X

AR12 22K/4AR12 22K/4

PR68 22/4PR68 22/4

SYS_RST-<26>

SLP_S3- SLP_S5-

ABC42

ABC41

ABC41

ABC42

10P/4/NPO/50V/J

10P/4/NPO/50V/J

AZ_BIT_CLK

10P/4/NPO/50V/J/X

10P/4/NPO/50V/J/X

RSMRST-

22P/4/N/50V/XPC17 22P/4/N/50V/XPC17

ABC37

ABC37

AM4D

AM4D

SYS_RSTL

PCIE_WAKE-

SLP_S3L

SLP_S5L

S0A3_GPIO

S5_MUX

A_TEST0

A_TEST1

A_TEST2

KBRST-

LPCPMEAGPIO86

AGPIO23

M2A_-CLKREQ

M2ASSD_IFDET

EC_USB_OC1

AGPIO24

AX1

AX1

12

32.768K/12.5p/20ppm/TF38/35K/D

32.768K/12.5p/20ppm/TF38/35K/D

3 4

AXC2

AXC2

15P/4/NPO/50V/J

15P/4/NPO/50V/J

ARSTA_PERST-

RSMRST-

PWRBTN-

A_AZBCLK

AZ_SDIN1

AZ_SDIN2

A_AZRSTL

A_AZSYNC

A_AZSOUT

RTCCLK

RTCCLK

A_RTC_XI

A_RTC_XO

AU22

LPC_RST_L

PCIE_RST_L/EGPIO26

AL7

AP5

RSMRST_L

AN5

PWR_BTN_L/AGPIO0

AM3

PWR_GOOD

AM4

SYS_RESET_L/AGPIO1

AL5

WAKE_L/AGPIO2

AT2

SLP_S3_L

AP2

SLP_S5_L

AR3

S0A3_GPIO/AGPIO10/SGPIO0_CLK

S5_MUX_CTRL/EGPIO42

AP4

AM6

TEST0

AM7

TEST1/TMS

AT3

TEST2

AN24

ESPI_RESET_L/KBRST_L

AL2

LPC_PME_L/AGPIO22

AW17

AGPIO86

AN3

AGPIO23/SGPIO0_LOAD

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPI O92

AT23

AV24

CLK_REQ1_L/AGPIO115

AT24

CLK_REQ2_L/AGPIO116

AL23

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AR22

CLK_REQG_L/OSCIN/EGPIO132

AL1

USB_OC0_L/AGPIO16

AM1

USB_OC1_L/TDI/AGPIO17

AR1

USB_OC2_L/TCK/AGPIO18

AP1

USB_OC3_L/TDO/AGPIO24

AW3

AZ_BITCLK

AV3

AZ_SDIN0

AU5

AZ_SDIN1

AV4

AZ_SDIN2

AU1

AZ_RST_L

AU2

AZ_SYNC

AU4

AZ_SDOUT

AP8

RTCCLK

AW5

X32K_X1

AW6

X32K_X2

AX1

AX1

SHW/D0.64*5.08*6.74

SHW/D0.64*5.08*6.74

AR114 33/4AR114 33/4

LPC_RST-<18,31>

AR60 33/4AR60 33/4

PCIE_RST-<12,16,32>

AR0 0/4/SHT/XAR0 0/4/SHT/X

-PSOUT<18>

APU_PWOK<23>

PCIE_WAKE-<12,16,29,30,33>

SLP_S3-<18,23>

SLP_S5-<18,27>

PR69 22/4PR69 22/4

PR70 22/4PR70 22/4

S0A3_GPIO<23>

S5_MUX<27>

KBRST-<18>

LPCPME-<12,18>

AGPIO86<12>

TP16TP16

M2A_-CLKREQ<32>

M2ASSD_IFDET<32>

EGPIO132<38>

EC_USB_OC1<31>

AGPIO24<38>

-AZ_RST<21>

AR18 22/4AR18 22/4

AR115 8.2K/4/1A R115 8.2K/4/1

AR116 8.2K/4/1A R116 8.2K/4/1

AR55 22/4AR55 22/4

AR54 22/4AR54 22/4

AR19 22/4AR19 22/4

AZ_BIT_CLK<21>

AZ_SDATA_IN0<21>

AZ_SYNC<21>

AZ_SDATA_OUT<21 >

AR94 1K/4/1/XAR94 1K/4/1/X

AXR1 20M/4AXR1 20M/4

AXC1

AXC1

15P/4/NPO/50V/J

15P/4/NPO/50V/J

ACPI/SD/AZ/GPIO/RTC/I2C/MISC

ACPI/SD/AZ/GPIO/RTC/I2C/MISC

AM4 REV 0.92

AM4 REV 0.92

PART 4 OF 12

PART 4 OF 12

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

EGPIO100

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

AGPIO5/DEVSLP0

AGPIO9/SGPIO0_DATAOUT

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

SATA_ACT_L/AGPIO130

AGPIO40/SGPIO0_DATAIN

SPKR/AGPIO91

BLINK/AGPIO11

FANIN0/AGPIO84

FANOUT0/AGPIO85

TEST46[13]

EGPIO95

EGPIO96

EGPIO97

EGPIO98

EGPIO99

AGPIO3

AGPIO4

AGPIO6

AGPIO8

AW11

AV12

AW12

AU13

AV13

AT14

AU25

AV25

AK3

AK2

AT6

AR6

AP22

AN8

AP7

AN2

AV22

AU23

AM22

AR4

AW23

AT5

AN23

AP23

AL4

SMBCLK

SMBDATA

SMBCLK1

SMBDATA1

A_GPIO3

M2_DEVSLP

A_GPIO6

M2A_DETECT-

AGPIO89

AGPIO90

ASATA_LE D-

SPKR

APU_TEST46

EGPIO95 <30>

EGPIO96 <30>

EGPIO97 <30>

SMBCLK <10,11,24,27,31,38>

SMBDATA <10,11,24,27,31,38>

SMBCLK1 <16,32,33>

SMBDATA1 <16,32,33>

AR121 0/4/SHT/XAR121 0/4/SHT/X

M2A_DETECT- <32>

TP17TP17

PEX16_PRSNT- <16>

ASATA_LE D- <26>

SPKR <26>

AGPIO85 <31>

TP7TP7

CPU_FAN

SYS_FAN_1

SYS_FAN_2

SYS_FAN_3

M2_DEVSLP <32>

FAN_0_RPM <31>

SMBCLK

SMBDATA

SMBCLK

SMBDATA

ABC22

ABC22

100P/4/NPO/50V/J/X

100P/4/NPO/50V/J/X

SMBCLK1

SMBDATA1

A_GPIO3

AR31 2.2K/4/1AR31 2.2K/4/1

AR53 2.2K/4/1AR53 2.2K/4/1

ABC23

ABC23

100P/4/NPO/50V/J/X

100P/4/NPO/50V/J/X

AR80 2.2K/4/1AR80 2.2K/4/1

AR81 2.2K/4/1AR81 2.2K/4/1

AR91 8.2K/4AR91 8.2K/4

AR92 1K/4/1/XAR92 1K/4/1/X

3VDUAL

3VDUAL

3VDUAL

A A

8

AR93 8.2K/4AR93 8.2K/4

7

RTCCLK

ORTCXO

ORTCR1 20M/4ORTCR1 20M/4

1 2

3 4

ORTC2

ORTC2

12P/4/NPO/50V/J/X

12P/4/NPO/50V/J/X

6

5

ORTCXI

ORTCX

ORTCX

32.768K/12.5p/20ppm/TF38/35K/D

32.768K/12.5p/20ppm/TF38/35K/D

ORTC1

ORTC1

12P/4/NPO/50V/J/X

12P/4/NPO/50V/J/X

4

ORTCX

ORTCX

SHW/D0.64*5.08*6.74

SHW/D0.64*5.08*6.74

ORTCXI

ORTCXO

RTC

RTC

1

XI

VDD

2

XO

CLKOUT

3

INT-

SCL

VSS4SDA

9

BGND

PCF85063TP/HWSON8

PCF85063TP/HWSON8

3

8

7

6

5

RTCVDD3

SMBCLK1

SMBDATA1

TP12TP12

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

AM4 MISC

AM4 MISC

AM4 MISC

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

7 38Tuesday, November 12, 2019

7 38Tuesday, November 12, 2019

7 38Tuesday, November 12, 2019

1

Page 8

VDDIO Max=15.5A

VDDIO_MEM

VBAT_2

RB 1K/4/1RB 1K/4/1

12

BAT

BAT

BAT-SK/BK/P/S/D/SN

BAT-SK/BK/P/S/D/SN

AM4F

AM4F

K36

VDDIO_MEM_S3

K39

VDDIO_MEM_S3

L32

VDDIO_MEM_S3

L35

VDDIO_MEM_S3

L38

VDDIO_MEM_S3

M29

VDDIO_MEM_S3

M31

VDDIO_MEM_S3

M34

VDDIO_MEM_S3

M37

VDDIO_MEM_S3

N28

VDDIO_MEM_S3

N30

VDDIO_MEM_S3

N33

VDDIO_MEM_S3

N36

VDDIO_MEM_S3

N39

VDDIO_MEM_S3

P27

VDDIO_MEM_S3

P29

VDDIO_MEM_S3

P32

VDDIO_MEM_S3

P35

VDDIO_MEM_S3

P38

VDDIO_MEM_S3

R28

VDDIO_MEM_S3

R31

VDDIO_MEM_S3

R34

VDDIO_MEM_S3

R37

VDDIO_MEM_S3

T27

VDDIO_MEM_S3

T29

VDDIO_MEM_S3

T33

VDDIO_MEM_S3

T36

VDDIO_MEM_S3

T39

VDDIO_MEM_S3

U28

VDDIO_MEM_S3

U30

VDDIO_MEM_S3

U32

VDDIO_MEM_S3

U35

VDDIO_MEM_S3

U38

VDDIO_MEM_S3

V27

VDDIO_MEM_S3

V29

VDDIO_MEM_S3

V31

VDDIO_MEM_S3

V34

VDDIO_MEM_S3

V37

VDDIO_MEM_S3

W28

VDDIO_MEM_S3

W33

VDDIO_MEM_S3

W34

VDDIO_MEM_S3

W36

VDDIO_MEM_S3

W39

VDDIO_MEM_S3

Y27

VDDIO_MEM_S3

Y29

VDDIO_MEM_S3

Y31

VDDIO_MEM_S3

Y32

VDDIO_MEM_S3

Y35

VDDIO_MEM_S3

Y38

VDDIO_MEM_S3

AA28

VDDIO_MEM_S3

AA34

VDDIO_MEM_S3

AA37

VDDIO_MEM_S3

AB27

VDDIO_MEM_S3

AB29

VDDIO_MEM_S3

AB31

VDDIO_MEM_S3

AB32

VDDIO_MEM_S3

AB33

VDDIO_MEM_S3

AB36

VDDIO_MEM_S3

AB39

VDDIO_MEM_S3

AC28

VDDIO_MEM_S3

AC30

VDDIO_MEM_S3

AC32

VDDIO_MEM_S3

AC35

VDDIO_MEM_S3

AC38

VDDIO_MEM_S3

AD27

VDDIO_MEM_S3

AD29

VDDIO_MEM_S3

AD31

VDDIO_MEM_S3

AD34

VDDIO_MEM_S3

AD37

VDDIO_MEM_S3

AE28

VDDIO_MEM_S3

AE30

VDDIO_MEM_S3

AE33

VDDIO_MEM_S3

AE36

VDDIO_MEM_S3

AE39

VDDIO_MEM_S3

AF27

VDDIO_MEM_S3

AF29

VDDIO_MEM_S3

AF32

VDDIO_MEM_S3

AF35

VDDIO_MEM_S3

AF38

VDDIO_MEM_S3

AG33

VDDIO_MEM_S3

AG34

VDDIO_MEM_S3

AG35

VDDIO_MEM_S3

AG37

VDDIO_MEM_S3

AH39

VDDIO_MEM_S3

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

3VDUAL

VBAT<18,31>

20mil

POWER

POWER

VDDIO_AUDIO

VDDCR_SOC_S5

VDDCR_SOC_S5

VDDBT_RTC_G

AM4 REV 0.92

AM4 REV 0.92

PART 6 OF 12

PART 6 OF 12

AQ8

AQ8

BAT54C/SOT23/200mA

BAT54C/SOT23/200mA

CR2032+BAT

CR2032+BAT

CR2032

CR2032

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDD_18

VDD_18

VDD_33

VDD_33

VDDP_S5

VDDP_S5

VDD_18_S5

VDD_18_S5

VDD_33_S5

VDD_33_S5

20mil20mil

AR89 1K/4/1AR89 1K/4/1

ABC11

ABC11

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

AM18

AM19

AM20

AN18

AN19

AN20

AP18

AP19

AP20

AM15

AJ20

AK20

AJ21

AK21

AJ16

AJ17

AJ18

AK18

AJ15

AK15

AJ19

AK19

AL15

A_VDDP

VDDP Max=8.5A

VDDIO AUDIO 1.5/1.8V

VDDIO AUDIO Max=0.25A

Realtek suggest: 1.5V

A_VDD1V8

VDD18 Max=2A

★ DONE

VCC3

VDD33 Max=0.25A

★ DONE

A_VDDPS5

VDDP S5 Max=1A

★ DONE

VDDCR_SOC_S5

VDDCR SOC S5 Max=0.9A

A_VDD18S5

VDDP18 S5 Max=0.5A

★ DONE

3VDUAL

VDD33_S5 Max=0.25A

★ DONE

RTCVDD

VDDBT_RTC_G Max=4.5uA

RTCVDD3

ABC12

ABC12

1U/4/X5R/6.3V/K

1U/4/X5R/6.3V/K

A_VDDIOA

AR65 0/4/XAR65 0/4/X

AR47 0/4AR47 0/4

A_BC6

A_BC6

2.2u/4/X5R/6.3V/M

2.2u/4/X5R/6.3V/M

請靠近AM4.AM15

VDDCR_SOC_S5

For STR FAIL ISSUE

AC9

AC9

10u/6/X5R/6.3V/M

10u/6/X5R/6.3V/M

RTCVDD3

RTCVDD3

ABC15

ABC15

2.2u/6/X5R/6.3V/K

2.2u/6/X5R/6.3V/K

A_VDD1V8

A_VDD18S5

AC10

AC10

10u/6/X5R/6.3V/M

10u/6/X5R/6.3V/M

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

5VDUAL

A_R4

A_R4

2.2/4

2.2/4

A_C1

A_C1

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

AR100 20K/4/1/XAR100 20K/4/1/X

AQ9

AQ9

3

Vin

Vin

AP2138N-1.5TRG1/SOT23/250mA

AP2138N-1.5TRG1/SOT23/250mA

A_C2

A_C2

1

2

G Vo

G Vo

CHECK

3VDUAL

A_R3

A_R3

8.2K/4/1

8.2K/4/1

3VDUAL

CLR_CMOS

CLR_CMOS

PH/1*2/BK/2.54/VA/D

PH/1*2/BK/2.54/VA/D

O_-RTCRST <18>

RTCVDD_A

AR99 1K/4/1AR99 1K/4/1

ABC14

ABC14

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

RTCVDD

A_Q2

A_Q2

1

POK

2

EN

3

VIN

CNTL4REFIN

HAC11

HAC11

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

GND

VOUT

PGND

RT9018B-18GSP/SO8/3A

RT9018B-18GSP/SO8/3A

9

SPEC. MAX :1.9W.

RTCVDD

ABC13

ABC13

0.1U/4/X7R/16V/K

0.1U/4/X7R/16V/K

POWER

POWER

AM4 REV 0.92

AM4 REV 0.92

PART 12 OF 12

PART 12 OF 12

Vcore SOC EDC=75AVcore EDC =125A

Vcore SOC 0.75~1.2V

B5

VDDCR_SOC

B8

VDDCR_SOC

B11

VDDCR_SOC

B14

VDDCR_SOC

B17

VDDCR_SOC

B20

VDDCR_SOC

C4

VDDCR_SOC

C7

VDDCR_SOC

C10

VDDCR_SOC

C13

VDDCR_SOC

C16

VDDCR_SOC

C19

VDDCR_SOC

D3

VDDCR_SOC

E2

VDDCR_SOC

F7

VDDCR_SOC

F10

VDDCR_SOC

F13

VDDCR_SOC

F16

VDDCR_SOC

G3

VDDCR_SOC

G6

VDDCR_SOC

G9

VDDCR_SOC

G12

VDDCR_SOC

G15

VDDCR_SOC

G18

VDDCR_SOC

H2

VDDCR_SOC

J7

VDDCR_SOC

J10

VDDCR_SOC

J12

VDDCR_SOC

J14

VDDCR_SOC

J16

VDDCR_SOC

K3

VDDCR_SOC

K6

VDDCR_SOC

K9

VDDCR_SOC

K11

VDDCR_SOC

K13

VDDCR_SOC

K15

VDDCR_SOC

L2

VDDCR_SOC

L10

VDDCR_SOC

L12

VDDCR_SOC

L14

VDDCR_SOC

L16

VDDCR_SOC

L18

VDDCR_SOC

L20

VDDCR_SOC

L22

VDDCR_SOC

L24

VDDCR_SOC

L26

VDDCR_SOC

M9

VDDCR_SOC

M11

VDDCR_SOC

M13

VDDCR_SOC

M15

VDDCR_SOC

M17

VDDCR_SOC

M19

VDDCR_SOC

M21

VDDCR_SOC

M23

VDDCR_SOC

M25

VDDCR_SOC

N10

VDDCR_SOC

N12

VDDCR_SOC

N14

VDDCR_SOC

N16

VDDCR_SOC

N18

VDDCR_SOC

N20

VDDCR_SOC

N22

VDDCR_SOC

N24

VDDCR_SOC

N26

VDDCR_SOC

P9

VDDCR_SOC

P11

VDDCR_SOC

P13

VDDCR_SOC

R10

VDDCR_SOC

R12

VDDCR_SOC

T11

VDDCR_SOC

T13

VDDCR_SOC

U12

VDDCR_SOC

V13

VDDCR_SOC

8 38Tuesday, November 12, 2019

8 38Tuesday, November 12, 2019

8 38Tuesday, November 12, 2019

Vcore 0.75~1.5V

VCORE VCORE_SOC

AM4L

AM4L

M7

VDDCR_CPU

N3

VDDCR_CPU

N6

VDDCR_CPU

P2

VDDCR_CPU

R7

VDDCR_CPU

T3

VDDCR_CPU

T6

VDDCR_CPU

T9

VDDCR_CPU

U2

VDDCR_CPU

U10

VDDCR_CPU

V9

VDDCR_CPU

V11

VDDCR_CPU

W3

VDDCR_CPU

W6

VDDCR_CPU

W10

VDDCR_CPU

W12

VDDCR_CPU

Y2

VDDCR_CPU

Y9

VDDCR_CPU

Y11

VDDCR_CPU

Y13

VDDCR_CPU

AA7

VDDCR_CPU

AA10

VDDCR_CPU

AA12

VDDCR_CPU

AB3

VDDCR_CPU

AB6

VDDCR_CPU

AB9

VDDCR_CPU

AB11

VDDCR_CPU

AB13

VDDCR_CPU

AC2

VDDCR_CPU

AC10

VDDCR_CPU

AC12

VDDCR_CPU

AD7

VDDCR_CPU

AD9

VDDCR_CPU

AD11

VDDCR_CPU

AD13

VDDCR_CPU

AE3

VDDCR_CPU

AE6

VDDCR_CPU

AE10

VDDCR_CPU

AE12

VDDCR_CPU

AF2

VDDCR_CPU

AF9

VDDCR_CPU

AF11

VDDCR_CPU

AF13

VDDCR_CPU

AG7

VDDCR_CPU

AG10

VDDCR_CPU

AG12

VDDCR_CPU

AG14

VDDCR_CPU

AG16

VDDCR_CPU

AG18

VDDCR_CPU

AG20

VDDCR_CPU

AG22

VDDCR_CPU

AG24

VDDCR_CPU

AG26

VDDCR_CPU

AH3

VDDCR_CPU

AH6

VDDCR_CPU

AH9

VDDCR_CPU

AH11

VDDCR_CPU

AH13

VDDCR_CPU

AH15

VDDCR_CPU

AH17

VDDCR_CPU

AH19

VDDCR_CPU

AH21

VDDCR_CPU

AH23

A_VDD18S5

AM4 1.8V, 500mA

A_R1

A_R1

A_C3

A_C3

127K/4/1

8

A_Q2_FBA_Q2_EN

7

FB

6

A_VDD18S5

5

R2

R1

127K/4/1

0.1u/4/X7R/16V/K/X

0.1u/4/X7R/16V/K/X

A_R2

A_R2

100K/4/1

100K/4/1

22u/6/X5R/6.3V/M

22u/6/X5R/6.3V/M

0.8*[(R1+R2)/R1] = Vout

ABC16

ABC16

1U/4/X5R/6.3V/K

1U/4/X5R/6.3V/K

ABC17

ABC17

0.22U/4/X7R/16V/K

0.22U/4/X7R/16V/K

A_C5

A_C5

A_C4

A_C4

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

A_VDD18S5

A_C6

A_C6

2.2U/6/X5R/6.3V/K

2.2U/6/X5R/6.3V/K

CLR_CMOS

SHORT

NOT ADD ICT FOR RTCVDD PIN

CLEAR CMOS

NORMALOPEN

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

VDDCR_CPU

AH25

VDDCR_CPU

AH27

VDDCR_CPU

AJ2

VDDCR_CPU

AJ10

VDDCR_CPU

AJ12

VDDCR_CPU

AJ14

VDDCR_CPU

AJ22

VDDCR_CPU

AJ24

VDDCR_CPU

AK7

VDDCR_CPU

AK9

VDDCR_CPU

AK11

VDDCR_CPU

AK13

VDDCR_CPU

AL3

VDDCR_CPU

AL6

VDDCR_CPU

AL10

VDDCR_CPU

AL12

VDDCR_CPU

AL14

VDDCR_CPU

AM2

VDDCR_CPU

AM8

VDDCR_CPU

AN7

VDDCR_CPU

AN10

VDDCR_CPU

AN13

VDDCR_CPU

AP3

VDDCR_CPU

AP9

VDDCR_CPU

AP12

VDDCR_CPU

AR2

VDDCR_CPU

AT4

VDDCR_CPU

AU3

VDDCR_CPU

AU6

VDDCR_CPU

AU9

VDDCR_CPU

AU12

VDDCR_CPU

AU15

VDDCR_CPU

AV5

VDDCR_CPU

AV8

VDDCR_CPU

AV11

VDDCR_CPU

AV14

VDDCR_CPU

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

CPU POWER & GND

CPU POWER & GND

CPU POWER & GND

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

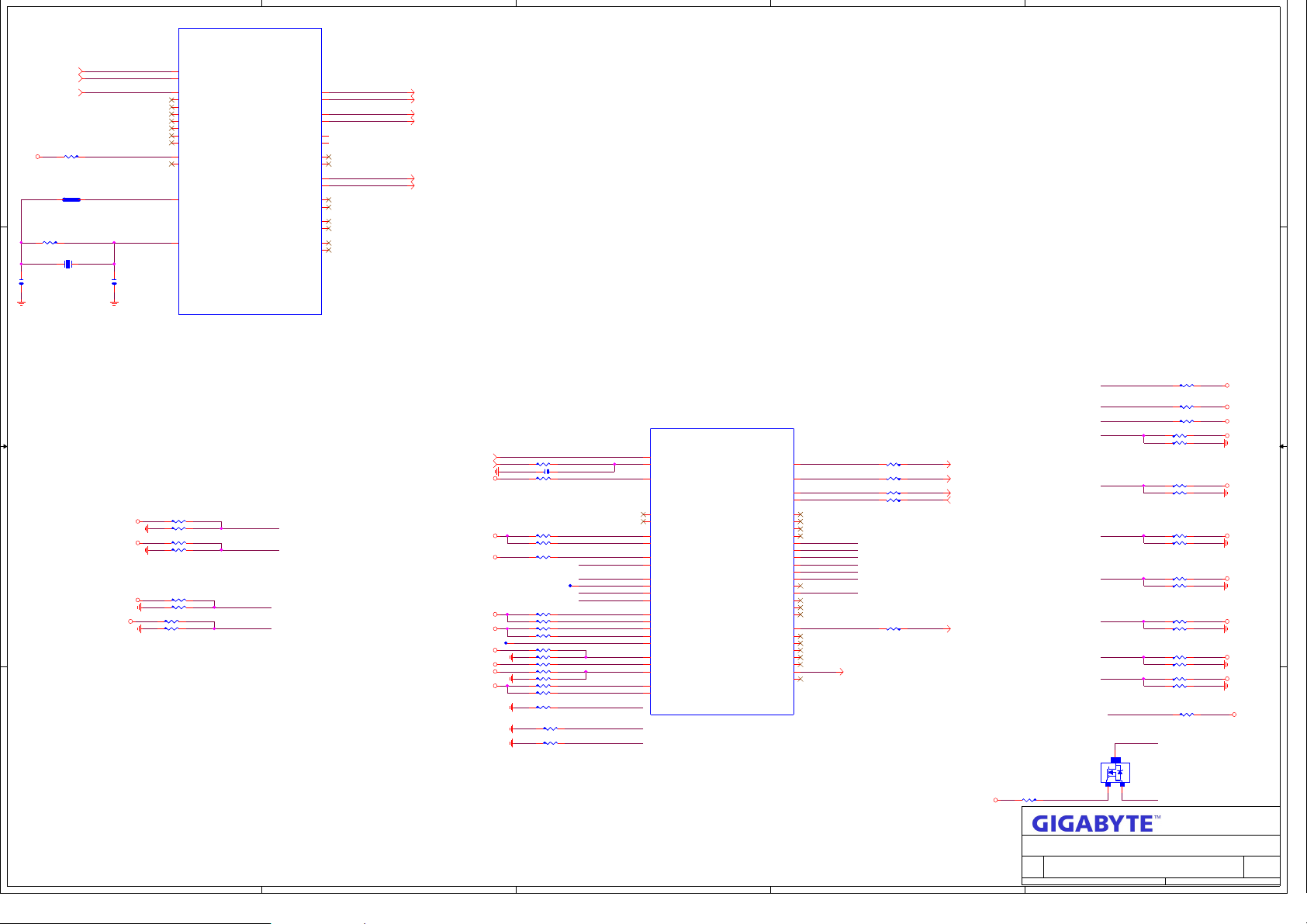

Page 9

8

D D

C C

B B

7

6

A48M_X1

AXR2 1M/4AXR2 1M/4

A48M_X2

AX2

AX2

31

2 4

AXC3

AXC3

12p/4/NPO/50V/J

12p/4/NPO/50V/J

48M/12p/30ppm/3.2*2.5/50/S [10XT5-848000-00R]

48M/12p/30ppm/3.2*2.5/50/S [10XT5-848000-00R]

AXC4

AXC4

12p/4/NPO/50V/J

12p/4/NPO/50V/J

5

VCC3

VCC3

A_VDD1V8

X16 Slot

M.2 Socket

Promontory

DB_CLK<18>

LPC_CLK0<31>

LPC_CLK1<18>

4

AR83 2K/4/1AR83 2K/4/1

AR84 8.2K/4/1AR84 8.2K/4/1

AR85 1K/4/1/XAR85 1K/4/1/X

AR86 10K/4/1AR86 10K/4/1

AR87 1K/4/1/XAR87 1K/4/1/X

AR88 8.2K/4/1AR88 8.2K/4/1

AR90 1K/4/1/XAR90 1K/4/1/X

A_GFX_CLKP<16>

A_GFX_CLKN<16>

A_GPP_CLKP1<32>

A_GPP_CLKN1<32>

PM_CLKP<12>

PM_CLKN<12>

LPC_CK0

LPC_CK1

LFRAME-

A_SPI_CLK

A48M_X1

A48M_X2

AR106 10/4AR106 10/4

AR97 10/4AR97 10/4

AR69 22/4AR69 22/4

LAD0<18,31>

LAD1<18,31>

LAD2<18,31>

LAD3<18,31>

LFRAME-<18,31>

LDRQ0-<18>

SERIRQ<18,31>

AGPIO88<38>

A_SPI_CLK SPI_CLK

A_SPI_CS-

A_SPI_DI

A_SPI_DO

A_SPI_HD-

AR56 22/4AR56 22/4

AR57 22/4AR57 22/4

AR58 22/4AR58 22/4

AR59 22/4AR59 22/4

AR128 22/4AR128 22/4

AR129 22/4AR129 22/4

LPC_CK0

LPC_CK1

LAD0

LAD1

LAD2

LAD3

LFRAMELDRQ0SERIRQ

AGPIO88

SPI_CS-

SPI_DI

SPI_DO

SPI_WP-A_SPI_WPSPI_HD-

AM4E

AM4E

AF6

GFX_CLKP

AF7

GFX_CLKN

AG5

GPP_CLK0P

AG6

GPP_CLK0N

AH4

GPP_CLK1P

AH5

GPP_CLK1N

AH7

GPP_CLK2P

AH8

GPP_CLK2N

AJ6

GPP_CLK3P

AJ7

GPP_CLK3N

AJ1

X48M_X1

AH1

X48M_X2

AU20

LPCCLK0/EGPIO74

AU19

LPCCLK1/EGPIO75

AW20

LAD0/EGPIO104

AV21

LAD1/EGPIO105

AT21

LAD2/EGPIO106

AT20

LAD3/EGPIO107

AW18

LFRAME_L/EGPIO109

AT15

ESPI_ALERT_L/LDRQ0_L/EGPIO108

AW21

SERIRQ/AGPIO87

AV19

LPC_CLKRUN_L/AGPIO88

AV18

LPC_PD_L/AGPIO21

AT18

EGPIO70

AW14

SPI_CLK/ESPI_CLK/EGPIO117

AT17

SPI_CS1_L/EGPIO118

AW15

SPI_CS2_L/ESPI_CS_L/EGPIO119

AU14

SPI_DI/ESPI_DAT1/EGPIO120

AU16

SPI_DO/ESPI_DAT0/EGPIO121

AV16

SPI_WP_L/ESPI_DAT2/EGPIO122

AV15

SPI_HOLD_L/ESPI_DAT3/EGPIO133

AU17

SPI_TPM_CS_L/AGPIO76

3

CLK/USB/SPI/LPC

CLK/USB/SPI/LPC

AM4 REV 0.92

AM4 REV 0.92

PART 5 OF 12

PART 5 OF 12

AM4/[10SC1-P01331-11R]

AM4/[10SC1-P01331-11R]

48M_OSC

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB0_ZVSS

USB1_ZVSS

USB2_ZVSS

USB3_ZVSS

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

USB_SS_3TXP

USB_SS_3TXN

USB_SS_3RXP

USB_SS_3RXN

AR7

AT11

AU7

AU8

AW8

AW9

AU10

AU11

AV9

AV10

AJ3

AN6

AK6

AK5

AJ4

AK8

AF3

AF4

Y3

Y4

AB1

AC1

AA2

AA3

AC3

AC4

AD2

AE2

AG2

AG3

AE1

AF1

2

USB_ZVSS

A_HSDP0

A_HSDN0

A_HSDP1

A_HSDN1

A_HSDP2

A_HSDN2

A_HSDP3

A_HSDN3

A_USB_ZVS0

A_USB_ZVS1

A_USB_ZVS2

A_USB_ZVS3

A_SS_ZVS S

A_SS_ZVDD

A_SS_TX0P

A_SS_TX0N

A_SS_RX0P

A_SS_RX0N

A_SS_TX1P

A_SS_TX1N

A_SS_RX1P

A_SS_RX1N

A_SS_TX2P

A_SS_TX2N

A_SS_RX2P

A_SS_RX2N

A_SS_TX3P

A_SS_TX3N

A_SS_RX3P

A_SS_RX3N

AR9 11.8K/4/1AR9 11.8K/4/1

AR10 200/4/1/XAR10 200/4/1/X

AR11 200/4/1/XAR11 200/4/1/X

AR14 200/4/1/XAR14 200/4/1/X

AR15 200/4/1/XAR15 200/4/1/X

AR16 1K/4/1AR16 1K/4/1

AR17 1K/4/1AR17 1K/4/1

A_SS_TX0P <19>

A_SS_TX0N <19>

A_SS_RX0P <19>

A_SS_RX0N <19>

A_SS_TX1P <19>

A_SS_TX1N <19>

A_SS_RX1P <19>

A_SS_RX1N <19>

A_SS_TX2P <19>

A_SS_TX2N <19>

A_SS_RX2P <19>

A_SS_RX2N <19>

A_SS_TX3P <19>

A_SS_TX3N <19>

A_SS_RX3P <19>

A_SS_RX3N <19>

1

A_HSDP0 <19>

A_HSDN0 <19>

A_HSDP1 <19>

A_HSDN1 <19>

A_HSDP2 <19>

A_HSDN2 <19>

A_HSDP3 <19>

A_HSDN3 <19>

A_VDDPS5

★1.8V SPI ROM USE

A_VDD1V8 A_VDD1V8

ARN1

ARN1

1K/8P4R/4

1K/8P4R/4

9 38Tuesday, November 12, 2019

9 38Tuesday, November 12, 2019

9 38Tuesday, November 12, 2019

1

A_VDD1V8

VCC3

NR237

AQB1

AQB1

AQB2

AQB2

NR237

330/4/1

330/4/1

SPI_CS2-

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

SOT23

SOT23

132

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

SOT23

SOT23

132

SPI_CS2-

A_SPI_WP-

4

B_BIOS

B_BIOS

1

CS#

2

SO

3

WP#

4

VSS

128M/SPI/SO8/200mil/S

128M/SPI/SO8/200mil/S

VDD

HOLD#

SCK

8

7

6

5

SI

A_VDD1V8

AC19 0.1u/4/X7R/16V/KAC19 0.1u/4/X7R/16V/K

A_SPI_HD-A_SPI_DI

A_SPI_CLK

A_SPI_DO

3

A_SPI_WP-

A_SPI_DO

A_SPI_DI

AR42 8.2K/4/XAR42 8.2K/4/X

AR101 8.2K/4/XAR101 8.2K/4/X

AR102 8.2K/4/XAR102 8.2K/4/X

Fix flash BIOS fail Issue 1K to 33 0 ohm

CS2

CS1

-SPI_HOLD_M<31>

-SPI_HOLD_B<31>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

-SPI_HOLD_M

-SPI_HOLD_B

DDR4 CHANNEL A

DDR4 CHANNEL A

DDR4 CHANNEL A

B450 AORU S M 1.05

B450 AORU S M 1.05

B450 AORU S M 1.05

1 2

3 4

5 6

7 8

指定用

DII

NR238

NR238

330/4/1

330/4/1

指定用

DII

SPI_CS1-

AQM1

AQM1

AQM2

AQM2

-SPI_HOLD_B

A A

SPI_CS1-

1

2

A_SPI_WP-

3

4

8

NR235 8.2K/4NR235 8.2K /4

M_BIOS

M_BIOS

CS#

SO

WP#

VSS

128M/SPI/SO8/200mil/S

128M/SPI/SO8/200mil/S

VDD

HOLD#

SCK

8

7

6

5

SI

A_VDD1V8

AC18 0.1U/4/X7R/16V/KAC18 0.1U/4/X7R/16V/K

A_SPI_HD-A_SPI_DI

A_SPI_CLK

A_SPI_DO

7

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

SOT23

SOT23

132

A_SPI_CS- A_SPI_CS-CS1 CS2

MMBT2222A/SOT23/600mA/40

MMBT2222A/SOT23/600mA/40

SOT23

SOT23

132

6

-SPI_HOLD_M

M_BIOS

M_BIOS

SMD SPI SOCKET 8P 200MIL LOTES/[10SL2-000008-31R]/X

SMD SPI SOCKET 8P 200MIL LOTES/[10SL2-000008-31R]/X

NR234 8.2K/4NR234 8.2K /4

5

Page 10

8

Rev:0.5

D D

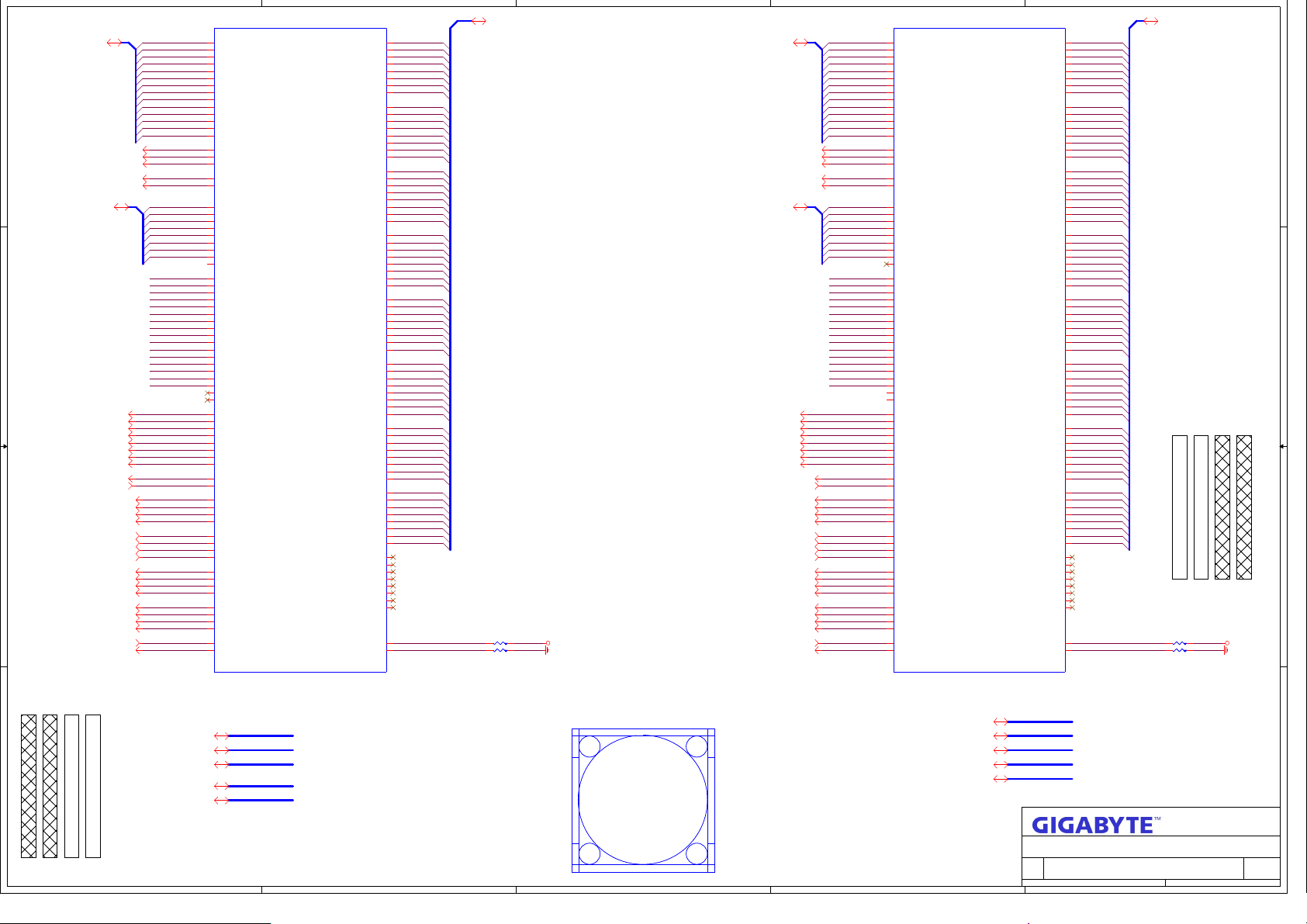

MODT_A[0.. 3]<4>

MDA[0..63]<4>

MAAA[0..16]<4>

DQSA[0..7]<4>

-DQSA[0..7]<4>

C C

B B

MAC11 1u/4/X5R/6.3V/ KMAC11 1u/4/X5R/ 6.3V/K

MAC16 0.1U/4/X7R/ 16V/KMAC16 0.1U/ 4/X7R/16V/K

VPP_SPD

A A

8

DDRVTT

MODT_A[0.. 3]

MDA[0..63]

MAAA[0..16]

DQSA[0..7]

-DQSA[0..7]

VDDIO_MEM

VPP_MEM

VREF_DDRA

SMBDATA<7,11,24,27,31,38>

SMBCLK<7,11,24,27,31,38>

MA_BA1<4>

MA_BA0<4>

MA_BG1<4>

MA_BG0<4>

MA_CLKL1<4>

MA_CLKH1<4>

MA_CLKL0<4>

MA_CLKH0<4>

MA0_CS0-<4> MA1_CS0-<4>

MA0_CKE1<4>

MA0_CKE0<4>

MAAA[0..17]<4>

SMBDATA

SMBCLK

MA_CLKL1

MA_CLKH1

MA_CLKL0

MA_CLKH0

MA0_CKE1

MA0_CKE0

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

MAAA16

MAAA17

7

DDR4_4

DDR4_4

77

VTT

221

VTT

2

VSS

4

VSS

6

VSS

9

VSS

11

VSS

13

VSS

15

VSS

17

VSS

20

VSS

22

VSS

24

VSS

26

VSS

28

VSS

31

VSS

33

VSS

35

VSS

37

VSS

39

VSS

42

VSS

44

VSS

46

VSS

48

VSS

50

VSS

53

VSS

55

VSS

57

VSS

94

VSS

96

VSS

98

VSS

101

VSS

103

VSS

105

VSS

107

VSS

109

VSS

112

VSS

114

VSS

116

VSS

118

VSS

120

VSS

123

VSS

125

VSS

127

VSS

129

VSS

131

VSS

134

VSS

136

VSS

138

VSS

147

VSS

149

VSS

151

VSS

154

VSS

156

VSS

158

VSS

160

VSS

162

VSS

165

VSS

167

VSS

169

VSS

171

VSS

173

VSS

176

VSS

178

VSS

180

VSS

182

VSS

184

VSS

187

VSS

189

VSS

191

VSS

193