Page 1

L

L

A

A

U

U

Monitor Models:

1493

1793

1993

2093

2793

3693

Safety Isolating

Transformer Models:

ISO XFR-75W

ISO XFR-100W

N

N

A

A

M

M

E

E

C

C

I

I

V

V

R

R

E

E

S

S

Page 2

2 YEAR LIMITED WARRANTY

This product is warranted by CERONIX to be free of defects in material

and workmanship for a period of two years from the date of purchase.

All parts and labor are free of charge during the warranty period.

This warranty does not cover mechanical breakage due to physical abuse.

It is the customer's responsibility for shipping the defective unit to and from

CERONIX or one of the authorized service centers for repair.

Please attach a note describing the problem.

CERONIX Inc.

13350 New Airport Road

Auburn, CA. 95602-7419

Phone: (530) 886-6400

FAX: (530) 888-1065

WEB: www.ceronix.com

CERONIX shall not be liable for any consequential damages, including

without limitation damages resulting from loss of use.

Ceronix will repair XX93 monitors after the 2 year warranty,

for a minimal charge, plus shipping to and from Ceronix.

®

Recognized under the Component Program of Underwriters Laboratories Inc., the

Canadian Standards Association, and TÜV Product Service.

Compliance to the following Standards:

IEC 60950, CAN/CSA-C22.2 No. 60950-00, ANSI/UL 60950, CAN/CSA-C22.2 No.

1-98, IEC 65:85 + A1:87 + A2:89 + A3:92.

ISO 9001:1994 Certified through TÜV Management Service.

COPYRIGHT 2002

CERONIX

All rights reserved.

The information contained in this manual

is subject to change without prior notice.

©

Page 3

ABOUT THIS MANUAL

This manual is specifically written to aid the service technician, repairing

CERONIX Models 1493, 1793, 1993, 2093, 2793, and 3693 color monitors.

There are three main sections:

1. General Description.

2. Circuit Description.

3. Repair Setup and Appendix.

Introduction Block

Diagram

Installation

Instructions

Description

BLOCK

Diagram

Schematics

&

Assembly

Drawings

Circuit

Description

Trouble

shooting

Handbook

Appendix

Convergence

Degaussing

P/O Form

PRAs

To understand how the Monitor works, it is best to know what each circuit

does and how each circuit relates to the other circuits. The Block Diagram is

presented in a simplified view and a comprehensive view to accomplish the goal of

understanding the whole unit. Once the general picture is clear, the complexity of

each circuit will be easier to understand.

The Circuit Description is also written in two views, a simplified view and a

detailed view to help give the reader a clear understanding of what each

component does. This understanding is most helpful for the more complex

problems or multiple problems that sometimes occur.

The power supply trouble shooting section describes methods used to power up

various monitor circuits, when there is a fault in the monitor, which disables the

power supply.

The appendix includes; filament voltage test, convergence procedure,

replacement parts purchase order form, degaussing coil attachment specification,

high pot test, wire routing drawing, production assembly drawings (PADs), C, I, J,

& K film resistor arrays and a parts list addendum. The parts list addendum is

used to add new information describing part changes. Tables, suitable for pasting

on these pages, will be published as new variations of the XX93 monitors are

produced.

i

Page 4

TABLE OF CONTENTS

About This Manual.............................................................................................................

Table of Contents................................................................................................................

CERONIX Monitor Simplified Block Diagram.................................................................

Installation Instructions; English, French, and German................................................

CERONIX Monitor Electrical Specification......................................................................

1493, 1793, 1993, 2093, 2793, and 3693 General Operation Description.

Video Interface, Amps & Beam Current Sense........

Auto Bias, Bias Sync Delay, & Auto Bright.............

CRT, Blanking, Sync, & Vertical deflection.............

Horizontal Deflection & Remote...............................

Horizontal Size & Power Supply...............................

P/S, Safety Shutdown Circuits, Degaussing.............

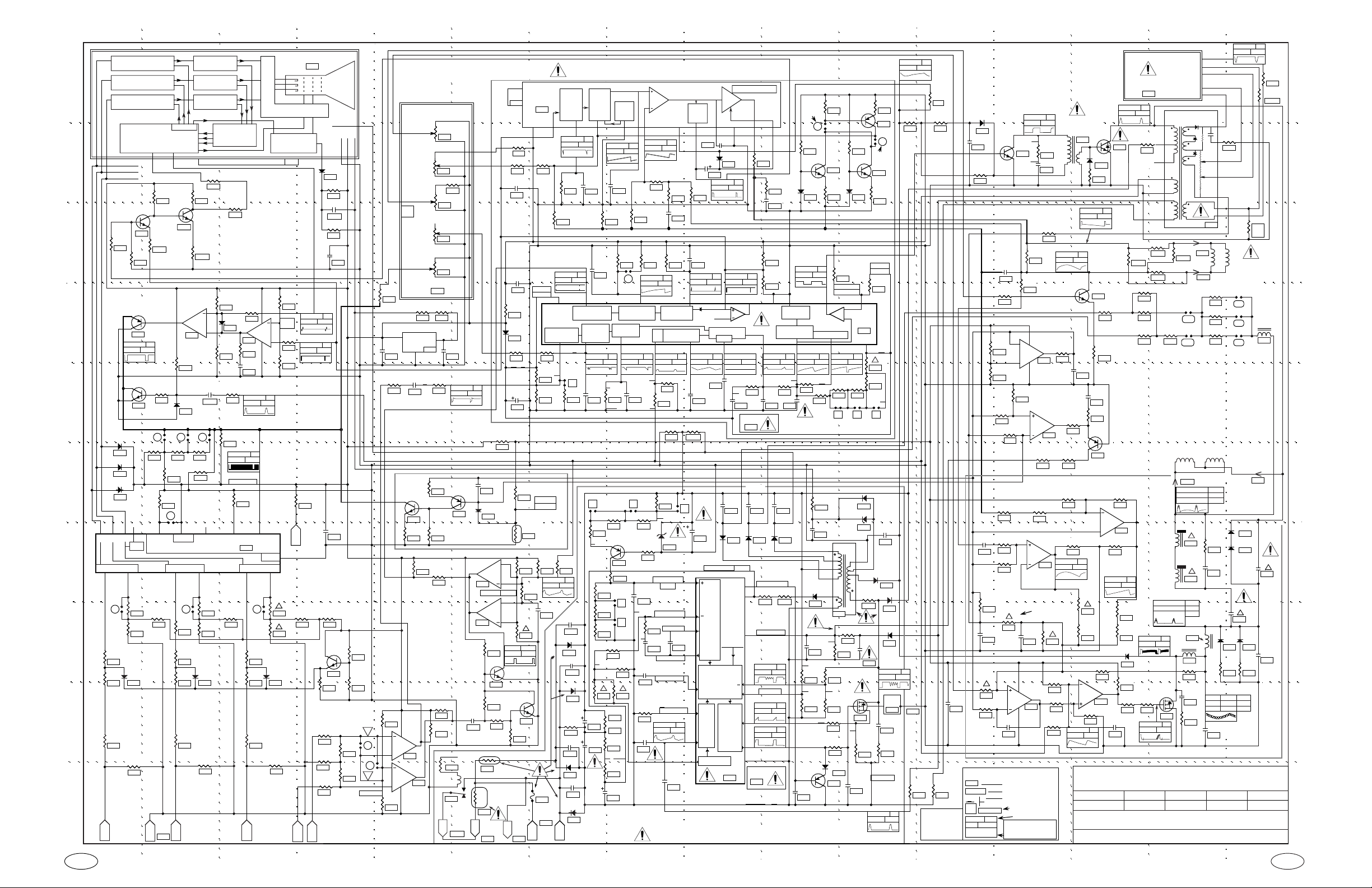

Monitor BLOCK DIAGRAM..............................................................................................

Monitor Schematics and Assembly Drawings

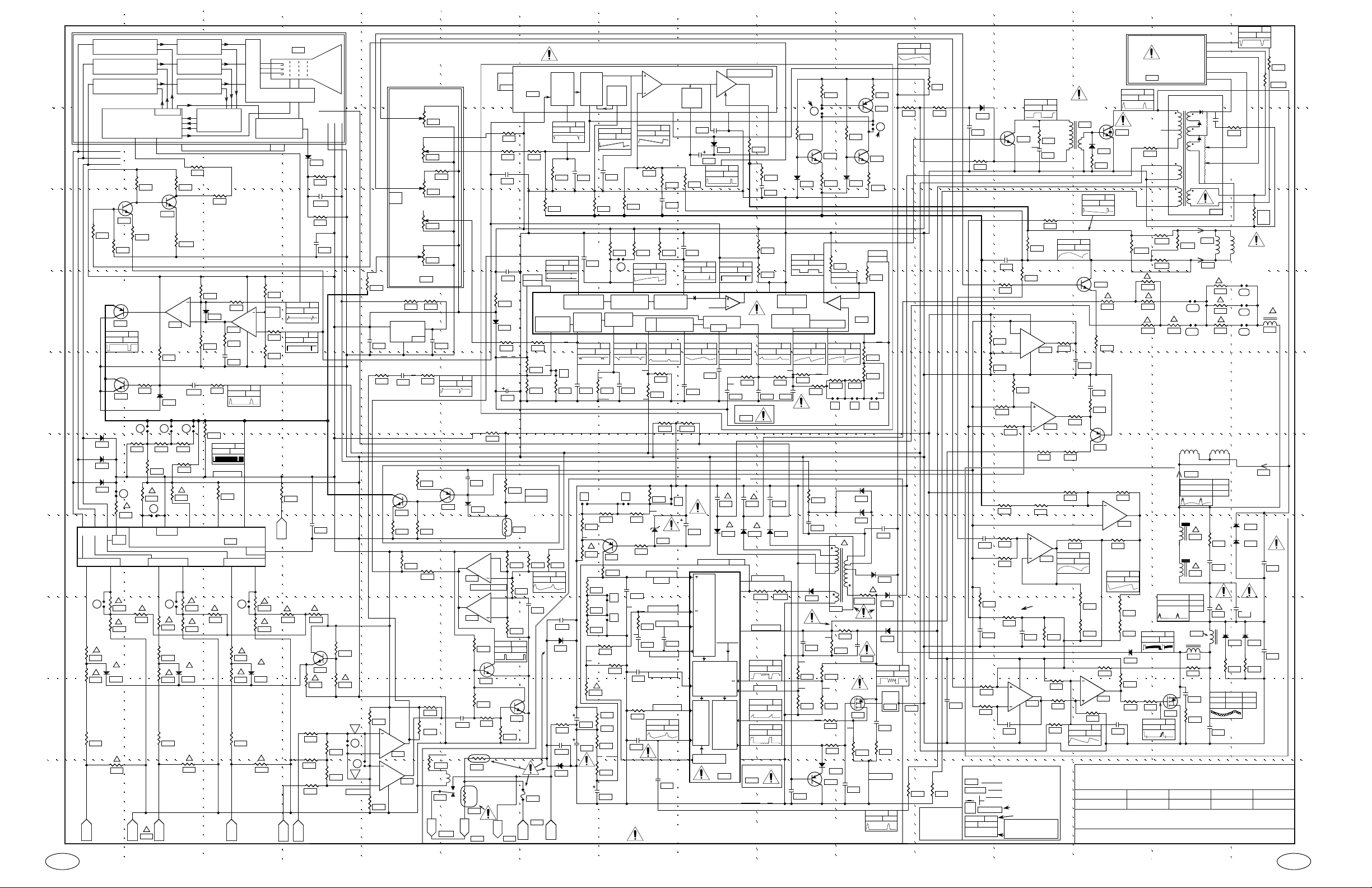

1493-CGA Main Board Schematic..(4233/4235)...............................................................

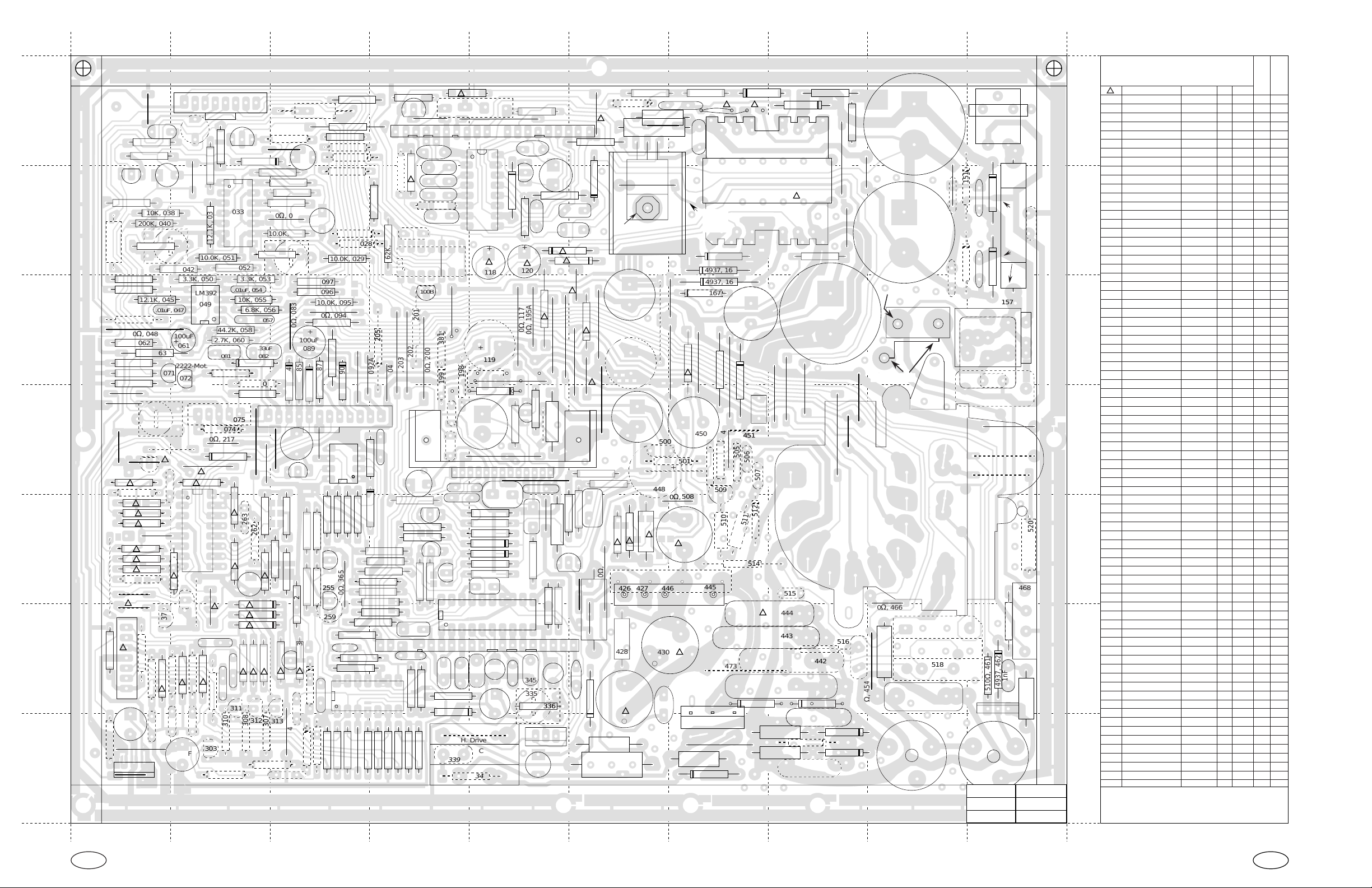

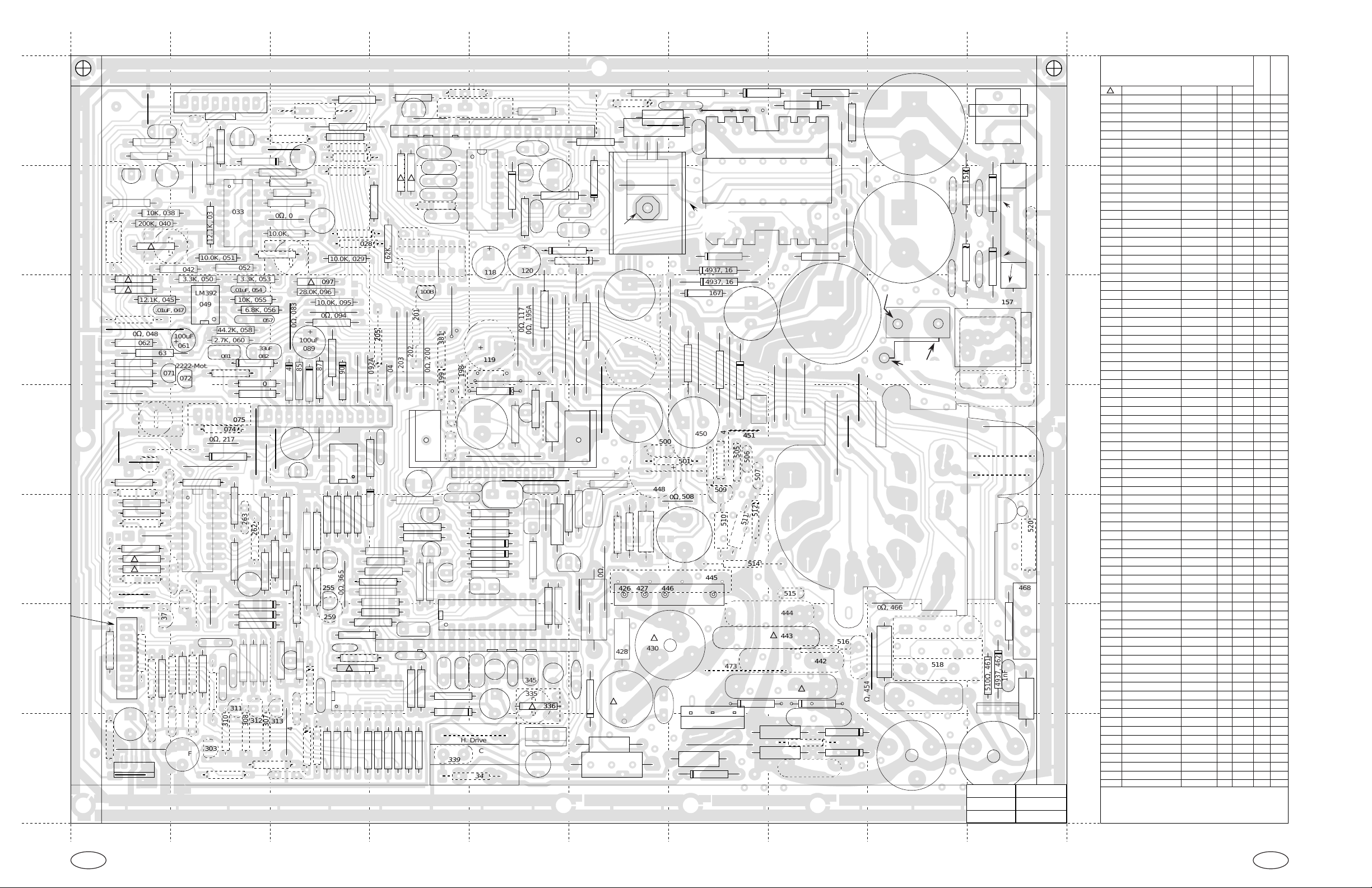

1493-CGA Main Board Technician Assembly Drawing...................................................

1493-VGA/SVGA Main Board Schematic..(4200/4252)....................................................

1493-VGA/SVGA Main Board Technician Assembly Drawing........................................

1793-VGA Main Board Schematic..(4243/4244)..............................................................

1793-VGA Main Board Technician Assembly Drawing...................................................

1793-SVGA Main Board Schematic ..(4247/4250)............................................................

1793-SVGA Main Board Technician Assembly Drawing.................................................

1993-VGA Main Board Schematic..(4221/4255)...............................................................

1993-VGA Main Board Technician Assembly Drawing...................................................

1993-SVGA Main Board Schematic..(4249/4256).............................................................

1993-SVGA Main Board Technician Assembly Drawing.................................................

2093-CGA Main Board Schematic..(4112/4166)...............................................................

2093-CGA Main Board Technician Assembly Drawing...................................................

2093-VGA Main Board Schematic..(4224/4227/4108)......................................................

2093-VGA Main Board Technician Assembly Drawing...................................................

2793-CGA Main Board Schematic..(4104)........................................................................

2793-CGA Main Board Technician Assembly Drawing...................................................

2793-VGA Main Board Schematic..(4231)........................................................................

2793-VGA Main Board Technician Assembly Drawing...................................................

2793-VGA Main Board Schematic..(4254)........................................................................

2793-VGA Main Board Technician Assembly Drawing...................................................

3693-CGA Main Board Schematic..(4172)........................................................................

3693-CGA Main Board Technician Assembly Drawing...................................................

Video Board Schematic......................................................................................................

Video Board Technician Assembly Drawing..(Component Side).....................................

Video Board Technician Assembly Drawing..(Conductor Side).......................................

Safety Critical Components for XX93 Monitors..(English)..............................................

Safety Critical Components for XX93 Monitors..(German)..............................................

Replacement Part List.......................................................................................................

Blocks A-D...............................

Blocks E-G...............................

Blocks H-L...............................

Blocks M-P..............................

Blocks Q-T...............................

Blocks U-Z...............................

i

ii-iii

1

2-4

5-8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45-63

Detailed Circuit Description

Video Interface Circuit, Function, Description (+ & - Analog)........................................

5.6V to 1.1V, -Analog, DC, Video Interface Circuit Description......................................

0V to .7V, +Analog, DC Video Interface Circuit Description...........................................

1Vp-p, +Analog, AC Video Interface Circuit Description.................................................

64

65

66

67

ii

Page 5

TABLE OF CONTENTS

Video Amplifier Circuit, Function, Description.................................................................

Video Amplifier Circuit Description and Schematic.........................................................

Video Board Power Supply and Arc Protect Schematic....................................................

CRT Auto Bias and Auto Bright Circuit, Function, Description......................................

CRT Auto Bias, Auto Bright, and Vertical Sync Delay Circuit Description....................

CRT Auto Bias and Auto Bright Schematic......................................................................

Monitor, Block Diagram Review........................................................................................

Blanking, Master Gain, and Fault Circuit, Function, Description..................................

Blanking, Master Gain, and Fault Circuit Description....................................................

Blanking, Master Gain, Beam Limiter, and Fault Schematic.........................................

Vertical and Horizontal Sync Circuit Description.............................................................

Vertical Deflection Circuit Description and Schematic....................................................

Horizontal Deflection Circuit Description and Schematic................................................

Horizontal Raster Width Control Circuit Description......................................................

Horizontal Raster Width and Position Control Schematic...............................................

Dynamic Focus Circuit Function and Description............................................................

Vertical Booster Amplifier Circuit and Description..........................................................

Simplified Power Supply Circuit, Function, Description..................................................

Switch Mode Power Supply Circuit Description and Schematic......................................

Trouble Shooting and Repair

Equipment Setup for repairing the Model XX93 Monitor..(English)...............................

Equipment Setup for repairing the Model XX93 Monitor..(German)..............................

Power Supply Trouble Shooting Tips.................................................................................

Trouble Shooting Handbook...............................................................................................

Filament Voltage Test..(English).......................................................................................

Filament Voltage Test..(German)......................................................................................

Setup and Convergence Procedure..(English)...................................................................

Setup and Convergence Procedure..(German)...................................................................

Replacement Parts, Purchase Order Form........................................................................

1493 Degaussing Coil Attachment Specification...............................................................

1793, 1993, 2093 Degaussing Coil Attachment Specification...........................................

2793, 3693 Degaussing Coil Attachment Specification.....................................................

HighPot, for Shock Hazards, Circuit Description..(English)............................................

HighPot, for Shock Hazards, Circuit Description..(German)...........................................

Wire Routing Instructions..................................................................................................

Precision Resistor Arrays..(C, I, J).....................................................................................

Precision Resistor Array..(K)..............................................................................................

Precision Resistor Array..(Blue).........................................................................................

Vertical Deflection Amplifier-Booster Technician Assembly Drawing............................

Monitor Input Drive Signal Worksheet.............................................................................

Declaration of Conformity..................................................................................................

68

68-69

70

71

72

73

74

75

76

77

78

79-81

82-83

84

85

86

87

88-89

90-91

92

93

94

95-97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

ISO XFR-75W and ISO XFR-100W Safety Isolating Transformer..................................

Circuit Description..(English).............................................................................................

Auto Voltage Select Schematic and Assembly Drawing...................................................

Circuit Description..(German)............................................................................................

Installation Instructions.....................................................................................................

Specifications.......................................................................................................................

Isolation Transformer Trouble shooting..(English)...........................................................

Isolation Transformer Troubleshooting..(German)...........................................................

Manual Voltage Select Schematic and Assembly Drawing..............................................

Part List Addendum...........................................................................................................

115

116

117

118

119-121

122-123

124

125

126

127-130

iii

Page 6

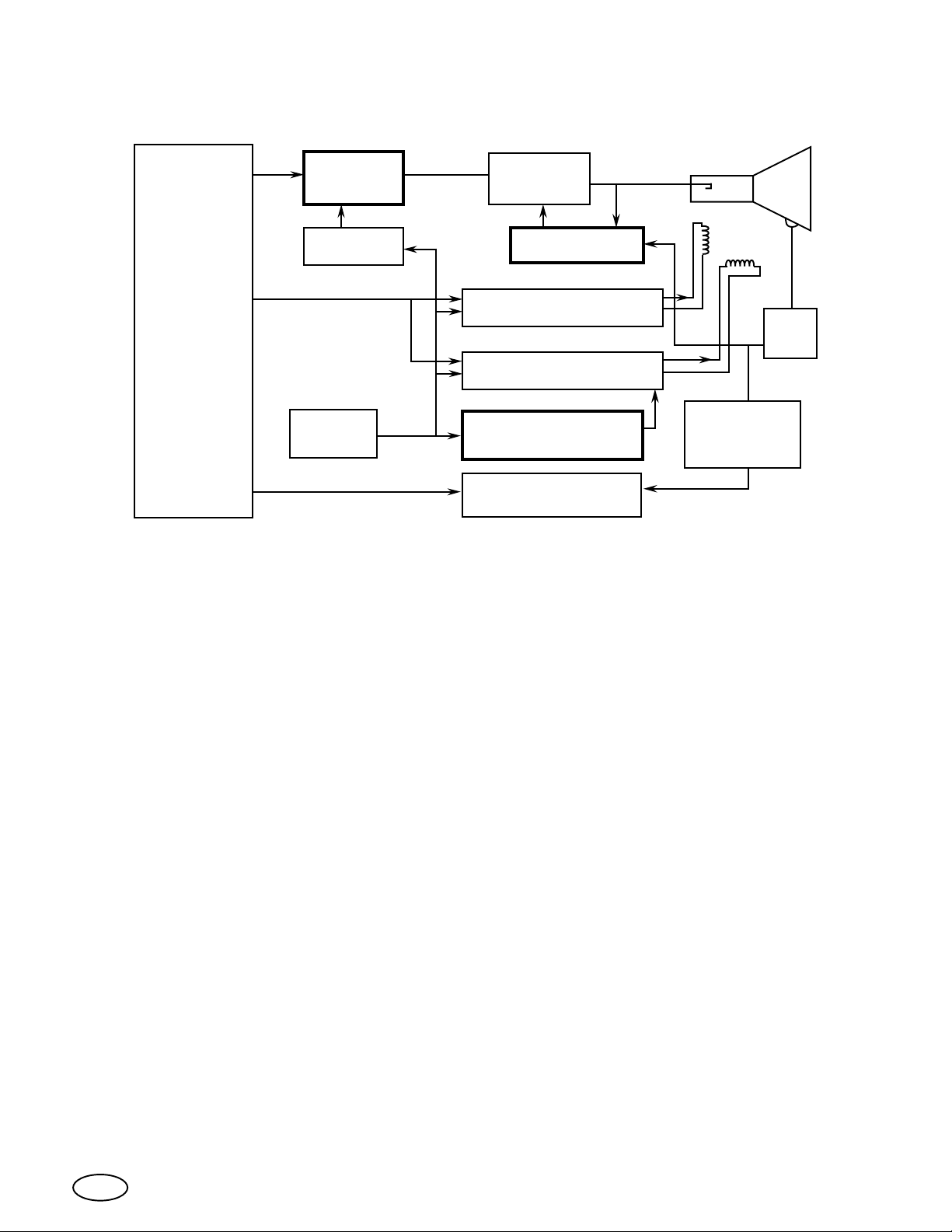

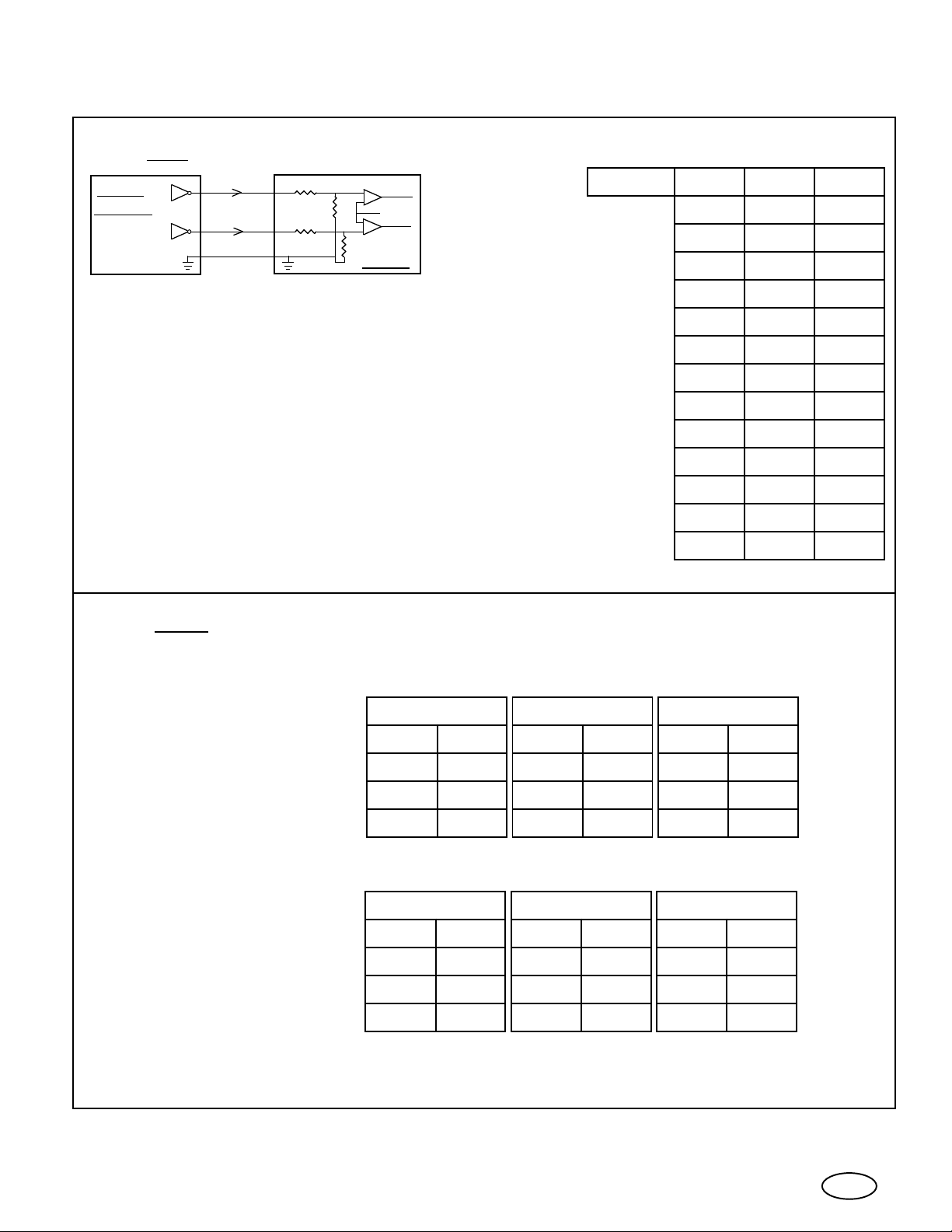

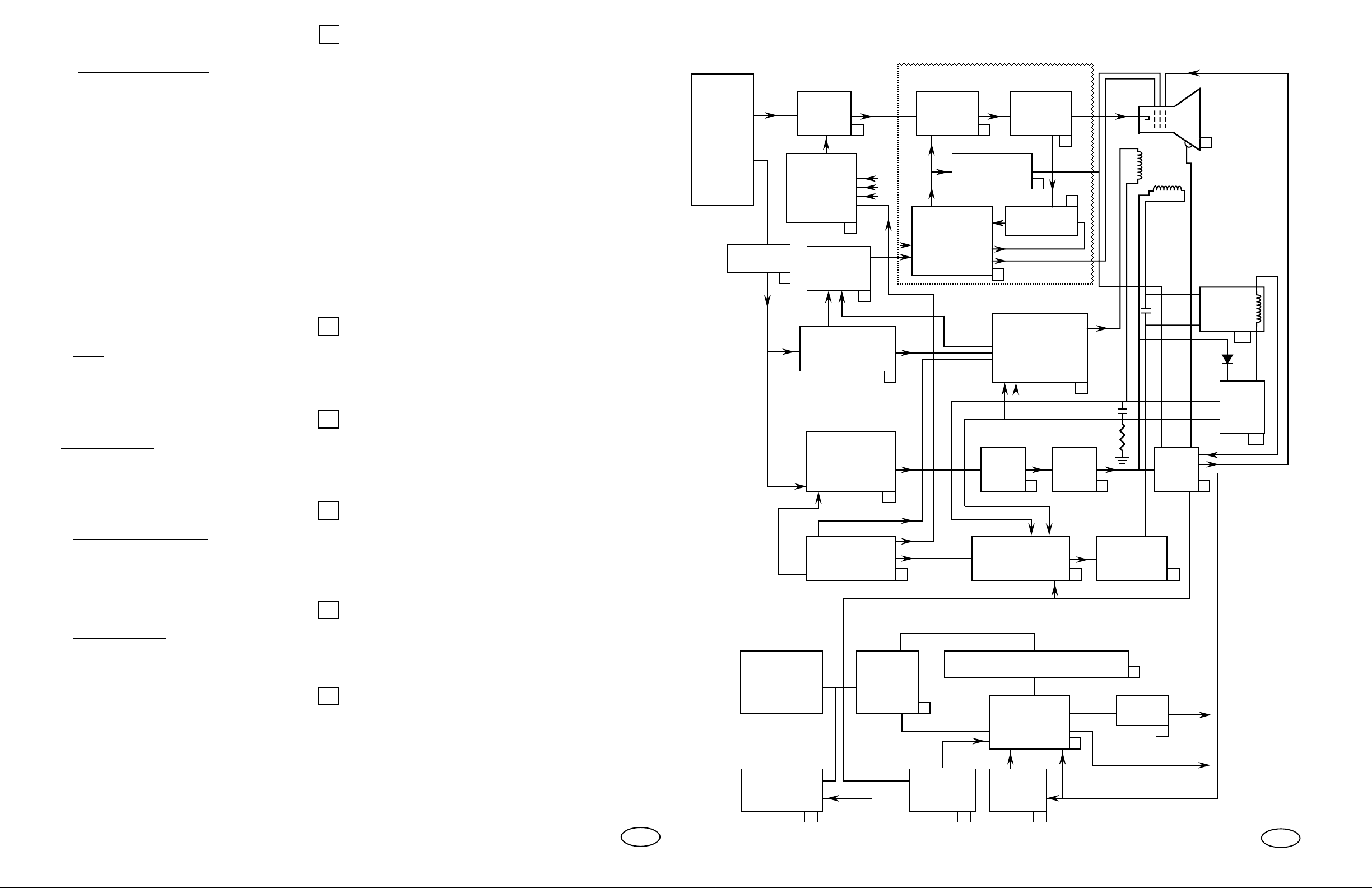

Monitor Simplified Block Diagram.

VIDEO

Output

Drive

Electronics

SYNC

Output

Isolated

Power

This block diagram gives a broad view of the circuit organization of the 1493,

1793, 1993, 2093, 2793, and 3693 monitors. The blocks with the bold outline

represent circuits which provide these monitors with a wide range of

operating conditions without the need for adjustment.

VIDEO

Interface

Blanking

Remote

Controls

VIDEO

Amps.

AUTO BIAS

Vertical Deflection

Horizontal Deflection

Horizontal Size

Control

POWER SUPPLY

CRT

FBT

IB

Fault &

High Temp.

Detection

The video interface circuit can be programmed to accept; +Analog AC or

DC coupled, -Analog, and 4 line TTL. The M. GAIN or contrast control is

located on the remote control board.

The auto bias circuit eliminates the need for the color setup procedure.

This circuit is designed to actively compensate for picture tube drift which

normally causes unbalanced color. The auto bias circuit also adjusts the

CRT gain to compensate for gain loss with age.

The horizontal size control circuit permits the horizontal size to be adjusted

from a remote control board. This circuit is also used to compensate for

pincushion distortion and blooming. Anti-blooming is accomplished by

correcting horizontal size variations which are caused by the additional load

on the flyback transformer under high beam current conditions.

Careful reading of all the information presented in this manual is a good

way to learn how to repair the CERONIX monitor.

1

Page 7

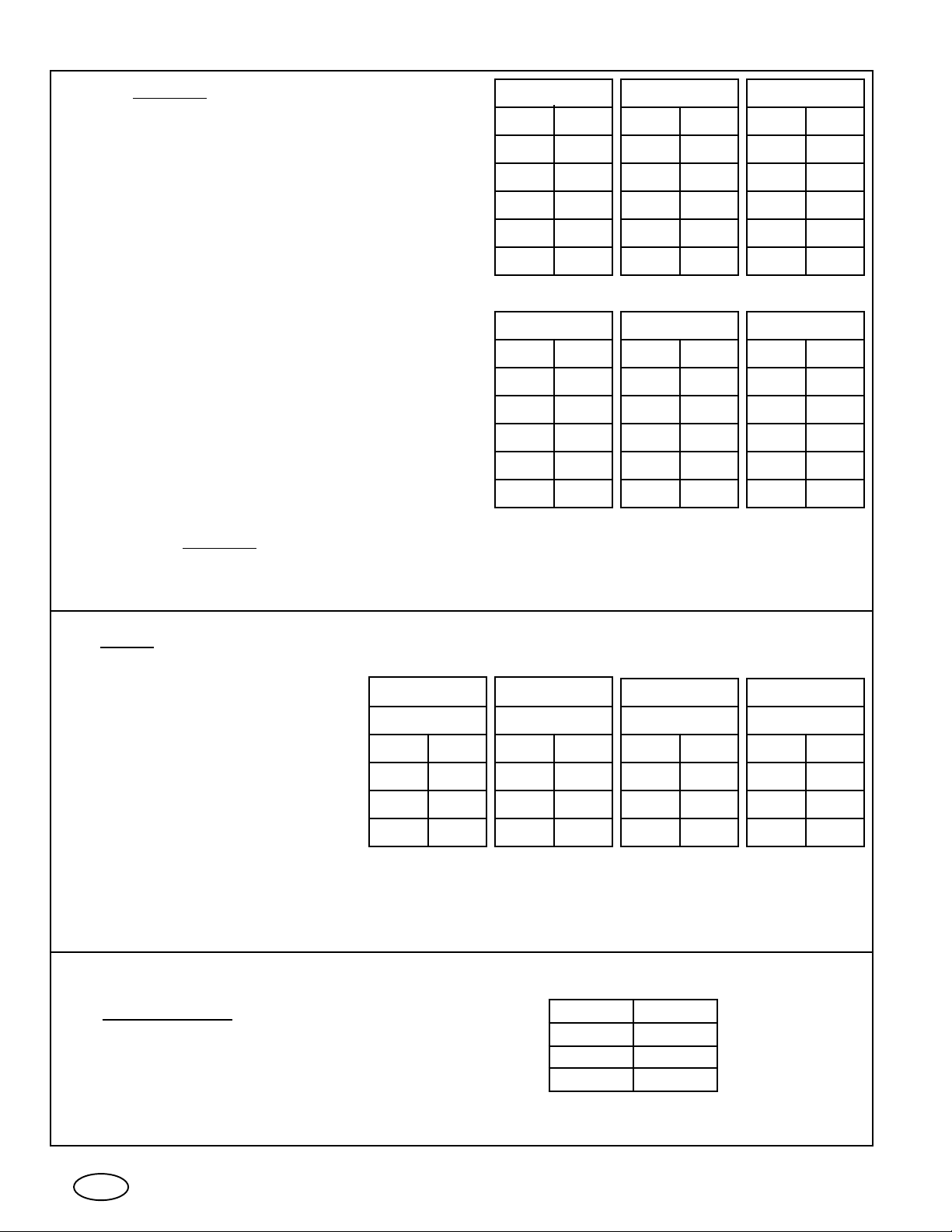

Installation Instructions For The XX93 Monitors.

1.

A 3 amp slow blow fuse (for the degaussing current) and a 75 VA isolation

transformer are the minimum requirements for using our monitor in a product.

2.

Unpack the monitor.

3.

Install the monitor in the enclosure.

4.

Connect the green/yellow ground wire to the earth ground connection on the enclosure.

This wire is connected to the ground screw, located on the monitor chassis behind the

serial number label.

Refer to the installation instructions supplied

by the system manufacturer for details of

mounting the monitor in the enclosure.

WARNING!

!

Failure to connect this ground wire before applying power is not

allowed, since this condition can produce a shock hazard. The

chassis to mains connector resistance shall not exceed 100mΩ.

Check that the following wires are properly connected;

5.

Green wire from the CRT aquadag braid to the video board.

A.

12 conductor flat cable from the video board to the main board.

B.

Red high voltage wire from the flyback transformer

C.

to the picture tube anode cap.

Yoke cable from the yoke to the main board.

D.

Remote cable from the remote control board to the main board.E.

Note;

6.

Plug in the

seven conductor

video connector.

7.

Plug in the power connector

from the isolation transformer.

Be sure these wires are secured such that they do not touch any metal parts.

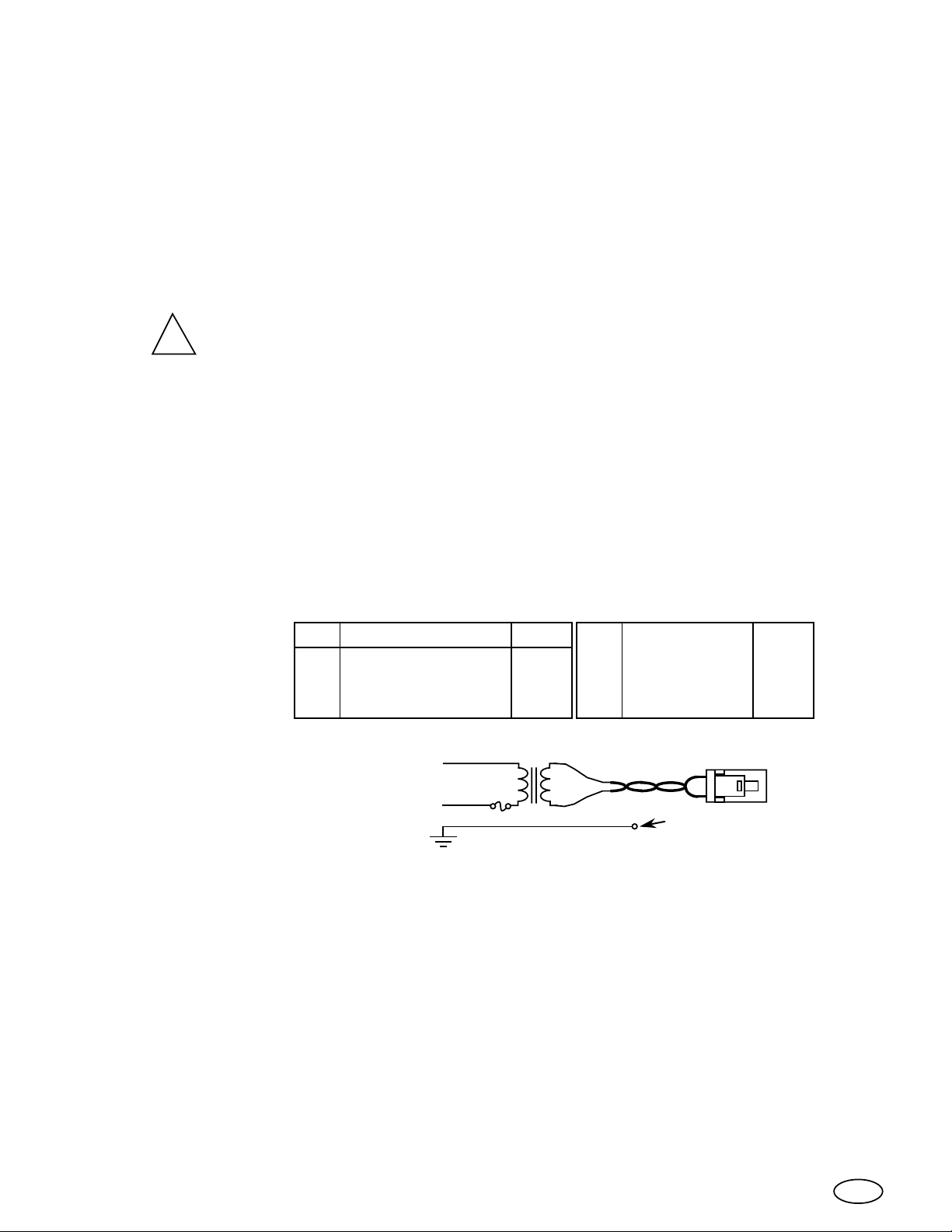

Pin Signal

0

+12V from monitor.

1

Horizontal sync.

2

Vertical sync.

ISOLATION TRANSFORMER

Mains

Power

3A-T

FUSE

GREEN / YELLOW WIRE

Color

White

Yellow

Purple

75VA

Signal ground.

3

Red video.

4

Green video.

5

Blue video.

6

Gray

Red

Green

Blue

Attached to the

monitor chassis.

Apply power to the monitor and the drive electronics.

8.

Check the focus and, if necessary, adjust the top control on the flyback transformer.

9.

Adjust the controls on the remote control board for proper;

10.

Horizontal Raster Size.

Vertical Raster Size.

Vertical Raster Position.

Horizontal Picture Position.

Video Gain.

11.

For convergence instructions, see page 100 & 101.

2

Page 8

Instructions d´installation des écrans XX93.

1. Un fusible á fusion lente de 3 amp (pour le courant du champ magnétique d´adjustement) et un

transformateur d´isolation de 75 VA sont le minimum requis pour utiliser nos écrans dans un produit.

2. Déballer l´écran.

3. Installer l´écran dans son carter.

Se référer aux instructions d´installation foumies par le fabriquant

du systéme pour les détails de montage de l´écran dans le carter.

4. Relier le fil de terre vert/jaune á la prise de terre sur le carter. Ce cable est relié á la vis

de terre située sur le chassis de l´écran derriére l´étiquette portant le numéro de série.

ATTENTION! Il n´est pas permis de ne pas relier ce fil de terre avant de mettre le courant, car

!

cette situation pourrait provoquer un choc électrique dangereux.

La résistance du chassis aux pricipales connections ne doit pas depasser 100mΩ.

5. Vérifier que les fils suivants sont correctement reliés:

A. Le fil vert de la tresse du tube cathodique aquadag á la carte video.

B. Le cable plat á 12 conducteurs de la carte vidéo á la carte principale.

C. Le cable rouge haut voltage du retout du transformateur au capuchon de

l´anode du tube cathodique.

D. Le fit de bobinage du bobinage á la carte principale.

E. Le fil de télécommande de la carte de la télécommande á la carte principale.

Note: Soyez sur que ces fils sont connectés en toute sécurité de sorte qu´ils ne

touchent aucune partie métallique.

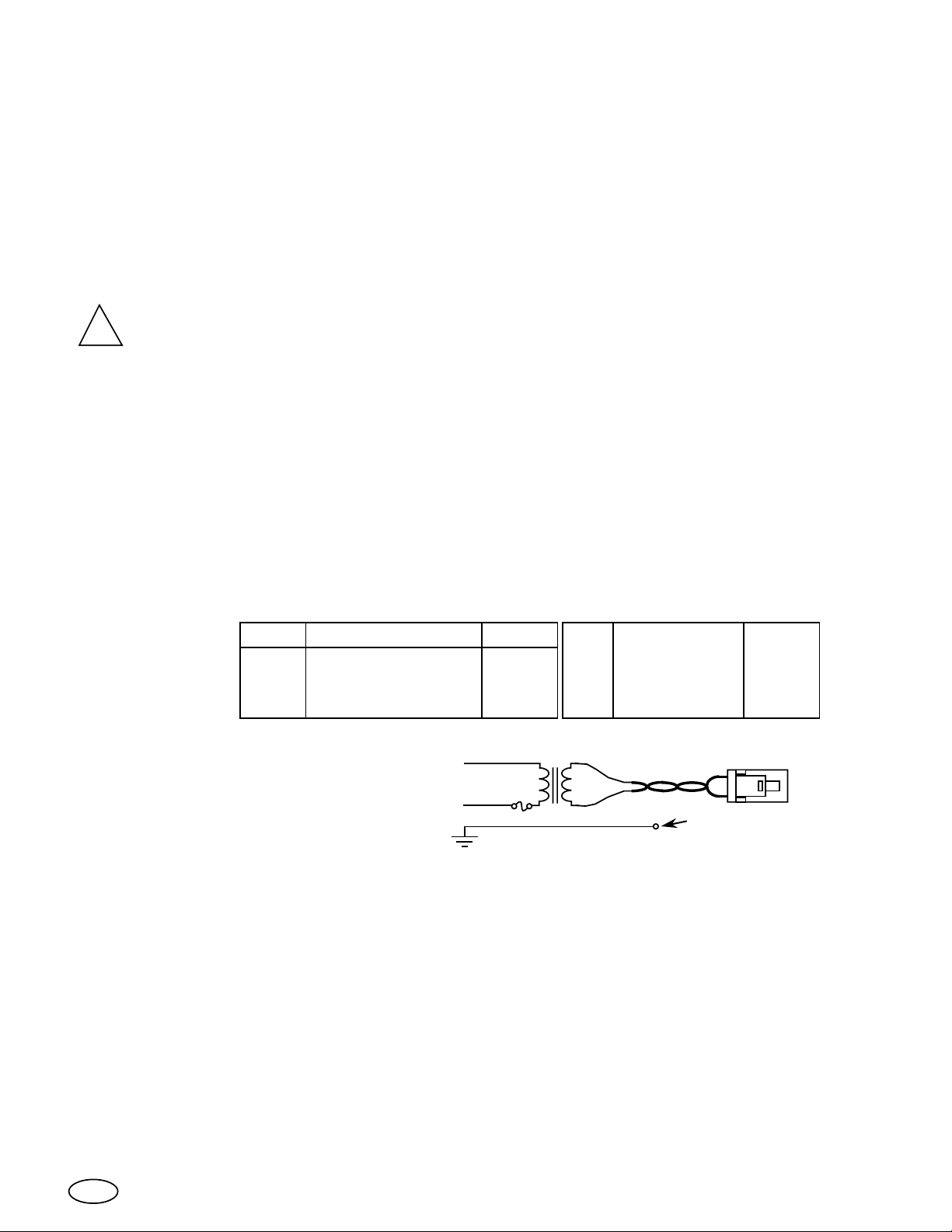

6. Brancher les

sept fils de la

connection vidéo:

Broche Signal Couleur

0

+ 12V de l´écran

1

Synchro Horizontale

2

Synchro Verticale

Blanc

Jaune

Violet

3

Signal de terre

4

Rouge vidéo

5

Vert vidéo

6

Bleu vidéo

Gris

Rouge

Vert

Bleu

TRANSFORMATEUR D'ISOLATION

7. Brancher les fils de courant

depuis le transformateur d'isolation:

Courant

Principaux

3A-T

75VA

FUSE

FIL VERT / JAUNE

Attasché au chassis

du moniteur.

8. Amener le courant á l´écran et au disque électronique.

9. Vérifier le foyer, et si nécessaire, régler le contróle sur le retour du transformateur.

10. Effectuer les réglages sur la carte de la commande á distance pour:

La taille du balayage horizontal.

La taille du balayage vertical.

La position du balayage fertical.

La position horizontale de l´image.

L´acquisition vidéo.

11. Pour les instructions de convergence, voir page 100 & 101.

3

Page 9

Installationsanweisungen für die XX93 Monitore.

1. Ein 3 Ampère-T sicherung (für die degaussing-Strömung) und ein 75 VA Isoliertransformator

ist die Minimum-Forderung für benutzen unseren Monitoren in einem Produkt.

2.

Packen Sie den Monitor aus.

Schließen Sie den Monitor

3.

im Gehause an.

4.

Verbinden Sie den Grüne/Gelben Schutzleiter zum Erdung anschluß auf dem Gehause.

Für Details, Folgen Sie den Installation-Anweisungen,

Vom Lieferanten der Antriebelektronik.

Dieser Draht ist verbunden zur der Erdung-Schraube auf dem Monitor-Chassis, und wird

hinter der Serien-Nummer-Aufschrift gefunden.

Unterlassen dieser Verbindung dieses Erdung-Drahts ist

WARNUNG!

!

gesetze widrig. Der Widerßtand von diesem anschluß biz

zum netzstecker darf 100mΩ nicht überschreiten.

Prüfe daß die folgenden Drähte ordentlich verbunden sind;

5.

Grüne Draht vom CRT aquadag zum Video Schaltpult.A.

B.

C.

D.

12 Leiter-Flachkabel vom Videoschaltpult zum Hauptschaltpult.

Rote hochspannungs Draht vom Flybacktransformator zur der Bildröhrenanode.

Jochkabel vom Joch zum Hauptschaltpult.

E. Fernsteuerung Kabel vom Fernsteuerungschaltpult zum Hauptschaltpult.

Notiz;

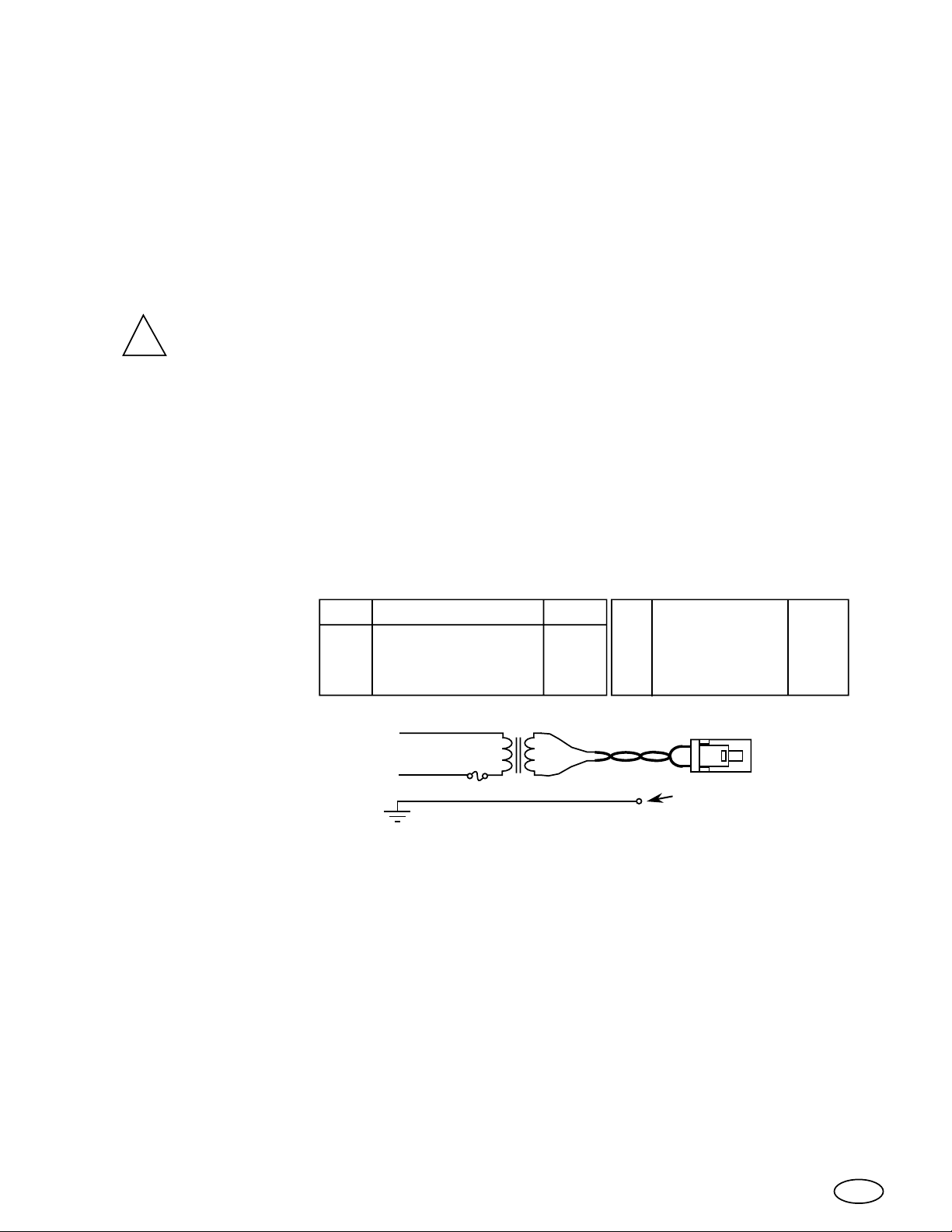

Stecken Sie den

6.

7 Leiter-VideoVerbindungsstecker ein.

Seien Sie sicher diese Drähte sind so befestigt daß sie kein Metallteil berühren.

0

+12V Von Monitor.

1

Horizontal sync.

Vertical sync.

2

FarbeSignalLeiter

Weiß

Gelb

Purpur

3

Signal-Erdung.

4

Rotes Video.

Grünes Video.

5

6

Blaues Video.

Grau

Rot

Grün

Blau

ISOLIERTRANSFORMATOR

7.

Stecken Sie den Stecker vom

Isoliertransformator ein.

Schalten Sie den Monitor und die Steuerung an.

8.

Prüfe Sie den Fokus und, wenn notwend, stell en Sie die obere Kontrolle ein auf dem

9.

Netzstrom

Grüne/Gelben Schutzleiter

3A-T

SICHERUNG

75VA

Verbindung ist auf dam

Monitore chassis.

Flybacktransformator.

10.

Stellen Sie die Kontrollen des Fernsteuerungsschaltung ein für richtige

- Horizontal Raster Größe.

- Vertical Raster Größe.

- Vertical Raster Position.

- Horizontal Bild Position.

- Video Kontrast.

Für Konvergenz-Anweisungen, auf seite 100 & 101.

11.

4

Page 10

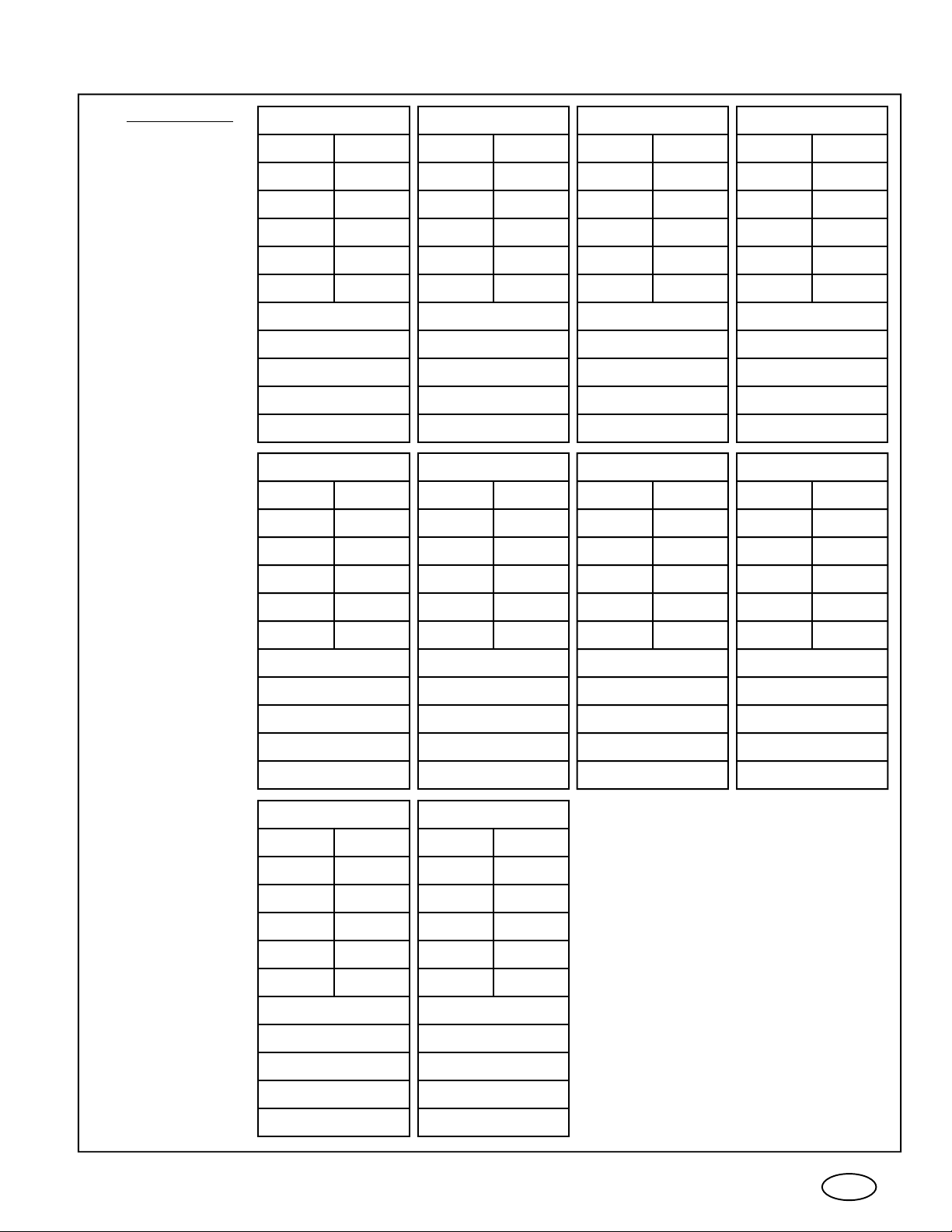

CERONIX

XX93 Monitor Electrical Specification.

INPUTS

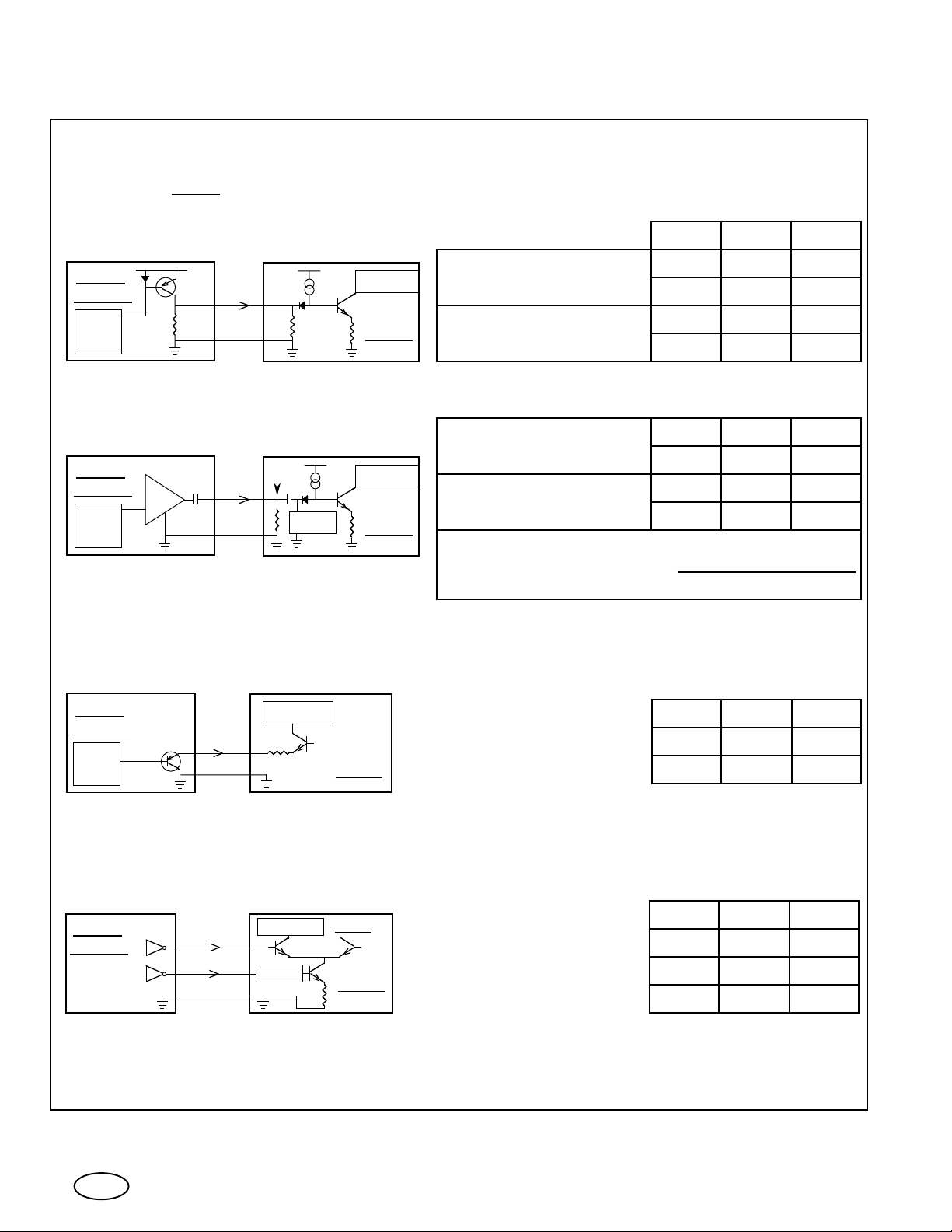

Standard Video Configurations, available, are:

1.

A. Positive Analog, DC Coupled.

Video

Source

D-A

75Ω

Video

Gnd

.6mA

75Ω

B. Positive Analog, AC Coupled.

Video

Source

D-A

Zo=75Ω

Amp.

Video

Gnd

75Ω

10uA

Clamp

C. Negative Analog.

To Amp.

Monitor

To Amp.

Monitor

Min. Typ. Max

.75V

Video

1.0V

Video

.75V

Video

1.0V

Video

Black level

Saturated color

Black level

Saturated color 1.00V 1.02V 1.04V

Black level

Saturated color

Black level

Saturated color

0.00V 0.02V 0.04V

0.75V 0.77V 0.79V

0.00V 0.02V 0.04V

Blk-.02V

Blk+.73V Blk+.75V Blk+.77V

Blk-.02V Blk+0.00V Blk+.02V

Blk+.98V

Blank

Blk+1.00VBlk+1.02V

Blk+.02V

AC voltages are referenced to the R, G, & B

video input voltage during horizontal sync (Hs).

Blank is the black level voltage during Hs.

Video

Source

D-A

Video

Gnd

To Amp.

IN

R

V

Blk.+.7 V

Monitor

Black levelRed & Green

Blue Black level

Saturated color

D. 4 Line TTL also available.

Black level

Color on

Low intensity

Full intensity

*

R,G,B

Video

Intensity

Gnd

Video

Source

*

No pullup resistor on intensity line.

To Amp.

BIAS

+12V

V

Monitor

B

Note: RS170 and other voltage combinations optional for analog video.

5.4V 5.6V 5.8V

4.85V 5.05V 5.25V

.7V .9V 1.1V

0V

2.7V 3.5V

.2V .5V

6.0V

0V .2V .4V

4.5V 4.6V 4.8V

5

Page 11

CERONIX

The Sync signals may be of either polarity and separate or composite.2.

XX93 Monitor Electrical Specification.

Sync

Source

For composite sync, vertical and horizontal

sync lines are connected together.

Hs

Vs

Gnd

1.8K

1.8K

220

Monitor

.15V

Ω,

2 PL

High input voltage

Low input voltage

Horizontal sync pulse

Vertical sync pulse

Horizontal frequencies:

Custom horizontal frequencies from 15KHz

to 39KHz are available upon request.

Vertical frequencies:

3.

The Power to the monitor is to be supplied by a secondary winding of an

isolation transformer.

Min. Typ. MaxModel

2.2V 3.5V 20V

-2.7V .30V .80V

1.5uS

65uS

15.5KHz 15.7KHz

29.3KHz 29.6KHz 29.9KHz

31.2KHz 31.5KHz 31.8KHz

34.9KHz 35.2KHz 35.6KHz

37.5KHz 37.9KHz 38.3KHz

4.0uS 12uS

.5mS 1.5mS

15.9KHz

55Hz45Hz 50Hz

61Hz51Hz 56Hz

65Hz55Hz 60Hz

75Hz65Hz 70Hz

120VAC 50Hz or 60Hz

230VAC 50HZ or 60Hz

Power

120VAC 50Hz or 60Hz

230VAC 50HZ or 60Hz

Power

Model 1493

Model 1793

Model 1993

Min. Max. Min. Max. Min. Max.

90VAC

180VAC

35W

90VAC145VAC

290VAC 290VAC180VAC

60W

40W 70W

145VAC 145VAC

Model 2093 Model 2793

90VAC

290VAC180VAC

45W 75W

Model 3693

Min. Max. Min. Max. Min. Max.

90VAC

180VAC

45W 75W 50W

290VAC 290VAC180VAC

90VAC145VAC

145VAC 145VAC

100W

90VAC

290VAC180VAC

50W 100W

6

Page 12

CERONIX

Five Controls are located on

4.

XX93 Monitor Electrical Specification.

a separate PCB for easy access.

Model 1493

Model 1793 Model 1993

Min. Max.Min. Max.Min. Max.

H SIZE--------------Horizontal raster size

V SIZE---------------Vertical raster size

V RAS. POS.-----Vertical raster position

H POS-------Horizontal picture position

M GAIN---------------------Master gain

10.1" 11.1" 11.9" 12.9"

7.3" 8.3" 8.6" 9.6"

0"

1" Right 1" Left 1" Right 1" Left

0mA .75mA 0mA .75mA 0mA

Model 2093

.50"

0"

Model 2793 Model 3693

.50"

13.4" 14.4"

9.8" 10.8"

0"

1" Right 1" Left

.50"

.75mA

Min. Max.Min. Max.Min. Max.

14.9" 15.9" 20.4" 21.4"

10.9" 11.9" 15.1" 16.1"

0"

1" Right 1" Left 1" Right 1" Left

0mA .75mA 0mA

.60"

0"

1.0"

1.5mA

27.4" 28.4"

20.3" 21.3"

0" 1.0"

1" Right 1" Left

0mA 1.5mA

The board Controls are located on the main PCB:

Focus and G2 on the FBT.

Optional board Controls are: pincushion, video black level, and horizontal hold control.

5.

Image

Environmental

6.

Color Temperature

Horizontal linearity

Vertical linearity

Pincushion

1493

17/19/2093

9300°K 9300°K 9300°K 9300°K

-2% +2%

-2% +2%

-2% +2%

-5% +5% -8% +8%

-5%

-3%

Operating temperature

Storage temperature

Operating humidity

Storage humidity

+5%

+3%

0° C

-8%

-5%

70° C

85° C-20° C

20% 80%

10% 95%

2793 3693

Min. Max.Min. Max.Min. Max.Min. Max.

-10% +10%

+8%

+5%

-10%

-8%

+10%

+8%

7

Page 13

CERONIX

Picture tube

7.

XX93 Monitor Electrical Specification.

1493-CGA/VGA/SVGA

1793-VGA/SVGA

1793-SVGA

1993-VGA/SVGA

Useful diagonal

Useful horizontal

Useful vertical

Useful area

Spacing of dot/line trios

Phosphor Trio Type

Deflection angle

Light transmission

CRT surface

Phosphor

Useful diagonal

Useful horizontal

Useful vertical

Useful area

Inch mm

13.2 335 16.1 409

11.1 281 12.9 328

8.3 211 9.6 245

92.1 in 593 cm 124 in 804 cm

.0110" .28mm .0098" .25mm

Dot

16 407

12.9 328

9.7 246

125 in 807 cm

22

.0106" .27mm

Dot

90°

Approximately Approximately

57% 50%

Polished/Curved

P22

2093-CGA 2793-CGA

Approximately

53%

Polished/Curved

P22

2093-VGA

Inch mm

18.9 480 26.8 679

15.9 404 21.4 544

11.9 303 16.1 408

189 in 1,224 cm 345 in 2,220 cm

22 2 2

18.9 480

15.9 404

11.9 303

189 in 1,224 cm

22

InchInch mmmm

Dot

90°90°

AR / Flat

P22

InchInch mmmm

Inch mm

18 457

14.4 366

10.8 274

165 in 1,003 cm

2222 2 2

.0102" .26mm

Dot

100°

Approximately

45%

AR / Curved

P22

2793-VGA

Inch mm

26.8 679

21.4 544

16.1 408

345 in

2

2,220 cm

Spacing of dot/line trios

Phosphor Trio Type

Deflection angle

Light transmission

CRT surface

Phosphor

Useful diagonal

Useful horizontal

Useful vertical

Useful area

Spacing of dot/line trios

Phosphor Trio Type

Deflection angle

Light transmission

CRT surface

Phosphor

.0331" .84mm .0326" .83mm

Line

Approximately Approximately

40% 38%

Polished/Curved

P22

2793-VGA

Inch mm

26.6 676

21.3 541

16.0 406

341 in 2,196 cm

22

.0299" .76mm

Line / Variable

110°

Approximately

81%

Polished/Flat

P22

.0307" .78mm

Line

90°

Approximately

40%

Polished/Curved

P22

3693-CGA

Inch mm

35.5 902

28.4 721

21.3 541

605 in 3,901 cm

22

.0394" 1mm

Line

111°

Approximately

32%

Polished/Curved

P22

Line

110°90°

Polished/Curved

P22

.0326" .83mm

Line

110°

Approximately

38%

Polished/Curved

P22

8

Page 14

Refer to the block diagram on page 15 (foldout) when reading this description.

A

The Video Interface is designed around a custom IC and will accept DC or AC

coupled positive analog video signals. It can also be used with negative analog

and 4 line TTL. This IC has a built in multiplier circuit for the master gain

control and blanking functions. Resistors are used to protect the IC and to set

the gain. The programmed gain is dependent on the input signal amplitude

except with the TTL mode. Solder jumpers and component substations are used

to program the Video Interface for the type of input signal to be received. The

output of the IC drives the video amplifiers. This drive is a current where 0 mA

is black and 10 mA is a saturated color.

B

The Video Amplifiers are of the push pull type. They are built partly on thick

films and partly on the video PCB. Spreading out the amplifier reduces the

component heat and improves the life of the unit. The bandwidth is 25 MHz with

40Vp-p output. The rise and fall times are 20nS.

C

The Beam Current Feedback circuit directs most of the beam current of each

amplifier to the beam current buffer. The only time this current is measured, by

the auto bias circuit, is during the time of the three faint lines at the top of the

screen and three lines thereafter. The CRT auto bias circuit is designed to adjust

the video amplifier bias voltage such that the beam current of each of the three

guns is set to a specific programmed value.

D

The

current signal into a low impedance voltage. This voltage is applied to the auto

bias IC through a 200 ohm resistor. After the three lines of beam current are

measured, the program pulse from the auto bias IC, produces a voltage drop

across this 200 ohm resistor that equals the amplitude of the beam current

voltage.

9

Beam Current Buffer converts the, high impedance low current, beam

Page 15

E

The CRT Auto Bias IC is a combination of digital and analog circuitry. The

digital part is a counter and control logic which steps the analog circuits through a

sequence of sample and hold conditions. The analog part uses a transconductance

amplifier to control the voltage on a 10uF capacitor (one per gun). This voltage is

buffered and sent to the video amplifiers as the bias voltage. In monitors without

CRT auto bias, this voltage is adjusted manually using a setup procedure to set

the color balance. With CRT auto bias, the color balance is set during the end of

each vertical blanking time.

The control sequence is:

1.

The cycle starts with a sync pulse from the vertical oscillator (15KHz)

or from the vertical sync delay. 15H later the grid pulse starts.

2.

The grid pulse on G1 causes cathode current which can be seen as the

three faint white lines at the top of the screen. This cathode current is

transmitted by the beam current feedback to the beam current buffer

where it is converted to a voltage and applied to the CRT auto bias

input pin. At this time the CRT auto bias IC outputs a reference

voltage at its input pin which sets the voltage across the coupling

capacitor. This coupling capacitor voltage is directly dependent on

beam current.

After the grid pulse is over, the program pulse matches the voltage

3.

from the beam current buffer. If the voltage from the beam current

buffer, during the grid pulse, is the same as the voltage from the

program pulse, the bias is correct and no bias adjustment is made for

that vertical cycle.

F

The timing of the auto bias IC is synchronized to the vertical oscillator and the

flyback pulses. For horizontal frequencies higher than 15.7KHz a Vertical Sync

Delay may be needed to position the grid pulse, generated 3 gray lines, at the top

of the screen. The need for the delay circuit is dependent on the particular CRT

vertical retrace time.

G

The aging of the picture tube (CRT) not only affects the balance of the cathode

cutoff voltage, which is corrected by the auto bias circuit, but it also affects the

gain of the CRT. The

by sensing any common bias voltage change, from the auto bias circuit, and

adjusts the screen voltage to hold the average bias voltage constant. The lower

adjustment on the flyback transformer which is the screen voltage, is used to set

the auto bright voltage to the center of its range. Therefore, the auto bright

circuits sets up a second control feedback loop to reduce picture variation due to

CRT aging. The auto bright circuit is also used to turn off the beam current when

the monitor power is turned off.

Auto Bright circuit actively corrects for CRT gain changes

10

Page 16

H

The CRT for the 1493, 1793 and 2093 monitors have a 90° deflection angle. The

1993 incorporates 100° while the 2793 CRT has 110° and the 3693 has 111°

deflection angles. These picture tubes have integral implosion protection and a

EHT of 25KV.

H1

The Vertical Dynamic Focus amplifies the parabolic waveform across the

vertical coupling capacitor from about 3Vp-p to about 200Vp-p, depending on CRT

requirements. This waveform sharpens the top and bottom portion of the raster

on dual focus CRT's.

H2

The

horizontal coupling capacitor, using a transformer to produce 300Vp-p output from

an input that is about 33Vp-p. This waveform is added to the vertical dynamic

waveform and sharpens the right and left sides of the raster.

Blanking is accomplished by setting the gain of the interface IC to zero during

blank time. The Horizontal Blanking pulse is generated by amplifying the flyback

pulse. The Vertical Blanking pulse is started by the vertical oscillator one shot

and ended by the counter in the auto bias IC via the "bias out" pulse. The Master

Gain control, located on the remote PCB, sets the gain of the video signal when

blanking is not active. The Beam Current Limiter circuit, which is designed to

keep the FBT from overloading, will reduce the video gain if the maximum

average beam current is exceeded. Also, the beam current is reduced if the FBT

approaches maximum operating temperature.

The

used to receive sync, one for vertical sync and the other for horizontal sync.

Resistor dividers are used to protect the comparator IC from over voltage damage.

For customers who do not require interlace, an additional vertical sync

stabilization circuit is included. This circuit synchronizes the vertical sync to the

horizontal cycle.

Horizontal Dynamic Focus amplifies the parabolic waveform across the

I

J

Sync Interface can accept separate or composite sync. Two comparators are

K

Vertical Oscillator generates the vertical free running frequency when no

The

vertical sync is present. When sync is applied, the vertical oscillator synchronizes

to the leading edge of the sync pulse.

L

The Vertical Control & Output circuit consists of:

1. One shot.

2. Ramp generator.

3. Vertical drive.

4. Vertical output.

11

Page 17

The sync pulse from the LA7851 triggers a one shot in the LA7838 which clamps

the vertical ramp generation capacitor to 5V during the first half of vertical

retrace. The ramp generation capacitor then charges via a constant current set by

an external resistor. This resistor is connected to the V SIZE pot, located on the

remote control board, for the vertical size adjustment. The vertical drive is a

differential amplifier which compares the ramp voltage to the yoke return

feedback current. The yoke feedback current and voltage circuits are used to set

the vertical linearity. The vertical Output is a power driver, with thermal

protection, which drives the vertical deflection yoke. It also has a special pump up

circuit which doubles the output voltage during vertical retrace. This voltage

doubler also increases the efficiency of the circuit since the high retrace voltage is

not present across the power driver during the trace time.

M

The

loop to generate the horizontal timing. The H POS. adjustment, on the remote

control board, sets the sync delay time which controls the picture position. The

phase locked loop uses the flyback pulse to generate a sawtooth wave which is

gated with the delayed sync pulse to control the horizontal oscillator.

Horizontal Control incorporates a variable sync delay and a phase locked

N

The Horizontal Driver supplies the high base current necessary to drive the

horizontal output transistor which has a beta as low as three. A transformer is

used to step up the current from the driver circuit and also protects the horizontal

output transistor from a continuous turned on state. A special clamp circuit is

connected to the transformer which reduces the turnoff time of the horizontal

output transistor for reduced power dissipation.

O

The Horizontal Output transistor is mounted to the rear frame which acts as a

heat sink. The collector conducts the 900 volt primary flyback pulses which should

not be measured unless the equipment is specifically designed to withstand this

type of stress. A linear ramp current is produced in the horizontal yoke by the

conduction of the horizontal output transistor (trace time). A fast current reversal

(retrace time) is achieved by the high voltage pulse that follows the turn off of the

horizontal output transistor. This pulse is due to the inductive action of the yoke

and flyback transformer.

P

The main function of the Flyback Transformer (FBT) is to generate a 25,000 volt

(EHT) potential for the anode of the picture tube. This voltage times the beam

current is the power that lights up the phosphor on the face of the picture tube.

At 1.5mA beam current, for the 2793 monitor, the FBT is producing almost 38

watts of high voltage power. The FBT also sources the focus voltage, screen grid

voltage, filament power, and has two more secondaries which are used for control

functions. The FBT has a built in high voltage load resistor which stabilizes the

EHT, for the low beam current condition. This resistor also discharges the EHT,

when the monitor is turned off, which improves the safety of handling the

monitor.

12

Page 18

Q

The Remote Control PCB houses the:

CONTROL DESCRIPTION CIRCUIT

1. H SIZE ----------- Horizontal raster size --------- Diode modulator

2. V SIZE ----------- Vertical raster size ------------- Vertical control

3. V RAS. POS. --- Vertical raster position ------- DC current to V. yoke

4. H POS ------------ Horizontal picture position -- H. sync delay

5. M GAIN ---------- Master gain ---------------------- Video interface

R

The Horizontal Size Control circuit has four inputs:

# SIGNAL FUNCTION

1. Horizontal size ------------------------------ Horizontal size control

2. Beam current -------------------------------- Blooming control

3. Vertical linear ramp -----------------------

4. Vertical parabolic + V. linear ramp ---

(#4)-(#3)=Vertical parabolic

}

(Pincushion)

The horizontal size control circuit sums the four signals at one node plus the

feedback from the diode modulator to drive a switching mode power driver. The

output of the power driver is then connected to the diode modulator through an

inductor to complete the control loop.

S

The Diode Modulator is a series element of the horizontal tuned circuit. It forms

a node between GND and the normal yoke return circuit. If this node is shorted to

GND, the result is maximum horizontal size. Forward current in the diode

modulator, at the start of retrace, keeps the node voltage clamped to ground until

enough current flows from the horizontal tuned circuit to exceed this forward

current. The horizontal size, therefore, is controlled by controlling the current to

this diode via the horizontal size control circuit.

T

A Voltage Doubler is used in the power supply for two reasons:

13

1. To improve the efficiency of the power supply.

2. To permit 120 volt and 230 volt operation. For the 230 volt

operation the voltage doubler is replaced with a bridge rectifier.

Page 19

U

XX93 Monitor Block Diagram.

The Switching Regulator is synchronized to the horizontal pulse and drives a power

MOSFET. Unlike most regulators that have a common GND, this power supply has a common

V+ and current is supplied from V- to GND. The MOSFET is connected to V– and signal

ground (GND) through a transformer which is used as an inductor for series switch mode

regulation. An operational amplifier, voltage reference, comparator, and oscillator in the power

supply controller IC are used to accomplished regulation by means of pulse width modulation.

The transformer has two taps on the main winding which are used to generate the +16 volt

and +24 volt supplies. It also has a secondary which is referenced to V- and supplies the power

supply. Since the power supply is generating its own power, a special start up circuit is built

into the power supply controller IC that delays start up until the capacitor which supplies the

IC is charged up enough to furnish the current to start the power supply. This capacitor is

charged with current through a high value resistor from the raw dc supply. This self sustaining

action is why the power supply chirps when an overload or underload occurs. Additional

secondaries to drive the horizontal raster shift circuit and the video amplifiers are also included

in the power transformer.

V

The Load consists primarily of the horizontal flyback circuit. The power supply will not

operate without the load since the voltage that sustains the power supply comes from a

secondary in the power transformer and depends on some primary current to generate

secondary current.

W

A +12V regulator is used to supply current, to all the control circuits in the monitor, with the

exception of the power supply. Many of the control circuits are decoupled from the +12 volt line

with a resistor or diode to minimize noise from common current loops.

X

The Over Voltage Protect circuit is built into the power supply and monitors the flyback

transformer peak pulse voltage. This circuit will turn off the power supply and hold it off if the

EHT exceeds its maximum rated value. Since excessive X-ray output occurs with excessive

EHT, this circuit provides X-ray protection.

Y

The Fault Detector senses beam current and temperature. This circuit will activate the

power supply shutdown circuit if either the maximum temperature is sensed or if the beam

current becomes large enough to threaten the FBT.

Z

The Degaussing circuit is connected across the isolated AC line. A posistor is used to allow a

large current to flow, in the degaussing coil, on power up. This current is then gradually

reduced by the increased temperature of the positive temperature coefficient thermistor in the

posistor. A relay is used to short the degaussing coil after the degaussing operation. This

greatly reduces posistor residual current in the degaussing coil. When repairing a monitor, the

degaussing coil should be unplugged, to avoid possible damage to the degaussing coil shorting

relay.

GAME

VIDEO

RGB

SYNC

V. & H.

VIDEO

3

SYNC

Interface

2

Interface

BLANKING

V retrace

Beam limit

High temp. limit

VERTICAL

J

VERTICAL

s

V

F.B.P.

M. gain

SYNC

DELAY

3

AB

I

F

OSCILLATOR

LA7851

K

LA7851

HORIZONTAL

CONTROL

s

H

H. Pos.

Sync delay

M

V. Size &

V. Ras. Pos.

REMOTE

CONTROLS

(PCB)

ISOLATION

Transformer DOUBLER

(IN GAME)

DEGAUSSING

CIRCUIT

Z

VOLTAGE

Raw DC

320V

+24V

G2≈290V

2 For Dual Focus

On Video Board.

G1≈–20V

VIDEO

AMPS.

Bias

3

3

Bright

3

CRT AUTO

BIAS IC

H. sync (FBP)

V. sync

CA3224E

Auto

Beam

3

Current

Feedback

G

3

Beam current

buffer

Program pulse

Grid pulse

E

VERTICAL

CONTROL &

3

CRT

C

V

DY

DY

H

D

H

EHT≈25KV

Dynamic Focus

used only on Dual

Focus CRTs

Horizontal

Dynamic

Focus

H2

OUTPUT

LA7838

I. V. Feedback

EHTG2

V+

Vertical

Dynamic

Focus

P

L

+

H.H.

Driver

PINCUSHION

HORIZONTAL

Size Control

QR

+52V to +129V

(VIDEO & DEFLECTION)

SWITCHING

REGULATOR

Shutdown

OVER

VOLTAGE

PROTECT

T

V-

-200V

FAULT

DETECTOR

LOAD

Y

Output

NO

DIODE

Modulator

Beam Current

+12V

Regulator

Vertical Deflection

Sync

X

+16V

+24-27V

U

FBP

FBT

S

V

+12V

W

Supply

H1

2

14

15

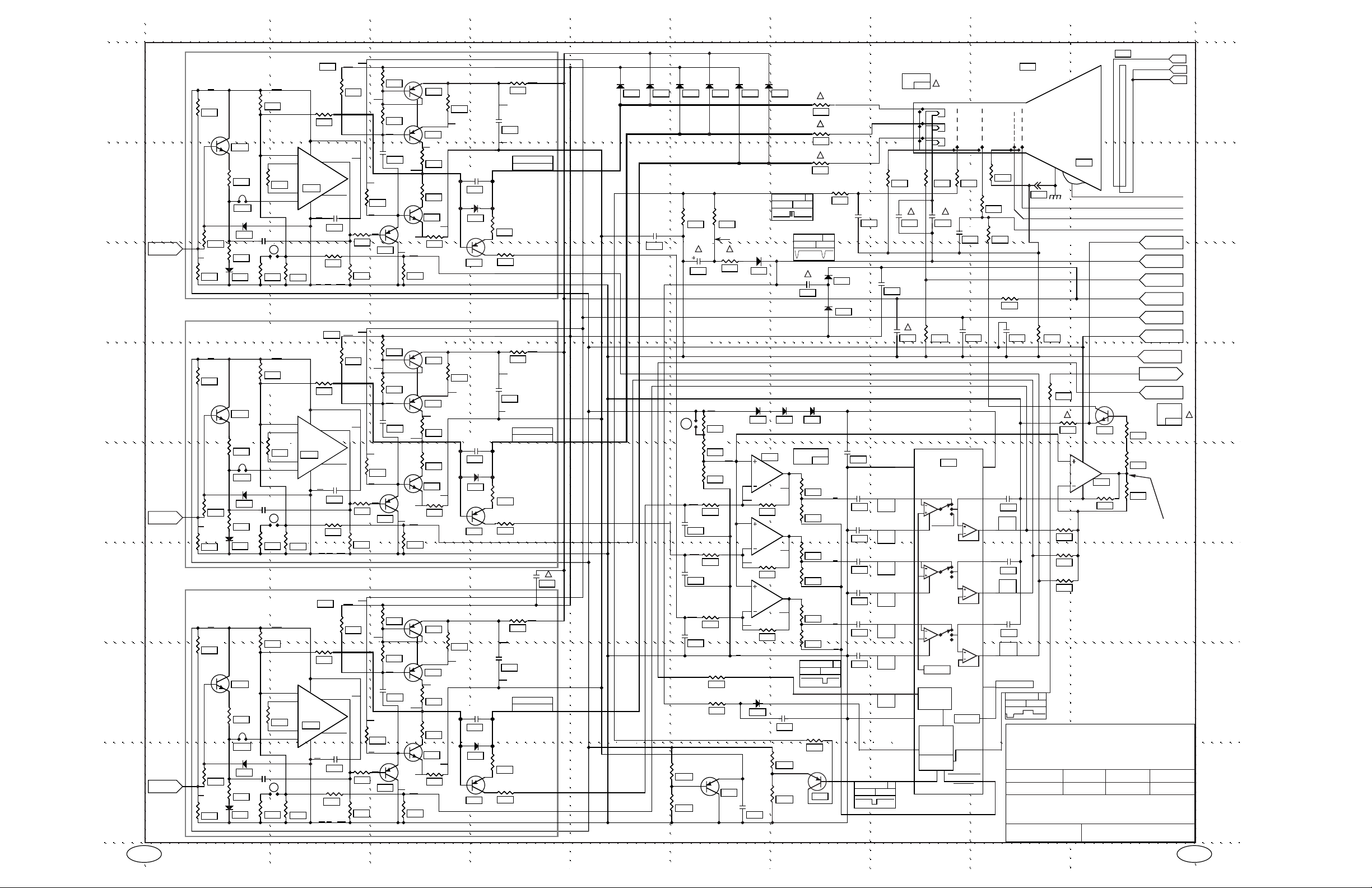

Page 20

BB

12V

TC2 GND

+

GND

TC9 iB OFF

16V

CC3

ABA

464Ω

261

258

G

Beam current

Feedback

Beam current

Feedback

Beam current

Feedback

B+G+R=∑

SOCKET BOARD CONNECTOR (TC) 206

TC 6TC 10

0Ω

088

6.8K

099

PN2222

1

2

3

100B

5

0Ω

100A

10

6

1/2

7

LM393

5

+

210

OPEN

077

.039uF

081

1N4937

080

T

U

909Ω

064

227

10

396 11

A- BL

+12V

IN

R

G

B5

K

243

218

264

Red Video Amp.

0

Green Video Amp.

Blue Video Amp.

Auto Bias

V

Sync

1

2

3

4

5

6

TC7 Red

TC5 Green

TC 3 Blue

62K

+12

V

098

PN2222

379

200K

CS=.45"

383

Retrace Boost

VERTICAL BLANKING

22K

384

0Ω

CS=.74

389

GND

PN2907A

212

4-7VDC

Hs

4-9Vpp 61,B4

HORIZONTAL

BLANKING

PN2222A (CPQ1322)

2.15K

078

072

GND

FDH400

084

FDH400

086

FDH400

213

16 13

B

IN R

R

21 1415 7 8

A5

J

S

412Ω 105Ω 604Ω

260 244 245

+12V

P

239

oRo Go GAINM+ ENA

B

BL

Controls XRC5346A

R

225

223

226

7

236 235

1N4148

271

278

0Ω

1N4148

270

277

8

0Ω 0Ω 0Ω

281 280 283

VC

G

5

GND

GREEN

INPUT

286

288

9

RED

GND

VC

292

3

R

VC

4

INPUT

BB

16

Beam

Current

Buffer

510Ω

006

+12V

6.8K

250

1N4148

253

1

1K

1.8K

248

.047uF

GND

270Ω

093

VIDEO GAIN LINE

604Ω

076

4-7VDC

5-9Vpp

11.5-12.5V

0Ω

228

512

TTL

241

BG

242

VC

BLUE

INPUT

CC DD EE FF GG HH II JJ KK LL MM NN OO PPAA

0Ω

8

211

1/2

LM393

210

4

208

207

0VDC

56Vpp 63,D6

Vs

62,B4

GND

IN

B

A5

L

266

276

GND

B

VERTICAL

6

CC DD EE FF GG HH II JJ KK LL MM NN OO PPAA

VIDEO BOARD

ARC PROTECT

Auto

Bright

6.8K

251

2

2.3-

2.7V

1.8K

3

+

368

1.8K

252

Hs

+12V

GND

0Ω

293

12V

VC

0

4

R

233

231

232

1N4148

268

284

s

V

VC

SYNC

800

2-3VDC

4Vpp 64,C4

4.5-5.3V

5Vpp 16,E5

GND

1.8K

328

1.8K

H

s

HORIZONTAL

VC

SYNC

12

CRT

127V TC8

TC4

1N4007

090

68.1K

085

100uF

+

089

127K

087

100uF

+12V

209

Vs

Vs

+

100uF

267

221

PN2222

274

M & N reverse Hs.

325

270Ω

326

0Ω

270Ω

330

331

TC1

2.15K

272

273275

GND

M

N

M

N

.14-.16V

Product safety note: Components marked by the

Horizontal

RC5

Size

10K

481

When replacing any of these components, be sure to use the parts specified in the parts list.

+12V

GND

RC8

+127V

Vertical

Vertical

Position

RC3

RC

002

Horizontal

Master

RC2

2.15K

062

+16V

+12V

OUT IN

+

100uF

304

12.1K

Hs

329

500Ω

Size

Raster

1K

20K

Position

1K

Gain

Remote Control

490

PCB

0Ω

0Ω

295

067

7812

+

GND

296

56pF

1.8K

3

I1

352

482

RC6

750Ω

486

483

+12V

GND

RC4

220uF

298

7.3VDC

5.5Vpp

RC1

01,D6

RC7

Hs

484

485

Vs

+127V

FBP

GND

+16V

+

MPSA64

D

036

Beam Current

Limiter Circuit.

14

355

13

355

10uF

014

1N4148

018

LM339

1.5-2VDC 60,D6

LM339

+12V

PN2222A

071

75Ω

066

CPQ1322

7.15K

366

1K

012

1K

065

7.15K

+12V

364

PN2222

22K

323

4

5

6

7

270Ω

327

1/4

LM339

+

1/4

LM339

+

3

12

+12V

355

2

1

355

GND

6.8K

321

6.8K

322

+24V

470Ω, 1/2W

Relay

200V.5A

470

468

.093" pin

162A

.047uF

GND

CC

318

159

25Ω@25˚C, 2A

Posistor

158

.093" pins

Degaussing

CC2

Connector

162

100K

HEAT

SINK

378

510Ω

004

0Ω

203

1,000pF

369

100uF

+

376

18Ω

367

1N4007

333

0Ω

202

17

220uF

334

18Ω

063

GND

9

+

1/4

8

11

+

1/4

10

200K

.05VDC

246

7V pp 58,C5

255

PN2222

257

200K

256

33K

247

Inrush Current Limit

CPR0434

Black Wire.

CC1

161

symbol on this schematic have special characteristics important to safety.

LA7838

Vertical

Deflection

+12V

1

Ramp

Reset

One Shot

377

Tr.

234 567 8 9 1011 12 13

5.5-6.4V

3Vpp 21,D5

93.1K

375

28.0K

402

100K

403

+12V

GND

Vs

5.5-6.5V

1.2Vpp 19,D5

11-12.4V

20, D5

20 19 18 17 16 14 13

VERTICAL

V+

Horizontal

SYNC INPUT

2.7K

2

5

15.8K

020

CPR0432

100kΩ@25˚C

T

180

15.8K

353

1K

357

3.92K

3.92K

356

Vs,Hs

254

169

I4

12K

7

I2

8.8K22K

I3

GND

H. S. +12V

+6V

I BEAM

7-10VDC

61, C2

FBP

68.1K

15.8K

360

354

2.1-2.4VDC

Hs

4.6Vpp 59,D6

3.3nF

358

2.2nF

150

FR205

148

152

2.2nF

155

FR205

156

3A Fuse

146

145

PC

PC

120VAC

2

INPUT

1

out

Ramp

Gen.

V. size

Reset

out

R/C

Vs

or

VERTICAL VERTICAL

± SYNC INPUT

PICTURE

POSITION

8

Hs

IA

I12

Slope

Vs

.01uF

374

VERT.

O/S

4Vpp 02,D6

1nF

351

Ramp

.1uF

410

OSC.

1.2Ω, 1W

Control

50/60Hz

5-6VDC

1.4Vpp 22,E5

1uF

401

385

DELAYED

SYNC O/S

Hs

9

25K

I5 350

6,10

-1.4V -2.8V

2.33K

J13 J14

91.4K

J1

2SA1371E

1

529

112

0Ω

114A

10.6K

J5

JD

260Ω

+2.9V

J16

JC

130Ω

+1.4V

J15

11K

J2

2

23.2K

106

62K

220uF

143A

250V

0Ω

144

220uF

250V

163

36K

143B

0Ω

114

7

90K

J6

220uF

128

8,14

Vert.

Drive

5.5-6.5V

Vs

1.4Vpp

23,F4

Vs

+25V

Retrace

Booster

Drive

68.1KΩ

393

GND

127K

388

2.2M

365K

362

363

4-6VDC

V

2.8Vpp 18,D5

V. osc.

ADJ.

OSCILLATOR

7.3-8.7V

4Vpp 03,D6

VERTICAL

TR.

-.2VDC

Vs 5.5-6.3V

1.5Vpp 04,E6

330pF

11

330pF

45K

I6

1

GND

2.7K

392

1uF

391

127K

361

Vs

OSC. O/S

SAW TOOTH

GENERATOR

Hs7.3-8.7V

6.8K

I13

100K

173

100K

390

.01uF

414

3.8Vpp 17,E5

1.4Vpp 05,E6

6.8nF

348

62K

167A

FBP

GND

+6V

I BEAM

V+

101.6K

JBJA

J18

JE

20

4.67K

220uF

175

BZT03-D160

160Vz

181

100K

113

6

6.5-7.5VDC

1,000pF

110

3

5

88K

J4

4

3.3nF

108

56pF

J3

104

33.2K

J7

3-4VDC

6.8nF

102

41,D1

6.5-7.5VDC

.5-.8VDC

3.4-4.2VDC

.1-.5VDC

9

5.7-6.3VDC

3Vpp

47,D2

56pF

107

1

2

3

4

5

6

7

8

330pF

123

-265V

CAUTION! POWER SUPPLY VOLTAGES REFERENCED FROM V-.

SCOPE GND MUST NOT BE CONNECTED TO GND AND V- AT THE SAME TIME.

V- V-

Thermal Protection

Vert.

Out

GND

100pF

398

1N4007

470uF

382

382

380

1.5-2.7V

Vs

24,E4

24Vpp

4.5-5.3V

Vs

5Vpp 16,E5

V Ref.

MULTIPLIER

BIAS

Hs 3-7VDC

0Vpp

06,E6

+

1uF

347

18

1uF

+

H. +12V

I PRA

Video V+

+

100uF

120

+43V

250V

1N4937

121

GND

16.3-19VDC

55, E1

+15V

INPUT

+17V

ERROR

INPUT

AMP.

INPUT

Over

COMP.

Voltage

}

Protect

INPUT

Output

CONTROL &

FAULT SENSE

4uS

COMP.

DELAY

Rx

Osc.

Cx

+7.5V

OUTPUT

Current

SENSE

DRIVE

REF.

XRC5184

115

J PRA PINS:

+

V-

Boost

0Ω

395

Vs.1-.3VCD

15

GND

LA7851

784523

13

I7 I8

416

V+

100uF

+

118

+61V

1N4937

122

16

14.8-18VDC

0Ω

15

132

14

5.5-6.8VDC

3-5VDC

5Vpp 52,F1

12

13

3-6VDC

0.1VDC

1Vpp 51,F1

11

1-4VDC

12Vpp

10

9

J PRA

111

3,10,15,

4.7Ω

396

.1uF

397

22K

370

15.8K

408

PROTECT

HORIZONTAL

OSCILLATOR

.2Vpp 07,E6

33K10K

.01uF

220uF

100V

182

+127V

1N4937

167

30Ω

139

50,E2

&19

Vertical Linearity Circuit

DECREASES

200K

TOP AND

BOTTOM

412

VERT. SIZE.

I

D5

200K 200K

PN2222

411

1N4148

84.5K

407

406

GND

.4VDC

Hs

.7Vpp 12,E5

12

X-RAY

DISCHARGE

3.6Vpp 08,E6

14

1K

I9

6.8nF

+55V

1N4937

20

1.00M

17 18

14.7K

MPSA64

2,200pF

131

Hs3-4VDC

15

9.31K

I10

+ 1600Hz

0Ω

0Ω

198A

+16V

+

1,000uF

171

1

2

8

5

9

141

12

16

.1uF

124

V-

1.00M

15.8K

J11 J12

510Ω

12

D

134J10

J8

18Ω

133

1N4007

127

Hs2.4-3.4VDC

345346344

3.92K

418

5.4-6VDC

11, E5

+

comp.

-

5-6VDC

09,E6

7Vpp

H.Fo ADJ.

680Ω

I16

+800Hz

1,000uF

166

191K

126

38.3K

J9

13

116

PN2907A

372371

PN2222

1N4148

405

+12V

GND

11

415

H. V+

Hs

340Ω

I15

ICID

1N4937

170

1N4937

169

GND

6

3

4

10 / 11

0Ω

10

533

533/532

3,300pF

125

CPQ1304

136

0.33Ω

2W

137

100pF

129

200K

413

409

D5

H

INCREASES

TOP AND

BOTTOM

VERT. SIZE.

373

169K

404

10.8-12V

10, E6

3.92K

417

10

17

2.15K

336

170Ω

I14

+400Hz

16

IB

+61V

+43V

I BEAM

V+

1,000uF

450

1N4937

168

FR205

142

1N4148

130

No DVM

300Vpp 40,G1

HEAT

SINK

200pF

1KV

138

47Ω

1/2W, CC

140

V-

TP49, G1

0VDC

27Vpp 57,F1

FBP

GND

+6V

+

135

+25V

+25V

Hs

22-28V

.8Vpp 25,F7

V. +12V

0Ω

422

+43V

V+

+61V

+25V

0Ω

136A

1770Ω176

Vs

0Ω

196

2.2K.5W

341

+25V

FBP

GND

PS FBP

H. S.+12V

FBP

GND

+12V

PS FBP

PS FBP

FBP

+12V

GND

0Ω

Measurements

are taken with

a white screen.

Hs - 5uS/div.

Vs - 2mS/div.

0VDC

Hs

56V

EHT

470Ω

1/2W

465

FOCUS

SCREEN

Beam

4

3

FIL.

2

Current

GND

VERTICAL

DEFLECTION

YOKE

S4

S2

S1

FR205

440

FR205

438

1.5uF

250V

400V

443

HER205 HER205

477

.10Ω

.10Ω

1W

475

Vs

20VDC

15Vpp

37,I6

Min.Max.

H Size

GND

478

1W

476

28,D3

0Ω

524

&

525

CPT1538

12mH

447

YC4

445

.033uF

800V

1.6KV

441

0.1uF

200V

437

GND

0Ω

0Ω,

092

092A

0

1

2

3

4

5

6

7

8

TC11

Fil.

TC12

Fil. Rtn.

Video

Board

800

NO DVM

Hs

.9KVpp

1N4007

+

100uF

200Ω 2W

12-18VDC

Hs

Horizontal Drive

2SC

4159

33Vpp 26,E7

337

GND

342

338

340

19

20

100Ω

I11

2,200pF

343

Transformer

CPT1505

2

332

3

1

4

12-18VDC

50Vpp

2SD1651

1N4007

435

1.2Ω

434

29,F6

27,G6

NC

433

0Ω

452

GND

Vs

V-

0Ω

466

390Ω, 2W

12-18VDC

1,000uF

35V

VRP

10.0K

I BEAM

022

+6V

VFB

10.0K

023

12.1K

+6V

034

I BEAM

V-

V HYP

H SIZE

+

449

0Ω

193

H. S. +12V

13

12

GND

15.8K

62K

011

421

0Ω

192

V

0 TO 7 VDC

+6V

4

1/4

14

LM324

033

11

High Temperature Or

Excessive Beam

037

Current, Monitor Shut

Down Circuit.

3

1/4

LM324

2

033

200K

I BEAM

V-

+6V

VFB

V HYP

H SIZE

0Ω

194

.33uF

10K

038

082

200K

040

6V

3.92K

009

68.1K

I BEAM

097

.1uF

010

H SIZE

V-

+6V

GND

+25V

HS +12V

44.2K

+

H SIZE

100uF

061

043

12.1K

045

GND

5

6

.01uF

047

109

HORIZONTAL WIDTH CONTROL

H. S. +12V

10.0K

029

5

1/4

LM324

6

033

Parabolic

Pincushion

Blooming

correction.

.01uF

054

8

1/2

7

LM392

049

4

10.0K

3-5Vpp

RAS. POS.

510Ω

021

1

10.0K

7

5.6-6.2VDC

2-3.6Vpp 33,B2

Correction

200K

044

44.2K

058

10K

055

095

Vs

31,F5

2SC3467

+

100uF

026

22K

017

200K

005

031

6V

3.3K

050

Vs

2

3

2-2.5VDC

4.4Vpp 39,B3

+

GND

28K

041

3.3K

042

1/2

LM392

6.8K

056

420

100uF

25V

035

0Ω

019

2SA

1371

008

9

10

28.0K

049

Hs

0Ω

191

100Ω

1/2W

394

GND

1/4

LM324

3.3K

053

-Linear

Pincushion

Correction

5.6-6.2VDC

1-1.7V 34,B2

096

1

6.8nF

057

+61V

+43V

10.0K

051

033

15.8K

030

3.3K

052

1N4937

462

2.7K

060

0Ω

8

Vs

Open

419F

22K

189

4.7Ω

185

4.7Ω

195

4-19VDC

27Vpp 36,J7

510Ω

0.8-7VDC

12Vpp 38,J7

461094

Screen

FOCUS

FLYBACK

TRANSFORMER

10

6

9

8

7

5

1

CPT1558

0Ω

Open

419B

419E

0Ω

419A

0Ω

188

HORIZONTAL YOKE

446

YC3

107V or 127VDC

120Vpp 250Vpp

H. Linearity

4VDC

20VDC

30Vpp 35,H7

200Vpp

Min.Max.

CPT1528

Hs

50uH

IRF520

460

Hs

EHT

453

YC1

426

YC2

427

Horizontal Raster Adj.

150Ω 1/2W

425

270Ω

SR

424

510Ω

423

SL

Hs

32,F6

H Size

Min.Max.

470Ω

430

1/2W

428

coil

1,000pF

432

431

Hs

H Size

444

457

458

0Ω

454

1nF

500V

4VDC

463

11Vpp

Ω

470

1/2W

464

6.8uF 100V

456

HORIZONTAL WIDTH DRIVE

No

.

LTR.No

.

X

X

X-

X-Y VDC

Y V

X-Y VDC

Sync.

TP-REF.Vp-p

WAVEFORM

LEGEND

BOARD PART No.

PART No. ON PRA.

PRA PIN No.

DC VOLTAGE RANGE,

{

USING A DMM.

USE V. or H. SYNC.

AC VOLTS

Peak to Peak

Measured with scope

TEST POINT

ASS. REF.

CERONIX

SCALE

:

DRAWN BY:

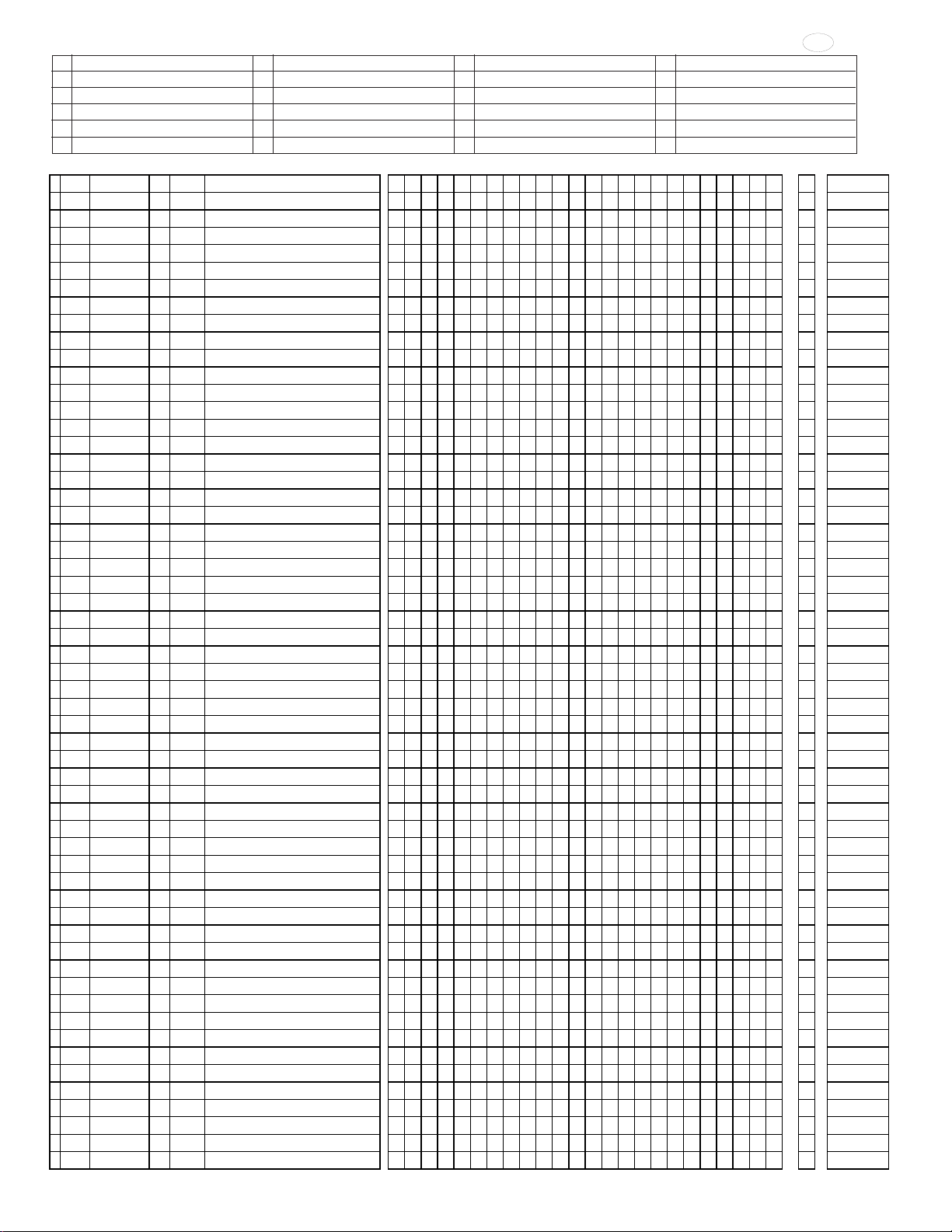

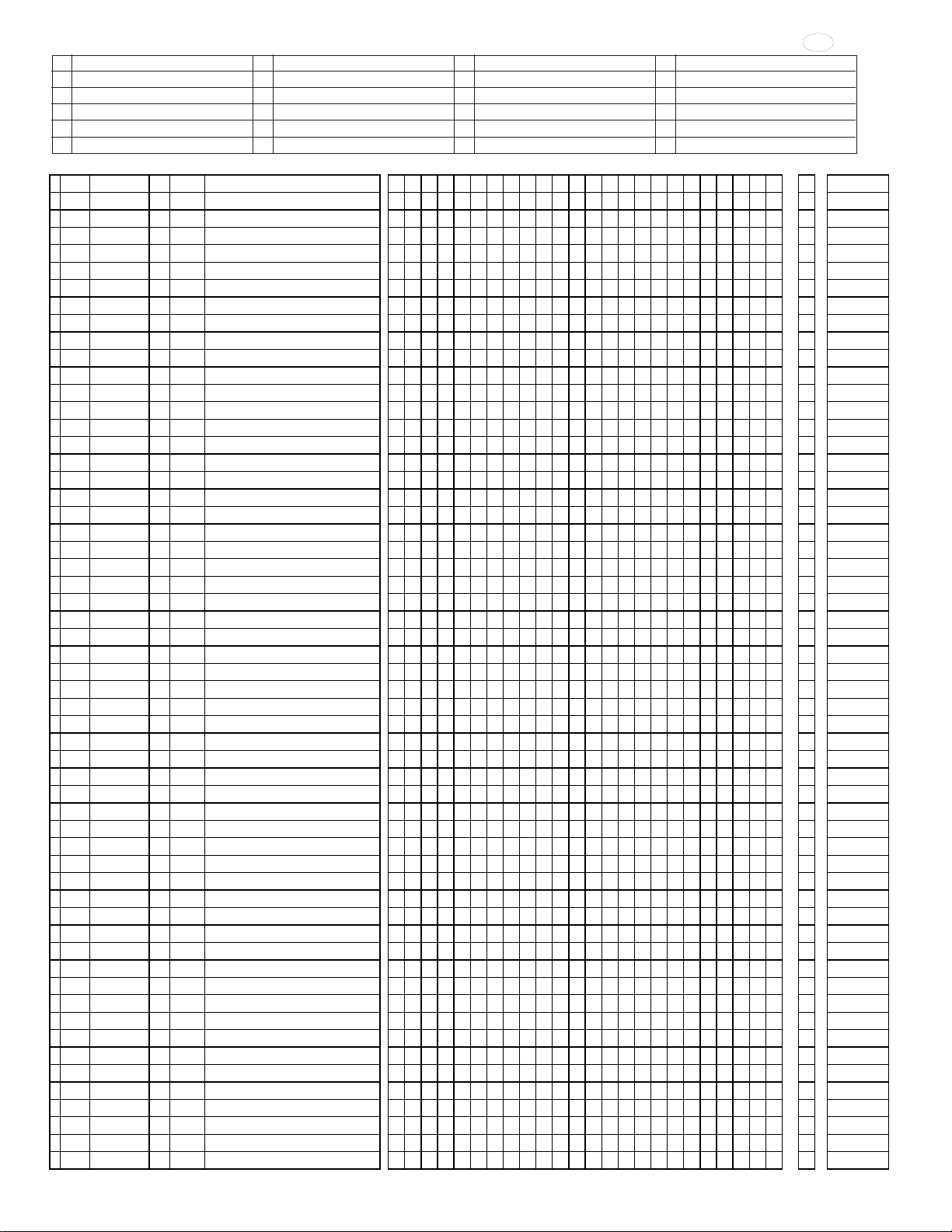

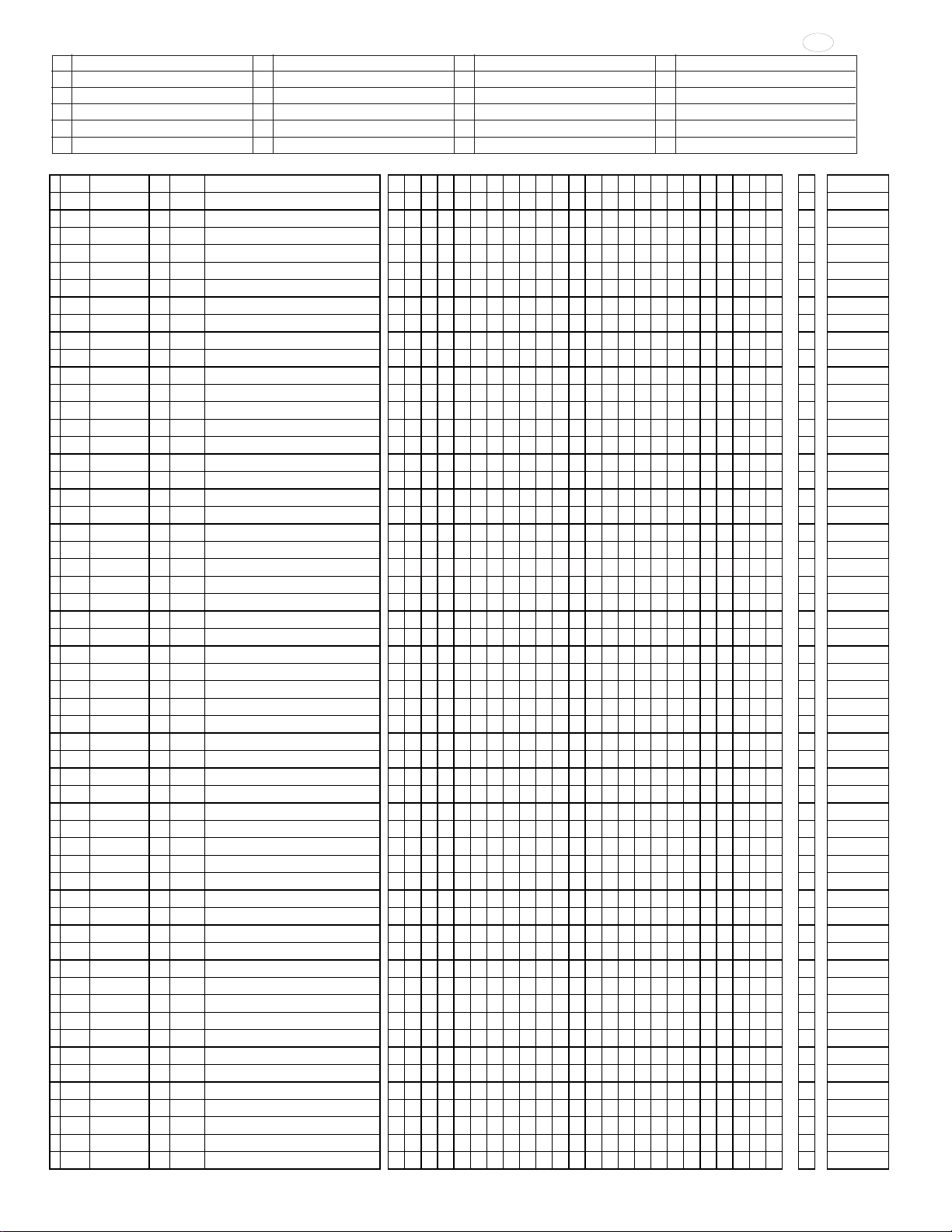

CERONIX Model 1493-CGA Monitor Circuit.

CERONIX

PART NO.

DATE & REV.

NONE

F. H.

2/18/92

CPA4233, CPA4235

13350 New Airport Road

Auburn, California 95602

4/10/96-E1

9/30/96-E4

3/24/99-E5

03/06/02-E8

9

16

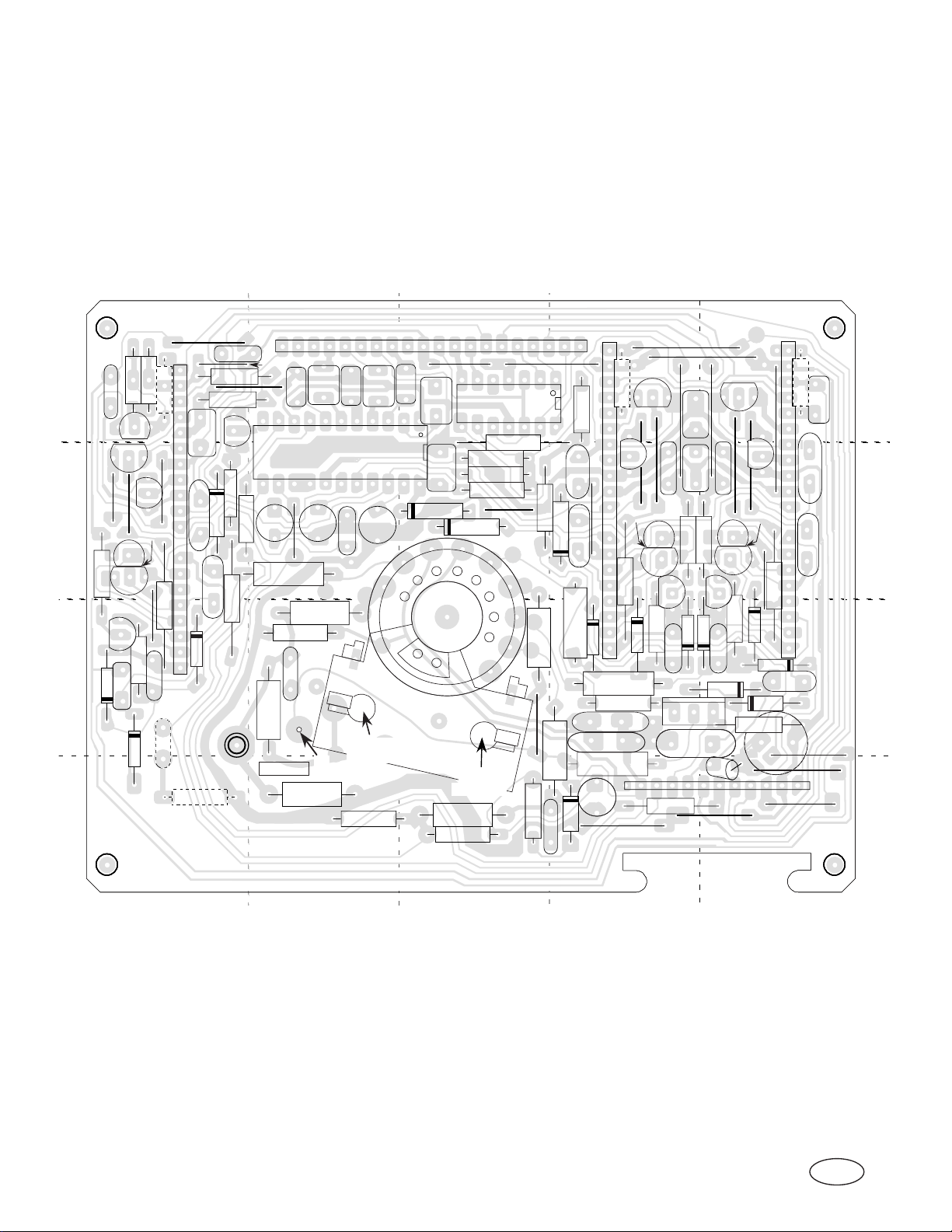

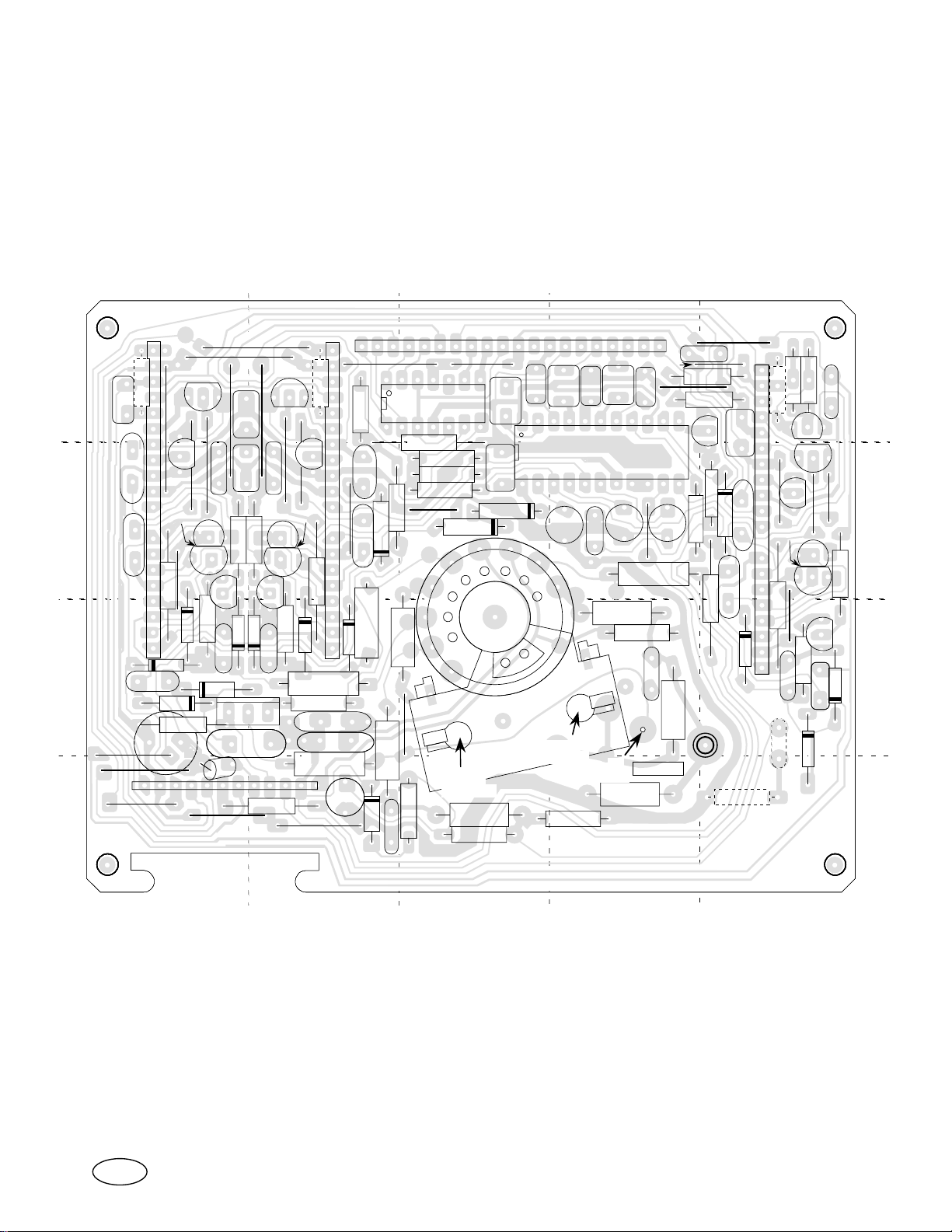

Page 21

9

ABCDEFGHI J

1

2

3

4

5

6

7

62K, 011

1K, 012

A64

036

15.8K, 037

10K, 038

200K, 040

28.0K,

039

039

043

44.2K,

044

200K,

12.1K, 045

046

0Ω, 048

062

2.15K,

18Ω, 063

064

909Ω,

1K, 065

75Ω, 066

0Ω,067

0Ω, 068

0Ω, 222

223 242

224

225

226

227

0Ω, 228

0Ω,

293

292

0Ω,

+

220uF

298

294

7812, 296

0Ω, 295

231

235

235

236

236

6

5

291

4

3

2

1

0

0

0Ω, 297

232

233

234

230

230

0Ω, 001

.1uF

010

10uF

+

014

041

3.3K,

.01uF, 047

071

070

070

221

237

288

290

300

100uF

Remote Connector

002

+

016

016

0Ω, 015

042

3.3K, 050

LM392

100uF

+

061

2222-Mot.

072

2222-Mot.

219

220

C5346A

241

239

238

285

286

287

301

302

+

304

CPS1804

1371

008

009

3.92K

4148, 018

22K, 017

LM324

033

12.1K, 034

10.0K, 051

049

240

0Ω,

303

052

3.3K,

3.3K, 053

.01uF, 054

10K, 055

6.8K, 056

6.8nF,

44.2K, 058

2.7K, 060

.039uF,

081

2.15K,

074

0Ω, 217

H400, 213

218

266

NORMAL POLARITY SHOWN

283

284

282

282

281

0Ω,

311

310

305

078

075

075

280

243264

0Ω,

4937,

604Ω,

263

+

100uF

267

278

308

.33uF

215

0Ω,

262

268

277

312

0Ω

019

15.8K, 020

510Ω, 021

10.0K, 022

10.0K, 023

0Ω, 032

10.0K, 031

030

15.8K,

057

082

080

077

077

076

206

0Ω, 214

0Ω, 216

244

105Ω,

260

261

412Ω,

270

271

276

313

307

315

316

510Ω, 004

003

200K, 005

006

+

026

10.0K, 029

097

096

10.0K, 095

0Ω, 094

093

270Ω,

088

0Ω,

127K, 087

CPS1757

LM393

0Ω, 211

210

247

247

1.8K, 248

6.8K, 250

33K,

254

2222

256

255

255

200K,

2222

259

15.8K,

3.3nF,

3.92K, 356

LM339

355

47nF,318

320

321

6.8k, 322

6.8K,

006510Ω,

527

024

025

4007, 090

6.8K, 251

0Ω, 365

127K, 361

1K,

357

22K, 323

007

100uF

+

035

100uF

68.1K,

28.0K,

0Ω, 083

+

100uF

089

H400,084

68.1K, 085

400, 086

12 pin video board connector.

+

100uF

209

212

2907

245

246

604Ω,

200K,

258

257

464Ω,

272

272

100K,

3.92K,

274

273

275

2222

319

309

317

0Ω, 314

027

028

0Ω, 092

0Ω, 092A

1.0K, 208

252

252

4148,253

1.8K,

22K, 370

1.8K, 368

18Ω, 367

7.15K,

7.15K,

2.2M, 363

365K, 362

365K, 362

360

358

0Ω. 324

1.8K, 325

099

6.8K,

205

205

47nF,207

366

366

364

270Ω, 326

100K, 113

1371

112

JA

105

106

62K, 098

2222

0Ω, 202

0Ω, 203

0Ω, 204

100uF

+

376

93.1K,

2222

200K, 372

200K, 371

.01uF

414

IA

352

56pF

354

68.1K,

0Ω, 328

270Ω, 327

270Ω, 330

0Ω, 114A

JB

JC & JD

1nF

110

3.3nF

108

56pF

107

56pF

104

103

103

6.8nF

102

101

10

0Ω, 100A

5

100B

201

381

0Ω, 200

199

399

377

1nF, 369

375

373

H

409

2907

411

200K, 413

200K, 412

Horizontal Control

351

1000pF,

12.1K, 329

15.8K, 353

4007,333

339

1.8K, 331

529

115A

J PRA, 111 Power Supply

127

4007, 116

+

380

1uF

347

334

402

404

404

+

+

382

1uF

401

403

407

407

415

120

383

200K,

0Ω, 389

346

.01uF

332

118

119

IB IC ID

348

220uF

0Ω, 198A

198

381A

470uF

50V

LA7838

374.01uF,

2222

330pF

H. Drive,

115

C5184

+

4007,

+

28.0K,

100K,

169K,

4148, 405