GENESYS GL602USB-A, GL602USB Datasheet

Your Imagination, Our Creatio

n

GL602USB

GL602USB-A

USB KEYBOARD

MICROCONTROLLER

SPECIFICATION 1.6

Feb. 28, 2001

Genesys Logic, Inc.

10F, No.11, Ln.3, Tsao Ti Wei, Shenkeng, Taipei, Taiwan

Tel: +886-2-2664-6655 Fax: +886-2-2664-5757

http://www.genesyslogic.com/

Index

1 FEATURES............................................................................................................4

2 FUNCTIONAL OVERVIEW...............................................................................5

3 PIN DEFINITIONS AND DESCRIPTIONS......................................................6

3.1 GL602USB...............................................................................................................................6

3.2 GL602USB-A...........................................................................................................................7

4 FUNCTIONAL DESCRIPTION .........................................................................9

4.1 MEMORY ORGANIZATION.................................................................................................9

4.2 USB FUNCTION REGISTERS.............................................................................................11

4.3 MCU FUNCTION REGISTERS............................................................................................16

4.4 GENERAL PURPOSE I/O PORTS .......................................................................................18

4.5 TIMER INTERRUPT.............................................................................................................18

4.6 USB ENGINE.........................................................................................................................19

4.7 INSTRUCTION SET SUMMARY........................................................................................21

5 Firmware Programming Guide..........................................................................23

5.1 USB Power On Reset and Bus Reset Initialization.................................................................23

5.2 Suspend/Resume/Wakeup ......................................................................................................24

5.3 Receive Packet via Endpoint 0...............................................................................................25

5.4 Transmit Packet via Endpoint 0..............................................................................................26

5.5 Transmit Packet via Endpoint 1/2/3........................................................................................27

5.6 Timer Interrupt .......................................................................................................................28

5.7 Conditional Branch.................................................................................................................28

5.8 Change Register Bank............................................................................................................28

5.9 Change Code Bank.................................................................................................................28

5.10 Receive Data from PS/2 Mouse Port......................................................................................29

5.11 Scan Key Matrix.....................................................................................................................30

5.12 Turn LED On/Off...................................................................................................................30

6 ABSOLUTE MAXIMUM RATINGS................................................................31

7 ELECTRICAL CHARACTERISTICS.............................................................31

8 PACKAGE DIAGRAMS....................................................................................33

8.1 40-pin P-DIP...........................................................................................................................33

8.2 24-pin SOP .............................................................................................................................34

Revision 1.6 -2- 02/28/2000

Figures

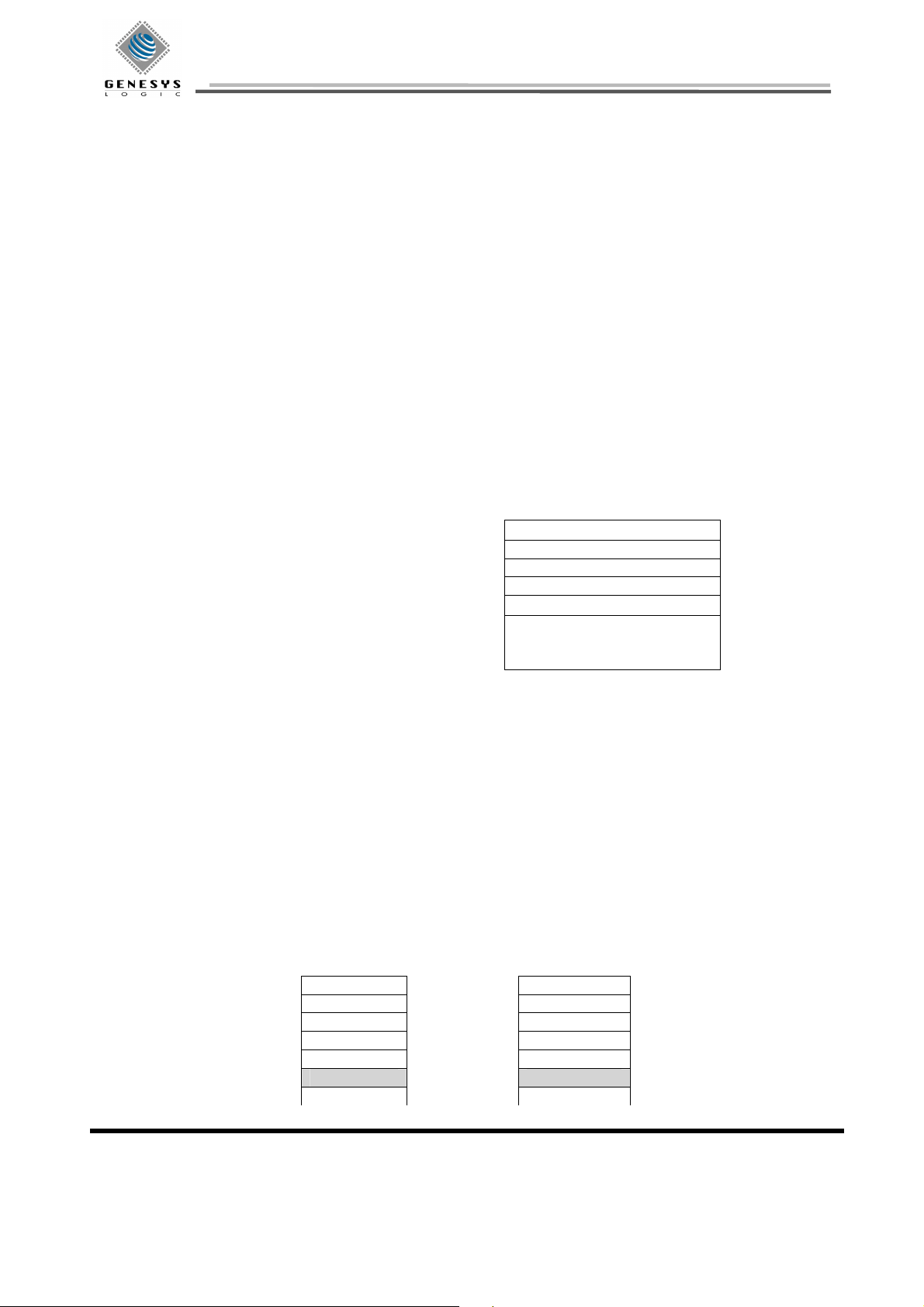

Figure 3-1 40-pin DIP (GL602USB) ........................................................................... 7

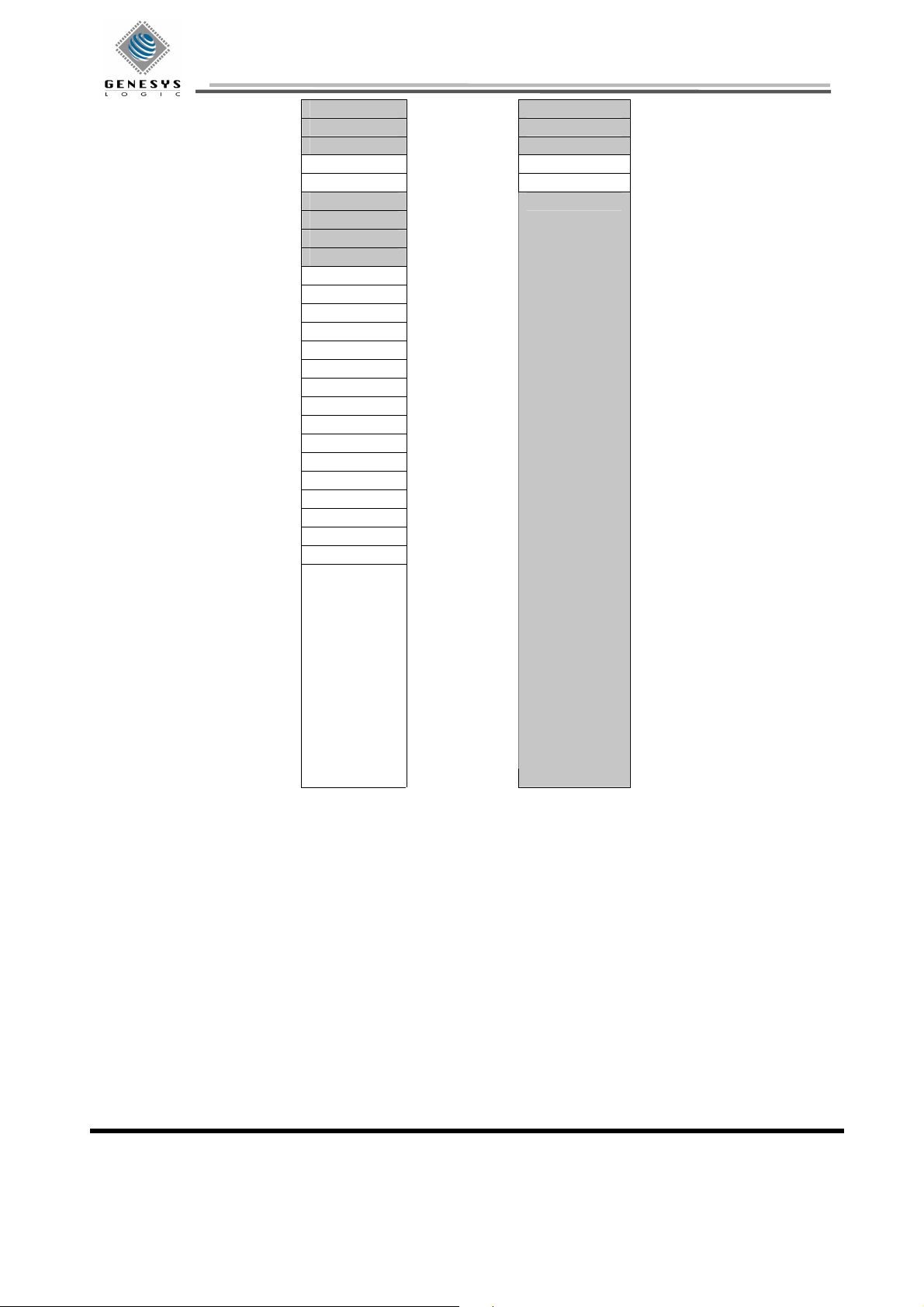

Figure 3-2 24-pin SOP (GL602USB-A)...................................................................... 8

Figure 4-1 Program Memory Space............................................................................. 9

Figure 4-2 Data Memory Space................................................................................. 10

Figure 4-3 Differential Input Sensitivity over Entire Common Mode Range ........... 20

Figure 4-4 Receiver Jitter Tolerance.......................................................................... 20

Figure 4-5 Data Signal Rise and Fall Time................................................................ 21

Figure 7-3 Package outline dimension for 40-pin P-DIP........................................... 33

Figure 7-4 Package outline dimension for 24-pin SOP ............................................. 35

Tables

Table 3-1 GL602USB Pin Definitions and Descriptions............................................. 6

Table 3-2 GL602USB-A Pin Definitions and Descriptions......................................... 7

Table 4-1 USB Function Register Summary ............................................................. 11

Table 4-2 MCU Function Register Summary............................................................ 16

Revision 1.6 -3- 02/28/2000

1. FEATURES

• Low-cost solution for low-speed USB keyboard

• 8-bit micro-controller

− Operation Speed: 6MHz clock input

− Performance: 3 MIPS @ 6MHz

− Single cycle instruction execution

− RISC-like architecture

− USB optimized instruction set

• USB Specification Compliance

− Conforms to USB 12Mbps Specification, Version 1.1

− Conforms to USB HID Class Specification, Version 1.1

− Supports 1 device address and 4 endpoints (include endpoint 0)

• I/O ports

− Up to 7(GL602USB)/5(GL602USB-A) general purpose I/O pins (OTP type is less a GPIO pin than mask

type).

− Up to 8 sense pins and 1 I/O pin with remote wakeup capability

− Up to 18(GL602USB)/8(GL602USB-A) output pins optimized for key matrix drive pin

− Up to 8(GL602USB)/4(GL602USB-A) output pins optimized for key matrix sense pin

− Up to 3(GL602USB)/1(GL602USB-A) I/O pins with LED drive capability

• Internal memory

− 96 bytes of RAM

− 4K x 14 of program ROM

• On-chip 3.3v output

− No external regulator required

• Improved output drivers with slew-rate control to reduce EMI

• 6 MHz external clock

• Internal power-on reset (POR)

• Internal power-fail detector

• Supports suspend/normal mode power management

− Suspend current lower than 400µA for the whole keyboard system (mask type)

• 8-bit free-running timer

• Available in cost saving 40-pin(GL602USB) PDIP, 24-pin(GL602USB-A) SOP

• Support a PS/2 mouse to USB mouse converter in the default firmware.

Revision 1.6 -4- 02/28/2000

2. FUNCTIONAL OVERVIEW

The GL602USB is an 8-bit RISC-like high performance microcontroller with a built-in 1.5Mbps SIE and

transceiver. The microcontroller features 33 instructions optimized for USB keyboard. There are 96 bytes onchip RAM and 4K x 14 bits program ROM incorporated into the micro-controller. The micro-controller features

18 output pins and 8 input pins to make a 18 x 8 key matrix. Additionally, 3 GPIO pin s are strong enough to

drive LEDs. 4 GPIO pins can be used by any function, for example, support a PS/2 3D mouse to USB 3D mouse

converter in the default firmware. Legacy USB cable can be used for keyboard in USB mode. All GPIO ports

feature low EMI emissions as a result of improved output drivers with slew-rate control.

Revision 1.6 -5- 02/28/2000

3. PIN DEFINITIONS AND DESCRIPTIONS

3.1 GL602USB

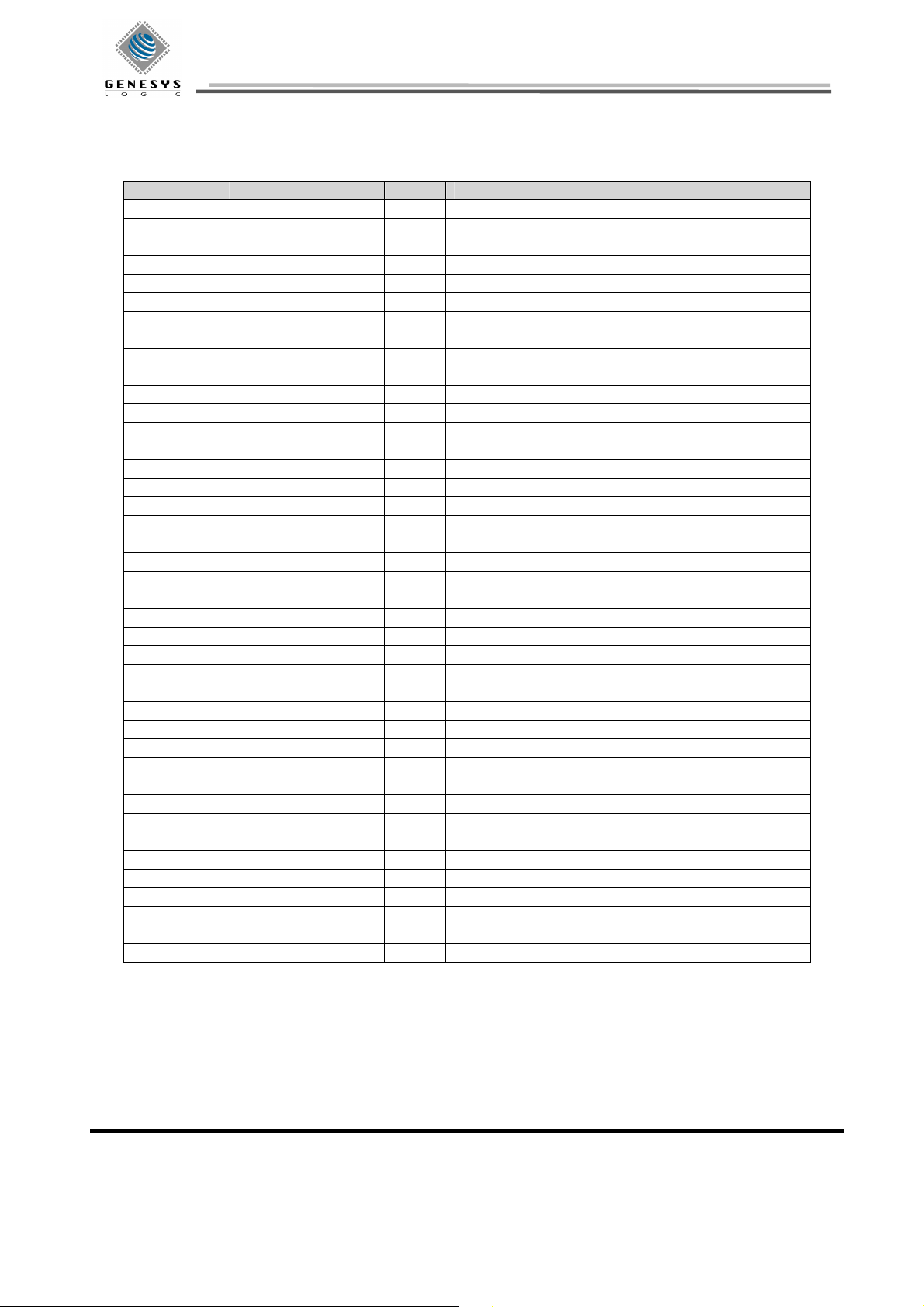

Table 3-1 GL602USB Pin Definitions and Descriptions

Pin No. Name I/O Description

1 GND - Ground

2 V3.3 O 3.3V output

3 D+ I/O USB data+

4 D- I/O USB data5 DRV1 O Key matrix output drive 1, open drain output

6 DRV2 O Key matrix output drive 2, open drain output

7 P1.1/MOUSE CLK I/O Port 1 bit 1 / PS2 mouse clock input

8 P1.2/MOUSE DATA I/O Port 1 bit 2 / PS2 mouse data input

9 P1.3/VPP I/O Port 1 bit 3 (for mask) / 12.75V programming power

(for OTP)

10 P1.4/PWRCTL I/O Port 1 bit 4 / PS2 mouse power control

11 DRV3 O Key matrix output drive 3, open drain output

12 DRV4 O Key matrix output drive 4, open drain output

13 DRV5 O Key matrix output drive 5, open drain output

14 DRV6 O Key matrix output drive 6, open drain output

15 DRV7 O Key matrix output drive 7, open drain output

16 DRV8 O Key matrix output drive 8, open drain output

17 DRV9 O Key matrix output drive 9, open drain output

18 DRV10 O Key matrix output drive 10, open drain output

19 DRV11 O Key matrix output drive 11, open drain output

20 DRV12 O Key matrix output drive 12, open drain output

21 DRV13 O Key matrix output drive 13, open drain output

22 DRV14 O Key matrix output drive 14, open drain output

23 DRV15 O Key matrix output drive 15, open drain output

24 DRV16 O Key matrix output drive 16, open drain output

25 DRV17 O Key matrix output drive 17, open drain output

26 DRV18 O Key matrix output drive 18, open drain output

27 SENSE1 I Key matrix input sense 1, internal pull up 10K

28 SENSE2 I Key matrix input sense 2, internal pull up 10K

29 SENSE3 I Key matrix input sense 3, internal pull up 10K

30 SENSE4 I Key matrix input sense 4, internal pull up 10K

31 SENSE5 I Key matrix input sense 5, internal pull up 10K

32 SENSE6 I Key matrix input sense 6, internal pull up 10K

33 SENSE7 I Key matrix input sense 7, internal pull up 10K

34 SENSE8 I Key matrix input sense 8, internal pull up 10K

35 P1.5/NUMLOCK I/O Port 1 bit 5/number lock indicator, internal pull up

36 P1.6/CAPSLOCK I/O Port 1 bit 6/caps lock indicator, internal pull up

37 P1.7/SCROLLLOCK I/O Port 1 bit 7/scroll lock indicat or, internal pull up

38 VDD - Voltage supply

39 XTAL1 O Ceramic resonator or crystal out

40 XTAL2 I Ceramic resonator or crystal in

Note 1: Name or description after “/” means default function specified by Genesys Logic firmware

Revision 1.6 -6- 02/28/2000

GND

V3.3

D+

D-

DRV1

DRV2

P1.1/MOUST CLK

P1.2/MOUSE DATA

P1.3

P1.4/PWRCTL

DRV3

DRV4

DRV5

DRV6

DRV7

DRV8

DRV9

DRV10

DRV11

DRV12

3.2 GL602USB-A

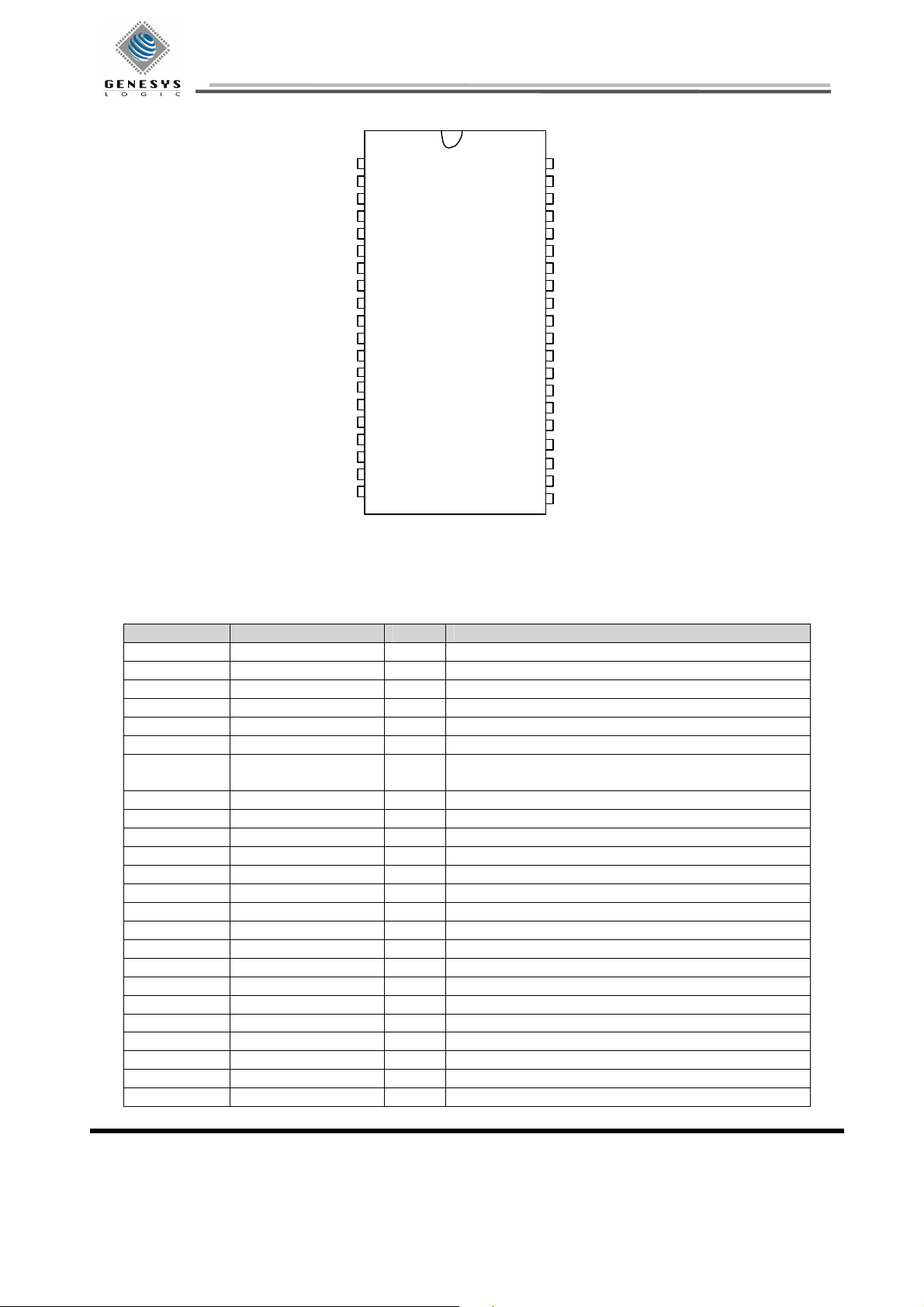

Table 3-2 GL602USB-A Pin Definitions and Descriptions

Pin No. Name I/O Description

1 GND - Ground

2 V3.3 O 3.3V output

3 D+ I/O USB data+

4 D- I/O USB data5 P1.1/MOUSE CLK I/O Port 1 bit 1/PS2 mouse clock input

6 P1.2/MOUSE DATA I/O Port 1 bit 2/PS2 mouse data input

7 P1.3/VPP I/O Port 1 bit 3 (for mask) / 12.75V programming power

8 P1.4/PWRCTL I/O Port 1 bit 4 / PS2 mouse power control

9 DRV7 O Key matrix output drive 7, open drain output

10 DRV8 O Key matrix output drive 8, open drain output

11 DRV10 O Key matrix output drive 10, open drain output

12 DRV12 O Key matrix output drive 12, open drain output

13 DRV13 O Key matrix output drive 13, open drain output

14 DRV15 O Key matrix output drive 15, open drain output

15 DRV16 O Key matrix output drive 16, open drain output

16 DRV17 O Key matrix output drive 17, open drain output

17 SENSE1 I Key matrix input sense 1, internal pull up 10K

18 SENSE3 I Key matrix input sense 3, internal pull up 10K

19 SENSE6 I Key matrix input sense 6, internal pull up 10K

20 SENSE8 I Key matrix input sense 8, internal pull up 10K

21 P1.7/LED I/O Port 1 bit 7/LED indicator

22 VDD - Voltage supply

23 XTAL1 O Ceramic resonator or crystal out

24 XTAL2 I Ceramic resonator or crystal in

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Figure 3-1 40-pin DIP (GL602USB)

(for OTP)

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

XTAL2

XTAL1

VDD

P1.7SCROLOCK

P1.6/CAPSLOCK

P1.5/NUMLOCK

SENSE8

SENSE7

SENSE6

SENSE5

SENSE4

SENSE3

SENSE2

SENSE1

DRV18

DRV17

DRV16

DRV15

DRV14

DRV13

Revision 1.6 -7- 02/28/2000

Note 1: Name or description after “/” means default function specified by Genesys Logic firmware

GND

V3.3

D-

P1.1/MOUSE CLK

P1.2/MOUSE DATA

P1.3/VPP

P1.4/PWRCTL

DRV7

DRV8

DRV10

DRV12

Figure 3-2 24-pin SOP (GL602USB-A)

D+

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

XTAL2

XTAL1

VDD

P1.7/LED

SENSE8

SENSE6

SENSE3

SENSE1

DRV17

DRV16

DRV15

DRV13

Revision 1.6 -8- 02/28/2000

4. FUNCTIONAL DESCRIPTION

The Genesys Logic GL602USB micro-controller is optimized for PC keyboard. This USB microcontroller

conforms to the low-speed (1.5Mbps) requirements of the USB Specification version 1.1. The micro-controller is a

self-contained unit with an USB SIE, an USB transceiver, an 8-bit RISC-like microcontroller, a timer, data and

program memories. It supports one USB device address and four endpoints (include endpoint 0).

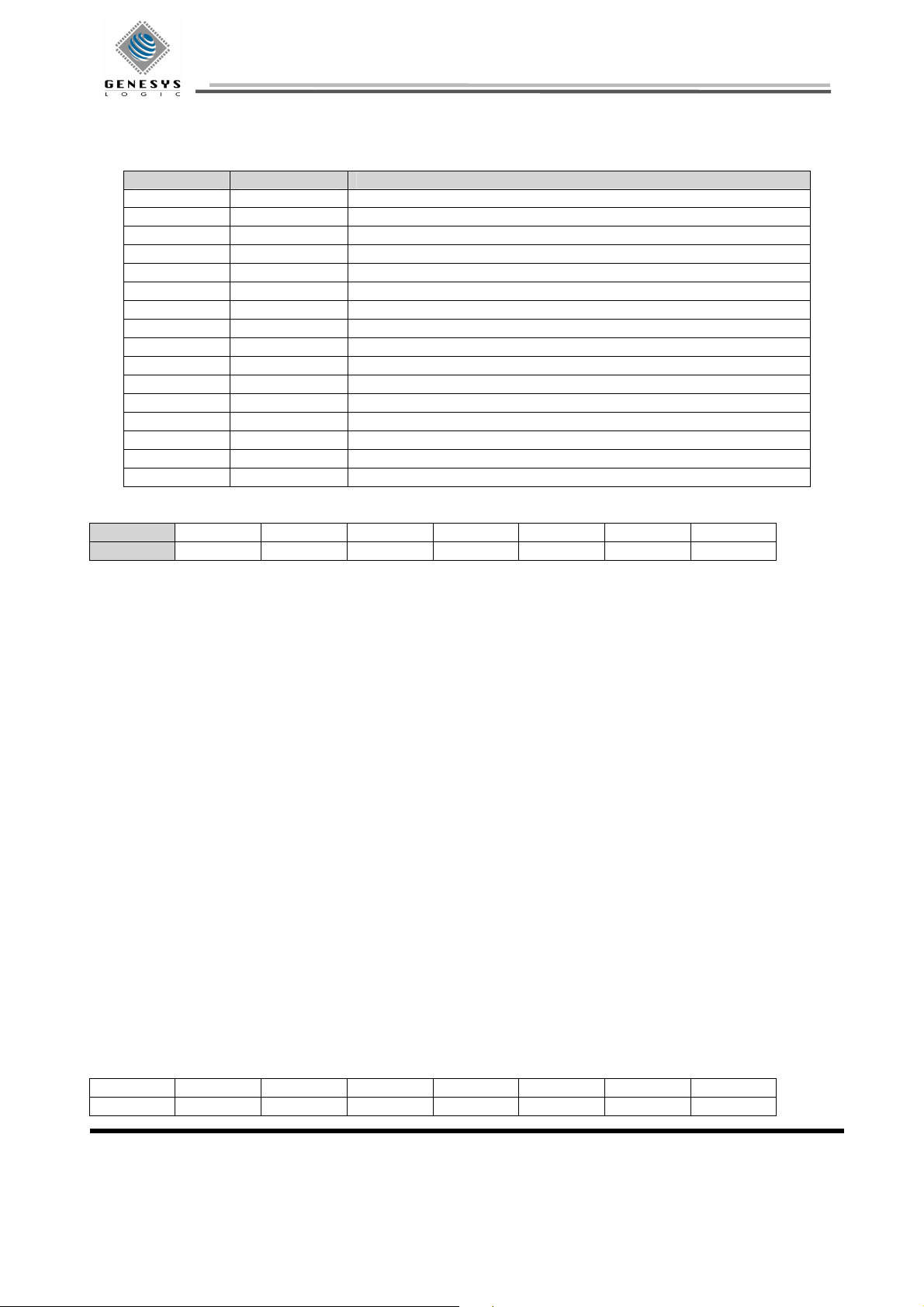

4.1 MEMORY ORGANIZATION

The memory in the microcontroller is organized into user program memory in program ROM and data memory

in SRAM space.

4.1.1 Program Memory Organization

The 12-bit Program Counter (PC) is capable of addressing 4K x 14 of program space. All of the 4K * 14 ROM

space can be used. The program memory space is divided into two functional groups: Interrupt Vectors and

program code. After a reset, the Program Counter points to location zero of the program space and all registers

are reset to the default value. After a timer interrupt, the Program Counter points the location 0x0004 of the

program space.

Address

After Reset

After Timer Interrupt

0x0005

Figure 4-1 Program Memory Space

4.1.2 Data Memory Organization

The data memory is partitioned into two Banks that contain the General Purpose Registers, MCU Function

Registers and USB Function Registers. Bit BS is the bank select bit.

BS (STATUS<5>) = 1 → Bank 1

BS (STATUS<5>) = 0 → Bank 0

The lower locations of each Bank are reserved for MCU Function Registers and USB Function Registers.

Above the MCU Function Registers and USB Function Registers are General Purpose Registers implemented

as SRAM. Both Bank 0 and Bank 1 contain MCU Function Registers. USB Function Registers are l ocated in

Bank 0. Some “high use” MCU Function Registers from Bank 0 are mirrore d in Bank 1 for code reduction and

quicker access.

Data

Memory

Address

00h INDR 80h INDR

01h TIMER 81h PSCON

02h PCL 82h PCL

03h STATUS 83h STATUS

04h INDAR 84h INDAR

05h 85h

06h PORT1 86h PORT1CON

Data Memory

0x0000 Reset Vector

→

0x0004 Timer Interrupt Vector

→

0x0FFF

Address

4K x 14 ROM

Revision 1.6 -9- 02/28/2000

07h 87h

08h 88h

09h 89h

0Ah PCHBUF 8Ah PCHBUF

0Bh INTEN 8Bh INTEN

0Ch 8Ch

0Dh 8Dh

0Eh 8Eh

0Fh 8Fh

10h DEVCTL

11h EVTFLG

12h DEVADR

13h RXCTL0

14h TXCTL0

15h TXCTL123

16h FFDAT0

17h FFDAT123

18h DRVSEL

19h SENSE

1Ah FFRST

1Bh MODESEL

1Ch PS2CTL

1Dh EPSEL

1Eh SERCTL

1Fh SERDAT

20h

7Fh

Bank 0 Bank 1

General

Purpose

Registers

(96 bytes)

FFh

Figure 4-2 Data Memory Space

Revision 1.6 -10- 02/28/2000

4.2 USB FUNCTION REGISTERS

Table 4-1 USB Function Register Summary

Address Name Function

10h DEVCTL Device control register

11h EVTFLG Event flag register

12h DEVADR USB device add r ess register

13h RXCTL0 Endpoint 0 receive control register

14h TXCTL0 Endpoint 0 transmit control register

15h TXCTL123 Endpoint 1/2/3 transmit control register

16h FFDAT0 Endpoint 0 FIFO data port

17h FFDAT123 Endpoint 1/2/3 FIFO data port

18h DRVSEL Key matrix drive pin control register

19h SENSE Key matrix sense register

1Ah FFRST FIFO reset register

1Bh MODESEL USB mode select register

1Ch Reserved

1Dh EPSEL Endpoint select register

1Eh SERCTL PS/2 mouse port control register

1Fh SERDAT PS/2 mouse port data register

DEVCTL (Address 10h, Device control register)

R/W

[1]

R/W R/W R/W R/W R/W R/W

EP3STL EP2STL EP1STL EP0STL WAKE WKDIS PWRDN

EP3STL: Endpoint 3 stall bit

1: Endpoint 3 will respond with a STALL to a valid transaction

0: Endpoint 3 will not respond with a STALL to a valid transaction

EP2STL: Endpoint 2 stall bit

1: Endpoint 2 will respond with a STALL to a valid transaction

0: Endpoint 2 will not respond with a STALL to a valid transaction

EP1STL: Endpoint 1 stall bit

1: Endpoint 1 will respond with a STALL to a valid transaction

0: Endpoint 1 will not respond with a STALL to a valid transaction

EP0STL: Endpoint 0 stall bit

1: Endpoint 0 will respond with a STALL to a valid transaction.

0: Endpoint 0 will not respond with a STALL to a valid transaction

WAKE: Wake-up bit

1: Set this bit to wake up host controller by placing USB bus into K state

0: Clear this bit to force USB bus leave K state

WKDIS: Wake-up disable bit

1: Disable remote wake-up capability

0: Enable remote wake-up capability

PWRDN: Power-down mode bit

1: Entering power-down mode

If USB suspend is detected, firmware should set this bit to enter power-down mode. In power-down mode,

6MHz crystal clock will be stopped. Hardware will automatically clear PWRDN bit upon hardware reset,

USB D+/D- toggle, SENSE1~SENSE8 at logic ‘0’, or Port 1.1 at logic ‘0’.

Value on POR: “0 0 0 0 0 0 0 0”

Note 1: “R/W” means readable and writable bit

EVTFLG (Address 11h, Event flag register)

R/W1C

[1]

R/W1C R/W1C R/W1C R/W1C R/W1C R/W1C R/W1C

WAKEUP RESUME SUSPD EP3TX EP2TX EP1TX EP0TX EP0RX

Revision 1.6 -11- 02/28/2000

Loading...

Loading...