Page 1

GE

Intelligent Platforms

Hardware Reference

V7768/V7769*

Intel® Core™ Duo Processor VME Single Board

Computer

THE V7768/V7769 IS DESIGNED TO MEET THE EUROPEAN UNION (EU) RESTRICTIONS OF

HAZARDOUS SUBSTANCE (ROHS) DIRECTIVE (2002/95/EC) CURRENT REVISION.

Publication No: 500-9300007768-000 Rev. E

Page 2

Document History

Hardware Reference Document Number: 500-9300007768-000 Rev. E

January 4, 2012

Waste Electrical and Electronic Equipment (WEEE) Returns

GE is registered with an approved Producer Compliance Scheme (PCS) and, subject to suitable

contractual arrangements being in place, will ensure WEEE is processed in accordance with

the requirements of the WEEE Directive.

GE will evaluate requests to take back products purchased by our customers before

August 13, 2005 on a case by case basis. A WEEE management fee may apply.

Page 3

Table of Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

List of Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1 • Installation and Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.1 Unpacking Procedures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

1.2 Hardware Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

1.2.1 V7768 Board Layout Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.2.2 Mezzanine Board Layout Information (V7769) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.3 Installation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

1.3.1 BIOS Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4 Front/Rear Panel Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

1.5 Front Panel Layouts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

2 • Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2.1 BGA CPU. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.2 Physical Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.3 Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

2.4 I/O Port Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

2.5 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

2.5.1 Legacy PIC System Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.5.2 PCI Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

2.6 Integrated Peripherals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

2.7 Ethernet Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

2.8 Video Graphics Adapter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

3 • Embedded PC/RTOS Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

3.1 VME Bridge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

3.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

3.1.2 I2C/SMBus Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.2 Embedded PCI Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.3 Timers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

3.3.1 Timer Control Status Register 1 (TCSR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

3.3.2 Timer Control Status Register 2 (TCSR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.3 Timer 1 & 2 Load Count Register (TMRLCR12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.4 Timer 3 Load Count Register (TMRLCR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.3.5 Timer 4 Load Count Register (TMRLCR4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.3.6 Timer 1 & 2 Current Count Register (TMRCCR12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.3.7 Timer 3 Current Count Register (TMRCCR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

3.3.8 Timer 4 Current Count Register (TMRCCR4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

3.3.9 Timer 1 IRQ Clear (T1IC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3.10 Timer 2 IRQ Clear (T2IC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

3.3.11 Timer 3 IRQ Clear (T3IC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.3.12 Timer 4 IRQ Clear (T4IC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Table of Contents 3

.

Page 4

3.4 Watchdog Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.4.1 WDT Control Status Register (WCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.4.2 WDT Keepalive Register (WKPA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.5 NVRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.6 VME Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

3.7 CompactFlash Disk (V7768 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

3.7.1 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

3.8 Remote Ethernet Booting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

3.8.1 Boot BIOS Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Maintenance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

A • Appendix A: Connector Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

A.1 V7768 VME Connectors and Pinouts (P1 and P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

A.2 V7768 PCI-X PMC Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

A.2.1 V7768 PCI-X PMC Site Connector and Pinout (J11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

A.2.2 V7768 PCI-X PMC Site Connector and Pinout (J12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

A.2.3 V7768 PCI-X PMC Site Connector and Pinout (J13) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

A.2.4 Mezzanine PCI-X PMC Site Connector and Pinout (J14) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

A.3 V7769 Mezzanine Backplane Connectors (P1 and P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

A.4 V7769 Mezzanine PCI-X PMC Site 1 Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

A.4.1 Mezzanine PCI-X PMC Site 1 Connector and Pinout (J11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

A.4.2 Mezzanine PCI-X PMC Site 1 Connector and Pinout (J12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

A.4.3 Mezzanine PCI-X PMC Site 1 Connector and Pinout (J13) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

A.5 V7769 Mezzanine PCI-X PMC Site 2 Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

A.5.1 Mezzanine PCI-X PMC Site 2 Connector and Pinout (J21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

A.5.2 Mezzanine PCI-X PMC Site 2 Connector and Pinout (J22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

A.5.3 Mezzanine PCI-X PMC Site 2 Connector and Pinout (J23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

A.5.4 Mezzanine PCI-X PMC Site 2 Connector and Pinout (J24) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

A.6 USB Connectors and Pinout (J29 and J30) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

A.7 Gigabit Ethernet Connectors and Pinouts (J15 and J18) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

A.8 Video Graphics Adapter and Pinout (J28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

A.9 Serial Connector and Pinout (J35) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

A.10 Mouse/Keyboard Connector and Pinout (J38) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

A.11 V7769 Mezzanine SAS Connector and Pinout (J28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

B • Appendix B: AMI BIOS Setup Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

B.1 First Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

B.2 Main Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

B.3 Advanced BIOS Setup Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

B.4 PCI/PnP Setup Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

B.5 Boot Setup Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

B.6 Security Setup Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

B.7 Chipset Setup Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

B.8 Exit Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

C • Appendix C: Remote Booting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

C.1 Enabling the Front Panel (FP) LAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

C.2 Boot Menus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

C.2.1 First Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

C.2.2 Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

C.3 BIOS Features Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

4 V7768/V7769 Hardware Reference Manual

Page 5

List of Figures

Figure 1 V7768 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

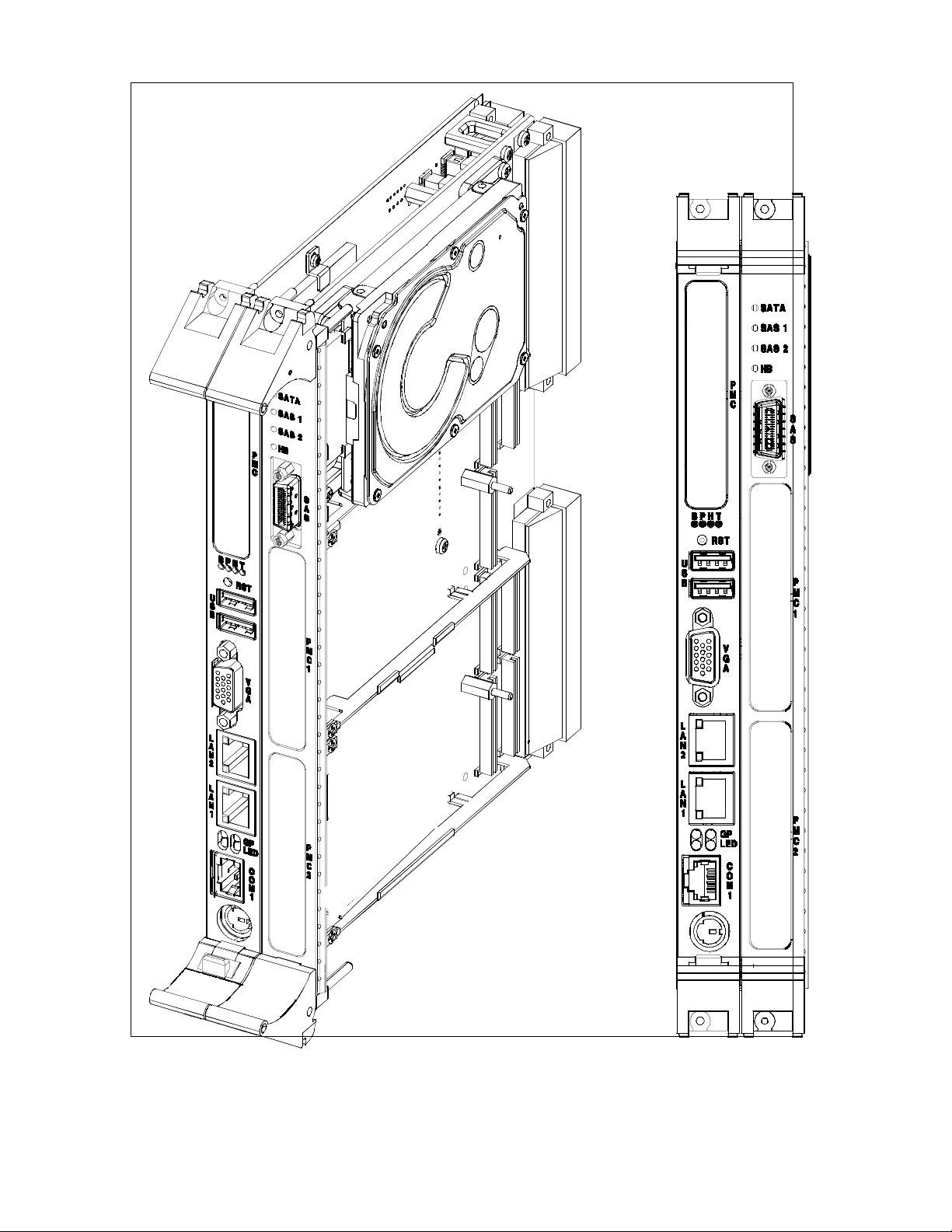

Figure 2 Illustration of V7768 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 3 V7769 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Figure 4 Illustration of V7769 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 1-1 V7768 Connector Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 1-2 COM1 Termination Headers (E13, E14, E17) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

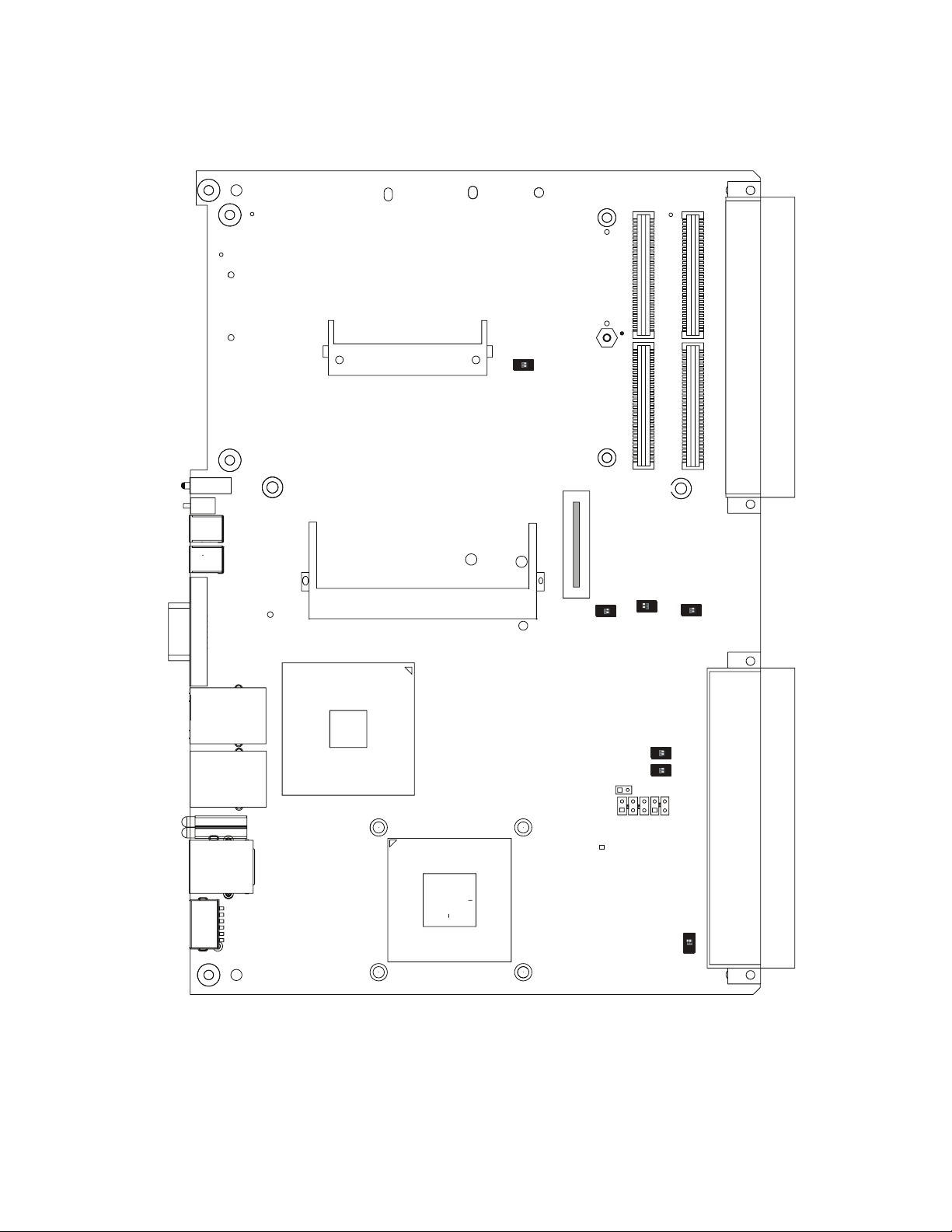

Figure 1-3 Mezzanine Board Connector Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

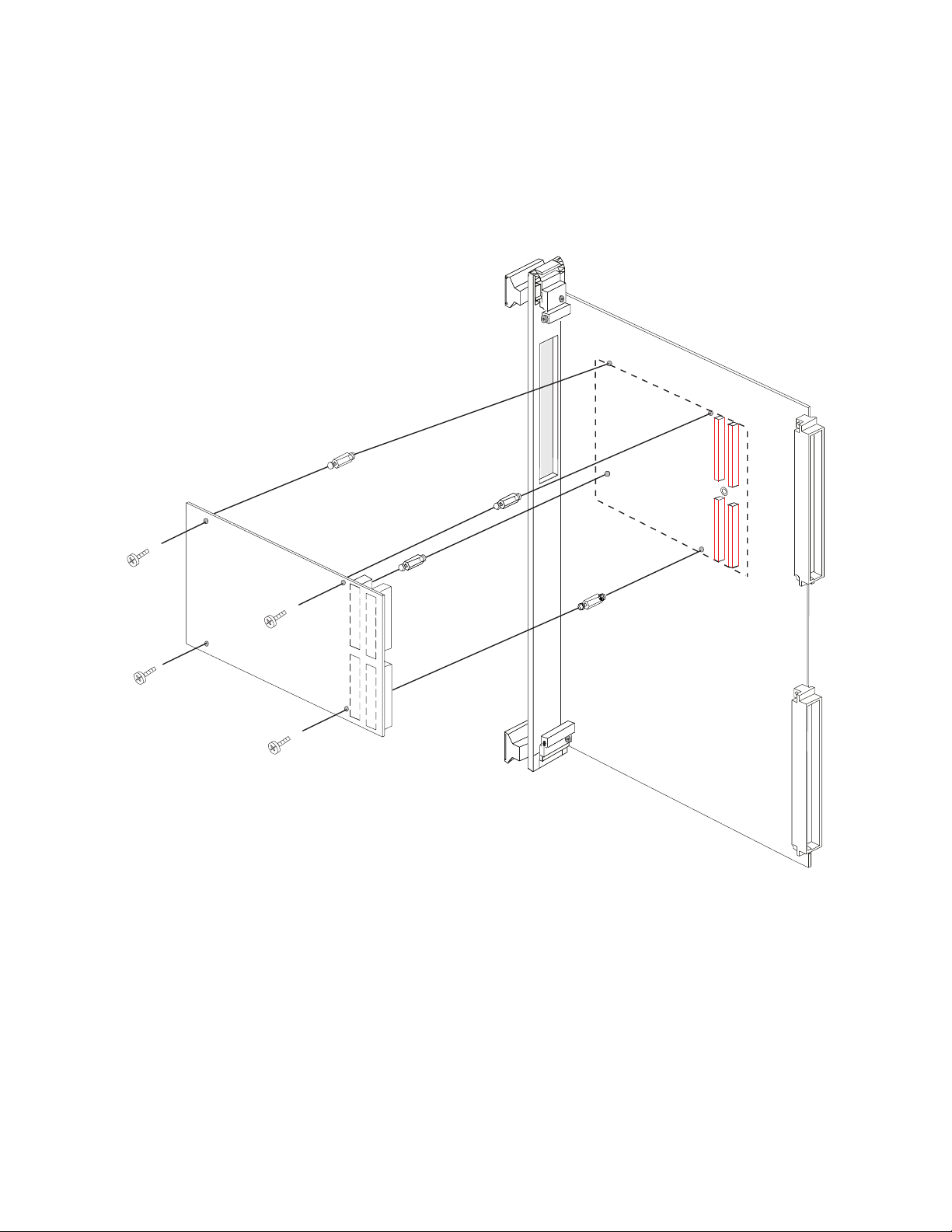

Figure 1-4 Installing the PMC Card on the V7768/V7769 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Figure 1-5 Backside Mounting for the PMC Card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 1-6 Installation of Mezzanine Board onto the Main Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 1-7 V7768 Front Panel Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 1-8 Mezzanine Front Panel Layout (for V7769) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Figure 2-1 Connections for the PC Interrupt Logic Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure A-1 V7768 Connector Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure A-2 V7769 Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Figure A-3 VME Connectors (P1/P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Figure A-4 V7768 PCI-X PMC Site Connector (J11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Figure A-5 V7768 PCI-X PMC Site Connector (J12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Figure A-6 V7768 PCI-X PMC Site Connector (J13) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Figure A-7 Mezzanine PCI-X PMC Site Connector (J14 ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure A-8 V7769 Backplane Connectors (P1 and P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Figure A-9 Mezzanine PCI-X PMC Site Connector (J11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Figure A-10 Mezzanine PCI-X PMC Site Connector (J12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Figure A-11 Mezzanine PCI-X PMC Site Connector (J13 ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure A-12 Mezzanine PCI-X PMC Site Connector (J21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Figure A-13 Mezzanine PCI-X PMC Site Connector (J22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Figure A-14 Mezzanine PCI-X PMC Site Connector (J23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Figure A-15 Mezzanine PCI-X PMC Site Connector (J24) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Figure A-16 USB Connector (J29 and J30) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure A-17 Gigabit Ethernet Connector (J18) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Figure A-18 SVGA Connector (J28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Figure A-19 Serial Connector (J35) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure A-20 Mouse/Keyboard Connector (J38) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Figure A-21 Mouse/Keyboard Splitter Cable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Figure A-22 Mezzanine Connector (J28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

List of Figures 5

.

Page 6

List of Tables

Table 1-1 V7768 Connectors and Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Table 1-2 Universe IID Mapping/SYSFAIL Generation - Switch (S6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Table 1-3 VME Strapping - Switch (S7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Table 1-4 VME System Controller - Switch (S10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Table 1-5 Battery Enable - Switch (S11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Table 1-6 Password Clear/BIOS Boot Mode - Switch (S12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Table 1-7 COM1 Configuration (RS232/RS422 Select) - Header (E13, E14, E17) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Table 1-8 Mezzanine Connectors and Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Table 1-9 Switch (S2) Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Table 2-1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Table 2-2 V7768/V7769 I/O Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Table 2-3 Interrupt Line Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Table 2-4 Interrupt Vector Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Table 2-5 PCI Device Interrupt Mapping by the BIOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Table 2-6 Supported Graphics Video Resolutions for Windows XP (Analog) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Table 3-1 PCI Configuration Space Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 3-2 TCSR1 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Table 3-3 Selectable Clock Source for Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Table 3-4 TCSR2 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Table 3-5 TMRLCR12 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Table 3-6 TMRLCR3 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Table 3-7 TMRLCR4 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Table 3-8 TMRCCR12 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Table 3-9 TMRCCR3 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Table 3-10 TMRCCR4 Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Table 3-11 WCSR Bit Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Table 3-12 Selecting Timeout Value of the WDT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Table 3-13 Register Definitions Offset from BAR0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Table A-1 V7768 VME Connector Pinout (P1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Table A-2 V7768 VME Connector Pinout (P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Table A-3 V7768 PCI-X PMC Site Connector Pinout (J11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Table A-4 V7768 PCI-X PMC Site Connector Pinout (J12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Table A-5 V7768 PCI-X PMC Site Connector Pinout (J13) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Table A-6 Mezzanine PCI-X PMC Site Connector Pinout (J14 ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Table A-7 V7769 Backplane Connector Pinouts (P1 and P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Table A-8 Mezzanine PMC Site Connector Pinout (J11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Table A-9 Mezzanine PCI-X PMC Site Connector Pinout (J12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Table A-10 Mezzanine PCI-X PMC Site Connector Pinout (J13 ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Table A-11 Mezzanine PMC Site Connector Pinout (J21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Table A-12 Mezzanine PCI-X PMC Site Connector Pinout (J22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

6 V7768/V7769 Hardware Reference Manual

Page 7

Table A-13 Mezzanine PCI-X PMC Site Connector Pinout (J23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Table A-14 Mezzanine PCI-X PMC Site Connector Pinout (J24) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Table A-15 USB Connector Pinout (J29 and J30) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Table A-16 Gigabit Ethernet Connector Pinout (J18) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Table A-17 SVGA Connector Pinout (J28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Table A-18 Serial Connector Pinout (J35) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Table A-19 Mouse/Keyboard Connector Pinout (J38) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Table A-20 Mouse/Keyboard Splitter Cable Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Table A-21 Mezzanine SAS Connector Pinout (J28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table B-1 AMI BIOS First Boot Menu. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table B-2 AMI BIOS Main Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

Table B-3 AMI BIOS Advanced Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

Table B-4 AMI BIOS PCI/PnP Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

Table B-5 AMI BIOS Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Table B-6 AMI BIOS Security Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

Table B-7 AMI BIOS Chipset Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Table B-8 AMI BIOS Exit Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

Table C-1 Enable the Front Panel LAN for Remote Booting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table C-2 Boot-from-LAN BIOS First Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

Table C-3 Boot-from-LAN BIOS Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

List of Tables 7

.

Page 8

Overview

GE’s V7768/V7769* are single board computers (SBCs) in a dual-slot, passively

cooled, VME Eurocard form factor.

®

The V7768* is a full featured Intel

the V7769* is a full featured Intel Core 2 Duo-based SBC. The V7768/V7769 utilize

the advanced technology of Intel’s 945GM chipset and the ICH7-M I/O Controller

Hub. The 945GM chipset runs on a 533 MHz front-side bus with the Celeron M

processor and a 667 MHz front-side bus with the Core 2 Duo processor.

The V7768/V7769 are compliant with the VMEbus Specification VITA 1-1994 and

feature a transparent PCI-to-VME bridge, allowing your board to function as a

system controller or peripheral CPU in multi-CPU systems.

The V7768 is a single-slot board, and the V7769 is a dual-slot board. The V7769

has the same functionality as the V7768 and also connects to the ACC-0623*

(which will be referred to as the mezzanine board throughout this manual),

making it a dual-slot board. Because the functionality is so similar, this manual

will refer to both boards (V7768/V7769) throughout unless the material is

referring to the V7768 or V7769 only.

CoreTM 2 Duo or Celeron® M-based SBC, and

8 V7768/V7769 Hardware Reference Manual

Page 9

Desktop Features of the V7768/V7769

• Up to 2.0 GByte DDR2 SDRAM (One SODIMM)

• SVGA port (front I/O)

• Dual Gigabit Ethernet (GbE) (front I/O)

• One RS232/422 COM port (front I/O)

• One RS232/422 COM support (rear I/O)

• Two USB 2.0 ports (front I/O)

• Four USB 2.0 support (rear I/O)

• Supports two SATA connections (rear I/O)

• One 2.5-in. SATA hard drive (optional for V7769 only)

• Dual SAS connector (front I/O on V7769 only)

• Real-Time clock/calendar

• Front panel reset switch

• PS/2 Keyboard/Mouse connection (front I/O)

• Onboard parallel connector

The 945GM chipset allows the V7768/V7769 to be capable of executing many of

today’s desktop operating systems such as Microsoft

®

Vista

V7768/V7769 are described in Chapter 2: Standard Features of this manual.

, Linux® 2.6.x, and VxWorks® 6.x. The standard desktop features of the

®

’s W in do w s® XP, Windows

Overview 9

Page 10

Embedded Features of the V7768/V7769

• Remote booting out the front panel only

• Up to 8 GByte of bootable CompactFlash (optional)

• PCI-X capable PMC site with VITA 35 P2 I/O (factory populated on V7768

and main board of V7769)

• VITA 1-1994 with byte swap

• 32 KByte NVRAM

• Software-selectable Watchdog Timer with reset

• PMC expansion site Chapter 3: Embedded PC/RTOS Features

The embedded features of the V7768/V7769 are described in Chapter 3 of this

manual.

The V7768/V7769 are suitable for use in a variety of applications, such as:

telecommunications, simulation, instrumentation, industrial control, process

control and monitoring, factory automation, automated test systems, data

acquisition systems and anywhere that the highest performance processing

power for VME in a single or dual slot is desired.

10 V7768/V7769 Hardware Reference Manual

Page 11

Intel 945GM Chipset

The V7768/V7769 incorporate the latest Intel chipset technology, the 945GM. The

Intel 945GM chipset is an optimized integrated graphics solution with up to a

667 MHz system bus. The chipset has a low power design, advanced power

management, supporting up to 2 GByte of DDR2 system memory. The 945GM is a

Memory Controller Hub (MCH) component, providing the processor interface,

system memory interface (DDR2 SDRAM) and SVGA port.

Key features for the 945GM:

• 533 MHz Processor system bus controller for the Celeron M

• 667 MHz Processor system bus controller for the Intel Core 2 Duo

• Up to 2 GByte DDR2 Memory via SODIMM

• High-speed DMI architecture interface for communication with the ICH7-M

The 945GM supports the Intel ICH7-M I/O controller hub. The ICH7-M supports

most of the high speed I/O interfaces of the V7768/V7769.

Key features for the ICH7-M:

• USB 2.0

(I/O controller)

• SATA

• IDE (Primary only)

• PCI

• PCI Express (PCIe)

Overview 11

Page 12

Figure 1 V7768 Block Diagram

Intel

Core 2 Duo

or

Celeron M

Processor

LEDs

Reset

USB

USB

SVGA

RJ45

RJ45

RJ45

Mouse/

Keyboard

DDR2

Memory

Up to 2 GByte

SODIMM

LAN1

LAN2

COM 1 (RS232/RS422)

DDR2

Intel 82571

Dual

Gigabit

Ethernet

Up to 8 GByte

CompactFlash

USB 2.0 x2

PCIe x1

FWH

PATA

667MHz

FSB

Intel

945GM

Express

DMI

x 4

Intel

82801GMB

I/O Controller

(ICH7-M)

L

P

C

Super I/O

P

C

I

33

M

H

z

32

b

i

t

PCIe x4

PCIe x8

P

C

I

33

M

H

z

32

b

i

t

Tundra

Universe IID

VME

FPGA

PEX8114

PCIe-PCIX

Bridge

PCIX

133MHz

64-bit

PCIX

PMC

Site

NVRAM

M

e

a

z

z

a

n

i

n

e

C

o

n

n

PMC I/O (VITA-35)

Byte Swap Logic

P1

VME

VME

P2

USB 2.0 x 4

SATA x 2

12 V7768/V7769 Hardware Reference Manual

COM2 (RS232/RS422)

Page 13

Figure 2 Illustration of V7768

Overview 13

Page 14

Figure 3 V7769 Block Diagram

SAS

Connector

2.5 in.SATA Drive

2 x SAS

SATA

SATA to IDE

Converter

SATA

LSI1064

SAS/SATA

Controller

PCIE x4

PEX8518

PCIE Switch

M

e

a

z

z

a

n

i

n

e

C

o

n

n

PCIE x8

PCI-X 64, 100

PCI-X

PMC

Site 1

P1

IDE

Up to 4 GByte

CompactFlash

14 V7768/V7769 Hardware Reference Manual

PCIE x4

PEX8114

PCIE-PCIX

Bridge

PCI-X

PMC

Site 2

P2

Vita 35

Page 15

Figure 4 Illustration of V7769

Overview 15

Page 16

Organization

This manual is composed of the following chapters and appendices:

Chapter 1 - Installation and Setup describes unpacking, inspection, hardware

jumper settings, connector definitions, installation, system setup and operation of

the V7768/V7769.

Chapter 2 - Standard Features describes the unit design in terms of the standard

PC memory and I/O maps, along with the standard interrupt architecture.

Chapter 3 - Embedded PC/RTOS Features describes the unit features that are

beyond standard functions.

Maintenance provides information relative to the care and maintenance of the

unit.

Appendix A - Connector Pinouts illustrates and defines the connectors included

in the unit’s I/O ports.

Appendix B - AMI BIOS Setup Utility describes the menus and options

.

associated with the American Megatrends, Inc

(system) BIOS.

Appendix C - Remote Booting describes the menus and selections necessary to

boot from the SBC remotely.

16 V7768/V7769 Hardware Reference Manual

Page 17

References

Intel Celeron M Processor on 65 nm Processor

January 2007, Order Number 312726-004

Intel Core 2 Duo Processor for Intel Centrino® Duo Processor Technology

Process Datasheet

September 2007, Revision 004, Order Number 314078-004

Mobile Intel 945 Express Chipset Family

November 2006, Order Number 309219-003

Intel I/O Controller Hub 7 (ICH 7) Family Datasheet

January 2006, Order Number 307013-002

Intel 82571EB/82572EI Gigabit Ethernet Controller Product Datasheet

December 2006, Revision 2.0

PCI Local Bus Specification, Rev. 2.2

PCI Special Interest Group

P.O. Box 14070

Portland, OR 97214

(800) 433-5177 (U.S.)

(503) 797-4207 (International)

(503) 234-6762 (FAX)

LPC47M107 100-Pin Enhanced Super I/O with LPC Interface for Consumer

Applications

Standard Microsystems Corp.

80 Askay Dr.

Hauppauge, NY 11788-8847

www.smsc.com

CMC Specification, 1386 from:

IEEE Standards Department

Copyrights and Permissions

445 Hoes Lanes, P.O. Box 1331

Piscataway, NJ 08855-1331

PMC Specification, 1386.1 from:

IEEE Standards Department

Copyrights and Permissions

445 Hoes Lanes, P.O. Box 1331

Piscataway, NJ 08855-1331, USA

Overview 17

Page 18

Safety Summary

The following general safety precautions must be observed during all phases of

the operation, service and repair of this product. Failure to comply with these

precautions or with specific warnings elsewhere in this manual violates safety

standards of design, manufacture and intended use of this product.

GE assumes no liability for the customer's failure to comply with these

requirements.

Ground the

System

Do Not Operate in

an Explosive

Atmosphere

Keep Away from

Live Circuits

Do Not Service or

Adjust Alone

Do Not Substitute

Parts or Modify

System

Dangerous

Procedure

Warnings

To minimize shock hazard, the chassis and system cabinet must be connected to

an electrical ground. A three-conductor AC power cable should be used. The

power cable must either be plugged into an approved three-contact electrical

outlet or used with a three-contact to two-contact adapter with the grounding

wire (green) firmly connected to an electrical ground (safety ground) at the power

outlet.

Do not operate the system in the presence of flammable gases or fumes. Operation

of any electrical system in such an environment constitutes a definite safety

hazard.

Operating personnel must not remove product covers. Component replacement

and internal adjustments must be made by qualified maintenance personnel. Do

not replace components with power cable connected. Under certain conditions,

dangerous voltages may exist even with the power cable removed. To avoid

injuries, always disconnect power and discharge circuits before touching them.

Do not attempt internal service or adjustment unless another person capable of

rendering first aid and resuscitation is present.

Because of the danger of introducing additional hazards, do not install substitute

parts or perform any unauthorized modification to the product. Return the

product to GE for service and repair to ensure that safety features are maintained.

Warnings, such as the example below, precede only potentially dangerous

procedures throughout this manual. Instructions contained in the warnings must

be followed.

WARNING

Dangerous voltages, capable of causing death, are present in this system.

Use extreme caution when handling, testing and adjusting.

18 V7768/V7769 Hardware Reference Manual

Page 19

Warnings,

Cautions

and Notes

STOP

Informs the operator that a practice or procedure should not be performed. Actions could result in

injury or death to personnel, or could result in damage to or destruction of part or all of the

system.

WARNING

WARNING denotes a hazard. It calls attention to a procedure, practice, or

condition, which, if not correctly performed or adhered to, could result in

injury or death to personnel.

CAUTION

CAUTION denotes a hazard. It calls attention to an operating procedure,

practice, or condition, which, if not correctly performed or adhered to, could

result in damage to or destruction of part or all of the system.

NOTE

NOTE denotes important information. It calls attention to a procedure, practice, or condition which

is essential to highlight.

TIP

Tip denotes a bit of expert information.

LINK

This is link text.

Overview 19

Page 20

1 • Installation and Setup

This chapter describes the hardware jumper settings, connector descriptions,

installation, system setup and operation of the V7768/V7769.

1.1 Unpacking Procedures

Any precautions found in the shipping container should be observed. All items

should be carefully unpacked and thoroughly inspected for damage that might

have occurred during shipment. The board(s) should be checked for broken

components, damaged printed circuit board(s), heat damage and other visible

contamination. All claims arising from shipping damage should be filed with the

carrier and a complete report sent to GE Customer Care along with a request for

advice concerning the disposition of the damaged item(s).

CAUTION

Some of the components assembled on GE products may be

sensitive to electrostatic discharge and damage may occur on

boards that are subjected to a high energy electrostatic field. When

the board is placed on a bench for configuring, etc., it is suggested

that conductive material be inserted under the board to provide a

conductive shunt. Unused boards should be stored in the same

protective boxes in which they were shipped.

1.2 Hardware Setup

The V7768/V7769 are factory populated with user-specified options as part of the

V7768/V7769 ordering information. Contact Sales for ordering information at

1-800-322-3616. For option upgrades or for any type of repairs, contact customer

care to receive a Return Material Authorization (RMA).

GE Customer Care is available at:

(1-800-433-2682), 1-780-401-7700.

Or, visit our website www.ge-ip.com.

The V7768/V7769 are tested for system operation and shipped with factoryinstalled header jumpers. The physical locations of the headers and connectors for

the SBC with the PMC option are illustrated in Figure 1-1 on page 21 and

Figure 1-1 on page 21. The definitions of the connectors, headers and switches are

included in Table 1-1 on page 22.

CAUTION

All jumpers marked User Configured in the following tables may be

changed or modified by the user. All jumpers marked Factory

Configured should not be modified by the user.

Care must be taken when making jumper modifications to ensure

against improper settings or connections. Improper settings may

result in damage to the unit.

Modifying any jumper not marked User Configured will void the

Warranty and may damage the unit.

20 V7768/V7769 Hardware Reference Manual

Page 21

1.2.1 V7768 Board Layout Information

Figure 1-1 V7768 Connector Locations

J11

J12

J30

J29

USB

USB

SVGA

J28

GbE

GbE

J33

J32

CompactFlash

P7

SODIMM

J34

P1

ON

1 2

S7

J13

J14

J37

(used for V7769 version)

1 2

ON

ON

1 2

S12

S8

E13

E14

13

5

1 2

1 2

E17

13

ON

1 2

S6

ON

S10

ON

S11

P2

M/K

COM1

J38

INDICATES PIN 1

J35

ON

1 2

S9

Installation and Setup 21

.

Page 22

Table 1-1 V7768 Connectors and Switches

Connector Function

P1 VME interface connector

P2 USB 2.0, Serial ATA, digital video, COM3 and COM4, Gigabit Ethernet

P7 CompactFlash socket

J34 SODIMM socket

J29 and J30 USB ports

J38 Mouse/Keyboard PS/2 Type connector

J15 and J18 Gigabit Ethernet connectors

J11, J12, J13 and J14 PMC Site connectors

J35 Serial port connector (COM1)

J28 SVGA connector

J37 Board to Board connector for V7769

Header Function

E13 COM1 Configuration

E14 COM1 Configuration

E17 COM1 (RS422 Termination)

Switches Function

S6 Mapping/Sysfail generation

S7 VME SYSRESET

S8 Factory Conf igurable

S9 Factory Conf igurable

S10 System Controller

S11 Battery enable

S12 RTC Reset and Boot Pause

Table 1-2 Universe IID Mapping/SYSFAIL Generation - Switch (S6)

Position State Function

1-4 On Enable SYSFAIL Generation

1-4 Off NO SYSFAIL after reset

2-3 On Map UNIV2 to Memory Space

2-3 Off Map UNIV2 to I/O Space

Table 1-3 VME Strapping - Switch (S7)

Position State Function

1-4 On Enable VME SYSRESET Driver

2-3 On Enable SYSRESET Receiver

22 V7768/V7769 Hardware Reference Manual

Page 23

CMOS Password

Table 1-4 VME System Controller - Switch (S10)

Position State Function

1-4 On Force VME controller based on 2-3 state

1-4 Off Enable auto system controller

2-3 On Force system controller (any slot)

2-3 Off Force non-system controller (any slot)

Table 1-5 Battery Enable - Switch (S11)

Position State Function

1-4 On Enable Battery

1-4 Off Disable Battery

2-3 On Factory Use Only

2-3 Off Factory Use Only

NOTE

The BIOS has the capability of password protecting casual access to

the unit’s CMOS setup screens. The CMOS Clear jumper allows the

user to clear the password in the case of a forgotten password.

Table 1-6 Password Clear/BIOS Boot Mode - Switch (S12)

Position State Function

1-4 Off Normal

1-4 On Clear CMOS/Password

2-3 On Boot with Post Errors

2-3 Off Boot Halt on Post Errors

NOTE

The default settings in the tables are in bold.

To clear the CMOS password:

1. Turn off power to the unit.

2. Move switch S12 position 1 to On.

3. Wait approximately 5 seconds.

4. Move switch S12 position 1 to Off.

5. Power up the unit.

When power is reapplied to the unit, the CMOS password will be cleared, and the

CMOS will be set to its defaults.

Installation and Setup 23

.

Page 24

Table 1-7 COM1 Configuration (RS232/RS422 Select) - Header (E13, E14, E17)

Select E13 Position E14 Position E17 Position

RS232 In 3-5, 4-6 Both Out

RS422 w/Termination Out 1-3, 2-4 1-2, 3-4

RS422 w/o Termination Out 1-3, 2-4 Both Out

Figure 1-2 COM1 Termination Headers (E13, E14, E17)

E13

5

E17

13

E14

13

RS232 RS422 w/Termination RS422 w/o Termination

E13

E14

13

5

E17

13

E13

E14

13

5

E17

13

24 V7768/V7769 Hardware Reference Manual

Page 25

1.2.2 Mezzanine Board Layout Information (V7769)

Figure 1-3 Mezzanine Board Connector Locations

J28

J27

P5

J11

J13

ON

1 2

ON

1 2

S1

S2

P1

E10

E9

J12

E6

J21

J23

J22

P2

J24

Installation and Setup 25

.

Page 26

Table 1-8 Mezzanine Connectors and Switches

Connector Function

P1 VME interface connector

P2 Vita 35 PCI-X PMC connector

P5 Board to Board connector

J11, J12, and J13 PCI-X PMC Site 1 connectors

J21, J22, J23 and J24 PCI-X PMC Site 2 connectors

J27 2.5 in. SATA drive connector

J28 SAS connector

Header Function

E6 SMBus debug header

E9 Not Used

E10 Not Used

Switches Function

S1 Reserved

S2 Enable/Disable JTAG

Table 1-9 Switch (S2) Settings

Position State Function

1-4 Off Disable JTAG

1-4 On Enable JTAG

2-3 Off Not Used

2-3 On Not Used

26 V7768/V7769 Hardware Reference Manual

Page 27

1.3 Installation

The V7768/V7769 conform to the VME physical specification for a 6U board. The

V7768/V7769 can be used for the system controller or as a peripheral board. It can

be plugged directly into any standard chassis accepting either type of board.

The following steps describe the GE-recommended method for installation and

powerup of the V7768/V7769:

1. If a PMC module is to be used, connect it to the V7768/V7769 prior to board

installation (as shown in Figure 1-4 on page 28). Refer to the Product Manual for the PMC module for configuration and setup.

NOTE

Air flow as measured at the output side of the heatsink is to be

greater than 450 LFM.

2. Insert the V7768/V7769 into a VME chassis system controller or peripheral

slot. While ensuring that the board is properly aligned and oriented in the

supporting board guides, slide the board smoothly forward against the mat

ing connector. Use the ejector handles to firmly seat the board.

3. All needed peripherals can be accessed from the front panel or the rear I/O.

Each connector is clearly labeled, and detailed pinouts are in

Connector Pinouts.

Appendix A:

-

4. Connect a keyboard and mouse if the system has not been previously configured.

5. The V7768 features an optional CompactFlash Disk resident on the board.

Refer to

6. If an external drive module is installed, the BIOS Setup program must be

used to configure the drive types. See

to properly configure the system.

7. If a drive module is present, install the operating system according to the

manufacturer’s instructions.

Chapter 3: Embedded PC/RTOS Features for setup details.

Appendix B: AMI BIOS Setup Utility

1.3.1 BIOS Setup

The V7768/V7769 has an onboard BIOS Setup program that controls many

configuration options. These options are saved in a special non-volatile, batterybacked memory chip and are collectively referred to as the board’s CMOS

Configuration. The CMOS configuration controls many details concerning the

behavior of the hardware from the moment power is applied.

Details of the V7768/V7769 BIOS setup program are included in

Appendix B: AMI BIOS Setup Utility.

Installation and Setup 27

.

Page 28

Figure 1-4 Installing the PMC Card on the V7768/V7769

28 V7768/V7769 Hardware Reference Manual

Page 29

Figure 1-5 Backside Mounting for the PMC Card

Back of V7768 SBC

(Solder Side)

Installation and Setup 29

.

Page 30

Figure 1-6 Installation of Mezzanine Board onto the Main Board

See Figure 4 on page 15 for the image of the fully installed V7769.

30 V7768/V7769 Hardware Reference Manual

Page 31

1.4 Front/Rear Panel Connectors

The V7768/V7769 provide front panel access for the PMC expansion site, an

optional Gigabit Ethernet port, one 10/100 RJ45 connector, one serial port, SVGA,

keyboard/mouse, the manual reset switch and the status LEDs. A drawing of the

V7768/V7769 front panels are shown in Figure 1-7 and Figure 1-8. The front panel

connectors and indicators are labeled as follows:

V7768 • USB Dual USB 2.0 Ports

• LAN1 10/100/1000 Mbit Ethernet connector for port 1

• LAN2 10/100/1000 Mbit Ethernet connector for port 2

• M/K Mouse/keyboard connector

• COM1 Serial Port

• RST Manual reset switch

• BPHT Status LEDs

• VGA Analog Video connector

• A L Activity and Link Status LEDs for rear GbE

V7769 • SATA Serial ATA Activity LED

• SAS1 SAS Lane 1

• SAS2 SAS Lane 2

• HB Heartbeat LED for SAS/SATA controller

The V7768/V7769 provide rear I/O support for the following: digital video, two

SATA ports, one Serial and four USB ports. The V7768/V7769 are compatible with

GE’s Rear Transition Modules ACC-0602RC and

ACC-0603RC.

The front panel connectors, including connector pinouts and orientation, for the

V7768/V7769 are defined in Appendix A: Connector Pinouts.

Installation and Setup 31

.

Page 32

1.5 Front Panel Layouts

Figure 1-7 V7768 Front Panel Layout

Status LEDs (from left to right)

Boot Done (B) Booting - Indicates BIOS

Boot is in progress. When

LED is Off, CPU has

finished POST and is ready

(Red LED).

PWR (P) Power - Indicates when

power is applied to the

board, (Green LED).

IDE (H) Activity Indicator - Flashes

when IDE activity is

occurring, (Yellow LED).

Sysfail (T) VME failure - Lights during

VME SYSFAIL condition,

(Red LED).

RST Switch

Reset Allows the system to be

reset from the front panel.

Activity

Link

Activity

Link

LAN1 and LAN2 LEDs

Activity Indicates the Ethernet is

active, (Yellow LED).

Link 10Base-T (LED Off)

100Base-TX (Yellow LED) or

1000Base-T (Green LED)

GP LED (User Configurable, general

purpose LEDs)

Controlled by accessing I/O port 0xA4B bits 7-4.

The LEDs are turned off by

setting the associated bit and

turned on by clearing the

associated bit.

Upper/Right LED - Bit 7

Upper/Left LED - Bit 6

Lower/Right LED - Bit 5

Lower/Left LED - Bit 4

32 V7768/V7769 Hardware Reference Manual

Page 33

Figure 1-8 Mezzanine Front Panel Layout (for V7769)

Status LEDs (from top to bottom)

A fault is being indicated when any of the

LEDs on the mezzanine board for the

V7769 are red.

SATA SerialATA Activity - LED will

flash to indicate activity on

the SATA drive,

(Green LED).

SAS1 SCSI Activity - LED will

flash to indicate activity on

the first SAS Lane,

(Green LED).

SAS2 SCSI Activity - LED will

flash to indicate activity on

the second SAS Lane,

(Green LED).

HB Heartbeat Activity - LED will

flash to indicate activity on

the secondary SCSI drive,

(Green LED).

Installation and Setup 33

.

Page 34

2 • Standard Features

The V7768/V7769 are single board computers loaded with either an Intel Core 2

Duo or Celeron M processor and compatible with modern industry standard

desktop systems. The V7768/V7769 therefore retain industry standard memory

and I/O maps along with a standard interrupt architecture. The integrated

peripherals described in this section (such as serial ports, USB ports,

CompactFlash drive, video controller and Ethernet controller) are all memory

mapped the same as similarly equipped desktop systems, ensuring compatibility

with modern operating systems.

The following sections describe the standard features of the V7768/V7769.

2.1 BGA CPU

The V7768 is factory populated with either an Intel Core 2 Duo or Celeron M

processor. The V7769 is factory populated with an Intel Core 2 Duo processor.

To change the memory size or CompactFlash size contact Customer Care to

receive a Return Material Authorization (RMA).

GE Customer Care is available at:

(1-800-433-2682), 1-780-401-7700.

Or, visit our website www.ge-ip.com.

2.2 Physical Memory

The V7768/V7769 provide DDR2 Synchronous DRAM (SDRAM) as system

memory. Memory can be accessed as bytes, words or longwords.

The SDRAM is accessible to the VME bus through the PCI-to-VME bridge and is

addressable by the local processor.

The V7768/V7769 have a maximum memory configuration of 2 GByte of DDR2

SDRAM memory. This configuration calls for a single 2 GByte SODIMM (one

200-pin SODIMM DDR2 module). The SDRAM is dual-ported to the VME

through the PCI-to-VME bridge and is addressable by the local processor, as well

as the VME slave interface by another VME master. Caution must be used when

sharing memory between the local processor and the VME to prevent a VME

deadlock and to prevent a VME master from overwriting the local processor ’s

operating system.

NOTE

When using the Configure utility of GE’s IOWorks Access to configure RAM, do not request more

than 25 percent of the physical RAM. Exceeding the 25 percent limit may result in known bugs that

causes unpredictable behavior during the boot sequence, and requires the use of an emergency

repair disk to restore the computer. It is recommended that an emergency repair disk be kept upto-date and easily accessible.

34 V7768/V7769 Hardware Reference Manual

Page 35

The V7768/V7769 include 32 KByte of non-volatile SRAM which can be accessed

by the CPU at any time, and is used to store system data that must not be lost

during power-off conditions.

NOTE

Memory capacity may be extended as parts become available.

2.3 Memory Map

Table 2-1 Memory Map

Mode Memory Address Range Size Description

Protected Mode $FFFF 0000 - $FFFF FFFF 64 KByte ROM BIOS Image

$C000 0000 - $FFFE FFFF 0.9 GByte Unused*

$0010 0000 - $BFFF FFFF 3 GByte Reserved for **

Real Mode $E0000 - $FFFFF 128 KByte

$C0000 - $DFFFF 128 KByte

$A0000 - $BFFFF 128 KByte

$00000 - $9FFFF 640 KByte

* This space can be used to set up protected mode PCI-to-VME windows (also referred to as PCI slave images). BIOS will also

map onboard PCI based NVRAM, Timers and Watchdog Timers in this area.

** This space can be allocated as shared memory (for example, between the BGA CPU and VME Master). Note that if a PMC

board is loaded, the expansion BIOS may be placed in this area.

Onboard Extended Memory

(not filled on all systems)

2.4 I/O Port Map

Like a desktop system, the V7768/V7769 include special input/output instructions

that access I/O peripherals residing in I/O addressing space (separate and distinct

from memory addressing space). Locations in I/O address space are referred to as

ports. When the CPU decodes and executes an I/O instruction, it produces a 16-bit

I/O address on lines A00 to A15 and identifies the I/O cycle with the M/I/O control

line. Thus, the CPU includes an independent 64 KByte I/O address space, which is

accessible as bytes, words or longwords.

Standard hardware circuitry reserves only 1,024 byte of I/O addressing space

from I/O $000 to $3FF for peripherals. All standard PC I/O peripherals, such as

serial and parallel ports, hard and floppy drive controllers, video system, realtime clock, system timers and interrupt controllers are addressed in this region of

I/O space. The BIOS initializes and configures all these registers properly;

adjusting these I/O ports directly is not normally necessary.

Standard Features 35

Page 36

The assigned and user-available I/O addresses are summarized in the I/O Address

Map, Table 2-2.

Table 2-2 V7768/V7769 I/O Address Map

I/O Address Range

$000 - $00F 16 DMA Controller 1

$010 - $01F 16 Reserved

$020 - $021 2 Master Interrupt Controller

$022 - $03F 30 Reserved

$040 - $043 4 Programmable Timer

$044 - $05F 30 Reserved

$060 - $064 5 Keyboard, Speaker, System Configuration

$065 - $06F 11 Reserved

$070 - $071 2 Real-Time Clock

$072 - $07F 14 Reserved

$080 - $08F 16 DMA Page Registers

$090 - $091 2 Reserved

$092 1 Alt. Gate A20/Fast Reset Register

$093 - $09F 11 Reserved

$0A0 - $0A1 2 Slave Interrupt Controller

$0A2 - $0BF 30 Reserved

$0C0 - $0DF 32 DMA Controller 2

$0E0 - $16F 142 Reserved

$170 - $177 8 ICH7-M Secondary Hard Disk Controller

$178 - $1EF 120 User I/O

$1F0 - $1F7 8 ICH7-M Primary Hard Disk Controller

$1F8 - $277 128 User I/O

$278 - $27F 8 I/O Chip Reserved

$280 - $2E7 104 Reserved

$2E8 - $2EE 7 UART* COM4 Serial I/O*

$2EF - $2F7 9 User I/O

$2F8 - $2FE 7 Super I/O Chip COM2 Serial I/O (16550 Compatible)

$2FF - $36F 113 Reserved

$370 - $377 8 Super I/O Chip* Secondary Floppy Disk Controller*

$378 - $37F 8 Super I/O Chip Reserved

$380 - $3E7 108 Reserved

$3E8 - $3EE 7 UART* COM3 Serial I/O*

$3F0 - $3F7 8 Super I/O Chip* Primary Floppy Disk Controller*

$3F8 - $3FE 7 Super I/O Chip COM1 Serial I/O (16550 Compatible)

$3FF - $4FF 256 Reserved

$500 - $CFF 2048 Reserved

*While these I/O ports are reserved for the listed functions, they are not implemented on the V7768/

V7769. They are listed here to make the user aware of the standard PC usage of these ports.

Size in

Bytes

HW Device PC/AT Function

36 V7768/V7769 Hardware Reference Manual

Page 37

2.5 Interrupts

2.5.1 Legacy PIC System Interrupts

In addition to an I/O port address, an I/O device has a separate hardware

interrupt line assignment. Assigned to each interrupt line is a corresponding

interrupt vector in the 256-vector interrupt table at $00000 to $003FF in memory.

The 16 maskable interrupts and the single Non-Maskable Interrupt (NMI) are

listed in Table 2-3 along with their functions. Table 2-4 on page 38 details the

vectors in the interrupt vector table. The interrupt number in HEX and decimal

are also defined for real and protected mode in Table 2-4 on page 38.

The interrupt hardware implementation on the V7768/V7769 is standard for

computers built around the PC architecture, which evolved from the IBM PC/XT.

In the IBM PC/XT computers, only eight interrupt request lines exist, numbered

from IRQ0 to IRQ7 at the Programmable Interrupt Controller (PIC). The IBM PC/

AT computer added eight more IRQx lines, numbered IRQ8 to IRQ15, by

cascading a second slave PIC into the original master PIC. IRQ2 at the master PIC

was committed as the cascade input from the slave PIC. This architecture is

represented in Figure 2-1 on page 42.

To maintain backward compatibility with PC/XT systems, IBM chose to use the

new IRQ9 input on the slave PIC to operate as the old IRQ2 interrupt line on the

PC/XT Expansion Bus. Thus, in AT systems, the IRQ9 interrupt line connects to

the old IRQ2 pin (pin B4) on the AT Expansion Bus (or ISA bus).

Table 2-3 Interrupt Line Assignments

IRQ AT Function Comments

NMI Parity Errors

(Must be enabled in BIOS Setup)

0 System Timer Set by BIOS Setup

1 Keyboard Set by BIOS Setup

2Duplexed to IRQ9

3COM2

4COM1

5Unused

6 Floppy Controller

7Unused

8Real-Time Clock

9 Old IRQ2 SVGA or Network I/O

10 Not Assigned Determined by BIOS

11 Not Assigned Determined by BIOS

12 Mouse

13 Math Coprocessor

14 AT Hard Drive

15 Flash Drive

Used by V7768/V7769 PCI bus Interface

Standard Features 37

Page 38

Table 2-4 Interrupt Vector Table

Interrupt No.

HEX DEC

00 0 Divide Error Same as Real Mode

01 1 Debug Single Step Same as Real Mode

02 2 NMI Memory Parity Error,

03 3 Debug Breakpoint Same as Real Mode

04 4 ALU Overflow Same as Real Mode

05 5 Print Screen Array Bounds Check

06 6 Invalid OpCode

07 7 Device Not Available

08 8 IRQ0 Timer Tick Double Exception Detected

09 9 IRQ1 Keyboard Input Coprocessor Segment Overrun

0A 10 IRQ2 BIOS Reserved Invalid Task State Segment

0B 11 IRQ3 COM2 Serial I/O Segment Not Present

0C 12 IRQ4 COM1 Serial I/O Stack Segment Overrun

0D 13 IRQ5 Unassigned Not Assigned

0E 14 IRQ6 Floppy Disk Controller Page Fault

0F 15 IRQ7 Not Assigned Not Assigned

10 16 BIOS Video I/O Coprocessor Error

11 17 System Configuration Check Same as Real Mode

12 18 Memory Size Check Same as Real Mode

13 19 XT Floppy/Hard Drive Same as Real Mode

14 20 BIOS Comm I/O Same as Real Mode

15 21 BIOS Cassette Tape I/O Same as Real Mode

16 22 BIOS Keyboard I/O Same as Real Mode

17 23 BIOS Printer I/O Same as Real Mode

18 24 ROM BASIC Entry Point Same as Real Mode

19 25 Bootstrap Loader Same as Real Mode

1A 26 Time of Day Same as Real Mode

1B 27 Control/Break Handler Same as Real Mode

1C 28 Timer Control Same as Real Mode

1D 29 Video Parameter Table Pntr Same as Real Mode

1E 30 Floppy Parm Table Pntr Same as Real Mode

1F 31 Video Graphics Table Pntr Same as Real Mode

20 32 DOS Terminate Program Same as Real Mode

21 33 DOS Function Entry Point Same as Real Mode

22 34 DOS Terminate Handler Same as Real Mode

23 35 DOS Control/Break Handler Same as Real Mode

24 36 DOS Critical Error Handler Same as Real Mode

25 37 DOS Absolute Disk Read Same as Real Mode

26 38 DOS Absolute Disk Write Same as Real Mode

27 39 DOS Program Terminate,

28 40 DOS Keyboard Idle Loop Same as Real Mode

IRQ Line Real Mode Protected Mode

VME Interrupts

Stay Resident

Same as Real Mode

(Must be enabled in BIOS Setup)

Same as Real Mode

38 V7768/V7769 Hardware Reference Manual

Page 39

Table 2-4 Interrupt Vector Table (Continued)

Interrupt No.

HEX DEC

29 41 DOS CON Dev. Raw Output Same as Real Mode

2A 42 DOS 3.x+ Network Comm Same as Real Mode

2B 43 DOS Internal Use Same as Real Mode

2C 44 DOS Internal Use Same as Real Mode

2D 45 DOS Internal Use Same as Real Mode

2E 46 DOS Internal Use Same as Real Mode

2F 47 DOS Print Spooler Driver Same as Real Mode

30-60 48-96 Reserved by DOS Same as Real Mode

61-66 97-102 User Available Same as Real Mode

67-6F 103-111 Reserved by DOS Same as Real Mode

70 112 IRQ8 Real-Time Clock

71 113 IRQ9 Redirect to IRQ2

72 114 IRQ10 Not Assigned

73 115 IRQ11 Not Assigned

74 116 IRQ12 Mouse

75 117 IRQ13 Math Coprocessor

76 118 IRQ14 AT Hard Drive

77 119 IRQ15 Flash Drive

78-7F 120-127 Reserved by DOS Same as Real Mode

80-F0 128-240 Reserved for BASIC Same as Real Mode

F1-FF 241-255 Reserved by DOS Same as Real Mode

IRQ Line Real Mode Protected Mode

Standard Features 39

Page 40

2.5.2 PCI Interrupts

The PMC PCI-X sites of the V7769 connect Standard PCI Interrupt Lines to the

PCI-E to PCI-X bridge as shown in Figure 2-1 on page 42. The PCI-E bridge (PLX

PEX8114) converts the PCI INTx interrupts into virtual PCI Express interrupts

that are signaled back to the chipset over the PCI Express Interface.

Interrupts on Peripheral Component Interconnect (PCI) Local Bus are defined as

“level sensitive,” asserted low (negative true), using open drain output drivers.

The assertion and de-assertion of an interrupt line, INTx#, is asynchronous. A

device asserts its INTx# line when requesting attention from its device driver.

Once the INTx# signal is asserted, it remains asserted until the device driver clears

the pending request. When the request is cleared, the device de-asserts its INTx#

signal.

PCI defines one interrupt line for a single function device and up to four interrupt

lines for a multifunction device or connector. For a single function device, only

INTA# may be used while the other three interrupt lines have no meaning.

Figure 2-1 on page 42 depicts the V7768/V7769 interrupt logic pertaining to FPGA

timer operations and the PCI expansion site.

Any function on a multifunction device can be connected to any of the INTx#

lines. The Interrupt Pin register defines which INTx# line the function uses to

request an interrupt. If a device implements a single INTx# line, it is called INTA#;

if it implements two lines, they are called INTA# and INTB#; and so forth. For a

multifunction device, all functions may use the same INTx# line, or each may

have its own (up to a maximum of four functions), or any combination thereof. A

single function can never generate an interrupt request on more than one INTx#

line.

The PIC accepts the PCI interrupts through lines that are defined by the BIOS.

40 V7768/V7769 Hardware Reference Manual

Page 41

PCI Device

Interrupt Map

The PCI bus-based external devices include the PMC sites, Ethernet controller

and the PCI-to-VME bridge. The default BIOS maps these external devices to the

PCI Interrupt Request (PIRQx) lines of the ICH. This mapping is illustrated in

Figure 2-1 on page 42 and is defined in Table 2-5.

Table 2-5 PCI Device Interrupt Mapping by the BIOS

Device Component Vendor ID Device ID ID Select PCI IRQ

PCI-to-VME Bridge Tundra Universe IID 0x10E3 0x0000 AD27 INTD REQ1

Timer/SRAM FPGA GE Proprietary 0x114A 0x0004 AD26 INTC N/A

PMC N/A N/A N/A AD24 INTA, B, C, D REQ0

Ethernet Controller Intel 82571EB 0x8086 0x105E N/A N/A N/A

PCI Host Bridge GMCH 0x8086 0x27A0 N/A N/A N/A

VGA Controller GMCH 0x8086 0x27A2 N/A N/A N/A

Integrated Graphics GMCH 0x8086 0x27A6 N/A N/A N/A

PCI-LPC Bridge ICH7-M 0x8086 0x27BD N/A N/A N/A

USB UHCI Controller ICH7-M 0x8086 0x27C8

USB EHCI ICH7-M 0x8086 0x27CC N/A N/A N/A

SMBus Controller ICH7-M 0x8086 0x27DA N/A N/A N/A

PCI-E Controller ICH7-M 0x8086 0x27D0 N/A N/A N/A

PCI-E Controller ICH7-M 0x8086 0x27E0 N/A N/A N/A

DMI-PCI Bridge ICH7-M 0x8086 0x2448 N/A N/A N/A

PCI-E Switch* PLX 8518 0x10B5 0x8518 N/A N/A N/A

PCI-E to PCI-X

Bridge*

LSI SAS Controller* LSI1064E 0x1000 0x0056 AD16 N/A N/A

PCI-E Graphics Port GMCH 0x8086 27A1 N/A N/A N/A

SATA Controller ICH7-M 0x8086 27C4 N/A N/A N/A

* Only available on V7769.

PLX 8114 0x10B5 0x8114 N/A N/A N/A

0x27C9

0x27CA

0x27CB

N/A N/A N/A

Arbitration

Request Line

Standard Features 41

Page 42

Figure 2-1 Connections for the PC Interrupt Logic Controller

I/O CONTROLLER

HUB ICH7-M

PMC237

PIC Master/Slave

IRQ0 - IRQ15

MAPPED BY BIOS

CONNECTIONS

MAPPED BY BIOS

PCI INTERRUPT

MAPPER PIRQA - PIRQH

Timers/NVRAM

FPGA

Universe IID

PCI-E

PCI-E

Front Panel

82571

Ethernet

PCI-E to PCI-X

PCI-X

PMC

PCI-X

INTA - INTD

2.6 Integrated Peripherals

The V7768/V7769 incorporate an SMSC Super I/O (SIO) chip. The SIO provides

the V7768/V7769 with two 16550 UART-compatible serial ports, keyboard and

mouse ports, and general purpose I/O for system functions, available via the VME

backplane connectors.

The SATA interface is provided by the Intel I/O Controller Hub chip (ICH7-M). It

is routed out of the VME backplane P2 connector. The SATA interface supports

two channels known as the primary and secondary channels.

Selection of drive type, along with detailed SATA selections, are available in the

CMOS Advanced BIOS Setup Menu.

42 V7768/V7769 Hardware Reference Manual

Page 43

2.7 Ethernet Controller

The network capability is provided by the Intel 82571 Dual Ethernet Controller for

Gigabit Ethernet. This Ethernet controller is PCI-E bus based and is software

configurable. The V7768/V7769 support 10Base-T, 100Base-TX and 1000Base-T

Ethernet.

10Base-T A network based on the 10Base-T standard uses unshielded twisted-pair cables,

providing an economical solution to networking by allowing the use of existing

telephone wiring and connectors. The RJ45 connector is used with the 10Base-T

standard. 10Base-T has a maximum length of 100 meters.

100Base-TX The V7768/V7769 also support the 100Base-TX Ethernet. A network based on a

100Base-TX standard uses unshielded twisted-pair cables. 100Base-TX has a

maximum length of 100 meters.

1000Base-T The V7768/V7769 support 1000Base-T Ethernet using the Intel 82571 dual

Ethernet controller. The interface uses shielded cables with four pairs of

conductors, along with an RJ45 connector on the front panel.

NOTE

Ethernet activity is noted on the front panel LEDs by a blinking

yellow LED. The yellow LED will be on continuously when the

Ethernet port is linked but with no activity.

Standard Features 43

Page 44

2.8 Video Graphics Adapter

The SVGA port on the V7768/V7769 is controlled by the Intel 945GM Graphic and

Memory Controller Hub (GMCH). The GMCH is hardware and BIOS compatible

with the industry SVGA and digital video standards supporting both VESA highresolution and extended video modes. Table 2-6 shows the graphics video modes

supported by the GMCH video controller for analog monitors.

Table 2-6 Supported Graphics Video Resolutions for Windows XP (Analog)

Screen Resolution Maximum Colors Maximum Refresh Rates (Hz)

640 x 480 High and True are supported at all

800 x 600 85

1024 x 768 85

1080 x 1280 75

1600 x 1200 60

Not all SVGA monitors support resolutions and refresh rates beyond 640 x 480 at

85 Hz. Do not attempt to drive a monitor to a resolution or refresh rate beyond its

capability.

resolutions.

85

44 V7768/V7769 Hardware Reference Manual

Page 45

3 • Embedded PC/RTOS Features

GE’s V7768/V7769 feature additional capabilities beyond those of a typical

desktop computer system. The units provide four software-controlled, generalpurpose timers along with a programmable Watchdog Timer for synchronizing

and controlling multiple events in embedded applications. The V7768 provides a

bootable CompactFlash Disk system and 32 KByte of non-volatile RAM. Also, the

V7768/V7769 support an embedded intelligent VME bridge to allow compatibility