Page 1

Artisan Technology Group is your source for quality

new and certied-used/pre-owned equipment

• FAST SHIPPING AND

DELIVERY

• TENS OF THOUSANDS OF

IN-STOCK ITEMS

• EQUIPMENT DEMOS

• HUNDREDS OF

MANUFACTURERS

SUPPORTED

• LEASING/MONTHLY

RENTALS

• ITAR CERTIFIED

SECURE ASSET SOLUTIONS

SERVICE CENTER REPAIRS

Experienced engineers and technicians on staff

at our full-service, in-house repair center

Instra

Remotely inspect equipment before purchasing with

our interactive website at www.instraview.com

Contact us: (888) 88-SOURCE | sales@artisantg.com | www.artisantg.com

SM

REMOTE INSPECTION

View

WE BUY USED EQUIPMENT

Sell your excess, underutilized, and idle used equipment

We also offer credit for buy-backs and trade-ins

www.artisantg.com/WeBuyEquipment

LOOKING FOR MORE INFORMATION?

Visit us on the web at www.artisantg.com for more

information on price quotations, drivers, technical

specications, manuals, and documentation

Page 2

GE

Intelligent Platforms

Hardware Reference

C2K* 6U CPCI

Single Board Computer

Publication No: 70000524-800 Rev. C

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 3

Document History

Hardware Reference Document Number: 70000524-800 Rev. C

September 30, 2011

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 4

Chapter 1: Introduction

1.1 Overview .......................................................................................................................... 1-1

1.2 Specifications ................................................................................................................... 1-3

1.3 Compliance ...................................................................................................................... 1-4

1.4 C2K GPIO DC Electrical Characteristics ......................................................................... 1-4

1.5 Block Diagram ................................................................................................................. 1-5

1.6 Technical Support ............................................................................................................ 1-7

1.7 Related Documents ......................................................................................................... 1-7

Chapter 2: Installation

2.1 What Is Included .............................................................................................................. 2-1

2.2 Equipment Needed .......................................................................................................... 2-1

2.3 Power Requirements ....................................................................................................... 2-2

2.4 Configurations Jumpers ................................................................................................... 2-2

2.4.1 FLASH_WP# (P6) ................................................................................................ 2-2

2.4.2 EM_BOOTSEL# (P7) ........................................................................................... 2-2

2.4.3 PCI VIO Select (P9, P12) ..................................................................................... 2-2

2.4.4 COP_EN (P10) .................................................................................................... 2-3

2.4.5 C8051 Debug (P11) ............................................................................................. 2-3

2.4.6 Header/Jumper Locations .................................................................................... 2-3

2.5 Installation ........................................................................................................................ 2-3

2.5.1 C2K C-style Installation ........................................................................................ 2-3

2.5.2 C2K N-style Installation ........................................................................................ 2-4

2.6 U-Boot Utility .................................................................................................................... 2-7

2.6.1 Installation ............................................................................................................ 2-7

2.6.2 Initialization .......................................................................................................... 2-7

2.6.3 Commands ........................................................................................................... 2-7

2.6.4 Information Commands ........................................................................................ 2-9

2.6.5 Memory Commands ........................................................................................... 2-10

2.6.6 Flash Memory Commands ................................................................................. 2-11

2.6.7 Execution Control Commands ........................................................................... 2-12

2.6.8 Download Commands ........................................................................................ 2-12

2.6.9 Environment Variables Commands ................................................................... 2-13

2.6.10 Miscellaneous Commands ................................................................................. 2-14

Table of Contents

C2K User’s Guide 3

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 5

Chapter 3: Interfaces

3.1 Front Panel ...................................................................................................................... 3-1

3.2 Connectors ....................................................................................................................... 3-2

3.2.1 Connector Locations ............................................................................................ 3-2

3.2.2 CompactPCI Connector Pin Assignments ........................................................... 3-4

3.2.3 PMC Connector Pin Assignments ...................................................................... 3-10

3.2.4 COP Port (J6) Pin Assignments ......................................................................... 3-14

3.2.5 JTAG Port (J7) Pin Assignments ....................................................................... 3-14

3.2.6 Front-panel USB (USB4) Connector (J8) Pin Assignments ............................... 3-15

3.2.7 Serial I/O COM Port Termination Header (P15) Pin Assignments ..................... 3-15

3.3 Front-panel LEDs ........................................................................................................... 3-16

Chapter 4: Functional Blocks

4.1 Processor ......................................................................................................................... 4-1

4.2 DDR SDRAM ...................................................................................................................4-1

4.3 Flash Memory .................................................................................................................. 4-1

4.3.1 Flash Write Protection .......................................................................................... 4-1

4.3.2 Boot Code Selection ............................................................................................ 4-3

4.4 PCI Busses ...................................................................................................................... 4-3

4.5 Device Bus ....................................................................................................................... 4-4

4.6 SMBus ............................................................................................................................. 4-4

4.7 Gigabit Ethernet ............................................................................................................... 4-4

4.8 Serial I/O .......................................................................................................................... 4-5

4.8.1 Serial RS-232/422 Ports—COM1, COM2 ............................................................ 4-5

4.8.2 Serial RS-232/422 Ports—COM3, COM4 ............................................................ 4-5

4.8.3 Serial RS-422/485 Ports—COM5–COM8 ............................................................ 4-5

4.9 USB Ports ........................................................................................................................ 4-6

4.10 General-Purpose I/O ........................................................................................................4-6

4.11 Serial ATA I/O .................................................................................................................. 4-6

4.12 Counter/Timers ................................................................................................................ 4-7

4.12.1 Watchdog Timer ................................................................................................... 4-7

4.13 FPGA ............................................................................................................................... 4-8

4.13.1 System Management Interrupt ............................................................................. 4-8

4.14 RTC .................................................................................................................................. 4-9

4.15 CompactPCI Backplane Interface .................................................................................... 4-9

4.16 IPMI and Hot Swap ........................................................................................................ 4-11

4.16.1 Hot Swap Controller ........................................................................................... 4-11

4.16.2 CPLD ................................................................................................................. 4-11

4.16.3 PCI 6254 cPCI Bus Bridge ................................................................................. 4-11

4.16.4 C8051 Microcontroller ........................................................................................ 4-11

4.17 PMC Sites ...................................................................................................................... 4-14

4.17.1 PMC0 Site Features ........................................................................................... 4-14

4.17.2 PMC1 Site Features ........................................................................................... 4-15

4.18 Temperature Sensor ...................................................................................................... 4-15

4.19 Interrupt Circuitry ........................................................................................................... 4-15

4.20 EEPROMS ..................................................................................................................... 4-16

4 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 6

4.21 JTAG Boundary Scan Circuitry ...................................................................................... 4-17

4.21.1 Configuration Headers ....................................................................................... 4-17

Chapter 5: Resources

5.1 Memory and I/O Address Mapping .................................................................................. 5-1

5.1.1 PCI Buses ............................................................................................................ 5-1

5.1.2 SMBus ................................................................................................................. 5-2

5.1.3 Device Bus ........................................................................................................... 5-2

5.1.4 Multi-Purpose Pins (MPP) .................................................................................... 5-3

5.2 FPGA Registers ............................................................................................................... 5-4

5.2.1 Main Registers ..................................................................................................... 5-7

5.2.2 Interrupt Registers ............................................................................................. 5-11

5.2.3 GPIO Registers .................................................................................................. 5-16

5.2.4 Counter/timers ................................................................................................... 5-37

5.2.5 USART Registers ............................................................................................... 5-45

5.2.6 Standard USART Registers ............................................................................... 5-46

5.2.7 USART Divisor Latch Registers ......................................................................... 5-53

5.3 Component Locations .................................................................................................... 5-54

Chapter 6: Transition Module C2K-TM

6.1 Overview .......................................................................................................................... 6-1

6.2 Physical Description ......................................................................................................... 6-2

6.3 Block Diagram .................................................................................................................. 6-3

6.4 Connector Pin Assignments ............................................................................................. 6-4

6.4.1 CompactPCI Connectors ..................................................................................... 6-4

6.4.2 Ethernet Connectors (J6, J7, and J8) .................................................................. 6-7

6.4.3 Serial ATA Connectors (P19, P20) ...................................................................... 6-7

6.4.4 USB Connectors (J9, J10, and J11) .................................................................... 6-8

6.4.5 Serial RS-232 Connectors—COM1, COM2 (P15, P16) ....................................... 6-8

6.4.6 Serial RS-422/485—COM1–COM8 (P1–P8) ....................................................... 6-9

6.4.7 Serial RS-232—COM3, COM4 (P9, P10) ............................................................ 6-9

6.4.8 BATT+ Header (P13) ........................................................................................... 6-9

6.4.9 ICMB Interface Header (P17) ............................................................................ 6-10

6.4.10 GPIO Connector (P14) ....................................................................................... 6-10

6.4.11 Misc. Connector (P18) ....................................................................................... 6-11

6.4.12 PMC I/O Connectors (P11 and P12) .................................................................. 6-12

6.5 Connector Locations ...................................................................................................... 6-13

6.6 TM Schematics .............................................................................................................. 6-14

Index

C2K User’s Guide 5

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 7

List of Figures

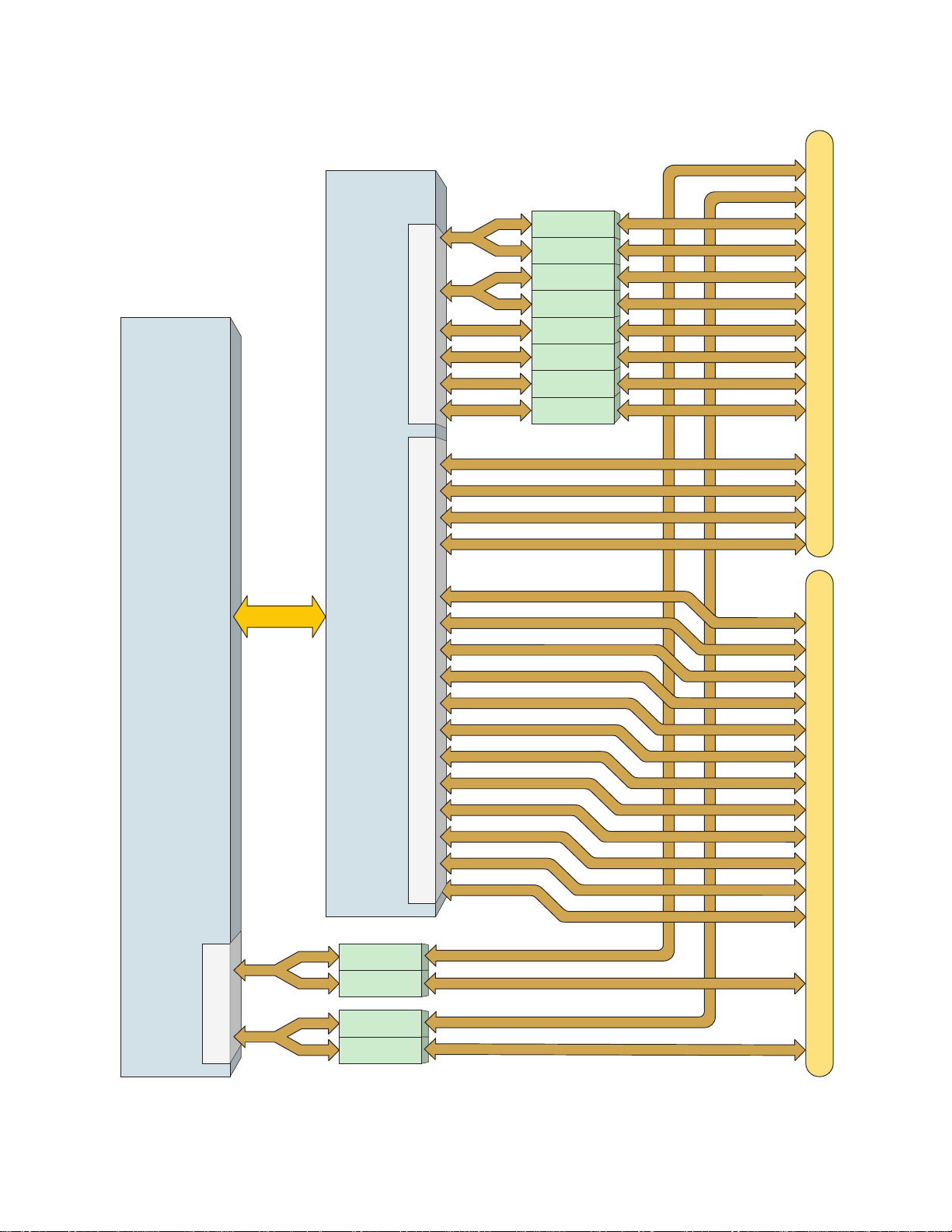

Figure 1-1 C2K Block diagram (a) ........................................................................................................ 1-5

Figure 1-2 C2K Block diagram (b) ........................................................................................................ 1-6

Figure 2-1 C2K (C-style) with PMC modules installed ......................................................................... 2-5

Figure 2-2 C2K (N-style) with PMC modules installed ......................................................................... 2-6

Figure 3-1 Front panels: a. C-style; b. N-style...................................................................................... 3-1

Figure 3-2 Connector locations (C-style).............................................................................................. 3-2

Figure 3-3 Connector locations (N-style).............................................................................................. 3-3

Figure 3-4 USB front-panel connector (J8) pinout.............................................................................. 3-15

Figure 3-5 Front-panel LEDs.............................................................................................................. 3-16

Figure 4-1 Watchdog timer circuitry...................................................................................................... 4-8

Figure 4-2 SMI processing ................................................................................................................... 4-9

Figure 4-3 Interrupt circuitry ............................................................................................................... 4-16

Figure 4-4 JTAG circuitry.................................................................................................................... 4-18

Figure 5-1 C2K component locations (primary side) .......................................................................... 5-54

Figure 5-2 C2K component locations (secondary side)...................................................................... 5-55

Figure 6-1 C2K-TM block diagram ....................................................................................................... 6-3

Figure 6-2 Ethernet RJ-45 connector pinout ........................................................................................ 6-7

Figure 6-3 SATA connector pinout ....................................................................................................... 6-7

Figure 6-4 USB connector pinout ......................................................................................................... 6-8

Figure 6-5 Serial RS-232 DB9 connector pinout .................................................................................. 6-8

Figure 6-6 C2K-TM connector locations............................................................................................. 6-13

C2K User’s Guide 6

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 8

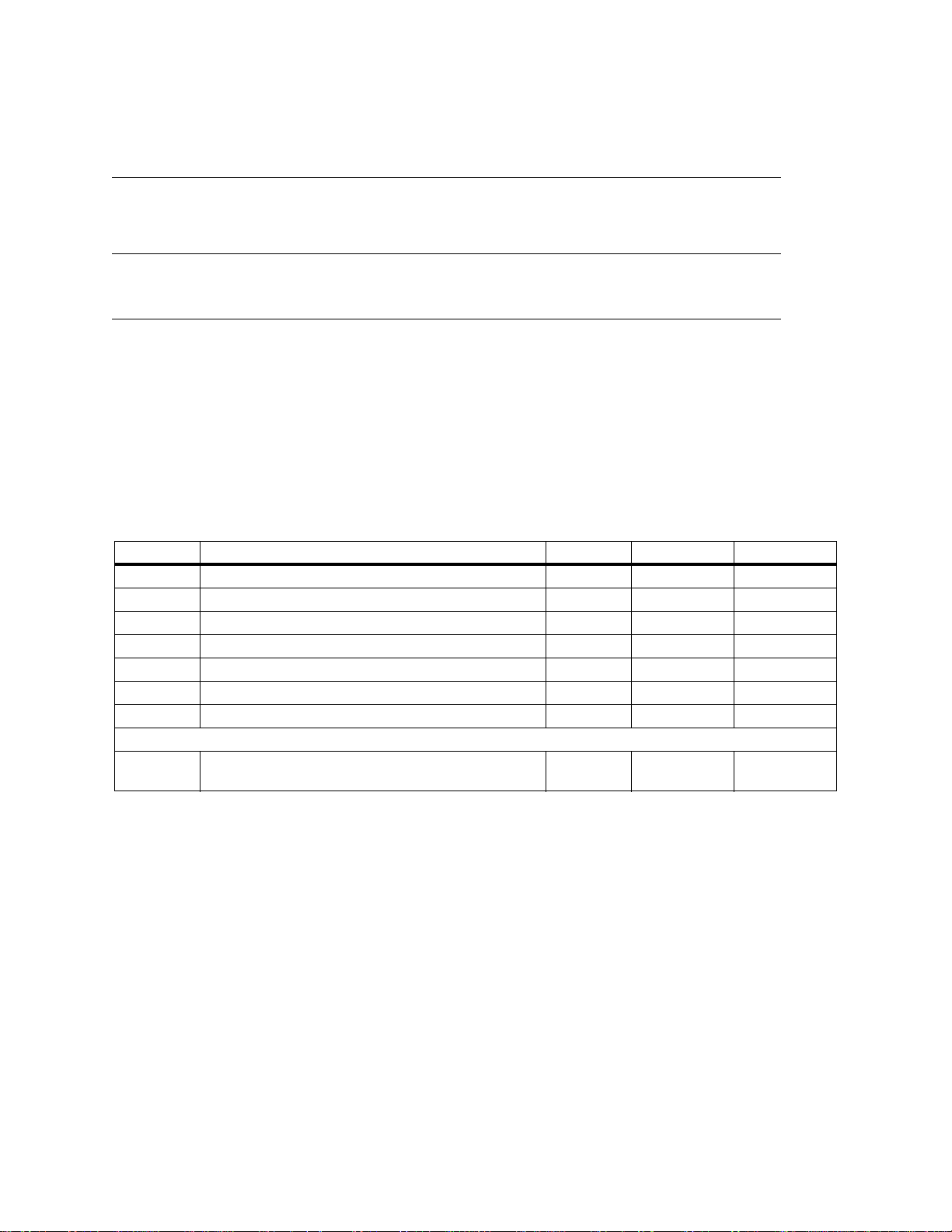

List of Tables

Table 1-1 C2K GPIO DC Electrical Characteristics..............................................................................1-4

Table 3-1 cPCI connector J1 pin assignments .....................................................................................3-4

Table 3-2 CompactPCI connector J2 pin assignments ........................................................................3-5

Table 3-3 CompactPCI connector J3 pin assignments ........................................................................3-6

Table 3-4 cPCI connector J4 pin assignments .....................................................................................3-7

Table 3-5 CompactPCI connector J5 pin assignments ........................................................................3-8

Table 3-6 PMC0_J11 and PMC0_J12 pin assignments..................................................................... 3-10

Table 3-7 PMC0_J13 and PMC0_J14 pin assignments..................................................................... 3-11

Table 3-8 PMC1_J21 and PMC1_J22 pin assignments..................................................................... 3-12

Table 3-9 PMC1_J23 and PMC1_J24 pin assignments..................................................................... 3-13

Table 3-10 COP Port (J20) pin assignments........................................................................................3-14

Table 3-11 JTAG Port (J7) pin assignments ........................................................................................3-14

Table 3-12 Front-panel Ethernet connector (J8) pin assignment .........................................................3-15

Table 3-13 Serial I/O COM port termination header (P15) pin assignments ........................................3-15

Table 4-1 Gigabit Ethernet on-board indicator LEDs. ..........................................................................4-4

Table 4-2 USB on-board indicator LEDs ..............................................................................................4-6

Table 4-3 SATA on-board activity indicator LEDs ................................................................................4-7

Table 4-4 C8051 external I/O ports pin assignments ......................................................................... 4-12

Table 4-5 I/O controller pin assignments............................................................................................4-13

Table 5-1 PCI local bus configuration ..................................................................................................5-1

Table 5-2 SMBus addressing ...............................................................................................................5-2

Table 5-3 Device bus devices, access, size and default address range ..............................................5-2

Table 5-4 MV64460 System Controller MPP pin assignments ............................................................5-3

Table 5-5 FPGA memory map - 16-bit Chip Select..............................................................................5-4

Table 5-6 FPGA memory map - 8-bit Chip Select................................................................................5-7

Table 5-7 Main registers.......................................................................................................................5-7

Table 5-8 Interrupt summary registers ...............................................................................................5-11

Table 5-9 GPIO registers ...................................................................................................................5-16

Table 5-10 Counter/timer registers.......................................................................................................5-37

C2K User’s Guide 7

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 9

Table 5-11 USART Resister .................................................................................................................5-45

Table 5-12 Standard 16550-compatible USART registers ...................................................................5-46

Table 5-13 Baud-rate divisor settings ...................................................................................................5-53

Table 6-1 CompactPCI connector J3 pin assignments ........................................................................6-4

Table 6-2 cPCI connector J4 pin assignments .....................................................................................6-5

Table 6-3 CompactPCI connector J5 pin assignments ........................................................................6-6

Table 6-4 Ethernet RJ-45 rear-panel connectors (J6, J7, J8) pin assignments ...................................6-7

Table 6-5 Serial ATA connectors (P19, P20) pin assignments ............................................................6-7

Table 6-6 USB connectors (J9, J10, and J11) pin assignments...........................................................6-8

Table 6-7 COM1 (P15) and COM2 (P16) pin assignments ..................................................................6-8

Table 6-8 COM1 (P1) through COM8 (P8) pin assignments ................................................................6-9

Table 6-9 COM3 (P9) and COM4 (P10) pin assignments ....................................................................6-9

Table 6-10 BATT+ header (P13) pin assignment ...................................................................................6-9

Table 6-11 ICMB interface header (P17) pin assignment ....................................................................6-10

Table 6-12 GPIO on-board header (P2) pin assignments ....................................................................6-10

Table 6-13 JTAG header (P18) pin assignments .................................................................................6-11

Table 6-14 PMC0_P11 and PMC1_P12 pin assignments....................................................................6-12

C2K User’s Guide 8

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 10

Chapter 1: Introduction

1.1 Overview

The C2K* is a 6U PICMG 2.16 compatible Single Board Computer intended for both system controller and peripheral slot applications. The board provides a CPU core, PICMG 2.16 compatible

backplane interface, and several peripheral devices/interfaces. The CPU core circuitry consists of

a Freescale MPC7448 or MPC7447A CPU operating at up to 1.4GHz, the Marvell® MV64460

PCI controller, up to 1GB of 167MHz DDR system memory, up to 512MB of boot memory, and

general support logic. An expanded feature list is below.

• 6U PICMG 2.16 compatible Single Board Computer, with full hot-swap support per

PICMG 2.1.

• IPMI controller with IPMB0 serial interface, per PICMG 2.9. Peripheral and BMC functions.

• 500MHz to 1.4GHz MPC7448 CPU, or 500MHz to 1.0GHz MPC7447A CPU with

Marvell MV64460 PCI Controller.

• Up to two 512MB banks of 167MHz DDR SDRAM, with ECC.

• PLX PCI 6254 PCI-to-PCI Interface for CPCI backplane.

• Two selectable 115kbps RS-232 or 2Mbps source-synchronous RS-422 ports available to

the backplane connectors.

• Six additional 460kbps source-synchronous RS-422/485 ports available to the backplane

connectors.

• Two 10/100/1000T Ethernet ports available to the backplane connector J3, wired per

PICMG 2.16.

• One 10/100/1000T Ethernet port available to the backplane J4.

• One 64-bit, PCI 33/66MHz or PCI-X 133MHz PMC site, with selectable +3.3V/+5.0V

VIO.

• One 64-bit PCI 33/66MHz PMC site with selectable +3.3V/+5.0V VIO.

• One bank of 64MB to 512MB Boot FEPROM with protected area feature.

• Three USB2.0 ports to the backplane connectors.

• One USB2.0 port to the front panel, on convection models.

• Thermal probe to monitor CPU die temperature and board ambient temperature.

• Sixteen 32-bit general-purpose counter/timers.

• Real Time Clock

• Two 1.5Gbps SATA 1.0 ports to the backplane.

• N-style and C-style versions.

C2K User’s Guide 1-1

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 11

Introduction

C2K Transition Module

GEIP offers an optional C2K Transition Module (C2K-TM) with the following on-board and

rear-panel connections:

• BATT+ (P13)—on-board 2 x 5 connector

• ETH0 (J6)—rear-panel RJ-45 connector

• ETH1 (J7)—rear-panel RJ-45 connector

• ETH2 (J8)—rear-panel RJ-45 connector

• GPIO connector (P14)—on-board 2 x 10-pin header

• ICMB interface (P17)—on-board 2 x 5-pin header

• Misc. Control header (P18)—on-board 2 x 5-pin header

• PMC0 I/O (P11)—on-board 2 x 32-pin header

• PMC1 I/O (P12)—on-board 2 x 32-pin header

• Reset switch, (S1)—rear-panel manual hardware reset micro-switch

• SATA1 (P19)—rear-panel connector

• SATA2 (P20)—rear-panel connector

• Serial I/O: COM1, COM2 RS-232 (P15, P16)—rear-panel DB9 connectors

• Serial I/O: COM3, COM4 RS-232 (P10, P9)—on-board 2 x 5-pin headers

• Serial I/O: COM1–COM4 RS-422 (P1–P4)—on-board 2 x 5-pin headers

• Serial I/O: COM5–COM8 RS-485 (P5–P8)—on-board 2 x 5-pin headers

• USB1 (J9)—rear-panel Type A USB connector

• USB2 (J10)—rear-panel Type A USB connector

• USB3 (J11)—rear-panel Type A USB connector

1-2 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 12

1.2 Specifications

Physical Description

Form Factor: 6U per PICMG 2.16

Height: 233.20 ± 0.15 mm (9.1811 ± 0.0059 in.)

Depth: 159.85 ± 0.15 mm (6.2933 ± 0.0059 in.)

Weight

C-style:

N-style:

Power Requirements

+5V, +3.3V, +12V: Required from the cPCI backplane

±12V: As required by installed PMC modules

TBD

TBD

NOTE: The +12V requires 10mA for the Hot Swap circuitry which is

otherwise not used by the board.

Introduction

Power Consumption

Peak: 5.7A 4.10A

Idle: TBD TBD

Inrush: 2.0A @ 120µs 2.0A @ 120µs

BATT+: 10µA

Total: 42W

* Measured at VxWorks® prompt

+5V +3.3V

Temperature (operating)

C-style: 0° C to 70° C (ambient)

N-style: -40° C to 85° C

Temperature (storage)

C-style: -40° C to 85° C

N-style: -55° C to 105° C

Relative Humidity - @ 40° C (non-condensing)

C-style: 5–95% @ 40° C

N-style: 5–95% @ 40° C

Shock (half-sine)

C-style: 20g peak / 6ms (3 axes, up & down, 3 hits / direction)

N-style: 40g peak / 11ms (3 axes, up & down, 3 hits / direction),

100g peak / 6ms (3 axes, up & down, 3 hits / direction)

Vibration (random)

C-style: 0.04g2 / Hz @ 5-100Hz (2g rms), 60 min. / axis

N-style: 0.1g2 / Hz @ 5-2000Hz (12g rms), 60 min. / axis

C2K User’s Guide 1-3

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 13

1.3 Compliance

MTBF

Calculations are available in accordance with MIL-HDBK-217.

Please contact GEIP for latest values.

Safety

Designed to meet standard UL1950/60950

Emissions

Designed to meet FCC Part15, SubPart A

1.4 C2K GPIO DC Electrical Characteristics

Introduction

Table 1-1 C2K GPIO DC Electrical Characteristics

Symbol Parameter Min Max Unit

GPIO

Igpio GPIO source current 12 mA

lgpio GPIO sink current 12 mA

Vih GPIO input high voltage 2.0 5.5 V

Vil GPIO input low voltage 0.8 V

Voh GPIO output high voltage 2.4 V

Vol GPIO output low voltage 0.4

Unit Supply Current and Power Dissipation

Ppmc

Maximum Power available to each PMC site, sum of

+5.0V and +3.3V powers

7.5 W

1-4 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 14

1.5 Block Diagram

MPC7448

G4

Processor

512KB

L2 Cache

MPX

Bus

167MHz

MV64460

PowerPC

System

Controller

DDR

SDRAM

Mem Bus

167MHz

PCI Bus 0

64-bit 33/66MHz64-bit 33/66MHz

RGMII0

RGMII1

RGMII2

COP (J6)

PCI Bus 0

or 133MHz

PCI-X

PCI 6254

cPCI

Bridge

PMC0

J11

J12

J13

J14

VSC8244

Gigabit

Ethernet

PHY

JTAG_J7

to

JTAG

Scan

Chain

cPCI bus

ETH0

ETH1

ETH2

Introduction

cPCI_J1

cPCI_J2

cPCI_J3

cPCI_J3

cPCI_J4

PCI Bus 1

64-bit 33/66MHz

Tem p

Sensor

Board

Config.

EEPROM

User

EEPROM

RTC

Device Bus

Flash

ROM

(soldered)

PMC1

J21

J22

J23

J24

PCI2050B

PCI/PCI

Bridge

GD31244

SATA

Controller

FPGA

SATA 1

SATA 2

ISP 1563

USB 2.0

Controller

8051

IPMC

Hot

Swap

Ctlr

cPCI_J5

USB1

USB2

USB3

Figure 1-1 C2K Block diagram (a)

C2K User’s Guide 1-5

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 15

MV64460

PowerPC

System

Controller

FPGA

USART

COM3

COM4

COM5

COM6

COM7

COM8

GPIO0

GPIO1

GPIO2

GPIO3

RS-232 I/F

RS-422 I/F

RS-232 I/F

RS-422 I/F

RS-422 I/F

RS-485 I/F

RS-485 I/F

RS-485 I/F

RS-485 I/F

Introduction

cPCI_J4

MPSC

Device

Bus

UART0

UART1

GPIO

RS-422 I/F

RS-232 I/F

RS-422 I/F

RS-232 I/F

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

COM1 (RS-422)

COM1 (RS-232)

COM2 (RS-422)

COM2 (RS-232)

cPCI_J5

Figure 1-2 C2K Block diagram (b)

1-6 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 16

Introduction

1.6 Technical Support

Most issues can be resolved by referring to this manual. If any problems cannot be resolved,

please contact GEIP Technical Support:

If products must be returned, contact GE for a Return Material Authorization (RMA) Number.

This RMA Number must be obtained prior to any return.

RMA request forms can be obtained from:

www.ge-ip.com/rma

GE Technical Support is available at: 1-800-433-2682 in North America,

or +1-780-401-7700 for international calls. Requests for Technical Support can be sent to:

support.huntsville.ip@ge.com

Or, visit our website:

www.ge-ip.com

1.7 Related Documents

For more information on C2K components, refer to the following documents:

Components

• MPC7448 RISC Microprocessor Hardware Specifications—Motorola® Inc., MPC7448EC

Rev. 2, February 2004

• MV64460, MV64461, MV64462 System Controller Hardware Specification - Parts 1 &

2—Marvell Semiconductor, Inc.®, Doc. no. MV-S101286-00(01) Rev B, July 2004

• PCI 6254 (HB6) Dual Mode Universal PCI-to-PCI Bridge DataBook—PLX Technology,

Inc., Version 2.0, May 2003

• PCI2050B PCI-to-PCI Data Manual—Texas Instruments Incorporated, SCPS076E,

November 2004

• ISP1563 Hi-Speed USB PCI Host Controller Product Data—Philips Semiconductors, Document Order Number 9397 750 14244 Rev 01, July 2005

• Intel® 31244 PCI-X to Serial ATA Controller Datasheet—Intel Corporation, Document

Number 273595-005, April 2004

• VSC8244 Quad Port 10/100/1000Base-T PHY with RGMII / RTBI MAC Interfaces—Vitesse Semiconductor Corporation, PB-VSC8244-002, September 2004

• 512Mb: x4, x8, x16, DDR SDRAM Datasheet—Micron Technology, Inc., Rev G 4/04 EN,

April 2004

• Spartan-3E FPGA Family: Complete Data Sheet—Xilinx, Inc., DS312, March 2005

• S29GLxxxN MirrorBit™ Flash Family S29GL512N, S29GL256N, S29GL128N, Data

Sheet—AMD Spansion

• S29GLxxxM MirrorBit™ Flash Family S29GL256M, S29GL128M, S29GL064M,

S29GL032M Data Sheet—AMD Spansion, Publication Number: S29GLxxxM_00 Revi

sion A Amendment 4, March 2004

-

C2K User’s Guide 1-7

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 17

• C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Mixed Signal ISP Flash MCU Family—Silicon Laboratories Inc., Rev 1.3, August 2004

• M41T62 Serial Access Real-Time Clock with Alarms - STMicroelectronics, Rev 10.0,

November 2005

• LTC4244/LTC4244-1 Rugged, CompactPCI Bus Hot Swap Controllers—Linear Technology Corporation, 42441f, February 2004

• Maxim MAX6657/MAX6658/MAX6659 ±1°C, SMBus-Compatible Remote/Local Temperature Sensors with Overtemperature Alarms—Maxim Integrated Products, 19-2034;

Rev. 2, March 2002

Specifications

• ICMB 1.0 Rev 1.3—Intelligent Chassis Management Bus Bridge Specification, April

2003.

• IEEE Std. 802.3-2002—IEEE Standard for Information Technology- Telecommunications

and information exchange between systems- Local and metropolitan area networks - Specific requirements Part 3: Carrier sense multiple access with collision detection

(CSMD/CD) access method and physical layer specifications, March 2002.

• IEEE Std. 1101.2-1992(2001)—IEEE Standard for Mechanical Core Specifications for

Conduction-Cooled Eurocards, January 1993.

• IEEE Std. 1101.10-1996—IEEE Standard for Additional Mechanical Specifications for

Microcomputers using the IEEE Std 1101.1-1991 Equipment Practice, December 1996.

• IEEE Std. 1149.1-1990—IEEE Standard Test Access Port and Boundary Scan Architecture, June 1993.

Introduction

• IEEE Std. 1284-2000—IEEE Standard Signaling Method for a Bidirectional Parallel

Peripheral Interface for Personal Computers, September 2000.

• IEEE1386-2001—IEEE Standard for a Common Mezzanine Card (CMC) Family, June,

2001.

• IEEE1386.1-2001—IEEE Standard Physical and Environmental Layers for PCI Mezzanine Cards (PMC), June, 2001.

• IEEE Std. 802.3-2002—Part 3: Carrier Sense Multiple Access Collision Detection

(CSMA/CD) Access Method and Physical Layer Definitions, March 2002.

• Intel, Universal Host Controller Interface (UHCI) Design Guide, Revision 1.1,

297650-002.

• IPC-A-610—Acceptability of Electronic Assemblies, Revision C, January 2000.

• IPC-6012A with Amendment 1—Qualification and Performance Specification for Rigid

Printed Boards, July 2000.

• PICMG 2.0 Rev 3.0—CompactPCI Specification, October 1999.

• PICMG 2.1 Rev 2.0—Hot Swap Specification, January 2001

• PICMG 2.16 Rev 1.0—Packet Switching Backplane Specification, September 2001

• PICMG 2.3 Rev 1.0—PMC on CompactPCI Specification, August, 1998.

• PICMG 2.9 Rev 1.0—CompactPCI System Management Specification, February, 2000.

• PCI Special Interest Group—PCI Local Bus Specification, Revision 2.3, October 2001.

1-8 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 18

Introduction

• PCI Special Interest Group—PCI-X Local Bus

• Phillips Semiconductors—The I2C Specification, version 2.1, document 9398-393-40011,

January 2000.

• TIA / EIA-232-F-1997, Telecommunications Industry Association—Interface Between

Data Terminal Equipment and Data Circuit-Terminating Equipment Employing Serial

Binary Data Interchange, October 1997.

• TIA / EIA-485-F-1997, Telecommunications Industry Association—

• VITA Standards Organization, VITA 20-2001—American National Standard for Conduction Cooled PMC, August, 2001.

• VITA Standards Organization, VITA 30.1-2002—American National Standard for 2mm

Connector Practice on Conduction Cooled Euroboards, August, 2002.

• VITA Standards Organization, VITA 32-2002—Processor PMC Standard for Processor

PCI Mezzanine Cards, September 2002.

• VITA Standards Organization, VITA 39-2003—PCIX Auxiliary Standard for PMCs and

Processor PMCs, August 2003.

• Universal Serial Bus Specification, Revision 2.0, April 2000.

1. PICMG Specifications are available to PICMG members only. GEIP is not authorized to distribute copies of

these specifications. More information can be found at http://www.picmg.org.

2. VITA Specifications are available to VITA members only. GEIP is not authorized to distribute copies of these

specifications. More information can be found at http://www.vita.com.

3. Data sheets from hardware components can be downloaded from individual vendors web sites.

C2K User’s Guide 1-9

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 19

Chapter 2: Installation

2.1 What Is Included

The C2K Single Board Computer (SBC) is shipped with the following items:

• C2K SBC Printed Circuit Assembly

2.2 Equipment Needed

The following items are needed to install and operate the C2K:

• C-style CompactPCI-compatible chassis

or

• N-style CompactPCI-compatible chassis

E.S.D.

Caution! Always use proper Electrostatic Discharge (ESD) protection when han-

dling printed circuit boards to avoid seriously damaging components. Product handlers must always be properly grounded.

C2K User’s Guide 2-1

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 20

Installation

2.3 Power Requirements

The C2K requires +5.0V and +3.3V from the CompactPCI backplane and Hot Swap functions

require +12V. Installed PMC modules may require ±12V.

2.4 Configurations Jumpers

The C2K provides the following configuration header/jumpers:

2.4.1 FLASH_WP# (P6)

P6 is a 2-pin Flash Write-Protect header/jumper that enables write-protection for the flash memory.

If a jumper is installed on P6, the FLASH_WP# signal is asserted preventing writes to the

flash ROM.

If a jumper is not installed on P6, the FLASH_WP# signal is de-asserted allowing writes the

flash ROM.

2.4.2 EM_BOOTSEL# (P7)

P7 is a 2-pin Emergency Boot Select header/jumper that determines which boot code the C2K will

execute after reset. Boot code provided by GEIP is stored in the upper 8MB of flash memory.

If a jumper is installed on the EM_BOOTSEL header (P7), the GEIP firmware will boot

from the GEIP provided emergency boot code stored in the Emergency Boot area of flash.

If a jumper is not installed on the EM_BOOTSEL header (P7), the firmware will jump to

user boot code area and begin executing custom boot code (see “Boot Code Selection” on

page 4-3).

2.4.3 PCI VIO Select (P9, P12)

P9 and P12 are 3-pin header/jumpers that set the VIO for PCI Busses (PMC sites) at +3.3V or

+5V. P12 controls the VIO for PCI Bus 0 (PMC0) and P9 controls VIO for PCI Bus 1 (PMC1).

If a jumper is installed on pins 1 and 2, the VIO is set to +3.3V.

If a jumper is installed on pins 2 and 3, the VIO is set to +5V

1. +3.3V

2. PMC VIO

3. +5V

12 3

C2K User’s Guide 2-2

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 21

Installation

2.4.4 COP_EN (P10)

P10 is a 2-pin COP Enable header/jumper that isolates the MPC7448 processor from the JTAG

Scan chain and connects the COP header (J6) to the processor to enable software debugging (see

“JTAG circuitry” on page 4-18).

If a jumper is installed on P10, the on-board COP header (J6) is connected to the MCP7448

processor for software debugging.

If a jumper is not installed on P10, the COP header (J6) is disconnected from the processor.

2.4.5 C8051 Debug (P11)

P11 is a 2-pin C8051 Debug header/jumper that isolates the C8051 Microcontroller from the

JTAG Scan chain to enable IPMI software debugging.

If a jumper is installed on P11, the C8051 debugging is enabled.

If a jumper is not installed on P11, the C8051 debugging is disabled.

2.4.6 Header/Jumper Locations

For header/jumper locations, please refer to Figure 3-2 on page 3-2.

NOTE: With the exception of the PCI Bus VIO Select header/jumpers (P9 and P12), none of the

preceding header/jumpers need to have a jumper installed for C2K initial power-up.

2.5 Installation

Caution! Do not attempt to install the C2K in a backplane where the J4 connector is

bused or routed in accordance with the CompactPCI H110 specification. The C2K is

equipped with an IEC key to prevent such installation but if the backplane is not

keyed, installation is still possible.

Caution! Do not attempt to install the C2K in a Fabric slot of a PICMG 2.16 Packet

Switching Backplane. The C2K is equipped with an IEC key to prevent such

installation, but if the backplane is not keyed installation is still possible.

2.5.1 C2K C-style Installation

1. Remove the C2K from the static-safe envelope (see “E.S.D. Caution” on page 2-1).

2-3 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 22

Installation

2. Install optional PMC module(s) per manufacturers instructions (see “PMC Sites” on

page 4-14 for restrictions).

3. Configure the PMC VIO using VIO configuration jumpers P9, P12 (see “PCI VIO Select

(P9, P12)” on page 2-2).

4. Install the C2K in a 6U C-style CompactPCI-compliant chassis.

5. Slide the C2K into the slot guide, applying even pressure to the upper and lower extraction

handles. Be careful not to bend connector pins.

NOTE: The C-style C2K is Hot Swap-compliant and can be installed in and removed from

a powered-on Hot Swap-compliant chassis.

After sliding the C2K in the slot guide until the card engages the pins, wait for the blue

front-panel Hot Swap LED to turn off before closing the ejector handle switch (bottom

ejector handle).

6. Push up on the lower extraction handle and down on the upper handle to seat the CompactPCI connectors in the backplane connectors. The red tab on the extraction handles should

“click” when the board is locked into the chassis.

7. Tighten the small phillips-head screws embedded in the upper and lower extraction handles

to secure the C2K to the chassis.

8. Apply power to the chassis.

NOTE: C2K can be installed in a system controller or peripheral slot. If the C2K is not installed

in a system slot, a system controller card must be installed in the system slot to supply a PCI reference clock to C2K.

2.5.2 C2K N-style Installation

1. Remove the C2K SBC from the static-safe envelope (see “E.S.D. Caution” on page 2-1).

2. Install optional PMC module(s) per manufacturers instructions (see “PMC Sites” on

page 4-14 for restrictions).

3. Configure the PMC VIO using VIO configuration jumpers P9, P12 (see “PCI VIO Select

(P9, P12)” on page 2-2).

4. Install the C2K in a 6U N-style CompactPCI-compliant chassis.

5. Slide the C2K into the slot guide, applying even pressure to the upper and lower extraction

handles. Be careful not to bend connector pins.

6. Tighten upper and lower Wedge-Loks™ to 115inch/ounces using a 3/32-inch hex driver.

This secures the C2K in the system chassis and ensures proper heat conduction. Do not

overtighten.

7. Apply power to the chassis.

NOTE: C2K can be installed in a system controller or peripheral slot. If the C2K is not installed

in a system slot, a system controller card must be installed in the system slot to supply a PCI reference clock to C2K.

C2K User’s Guide 2-4

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 23

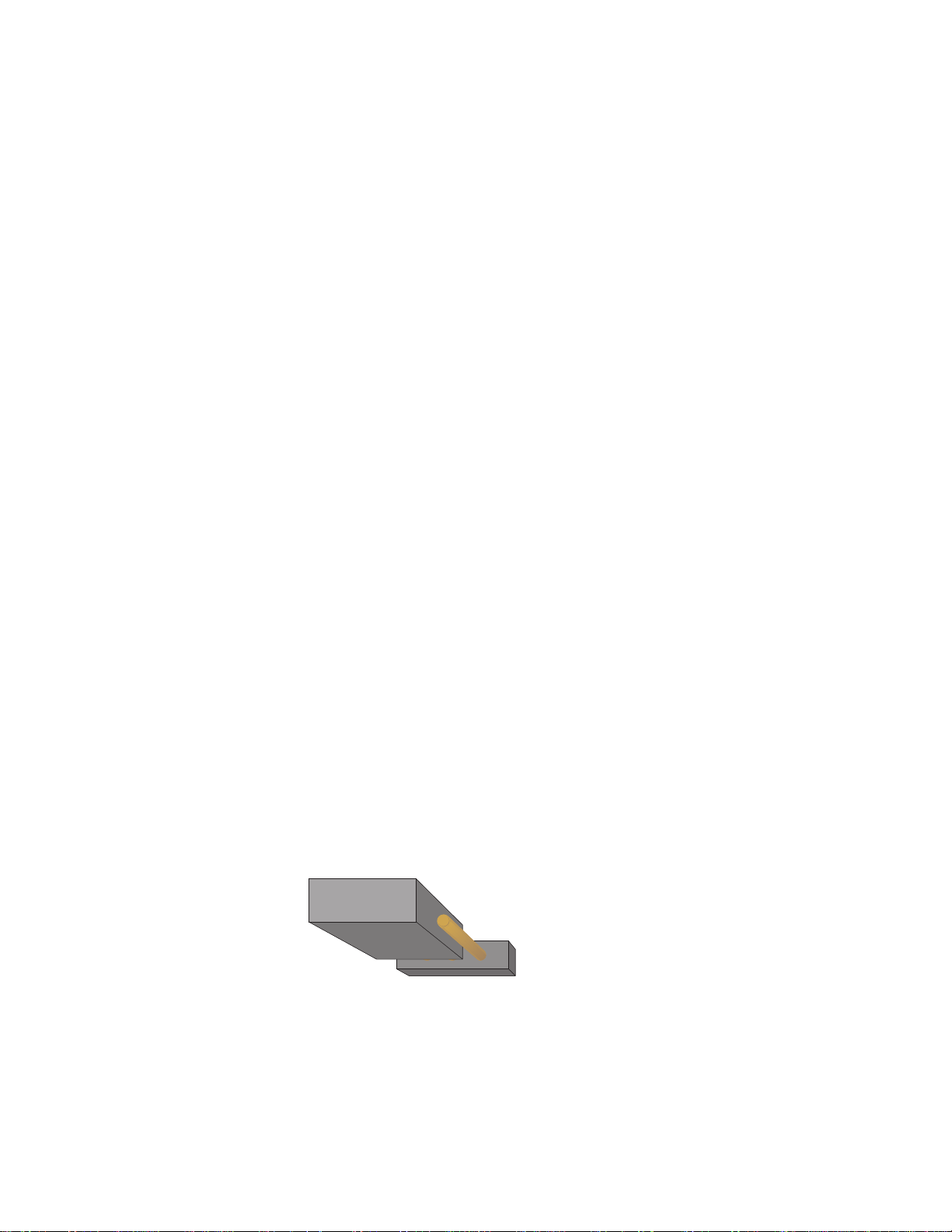

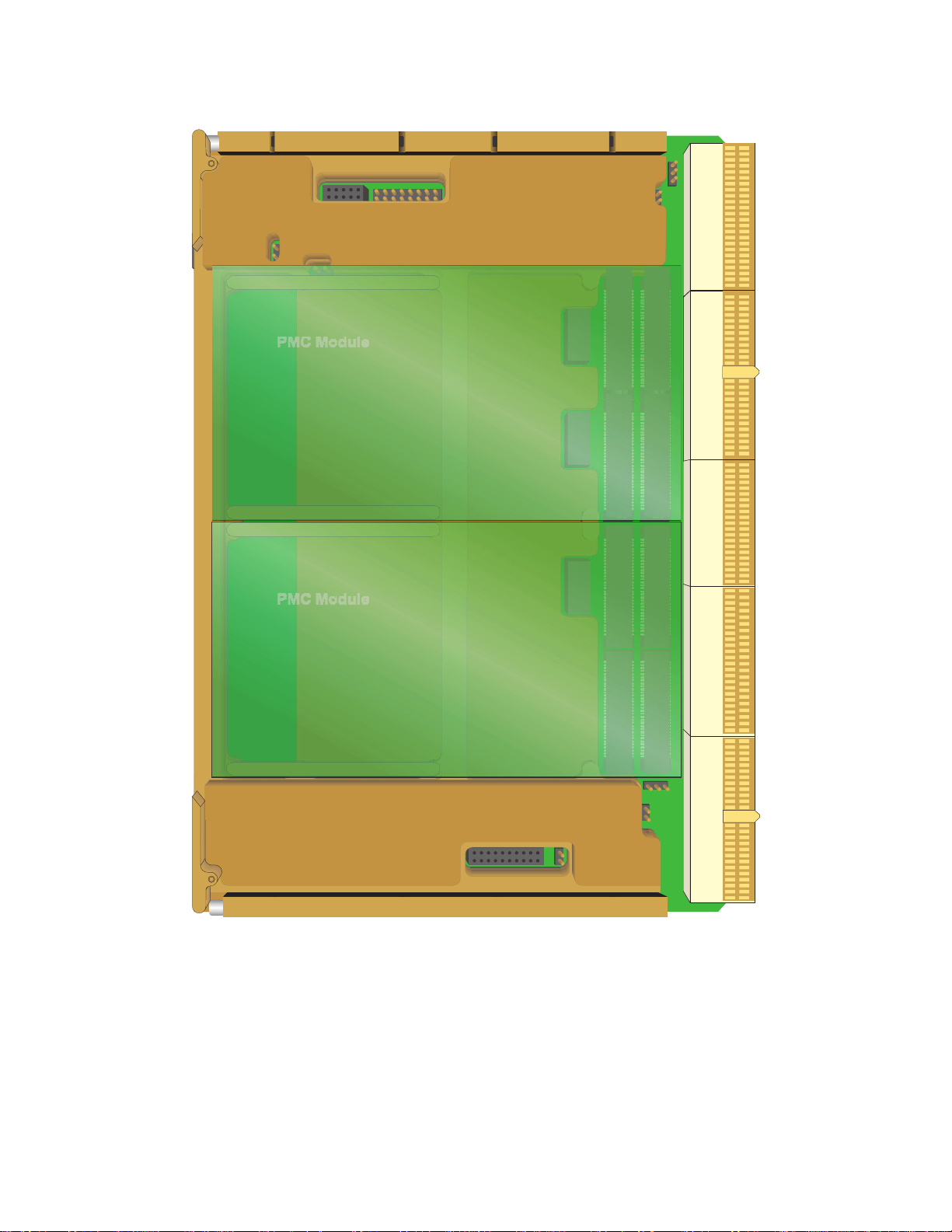

PMC Module

Installation

PMC Module

Figure 2-1 C2K (C-style) with PMC modules installed

2-5 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 24

PMC Module

Installation

PMC Module

Figure 2-2 C2K (N-style) with PMC modules installed

C2K User’s Guide 2-6

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 25

Installation

2.6 U-Boot Utility

The C2K includes a universal boot loader (U-Boot) utility that is pre-installed in flash ROM.

U-Boot is designed to work with any operating system including Linux and VxWorks® and performs the following functions:

• Load the O/S kernel from Ethernet, user flash area, or USB

• Program the user flash

• Program the boot flash (self update)

• Load the O/S kernel from user flash

• Set the Real-Time Clock

• Save boot parameters in EEPROM

• Configure the MV64460 Memory Controller

2.6.1 Installation

The C2K is shipped with U-Boot pre-installed in flash memory.

2.6.2 Initialization

The C2K has been initialized during production and testing.

2.6.3 Commands

The following is a summary of commands the U-Boot utility uses for the C2K:

?

autoscr

base

bdinfo

boot boots default, e.g., run ‘bootcmd’

bootd boots default, e.g., run ‘bootcmd’

bootelf

bootm

bootp

bootvx

cmp

coninfo

cp

crc32

date

echo

erase

flinfo

alias for ‘help’

runs script from memory

prints or sets address offset

prints Board Info structure

boots from an ELF image in memory

boots application image from memory

boots image from the network using BootP/TFTP protocol

boots VxWorks from an ELF image

compares memory

prints console devices and information

copies memory

calculates checksum

gets / sets / resets date and time

echoes arguments to console

erases flash memory

prints flash memory information

2-7 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 26

Installation

to

help

iminfo

imls

loadb

loads

loop

md

mm

mtest

mw

nm

ping

printenv

protect

rarpboot

reset

run

saveenv

setenv

sleep

tfpboot

version

starts application at address ‘addr’

prints online help

prints header information for application image

lists all images found in flash

loads binary file over serial line (kermit mode)

loads S-Record file over serial line

performs infinite loop on address range

displays memory

modifies memory (auto-incrementing)

tests RAM

writes memory (fill)

modifies memory (constant address)

sends ICMP ECHO REQUEST to network host

prints environment variables

enables or disables flash write-protect

boots image from network using RARP/TFRP protocol

resets the CPU

runs commands in an environment variable

saves environment variables to a persistent storage

sets environment variables

delays execution for some time

boots image from network using TFTP protocol

prints monitor version

C2K User’s Guide 2-8

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 27

2.6.4 Information Commands

The following U-Boot commands provide information

bdinfo

C2K=> help bdinfo

bdinfo:

prints board information used by U-Boot, such as memory addresses and sizes, clock frequencies

and MAC addresses.

coninfo

C2K=> help coninfo

cp [.b, .w, .l] source target count:

displays console I/O device information.

flinfo

C2K=> help flinfo

flinfo:

Installation

prints information for all flash memory banks.

flinfo N:

prints information for flash memory bank # N.

iminfo

C2K=> help iminfo

iminfo addr [addr ...]:

prints header information for application image starting at address ‘addr’ in memory; this includes verification of the image contents (magic number, header and payload checksums).

imls

C2K=> help imls

imls:

prints information about all images found at sector boundaries in flash.

help

C2K=> help

help [command ...]:

shows help information (for ‘command’).

prints online help for the monitor commands.

without arguments, it prints a short usage message for all commands.

to get detailed information about specific commands, type ‘help’ with one or more command names

as arguments.

2-9 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 28

2.6.5 Memory Commands

base

C2K=> help base

base:

prints address offset from memory commands.

base off:

sets address offset for memory commands to ‘off’.

crc32

C2K=> help crd32

crc32 address count [addr]:

calculates CRC32 checksum [save at addr].

cmp

C2K=> help cmp

Installation

cmp [.b, .w, .l] adder1 addr2 count:

compares memory.

cp

C2K=> help cp

cp [.b, .w, .l] source target count:

copies memory.

md

C2K=> help md

md [.b, .w, .l] address [# of objects]:

displays memory.

mm

C2K=> help mm

mm [.b, .w, .l] address:

modifies memory, automatically increments address.

mtest

C2K=> help mtest

mtest [start [end [pattern]]]:

performs simple RAM read/write test.

C2K User’s Guide 2-10

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 29

mw

C2K=> help mw

mw [.b, .w, .l] address value [count]:

perform memory write.

nm

C2K=> help nm

nm [.b, .w, .l] address:

modifies memory, read and keep address.

loop

C2K=> help loop

loop [.b, .w, .l] address number_of_objects:

performs loop on a set of addresses.

2.6.6 Flash Memory Commands

erase

C2K=> help erase

Installation

erase start end:

erases flash from addr ‘start’ to addr ‘end’.

erase N:SF [-SL]:

erases sectors SF–SL in flash bank # N.

erase bank N:

erases flash bank # N.

erase all:

erases all flash banks.

protect

C2K=> help protect

protect on start end:

protects flash from addr ‘start’ to addr ‘end’.

protect on N:SD [-SL]:

protects sectors SF–SL in flash bank # N.

protect on bank N:

protects flash bank N.

protect on start all:

protects all flash banks.

2-11 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 30

protect off start end:

enables writes to flash from addr ‘start’ to addr ‘end’.

protect on N:SD [-SL]:

enables writes to sectors SF–SL in flash bank # N.

protect on bank N:

enables writes to flash bank N.

protect on start all:

enables writes to all flash banks.

2.6.7 Execution Control Commands

boot

C2K=> help boot

bootm

C2K=> help bootm

bootm [addr [arg...]]:

Installation

boots application image stored in memory passing argument ‘arg ...’; when booting a Linux kernel,

‘arg’ can be the address of an initrd image.

go

C2K=> help go

go addr[arg ...]:

starts application at address ‘addr’ passing ‘arg’ as arguments.

2.6.8 Download Commands

bootp

C2K=> help bootp

bootp [loadAddress] [bootfilename]:

bootelf

C2K=> help bootelf

bootelf [address]:

loads address of ELF image.

bootvx

C2K=> help bootvx

bootvx [address]:

loads address of VxWorks ELF image.

C2K User’s Guide 2-12

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 31

loadb

C2K=> help loadb

loadb [off] [baud]:

loads binary file over serial line with offset ‘off’ and baud rate ‘baud’.

loads

C2K=> help loads

loads [off] [baud]:

loads S-Record fileover serial line with offset ‘off’ and baud rate ‘baud’.

rarpboot

C2K=> help rarpboot

rarpboot [loadAddress] [bootfilename]:

prints values of all environment variables.

tftpboot

C2K=> help tftpboot

Installation

tftpboot [loadAddress] [bootfilename]:

2.6.9 Environment Variables Commands

printenv

C2K=> help printenv

printenv:

prints values of all environment variables.

printenv name ...

print value of environment variable ‘end’.

saveenv

C2K=> help saveenv

saveenv:

no help available.

setenv

C2K=> help setenv

setenv name value ...

sets environment variable ‘name’ to ‘value...’

setenv name:

deletes environment variable ‘name’.

2-13 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 32

run

C2K=> help run

run var [...]:

runs the commands in the environment variable(s) ‘var’.

bootd

C2K=> help bootd

bootd:

no help available

2.6.10 Miscellaneous Commands

ping

C2K=> help ping

ping pingaddress:

date

C2K=> help date

Installation

date [MMDDhhmm [CC]YY][.ss]:

date reset:

without arguments: prints data and time.

with arguments: sets the system date and time.

with ‘reset’ argument: resets the Real-Time Clock.

reset

C2K=> help reset

reset:

no help available.

sleep

C2K=> help sleep

sleep N:

delays execution for N seconds (N is _decimal_ !!!!).

version

C2K=> help version

version:

no help available.

C2K User’s Guide 2-14

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 33

Chapter 3: Interfaces

3.1 Front Panel

The C2K front-panel (C-style version only)

includes the following features:

• LEDs

• Two PMC front panel cutouts

• USB connector (J8)

• Recessed manual reset switch

LEDs: Hot Swap (blue), PWR (green), PBIT

(green), and User (yellow), 8051 (yellow).

PMC Cutouts: two cutouts to accommodate installed

PMC module front panels.

USB Connector: USB4—Type A USB connector

(J8).

Recessed Reset: provides access to a recessed reset

micro-switch for performing a manual hardware

reset.

TIP: A straightened paper clip can be

used to access the recessed reset button.

RESET

USB

USB

PMC1PMC1

PBIT

PWR

USER

PBIT

USER

IPMC

IPMC

PWR

HS

HS

b.a.

Figure 3-1 Front panels: a. C-style; b. N-style

C2K User’s Guide 3-1

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 34

3.2 Connectors

3.2.1 Connector Locations

Interfaces

J8

P7

P11

J7

P15

J21

J23

P6

P9

J22

J24J12

J5

J4

J3

J11

J2

J13

J14

P12

J1

P13

J6

P10

(Drawing not to scale)

Figure 3-2 Connector locations (C-style)

NOTE: The front-panel USB connector (J8) is only available on C-style versions of the C2K.

C2K User’s Guide 3-2

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 35

Interfaces

P7

J7

P11

P15

J21

J23

P6

P9

J22

J24J12

J5

J4

J3

J11

J13

J6

P10

Figure 3-3 Connector locations (N-style)

P12

P13

J2

J14

J1

3-3 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 36

Connector Legend

Interfaces

J1–J5: P6:

J11–J14: P11:

J21–J24: P12:

CompactPCI connectors ROM_WP#

COP header EM_BOOTSEL#

J6: P7:

JTAG header PMC1 VIO Selection header

J7: P9:

USB front-panel connector COP Interface Enable

J8: P10:

PMC0 site connectors C8051 Debug Enable

PMC1 site connectors PMC0 VIO Selection header

COM Port Termination header

P15:

3.2.2 CompactPCI Connector Pin Assignments

CPCI_J1 Pin Assignments

Table 3-1 cPCI connector J1 pin assignments

Pin A B C D E F

J1-25

J1-24

J1-23

J1-22

J1-21

J1-20

J1-19

J1-18

J1-17

J1-16

J1-15

J1-12–14

J1-11

J1-10

J1-9

J1-8

J1-7

J1-6

J1-5

J1-4

J1-3

J1-2

J1-1

+5V REQ64# ENUM# +3.3V +5V GND

AD1 +5V VIO AD0 ACK64# GND

+3.3V AD4 AD3 +5V AD2 GND

AD7 GND +3.3V AD6 AD5 GND

+3.3V AD9 AD8 M66EN C/BE0# GND

AD12 GND VIO AD11 AD10 GND

+3.3V AD15 AD14 GND AD13 GND

SERR# GND +3.3V PA R C/BE1# GND

+3.3V IPMB_SCL IPMB_SDA GND PERR# GND

DEVSEL# GND VIO STOP# LOCK# GND

+3.3V FRAME# IRDY# BD_SEL# TRDY# GND

AD18 AD17 AD16 GND C/BE2# GND

AD21 GND +3.3V AD20 AD19 GND

C/BE3# IDSEL AD23 GND AD22 GND

AD26 GND VIO AD25 AD24 GND

AD30 AD29 AD28 GND AD27 GND

REQ0# PCI_PRESENT# +3.3V CLK0 AD31 GND

BRSVP1A5 BRSVP1B5 PCI_RST# GND GNT0# GND

IPMB_PWR HEALTHY# VIO INTP INTS GND

INTA# INTB# INTC# +5V INTD# GND

TCK +5V TMS TDO TDI GND

+5V -12V TRST# +12 +5V GND

C2K User’s Guide 3-4

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 37

cPCI_J2 Pin Assignments

Table 3-2 CompactPCI connector J2 pin assignments

Pin A B C D E F

J2-22

J2-21

J2-20

J2-19

J2-18

J2-17

J2-16

J2-15

J2-14

J2-13

J2-12

J2-11

J2-10

J2-9

J2-8

J2-7

J2-6

J2-5

J2-4

J2-3

J2-2

J2-1

GA4 GA3 GA2 GA1 GA0 GND

CLK6 GND rsvd rsvd rsvd GND

CLK5 GND rsvd GND rsvd GND

GND GND SMB_SDA SMB_SCL SMB_ALERT# GND

BRSVP2A18 BRSVP2B18 BRSVP2C18 GND BRSVP2E18 GND

BRSVP2A17 GND PRST# REQ6# GNT6# GND

BRSVP2A16 BRSVP2B16 DEG# GND BRSVP2E16 GND

BRSVP2A15 GND FAL# REQ5# GNT5# GND

AD35 AD34 AD33 GND AD32 GND

AD38 GND VIO AD37 AD36 GND

AD42 AD41 AD40 GND AD39 GND

AD45 GND VIO AD44 AD43 GND

AD49 AD48 AD47 GND AD46 GND

AD52 GND VIO AD51 AD50 GND

AD56 AD55 AD54 GND AD53 GND

AD59 GND VIO AD58 AD57 GND

AD63 AD62 AD61 GND AD60 GND

C/BE5# CPCI_64EN# VIO C/BE4# PAR64 GND

VI/O BRSVP2B4 C/BE7# GND C/BE6# GND

CLK4 GND GNT3# REQ4# GNT4# GND

CLK2 CLK3 SYSEN# GNT2# REQ3# GND

CLK1 GND REQ1# GNT1# REQ2# GND

Interfaces

NOTES:

SMB_SCL: This signal is not supported on C2K.

a.

SMB_SDA: This signal is not supported on C2K.

b.

3-5 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 38

cPCI_J3 Pin Assignments

Table 3-3 CompactPCI connector J3 pin assignments

Pin A B C D E F

J3-19

J3-18

J3-17

J3-16

J3-15

J3-14

J3-13

J3-12

J3-11

J3-10

J3-9

J3-8

J3-7

J3-6

J3-5

J3-4

J3-3

J3-2

J3-1

GND GND GND GND GND GND

ETH0_DA+ ETH0_DA- GND ETH0_DC+ ETH0_DC- GND

ETH0_DB+ ETH0_DB- GND ETH0_DD+ ETH0_DD- GND

ETH1_DA+ ETH1_DA- GND ETH1_DC+ ETH1_DC- GND

ETH1_DB+ ETH1_DB- GND ETH1_DD+ ETH1_DD- GND

+3.3V +3.3V n/c +5V +5V GND

PMC0_5 PMC0_4 PMC0_3 PMC0_2 PMC0_1 GND

PMC0_10 PMC0_9 PMC0_8 PMC0_7 PMC0_6 GND

PMC0_15 PMC0_14 PMC0_13 PMC0_12 PMC0_11 GND

PMC0_20 PMC0_19 PMC0_18 PMC0_17 PMC0_16 GND

PMC0_25 PMC0_24 PMC0_23 PMC0_22 PMC0_21 GND

PMC0_30 PMC0_29 PMC0_28 PMC0_27 PMC0_26 GND

PMC0_35 PMC0_34 PMC0_33 PMC0_32 PMC0_31 GND

PMC0_40 PMC0_39 PMC0_38 PMC0_37 PMC0_36 GND

PMC0_45 PMC0_44 PMC0_43 PMC0_42 PMC0_41 GND

PMC0_50 PMC0_49 PMC0_48 PMC0_47 PMC0_46 GND

PMC0_55 PMC0_54 PMC0_53 PMC0_52 PMC0_51 GND

PMC0_60 PMC0_59 PMC0_58 PMC0_57 PMC0_56 GND

PMC0_VIO PMC0_64 PMC0_63 PMC0_62 PMC0_61 GND

Interfaces

NOTES:

ETHn: Gigabit Ethernet signals per PICMG 2.16 R1.0 (ETH0, ETH1)

a.

PMC0 I/O: from PMC0_J14 per PICMG 2.3 (PMC0_1–64)

b.

PMC0_VIO: +3.3V or +5V according PMC0 VIO Selection header/jumper—P12

c.

d.

J3-C-14 is connected to +3.3V on Rev.10 and Rev. 20 level boards.

C2K User’s Guide 3-6

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 39

CPCI_J4 Pin Assignments

Table 3-4 cPCI connector J4 pin assignments

Pin A B C D E F

J4-25

J4-24

J4-23

J4-22

J4-21

J4-20

J4-19

J4-18

J4-17

J4-16

J4-15

J4-12–14

J4-11

J4-10

J4-9

J4-8

J4-7

J4-6

J4-5

J1-4

J4-3

J4-2

J4-1

n/c n/c n/c n/c n/c GND

GPIO_0 GPIO_1 GPIO_2 GPIO_3 n/c GND

n/c n/c n/c n/c n/c GND

COM8_RXC- n/c n/c COM1_RXC- COM2_RXC- GND

COM8_RXC+ n/c n/c COM1_RXC+ COM2_RXC+ GND

COM8_TXC- COM3_232_RX n/c COM1_TXC- COM2_TXC- GND

COM8_TXC+ COM3_232_TX n/c COM1_TXC+ COM2_TXC+ GND

COM8_RXD- n/c n/c COM1_RXD- COM2_RXD- GND

COM8_RXD+ n/c n/c COM1_RXD+ COM2_RXD+ GND

COM8_TXD- COM4_232_RX n/c COM1_TXD- COM2_TXD- GND

COM8_TXD+ COM4_232_TX n/c COM1_TXD+ COM2_TXD+ GND

COM3_RXC- COM4_RXC- COM5_RXC- COM6_RXC- COM7_RXC- GND

COM3_RXC+ COM4_RXC+ COM5_RXC+ COM6_RXC+ COM7_RXC+ GND

COM3_TXC- COM4_TXC- COM5_TXC- COM6_TXC- COM7_TXC- GND

COM3_TXC+ COM4_TXC+ COM5_TXC+ COM6_TXC+ COM7_TXC+ GND

COM3_RXD- COM4_RXD- COM5_RXD- COM6_RXD- COM7_RXD- GND

COM3_RXD+ COM4_RXD+ COM5_RXD+ COM6_RXD+ COM7_RXD+ GND

COM3_TXD- COM4_TXD- COM5_TXD- COM6_TXD- COM7_TXD- GND

COM3_TXD+ COM4_TXD+ COM5_TXD+ COM6_TXD+ COM7_TXD+ GND

n/c n/c n/c n/c n/c GND

ETH2_DA+ ETH2_DA- GND ETH2_DC+ ETH2_DC- GND

ETH2_DB+ ETH2_DB- GND ETH2_DD+ ETH2_DD- GND

Interfaces

NOTES:

ETHn: Gigabit Ethernet (ETH2)

a.

GPIO: General purpose I/O (GPIO_0–GPIO_3)

b.

Serial I/O: COM1, COM2 (RS-422), COM3, COM4 (RS232/422), COM5–COM8 (RS-422/485)

c.

3-7 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 40

cPCI_J5 Pin Assignments

Table 3-5 CompactPCI connector J5 pin assignments

Pin A B C D E F

J5-22

J5-21

J5-20

J5-19

J5-18

J5-17

J5-16

J5-15

J5-14

J5-13

J5-12

J5-11

J5-10

J5-9

J5-8

J5-7

J5-6

J5-5

J5-4

J5-3

J5-2

J5-1

PMC1_5 PMC1_4 PMC1_3 PMC1_2 PMC1_1 GND

PMC1_10 PMC1_9 PMC1_8 PMC1_7 PMC1_6 GND

PMC1_15 PMC1_14 PMC1_13 PMC1_12 PMC1_11 GND

PMC1_20 PMC1_19 PMC1_18 PMC1_17 PMC1_16 GND

PMC1_25 PMC1_24 PMC1_23 PMC1_22 PMC1_21 GND

PMC1_30 PMC1_29 PMC1_28 PMC1_27 PMC1_26 GND

PMC1_35 PMC1_34 PMC1_33 PMC1_32 PMC1_31 GND

PMC1_40 PMC1_39 PMC1_38 PMC1_37 PMC1_36 GND

PMC1_45 PMC1_44 PMC1_43 PMC1_42 PMC1_41 GND

PMC1_50 PMC1_49 PMC1_48 PMC1_47 PMC1_46 GND

PMC1_55 PMC1_54 PMC1_53 PMC1_52 PMC1_51 GND

PMC1_60 PMC1_59 PMC1_58 PMC1_57 PMC1_56 GND

PMC1_VIO PMC1_64 PMC1_63 PMC1_62 PMC1_61 GND

BATT+ EM_BOOTSEL# GPIO_4 GPIO_9 GPIO_14

/ PROCFAIL#

ROM_WP# BIT_PASS# PMC_JTAG_EN# GPIO_8 GPIO_13 GND

PB_RST_IN# GPIO_15 / NMI# ICMB_D- GPIO_7 GPIO_12 GND

SATA1_RX- SATA2_RX- ICMB_D+ GPIO_6 GPIO_11 GND

SATA1_RX+ SATA2_RX+ unused GPIO_5 GPIO_10 GND

SATA1_TX- SATA2_TX- USB1_PWR USB2_PWR USB3_PWR GND

SATA1_TX+ SATA2_TX+ USB1_D- USB2_D- USB3_D- GND

COM1_232_RX COM2_232_RX USB1_D+ USB2_D+ USB3_D+ GND

COM1_232_TX COM2_232_TX USB1_GND USB2_GND USB3_GND GND

Interfaces

GND

NOTES:

BATT+: External battery input. The +3.3V supply from the system is used as a battery backup

a.

for the NVRAM and RTC devices.

BIT_PASS#: Built-In Test (BIT) Status output. At power-up or after reset, this signal is de-asserted

b.

(high). After the firmware Built-In-Test has successfully completed, this signal is

asserted (low).

EM_BOOTSEL#: Emergency Boot Select input. When this signal is not asserted (high), the boot code is

c.

allowed to exit GEIP-provided boot code. When this input is asserted (low), the boot

code continues to execute from GEIP-provided (Emergency Boot code) boot code.

This signal is pulled high.

GPIO: General purpose I/O (GPIO_4–GPIO_14)

d.

ICMB: Inter-Chassis Management Bus

e.

NMI#: GPIO_15 or Non-Maskable Interrupt input. To make this signal non-maskable, the

f.

CPU_MRS[EE] interrupt mask bit, as well as the bridge mask, must be set.

PB_RST_IN#: Push-button reset button signal from backplane (C2K-TM).

g.

PMC1 I/O: from PMC1_J24 per PICMG 2.3

h.

C2K User’s Guide 3-8

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 41

NOTES:

PMC1_VIO: +5V or +3.3V according to PMC1 VIO Selection header/jumper—P9.

i.

PMC_JTAG_

j.

EN#:

Includes the PMC sites in the JTAG Scan chain. When this signal is asserted (low),

the PMC modules installed on the PMC sites are included in the JTAG Scan chain.

NOTE: This function is intended to be used during manufacturing test time.

PROCFAIL#: GPIO_14 or Processor Fail output. This signal is asserted when a processor failure

k.

(watchdog timer expire) has been detected.

ROM_WP#: Flash write-protect input. When asserted (active low) the flash memory is write-pro-

l.

tected. This signal is pulled up enabling writes to flash memory for backplanes that do

not support a write-protect feature.

Serial ATA: 1.5Gb/s serial ATA (SATA1, SATA2).

m.

Serial I/O: These ports are configured as RS-232 (transmit and receive signals only) (COM1,

n.

COM2)

USB Standard USB 2.0 ports (USB1, USB2, USB3)

o.

Interfaces

3-9 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 42

Interfaces

3.2.3 PMC Connector Pin Assignments

PMC0 Connectors

Table 3-6 PMC0_J11 and PMC0_J12 pin assignments.

PMC0_J11 PMC0_J12

Pin Assignment Pin Assignment Pin Assignment Pin Assignment

1 2 1 2

PMC0_TCK -12V +12V PMC0_TRST#

3 4 3 4

GND PMC0_INTA# PMC0_TMS PMC0_TDO

5 6 5 6

PMC0_INTB# PMC0_INTC# PMC0_TDI GND

7 8 7 8

BUSMODE1# +5V GND rsvd

9 10 9 10

PMC0_INTD# rsvd rsvd rsvd

11 12 11 12

GND 3.3Vaux BUSMODE2# +3.3V

13 14 13 14

PCI0_CLK GND PMC0_RST# BUSMODE3#

15 16 15 16

GND PCI0_GNT0# +3.3V BUSMODE4#

17 18 17 18

PCI0_REQ0# +5V PME# GND

19 20 19 20

VIO PCI0_AD31 PCI0_AD30 PCI0_AD29

21 22 21 22

PCI0_AD28 PCI0_AD27 GND PCI0_AD26

23 24 23 24

PCI0_AD25 GND PCI0_AD24 +3.3V

25 26 25 26

GND PCI0_C/BE3# PCI0_IDSEL PCI0_AD23

27 28 27 28

PCI0_AD22 PCI0_AD21 +3.3V PCI0_AD20

29 30 29 30

PCI0_AD19 +5V PCI0_AD18 GND

31 32 31 32

VIO PCI0_AD17 PCI0_AD16 PCI0_C/BE2#

33 34 33 34

PCI0_FRAME# GND GND rsvd

35 36 35 36

GND PCI0_IRDY# PCI0_TRDY# +3.3V

37 38 37 38

PCI0_DEVSEL# +5V GND PCI0_STOP#

39 40 39 40

PCIXCAP PMC0_LOCK# PCI0_PERR# GND

41 42 41 42

rsvd rsvd +3.3V PCI0_SERR#

43 44 43 44

PCI0_PAR GND PCI0_C/BE1# GND

45 46 45 46

VIO PCI0_AD15 PCI0_AD14 PCI0_AD13

47 48 47 48

PCI0_AD12 PCI0_AD11 PCI0_M66EN PCI0_AD10

49 50 49 50

PCI0_AD9 +5V PCI0_AD8 +3.3V

51 52 51 52

GND PCI0_C/BE0# PCI0_AD7 rsvd

53 54 53 54

PCI0_AD6 PCI0_AD5 +3.3V rsvd

55 56 55 56

PCI0_AD4 GND rsvd GND

57 58 57 58

VIO PCI0_AD3 rsvd rsvd

59 60 59 60

PCI0_AD2 PCI0_AD1 GND rsvd

61 62 61 62

PCI0_AD0 +5V PCI0_ACK64# +3.3V

63 64 63 64

GND PCI0_REQ64# GND rsvd

NOTES:

BUSMODE1#: C2K ignores this signal.

a.

BUSMODE2–4#: Wired to indicate “Return ‘Card Present’ if PCI capable and uses PCI Protocol” mode,

b.

as defined in IEEE 1386-2001.

3.3Vaux: Not connected on C2K.

c.

C2K User’s Guide 3-10

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 43

Interfaces

NOTES:

VIO +3.3V or +5V according to PMC0 VIO Selection header/jumper—P12.

d.

rsvd Reserved and not connected.

e.

Table 3-7 PMC0_J13 and PMC0_J14 pin assignments.

PMC0_J13 PMC0_J14

Pin Assignment Pin Assignment Pin Assignment Pin Assignment

1 2 1 2

rsvd GND PMC0_1 PMC0_2

3 4 3 4

GND PCI0_C/BE7# PMC0_3 PMC0_4

5 6 5 6

PCI0_C/BE6# PCI0_C/BE5# PMC0_5 PMC0_6

7 8 7 8

PCI0_C/BE4# GND PMC0_7 PMC0_8

9 10 9 10

VIO PCI0_PAR64 PMC0_9 PMC0_10

11 12 11 12

PCI0_AD63 PCI0_AD62 PMC0_11 PMC0_12

13 14 13 14

PCI0_AD61 GND PMC0_13 PMC0_14

15 16 15 16

GND PCI0_AD60 PMC0_15 PMC0_16

17 18 17 18

PCI0_AD59 PCI0_AD58 PMC0_17 PMC0_18

19 20 19 20

PCI0_AD57 GND PMC0_19 PMC0_20

21 22 21 22

VIO PCI0_AD56 PMC0_21 PMC0_22

23 24 23 24

PCI0_AD55 PCI0_AD54 PMC0_23 PMC0_24

25 26 25 26

PCI0_AD53 GND PMC0_25 PMC0_26

27 28 27 28

GND PCI0_AD52 PMC0_27 PMC0_28

29 30 29 30

PCI0_AD51 PCI0_AD50 PMC0_29 PIO0_30

31 32 31 32

PCI0_AD49 GND PMC0_31 PMC0_32

33 34 33 34

GND PCI0_AD48 PMC0_33 PMC0_34

35 36 35 36

PCI0_AD47 PCI0_AD46 PMC0_35 PMC0_36

37 38 37 38

PCI0_AD45 GND PMC0_37 PMC0_38

39 40 39 40

VIO PCI0_AD44 PMC0_39 PMC0_40

41 42 41 42

PCI0_AD43 PCI0_AD42 PMC0_41 PMC0_42

43 44 43 44

PCI0_AD41 GND PMC0_43 PMC0_44

45 46 45 46

GND PCI0_AD40 PMC0_45 PMC0_46

47 48 47 48

PCI0_AD39 PCI0_AD38 PMC0_47 PMC0_48

49 50 49 50

PCI0_AD37 GND PMC0_49 PMC0_51

51 52 51 52

GND PCI0_AD36 PMC0_51 PMC0_52

53 54 53 54

PCI0_AD35 PCI0_AD34 PMC0_53 PMC0_54

55 56 55 56

PCI0_AD33 GND PMC0_55 PMC0_56

57 58 57 58

VIO PCI0_AD32 PMC0_57 PMC0_58

59 60 59 60

n/c rsvd PMC0_59 PMC0_60

61 62 61 62

n/c GND PMC0_61 PMC0_62

63 64 63 64

GND rsvd PMC0_63 PMC0_64

3-11 C2K User’s Guide

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 44

Interfaces

PMC1 Connectors

Table 3-8 PMC1_J21 and PMC1_J22 pin assignments.

PMC1_J21 PMC1_J22

Pin Assignment Pin Assignment Pin Assignment Pin Assignment

1 2 1 2

PMC1_TCK -12V +12V PMC1_TRST#

3 4 3 4

GND PMC1_INTA# PMC1_TMS PMC1_TDO

5 6 5 6

PMC1_INTB# PMC1_INTC# PMC1_TDI GND

7 8 7 8

BUSMODE1# +5V GND rsvd

9 10 9 10

PMC1_INTD# rsvd rsvd rsvd

11 12 11 12

GND 3.3Vaux BUSMODE2# +3.3V

13 14 13 14

PCI1_CLK GND PMC1_RST# BUSMODE3#

15 16 15 16

GND PCI1_GNT0# +3.3V BUSMODE4#

17 18 17 18

PCI1_REQ0# +5V PME# GND

19 20 19 20

VIO PCI1_AD31 PCI1_AD30 PCI1_AD29

21 22 21 22

PCI1_AD28 PCI1_AD27 GND PCI1_AD26

23 24 23 24

PCI1_AD25 GND PCI1_AD24 +3.3V

25 26 25 26

GND PCI1_C/BE3# PCI1_IDSEL PCI1_AD23

27 28 27 28

PCI1_AD22 PCI1_AD21 +3.3V PCI1_AD20

29 30 29 30

PCI1_AD19 +5V PCI1_AD18 GND

31 32 31 32

VIO PCI1_AD17 PCI1_AD16 PCI1_C/BE2#

33 34 33 34

PCI1_FRAME# GND GND rsvd

35 36 35 36

GND PCI1_IRDY# PCI1_TRDY# +3.3V

37 38 37 38

PCI1_DEVSEL# +5V GND PCI1_STOP#

39 40 39 40

GND PMC1_LOCK# PCI1_PERR# GND

41 42 41 42

rsvd rsvd +3.3V PCI1_SERR#

43 44 43 44

PCI1_PAR GND PCI0_C/BE1# GND

45 46 45 46

VIO PCI1_AD15 PCI1_AD14 PCI1_AD13

47 48 47 48

PCI0_AD12 PCI1_AD11 PCI1_M66EN PCI1_AD10

49 50 49 50

PCI0_AD9 +5V PCI1_AD8 +3.3V

51 52 51 52

GND PCI1_C/BE0# PCI1_AD7 rsvd

53 54 53 54

PCI1_AD6 PCI1_AD5 +3.3V rsvd

55 56 55 56

PCI1_AD4 GND rsvd GND

57 58 57 58

VIO PCI1_AD3 rsvd rsvd

59 60 59 60

PCI1_AD2 PCI1_AD1 GND rsvd

61 62 61 62

PCI1_AD0 +5V PCI0_ACK64# +3.3V

63 64 63 64

GND PCI0_REQ64# GND rsvd

NOTES:

BUSMODE1#: C2K ignores this signal.

a.